| ( |   | ) | <b>Preliminary Specification</b> |

|---|---|---|----------------------------------|

| ( | ٧ | ) | Final Specification              |

| Module           | 27" Color TFT-LCD |                     |

|------------------|-------------------|---------------------|

| Model Name       | M270DTN01.5       | A PIU               |

| Suffix Name      |                   | -10 <sup>11</sup> 0 |

| Document version | D01               | , ce                |

|             | Document  |                   |  |  |  |

|-------------|-----------|-------------------|--|--|--|

| APPROVED BY | James Kuo | Date: 2015/10/19  |  |  |  |

| PREPARED BY | Junda Lin | Date : 2015/10/19 |  |  |  |

| CUSTOMER APPROVED AND FEEDBACK |  |        |  |

|--------------------------------|--|--------|--|

| CUSTOMER                       |  |        |  |

| APPROVED BY                    |  | Date : |  |

Note: This Specification is subject to change without notice.

|     | <u>Contents</u>            |       |

|-----|----------------------------|-------|

|     | ltem                       | Page  |

| 1.  | Handling Precautions       | 4     |

| 2.  | General Description        | 5     |

| 3.  | Functional Block Diagram   | 10 IO |

| 4.  | Absolute Maximum Ratings   | 16    |

| 5.  | Electrical characteristics | 17    |

| 6.  | Signal Characteristic      | 18    |

| 7.  | Connector & Pin Assignment | 28    |

| 8.  | Reliability Test           | 35    |

| 9.  | Shipping Label             | 36    |

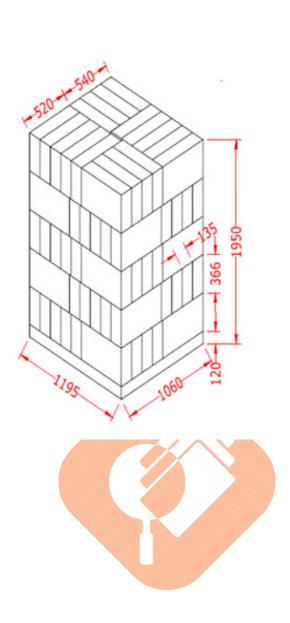

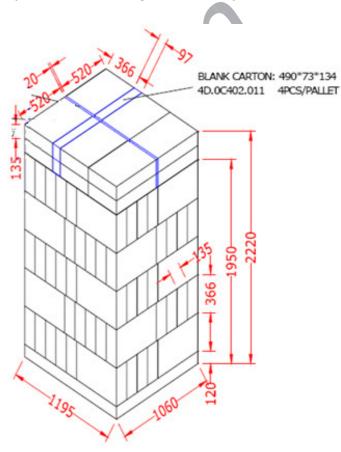

| 10. | Packing Precautions 5      | 37    |

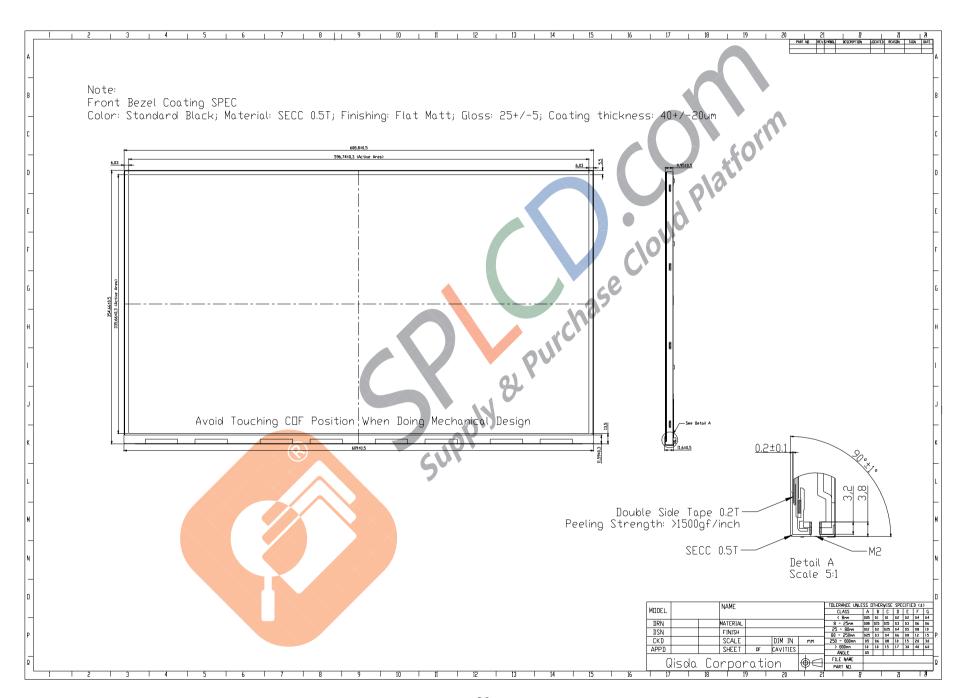

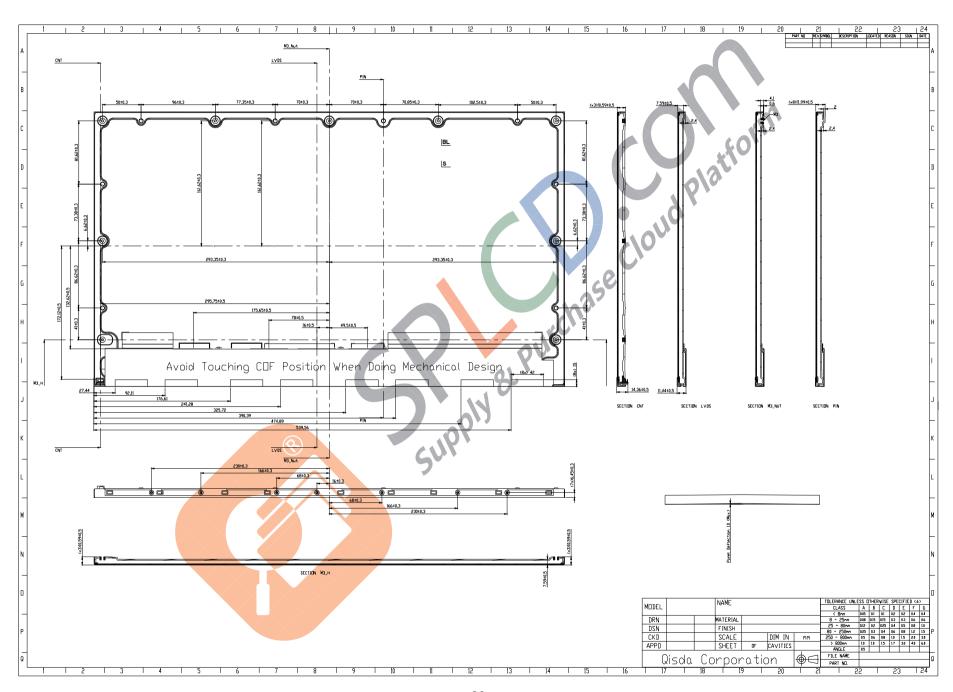

| 11. | Drawing                    | 38    |

|     |                            |       |

|     |                            |       |

|     |                            |       |

|     |                            |       |

|     |                            |       |

|                     | Record of Revision |      |               |  |  |

|---------------------|--------------------|------|---------------|--|--|

| Document<br>Version | Date<br>(Y/M/D)    | Page | Description   |  |  |

| D01                 | 2015/10/19         |      | First Version |  |  |

|                     |                    |      |               |  |  |

|                     |                    |      |               |  |  |

|                     |                    |      | "corin"       |  |  |

|                     |                    |      | plati         |  |  |

|                     |                    |      | • Jud         |  |  |

|                     |                    |      |               |  |  |

|                     |                    |      | chase         |  |  |

|                     |                    |      | O'II'CII'     |  |  |

|                     |                    |      |               |  |  |

|                     |                    |      |               |  |  |

|                     |                    |      | SUPP          |  |  |

|                     |                    |      | 7             |  |  |

|                     |                    |      |               |  |  |

|                     |                    |      |               |  |  |

|                     |                    |      |               |  |  |

|                     |                    |      |               |  |  |

|                     |                    |      |               |  |  |

|                     |                    |      |               |  |  |

|                     |                    |      |               |  |  |

# 1. Handling Precautions

- 1. Since front polarizer is easily damaged, pay attention not to scratch it.

- 2. Be sure to turn off power supply when inserting or disconnecting from input connector.

- 3. Wipe off water drop immediately. Long contact with water may cause discoloration or spots.

- 4. When the panel surface is soiled, wipe it with absorbent cotton or other soft cloth.

- 5. Since the panel is made of glass, it may break or crack if dropped or bumped on hard surface.

- 6. Since CMOS LSI is used in this module, take care of static electricity and insure human earth when handling.

- 8. Do not press the reflector sheet at the back of the module to any directions.

9. In case if a Module has to be put back into the module to any directions. 9. In case if a Module has to be put back into the packing container slot after once it was taken out from the container, do not press the center of the LED lightbar edge. Instead, press at the far ends of the LED light bar edge softly. Otherwise the TFT Module may be damaged.

- 10. At the insertion or removal of the Signal Interface Connector, be sure not to rotate nor tilt the Interface Connector of the TFT Module.

- 11. After installation of the TFT Module into an enclosure, do not twist nor bend the TFT Module even momentary. At designing the enclosure, it should be taken into consideration that no bending/twisting forces are applied to the TFT Module from outside. Otherwise the TFT Module may be damaged.

- 12. Small amount of materials having no flammability grade is used in the LCD module. The LCD module should be supplied by power complied with requirements of Limited Power Source (IEC60950 or UL1950), or be applied exemption.

- 13. Please avoid touching COF Position while you are doing mechanical design.

- 14. When storing modules as spares for a long time, the following precaution is necessary:

- a. Store them in a dark place. Do not expose the module to sunlight or fluorescent light.

- b. Keep the temperature between  $5^{\circ}$ C and  $35^{\circ}$ C at normal humidity.

# 2. General Description

This specification applies to the 27 inch-FHD Color a-Si TFT-LCD Module M270DTN01.5. The display supports the QHD -  $2560(H) \times 1440(V)$  screen format and 16.7M colors (RGB 8-bits data). The input interface is 8 port LVDS and this module doesn't contain a driver board for backlight.

# **Display Characteristics**

The following items are characteristics summary on the table under 25°C condition:

| ITEMS                                          | Unit              | SPECIFICATIONS                                                                                        |

|------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------|

| Screen Diagonal                                | mm                | 684.67(27.0")                                                                                         |

| Active Area                                    | mm                | 596.74 (H) × 335.66 (V)                                                                               |

| Pixels H x V                                   |                   | 2560(x3) x 1440                                                                                       |

| Pixel Pitch                                    | um                | 233.1 (per one triad) ×233.1                                                                          |

| Pixel Arrangement                              |                   | R.G.B. Vertical Stripe                                                                                |

| Display Mode                                   |                   | TN Mode, Normally White                                                                               |

| White Luminance ( Center )                     | cd/m <sup>2</sup> | 350 cd/m <sup>2</sup> (Typ.)                                                                          |

| Contrast Ratio                                 |                   | 1000(Typ.)                                                                                            |

| Optical Response Time                          | msec              | 5ms (Typ., on/off)                                                                                    |

| Power Consumption<br>(VDD line + LED line)     | Watt              | 33.8 W<br>LCD module:PDD(Typ)=6.5 @Black pattern Fv=144 Hz<br>Backlight unit:PBLu(Typ)=27.3 @ls=120mA |

| Color gamut                                    | %                 | 72                                                                                                    |

| Weight                                         | Grams             | 2500 (Typ.)                                                                                           |

| Outline Dimension                              | mm                | 609.00(H)×354.66(V)×11.60(D)                                                                          |

| Electrical Interface                           |                   | 8 port LVDS                                                                                           |

| Support Color                                  |                   | 16.7M colors (RGB 8-bit )                                                                             |

| Surface Treatment                              |                   | Anti-Glare, 3H                                                                                        |

| Temperature Range Operating Storage (Shipping) | °C<br>∘C          | 0 to +50<br>-20 to +60                                                                                |

| RoHS Compliance                                |                   | RoHS Compliance                                                                                       |

| TCO Compliance                                 |                   | TCO 6.0 Compliance                                                                                    |

# **Optical Characteristics**

The optical characteristics are measured on the following test condition.

#### **Test Condition:**

- I.Equiment setuo:Please refer to Note 2-I

- 2.Panel Lighting:30 Minutes

- 3.VDD=12.0V, Fv=144Hz, Is=120mA, Ta=2.5 $^{\circ}$ C

| Symbol          | Description                        |                  | Min.  | Тур.  | Max.       | Unit     | Remark      |

|-----------------|------------------------------------|------------------|-------|-------|------------|----------|-------------|

| Lw              | White Luminance (Center of screen) |                  | 300   | 350   |            | [cd/m²]  | Note 2-1    |

| Luni            | Luminance Uniformity               | (9 points)       | 75    | 80    |            | [%]      | Note 2-1    |

| CR              | Contrast Ratio (Center             | of screen)       | 600   | 1000  | A0         | -        | Note 2-1    |

| θR              | Horizontal Viewing Angle           | Right            | 75    | 85    | C,         |          |             |

| θ∟              | (CR=10)                            | Left             | 75    | 85    | <b>6</b> - |          |             |

| Фп              | <b>Vertical Viewing Angle</b>      | Up               | 70    | 80    | -          |          |             |

| ФL              | (CR=10)                            | Down             | 70    | 80    | -          | [degree] | Note 2-2    |

| θR              | Horizontal Viewing Angle           | Right            | 75    | 88    | -          | [aog.co] | By SR-3     |

| θι              | (CR=5)                             | Left             | 75    | 88    | -          |          |             |

| ΦR              | Vertical Viewing Angle             | Up               | 70    | 85    | -          |          |             |

| ФL              | (CR=5)                             | Down             | 70    | 85    | -          |          |             |

| TR              |                                    | Rising Time      | -     | 3.5   | 5.5        |          | Note 2-4    |

| TL              | Response Time                      | Falling Time     | -     | 1.5   | 2.5        | [msec]   | By TRD-1000 |

|                 |                                    | Rising + Falling | -     | 5     | 8          |          |             |

| Rx              |                                    | Red x            | 0.616 | 0.646 | 0.676      |          |             |

| Ry              |                                    | Red y            | 0.314 | 0.344 | 0.374      |          |             |

| Gx              |                                    | Green x          | 0.285 | 0.315 | 0.345      |          |             |

| Gy              | Color Coordinates                  | Green y          | 0.595 | 0.625 | 0.655      |          | D 0D 0      |

| Bx              | (CIE 1931)                         | Blue x           | 0.110 | 0.140 | 0.170      |          | By SR-3     |

| Ву              |                                    | Blue y           | 0.015 | 0.045 | 0.075      |          |             |

| Wx              |                                    | White x          | 0.283 | 0.313 | 0.343      |          |             |

| Wy              |                                    | White y          | 0.299 | 0.329 | 0.359      |          |             |

| СТ              | Crosstalk                          | •                | -     | -     | 1.5        | [%]      | Note 2-8    |

| F <sub>dB</sub> | Flicker (Center of screen)         |                  | -     | -     | -20        | [dB]     | Note 2-9    |

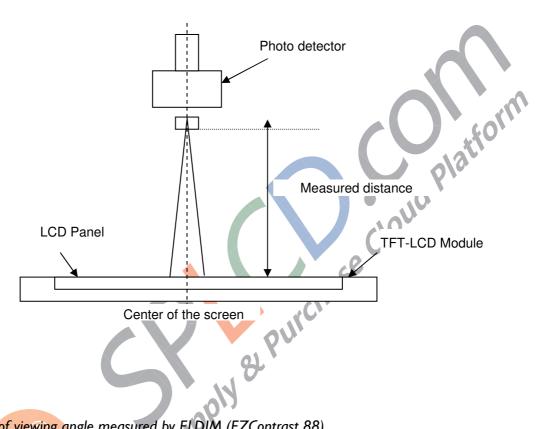

#### Note 2-1: Measurement method

The LCD module should be stabilized at given temperature for 30 minutes to avoid abrupt temperature change during measuring (at surface 35°C). In order to stabilize the luminance, the measurement should be executed after lighting Backlight for 30 minutes in a stable, windless and dark room.

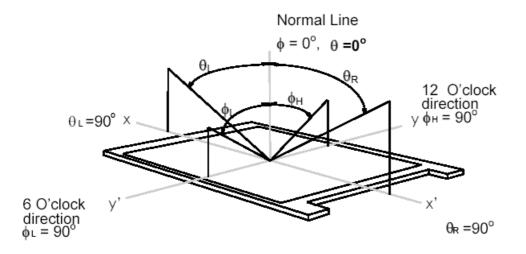

# Note 2-2: Definition of viewing angle measured by ELDIM (EZContrast 88)

Viewing angle is the measurement of contrast ratio  $\ge$ 10, at the screen center, over a 180° horizontal and 180° vertical range (off-normal viewing angles). The 180° viewing angle range is broken down as follows; 90° (θ) horizontal left and right and 90° (Φ) vertical, high (up) and low (down). The measurement direction is typically perpendicular to the display surface with the screen rotated about its center to develop the desired measurement viewing angle.

#### Note 2-3: Contrast ratio is measured by TOPCON SR-3

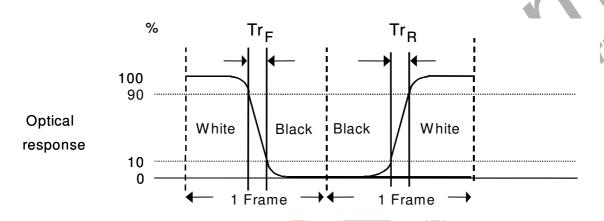

#### Note 2-4: Definition of Response time measured by Westar TRD-100A

The output signals of photo detector are measured when the input signals are changed from "Black" to "White" (rising time,  $T_R$ ), and from "White" to "Black" (falling time,  $T_F$ ), respectively. The response time is interval between the 10% and 90% of optical response.( *Black & White color definition: Please refer section* 3.4.3)

Note 2-5: Color chromaticity and coordinates (CIE) is measured by TOPCON SR-3

Note 2-6: Central luminance is measured by TOPCON SR-3

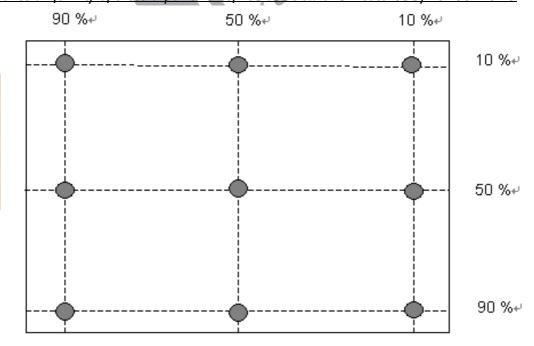

Note 2-7: Luminance uniformity of these 9 points is defined as below and measured by TOPCON SR-3

Uniformity =

$$\frac{\text{Minimum Luminance in 9 points (1-9)}}{\text{Maximum Luminance in 9 Points (1-9)}}$$

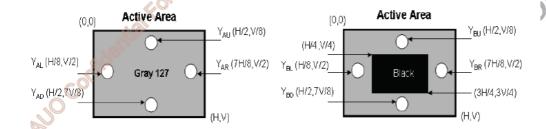

#### Note 2-8: Crosstalk is defined as below and measured by TOPCON SR-3

Crosstalk measurement

#### Definition:

$CT = Max. (CT_H, CT_V);$

#### Where

a. Maximum Horizontal Crosstalk:

$$CT_H = Max. (|Y_{BL} - Y_{AL}| / Y_{AL} \times 100 \%, |Y_{BR} - Y_{AR}| / Y_{AR} \times 100 \%);$$

Maximum Vertical Crosstalk:

$$CT_V = Max. (|Y_{BU} - Y_{AU}|/Y_{AU} \times 100\%, |Y_{BD} - Y_{AD}|/Y_{AD} \times 100\%);$$

b.  $Y_{AU}$ ,  $Y_{AD}$ ,  $Y_{AL}$ ,  $Y_{AR}$  = Luminance of measured location without Black pattern  $Y_{BU}$ ,  $Y_{BD}$ ,  $Y_{BL}$ ,  $Y_{BR}$  = Luminance of measured location with Black pattern

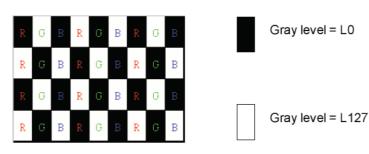

# Note 2-9: Test Patern: Subchecker Pattern measured by TOPCON SR-3

Flicker measurement

a. Test pattern: It is listed as following.

R: Red, G: Green, B:Blue

b. Measured position: Center of screen & perpendicular to the screen

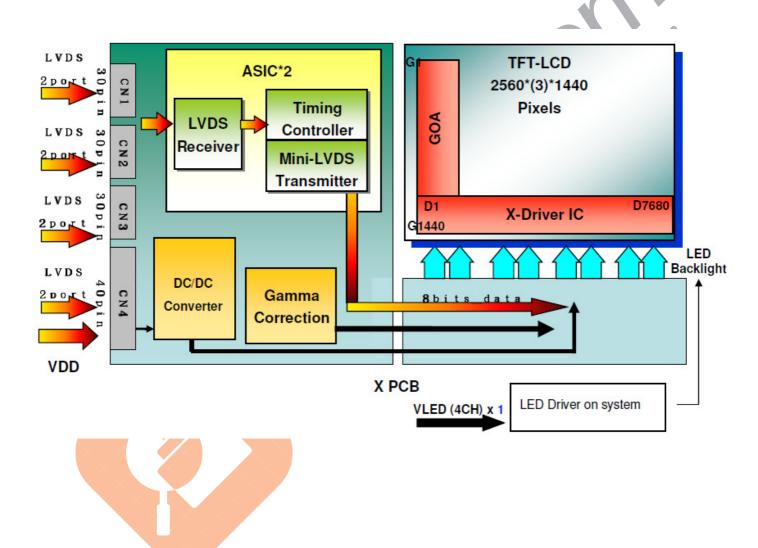

# 3. Functional Block Diagram

#### 3.TFT-LCD

#### 3-1. Blockv Diagram

The following shows the block diagram of the 27 inch Color TFT-LCD Module

# 3.2. Signal Description

| PIN# | Symbol  | DESCRIPTION                                          |

|------|---------|------------------------------------------------------|

| 1    | R1 0N   | Negative LVDS differential data input (Port1 data)   |

| 2    | R1 0P   | Positive LVDS differential data input (Port1 data)   |

| 3    | R1 1N   | Negative LVDS differential data input (Port1 data)   |

| 4    | R1 1P   | Positive LVDS differential data input (Port1 data)   |

| 5    | R1 2N   | Negative LVDS differential data input (Port1 data)   |

| 6    | R1 2P   | Positive LVDS differential data input (Port1 data)   |

| 7    | GND     | Ground                                               |

| 8    | R1 CLKN | Negative LVDS differential clock input (Port1 clock) |

| 9    | R1 CLKP | Positive LVDS differential clock input (Port1 clock) |

| 10   | GND     | Ground                                               |

| 11   | R2 3N   | Negative LVDS differential data input (Port1 data)   |

| 12   | R2 3P   | Positive LVDS differential data input (Port1 data)   |

| 13   | NC      | No connection (for AUO test only. Do not connect)    |

| 14   | NC      | No connection (for AUO test only. Do not connect)    |

| 15   | GND     | Ground                                               |

| 16   | R2 0N   | Negative LVDS differential data input (Port2 data)   |

| 17   | R2 0P   | Positive LVDS differential data input (Port2 data)   |

| 18   | R2 1N   | Negative LVDS differential data input (Port2 data)   |

| 19   | R2 1P   | Positive LVDS differential data input (Port2 data)   |

| 20   | R2 2N   | Negative LVDS differential data input (Port2 data)   |

| 21   | R2 2P   | Positive LVDS differential data input (Port2 data)   |

| 22   | GND     | Ground                                               |

| 23   | R2 CLKP | Negative LVDS differential clock input (Port2 clock) |

| 24   | R2 CLKP | Positive LVDS differential clock input (Port2 clock) |

| 25   | GND     | Ground                                               |

| 26   | R2 3N   | Negative LVDS differential data input (Port2 data)   |

| 27   | R2 3P   | Positive LVDS differential data input (Port2 data)   |

| 28   | NC      | No connection (for AUO test only. Do not connect)    |

| 29   | NC      | No connection (for AUO test only. Do not connect)    |

| 30   | NC      | No connection (for AUO test only. Do not connect)    |

| PIN# | Symbol        | DESCRIPTION                                          |

|------|---------------|------------------------------------------------------|

| 1    | R3 0N         | Negative LVDS differential data input (Port3 data)   |

| 2    | R3 0P         | Positive LVDS differential data input (Port3 data)   |

| 3    | R3 1N         | Negative LVDS differential data input (Port3 data)   |

| 4    | R3 1P         | Positive LVDS differential data input (Port3 data)   |

| 5    | R3 2N         | Negative LVDS differential data input (Port3 data)   |

| 6    | R3 2P         | Positive LVDS differential data input (Port3 data)   |

| 7    | GND           | Ground                                               |

| 8    | R3 CLKN       | Negative LVDS differential clock input (Port3 clock) |

| 9    | R3 CLKP       | Positive LVDS differential clock input (Port3 clock) |

| 10   | GND           | Ground                                               |

| 11   | R3 3N         | Negative LVDS differential data input (Port3 data)   |

| 12   | R3 3P         | Positive LVDS differential data input (Port3 data)   |

| 13   | NC            | No connection (for AUO test only. Do not connect)    |

| 14   | NC            | No connection (for AUO test only. Do not connect)    |

| 15   | GND           | Ground                                               |

| 16   | R4 0N         | Negative LVDS differential data input (Port4 data)   |

| 17   | R4 0P         | Positive LVDS differential data input (Port4 data)   |

| 18   | R4 1N         | Negative LVDS differential data input (Port4 data)   |

| 19   | R4 1P         | Positive LVDS differential data input (Port4 data)   |

| 20   | R4 2N         | Negative LVDS differential data input (Port4 data)   |

| 21   | R4 2P         | Positive LVDS differential data input (Port4 data)   |

| 22   | GND           | Ground                                               |

| 23   | R4 CLKP       | Negative LVDS differential clock input (Port4 clock) |

| 24   | R4 CLKP       | Positive LVDS differential clock input (Port4 clock) |

| 25   | GND           | Ground                                               |

| 26   | R4 3N         | Negative LVDS differential data input (Port4 data)   |

| 27   | R4 3P         | Positive LVDS differential data input (Port4 data)   |

| 28   | NC            | No connection (for AUO test only. Do not connect)    |

| 29   | NC            | No connection (for AUO test only. Do not connect)    |

| 30   | Polarity_SYNC | Polarity SYNC (O)                                    |

| PIN# | Symbol    | DESCRIPTION                                          |

|------|-----------|------------------------------------------------------|

| 1    | R5 0N     | Negative LVDS differential data input (Port5 data)   |

| 2    | R5 0P     | Positive LVDS differential data input (Port5 data)   |

| 3    | R5 1N     | Negative LVDS differential data input (Port5 data)   |

| 4    | R5 1P     | Positive LVDS differential data input (Port5 data)   |

| 5    | R5 2N     | Negative LVDS differential data input (Port5 data)   |

| 6    | R5 2P     | Positive LVDS differential data input (Port5 data)   |

| 7    | GND       | Ground                                               |

| 8    | R5 CLKN   | Negative LVDS differential clock input (Port5 clock) |

| 9    | R5 CLKP   | Positive LVDS differential clock input (Port5 clock) |

| 10   | GND       | Ground                                               |

| 11   | R5 3N     | Negative LVDS differential data input (Port5 data)   |

| 12   | R5 3P     | Positive LVDS differential data input (Port5 data)   |

| 13   | NC        | No connection (for AUO test only. Do not connect)    |

| 14   | NC        | No connection (for AUO test only. Do not connect)    |

| 15   | GND       | Ground                                               |

| 16   | R6 0N     | Negative LVDS differential data input (Port6 data)   |

| 17   | R6 0P     | Positive LVDS differential data input (Port6 data)   |

| 18   | R6 1N     | Negative LVDS differential data input (Port6 data)   |

| 19   | R6 1P     | Positive LVDS differential data input (Port6 data)   |

| 20   | R6 2N     | Negative LVDS differential data input (Port6 data)   |

| 21   | R6 2P     | Positive LVDS differential data input (Port6 data)   |

| 22   | GND       | Ground                                               |

| 23   | R6 CLKP   | Negative LVDS differential clock input (Port6 clock) |

| 24   | R6 CLKP   | Positive LVDS differential clock input (Port6 clock) |

| 25   | GND       | Ground                                               |

| 26   | R6 3N     | Negative LVDS differential data input (Port6 data)   |

| 27   | R6 3P     | Positive LVDS differential data input (Port6 data)   |

| 28   | NC        | No connection (for AUO test only. Do not connect)    |

| 29   | NC        | No connection (for AUO test only. Do not connect)    |

| 30   | 3D_EN (I) | 3D_EN (I)                                            |

| PIN# | Symbol  | DESCRIPTION                                          |

|------|---------|------------------------------------------------------|

| 1    | R7 0N   | Negative LVDS differential data input (Port7 data)   |

| 2    | R7 0P   | Positive LVDS differential data input (Port7 data)   |

| 3    | R7 1N   | Negative LVDS differential data input (Port7 data)   |

| 4    | R7 1P   | Positive LVDS differential data input (Port7 data)   |

| 5    | R7 2N   | Negative LVDS differential data input (Port7 data)   |

| 6    | R7 2P   | Positive LVDS differential data input (Port7 data)   |

| 7    | GND     | Ground                                               |

| 8    | R7 CLKN | Negative LVDS differential clock input (Port7 clock) |

| 9    | R7 CLKP | Positive LVDS differential clock input (Port7 clock) |

| 10   | GND     | Ground                                               |

| 11   | R7 3N   | Negative LVDS differential data input (Port7 data)   |

| 12   | R7 3P   | Positive LVDS differential data input (Port7 data)   |

| 13   | NC      | No connection (for AUO test only. Do not connect)    |

| 14   | NC      | No connection (for AUO test only. Do not connect)    |

| 15   | GND     | Ground                                               |

| 16   | R8 0N   | Negative LVDS differential data input (Port8 data)   |

| 17   | R8 0P   | Positive LVDS differential data input (Port8 data)   |

| 18   | R8 1N   | Negative LVDS differential data input (Port8 data)   |

| 19   | R8 1P   | Positive LVDS differential data input (Port8 data)   |

| 20   | R8 2N   | Negative LVDS differential data input (Port8 data)   |

| 21   | R8 2P   | Positive LVDS differential data input (Port8 data)   |

| 22   | GND     | Ground                                               |

| 23   | R8 CLKP | Negative LVDS differential clock input (Port8 clock) |

| 24   | R8 CLKP | Positive LVDS differential clock input (Port8 clock) |

| 25   | GND     | Ground                                               |

| 26   | R8 3N   | Negative LVDS differential data input (Port8 data)   |

| 27   | R8 3P   | Positive LVDS differential data input (Port8 data)   |

| 28   | NC      | No connection (for AUO test only. Do not connect)    |

| 29   | NC      | No connection (for AUO test only. Do not connect)    |

| 30   | NC      | No connection (for AUO test only. Do not connect)    |

| 31   | NC      | No connection (for AUO test only. Do not connect)    |

| 32   | NC      | No connection (for AUO test only. Do not connect)    |

| 33   | NC      | No connection (for AUO test only. Do not connect)    |

| 34   | GND     | Ground                                               |

| 35   | GND     | Ground                                               |

| 36   | NC      | No connection (for AUO test only. Do not connect)    |

# **Product Specification**

| 37 | VDD | Power Supply Input Voltage |

|----|-----|----------------------------|

| 38 | VDD | Power Supply Input Voltage |

| 39 | VDD | Power Supply Input Voltage |

| 40 | VDD | Power Supply Input Voltage |

# 4. Absolute Maximum Ratings

Absolute maximum ratings of the module are as following:

**Backlight Unit**

|             | Symbol | Min | Тур | Max | Unit | Conditions   |

|-------------|--------|-----|-----|-----|------|--------------|

| LED Current | ILED   | -   | 120 | 132 | [mA] | Note 4-1,4-2 |

**Absolute Ratings of Environment**

| Diolace Itacings of Eliviro                  | ·····ciic |      |      |       |                               |

|----------------------------------------------|-----------|------|------|-------|-------------------------------|

| Item                                         | Symbol    | Min. | Max. | Unit  | Conditions                    |

| Operating Temperature                        | ТОР       | 0    | +50  | [°C]  | Note 4-3                      |

| Center Glass Surface temperature (Operation) | TGS       | 0    | +65  | [°C]  | Note 4-3 Function judged only |

| Operation Humidity                           | НОР       | 5    | 90   | [%RH] | Note 4-3                      |

| Storage Temperature                          | TST       | -20  | +60  | [°C]  |                               |

| Storage Humidity                             | HST       | 5    | 90   | [%RH] |                               |

Note 4-1: With in Ta (25  $^{\circ}$ C)

Note 4-2: Permanent damage to the device may occur if exceeding maximum values

Note 4-3: For quality perfermance, please refer to AUO IIS(Incoming Inspection Standard).

- 1. 90% RH Max ( Ta  $\leq 39^{\circ}$ C)

- 2. Max wet-bulb temperature at 39°C or less (1'a  $\leq$  39°C)

- 3. No condensation

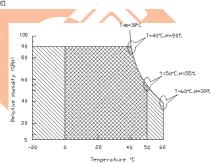

**Operating Range**

Storage Range

# 5. Electrical characteristics-TFT LCD Module

## **Power Specification**

Input power specifications are as following:

Permanent damage may occur if exceeding the following maximum rating.

| Symbol | Descripition                  | Min     | Max | Unit   | Remark  |

|--------|-------------------------------|---------|-----|--------|---------|

| VDD    | Power Supply<br>Input Voltage | GND-0.3 | 14  | [Volt] | Ta=25°C |

**Recommended Operating Condition**

| Symbol | Descripition                        | Min  | Тур | Max  | Unit   | Remark                                  |

|--------|-------------------------------------|------|-----|------|--------|-----------------------------------------|

| VDD    | Power Supply<br>Input Voltage       | 10.8 | 12  | 13.2 | [Volt] | · id P                                  |

| IDD    | Power Supply<br>Input Current (RMS) | -    | 0.5 | 1.3  | [A]    | VDD= 12.0V, All Black Pattern At 144Hz, |

| PDD    | VDD Power<br>Consumption            | -    | 6.5 | 15.6 | [Watt] | VDD= 12.0V, All Black Pattern At 144Hz  |

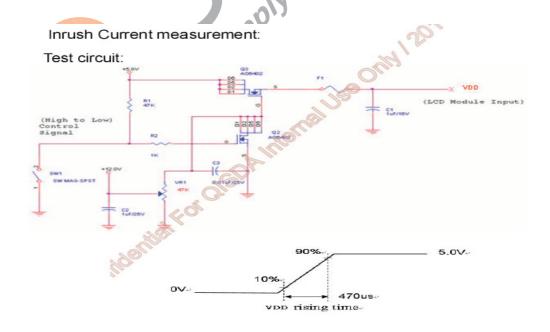

| IRush  | Inrush Current                      | -    |     | 3.0  | [A]    | Note 5-1                                |

| VDDrp  | Allowable LCD<br>Ripple Voltage     | -    |     | 500  | [mV]   | VDD= 12.0V, All Black Pattern At 144Hz  |

Note 5-1: Measurement conditions:

The duration of VDD rising time: 470us.

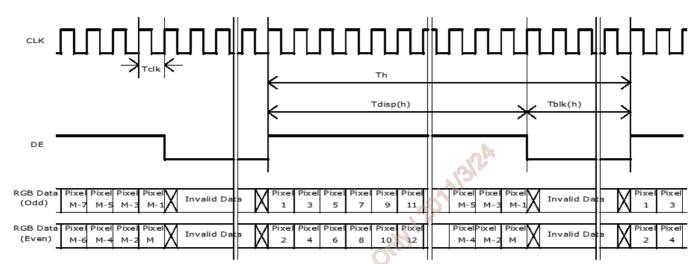

# 6. Signal Characteristic

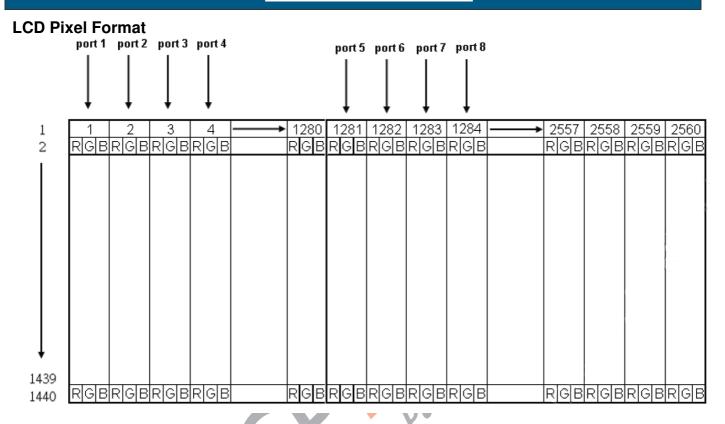

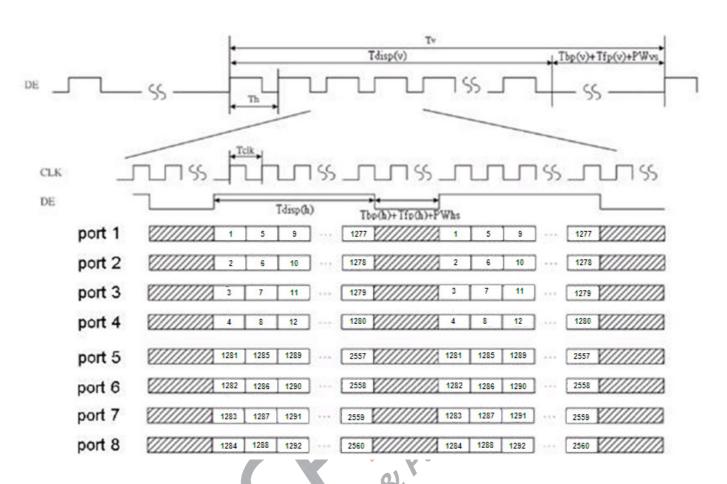

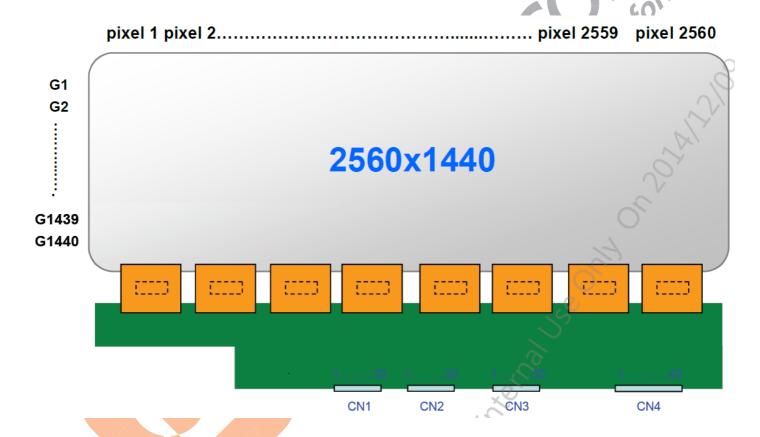

### Note 6-1: The module use 8 port-LVDS interface.

Port 1: 4N+1 N=0,~ 319 (1,5.. 1277pixel)

Port 2: 4N+2 N=0,~ 319 (2,6.. 1278pixel)

Port 3: 4N+3 N=0,~ 319 (3,7.. 1279pixel)

Port 4: 4N+4 N=0,~ 319 (4,8.. 1280pixel)

Port 5: 4N+1281 N=0,~ 319 (1281,1285.. 2557pixel)

Port 6: 4N+1282 N=0,~ 319 (1282,1286.. 2558pixel)

Port 7: 4N+1283 N=0,~ 319 (1283,1287.. 2559pixel)

Port 8: 4N+1284 N=0,~ 319 (1284,1288.. 2560pixel)

### **LVDS Data Format**

|                             | RCLKP  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                             | RCLKN  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                             | R1_0NP | R1R0         R1G0         R1R5         R1R4         R1R3         R1R2         R1R1         R1R0         R1G0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| m = m4 1                    | R1_1NP | R1G1 R1B1 R1B0 R1G5 R1G4 R1G3 R1G2 R1G1 R1B1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| port 1                      | R1_2NP | R1B2 DE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                             | R1_3NP | R1R6         R1B7         R1B6         R1G7         R1G6         R1R7         R1R6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                             | R2_0NP | R2R0         R2G0         R2R5         R2R4         R2R3         R2R2         R2R1         R2R0         R2G0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| port 2                      | R2_1NP | R2G1 R2B1 R2B0 R2G5 R2G4 R2G3 R2G2 R2G1 R2B1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                             | R2_2NP | R2B2 R2B4 R2B3 R2B2 R2B2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                             | R2_3NP | R2R6 R2B7 R2B6 R2G7 R2G6 R2R7 R2R6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                             |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                             | R3_0NP | X R3R0       X R3R5       X R3R4       X R3R3       X R3R2       X R3R1       X R3R0       X R3G0       X R3G0 |

| port 3                      | R3_1NP | R3G1 R3B1 R3B0 R3G5 R3G4 R3G3 R3G2 R3G1 R3B1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| porto                       | R3_2NP | R3B2 R3B5 R3B4 R3B3 R3B2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                             | R3_3NP | R3R6 R3B7 R3B6 R3G7 R3G6 R3R7 R3R6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                             | R4_0NP | R4R0         R4G0         R4R5         R4R4         R4R3         R4R2         R4R1         R4R0         R4G0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| entral terror terror terror | R4_1NP | R4G1 R4B1 R4B0 R4G5 R4G4 R4G3 R4G2 R4G1 R4B1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| port 4                      | R4_2NP | R4B2 R4B5 R4B4 R4B3 R4B2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                             | R4_3NP | R4R6 R4B7 R4B6 R4G7 R4G6 R4R7 R4R6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                             |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                             |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                             |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|        | R5_0NP   | R5R0 R5G0 R5R5 R5R4 R5R3 R5R2 R5R1 R5R0 R5G0                                                                              |

|--------|----------|---------------------------------------------------------------------------------------------------------------------------|

| nort E | R5_1NP   | R5G1 R5B1 R5B0 R5G5 R5G4 R5G3 R5G2 R5G1 R5B1                                                                              |

| port 5 | R5_2NP   | R5B2 DE                                                                                                                   |

|        | R5_3NP   | R5R6 R5B7 R5B6 R5G7 R5G6 R5R7 R5R6                                                                                        |

|        | R6_ONP   | R6R0         R6G0         R6R5         R6R4         R6R3         R6R2         R6R1         R6R0         R6G0         R6G0 |

|        | R6_1NP   | R6G1 R6B1 R6B0 R6G5 R6G4 R6G3 R6G2 R6G1 R6B1                                                                              |

| port 6 | R6_2NP   | R6B2 R6B3 R6B2 R6B3 R6B2                                                                                                  |

|        | R6_3NP   | R6R6         R6B7         R6B6         R6G7         R6G6         R6R7         R6R6                                        |

|        | R7_0NP   | R7R0 R7G0 R7R5 R7R4 R7R3 R7R2 R7R1 R7R0 R7G0                                                                              |

| _      | R7_1NP   | R7G1         R7B1         R7B0         R7G5         R7G4         R7G3         R7G2         R7G1         R7B1              |

| port 7 | R7_2NP   | R7B2 R7B4 R7B3 R7B2 R7B2                                                                                                  |

|        | R7_3NP   | R7R6         R7B7         R7B6         R7G7         R7G6         R7R7         R7R6                                        |

|        | R8_ONP   | R8R0                                                                                                                      |

|        | R8_1NP   | R8G1   R8B1   R8B0   R8G5   R8G4   R8G3   R8G2   R8G1   R8B1                                                              |

| port 8 | R8_2NP   | R8B2                                                                                                                      |

|        | R8_3NP   | R8R6                                                                                                                      |

|        | ,,,_,,,, | 500                                                                                                                       |

|        |          |                                                                                                                           |

|        |          |                                                                                                                           |

|        |          |                                                                                                                           |

# **Color versus Input Data**

The following table is for color versus input data (8bit). The higher the gray level, the brighter. the color.

|          | Gray<br>Level |                                               |    |    |    |    |                                |    |    |    |    | Col | or Inp | out D | ata |             |    |    |    |        |    |    |    |    |    |       |

|----------|---------------|-----------------------------------------------|----|----|----|----|--------------------------------|----|----|----|----|-----|--------|-------|-----|-------------|----|----|----|--------|----|----|----|----|----|-------|

| Color    |               | RED data<br>( <b>MSB</b> :R7, <b>LSB</b> :R0) |    |    |    |    | GREEN data<br>(MSB:G7, LSB:G0) |    |    |    |    |     |        |       |     | data<br>LSI |    | )  |    | Remark |    |    |    |    |    |       |

|          |               | R7                                            | R6 | R5 | R4 | R3 | R2                             | R1 | R0 | G7 | G6 | G5  | G4     | G3    | G2  | G1          | G0 | В7 | В6 | B5     | B4 | ВЗ | B2 | B1 | BO |       |

| Black    | -             | 0                                             | 0  | 0  | 0  | 0  | 0                              | 0  | 0  | 0  | 0  | 0   | 0      | 0     | 0   | 0           | 0  | 0  | 0  | 0      | 0  | 0  | 0  | 0  | 0  |       |

| White    | -             | 1                                             | 1  | 1  | 1  | 1  | 1                              | 1  | 1  | 1  | 1  | 1   | 1      | 1     | 1   | 1           | 1  | 1  | 1  | 1      | 1  | 1  | 1  | 1  | 1  |       |

| Gray 127 | -             | 0                                             | 1  | 1  | 1  | 1  | 1                              | 1  | 1  | 0  | 1  | 1   | 1      | 1     | 1   | 1           | 1  | 0  | 1  | 1      | 1  | 1  | 1  | 1  | 1  |       |

|          | Ш             | 0                                             | 0  | 0  | 0  | 0  | 0                              | 0  | 0  | 0  | 0  | 0   | 0      | 0     | 0   | 0           | 0  | 0  | 0  | 0      | 0  | 0  | 0  | 0  | 0  | Black |

| Red      | :             | :                                             | :  | :  | :  | :  | :                              | :  | :  | :  | :  | :   | :      | :     | :   | :           | :  | :  | :  | :      | :  | :  | :  | :  | :  |       |

| Red      | L255          | 1                                             | 1  | 1  | 1  | 1  | 1                              | 1  | 1  | 0  | 0  | 0   | 0      | 0     | 0   | 0           | 0  | 0  | 0  | 0      | 0  | 0  | 0  | 0  | 0  |       |

|          | Ш             | 0                                             | 0  | 0  | 0  | 0  | 0                              | 0  | 0  | 0  | 0  | 0   | 0      | 0     | 0   | 0           | 0  | 0  | 0  | 0      | 0  | 0  | 0  | 0  | 0  | Black |

| Green    | :             | :                                             | :  | :  | :  | :  |                                |    | :  | :  | :  |     |        | :     | :   |             | :  | :  | :  | :      | :  | :  | :  | :  | :  |       |

|          | L255          | 0                                             | 0  | 0  | 0  | 0  | 0                              | 0  | 0  | 1  | 1  | 1   | 1      | 1     | 1   | 1           | 1  | 0  | 0  | 0      | 0  | 0  | 0  | 0  | 0  |       |

|          | Ш             | 0                                             | 0  | 0  | 0  | 0  | 0                              | 0  | 0  | 0  | 0  | 0   | 0      | 0     | 0   | 0           | 0  | 0  | 0  | 0      | 0  | 0  | 0  | 0  | 0  | Black |

| Blue     | :             | :                                             | :  | :  | :  | :  | :                              | :  | :  | :  | :  | :   | :      | :     | :   | :           | :  | :  | :  | :      | :  | :  | :  | :  | :  |       |

|          | L255          | 0                                             | 0  | 0  | 0  | 0  | 0                              | 0  | 0  | 0  | 0  | 0   | 0      | 0     | 0   | 0           | 0  | 1  | 1  | 1      | 1  | 1  | 1  | 1  | 1  |       |

# **LVDS Specification**

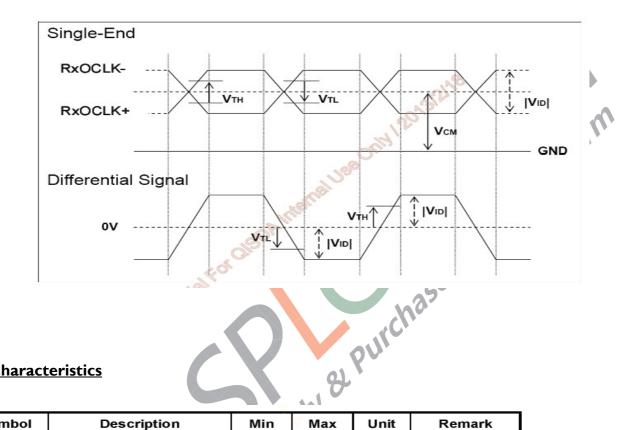

DC Characteristics of each signal are as following:

| Symbol          | Parameter                  | Min  | Тур  | Max  | Units |                       |

|-----------------|----------------------------|------|------|------|-------|-----------------------|

| V               | Differential Input High    |      | _    | +100 | mV    | VICM = 1.2V           |

| V <sub>TH</sub> | Threshold                  | -    | -    | +100 | IIIV  | Note 1                |

| V               | Differential Input Low     | 100  |      |      | \/    | VICM = 1.2V           |

| V <sub>TL</sub> | Threshold                  | -100 | -    | -    | mV    | Note 1                |

| V <sub>ID</sub> | Input Differential Voltage | 100  | -    | 600  | mV    | Note 6-2              |

| V               | Differential Input         | .10  | .40  | .45  | V     | VTH-VTL = 200MV (max) |

| V <sub>CM</sub> | Common Mode Voltage        | +1.0 | +1.2 | +1.5 | V     | Note 1                |

#### Note 6-2: LVDS Signal Waveform

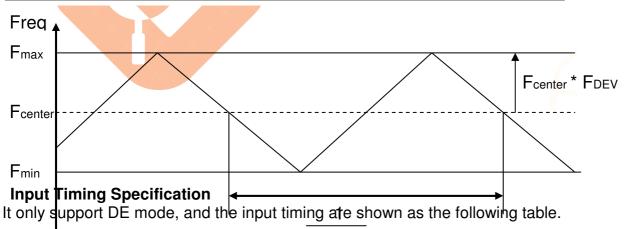

### **AC Characteristics**

| Symbol           | Description                                                              | Min | Max | Unit | Remark |

|------------------|--------------------------------------------------------------------------|-----|-----|------|--------|

| F <sub>DEV</sub> | Maximum deviation of input clock frequency during Spread Spectrum        | 1   | ± 3 | %    |        |

| F <sub>MOD</sub> | Maximum modulation<br>frequency of input clock<br>during Spread Spectrum | 1   | 200 | KHz  |        |

**FMOMin** Symbol Description Тур Max Unit Remark

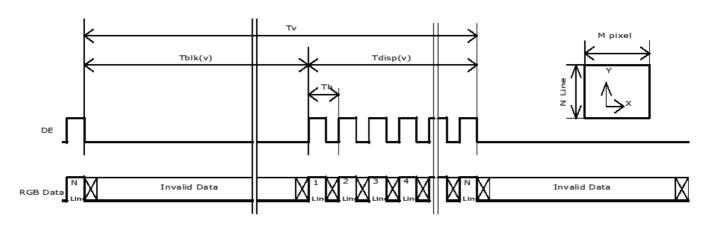

| Tv       |                    | Period    | 1452 | 1481  | 8192  | Th   |          |

|----------|--------------------|-----------|------|-------|-------|------|----------|

| Tdisp(v) | Vertical Section   | Active    | 1440 | 1440  | 1440  | Th   |          |

| Tblk(v)  | vortion coolion    | Blanking  | 12   | 41    | 6752  | Th   |          |

| Fv       |                    | Frequency | 30   | 120   | 145   | Hz   | Note 6-3 |

| Th       |                    | Period    | 359  | 360   | 1023  | Tclk |          |

| Tdisp(h) | Horizontal Section | Active    | 320  | 320   | 320   | Tclk |          |

| Tblk(h)  | Tionzomai occion   | Blanking  | 39   | 40    | 703   | Tclk |          |

| Fh       |                    | Frequency | 69.7 | 177.7 | 250.6 | KHz  | Note 6-4 |

| Tclk     | LVDS Clock         | Period    | 11.1 | 15.6  | 39.9  | ns   | 1/Fclk   |

| Fclk     | 2.23 0.00K         | Frequency | 25   | 64    | 90    | MHz  | Note 6-5 |

Note 6-3: The optimized setting is 119~145 Hz to driving for good picture quality.

Note 6-4: The equation is listed as following. Please don't exceed the above recommended value.

Fh (Min.) = Fclk (Min.) / Th ((Min.);

Fh (Typ.)= Fclk (Typ.) / Th (Typ.);

Fh (Max.)= Fclk (Max.) / Th (Min.);

Note 6-5: The equation is listed as following. Please don't exceed the above recommended value.

Fclk (Min.) = Fv (Min.) x Th ((Min.) x Tv (Min.);

Fclk (Typ.) = Fv (Typ.) x Th ((Typ.) x Tv (Typ.);

Fv x Th x Tv < Fclk (Max.)

### **Input Timing Diagram**

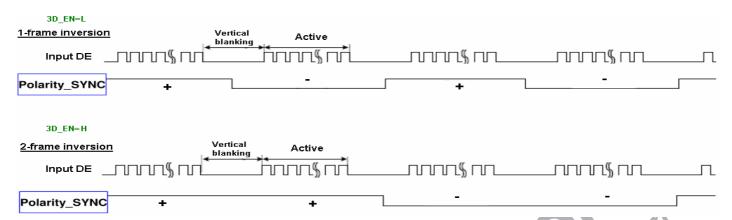

#### **3D Control**

3D Control I/O Characteristics

| Pin#      | Symbol        | I/O | Buffer | Description                    | Remark   |  |  |  |

|-----------|---------------|-----|--------|--------------------------------|----------|--|--|--|

|           |               |     | 50.    | Frame Inversion polarity Index |          |  |  |  |

| CN2_pin30 | Polarity_SYNC | 0   | 4mA    | 3D_EN=L :1-frame inversion     | Note 6-6 |  |  |  |

|           |               |     |        | 3D_EN=H :2-frame inversion     |          |  |  |  |

| CN3_pin30 | 3D_EN         |     | IPL*   | 3D enable control signal       |          |  |  |  |

**IPL:internal pull low**

Note 6-6

# **Product Specification**

**Absolute Maximum Rating**

| Symbol | Description               | Min     | Max | Unit   | Remark |

|--------|---------------------------|---------|-----|--------|--------|

| 3D_EN  | 3D enable control singnal | GND-0.3 | 5.0 | [Volt] | Ta=25  |

**Recommended Operating Condition**

| 0               |                     |                       | Rating |     |     |      |

|-----------------|---------------------|-----------------------|--------|-----|-----|------|

| Symbol          | Parameter           | Condition             | Min 50 | Тур | Max | Unit |

| V <sub>TH</sub> | Input High Voltage  |                       | 2.0    | -   | 3.6 | [V]  |

| V <sub>TL</sub> | Input Low Voltage   | PI                    | 0      | -   | 0.8 | [V]  |

| V <sub>OH</sub> | Output High Voltage | I <sub>OH</sub> =4mA  | 2.4    | -   | 3.4 | [V]  |

| V <sub>OL</sub> | Output Low Voltage  | l <sub>OL</sub> =-4mA | 0      | -   | 0.4 | [V]  |

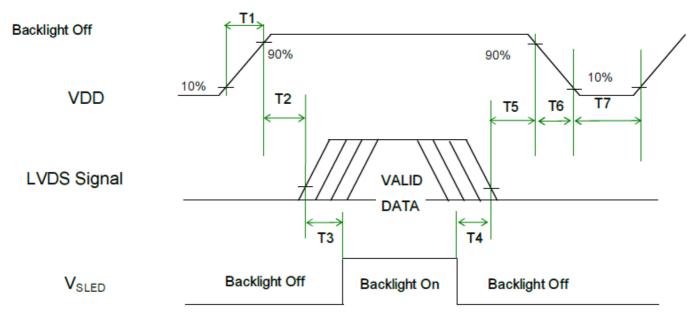

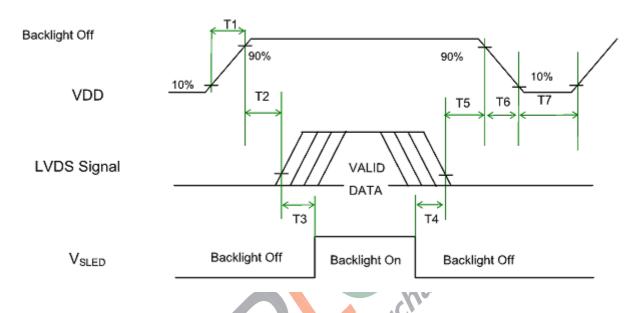

### Power ON/OFF Sequence

VDD power, LVDS signal and backlight on/off sequence are as follows. LVDS signals from any system shall be Hi-Z state when VDD is off.

| Compleal  |      | Value    |            | 11   | Domosile             |

|-----------|------|----------|------------|------|----------------------|

| Symbol    | Min. | Тур.     | Max.       | Unit | Remark               |

| T1        | 0.5  |          | 10 00      | [ms] |                      |

| T2        | 0    | _        | 50         | [ms] |                      |

| Т3        | 500  | -        | -          | [ms] |                      |

| T4        | 100  |          | <b>3</b> - | [ms] |                      |

| Т5        | 0    | J. Ipply | 50         | [ms] | Note 6-7<br>Note 6-8 |

| Т6        | 0    | 5        | 150        | [ms] | Note 6-8             |

| <b>T7</b> | 1000 | _        | -          | [ms] |                      |

**Note 6-7:** Recommend setting T5 = 0ms to avoid electronic noise when VDD is off.

Note 6-8: During T5 and T6 period, please keep the level of input LVDS signals with Hi-Z state.

# **Backlight Unit**

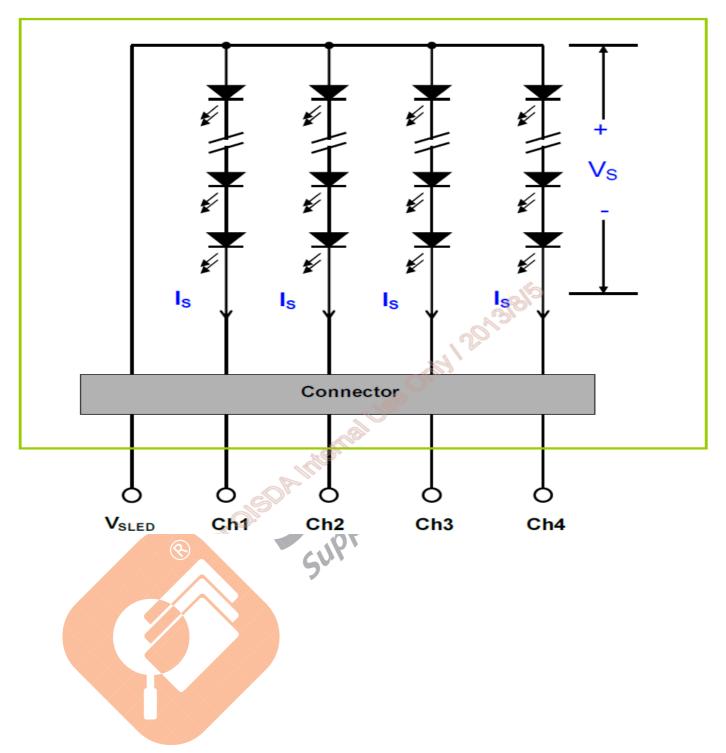

#### **Block Diagram**

The following shows the block diagram of the 27 inch Backlight Unit. And it includes 72 pcs LED in the LED light bar. (4 strings and 18 pcs LED of one string).

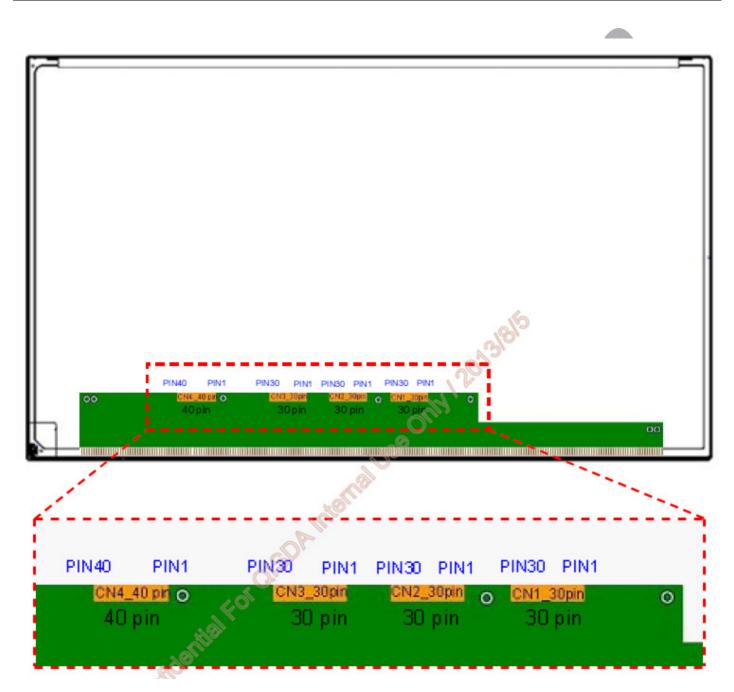

# 7. Connector & Pin Assignment

### **TFT LCD Module**

|                   | Manufacturer | STM               | Starconn          |

|-------------------|--------------|-------------------|-------------------|

| TFT-LCD Connector | Part Number  | MSCKT2407P30HB    | 115F40-R000RA-M3  |

|                   |              | (CNI / CN2 / CN3) | (CN4)             |

| Mating Connector  | Manufacturer | STM or compatible | JAE or compatible |

| Hading Connector  | Part Number  | PK2407P30V        | FI-NX40HL         |

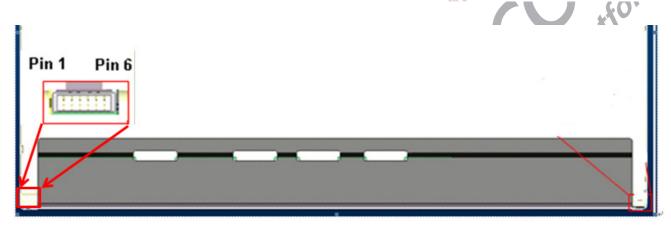

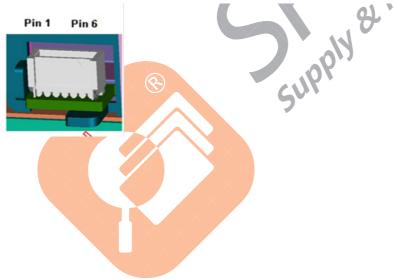

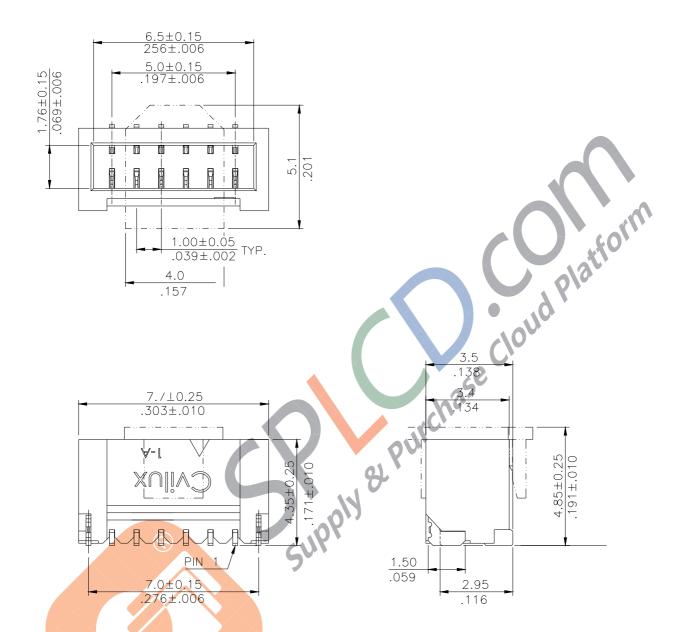

## Connector on Backlight Unit.

This connector is mounted on LED light-bar.

| Pooldisht Connector | Manufacturer | CVILUX                              |

|---------------------|--------------|-------------------------------------|

| Backlight Connector | Part Number  | CII406MIVL0-NH                      |

|                     | Manufacturer | ENTERY                              |

| Mating Connector    |              | H112K-P06N-00B (Non-Locking type)   |

| Tracing Connector   | Part Number  | H112K-P06N-11B(White) (Lockingtype) |

|                     |              | H112K-P06N-13B(Black) (Lockingtype) |

Physical interface is described as for the connector on module. These connectors are capable of accommodating the following signals and will be following components.

## **LED** connector Pin assignment

| Pin no. | Signal name         |

|---------|---------------------|

| 1       | IRLED (current out) |

| 2       | IRLED (current out) |

| 3       | VLED (voltage in)   |

| 4       | VLED (voltage in)   |

| 5       | IRLED (current out) |

| 6       | IRLED (current out) |

**Connector Pin Assignment**

| Pin# | Symbol     | Description                               | Remark |

|------|------------|-------------------------------------------|--------|

| 1    | Ch1        | LED Current Feedback Terminal (Channel 1) |        |

| 2    | Ch2        | LED Current Feedback Terminal (Channel 2) |        |

| 3    | $V_{SLED}$ | LED Power Supply Voltage Input Terminal   |        |

| 4    | $V_{SLED}$ | LED Power Supply Voltage Input Terminal   |        |

| 5    | Ch3        | LED Current Feedback Terminal (Channel 3) |        |

| 6    | Ch4        | LED Current Feedback Terminal (Channel 4) |        |

#### **Electrical Characteristics**

#### **Absolute Maximum Rating**

Parameter damage may occur if exceeding the following maximum rating.

| ٠, |        | nago may occar ii oxococ |      |     |            |          | 9                                                       |           |

|----|--------|--------------------------|------|-----|------------|----------|---------------------------------------------------------|-----------|

|    | Symbol | Description              | Min. | Max | <b>(</b> . | Unit     | Rem                                                     | ark       |

|    | la     | LED Chrise Coursest      | 0    | 150 | ס          | [mA]     | 100% dı                                                 | uty ratio |

|    | ls     | LED String Current       | U    | 210 | )          | [mA]     | Remark  100% duty ratio  Duty ratio 10% Pulse time=10ms |           |

|    |        | B                        |      |     | ur         | chase    |                                                         | ):        |

|    |        | <u> </u>                 |      | 14: |            | <u> </u> | 11.7                                                    |           |

# Parameter guideline for LED driving is under stable conditions at 25°C (Room Temperature):

| Symbol            | Parameter                                      | Min.   | Тур. | Max. | Unit                           | Note                                 |

|-------------------|------------------------------------------------|--------|------|------|--------------------------------|--------------------------------------|

| IR <sub>LED</sub> | LED Operation Current                          | -      | 120  | 132  | [mA]                           |                                      |

| V <sub>LB</sub>   | Light Bar Operation Voltage<br>(for reference) | 53.1   | 56.7 | 64.8 | [Volt]<br>Note 7-1<br>Note 7-5 |                                      |

| ΔVs               | Maximum Vs Voltage<br>Deviation of light bar   | -      | -    | 3.6  | [Volt]<br>Note 7-2             | Operating with fixed driving current |

| P <sub>BLU</sub>  | BLU Power consumption (for reference)          |        | 27.2 | 31.1 | [Watt]<br>Note 7-3             |                                      |

| LT <sub>LED</sub> | LED life Time (Typical)                        | 30,000 |      | -    | [Hour]<br>Note 7-4             |                                      |

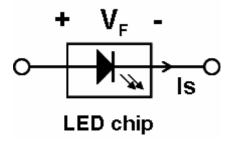

**Note 7-1:** Vs (Typ.) = VF (Typ.) X LED No. (one string);

a. V<sub>F</sub>: LED chip forward voltage, V<sub>F</sub> (Min.)=2.95V, V<sub>F</sub>(Typ.)=3.15V, V<sub>F</sub>(Max.)=3.6V

b. The same eugation to calculate Vs(Min.) & Vs (Max.) for respective V<sub>F</sub> (Min.) &  $V_F(Max.);$

- **Note 7-2:**  $\Delta Vs$  (Max.) =  $\Delta VF$  X LED No. (one string);

- a. ΔVF: LED chip forward voltage deviation; (0.2 V, each Bin of LED VF)

- Note 7-3: P<sub>BLU</sub> (Typ.) = Vs (Typ.) X Is (Typ.) X 4; (4 is total String No. of LED Light bar)

- Note 7-4: Definition of life time:

- Due to there are electrical proper *Note 7-5:* Recommendation for LED driver power design: component after long time operation. AUO strongly recommend the design value of LED driver board OVP (over voltage protection) should be 10% higher than max. value of LED string voltage (Vs) at least.

- Note 7-6: AUO strongly recommend "Analog Dimming" method for backlight brightness control for Wavy Noise Free. Otherwise, recommend that Dimming Control Signal (PWM Signal) should be synchronized with Frame Frequency.

## **Timing diagram**

### **Power ON/OFF Sequence**

VDD power, LVDS signal and backlight on/off sequence are as follows. LVDS signals from any system shall be Hi-Z state when VDD is off.

| _         | Val  | Value |      |  |

|-----------|------|-------|------|--|

| Parameter | Min. | Max.  | Unit |  |

| T1        | 0.5  | 10    | [ms] |  |

| T2        | 0    | 50    | [ms] |  |

| Т3        | 500  | -     | [ms] |  |

| T4        | 100  | -     | [ms] |  |

| T5        | 0    | 50    | [ms] |  |