# M29DW128G

## 128 Mbit (8 Mb x 16, multiple bank, page, dual boot) 3 V supply Flash memory

Data Brief

## Features

- Supply voltage

- www.DataSheet4U.com  $V_{CC} = 2.7$  to 3.6 V for Program, Erase and Read

- V<sub>PP</sub> =12 V for Fast Program (optional)

- Asynchronous Random/Page Read

- Page width: 8 words

- Page access: 25 ns

- Random access: 60 ns

- Programming time

- 15 µs per byte/word (typical)

- 32-word write buffer

- Erase verify

- Memory blocks

- Quadruple bank memory array:

- 16 Mbit+48 Mbit+48 Mbit+16 MbitParameter blocks (at top and bottom)

- Dual operation

- While Program or Erase in one bank, Read in any of the other banks

- Program/Erase Suspend and Resume modes

- Read from any block during Program Suspend

- Read and Program another block during Erase Suspend

- Unlock Bypass Program

- Faster production/batch programming

- Common Flash interface

- 64 bit security code

- 100,000 Program/Erase cycles per block

- Low power consumption

- Standby and automatic standby

- Hardware block protection

- V<sub>PP</sub>/WP pin for fast program and write protect of the four outermost parameter blocks

- Security features

- Standard protection

- Password protection

- Additional block protection

- Extended memory block

- Extra block used as security block or to store additional information

- Electronic signature

- Manufacturer code: 0020h

- Device code: 227Eh+2220h+2200h

- ECOPACK<sup>®</sup> packages available

For further information contact your local STMicroelectronics sales office.

www.numonyx.com

# Contents

| 1 | Description      |

|---|------------------|

| 2 | Part numbering   |

| 3 | Revision history |

ww.DataSheet4U.com

Numonyx

# List of tables

| Table 1. | Signal names                | 3 |

|----------|-----------------------------|---|

| Table 2. | Bank architecture           | 7 |

|          | Ordering information scheme |   |

| Table 4. | Document revision history   | ) |

ww.DataSheet4U.com

# List of figures

| Figure 1. | Logic diagram                               | 6 |

|-----------|---------------------------------------------|---|

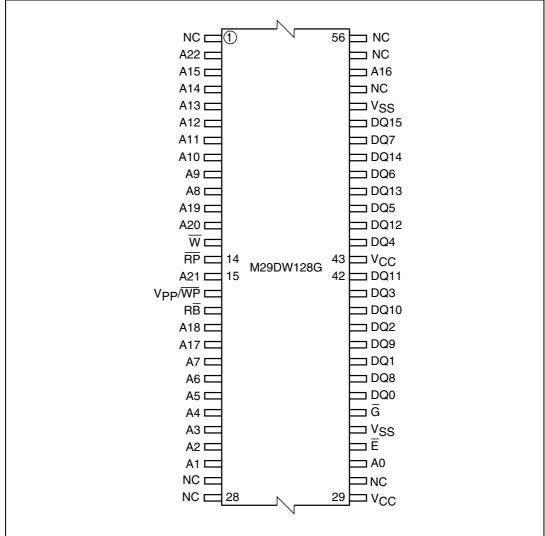

| Figure 2. | TSOP connections                            | 7 |

| Figure 3. | TBGA connections (top view through package) | 8 |

ww.DataSheet4U.com

## 1 Description

The M29DW128G is a 128 Mbit (8 Mb x 16) non-volatile memory that can be read, erased and reprogrammed. These operations can be performed using a single low voltage (2.7 to 3.6 V) supply. At Power-up the memory defaults to its Read mode.

The M29DW128G features an asymmetrical block architecture, with 8 parameter and 62 main blocks, divided into four banks, A, B, C and D, providing multiple bank operations. While programming or erasing in one bank, read operations are possible in any other bank. The bank architecture is summarized in *Table 2*. Four of the parameter blocks are at the top of the memory address space, and four are at the bottom.

Program and Erase commands are written to the command interface of the memory. An onchip Program/Erase controller simplifies the process of programming or erasing the memory by taking care of all of the special operations that are required to update the memory contents. The end of a program or erase operation can be detected and any error conditions identified. The command set required to control the memory is consistent with JEDEC standards.

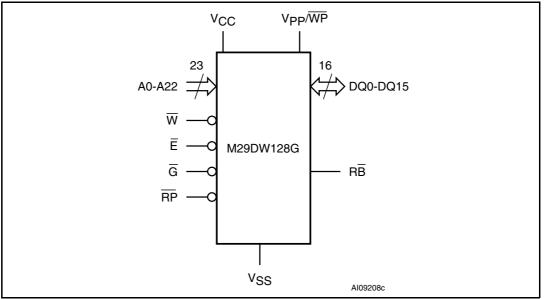

The Chip Enable, Output Enable and Write Enable signals control the bus operations of the memory. They allow simple connection to most microprocessors, often without additional logic.

The device supports Asynchronous Random Read and Page Read from all blocks of the memory array.

The M29DW128G has one extra 256 words block (extended block, 128 words factory locked and 128 words customer lockable) that can be accessed using a dedicated command. The extended block can be protected and so is useful for storing security information. However the protection is irreversible, once protected the protection cannot be undone.

Each block can be erased independently, so it is possible to preserve valid data while old data is erased.

The device features different levels of hardware and software block protection to avoid unwanted program or erase (modify):

- Hardware protection:

- The  $V_{PP}/\overline{WP}$  provides a hardware protection of the four outermost parameter blocks (two at the top and two at the bottom of the address space).

- Software protection

- Standard protection

- Password protection

- Additional protection features are available upon customer request.

The memory is offered in TSOP56 (14 x 20 mm) and TBGA64 (10 x 13 mm, 1 mm pitch) packages.

In order to meet environmental requirements, Numonyx offers the M29DW128G in ECOPACK<sup>®</sup> packages. ECOPACK packages are Lead-free. The category of second Level Interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label. The memory is supplied with all the bits erased (set to '1').

| Table 1. | Signal names   |

|----------|----------------|

|          | orginal manneo |

| Signal name         | Function                        | Direction |  |

|---------------------|---------------------------------|-----------|--|

| A0-A22              | Address inputs                  | Inputs    |  |

| DQ0-DQ15            | Data inputs/outputs             | I/O       |  |

| Ē                   | Chip Enable                     | Input     |  |

| G                   | Output Enable                   | Input     |  |

| W                   | Write Enable                    | Input     |  |

| RP                  | Reset/Block Temporary Unprotect | Input     |  |

| RB                  | Ready/Busy output               | Output    |  |

| V <sub>CC</sub>     | Supply voltage                  |           |  |

| V <sub>PP</sub> /WP | V <sub>PP</sub> /Write Protect  |           |  |

| V <sub>SS</sub>     | Ground                          |           |  |

| NC                  | Not connected internally        |           |  |

### Figure 1. Logic diagram

| Bank | Bank size | Parameter blocks |                         | Main blocks  |                           |  |

|------|-----------|------------------|-------------------------|--------------|---------------------------|--|

|      |           | N. of blocks     | Block size              | N. of blocks | Block size                |  |

| А    | 16 Mbit   | 4                | 64 Kbytes/<br>32 Kwords | 7            | 256 Kbytes/<br>128 Kwords |  |

| В    | 48 Mbit   | _                | _                       | 24           | 256 Kbytes/<br>128 Kwords |  |

| С    | 48 Mbit   | _                | _                       | 24           | 256 Kbytes/<br>128 Kwords |  |

| D    | 16 Mbit   | 4                | 64 Kbytes/<br>32 Kwords | 7            | 256 Kbytes/<br>128 Kwords |  |

#### Table 2. Bank architecture

ww.DataSheet4U.com

| 1 2 3 4 5 6 7 8                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $A \left( \begin{array}{c} NC \\ NC \end{array} \right) \left( \begin{array}{c} A3 \\ A3 \end{array} \right) \left( \begin{array}{c} A7 \\ A7 \end{array} \right) \left( \begin{array}{c} RB \\ BB \end{array} \right) \left( \begin{array}{c} \overline{W} \\ W \end{array} \right) \left( \begin{array}{c} A9 \\ A9 \end{array} \right) \left( \begin{array}{c} A13 \\ A13 \end{array} \right) \left( \begin{array}{c} NC \\ NC \end{array} \right)$ |

| $B \left( \begin{array}{c} NC \end{array} \right) \left( \begin{array}{c} A4 \end{array} \right) \left( \begin{array}{c} A17 \end{array} \right) \left( \begin{array}{c} V_{PP} / \overline{WP} \end{array} \right) \left( \begin{array}{c} \overline{RP} \end{array} \right) \left( \begin{array}{c} A8 \end{array} \right) \left( \begin{array}{c} A12 \end{array} \right) \left( \begin{array}{c} A22 \end{array} \right)$                          |

| C (NC) (A2) (A6) (A18) (A21) (A10) (A14) (NC)                                                                                                                                                                                                                                                                                                                                                                                                          |

| D (NC) (A1) (A5) (A20) (A19) (A11) (A15) (VCC)                                                                                                                                                                                                                                                                                                                                                                                                         |

| $E \left( \begin{array}{c} NC \end{array} \right) \left( \begin{array}{c} A0 \end{array} \right) \left( \begin{array}{c} DQ0 \end{array} \right) \left( \begin{array}{c} DQ2 \end{array} \right) \left( \begin{array}{c} DQ5 \end{array} \right) \left( \begin{array}{c} DQ7 \end{array} \right) \left( \begin{array}{c} A16 \end{array} \right) \left( \begin{array}{c} V_{SS} \end{array} \right)$                                                   |

| $F = \left( \begin{array}{c} V_{CC} \end{array} \right) \left( \begin{array}{c} E \end{array} \right) \left( \begin{array}{c} DQ8 \end{array} \right) \left( \begin{array}{c} DQ10 \end{array} \right) \left( \begin{array}{c} DQ12 \end{array} \right) \left( \begin{array}{c} DQ14 \end{array} \right) \left( \begin{array}{c} NC \end{array} \right) \left( \begin{array}{c} NC \end{array} \right)$                                                |

| $G \left( \begin{array}{c} NC \end{array} \right) \left( \begin{array}{c} \overline{G} \end{array} \right) \left( \begin{array}{c} DQ9 \end{array} \right) \left( \begin{array}{c} DQ11 \end{array} \right) \left( \begin{array}{c} V_{CC} \end{array} \right) \left( \begin{array}{c} DQ13 \end{array} \right) \left( \begin{array}{c} DQ15 \end{array} \right) \left( \begin{array}{c} NC \end{array} \right)$                                       |

| $H = \left( \begin{array}{c} NC \end{array} \right) \left( \begin{array}{c} V_{SS} \end{array} \right) \left( \begin{array}{c} DQ1 \end{array} \right) \left( \begin{array}{c} DQ3 \end{array} \right) \left( \begin{array}{c} DQ4 \end{array} \right) \left( \begin{array}{c} DQ6 \end{array} \right) \left( \begin{array}{c} V_{SS} \end{array} \right) \left( \begin{array}{c} NC \end{array} \right)$                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

Figure 3. TBGA connections (top view through package)

vw.DataSheet4U.com

Numonyx

## 2 Part numbering

#### Table 3. Ordering information scheme

|   |   | 1 | 1 |

|---|---|---|---|

|   | 1 |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   | ] |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   | - |

| - |   |   |   |

E = ECOPACK package, standard packing

F = ECOPACK package, tape & reel packing

Note: This product is also available with the extended block factory locked.

Devices are shipped from the factory with the memory content bits erased to '1'.

For a list of available options (speed, package, etc.) or for further information on any aspect of this device, please contact your nearest Numonyx Sales Office.

9/11

# 3 Revision history

#### Table 4.Document revision history

| Date        | Version | Revision details          |

|-------------|---------|---------------------------|

| 17-Sep-2007 | 1       | Initial release.          |

| 10-Dec-2007 | 2       | Applied Numonyx branding. |

/ww.DataSheet4U.com

ww.DataSheet4U.com

#### **Please Read Carefully:**

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH NUMONYX<sup>™</sup> PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN NUMONYX'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NUMONYX ASSUMES NO LIABILITY WHATSOEVER, AND NUMONYX DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF NUMONYX PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

Numonyx products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Numonyx may make changes to specifications and product descriptions at any time, without notice.

Numonyx, B.V. may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Numonyx reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Contact your local Numonyx sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Numonyx literature may be obtained by visiting Numonyx's website at http://www.numonyx.com.

Numonyx StrataFlash is a trademark or registered trademark of Numonyx or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 11/5/7, Numonyx, B.V., All Rights Reserved.

11/11