# MITSUBISHI MICROCOMPUTERS M37102M8-XXXSP/FP M37201M6-XXXSP SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER with ON-SCREEN DISPLAY CONTROLLER

## DESCRIPTION

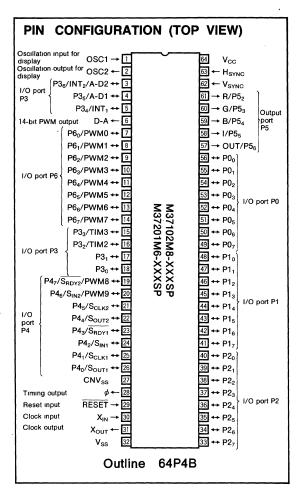

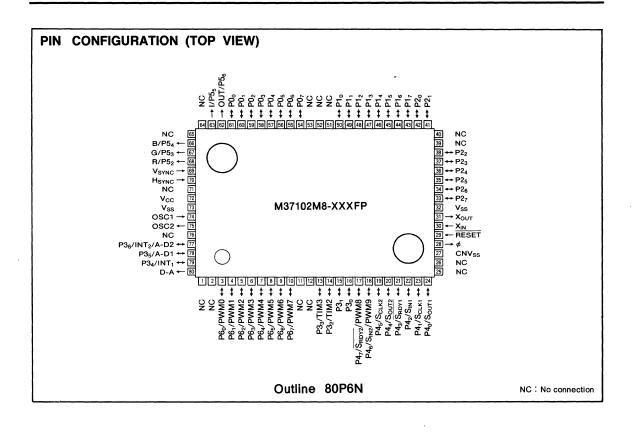

The M37102M8-XXXSP/FP is a single-chip microcomputer designed with CMOS silicon gate technology. It is housed in a 64-pin shrink plastic molded DIP or an 80-pin plastic molded QFP. This single-chip microcomputer is useful for the high-tech channel selection system for TVs.

In addition to their simple instruction sets, the ROM, RAM, and I/O addresses are placed on the same memory map to enable easy programming.

The differences between the M37102M8-XXXSP/FP and the M37201M6-XXXSP are noted below. The following explanations apply to the M37102M8-XXXSP. Specification variations for other chips are noted accordingly.

| Type name         | ROM size    | RAM size  |

|-------------------|-------------|-----------|

| M37102M8-XXXSP/FP | 16384 bytes | 320 bytes |

| M37201M6-XXXSP    | 24576 bytes | 384 bytes |

## **FEATURES**

- Number of basic instructions 69

- Memory size ROM ···· 16384 bytes (M37102M8-XXXSP/FP) 24576 bytes (M37201M6-XXXSP) RAM ·······320 bytes (M37102M8-XXXSP/FP)

384 bytes (M37201M6-XXXSP)

Kinds of character ......126

# APPLICATION

τv

## MITSUBISHI MICROCOMPUTERS M37102M8-XXXSP/FP M37201M6-XXXSP SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER with ON-SCREEN DISPLAY CONTROLLER

MITSUBISHI

MICROCOMPUTERS

D

2--52

# MITSUBISHI MICROCOMPUTERS M37102M8-XXXSP/FP M37201M6-XXXSP SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER with ON-SCREEN DISPLAY CONTROLLER

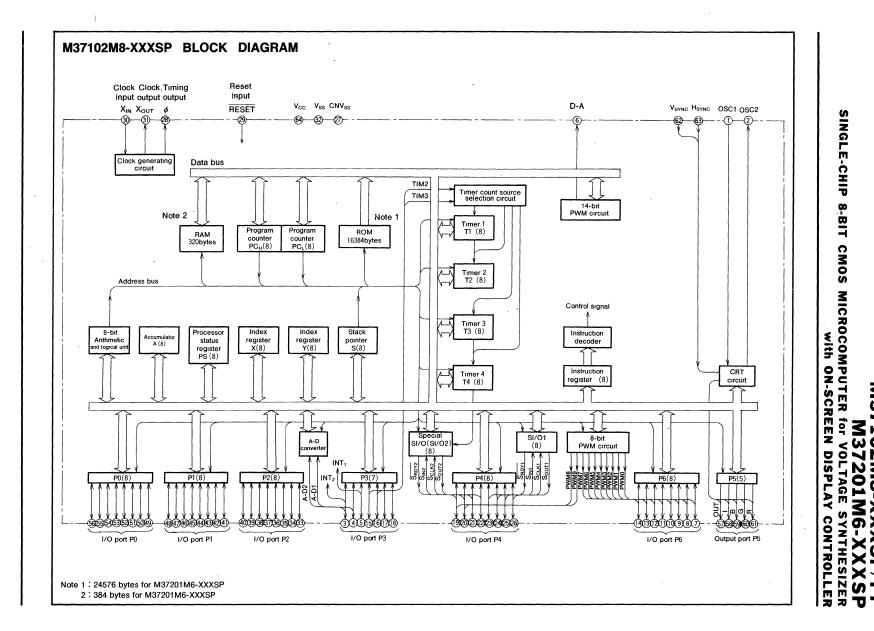

## FUNCTIONS OF M37102M8-XXXSP

| Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                   |           | Functions                                                                         |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------|-----------------------------------------------------------------------------------|--|--|

| Number of basic instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                   |           | 69                                                                                |  |  |

| Instruction execution time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                   |           | 1µs (minimum instructions, at 4MHz frequency)                                     |  |  |

| Clock frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                   |           | 4MHz                                                                              |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                   | ROM       | 16384bytes                                                                        |  |  |

| ••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | M37102M8-XXXSP/FP                 | RAM       | 320bytes                                                                          |  |  |

| Memory size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                   | ROM       | 24576bytes                                                                        |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | M37201M6-XXXSP                    | RAM       | 384bytes                                                                          |  |  |

| - Andrew Carrow Car | P0, P1, P2                        | 1/0       | 8-bit×3                                                                           |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | P3 <sub>0</sub> , P3 <sub>1</sub> | I/O       | 2-bit×1                                                                           |  |  |

| ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                   | 1/2       | 5-bit×1 (can be used as timer input pins, INT1, INT2 input pins and A-D           |  |  |

| Input/Output ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | P3 <sub>2</sub> -P3 <sub>6</sub>  | 1/0       | input pins)                                                                       |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | P4                                | I/O       | 8-bit×1 (can be used as serial I/O function pins and PWM output pins)             |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | P5                                | Output    | 5-bit×1 (can be used as R, G, B, I, OUT pins)                                     |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | P6                                | 1/0       | 8-bit×1 (can be used as PWM output pins)                                          |  |  |

| Serial I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                   |           | 8-bit×2 (Special serial I/O (8-bit)×1)                                            |  |  |

| Timers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                   |           | 8-bit timer×4                                                                     |  |  |

| Subroutine nesting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                   |           | 96levels (max )                                                                   |  |  |

| Lat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                   |           | Two external interrupts, nine internal interrupts,                                |  |  |

| Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                   |           | one software interrupt                                                            |  |  |

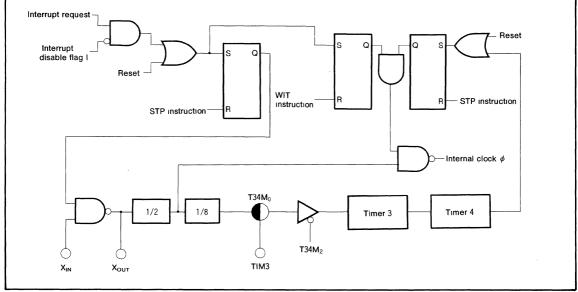

| Clock generating circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                   |           | Two built-in circuits (externally connected ceramic or quartz crystal oscillator) |  |  |

| Supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                   |           | 5V±10%                                                                            |  |  |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | at CRT display ON                 |           | 110mW (clock frequency X <sub>IN</sub> =4MHz, V <sub>CC</sub> =5.5V, Typ.)        |  |  |

| Power dissipation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | at CRT display OFF                |           | 55mW (clock frequency X <sub>IN</sub> =4MHz, V <sub>CC</sub> =5.5V, Typ )         |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | at stop mode                      |           | 1.65mW (Max )                                                                     |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Input/Output voltage              |           | 5V (Port P4 <sub>6</sub> , P4 <sub>7</sub> , P6 <sub>0</sub> -P6 <sub>7</sub> )   |  |  |

| Input/Output characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Output current                    |           | 10mA (Port P2 <sub>4</sub> -P2 <sub>7</sub> )                                     |  |  |

| Operating temperature range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                   |           | -10 to 70°C                                                                       |  |  |

| Device structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                   |           | CMOS silicon gate process                                                         |  |  |

| D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | M37102M8-XXXSP, M3720             | 1M6-XXXSP | 64-pin shrink plastic molded DIP                                                  |  |  |

| Package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | M37102M8-XXXFP                    |           | 80-pin plastic molded QFP                                                         |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Number of character               |           | 24 characters×3 lines                                                             |  |  |

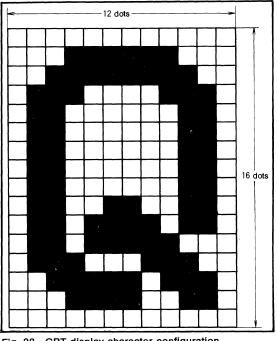

| CRT display function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Kinds of character                |           | 126 (12×16 dots)                                                                  |  |  |

# MITSUBISHI MICROCOMPUTERS M37102M8-XXXSP/FP M37201M6-XXXSP SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER with ON-SCREEN DISPLAY CONTROLLER

## **PIN DESCRIPTION**

| Pin                                  | Name                                                              | Input/<br>Output | Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------|-------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CC</sub> ,<br>V <sub>SS</sub> | Supply voltage                                                    |                  | Power supply inputs 5V $\pm$ 10% to V <sub>CC</sub> , and 0V to V <sub>SS</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| CNV <sub>ss</sub>                    | CNV <sub>SS</sub>                                                 |                  | This is connected to $V_{SS}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

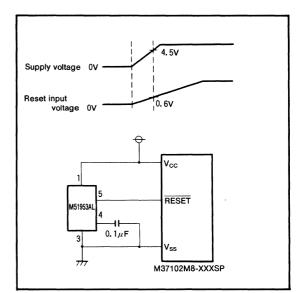

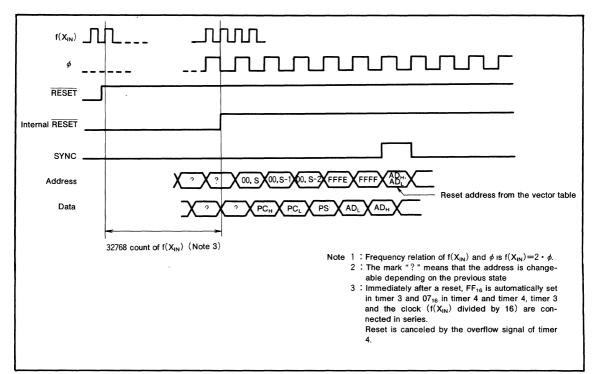

| RESET                                | Reset input                                                       | Input            | To enter the reset state, the reset input pin must be kept at a "L" for more than $2\mu$ s (under normal V <sub>CC</sub> conditions)<br>If more time is needed for the crystal oscillator to stabilize, this "L" condition should be maintained for the required time.                                                                                                                                                                                                                                                                                                                                                                                          |

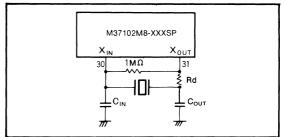

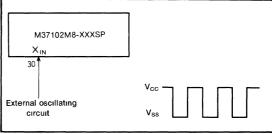

| X <sub>IN</sub>                      | Clock input                                                       | Input            | This chip has an internal clock generating circuit. To control generating frequency, an external ceramic or a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Х <sub>оит</sub>                     | Clock output                                                      | Output           | quartz crystal oscillator is connected between the $X_{IN}$ and $X_{OUT}$ pins. If an external clock is used, the clock source should be connected the $X_{IN}$ pin and the $X_{OUT}$ pin should be left open.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| φ                                    | Timing output                                                     | Output           | This is the timing output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

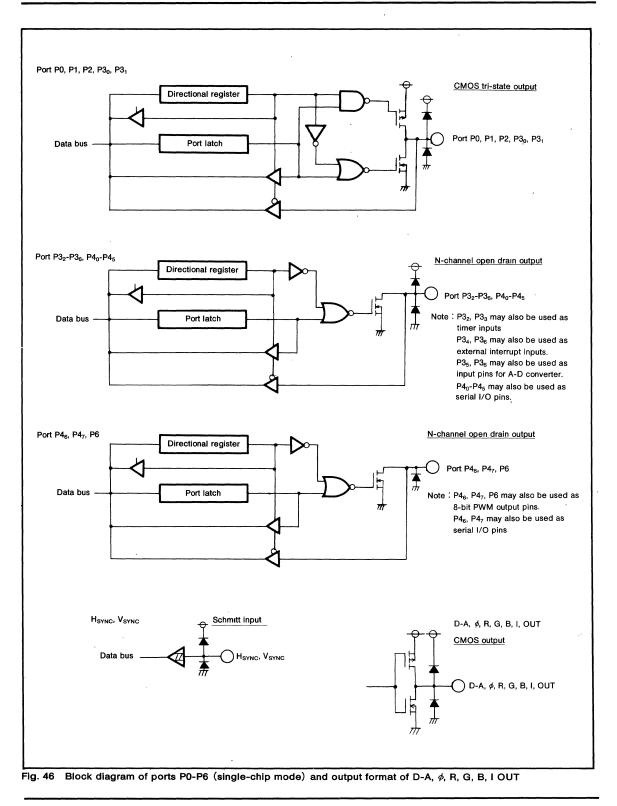

| P0 <sub>0</sub> -P0 <sub>7</sub>     | I/O port P0                                                       | 1/0              | Port P0 is an 8-bit I/O port with directional registers allowing each I/O bit to be individually programmed as<br>input or output At reset, this port is set to input mode. The output structure is CMOS output                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| P10-P17                              | I/O port P1                                                       | 1/0              | Port P1 is an 8-bit I/O port and has basically the same functions as port P0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| P20-P27                              | I/O port P2                                                       | 1/0              | Port P2 is an 8-bit I/O port and has basically the same functions as port P0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| P3 <sub>0</sub> -P3 <sub>6</sub>     | I/O port P3                                                       | I/O              | Port P3 is a 7-bit I/O port and has basically the same functions as port P0, but the output structure of $P3_0$ , $P3_1$ is CMOS output and the output structure of $P3_2$ -P3 <sub>6</sub> is N-channel open drain $P3_2$ , $P3_3$ are in common with external clock input pins of timer 2 and 3 $P3_4$ , $P3_6$ are in common with external interrupt input pins INT <sub>1</sub> and INT <sub>2</sub> $P3_5$ , $P3_6$ are in common with analog input pins of A-D converter (A-D1, A-D2)                                                                                                                                                                     |

| P4 <sub>0</sub> -P4 <sub>7</sub>     | I/O port P4                                                       | 1/0              | Port P4 is an 8-bit I/O port and has basically the same functions as port P0, but the output structure is N-channel open drain<br>When serial I/O1 is used,P4 <sub>0</sub> , P4 <sub>1</sub> , P4 <sub>2</sub> and P4 <sub>3</sub> work as S <sub>OUT1</sub> , S <sub>CLK1</sub> , S <sub>IN1</sub> and $\overline{S_{RDY1}}$ pins, respectively<br>When serial I/O2 is used, P4 <sub>4</sub> , P4 <sub>5</sub> , P4 <sub>6</sub> and P4 <sub>7</sub> work as S <sub>OUT2</sub> , S <sub>CLK2</sub> , S <sub>IN2</sub> and $\overline{S_{RDY2}}$ pins, respectively<br>Also P4 <sub>6</sub> , P4 <sub>7</sub> are in common with PWM output pins of PWM 8 and 9 |

| P60-P67                              | I/O port P6                                                       | 1/0              | Port P6 is an 8-bit I/O port and has basically the same functions as port P0, but the output structure is<br>N-channel open drain. This port is in common with PWM output pins PWM0-PWM7                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| OSC1,<br>OSC2                        | Clock input for CRT<br>display<br>Clock output for CRT<br>display | Input<br>Output  | This is the I/O pins of the clock generating circuit for the CRT display function.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| H <sub>SYNC</sub>                    | H <sub>SYNC</sub> input                                           | Input            | This is the horizontal synchronizing signal input for CRT display                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

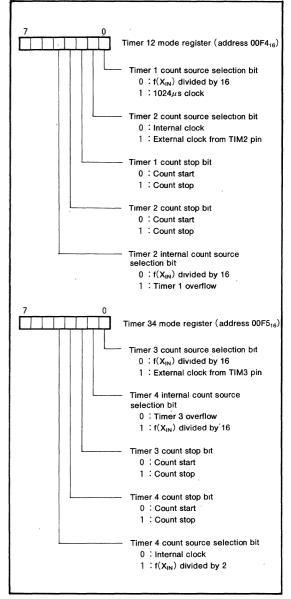

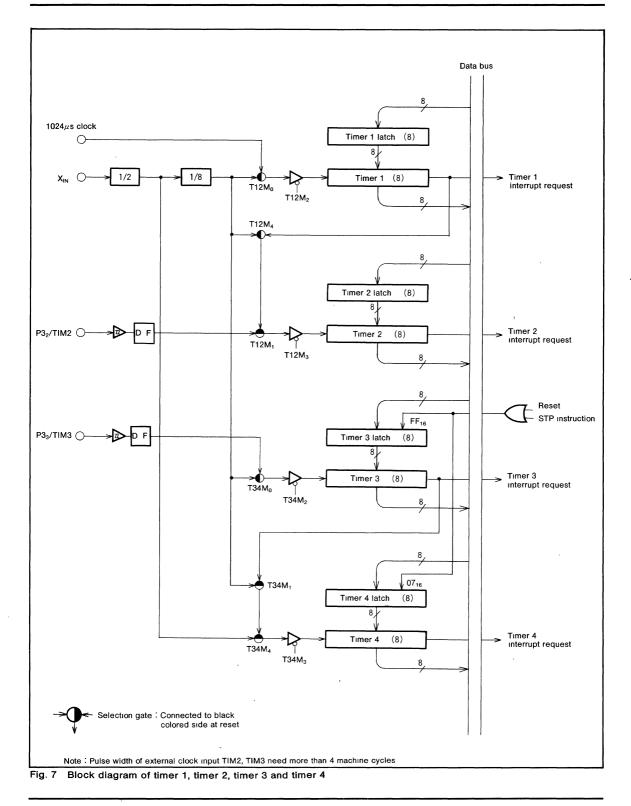

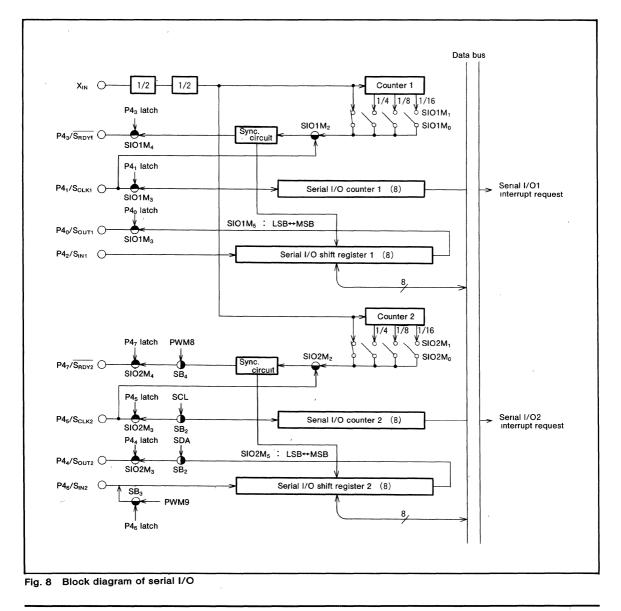

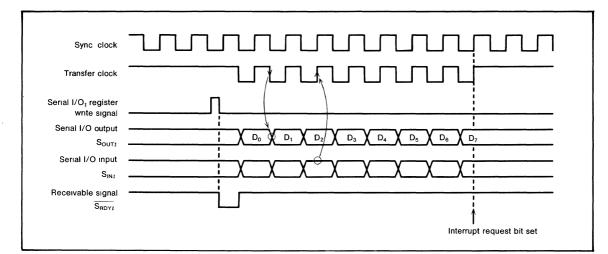

| V <sub>SYNC</sub>                    | V <sub>SYNC</sub> input                                           | Input            | This is the vertical synchronizing signal input for CRT display                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |