M37424M8-XXXSP M37524M4-XXXSP SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

## DESCRIPTION

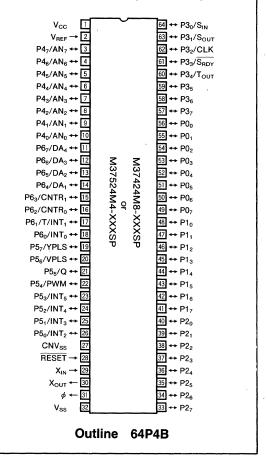

The M37424M8-XXXSP, M37524M4-XXXSP are single-chip microcomputers designed with CMOS silicon gate technology. They are housed in a 64-pin shrink plastic molded DIP.

This single-chip microcomputer is useful for business equipment and other consumer applications.

In addition to its simple instruction sets, the ROM, RAM, and I/O addresses are placed on the same memory map to enable easy programming.

The differences between the M37424M8-XXXSP and the M37524M4-XXXSP are noted below. The following explanations apply to the M37424M8-XXXSP.

Specification variations for other chips are noted accordingly.

| Type name      | Port P1 output structure |

|----------------|--------------------------|

| M37424M8-XXXSP | CMOS                     |

| M37524M4-XXXSP | N-channel open drain     |

### FEATURES

Number of basic instructions ......70 68 MELPS 740 basic instructions +2 multiply/divide instructions Memory size ROM ......16384 bytes RAM ...... 256 bytes Instruction execution time Power dissipation normal operation mode (at 4MHz frequency) ...... 30mW . 16-bit timer ······1 • Serial I/O (8-bit or 16-bit) .....1 PWM output (14-bit) ······ A-D converter (8-bit resolution) ......8-channel D-A converter (5-bit resolution) ······2 D-A converter (8-bit resolution) ------2 Watchdog timer External trigger output (1-bit) .....1 V pulse Y pulse generator Programmable I/O ports

## **APPLICATION**

Office automation equipment VCR equipment

## **PIN CONFIGURATION (TOP VIEW)**

≤

Ū

MITSUBISHI MICROCOMPUTERS  $\leq$  $\overline{\omega} \overline{\omega}$ 874 75 524 24 24M8-SS -0

μ 355

MITSUBISHI LELECTRIC

# M37424M8-XXXSP M37524M4-XXXSP

## SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

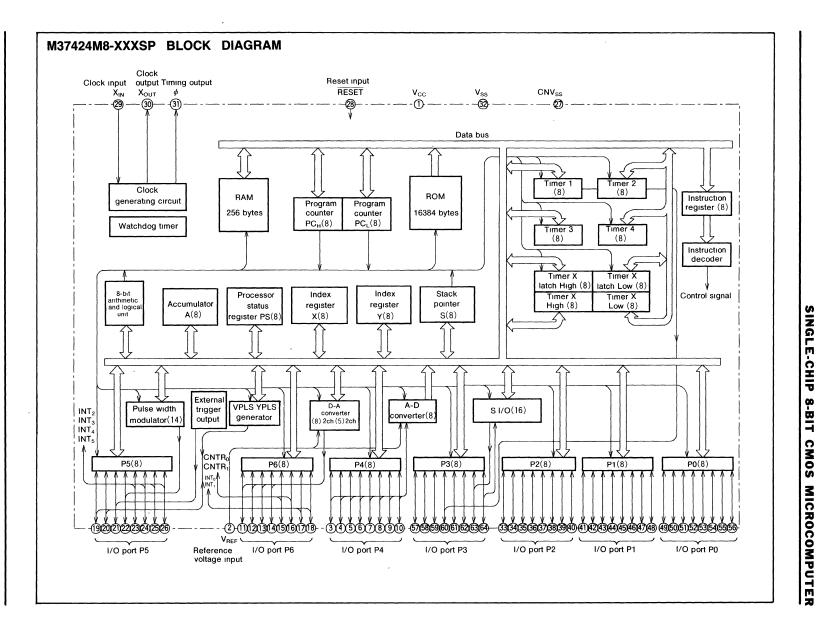

### FUNCTIONS OF M37424M8-XXXSP

|                              | Parameter                  |     | Functions                                       |  |

|------------------------------|----------------------------|-----|-------------------------------------------------|--|

| Number of basic instructions |                            |     | 70 (68 MELPS 740 basic instructions+2)          |  |

| Instruction execution time   |                            |     | 1µs (minimum instructions, at 4MHz frequency)   |  |

| Clock frequency              |                            |     | 4MHz                                            |  |

| Memory size                  | ROM                        |     | 16384 bytes                                     |  |

| Memory size                  | RAM                        |     | 256 bytes                                       |  |

| Input/Output ports           | P0, P1, P2, P3, P4, P5, P6 | 1/0 | 8-bit×7                                         |  |

| Serial I/O                   |                            |     | 8-bit or 16-bit×1                               |  |

| Timers                       |                            |     | 8-bit×4, 16-bit×1                               |  |

| A-D conversion               |                            |     | 8-bit×1 (8 channels)                            |  |

| D-A conversion               |                            |     | 5-bit×2, 8-bit×2                                |  |

| Pulse width modulator        |                            |     | 14-bit×1                                        |  |

| Watchdog timer               |                            |     | 15-bit×1                                        |  |

| Subroutine nesting           |                            |     | 96 levels (max )                                |  |

|                              |                            |     | 16 (external 8, Internal 8)                     |  |

| Clock generating circuit     | l.                         |     | Built-in (ceramic or quartz crystal oscillator) |  |

| Supply voltage               |                            |     | 5V±10%                                          |  |

| Power dissipation            |                            |     | 30mW (at 4MHz frequency)                        |  |

| Operating temperature ran    | ge                         |     | -10~70°C                                        |  |

| Device structure             |                            |     | CMOS silicon gate                               |  |

| Package                      |                            |     | 64-pin shrink plastic molded DIP                |  |

# M37424M8-XXXSP M37524M4-XXXSP

## SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

## **PIN DESCRIPTION**

| Pın                                  | Name                       | Input/<br>Output | Functions                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------|----------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CC</sub> ,<br>V <sub>SS</sub> | Supply voltage             |                  | Power supply inputs 5V $\pm10\%$ to $V_{cc},$ and 0V to $V_{ss}$ .                                                                                                                                                                                                                                                                                       |

| CNV <sub>ss</sub>                    | CNV <sub>SS</sub>          |                  | This is usually connected to $V_{\mbox{\scriptsize SS}}$                                                                                                                                                                                                                                                                                                 |

| V <sub>REF</sub>                     | Reference<br>voltage input | Input            | Reference voltage input pin for A-D and D-A converter                                                                                                                                                                                                                                                                                                    |

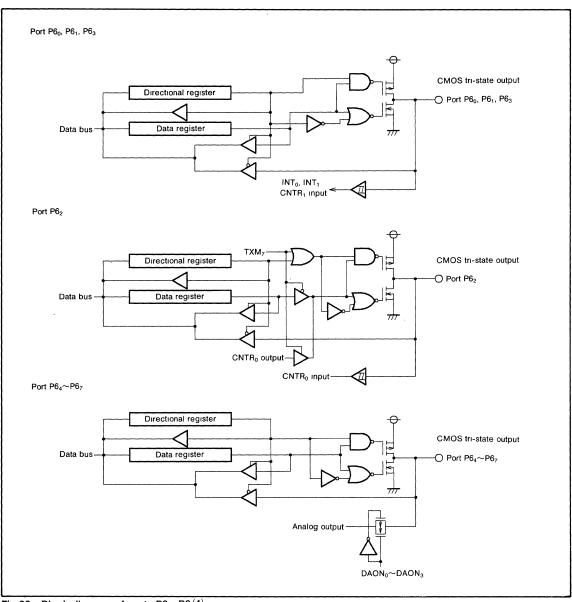

| RESET                                | Reset input                | Input            | To enter the reset state, the reset input pin must be kept at a "L" for more than $4\mu$ s (under normal V <sub>CC</sub> conditions) If more time is needed for the crystal oscillator to stabilize, this "L" condition should be maintained for the required time                                                                                       |

| X <sub>IN</sub>                      | Clock input                | Input            | This chip has an internal clock generating circuit To control generating frequency, an external ceramic or a grant point and the clock is used the clock                                                                                                                                                                                                 |

| Х <sub>оит</sub>                     | Clock output               | Output           | quartz crystal oscillator is connected between the $X_{IN}$ and $X_{OUT}$ pins if an external clock is used, the clock source should be connected the $X_{IN}$ pin and the $X_{OUT}$ pin should be left open                                                                                                                                             |

| φ                                    | Timing output              | Output           | This is the timing output pin                                                                                                                                                                                                                                                                                                                            |

| P0 <sub>0</sub> ~P0 <sub>7</sub>     | I/O port P0                | 1/0              | Port P0 is an 8-bit I/O port with directional register allowing each I/O bit to be individually programmed as input or output At reset, this port is set to input mode. The output structure is CMOS output                                                                                                                                              |

| P1 <sub>0</sub> ~P1 <sub>7</sub>     | I/O port P1                | 1/0              | Port P1 is an 8-bit I/O port and has basically the same functions as port P0. The output structure of M37424M8-XXXSP is CMOS output and that of M37524M4-XXXSP is N-channel open drain output                                                                                                                                                            |

| P2 <sub>0</sub> ~P2 <sub>7</sub>     | I/O port P2                | 1/0              | Port P2 is an 8-bit I/O port and has basically the same functions as port P0 The output structure is CMOS output                                                                                                                                                                                                                                         |

| P3₀~P3 <sub>7</sub>                  | I/O port P3                | 1/0              | Port P3 is an 8-bit I/O port and has basically the same functions as port P0 When serial I/O is used, P3 <sub>3</sub> , P3 <sub>2</sub> , P3 <sub>1</sub> , and P3 <sub>0</sub> work as $\overline{S_{RDY}}$ , CLK, $S_{OUT}$ , and $S_{IN}$ pins, respectively Also P3 <sub>4</sub> works as $T_{OUT}$ pin The output structure is N-channel open drain |

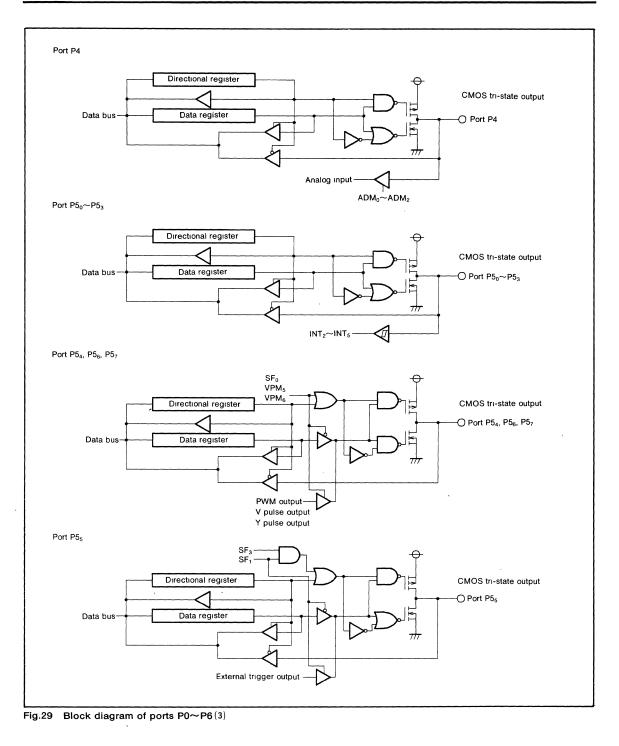

| P4 <sub>0</sub> ~P4 <sub>7</sub>     | I/O port P4                | 1/0              | Port P4 is an 8-bit I/O port and has basically the same functions as port P0 $P4_0 \sim P4_7$ work as analog input port $AN_0 \sim AN_7$                                                                                                                                                                                                                 |

| P5₀~P5 <sub>7</sub>                  | I/O port P5                | 1/0              | Port P5 is an 8-bit I/O port and has basically the same functions as port P0 P5 <sub>7</sub> , P5 <sub>6</sub> , P5 <sub>5</sub> , P5 <sub>4</sub> and P5 <sub>3</sub> ~P5 <sub>0</sub> are in common with the YPLS output, VPLS output, Q output, PWM output and interrupt input respectively                                                           |

| P6 <sub>0</sub> ~P6 <sub>7</sub>     | I/O port P6                | 1/0              | Port P6 is an 8-bit I/O port and has basically the same functions as port P0 $P6_7 \sim P6_4$ , $P6_3$ , $P6_2$ , and $P6_1$ , $P6_0$ are in common with the D-A output, CNTR output and interrupt input respectively                                                                                                                                    |

# M37424M8-XXXSP M37524M4-XXXSP

### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

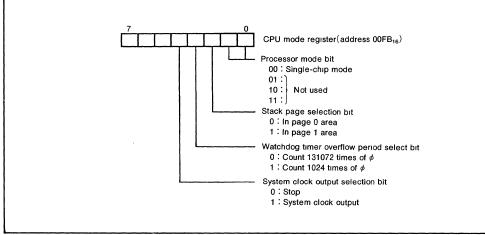

The CPU mode register is allocated to address 00FB<sub>16</sub>.

CPU MODE REGISTER

This register has a stack page selection bit.

### FUNCTIONAL DESCRIPTION CENTRAL PROCESSING UNIT (CPU)

The M37424, M37524 microcomputers use the standard MELPS 740 instruction set. For details of instructions, refer to the MELPS 740 CPU core basic functions, or the MELPS 740 Software Manual.

Machine-resident instructions are as follows:

The FST and SLW instructions are not provided.

The MUL and DIV instructions can be used.

The WIT instruction can be used.

The STP instruction are not provided.

#### Fig.1 Structure of CPU mode register

# M37424M8-XXXSP M37524M4-XXXSP

## SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

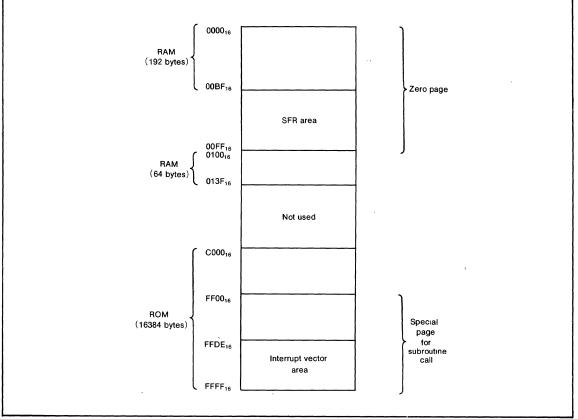

### MEMORY

- Special Function Register (SFR) Area The special function register (SFR) area contains the registers relating to functions such as I/O ports and timers.

- RAM

- RAM is used for data storage as well as a stack area.

- ROM

ROM is used for storing user programs as well as the interrupt vector area. Interrupt Vector Area

The interrupt vector area is for storing jump destination addresses used at reset or when an interrupt is generated.

• Zero Page

Zero page addressing mode is useful because it enables access to this area with fewer instruction cycles.

Special Page

Special page addressing mode is useful because it enables access to this area with fewer instruction cycles.

Fig.2 Memory map

## M37424M8-XXXSP M37524M4-XXXSP

## SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

| 00C0 <sub>16</sub> | Port P0                               |

|--------------------|---------------------------------------|

| 00C1 <sub>16</sub> | Port P0 directional register          |

| 00C2 <sub>16</sub> | Port P1                               |

| 00C3 <sub>16</sub> | Port P1 directional register          |

| 00C4 <sub>16</sub> | Port P2                               |

| 00C5 <sub>16</sub> | Port P2 directional register          |

| 00C6 <sub>16</sub> | Port P3                               |

| 00C7 <sub>16</sub> | Port P3 directional register          |

| 00C8 <sub>16</sub> | Port P4                               |

| 00C9 <sub>16</sub> | Port P4 directional register          |

| 00CA16             | Port P5                               |

| 00CB16             | Port P5 directional register          |

| 00CC16             | Port P6                               |

| 00CD16             | Port P6 directional register          |

| 00CE16             |                                       |

|                    | Reserved area                         |

| 00D0 <sub>16</sub> | ·                                     |

| 00D1 <sub>16</sub> | D-A output enable register            |

| 00D2 <sub>16</sub> | D-A3 conversion register              |

| 00D3 <sub>16</sub> | D-A4 conversion register              |

| 00D4 <sub>16</sub> | Pulse width modulation register H     |

| 00D5 <sub>16</sub> | Pulse width modulation register L     |

| 00D6 <sub>16</sub> | V pulse preset value P                |

| 00D7 <sub>16</sub> | V pulse preset value N                |

| 00D8 <sub>16</sub> | V pulse control register              |

| 00D916             | A-D successive approximation register |

| 00DA16             | A-D control register                  |

| 00DB16             | D-A1 conversion register              |

| 00DC16             | D-A2 conversion register              |

| 00DD <sub>16</sub> | Serial I/O mode register              |

| 00DE16             | Serial I/O register L                 |

| 00DF16             | Serial I/O register H                 |

| 00E0 <sub>16</sub>                       |                                           |  |

|------------------------------------------|-------------------------------------------|--|

|                                          | Reserved area                             |  |

| 00EC <sub>16</sub>                       |                                           |  |

| 00ED <sub>16</sub>                       | Interrupt polarity specification register |  |

| 00EE <sub>16</sub>                       | Special function selection register       |  |

| 00EF <sub>16</sub>                       | Watchdog timer                            |  |

| 00F0 <sub>16</sub>                       | Timer 1                                   |  |

| 00F1 <sub>16</sub>                       | Timer 2                                   |  |

| 00F2 <sub>16</sub><br>00F3 <sub>16</sub> | Timer 3                                   |  |

| 00F3 <sub>16</sub>                       | Timer 4<br>Timer X (low-order)            |  |

| 00F416                                   | Timer X (high-order)                      |  |

| 00F5 <sub>16</sub>                       | Timer X (high-order)                      |  |

| 00F0 <sub>16</sub>                       | Timer X latch (high-order)                |  |

| 00F8 <sub>16</sub>                       | Timer 1, 2 mode register                  |  |

| 00F9 <sub>16</sub>                       | Timer 3, 4 mode register                  |  |

| 00FA <sub>16</sub>                       | Timer X mode register                     |  |

| 00FB16                                   | CPU mode register                         |  |

| 00FC <sub>16</sub>                       |                                           |  |

| 00FD16                                   |                                           |  |

| 00FE16                                   | Interrupt control register 1              |  |

| 00FF <sub>16</sub>                       | Interrupt control register 2              |  |

|                                          | h                                         |  |

Fig. 3 SFR (Special Function Register) memory map

# M37424M8-XXXSP M37524M4-XXXSP

### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

#### INTERRUPTS

Interrupts can be caused by 16 different events. Interrupts are vectored interrupts with prioities shown in Table 1. Reset is also included in the table because its operation is similar to an interrupt.

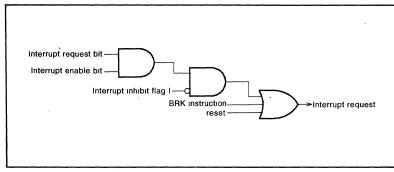

When an interrupt is accepted, the registers are pushed, interrupt inhibit flag I is set, and the program jumps to the address specified in the vector table. The interrupt request flag is cleared automatically. The reset and BRK instruction interrupt can never be inhibited. Other interrupt are disabled when the interrupt inhibit flag is set.

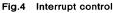

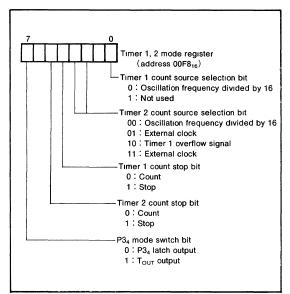

All interrupts except the BRK instruction interrupt have an interrupt request bit and an interrupt enable bit. The interrupt request bits are in interrupt request registers 1 and 2 and the interrupt enable bits are in interrupt control registers 1 and 2. Figure 5 shows the structure of the interrupt request registers 1 and 2, interrupt control registers 1 and 2 and interrupt polarity specification register.

For external interrupts ( $INT_0$  to  $INT_5$ ,  $CNTR_0$ , and  $CNTR_1$ ), the polarity of each pin's interrupt input can be set. Polarity for  $INT_0$  to  $INT_5$  and  $CNTR_1$  is set by bits 0 to 6 of the interrupt polarity specification register (address  $00ED_{16}$ ); polarity for  $CNTR_0$  is set by bit 6 of the timer X mode register (address  $00FA_{16}$ ). If "0" is written to one of these bits, the corresponding interrupt request is falling-edge active; if "1" is written, the corresponding interrupt request is risingedge active.  $INT_1$  can also be set to be both rising-edge and falling-edge active by setting bit 7 of the interrupt polarity specification register to "1". The meaning of the  $CNTR_0$  interrupt is different if it is used with timer X in pulse width measurement mode 1, pulse width measurement mode 2, or pulse period measurement mode. For details, see the section on timer X

Interrupts other than the BRK instruction interrupt and reset are accepted when the interrupt enable bit is "1", interrupt request bit is "1", and the interrupt inhibit flag is "0". The interrupt request bit can be reset with a program, but not set. The interrupt enable bit can be set and reset with a program.

Reset is treated as a non-maskable interrupt with the highest priority. Figure 4 shows interrupts control.

| Event                               | Priority | Vector addresses                        | Remarks                                 |

|-------------------------------------|----------|-----------------------------------------|-----------------------------------------|

| RESET                               | 1        | FFFF <sub>16</sub> , FFFE <sub>16</sub> | Non-maskable                            |

| INT <sub>0</sub> interrupt          | 2        | FFFD <sub>16</sub> , FFFC <sub>16</sub> | External interrupt (phase programmable) |

| INT <sub>1</sub> Interrupt          | 3        | FFFB <sub>16</sub> , FFFA <sub>16</sub> | External interrupt (phase programmable) |

| INT <sub>2</sub> interrupt          | 4        | FFF9 <sub>16</sub> , FFF8 <sub>16</sub> | External interrupt (phase programmable) |

| Timer 4 interrupt                   | 5        | FFF7 <sub>16</sub> , FFF6 <sub>16</sub> |                                         |

| Timer 1 interrupt                   | 6        | FFF5 <sub>16</sub> , FFF4 <sub>16</sub> |                                         |

| INT <sub>3</sub> interrupt          | 7        | FFF3 <sub>16</sub> , FFF2 <sub>16</sub> | External interrupt (phase programmable) |

| CNTR <sub>1</sub> interrupt         | 8        | FFF1 <sub>16</sub> , FFF0 <sub>16</sub> | External interrupt (phase programmable) |

| INT <sub>4</sub> interrupt          | 9        | FFEF <sub>16</sub> , FFEE <sub>16</sub> | External interrupt (phase programmable) |

| Timer X interrupt                   | 10       | FFED <sub>16</sub> , FFEC <sub>16</sub> |                                         |

| CNTR <sub>0</sub> interrupt         | 11       | FFEB <sub>16</sub> , FFEA <sub>16</sub> | External interrupt (phase programmable) |

| Timer 2 interrupt                   | 12       | FFE9 <sub>16</sub> , FFE8 <sub>16</sub> |                                         |

| Timer 3 interrupt                   | 13       | FFE7 <sub>16</sub> , FFE6 <sub>16</sub> |                                         |

| Serial I/O interrupt                | 14       | FFE5 <sub>16</sub> , FFE4 <sub>16</sub> |                                         |

| INT <sub>5</sub> interrupt          | 15       | FFE3 <sub>16</sub> , FFE2 <sub>16</sub> | External interrupt (phase programmable) |

| A-D conversion completion interrupt | 16       | FFE116, FFE016                          |                                         |

| BRK instruction interrupt           | 17       | FFDF <sub>16</sub> , FFDE <sub>16</sub> | Non-maskable software interrupt         |

#### Table 1. Interrupt vector address and priority

## M37424M8-XXXSP M37524M4-XXXSP

Fig.5 Structure of registers related to interrupt

# M37424M8-XXXSP M37524M4-XXXSP

#### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

#### TIMERS

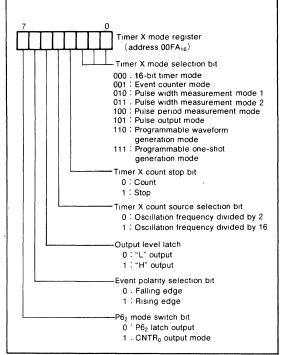

The M37424M8-XXXSP has five timers : timer X, timer 1, timer 2, timer 3, and timer 4. A block diagram of these timers is shown in Figure 9.

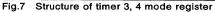

Timer X is a 16-bit timer. It has an independent 16-bit timer latch and can be used in eight modes. The structure of the timer X mode register is shown in Figure 8, and the eight timer X modes are described below.

#### (1) 16-bit timer mode [000]

Basic mode in which timer X functions as a 16-bit reload timer and timer X generates an interrupt request when it overflows.

The count source is selected by bit 4 of the timer X mode register : if this bit is "0", the count source is the oscillation frequency divided by 2; if it is "1", the count source is the oscillation frequency divided by 16. This bit is "0" immediately after a reset.

The timer counts down the value which decrements by one from the value set in the latch. At the next count pulse after it reaches  $FFF_{16}$  from  $0000_{16}$ , an timer X interrupt is generated, and at the same time the value in the timer latch is reloaded into the timer. The value is not reloaded into the timer until it overflows, even if the contents of the timer latch are overwritten.

When writing to the timer directly, write the upper value first, then the lower value. The upper value is overwritten at the same time that the lower value is written. When reading the timer, read the lower value first, then the upper value. At the point at which the lower value is read, the upper value is latched. If reading the lower value always read the upper value as well. There are no restrictions on which part of the timer latch should be written to or read first.

#### (2) Event counter mode [001]

Mode in which timer X operates in exactly the same way as in timer mode, except that the count source is the external pulse input from the  $CNTR_0$  pin The input polarity of the  $CNTR_0$  pin can be selected by bit 6 of the timer X mode register : if this bit is "0", falling edges are counted ; if it is "1", rising edges are counted.

#### (3) Pulse width measurement mode 1 [010]

Mode in which timer X measures the width of "H" or "L" period of the external pulse input from the  $CNTR_0$  pin.

The count source is selected by bit 4 of the timer X mode register : if this bit is "0", the count source is the oscillation frequency divided by 2; if it is "1", the count source is the oscillation frequency divided by 16. In this mode the timer counts up at the same time that the measurement ends, the value in the timer is latched into the timer latch and a  $CNTR_0$  interrupt request is generated.

Bit 6 of the timer X mode register selects whether the "H" period is measured or the "L" period. If this bit is "0", the

"L" period is measured ; if it is "1", the "H" period is measured.

#### (4) Pulse width measurement mode 2 [011]

Mode in which timer X continuously measures the width of both "H" and "L" periods of the external pulse input from the  ${\sf CNTR}_0$  pin.

The count source is selected by bit 4 of the timer X mode register : if this bit is "0", the count source is the oscillation frequency divided by 2; if it is "1", the count source is the oscillation frequency divided by 16. The value in the timer is latched at both the rising edges and falling edges of the external pulse, and a CNTR<sub>0</sub> interrupt request is generated. Whether the measured value is the "H" period or the "L" period can be determined by checking the level of the P6<sub>2</sub>/CNTR<sub>0</sub> pin. This mode can be used to measure the duty cycle of external pulses.

#### (5) Pulse period measurement mode [100]

Mode in which timer X measures the period of the external pulse input from the  $CNTR_0$  pin.

The count source is selected by bit 4 of the timer X mode register : if this bit is "0", the count source is the oscillation frequency divided by 2; if it is "1", the count source is the oscillation frequency divided by 16. If bit 6 of the timer X mode register is "0", the period from one falling edge to the next falling edge is measured; if it is "1", the period from one rising edge to the next rising edge is measured. The measured value is latched in the timer latch, and a CNTR<sub>0</sub> interrupt request is generated.

#### (6) Pulse output mode [101]

Mode in which an waveform of duty cycle 50% which is inverted every time timer X overflows is output to the  $\text{CNTR}_0$  pin.

The count source is selected by bit 4 of the timer X mode register : if this bit is "0", the count source is the oscillation frequency divided by 2; if it is "1", the count source is the oscillation frequency divided by 16.

#### (7) Programmable waveform generation mode [110]

Mode in which the contents of the output level latch allocated to bit 5 of the timer X mode register are output to the  $CNTR_0$  pin every time timer X overflows.

The count source is selected by bit 4 of the timer X mode register : if this bit is "0", the count source is the oscillation frequency divided by 2; if it is "1", the count source is the oscillation frequency divided by 16. Various different waveforms can be generated by updating the values in the output level latch, the timer and the timer latch, each time timer X overflows.

# M37424M8-XXXSP M37524M4-XXXSP

#### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

#### (8) Programmable one-shot generation mode [111]

Mode in which the active edge of an external pulse input from the  $P6_0/INT_0$  pin sets the value of the timer latch into timer X, and timer X starts to count. The  $CNTR_0$  pin goes "H" at the same time of the active edge of the  $INT_0$  pin input, and goes "L" when timer X overflows.

The count source is selected by bit 4 of the timer X mode register : if this bit is "0", the count source is the oscillation frequency divided by 2; if it is "1", the count source is the oscillation frequency divided by 16. The active edge of the  $INT_0$  pin is set by bit 0 of the interrupt polarity specification register, and is the same as the polarity of the  $INT_0$  interrupt.

Note that if the CNTR<sub>0</sub> pin is used as a pulse output pin (in pulse output mode, programmable waveform generation mode), bit 7 of the timer X mode register must be "1". If this bit switches from "0" to "1", an "L"-level signal will be output to the CNTR<sub>0</sub> pin. However, be aware that if timer X is switched to another pulse output mode while this bit is "1", the level output in the previous mode will still be held by the CNTR<sub>0</sub> pin.

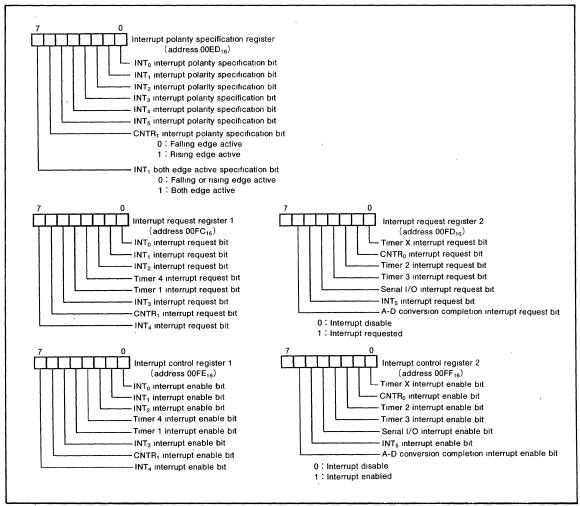

Timer 1, timer 2, timer 3, and timer 4 are all 8-bit timers with 8-bit timer latches. Writing to a timer latch sets the corresponding timer at the same time, except that, if the value written to the latch is n, the value actually set in the timer is (n-1). The timer has a count-down operation : at the next count pulse after it reaches FF<sub>16</sub> from  $00_{16}$ , the value in the timer latch is reloaded into the timer. If the value in the timer latch is n, the divide ratio is 1/(n+1). At the same time, the interrupt request bit corresponding to that timer is set to "1". Set the count source for each timer by the timer 1, 2 mode register (address  $00F8_{16}$ ).

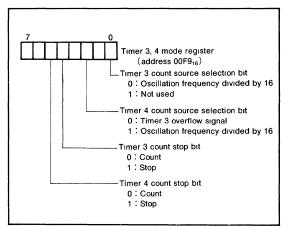

If an external clock is selected as the count source for timer 2, timer counts the P6<sub>3</sub>/CNTR<sub>1</sub> pin input. An inverting waveform every time timer 2 overflows can be output to the P3<sub>4</sub>/T<sub>OUT</sub> pin, by setting bit 7 of the timer 1, 2 mode register to "1". The structure of the timer 1, 2 mode register is shown in Figure 6 and the structure of the timer 3, 4 mode register is shown in Figure 7

At reset, timer 3 is set to  $FF_{16}$  and timer 4 is set to  $07_{16}$ .

# M37424M8-XXXSP M37524M4-XXXSP

Fig.6 Structure of timer 1, 2 mode register

Fig.8 Structure of timer X mode register

# M37424M8-XXXSP M37524M4-XXXSP

Fig.9 Block diagram of timer

# M37424M8-XXXSP M37524M4-XXXSP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

#### SERIAL I/O

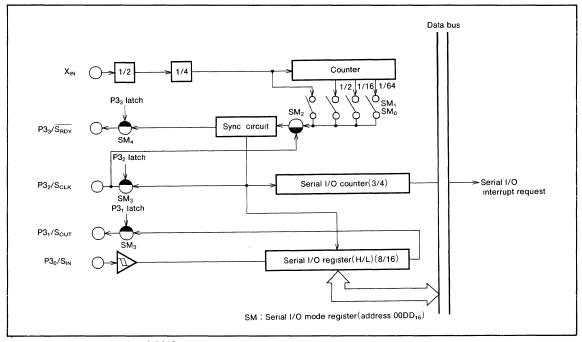

A block diagram of the serial I/O function is shown in Figure 11. The serial I/O receive enabled signal pin  $(\overline{S_{\text{RDY}}})$ , synchronous clock I/O pin (CLK), and data I/O pins  $(S_{\text{OUT}}, S_{\text{IN}})$  also function as the P3<sub>3</sub>, P3<sub>2</sub>, P3<sub>1</sub>, and P3<sub>0</sub> of the port P3.

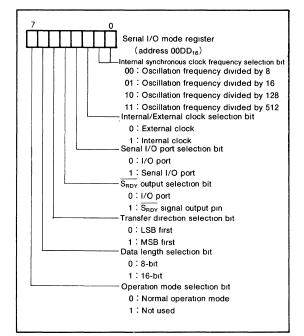

The serial I/O mode register has an 8-bit structure. Bits 1 and 0 select the synchronous clock : the oscillation frequency is divided by 8 if they are [00], by 16 if they are [01], by 128 if they are [10], or by 512 if they are [11]. Bit 2 selects an external clock.

Bits 3 and 4 are used to select whether part of port P3 is used for serial I/O. If bit 3 is "1", the  $P3_2$  is the I/O pin for the synchronous clock .

The P3<sub>1</sub> is the serial data output pin and the P3<sub>0</sub> is the serial data input pin. If using the P3<sub>0</sub> as the serial data input pin, set the bit in the directional register corresponding to P3<sub>0</sub> to "0" to set input mode. If serial I/O is being used, bit 3 must be set to "1". When bit 3 is "0", the P3<sub>2</sub> functions as an ordinary I/O pin.

Bit 4 selects whether the P3<sub>3</sub> is used as the output pin for the receive enabled signal  $\overline{S_{RDY}}$ . If this bit is "1", the  $\overline{S_{RDY}}$ signal is output; if it is "0", the P3<sub>3</sub> is an ordinary I/O pin.

Serial I/O register H and serial I/O register L are 8-bit registers for data transfer that can be used in both transmission and reception. For 8-bit transfer, serial I/O register L

Fig.10 Structure of serial I/O mode register

Fig.11 Block diagram of serial I/O

# M37424M8-XXXSP M37524M4-XXXSP

#### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

(address  $00DE_{16}$ ) is used ; for 16-bit transfer, serial I/O register H (address  $00DF_{16}$ ) is used for the upper byte and serial I/O register L for the lower byte. The data length to be transferred can be selected either 8 bits or 16 bits by setting bit 6 of the serial I/O mode register. Whether data transfer is MSB first or LSB first can be selected by setting bit 5 of the serial I/O mode register.

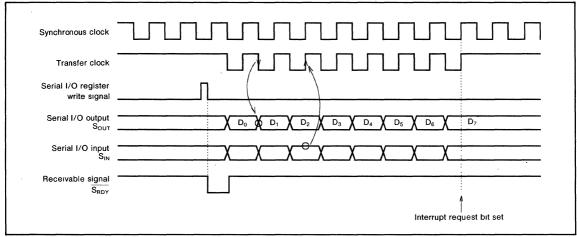

The operation of the serial I/O function will now be described. The operation differs depending on whether the internal clock or an external clock is selected as the synchronous clock. Use with the internal clock will be described first.

If the serial I/O register L is written to, the  $S_{RDY}$  signal is at "H" during the write cycle ; it then goes "L" when the write cycle ends to indicate reception enabled status. If the serial I/O register's transfer clock goes "L" even once, the  $\overline{S_{RDY}}$  signal goes "H". During the write cycle to the serial I/O register, "7" is set in the serial I/O counter for 8-bit transfer or "15" for 16-bit transfer, and the serial I/O register's transfer clock is forced to "H". After the write cycle ends, data is output to the P3<sub>1</sub> pin each time the transfer clock goes from "H" to "L". Data is input from the P3<sub>0</sub> pin

each time the transfer clock goes from "L" to "H" and, at the same time, the contents of the serial I/O register are shifted one bit. If bit 5 of the serial I/O mode register is "0", the data enters from the MSB and shifts to the right, if it is "1", the data enters from the LSB and shifts to the left.

When the serial I/O counter reaches "0" after counting either 8 or 16 transfer clocks, the transfer clock stops at "H" and the corresponding interrupt request bit is set.

If an external clock is selected as the synchronous clock, it must be controlled externally because, although the interrupt request bit is set, the transfer clock does not stop. Use a clock of no more that 500kHz with a duty cycle of 50% as the external clock.

The timing at which 8-bit data is transferred LSB-first is shown in Figure 12. If an external clock is used for the transfer, the external clock must be "H" when the serial I/O counter is initialized. Make sure that the serial I/O counter is initialized after the transfer clock switches. Initialize by writing to the serial I/O register H.

A connection example for transferring data from one M37424M8-XXXSP to another is shown in Figure 13.

Fig.12 Serial I/O timing

## M37424M8-XXXSP M37524M4-XXXSP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

Fig.13 Example of serial I/O connection

### **PWM OUTPUT CIRCUIT**

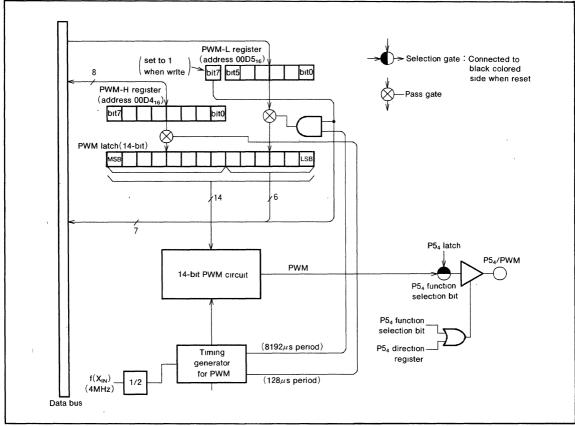

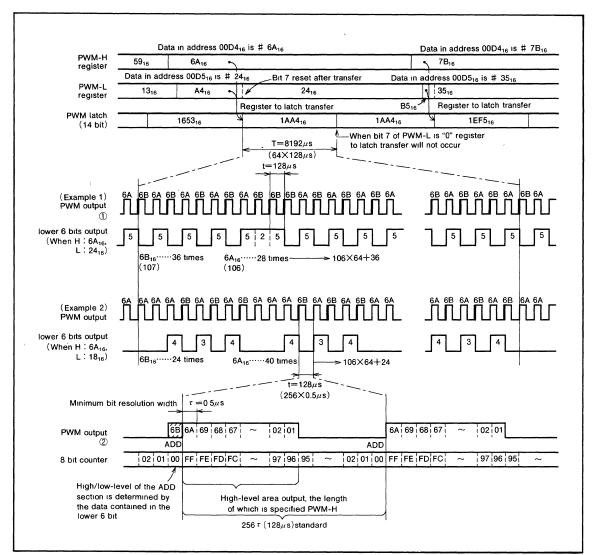

The M37424M8-XXXSP has a PWM function with a 14-bit resolution, a repeat period of  $8192\mu$ s when the oscillation frequency X<sub>IN</sub> is 4MHz (the explanation in the rest is based on the assumption that X<sub>IN</sub>=4MHz), and a minimum bit resolution width of 500ns. If data is set in the lower 6 bits of the pulse width modulation register L (PWM-L : address 00D5<sub>16</sub>) and the pulse width modulation register H (PWM-H : address 00D4<sub>16</sub>), and the port P5<sub>4</sub> function selection bit (bit 0 of the special function selection register) is set to "1", a PWM waveform is output from port P5<sub>4</sub>.

The period of  $8192\mu s$  is resolved into 16,384 minimum pulse widths (500ns), and the pulse width can be modulated in 500ns units in accordance with the 14 bits of data written into PWM-H and PWM-L. By dividing the  $8192\mu s$  repeat period into 64 short-area periods, pulses of approximately equal width can be output at a  $128\mu s$  period. A block diagram of the PWM circuit is shown in Figure 14.

The data written to the PWM register is transferred to the PWM latch at the repetition of the PWM period. The signals output to the PWM pin correspond to the contents of this latch. When data of PWM-L register is read, data in this latch has already been read allowing the data output by the PWM to be confirmed. In this case, the upper 2 bits of the 8-bit register becomes undefined. However, bit 7 of the PWM-L register indicated the completion of the data transfer from the PWM-L register to the PWM latch. If bit 7 is "0", the transfer has been completed, if bit 7 is "1", the transfer has not yet begun.

The timing diagram of the 14-bit PWM is shown in Figure 15. The 14-bit PWM divides the data within the PWM latch into the lower 6 bits and higher 8 bits.

A high-level area with a length N times  $\tau$  is output every short area of t=256× $\tau$  =128 $\mu$ s as determined by data N of the higher 8 bits. (Refer to PWM output ② in the lower part of Figure 15.) The contents of the lower 6 bits of data enable the leng-thening of the high signal by  $\tau$ .

Thus, the time for the high-level area is equal to the time set by the higher 8 bits or that plus  $\tau$ . As a result, the short-area period t(=128µs, approx. 7.8kHz) becomes an approximately repetitive period.

At reset the output of port  $P5_4$  is in the high impedance state and the contents of the PWM register and latch are undefined. Note that after setting the PWM register, its data is transferred to the latch.

# M37424M8-XXXSP M37524M4-XXXSP

| 6 lower-order bits of data | Area longer by $\tau$ than that of other t <sub>m</sub> (m = 0 ~63) |

|----------------------------|---------------------------------------------------------------------|

| 00000 <sup>LSB</sup>       | Nothing                                                             |

| 000001                     | m=32                                                                |

| 000010                     | m=16, 48                                                            |

| 000100                     | m = 8, 24, 40, 56                                                   |

| 001000                     | m = 4, 12, 20, 28, 36, 44, 52, 60                                   |

| 010000                     | m = 2, 6, 10, 14, 18, 22, 26, 30, 34, 38, 42, 46, 50, 54, 58, 62    |

| 100000                     | m = 1, 3, 5, 7,57, 59, 61, 63                                       |

Table 2.

Relation between the 6 lower-order bits of data and the space set by the ADD bit

Fig.14 Block diagram of PWM circuit

# M37424M8-XXXSP M37524M4-XXXSP

Fig.15 14-bit PWM timing diagram

# M37424M8-XXXSP M37524M4-XXXSP

### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

### A-D CONVERTER

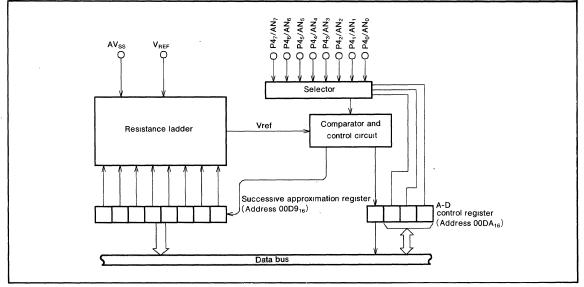

An 8-bit successive approximation method of A-D conversion is employed providing a precision of  $\pm$ 3LSB. A block diagram of the A-D converter is shown in Figure 16. Conversion is automatic once it is started with the program.

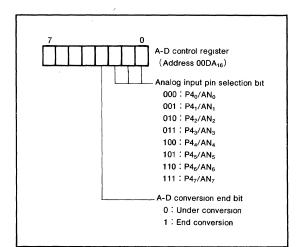

The analog inputs are used in common with port P4. Bits 2, 1 and 0 of the A-D control register (address  $00DA_{16}$ ) are used to select which pins are used for A-D conversion. The input condition is accomplished by setting to "0" the bit in the directional register that corresponds to the pin where A-D conversion is to take place. Bit 3 of the A-D control register is the A-D conversion end bit. During A-D conversion, this bit is "0", and upon completion becomes "1". Thus, it can be ascertained whether A-D conversion has been completed or not by inspecting this bit. The relation between the contents of the A-D control register and the selection of input pins are shown in Figure 17.

The results of the conversion can be found be reading the contents of the successive approximation register address  $00D9_{16}$  which stores the results of the conversion.

The procedure for executing A-D conversion is next explained. Firstly, the pin that is to be used for the A-D conversion is selected by setting bit 2, bit 1 and bit 0 of the A-D control register.

Next, clear the A-D conversion end bit to "0".

When the above is done, A-D conversion is started. A-D conversion completes after 49 clock cycles upon which the A-D conversion end bit is set to "1" and the results of the conversion can be found in the successive approximation register. Since the comparator consists of the capacitive coupled configuration,  $f(X_{\rm IN})$  is needed larger than 1MHz during A-D conversion.

Fig.17 Structure of A-D control register

Fig.16 Block diagram of A-D converter

# M37424M8-XXXSP M37524M4-XXXSP

### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

### **D-A CONVERTER**

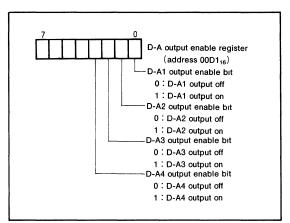

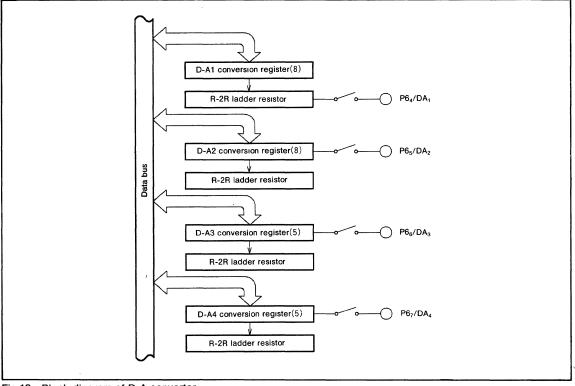

The M37424M8-XXXSP has two 8-bit resolution, R-2R method D-A converters and two 5-bit resolution D-A converters. A block diagram of the D-A converters is shown in Figure 19. If a value is written into one of the D-A conversion registers corresponding to these D-A converters, an analog voltage equivalent to that digital value is generated by the ladder resistors. If the corresponding D-A output enable bit (bit 0 to bit 3 of the D-A output enable register) is set to "1", that value is output to the corresponding output pin P6<sub>4</sub>/DA<sub>1</sub> to P6<sub>7</sub>/DA<sub>4</sub>. In this case, the directional register of that pin must be set to "0" to set input mode.

The relationship between analog voltage and digital value is as follows :

$$\begin{split} & \mathsf{V}{=}\mathsf{V}_{\mathsf{REF}}{\times}n/256(n{=}0\text{ to }255):\mathsf{DA}_1\text{ and }\mathsf{DA}_2\\ & \mathsf{V}{=}\mathsf{V}_{\mathsf{REF}}{\times}n/32(n{=}0\text{ to }31) :\mathsf{DA}_3\text{ and }\mathsf{DA}_4 \end{split}$$

Where V is the output voltage,  $V_{REF}$  is the reference voltage, and n is the value in the D-A conversion register.

At reset, the  $P6_4/DA_1$  to  $P6_7/DA_4$  pins go to high impedance. D-A output does not have a built-in buffer, so if connecting a low-impedance load, connect an external buffer as well.

The structure of the D-A output enable register is shown in Figure. 18.

Fig.18 D-A output enable register

Fig.19 Block diagram of D-A converter

# M37424M8-XXXSP M37524M4-XXXSP

#### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

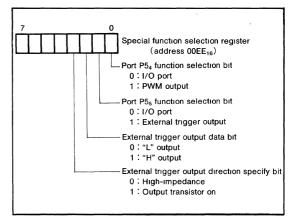

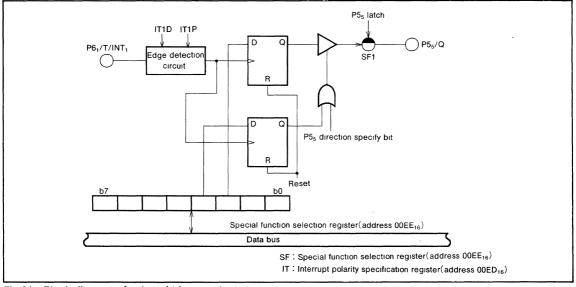

#### **EXTERNAL TRIGGER OUTPUT**

Port P5<sub>5</sub> operates as the pin Q which outputs the external trigger signal. Port P6<sub>1</sub> operates as the pin T which inputs the trigger clock. By setting bit 1 of the special function selection register (address  $00EE_{16}$ ) to "1", the P6<sub>1</sub>/T/INT<sub>1</sub> pin functions a trigger input pin and P6<sub>1</sub>, P5<sub>5</sub> can be used as the external trigger function pins.

In external trigger mode, the value set by the external trigger output data bit is output to port  $P5_5$  each time the active edge specified by bits 1 and 7 of the interrupt polarity specification register. Combinations of bits 3 and 4 of the special function selection register set port  $P5_5$  to output mode as shown in Table 3. If using external trigger output, set the  $P5_5$  directional bit to "0". At reset, this bit is cleared to "0".

#### Table 3. External trigger output

| External trigger<br>output data bit<br>External trigger output<br>direction specify bit | 0              | 1              |

|-----------------------------------------------------------------------------------------|----------------|----------------|

| 0                                                                                       | High-impedance | High-impedance |

| 1                                                                                       | L              | н              |

Fig.20 Structure of special function selection register

Fig.21 Block diagram of external trigger output

# M37424M8-XXXSP M37524M4-XXXSP

#### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

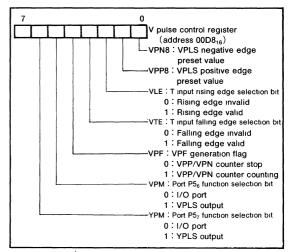

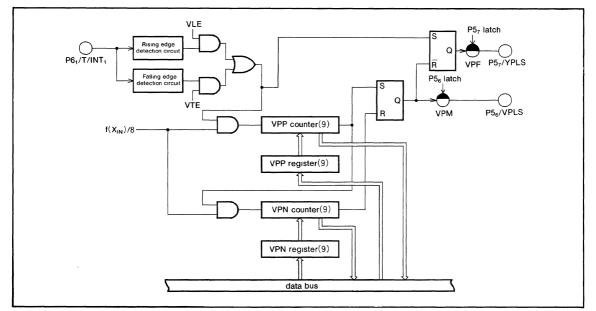

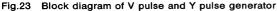

#### V PULSE AND Y PULSE GENERATOR

Port P5<sub>6</sub> operates as the VPLS pin to output the V pulse and port P5<sub>6</sub> operates as the T pin to input the trigger clock. P5<sub>6</sub> can be used as the V pulse output by setting bit 5 of the V pulse control register (00D8<sub>16</sub>) to "1". Port P5<sub>7</sub> operates as the YPLS pin which outputs the Y pulse. It can be used as the Y pulse (VPF signal) output by setting bit 6 of the V pulse control register to "1". Effective edge of trigger input can be selected by setting bits 2 and 3 of V pulse control register. Figure 22 shows the block diagram of the V pulse, Y pulse generator. Figure 23 shows the timing diagram of the V pulse and Y pulse.

At the falling or rising edge of T, the VPP counter starts. By the overflow signal of the VPP counter, VPLS goes "H". By the overflow signal of VPP counter, the VPN counter starts. By the overflow signal of the VPN counter, VPLS goes "L". When the VPP counter or the VPN counter is counting, bit 4 of the V pulse control register is "1".

The preset value of the VPP conter can be set by the 9-bit register with bit 1 of the V pulse control register being the most significant bit and the V pulse preset value P  $(00D6_{16})$  being the low-order eight bits. The preset value

of the VPN counter can be set by the 9-bit register with bit 0 of the V pulse control register being the most significant bit and the V pulse preset value N  $(00D7_{16})$  being the low-order eight bits.

Note that values of bits 0 and 1 of the V pulse control register are the current counting values in the VPP counter and the VPN counter, not the preset values of the counters.

Fig.22 Structure of V pulse control register

# M37424M8-XXXSP M37524M4-XXXSP

# M37424M8-XXXSP M37524M4-XXXSP

### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

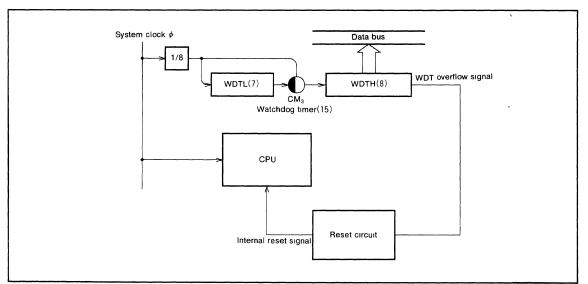

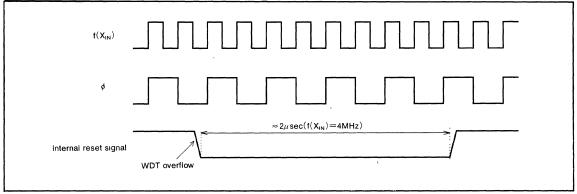

### WATCHDOG TIMER

The watchdog timer provides a method of returning to reset status if a runaway or other cause prevents a program from running a loop normally.

The watchdog timer is a 15-bit counter consisting of a lower seven bits and an upper eight bits (address  $00EF_{16}$ ). At reset or after the watchdog timer is written to,  $7FFF_{16}$  is set in this timer and it starts to count.

When the MSB reaches "0", an internal reset is generated. Therefore programs should normally be written to ensure that the watchdog timer is written to before this bit reaches "0". If address  $00EF_{16}$  is read, the value in the upper eight bits of the counter is read. Directly after a reset, the watchdog timer is stopped. After reset is released, the first write to address  $00EF_{16}$  validates the watchdog timer function.

The count source of the lower seven bits is a signal that is the system clock  $\phi$  divided by eight. The count source of the upper eight bits can be selected as either the overflow signal from the 7-bit counter or a signal that is the system clock  $\phi$  divided by eight, depending on the value of bit 3 of the CPU mode register (address 00FB<sub>16</sub>).

Fig.25 Block diagram of runaway detection function

Fig.26 Timing diagram of internal reset signal

# M37424M8-XXXSP M37524M4-XXXSP

### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

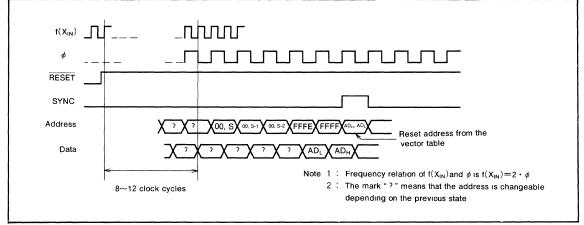

## I/O PORTS

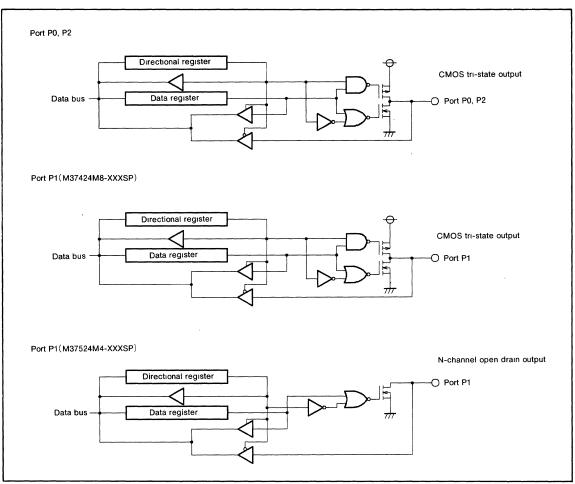

## (1) Port P0

Port P0 is an 8-bit I/O port with CMOS output. As shown in the memory map (Figure 1), port P0 can be accessed at zero page memory address 00C016. Port P0 has a directional register (address 00C116) which can be used to program each individual bit as input ("0") or as output ("1"). If the pins are programmed as output, the output data is latched to the port register and then output. When data is read from the output port the output pin level is not read, only the latched data in the port register is read. This allows a previously output value to be read correctly even though the output voltage level is shifted up or down. Pins set as input are in the floating state and the signal levels can thus be read. When data is written into the input port, the data is latched only to the port latch and the pin still remains in the floating state.

(2) Port P1

Port P1 has the same function as Port P0. The output structure of M37424M8-XXXSP is CMOS output. The output structure of M37524M4-XXXSP is N-channel open drain output.

(3) Port P2

Port P2 has the same function as Port P0.

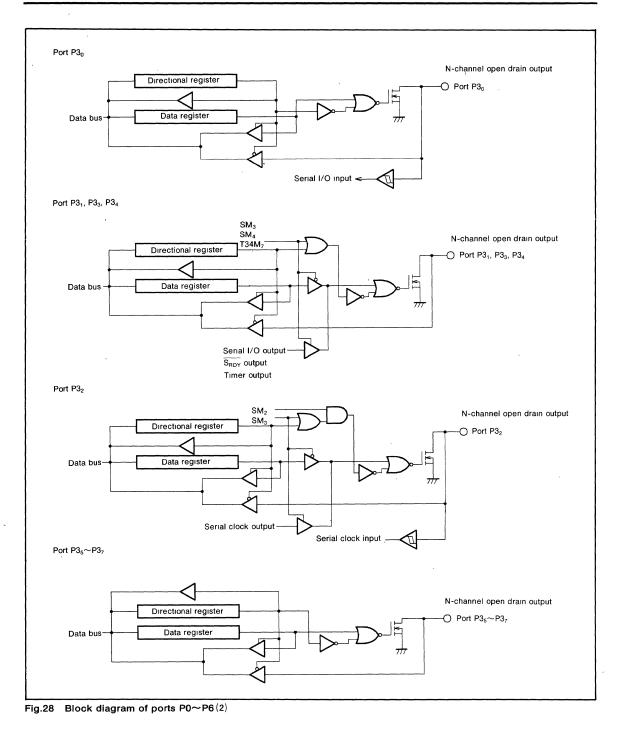

(4) Port P3

Port P3 has the same function as port P0, but it has Nchannel open drain output. Port P3 can also be used as serial I/O and timer output pins.

(5) Port P4

Port P4 has the same function as port P0. P47 through P40 can also be used as analog input pins AN7 through AN0.

#### (6) Port P5

Port P5 has the same function as port P0. Port P5 can also be used as  $INT_2 \sim INT_5$ , PWM output, external trigger output Q and V pulse, Y pulse output pins.

(7) Port P6

Port P6 has the same function as port P0. Port P6 can also be used as  $INT_0$ ,  $INT_1$ , trigger clock input T, timer I/O and D-A output pins.

# M37424M8-XXXSP M37524M4-XXXSP

## SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

Fig.27 Block diagram of ports P0~P6(1)

,

# M37424M8-XXXSP M37524M4-XXXSP

# M37424M8-XXXSP M37524M4-XXXSP

# M37424M8-XXXSP M37524M4-XXXSP

Fig.30 Block diagram of ports P0~P6(4)

## M37424M8-XXXSP M37524M4-XXXSP

## SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

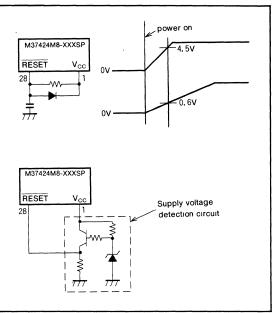

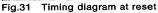

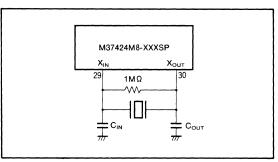

### **RESET CIRCUIT**

The M37424M8-XXXSP is reset according to the sequence shown in Figure 31. It starts the program from the address formed by using the content of address FFFF<sub>16</sub> as the high order address and the content of the address FFFE<sub>16</sub> as the low order address, when the RESET pin is held at "L" level for more than  $2\mu$ s while the power voltage is in the recommended operating condition and the crystal oscillator oscillation is stable and then returned to "H" level. The internal initializations following reset are shown in Figure 33. An example of the reset circuit is shown in Figure 32.

When the power on reset is used, the  $\overrightarrow{\text{RESET}}$  pin must be held "L" until the oscillation of X<sub>IN</sub>-X<sub>OUT</sub> becomes stable.

Fig.32 Example of reset circuit

# M37424M8-XXXSP M37524M4-XXXSP

|      |                                           | address               |                                        |  |  |  |  |

|------|-------------------------------------------|-----------------------|----------------------------------------|--|--|--|--|

| (1)  | Port P0 directional register              | (C1 <sub>16</sub> )   | 00 <sub>16</sub>                       |  |  |  |  |

| (2)  | Port P1 directional register              | (C3 <sub>16</sub> )   | 0016                                   |  |  |  |  |

| (3)  | Port P2 directional register              | (C 5 <sub>16</sub> )  | 00 <sub>16</sub>                       |  |  |  |  |

| (4)  | Port P3 directional register              | (C7 <sub>16</sub> )   | 00 <sub>16</sub>                       |  |  |  |  |

| (5)  | Port P4 directional register              | (C9 <sub>16</sub> )   | 0016                                   |  |  |  |  |

| (6)  | Port P5 directional register              | (CB <sub>16</sub> )   | 0016                                   |  |  |  |  |

| (7)  | Port P6 directional register              | ( C D <sub>16</sub> ) | 0016                                   |  |  |  |  |

| (8)  | D-A output enable register                | (D1 <sub>16</sub> )   | 0000                                   |  |  |  |  |

| (9)  | D-A3 conversion register                  | (D2 <sub>16</sub> )   | 0016                                   |  |  |  |  |

| (10) | D-A4 conversion register                  | (D3 <sub>16</sub> )   | 0016                                   |  |  |  |  |

| (11) | V pulse control register                  | (D 8 16)              | 0 0 0 0                                |  |  |  |  |

| (12) | A-D control register                      | ( D A <sub>16</sub> ) | 0000                                   |  |  |  |  |

| (13) | D-A1 conversion register                  | (DB <sub>16</sub> )   | 0016                                   |  |  |  |  |

| (14) | D-A2 conversion register                  | ( D C <sub>16</sub> ) | 0016                                   |  |  |  |  |

| (15) | Serial I/O mode register                  | ( D D <sub>16</sub> ) | 0016                                   |  |  |  |  |

| (16) | Interrupt polarity specification register | ( E D <sub>16</sub> ) | 0016                                   |  |  |  |  |

| (17) | Special function selection register       | (EE <sub>16</sub> )   | 0000                                   |  |  |  |  |

| (18) | Watchdog timer                            | (EF <sub>16</sub> )   | 7FFF <sub>16</sub>                     |  |  |  |  |

| (19) | Timer 3                                   | (F2 <sub>16</sub> )   | . FF <sub>16</sub>                     |  |  |  |  |

| (20) | Timer 4                                   | (F3 <sub>16</sub> )   | 07 <sub>16</sub>                       |  |  |  |  |

| (21) | Timer 1, 2 mode register                  | (F8 <sub>16</sub> )   | 0 0 0 0 0 0                            |  |  |  |  |

| (22) | Timer 3, 4 mode register                  | (F9 <sub>16</sub> )   | 0000                                   |  |  |  |  |

| (23) | Timer X mode register                     | (FA <sub>16</sub> )   | 0016                                   |  |  |  |  |

| (24) | CPU mode register                         | (FB <sub>16</sub> )   | 1 0 1 0 0                              |  |  |  |  |

| (25) | Interrupt request register 1              | (FC <sub>16</sub> )   | 0016                                   |  |  |  |  |

| (26) | Interrupt request register 2              | (FD <sub>16</sub> )   | 0016                                   |  |  |  |  |

| (27) | Interrupt control register 1              | (FE <sub>16</sub> )   | 0016                                   |  |  |  |  |

| (28) | Interrupt control register 2              | (FF <sub>16</sub> )   | 0016                                   |  |  |  |  |

| (29) | Processor status register                 | (PS)                  | 1                                      |  |  |  |  |

| (30) | Program counter                           | (PC <sub>H</sub> )    | Contents of address FFFF <sub>16</sub> |  |  |  |  |

|      |                                           | ( P C L)              | Contents of address FFFE <sub>16</sub> |  |  |  |  |

|      |                                           |                       |                                        |  |  |  |  |

Fig. 33 Internal state of microcomputer at reset

## M37424M8-XXXSP M37524M4-XXXSP

## SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

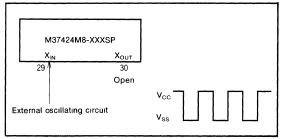

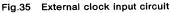

### **CLOCK GENERATING CIRCUIT**

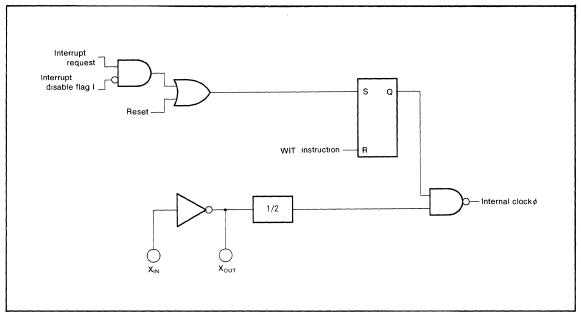

The built-in clock generating circuits are shown in Figure 36. When the WIT instruction is executed, the internal clock  $\phi$  stops in the "H" level but the oscillator continues running. This wait state is cleared when an interrupt is accepted. Since the oscillation does not stop, the next instructions are executed at once. To return from the wait status, the interrupt enable bit must be set to "1" before executing WIT instruction.

Since the M37424M8-XXXSP does not have STP instruction, the oscillation can not be stopped.

The circuit example using a ceramic oscillator (or a quartz crystal oscillator) is shown in Figure 34.

The constant capacitance will differ depending on which oscillator is used, and should be set to the manufactures suggested value.

The example of external clock usage is shown in Figure 35.  $X_{\rm IN}$  is the input, and  $X_{\rm OUT}$  is open.

Fig.34 External ceramic resonator circuit

Fig.36 Block diagram of the clock generating circuit

## M37424M8-XXXSP M37524M4-XXXSP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

#### **PROGRAMMING NOTES**

- (1) The frequency ratio of the timer is 1/(n+1).

- (2) Even though the BBC and BBS instructions are executed after the interrupt request bits are modified (by the program), those instructions are only valid for the contents before the modification. Also, at least one instruction cycle must be used (such as a NOP) between the modification of the interrupt request bits and the execution of the BBC and BBS instructions.

- (3) After the ADC and SBC instructions are executed (in decimal mode), one instruction cycle (such as a NOP) is needed before the SEC, CLC, or CLD instructions are executed.

- (4) A NOP instruction must be used after the execution of a PLP instruction.

## DATA REQUIRED FOR MASK ORDERING

Please send the following data for mask orders.

- (1) mask ROM confirmation form

- (2) mark specification form

- (3) ROM data ..... EPROM 3sets

# M37424M8-XXXSP M37524M4-XXXSP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

#### M37424M8-XXXSP **ABSOLUTE MAXIMUM RATINGS**

| Symbol          | Parameter                                                                                                                                                                                                                                                   | Conditions | Ratings                   | Unit |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------------|------|

| V <sub>cc</sub> | Supply voltage                                                                                                                                                                                                                                              |            | -0.3~7                    | v    |

| Vss             | Supply voltage                                                                                                                                                                                                                                              |            | 0                         | v    |

| VREF            | Reference voltage                                                                                                                                                                                                                                           | s          | $-0.3 \sim V_{cc} + 0.3$  | v    |

| V <sub>1</sub>  | Input voltage XIN, RESET, P30~P37, CNVSS                                                                                                                                                                                                                    |            | -0.3~7                    | v    |

| Vı              | Input voltage P0 <sub>0</sub> ~P0 <sub>7</sub> , P1 <sub>0</sub> ~P1 <sub>7</sub> , P2 <sub>0</sub> ~P2 <sub>7</sub> ,<br>P4 <sub>0</sub> ~P4 <sub>7</sub> , P5 <sub>0</sub> ~P5 <sub>7</sub> , P6 <sub>0</sub> ~P6 <sub>7</sub>                            |            | -0.3~V <sub>cc</sub> +0.3 | v    |

| Vo              | Output voltage P30~P37                                                                                                                                                                                                                                      |            | 0.3~7                     | v    |

| Vo              | Output voltage P0 <sub>0</sub> ~P0 <sub>7</sub> , P1 <sub>0</sub> ~P1 <sub>7</sub> , P2 <sub>0</sub> ~P2 <sub>7</sub> ,<br>P4 <sub>0</sub> ~P4 <sub>7</sub> , P5 <sub>0</sub> ~P5 <sub>7</sub> , P6 <sub>0</sub> ~P6 <sub>7</sub> ,<br>X <sub>OUT</sub> , φ |            | -0.3~V <sub>cc</sub> +0.3 | v    |

| Pd              | Power dissipation                                                                                                                                                                                                                                           | Ta=25°C    | 1000                      | mW   |

| Topr            | Operating temperature                                                                                                                                                                                                                                       |            | -10~70                    | °C   |

| Tstg            | Storage temperature                                                                                                                                                                                                                                         |            | -40~125                   | °C   |

### **RECOMMENDED OPERATING CONDITIONS** ( $v_{cc}=5v\pm10\%$ , $T_a=-10\sim70$ °C, unless otherwise noted)

| Symbol                 | Parameter                                                                                                                                                                                                                                                                                                                                                                              |                    | Limits                                |                     |      |  |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------------------------|---------------------|------|--|

| Symbol                 | Parameter                                                                                                                                                                                                                                                                                                                                                                              | Mın                | Тур                                   | Max                 | Unit |  |

| V <sub>cc</sub>        | Supply voltage                                                                                                                                                                                                                                                                                                                                                                         | 4.5                | 5                                     | 5.5                 | v    |  |

| V <sub>SS</sub>        | Supply voltage                                                                                                                                                                                                                                                                                                                                                                         |                    | 0                                     |                     | v    |  |

| V <sub>IH</sub>        | "H" input voltage P0 <sub>0</sub> ~P0 <sub>7</sub> , P1 <sub>0</sub> ~P1 <sub>7</sub> , P2 <sub>0</sub> ~P2 <sub>7</sub> ,<br>P3 <sub>0</sub> ~P3 <sub>7</sub> , P4 <sub>0</sub> ~P4 <sub>7</sub> , P5 <sub>0</sub> ~P5 <sub>7</sub> ,<br>P6 <sub>0</sub> ~P6 <sub>7</sub> , INT <sub>0</sub> ~INT <sub>5</sub> , CNTR <sub>0</sub> ,<br>CNTR <sub>1</sub> , T, RESET, X <sub>IN</sub> | 0.8V <sub>cc</sub> |                                       | V <sub>cc</sub>     | v    |  |

| VIL                    | "L" input voltage $P0_0 \sim P0_7$ , $P1_0 \sim P1_7$ , $P2_0 \sim P2_7$ ,<br>$P3_0 \sim P3_7$ , $P4_0 \sim P4_7$ , $P5_0 \sim P5_7$ ,<br>$P6_0 \sim P6_7$ , $INT_0 \sim INT_5$ ,<br>$CNTR_0$ , $CNTR_1$ , T                                                                                                                                                                           | 0                  |                                       | 0. 2V <sub>CC</sub> | v    |  |

| VIL                    | "L" input voltage RESET                                                                                                                                                                                                                                                                                                                                                                | 0                  |                                       | 0.12V <sub>cc</sub> | v    |  |

| VIL                    | "L" input voltage X <sub>IN</sub>                                                                                                                                                                                                                                                                                                                                                      | 0                  |                                       | 0.16V <sub>cc</sub> | v    |  |

| I <sub>он(peak)</sub>  | "H" peak output current P0 <sub>0</sub> ~P0 <sub>7</sub> , P1 <sub>0</sub> ~P1 <sub>7</sub> ,<br>P2 <sub>0</sub> ~P2 <sub>7</sub> , P4 <sub>0</sub> ~P4 <sub>7</sub> ,<br>P5 <sub>0</sub> ~P5 <sub>7</sub> , P6 <sub>0</sub> ~P6 <sub>7</sub> (Note 1)                                                                                                                                 |                    |                                       | -10                 | mA   |  |

| I <sub>он(avg)</sub>   | "H" average output current P0 <sub>0</sub> ~P0 <sub>7</sub> , P1 <sub>0</sub> ~P1 <sub>7</sub> ,<br>P2 <sub>0</sub> ~P2 <sub>7</sub> , P4 <sub>0</sub> ~P4 <sub>7</sub> ,<br>P5 <sub>0</sub> ~P5 <sub>7</sub> , P6 <sub>0</sub> ~P6 <sub>7</sub> (Note 1)                                                                                                                              |                    |                                       | -5                  | mA   |  |

| l <sub>o∟(</sub> peak) | "L" peak output current P0 <sub>0</sub> ~P0 <sub>7</sub> , P1 <sub>0</sub> ~P1 <sub>7</sub> ,<br>P2 <sub>0</sub> ~P2 <sub>7</sub> , P3 <sub>0</sub> ~P3 <sub>7</sub> ,<br>P4 <sub>0</sub> ~P4 <sub>7</sub> , P5 <sub>0</sub> ~P5 <sub>7</sub> ,<br>P6 <sub>0</sub> ~P6 <sub>7</sub> (Note 2)                                                                                           |                    |                                       | 10                  | mA   |  |

| l <sub>o∟(</sub> avg)  | "L" average output current P0 <sub>0</sub> ~P0 <sub>7</sub> , P1 <sub>0</sub> ~P1 <sub>7</sub> ,<br>P2 <sub>0</sub> ~P2 <sub>7</sub> , P3 <sub>0</sub> ~P3 <sub>7</sub> ,<br>P4 <sub>0</sub> ~P4 <sub>7</sub> , P5 <sub>0</sub> ~P5 <sub>7</sub> ,<br>P6 <sub>0</sub> ~P6 <sub>7</sub> (Note 2)                                                                                        |                    |                                       | 5                   | mA   |  |

| $f(X_{IN})$            | Clock oscillating frequency                                                                                                                                                                                                                                                                                                                                                            |                    | · · · · · · · · · · · · · · · · · · · | 4                   | MHz  |  |

Note 1. The total of "H" peak output current of port P0, P1, P2, P4, P5 and P6 is less than 65mA 2. The total of "L" peak output current of port P0, P1, P2, P3, P4, P5 and P6 is less than 65mA

## M37424M8-XXXSP M37524M4-XXXSP

### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

| Symbol          | Parameter                                                                                                                                                                                                                             | Test conditions                                                                                                                                                                                         | Limits |     |      | Unit |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|------|------|

|                 |                                                                                                                                                                                                                                       | rest conditions                                                                                                                                                                                         | Min    | Тур | Max  | Unit |

| V <sub>он</sub> | "H" output voltage $P0_0 \sim P0_7$ , $P1_0 \sim P1_7$ , $P2_0 \sim P2_7$ ,<br>$P4_0 \sim P4_7$ , $P5_0 \sim P5_7$ , $P6_0 \sim P6_7$                                                                                                 | I <sub>OH</sub> =-10mA                                                                                                                                                                                  | 3      |     |      | v    |

| V <sub>он</sub> | "H" output voltage φ                                                                                                                                                                                                                  | I <sub>ОН</sub> =-2.5mA                                                                                                                                                                                 | 3      |     |      | v    |

| Vol             | "L" output voltage P30~P37                                                                                                                                                                                                            | I <sub>OL</sub> =10mA                                                                                                                                                                                   |        |     | 2    | v    |

| V <sub>OL</sub> | "L" output voltage P0 <sub>0</sub> ~P0 <sub>7</sub> , P1 <sub>0</sub> ~P1 <sub>7</sub> , P2 <sub>0</sub> ~P2 <sub>7</sub> ,<br>P4 <sub>0</sub> ~P4 <sub>7</sub> , P5 <sub>0</sub> ~P5 <sub>7</sub> , P6 <sub>0</sub> ~P6 <sub>7</sub> | I <sub>OL</sub> =10mA                                                                                                                                                                                   |        |     | 2    | v    |

| Vol             | "L" output voltage $\phi$                                                                                                                                                                                                             | I <sub>OL</sub> =2.5mA                                                                                                                                                                                  |        |     | 2    | v    |

| V+-V-           | Hysteresis X <sub>IN</sub>                                                                                                                                                                                                            |                                                                                                                                                                                                         | 0.1    |     | 0.5  | v    |

| V+-V-           | Hysteresis RESET                                                                                                                                                                                                                      |                                                                                                                                                                                                         |        | 0.5 | 0.7  | v    |

| $v_{+} - v_{-}$ | Hysteresis INT <sub>0</sub> ~INT <sub>5</sub> , CNTR <sub>0</sub> , CNTR <sub>1</sub> , T                                                                                                                                             | Use as INT <sub>0</sub> ~INT <sub>5</sub> , CNTR <sub>0</sub> , CNTR <sub>1</sub> , T input                                                                                                             | 0.3    |     | 1.0  | v    |

| lн              | "H" input current RESET, XIN                                                                                                                                                                                                          | V <sub>IH</sub> =5V                                                                                                                                                                                     |        |     | 5    | μA   |

| l <sub>iH</sub> | "H" input current P0 <sub>0</sub> ~P0 <sub>7</sub> , P1 <sub>0</sub> ~P1 <sub>7</sub> , P2 <sub>0</sub> ~P2 <sub>7</sub> ,<br>P4 <sub>0</sub> ~P4 <sub>7</sub> , P5 <sub>0</sub> ~P5 <sub>7</sub> , P6 <sub>0</sub> ~P6 <sub>7</sub>  | V <sub>IH</sub> =5V                                                                                                                                                                                     |        |     | 5    | μA   |

| I <sub>IH</sub> | "H" input current P30~P37                                                                                                                                                                                                             | V <sub>IH</sub> =5V                                                                                                                                                                                     |        |     | 5    | μA   |

| հե              | "L" input current RESET, XIN                                                                                                                                                                                                          | V <sub>IL</sub> =0V                                                                                                                                                                                     | -5     |     |      | μA   |

| l <sub>IL</sub> | "L" input current $P0_0 \sim P0_7$ , $P1_0 \sim P1_7$ , $P2_0 \sim P2_7$ ,<br>$P4_0 \sim P4_7$ , $P5_0 \sim P5_7$ , $P6_0 \sim P6_7$                                                                                                  | V <sub>IL</sub> =0V                                                                                                                                                                                     | —5     |     |      | μA   |

| I <sub>IL</sub> | "L" input current P30~P37                                                                                                                                                                                                             | V <sub>IL</sub> =0V                                                                                                                                                                                     | -5     |     |      | μA   |

| l <sub>cc</sub> | Supply current                                                                                                                                                                                                                        | $\label{eq:rescaled} \begin{array}{l} f(X_{IN}) = 4MHz, \mbox{ output pins opened, input pins at } V_{SS} \mbox{ or } V_{CC}, \mbox{ and } A-D \mbox{ converter in the finished condition} \end{array}$ |        | 6   | 12 , | mA   |

#### ELECTRICAL CHARACTERISTICS (V<sub>cc</sub>=5V, V<sub>ss</sub>=0V, T<sub>a</sub>=25°C, f(X<sub>IN</sub>)=4MHz, unless otherwise noted)

ş

### A-D CONVERTER CHARACTERISTICS (V<sub>cc</sub>=5v, V<sub>ss</sub>=0v, T<sub>a</sub>=25°C, f(X<sub>IN</sub>)=4MHz, unless otherwise noted)

| Symbol            | Parameter            | <b>T</b>                          |     | Linut |                 |      |

|-------------------|----------------------|-----------------------------------|-----|-------|-----------------|------|

|                   |                      | Test conditions                   | Min | Тур   | Max             | Unit |

|                   | Resolution           | V <sub>REF</sub> =V <sub>CC</sub> |     |       | 8               | bits |

|                   | Absolute accuracy    | V <sub>REF</sub> =V <sub>CC</sub> |     |       | ±3              | LSB  |

| RLADDER           | Ladder resistor      | V <sub>REF</sub> =V <sub>CC</sub> | 20  | 1     |                 | kΩ   |