# RENESAS

# 7643 Group SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

# DESCRIPTION

The 7643 group is the 8-bit microcomputer based on the 7600 series core (740 family core compatible) technology.

The 7643 group is designed for PC peripheral devices, including the USB, DMAC, Serial I/O, UART, Timer and so on.

# **FEATURES**

| <flash memory="" mode=""></flash>                               |

|-----------------------------------------------------------------|

| Power source voltage                                            |

| At 24 MHz oscillation frequency, $\phi$ = 12 MHz 4.15 to 5.25 V |

| At 24 MHz oscillation frequency, $\phi$ = 6 MHz                 |

| Program/Erase voltage                                           |

| Vcc = 4.50 V to 5.25 V, or 3.00 V to 3.60 V                     |

|                                                                 |

| At 24 MHz oscillation frequency, $\phi = 6$ MHz (See Table 20.) |

| Memory size                                                     |

| Flash ROM 32 Kbytes                                             |

| RAM 2.5 Kbytes                                                  |

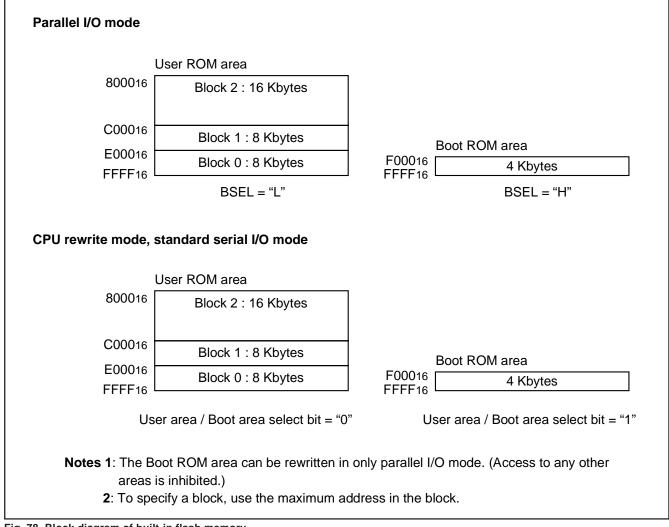

| •Flash memory mode 3 modes                                      |

| Parallel I/O mode                                               |

| Standard serial I/O mode                                        |

| CPU rewrite mode                                                |

| Programming method Programming in unit of byte                  |

| Erasing method                                                  |

| Batch erasing                                                   |

| Block erasing                                                   |

| Program/Erase control by software command                       |

| Command number                                                  |

| Number of times for programming/erasing                         |

| ROM code protection                                             |

| Available in parallel I/O mode and standard serial I/O mode     |

| • Operating temperature range (at programming/erasing)          |

|                                                                 |

|                                                                 |

| APPLICATION                                                     |

|                                                                 |

Audio, musical instrument, printer, scanner, modem, other PC peripheral devices

#### ■Notes

- 1. The specifications of this product are subject to change because it is under development. Inquire the use of Renesas Technology Corporation.

- 2. The flash memory version cannot be used for application embedded in the MCU card.

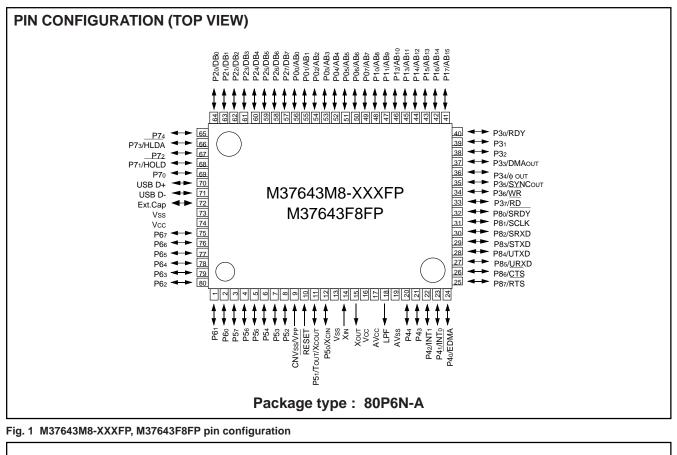

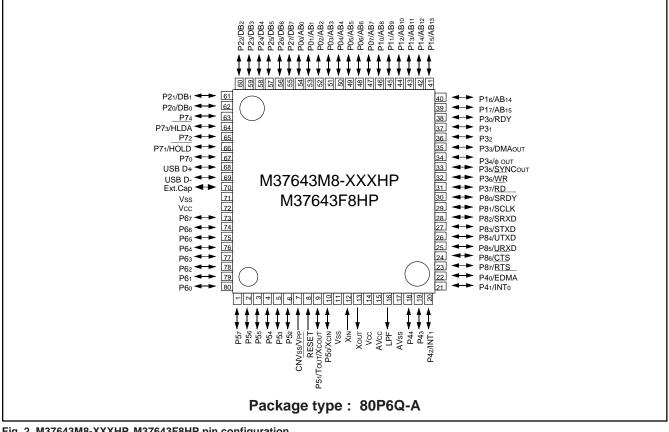

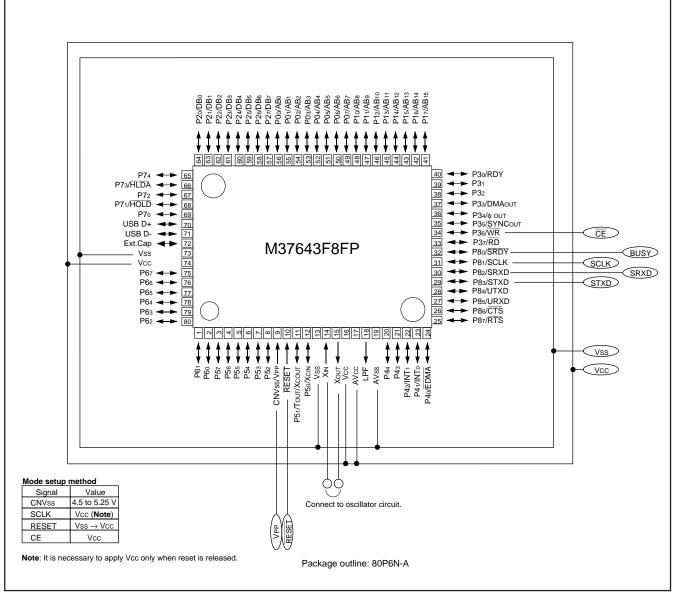

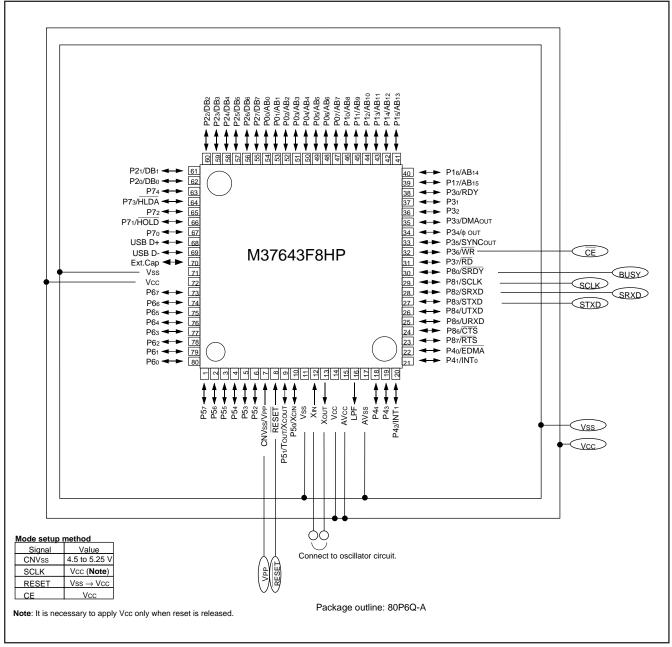

Fig. 2 M37643M8-XXXHP, M37643F8HP pin configuration

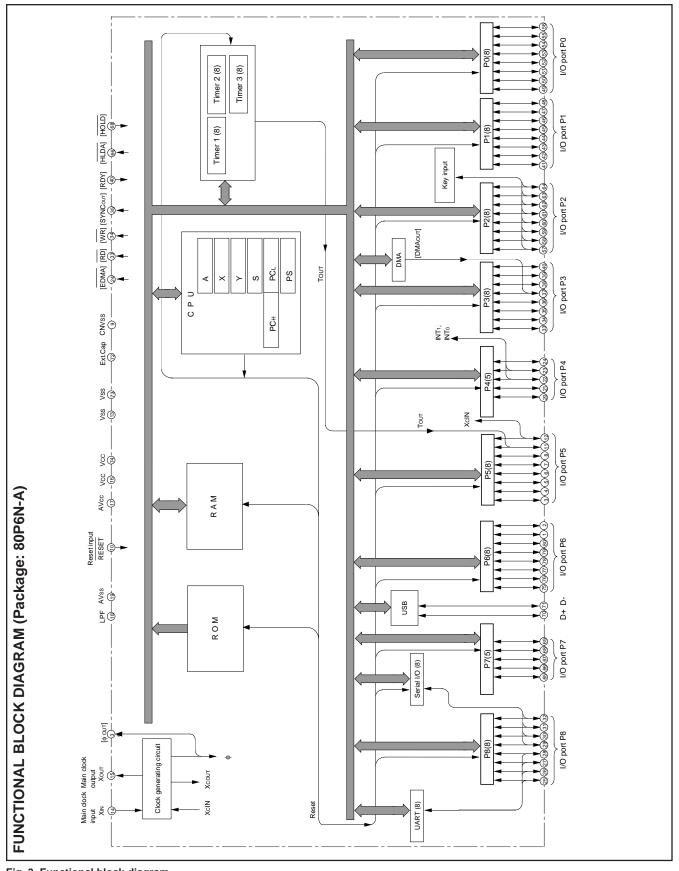

Fig. 3 Functional block diagram

# **PIN DESCRIPTION**

| Pin Name                                                                                 |                               | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Function except a port function                 |  |  |  |  |

|------------------------------------------------------------------------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|--|--|--|--|

| Vcc, Vss                                                                                 | Power source                  | <ul> <li>Apply 4.15 V – 5.25 V for 5 V version or 3.00 V – 3.60 V for 3 V version to the Vcc pin. Apply 0 V to the Vss pin.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                 |  |  |  |  |

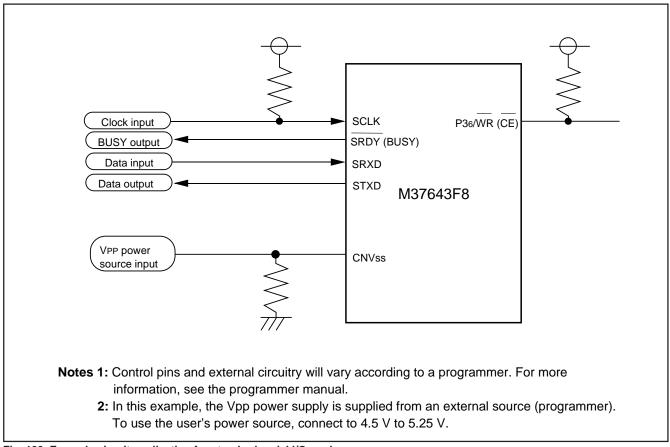

| CNVss/Vpp                                                                                | CNVss                         | <ul> <li>This controls the MCU operating mode. Connect this pin to Vss. If connecting this pin to Vcc, the<br/>internal ROM is inhibited. In the flash memory version this pin functions as a VPP power supply input pin.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                 |  |  |  |  |

| AVss/AVcc                                                                                | Analog power<br>supply        | These pins are the power supply inputs for analog circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                 |  |  |  |  |

| RESET                                                                                    | Reset input                   | Reset input pin for active "L."                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                 |  |  |  |  |

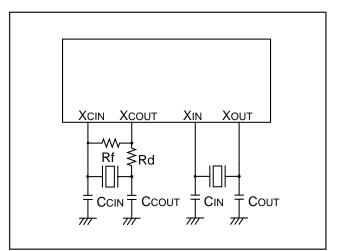

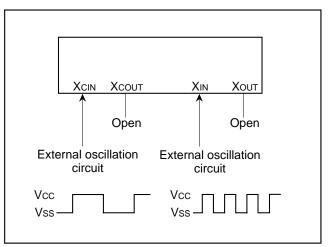

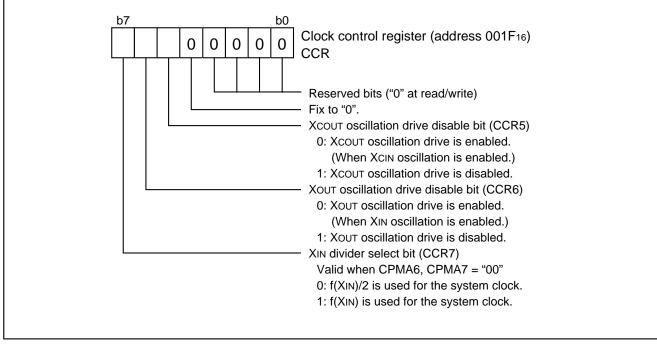

| Xin                                                                                      | Clock input                   | Connect a ceramic resonator or a quartz-crystal oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | between the XIN and XOUT pins to set the        |  |  |  |  |

| Хоит                                                                                     | Clock output                  | <ul> <li>oscillation frequency.</li> <li>If an external clock is used, connect the clock source to the XIN pin and leave the XOUT pin open.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                 |  |  |  |  |

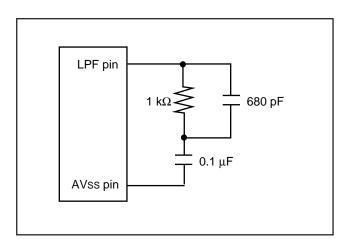

| LPF                                                                                      | LPF                           | Loop filter for the frequency synthesizer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                 |  |  |  |  |

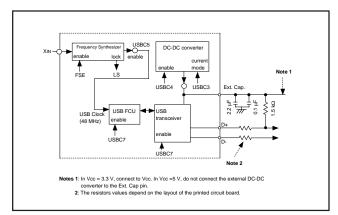

| Ext. Cap.                                                                                | 3.3 V line power supply       | <ul> <li>It is a capacitor connection pin for built-in DC-DC converte<br/>by permitting a USB line driver and connect a capacitor. Re<br/>DC converter cannot be used at Vcc = 3.3 V. Supply 3.3V</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | fer to "Notes on use" for details. Built-in DC- |  |  |  |  |

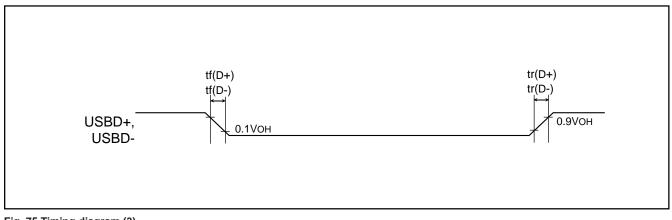

| USB D+                                                                                   | USB D+                        | • USB D+ voltage signal port. Connect a 27 to 33 $\Omega$ (recomm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | nended) resistor in series.                     |  |  |  |  |

| USB D-                                                                                   | USB D-                        | $\bullet$ USB D- voltage signal port. Connect a 27 to 33 $\Omega$ (recomm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | nended) resistor in series.                     |  |  |  |  |

| P00/AB0-<br>P07/AB7                                                                      | I/O port P0                   | <ul> <li>8-bit I/O port.</li> <li>CMOS compatible input level.</li> <li>CMOS 3-state output structure.</li> <li>I/O direction register allows each pin to be individually prog</li> <li>When connecting an external memory, these function as the structure of the st</li></ul> |                                                 |  |  |  |  |

| P10/AB8–<br>P17/AB15                                                                     | I/O port P1                   | <ul> <li>8-bit I/O port.</li> <li>CMOS compatible input level.</li> <li>CMOS 3-state output structure.</li> <li>I/O direction register allows each pin to be individually programmed as either input or output.</li> <li>When connecting an external memory, these function as the address bus.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                 |  |  |  |  |

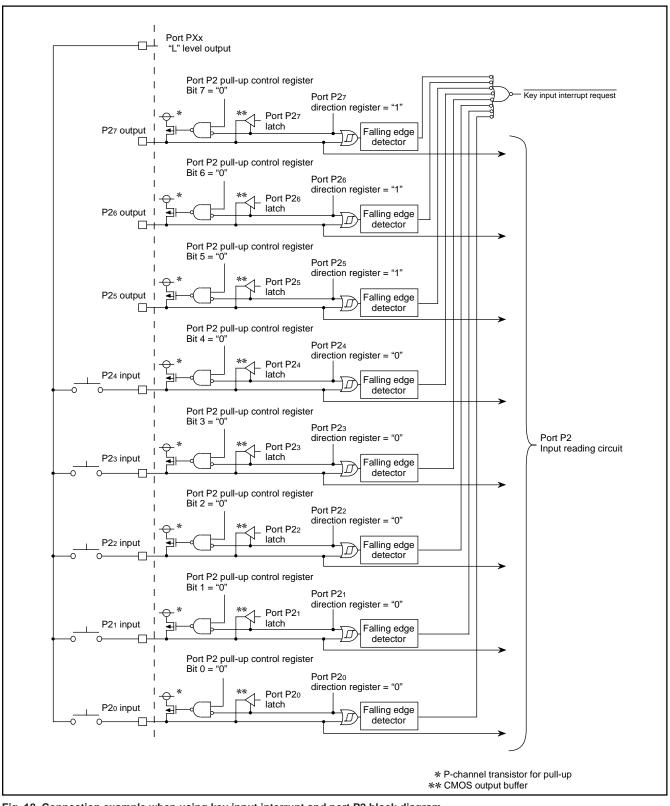

| P20/DB0–<br>P27/DB7                                                                      | I/O port P2                   | <ul> <li>8-bit I/O port.</li> <li>CMOS compatible input level or VIHL input level.</li> <li>CMOS 3-state output structure.</li> <li>I/O direction register allows each pin to be individually programmed as either input or output.</li> <li>When connecting an external memory, these function as the data bus.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Key-on wake-up interrupt input pin              |  |  |  |  |

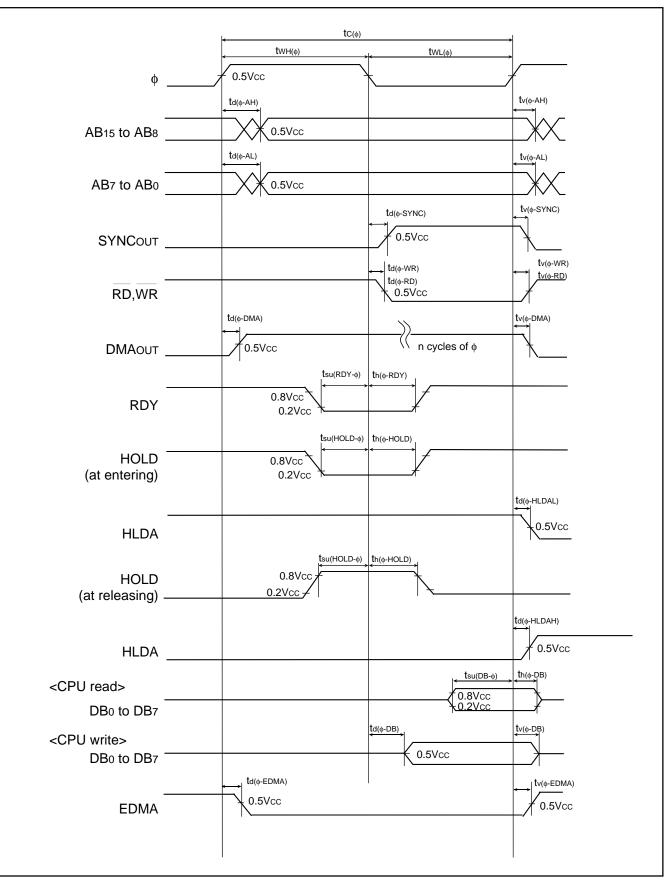

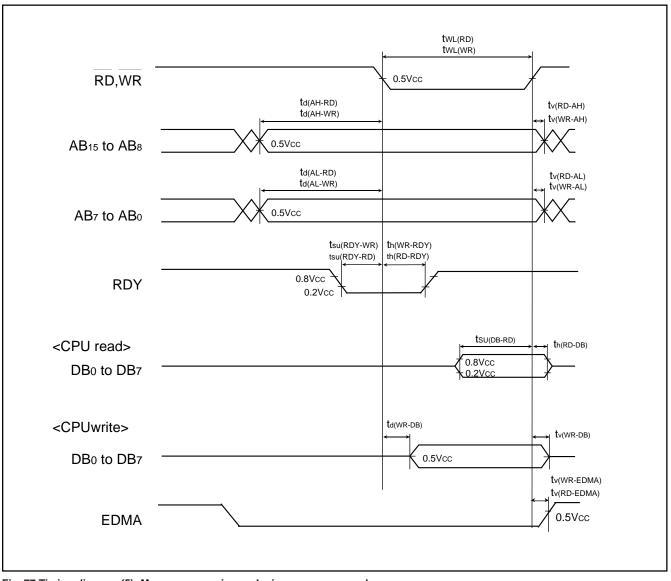

| P30/RDY,<br>P31, P32,<br>P33/DMAOUT,<br>P34/\$ OUT,<br>P35/SYNCOUT,<br>P36/WR,<br>P37/RD | I/O port P3<br>(See Remarks.) | <ul> <li>8-bit I/O port.</li> <li>CMOS compatible input level.</li> <li>CMOS 3-state output structure.</li> <li>I/O direction register allows each pin to be individually programmed as either input or output.</li> <li>When connecting an external memory, these function as the control bus.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | External memory control pin                     |  |  |  |  |

| P40/EDMA,                                                                                | I/O port P4                   | • 8-bit I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | External memory control pin                     |  |  |  |  |

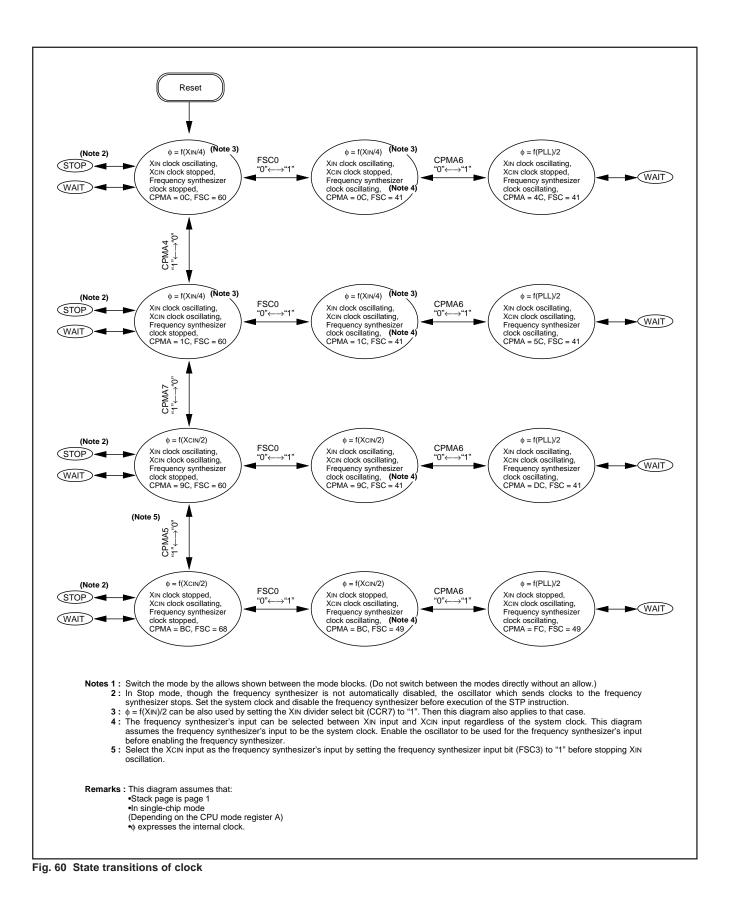

| P41/INT0,                                                                                |                               | CMOS compatible input level.     CMOS 3 state output structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | External interrupt pin                          |  |  |  |  |

| P42/INT1,<br>P43,P44                                                                     |                               | <ul> <li>CMOS 3-state output structure.</li> <li>I/O direction register allows each pin to be individually programmed as either input or output.</li> <li>When connecting an external memory, these function as the control bus.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                 |  |  |  |  |

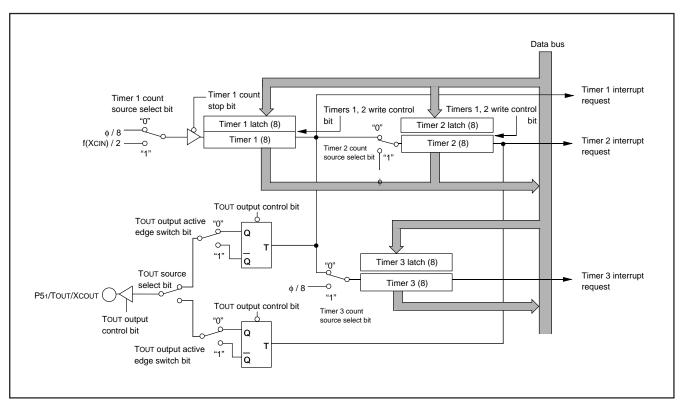

| P50/XCIN,                                                                                | I/O port P5                   | • 8-bit I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Sub-clock generating input pin                  |  |  |  |  |

| P51/TOUT/                                                                                |                               | CMOS compatible input level.     CMOS 3-state output structure.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | • Timers 1, 2 pulse output pins                 |  |  |  |  |

| Xcout,<br>P52,P53,P54,                                                                   |                               | <ul> <li>L/O direction register allows each pin to be individually programmed as either input or output.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Sub-clock generating output pin                 |  |  |  |  |

| P55,P56,P57                                                                              |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                 |  |  |  |  |

#### Table 2 Pin description (2)

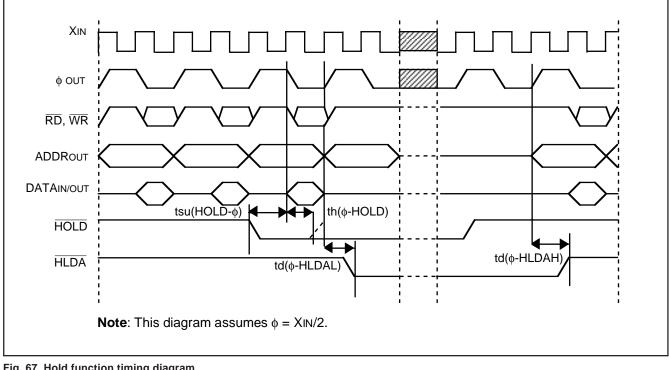

| Pin                                                                                               | Name        | Function                                                                                                                                                                                                                   | Function except a port function |

|---------------------------------------------------------------------------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| P60-P67                                                                                           | I/O port P6 | <ul> <li>8-bit I/O port.</li> <li>CMOS compatible input level.</li> <li>CMOS 3-state output structure.</li> <li>I/O direction register allows each pin to be individually programmed as either input or output.</li> </ul> |                                 |

| P70,<br>P71/HOLD,<br>P72,<br>P73/HLDA,<br>P74                                                     | I/O port P7 | <ul> <li>5-bit I/O port.</li> <li>CMOS compatible input level.</li> <li>CMOS 3-state output structure.</li> <li>I/O direction register allows each pin to be individually programmed as either input or output.</li> </ul> |                                 |

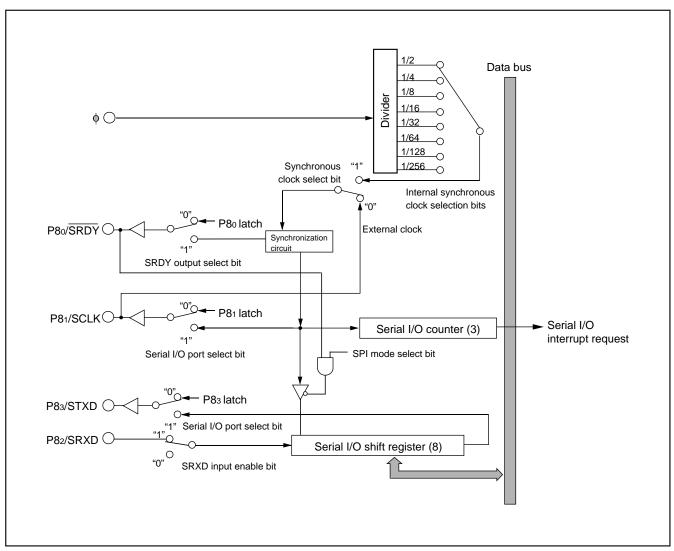

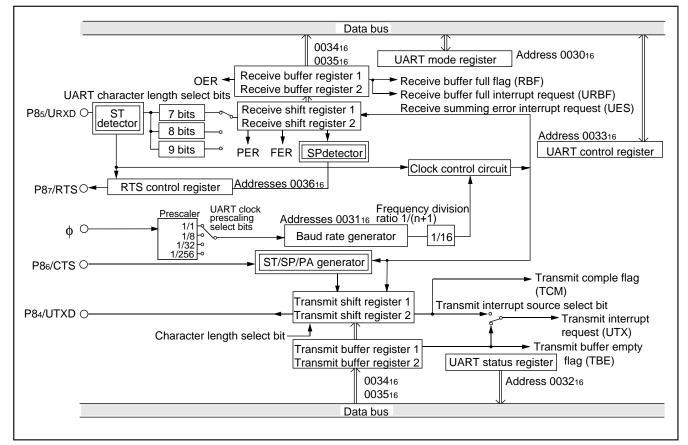

| P80/SRDY,<br>P81/SCLK,<br>P82/SRXD,<br>P83/STXD,<br>P84/UTXD,<br>P85/URXD,<br>P86/CTS,<br>P87/RTS | I/O port P8 | <ul> <li>8-bit I/O port.</li> <li>CMOS compatible input level.</li> <li>CMOS 3-state output structure.</li> <li>I/O direction register allows each pin to be individually programmed as either input or output.</li> </ul> | • Serial I/O pin<br>• UART pin  |

Remarks

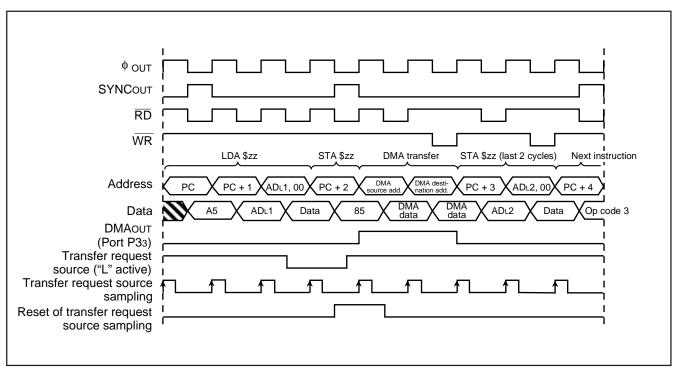

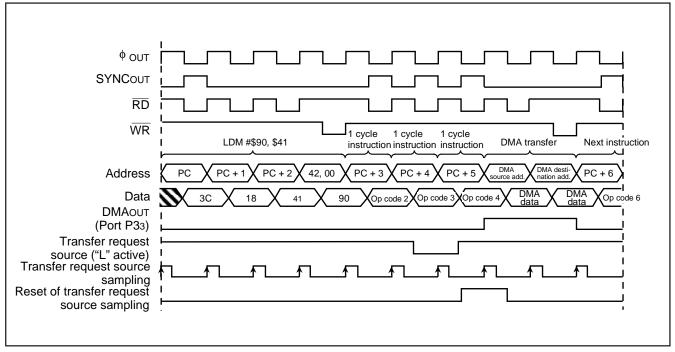

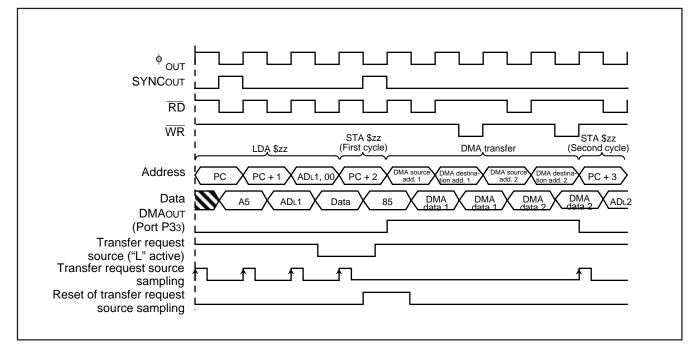

•DMAOUT pin

If externally detecting the timing of DMA execution, use the signal from this pin. It is "H" level during DMA transferring. This signal is valid in the memory expansion and microprocessor modes.

•SYNCout pin

If externally detecting the timing of OP code fetch, use the signal from this pin. This signal is valid in the memory expansion and microprocessor modes.

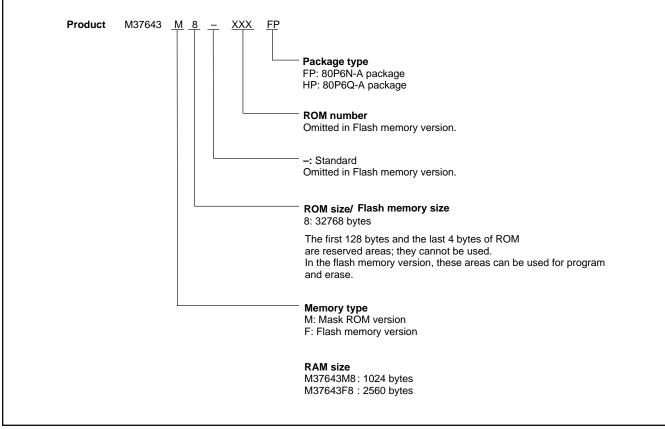

# PART NUMBERING

Fig. 4 Part numbering

# **GROUP EXPANSION**

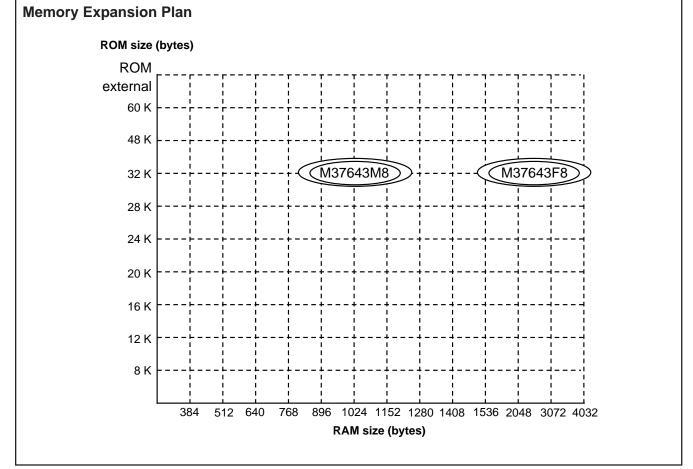

Renesas plans to expand the 7643 group as follows.

# Memory Type

Supports for mask ROM and flash memory versions.

## **Memory Size**

| ROM size | 32 Kbytes          |

|----------|--------------------|

| RAM size | 1024 to 2560 bytes |

#### Fig. 5 Memory expansion plan

Currently planning products are listed below.

#### Table 3 Support products

As of Jan. 2003

| Part number    | ROM size (bytes)<br>ROM size for User in() | RAM size<br>(bytes) | Package | Remarks              |

|----------------|--------------------------------------------|---------------------|---------|----------------------|

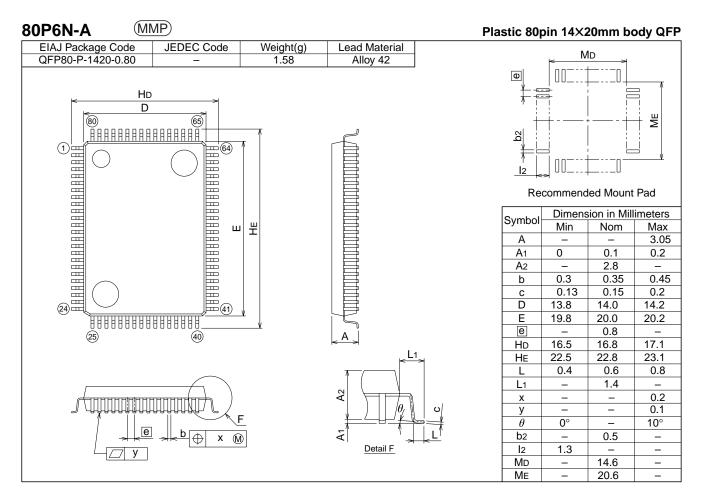

| M37643M8-XXXFP | 32768 (32636)                              | 1024                | 80P6N-A | Mask ROM version     |

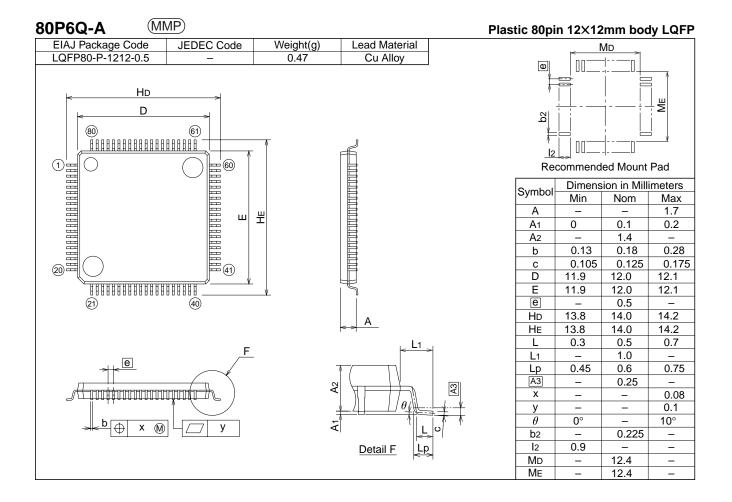

| M37643M8-XXXHP |                                            |                     | 80P6Q-A |                      |

| M37643F8FP     | 32768                                      | 2560                | 80P6N-A | Flash memory version |

| M37643F8HP     |                                            |                     | 80P6Q-A |                      |

# Packages

| 80P6N-A | 0.8 mm-pitch plastic molded QFP  |

|---------|----------------------------------|

| 80P6Q-A | 0.5 mm-pitch plastic molded LQFP |

# FUNCTIONAL DESCRIPTION CENTRAL PROCESSING UNIT (CPU)

The 7643 group uses the standard 7600 series instruction set. Refer to the 7600 Series Software Manual for details on the instruction set. The 7600 series has an upward compatible instruction set, of which instruction execution cycles are shortened, for 740 series.

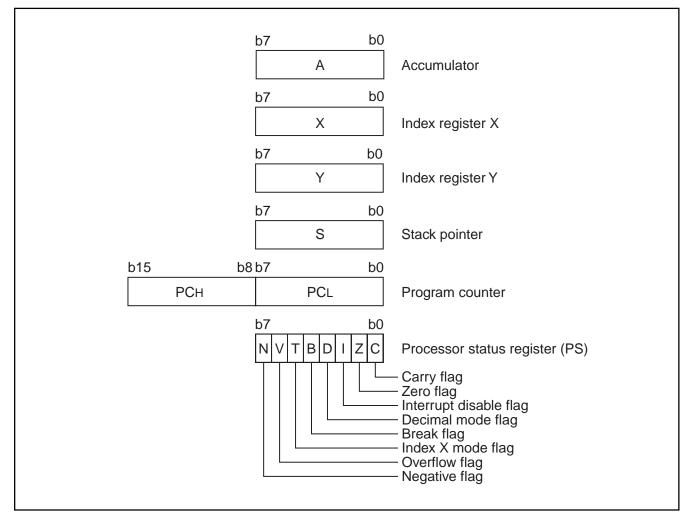

# [Accumulator (A)]

The accumulator is an 8-bit register. Data operations such as data transfer, etc., are executed mainly through the accumulator.

# [Index Register X (X)]

The index register X is an 8-bit register. In the index addressing modes, the value of the OPERAND is added to the contents of register X and specifies the real address.

# [Index Register Y (Y)]

The index register Y is an 8-bit register. In partial instruction, the value of the OPERAND is added to the contents of register Y and specifies the real address.

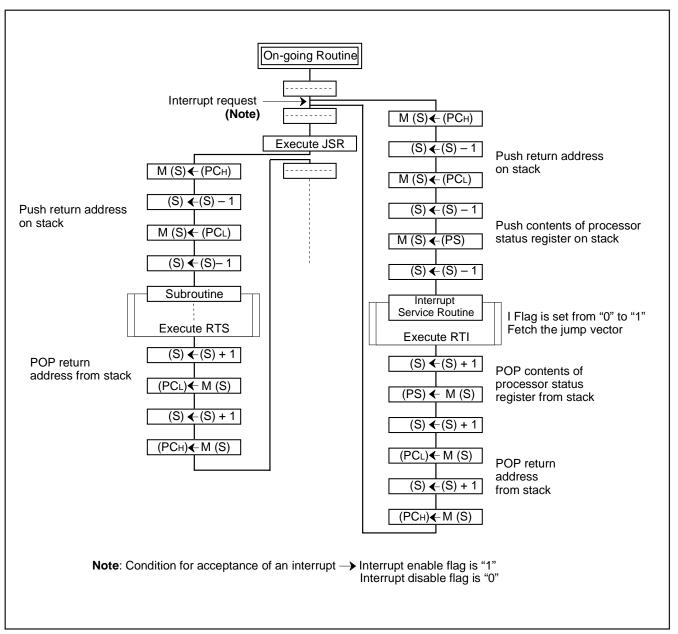

# [Stack Pointer (S)]

The stack pointer is an 8-bit register used during subroutine calls and interrupts. This register indicates start address of stored area (stack) for storing registers during subroutine calls and interrupts. The low-order 8 bits of the stack address are determined by the con-

tents of the stack pointer. The high-order 8 bits of the stack address are determined by the stack page selection bit. If the stack page selection bit is "0", the high-order 8 bits becomes "0016". If the stack page selection bit is "1", the high-order 8 bits becomes "0116". The operations of pushing register contents onto the stack and pop-

ping them from the stack are shown in Figure 7.

Store registers other than those described in Figure 7 with program when the user needs them during interrupts or subroutine calls.

# [Program Counter (PC)]

The program counter is a 16-bit counter consisting of two 8-bit registers PCH and PCL. It is used to indicate the address of the next instruction to be executed.

Fig. 6 7600 series CPU register structure

Fig. 7 Register push and pop at interrupt generation and subroutine call

Table 4 Push and pop instructions of accumulator or processor status register

|                           | Push instruction to stack | Pop instruction from stack |

|---------------------------|---------------------------|----------------------------|

| Accumulator               | PHA                       | PLA                        |

| Processor status register | PHP                       | PLP                        |

# [Processor status register (PS)]

The processor status register is an 8-bit register consisting of 5 flags which indicate the status of the processor after an arithmetic operation and 3 flags which decide MCU operation. Branch operations can be performed by testing the Carry (C) flag, Zero (Z) flag, Overflow (V) flag, or the Negative (N) flag. In decimal mode, the Z, V, N flags are not valid.

#### •Bit 0: Carry flag (C)

The C flag contains a carry or borrow generated by the arithmetic logic unit (ALU) immediately after an arithmetic operation. It can also be changed by a shift or rotate instruction.

#### •Bit 1: Zero flag (Z)

The Z flag is set if the result of an immediate arithmetic operation or a data transfer is "0", and cleared if the result is anything other than "0".

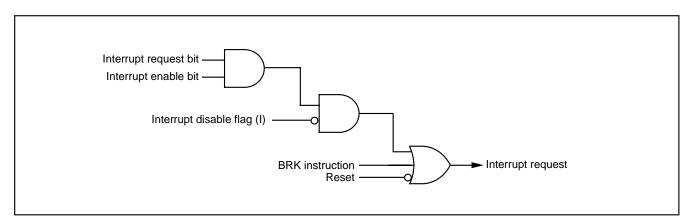

#### •Bit 2: Interrupt disable flag (I)

The I flag disables all interrupts except for the interrupt generated by the BRK instruction.

Interrupts are disabled when the I flag is "1".

#### •Bit 3: Decimal mode flag (D)

The D flag determines whether additions and subtractions are executed in binary or decimal. Binary arithmetic is executed when this flag is "0"; decimal arithmetic is executed when it is "1". Decimal correction is automatic in decimal mode. Only the ADC and SBC instructions can execute decimal arithmetic.

#### •Bit 4: Break flag (B)

The B flag is used to indicate that the current interrupt was generated by the BRK instruction. The BRK flag in the processor status register is always "0". When the BRK instruction is used to generate an interrupt, the processor status register is pushed onto the stack with the break flag set to "1".

#### •Bit 5: Index X mode flag (T)

When the T flag is "0", arithmetic operations are performed between accumulator and memory. When the T flag is "1", direct arithmetic operations and direct data transfers are enabled between memory locations.

#### •Bit 6: Overflow flag (V)

The V flag is used during the addition or subtraction of one byte of signed data. It is set if the result exceeds +127 to -128. When the BIT instruction is executed, bit 6 of the memory location operated on by the BIT instruction is stored in the overflow flag. it 7: Negative flag (N)

#### •Bit 7: Negative flag (N)

The N flag is set if the result of an arithmetic operation or data transfer is negative. When the BIT instruction is executed, bit 7 of the memory location operated on by the BIT instruction is stored in the negative flag.

#### Table 5 Set and clear instructions of each bit of processor status register

|                   | C flag | Z flag | I flag | D flag | B flag | T flag | V flag | N flag |

|-------------------|--------|--------|--------|--------|--------|--------|--------|--------|

| Set instruction   | SEC    | -      | SEI    | SED    | -      | SET    | -      | -      |

| Clear instruction | CLC    | -      | CLI    | CLD    | -      | CLT    | CLV    | _      |

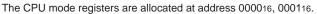

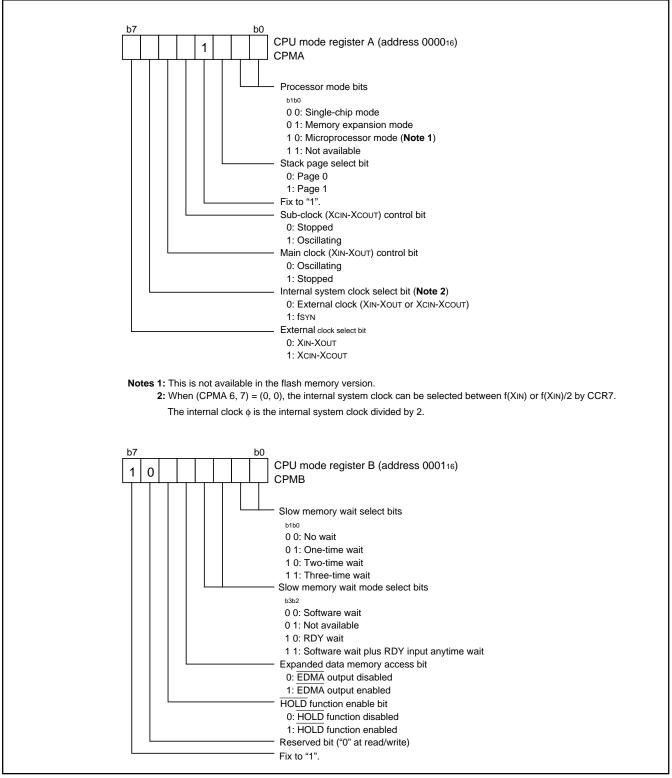

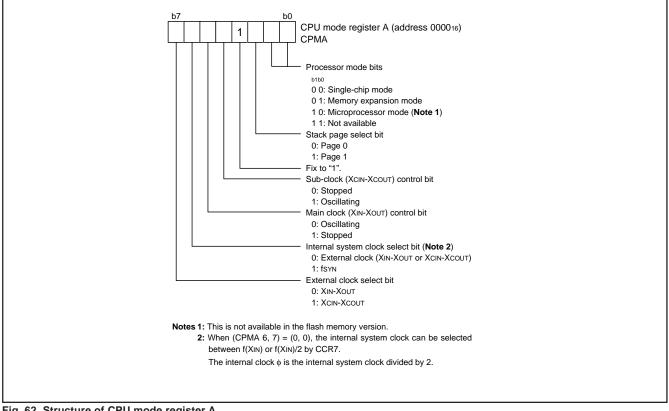

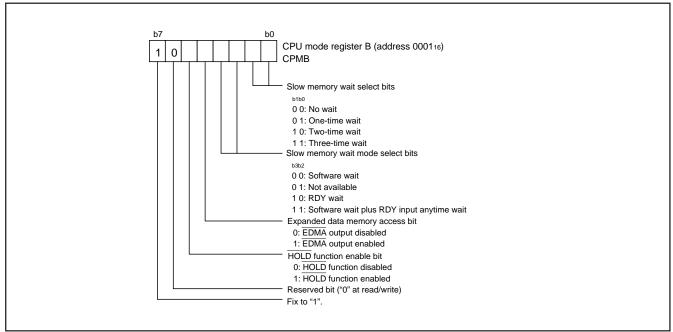

[CPU Mode Registers A, B (CPUMA, CPUMB)] 000016, 000116 The CPU mode register contains the stack page select bit and the CPU operating mode select bit and so on. Notes

Do not use the microprocessor mode in the flash memory version.

Fig. 8 Structure of CPU mode register

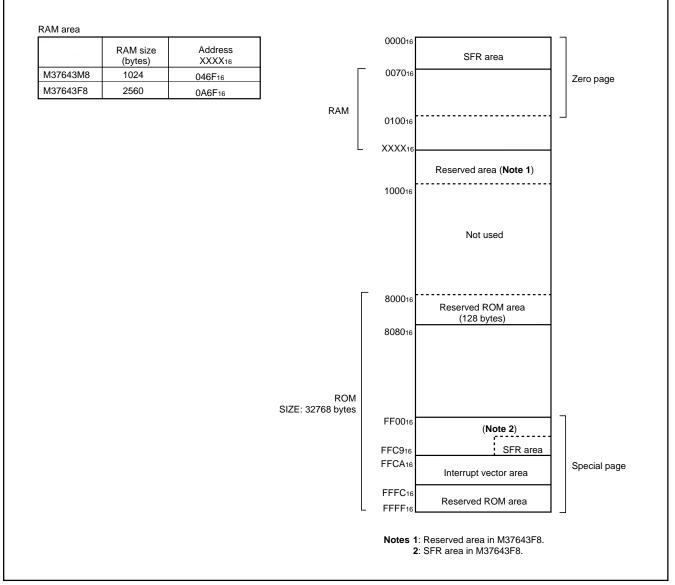

# MEMORY

# Special Function Register (SFR) Area

The Special Function Register area in the zero page contains control registers such as I/O ports and timers.

# RAM

RAM is used for data storage and for stack area of subroutine calls and interrupts.

# ROM

The first 128 bytes and the last 4 bytes of ROM are reserved for device testing and the rest is user area for storing programs. In the flash memory version, program and erase can be performed in the reserved area.

#### **Interrupt Vector Area**

The interrupt vector area contains reset and interrupt vectors.

#### Zero Page

Access to this area with only 2 bytes is possible in the zero page addressing mode.

# **Special Page**

Access to this area with only 2 bytes is possible in the special page addressing mode.

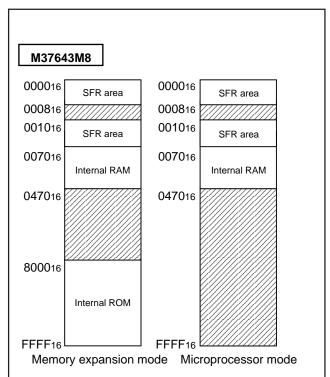

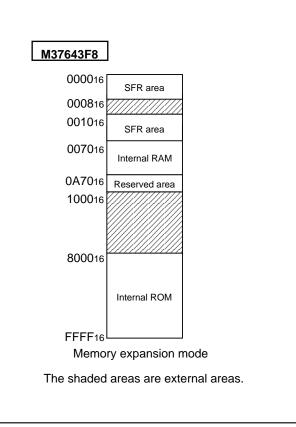

Refer to page 74 for the memory map of memory expansion and microprocessor modes.

Fig. 9 Memory map diagram

| 00016 CPU mode register A (CPUA)                                  | 003816 Reserved (Note 1)                                             |

|-------------------------------------------------------------------|----------------------------------------------------------------------|

| 00116 CPU mode register B (CPUB)                                  | 003916 Reserved (Note 1)                                             |

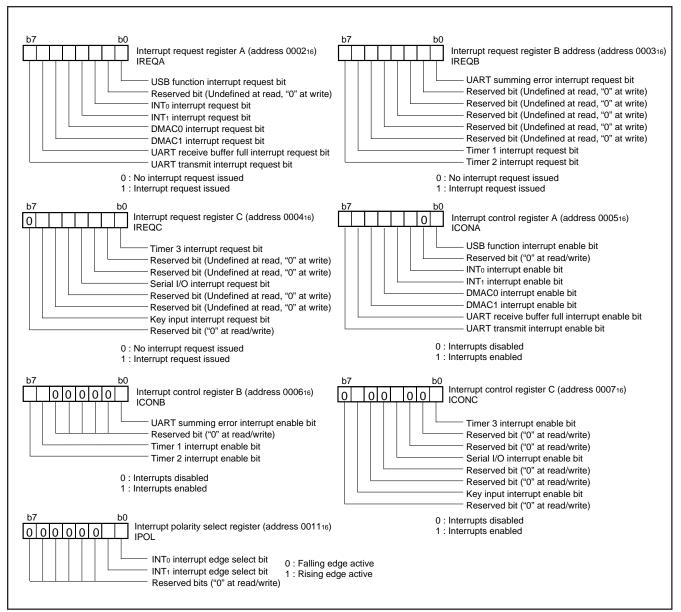

| 00216 Interrupt request register A (IREQA)                        | 003A16 Reserved (Note 1)                                             |

| 00316 Interrupt request register B (IREQB)                        | 003B16 Reserved (Note 1)                                             |

| 00316 Interrupt request register C (IREQC)                        | 003C16 Reserved (Note 1)                                             |

| 00516 Interrupt control register A (ICONA)                        | 003D16 Reserved (Note 1)                                             |

|                                                                   |                                                                      |

| 006 <sub>16</sub> Interrupt control register B (ICONB)            | 003E16 Reserved (Note 1)                                             |

| 007 <sub>16</sub> Interrupt control register C (ICONC)            | 003F16 DMAC index and status register (DMAIS)                        |

| 00816 Port P0 (P0)                                                | 004016 DMAC channel x mode register 1 (DMAx1)                        |

| 00916 Port P0 direction register (P0D)                            | 004116 DMAC channel x mode register 2 (DMAx2)                        |

| 00A <sub>16</sub> Port P1 (P1)                                    | 004216 DMAC channel x source register Low (DMAxSL)                   |

| 00B <sub>16</sub> Port P1 direction register (P1D)                | 004316 DMAC channel x source register High (DMAxSH)                  |

| 00C16 Port P2 (P2)                                                | 004416 DMAC channel x destination register Low (DMAxDL)              |

| 00D <sub>16</sub> Port P2 direction register (P2D)                | 0045 <sub>16</sub> DMAC channel x destination register High (DMAxDH) |

| 00E16 Port P3 (P3)                                                | 004616 DMAC channel x transfer count register Low (DMAxCL)           |

| 00F16 Port P3 direction register (P3D)                            | 004716 DMAC channel x transfer count register High (DMAxCH)          |

| 010 <sub>16</sub> Port control register (PTC)                     | 004816 Reserved (Note 1)                                             |

| 011 <sub>16</sub> Interrupt polarity select register (IPOL)       | 004916 Reserved ( <b>Note 1</b> )                                    |

| 012 <sub>16</sub> Port P2 pull-up control register (PUP2)         | 004A <sub>16</sub> Reserved ( <b>Note 1</b> )                        |

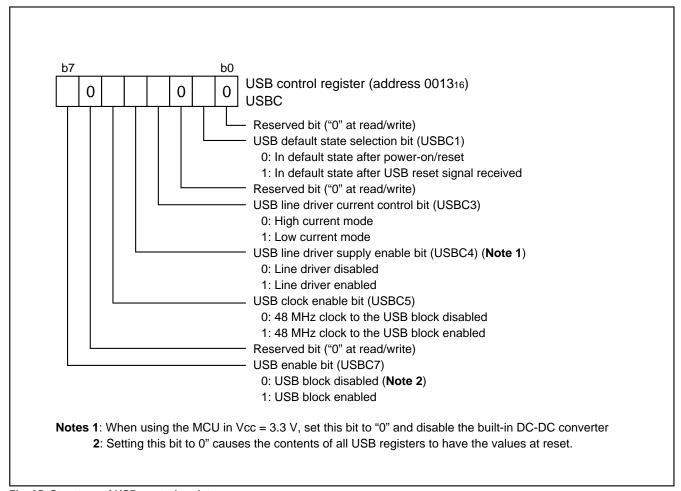

| 013 <sub>16</sub> USB control register (USBC)                     | 004B <sub>16</sub> Reserved ( <b>Note 1</b> )                        |

| 014 <sub>16</sub> Port P6 (P6)                                    | 004C <sub>16</sub> Reserved ( <b>Note 1</b> )                        |

| 015 <sub>16</sub> Port P6 direction register (P6D)                | 004D <sub>16</sub> Reserved ( <b>Note 1</b> )                        |

| 016 <sub>16</sub> Port P5 (P5)                                    | 004E <sub>16</sub> Reserved (Note 1)                                 |

| 017 <sub>16</sub> Port P5 direction register (P5D)                | 004F <sub>16</sub> Reserved (Note 1)                                 |

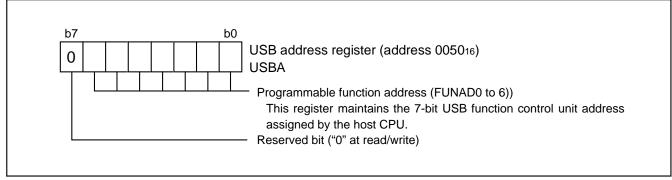

| 018 <sub>16</sub> Port P4 (P4)                                    | 005016 USB address register (USBA)                                   |

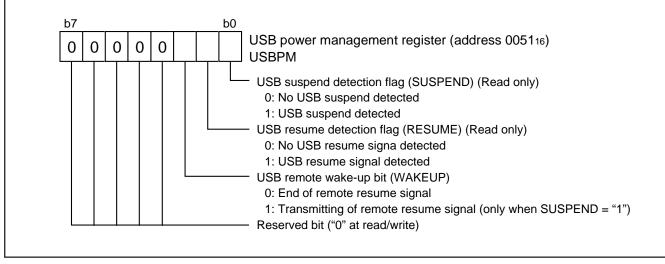

| 019 <sub>16</sub> Port P4 direction register (P4D)                | 005116 USB power management register (USBPM)                         |

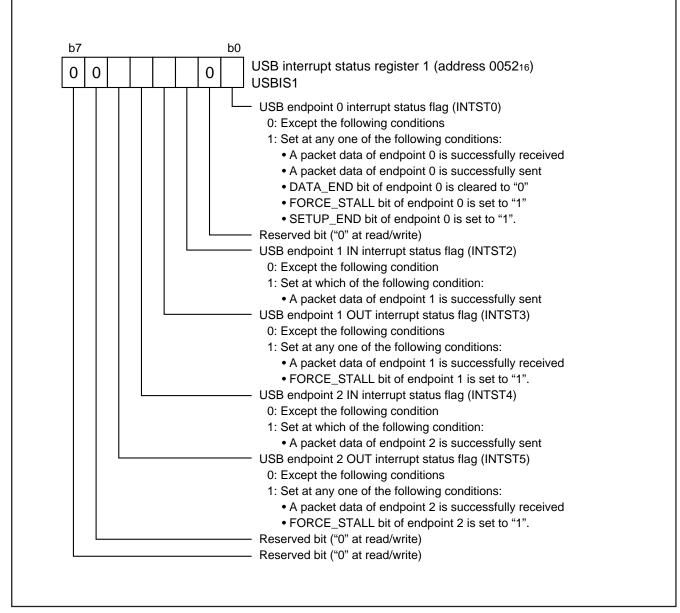

| 01A <sub>16</sub> Port P7 (P7)                                    | 005216 USB interrupt status register 1 (USBIS1)                      |

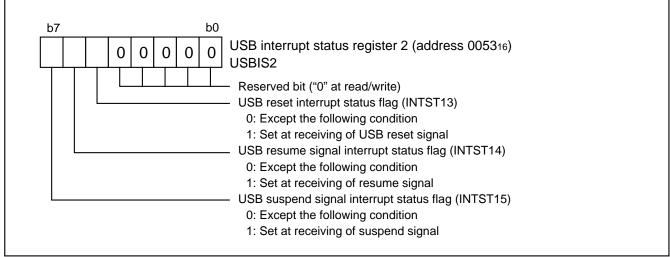

| 01B <sub>16</sub> Port P7 direction register (P7D)                | 005316 USB interrupt status register 2 (USBIS2)                      |

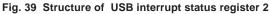

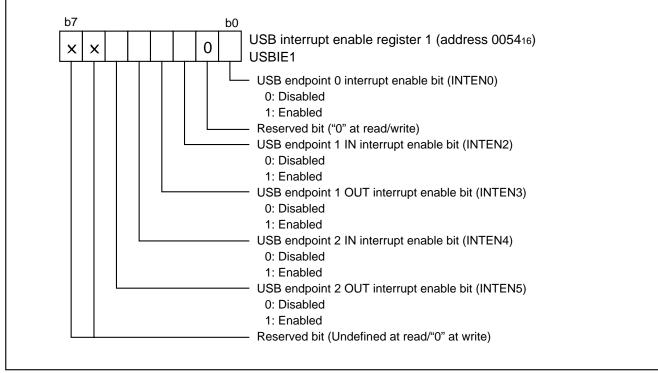

| 01C <sub>16</sub> Port P8 (P8)                                    | 005416 USB interrupt enable register 1 (USBIE1)                      |

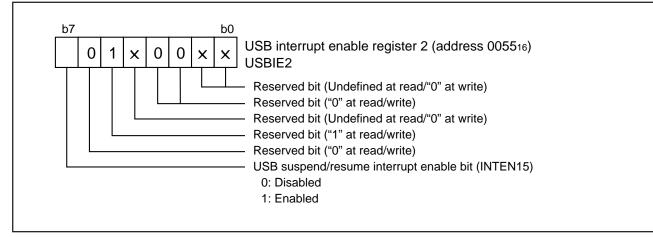

| 01D <sub>16</sub> Port P8 direction register (P8D)                | 005516 USB interrupt enable register 2 (USBIE2)                      |

| $01E_{16} \text{ Reserved (Note 1)}$                              | 005616 Reserved ( <b>Note 1</b> )                                    |

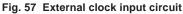

| 01F <sub>16</sub> Clock control register (CCR)                    | 0057 <sub>16</sub> Reserved ( <b>Note 1</b> )                        |

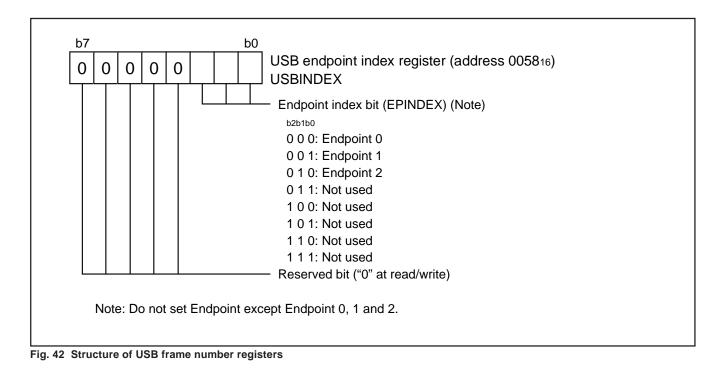

| 020 <sub>16</sub> Reserved ( <b>Note 1</b> )                      | 005816 USB endpoint index register (USBINDEX)                        |

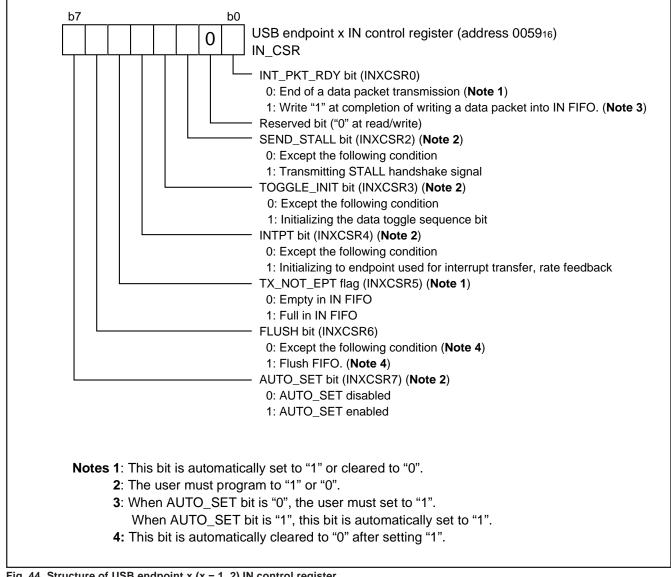

| 021 <sub>16</sub> Reserved ( <b>Note 1</b> )                      | 005916 USB endpoint x IN control register (IN_CSR)                   |

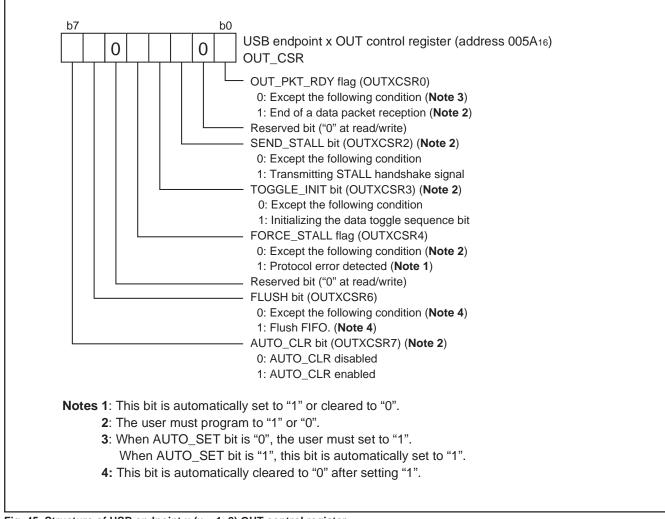

| 0216 Reserved ( <b>Note 1</b> )                                   | 005A <sub>16</sub> USB endpoint x IN control register (INCOR)        |

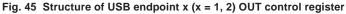

| 02216 Reserved (Note 1)<br>02316 Reserved (Note 1)                | 005B16 USB endpoint x IN max. packet size register (IN_MAXP)         |

| 02316 Timer 1 (T1)                                                |                                                                      |

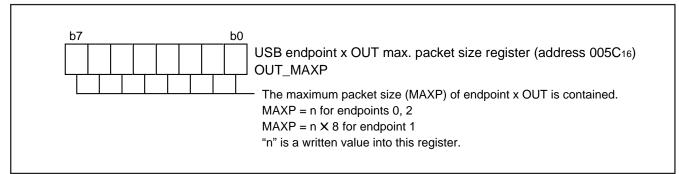

| 02416 Timer 2 (T2)                                                | 005C16 USB endpoint x OUT max. packet size register (OUT_MAXP)       |

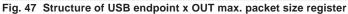

| 02516 Timer 3 (T3)                                                | 005D16 USB endpoint x OUT write count register (WRT_CNT)             |

| 02616 Inner 3 (13)<br>02716 Reserved ( <b>Note 1</b> )            | 005E16 Reserved (Note 1)                                             |

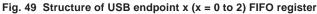

|                                                                   | 005F16 USB endpoint FIFO mode register (USBFIFOMR)                   |

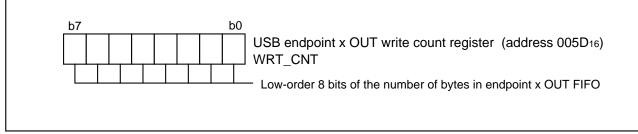

| 028 <sub>16</sub> Reserved (Note 1)                               | 006016 USB endpoint 0 FIFO (USBFIFO0)                                |

| 029 <sub>16</sub> Timer 123 mode register (T123M)                 | 006116 USB endpoint 1 FIFO (USBFIFO1)                                |

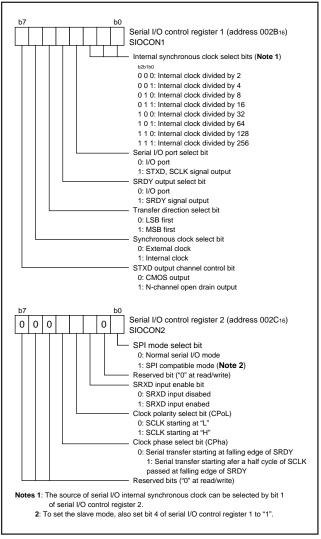

| 02A <sub>16</sub> Serial I/O shift register (SIOSHT)              | 006216 USB endpoint 2 FIFO (USBFIFO2)                                |

| 02B <sub>16</sub> Serial I/O control register 1 (SIOCON1)         | 0063 <sub>16</sub> Reserved (Note 1)                                 |

| 02C16 Serial I/O control register 2 (SIOCON2)                     | 006416 Reserved (Note 1)                                             |

| D2D <sub>16</sub> Reserved ( <b>Note 1</b> )                      | 006516 Reserved ( <b>Note 1</b> )                                    |

| 02E <sub>16</sub> Reserved (Note 1)                               | 006616 Reserved (Note 1)                                             |

| 02F <sub>16</sub> Reserved ( <b>Note 1</b> )                      | 0067 <sub>16</sub> Reserved ( <b>Note 1</b> )                        |

| 03016 UART mode register (UMOD)                                   | 0068 <sub>16</sub> Reserved ( <b>Note 1</b> )                        |

| 031 <sub>16</sub> UART baud rate generator (UBRG)                 | 0069 <sub>16</sub> Reserved ( <b>Note 1</b> )                        |

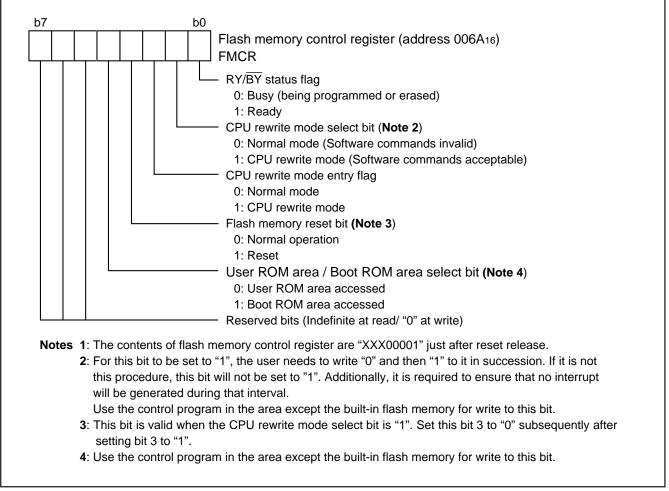

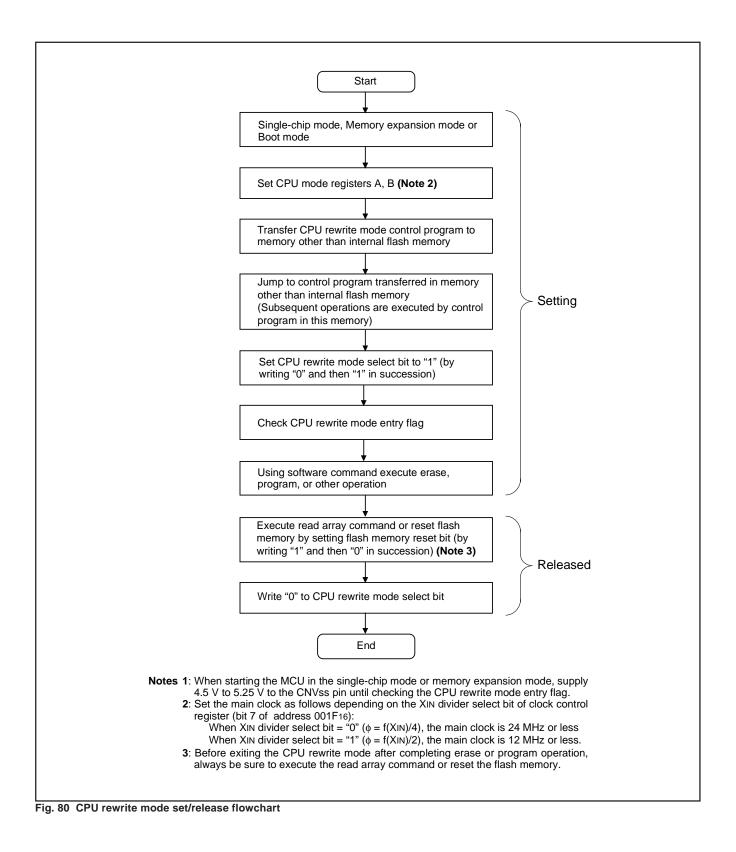

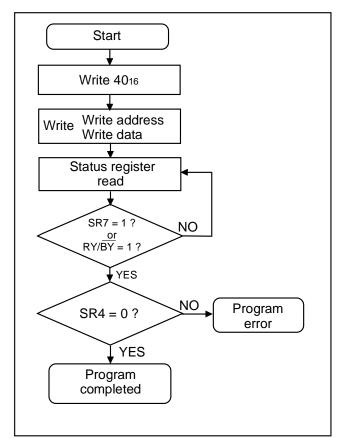

| 03216 UART status register (USTS)                                 | 006A <sub>16</sub> Flash memory control register (FMCR) (Note 2)     |

| 03316 UART control register (UCON)                                | 006B <sub>16</sub> Reserved ( <b>Note 1</b> )                        |

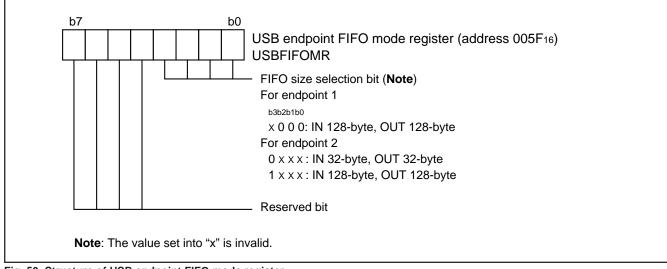

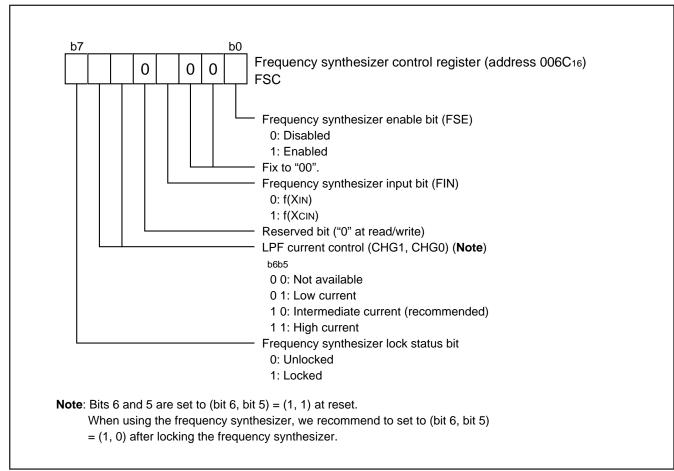

| 034 <sub>16</sub> UART transmit/receive buffer register 1 (UTRB1) | 006C16 Frequency synthesizer control register (FSC)                  |

| 035 <sub>16</sub> UART transmit/receive buffer register 2 (UTRB2) | 006D <sub>16</sub> Frequency synthesizer multiply register 1 (FSM1)  |

| 03616 UART RTS control register (URTSC)                           | 006E <sub>16</sub> Frequency synthesizer multiply register 2 (FSM2)  |

| 037 <sub>16</sub> Reserved ( <b>Note 1</b> )                      | 006F16 Frequency synthesizer divide register (FSD)                   |

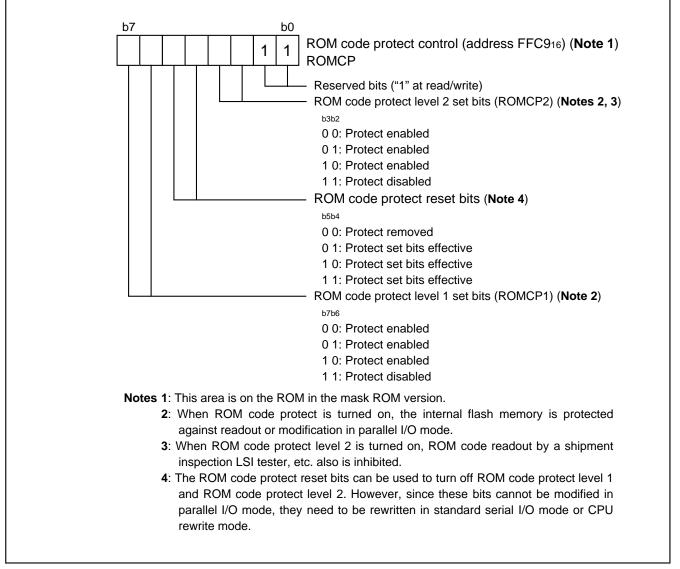

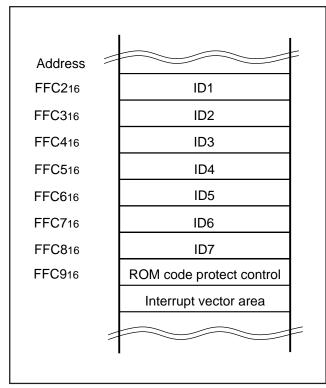

FFC916 ROM code protect control register (ROMCP) (Note 3)

Notes 1: Do not write any data to this addresses, because these areas are reserved.

2: This area is reserved in the mask ROM version.

3: This area is on the ROM in the mask ROM version.

Fig. 10 Memory map of special function register (SFR)

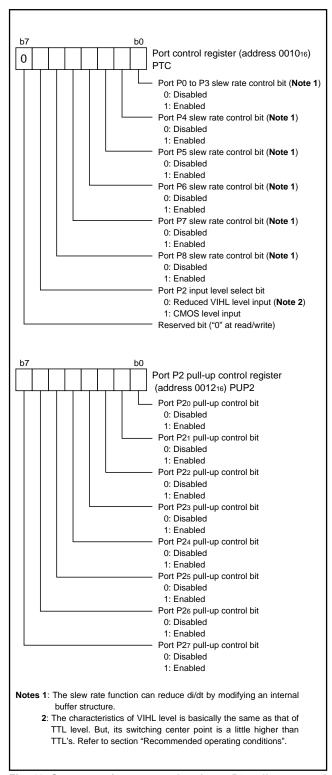

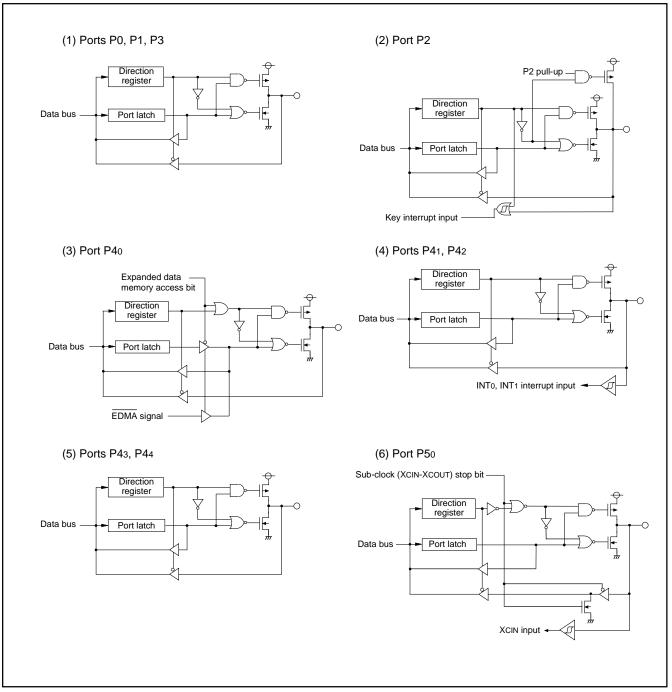

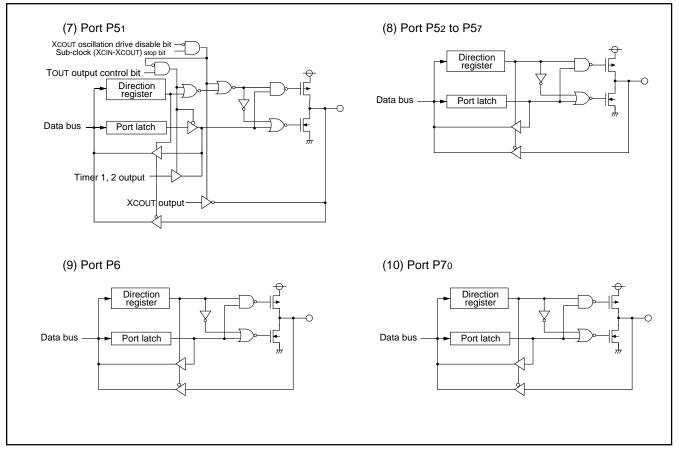

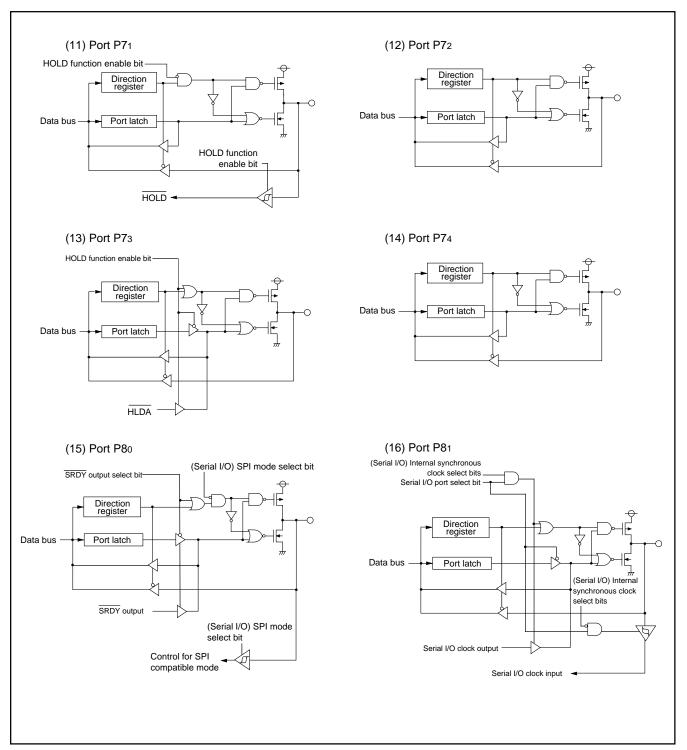

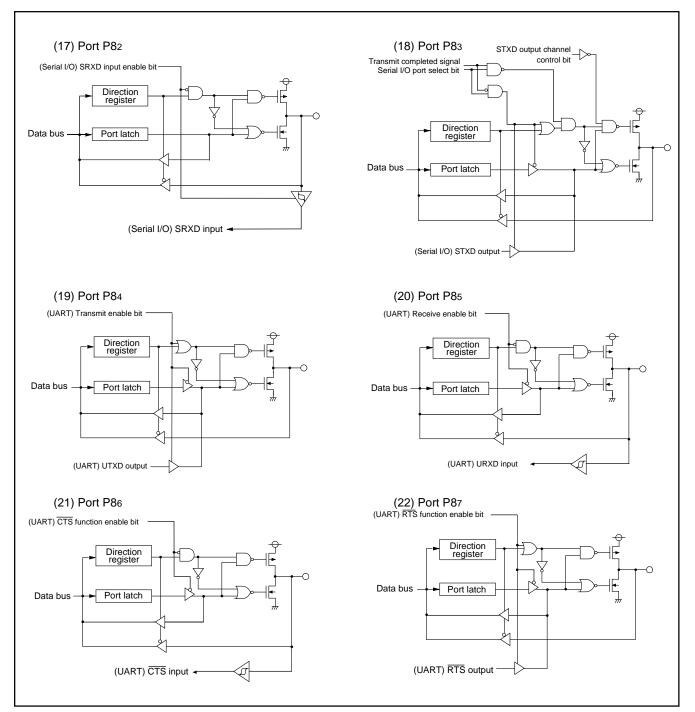

# I/O PORTS

# **Direction Registers**

The I/O ports P0–P8 have direction registers which determine the input/output direction of each individual pin. Each bit in a direction register corresponds to one pin, each pin can be set to be input port or output port.

When "0" is written to the bit corresponding to a pin, that pin becomes an input pin. When "1" is written to that bit, that pin becomes an output pin.

If data is read from a pin set to output, the value of the port output latch is read, not the value of the pin itself. Pins set to input are floating. If a pin set to input is written to, only the port output latch is written to and the pin remains floating.

#### **Slew Rate Control**

By setting bits 0 to 5 of the port control register (address 001016) to "1", slew rate control is enabled. VIHL or CMOS level can be used as a port P2 input level.

# **Pull-up Control**

By setting the port P2 pull-up control register (address 001216), pullup of each pin of port P2 can be controlled with a program. However, the contents of port P2 pull-up control register do not affect ports programmed as the output ports but as the input ports.

Fig. 11 Structure of port control and port P2 pull-up control registers

#### Table 6 List of I/O port function

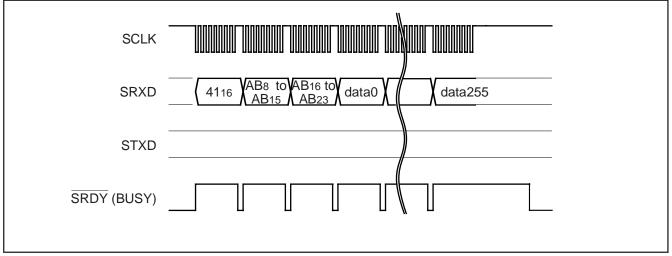

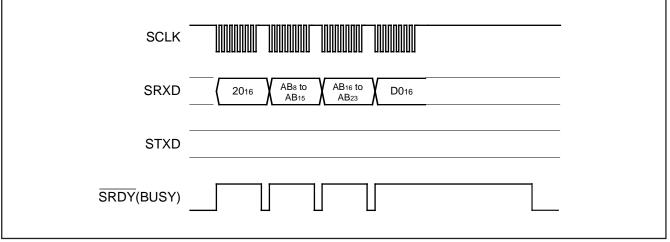

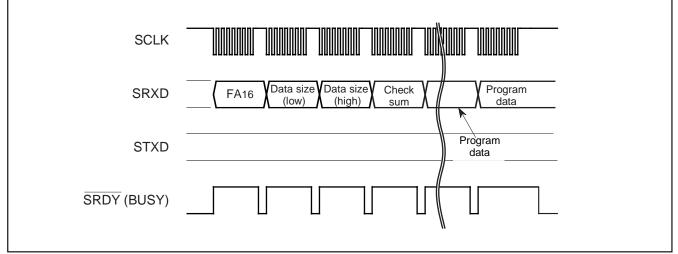

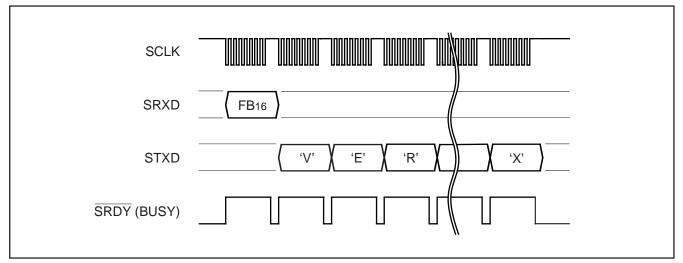

| Port P0 |                                                     |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |