**16-BIT CMOS MICROCOMPUTER**

#### DESCRIPTION

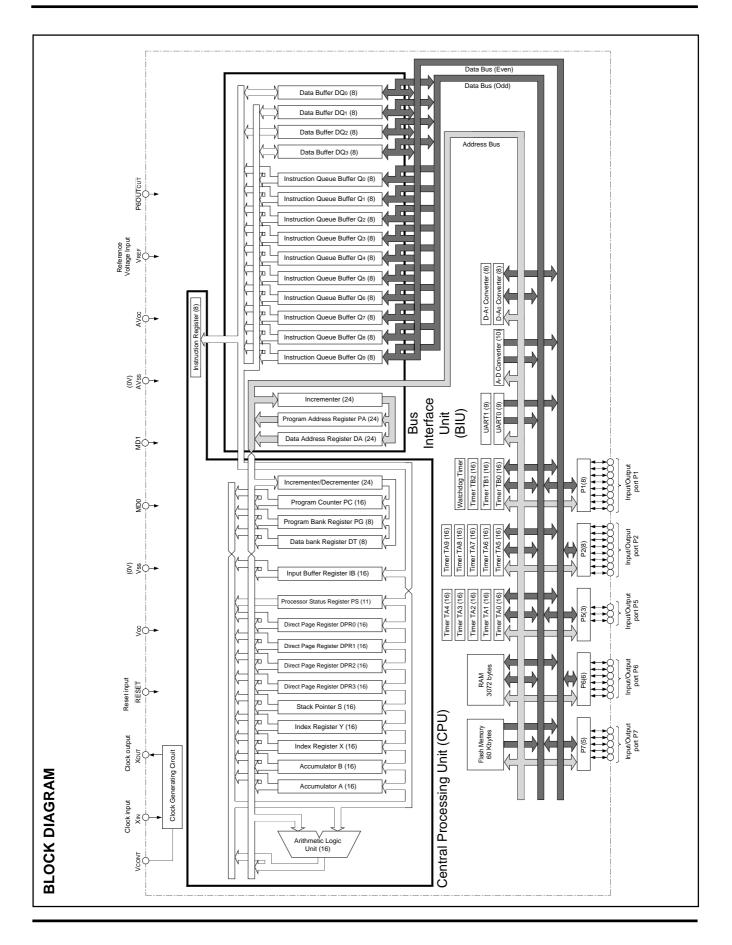

These are single-chip 16-bit microcomputers designed with high-performance CMOS silicon gate technology, including the internal flash memory and being packaged in 42-pin plastic molded SSOP or shrink plastic molded DIP. These microcomputers support the 7900 Series instruction set, which are enhanced and expanded instruction set and are upper-compatible with the 7700/7751 Series instruction set.

The CPU of these microcomputers is a 16-bit parallel processor that can also be switched to perform 8-bit parallel processing. Also, the bus interface unit of these microcomputers enhances the memory access efficiency to execute instructions fast. Therefore, these microcomputers are suitable for office, business, and industrial equipment controller that require high-speed processing of large data.

Also, they are suitable for motor-control equipment since each of them includes the motor control circuit.

For the internal flash memory, single-power-supply programming and erasure, using a PROM programmer or the control by the central processing unit (CPU), is supported. Also, each of these microcomputers has the memory area dedicated for storing a certain software which controls programming and erasure (reprogramming control software). Therefore, on these microcomputers, the program can easily be changed even after they are mounted on the board.

## DISTINCTIVE FEATURES

<Microcomputer mode>

| Number of basic machine instructions                            |

|-----------------------------------------------------------------|

| Memory                                                          |

| Flash memory (User ROM area) 60 Kbytes                          |

| RAM                                                             |

| Flash memory (Boot ROM area) 8 Kbytes                           |

| <ul> <li>Instruction execution time</li> </ul>                  |

| The fastest instruction at 20 MHz frequency 50 ns               |

| • Single power supply                                           |

| • Interrupts                                                    |

| Multi-functional 16-bit timer 10 + 3                            |

| (Three-phase motor drive waveform or Pulse motor drive waveform |

| output is available.)                                           |

| • Serial I/O (UART or Clock synchronous) 2                      |

| • 10-bit A-D converter 5-channel inputs                         |

| • 8-bit D-A converter2-channel outputs                          |

| <ul> <li>12-bit watchdog timer</li> </ul>                       |

| • Description of the stand (and a D1 D2 D5 D2 D7)               |

• Programmable input/output (ports P1, P2, P5, P6, P7) ...... 30

<Flash memory mode>

- Power supply voltage ...... 5 V ± 0.5 V

- Programming/Erase voltage ...... 5 V ± 0.5 V

- Programming method ..... Programming in a unit of word

- Erase method ......Block erase or Total erase M37906F8CFP, M37906F8CSP

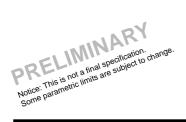

- ...... 4 blocks (8 Kbytes X 2, 16 Kbytes X 1, 28 Kbytes X 1)

- Programming/Erase control by software command

- Maximum number of reprograms ...... 100

### APPLICATION

- Control devices for office equipment such as copiers and facsimiles

- Control devices for industrial equipment such as communication and measuring instruments

- Control devices for equipment, requiring motor control, such as inverter air conditioners and general-purpose inverters

16-BIT CMOS MICROCOMPUTER

## **FUNCTIONS (Microcomputer mode)**

| -                              |                                |                                                                                                                            |  |  |  |

|--------------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                | Parameter                      | Functions                                                                                                                  |  |  |  |

| Number of basic machine inst   | ructions                       | 203                                                                                                                        |  |  |  |

| Instruction execution time     |                                | 50 ns (the fastest instruction at f(fsys) = 20 MHz)                                                                        |  |  |  |

| External clock input frequency | f(XIN)                         | 20 MHz (Max.)                                                                                                              |  |  |  |

| System clock input frequency   | f(fsys)                        | 20 MHz (Max.)                                                                                                              |  |  |  |

| Memory size                    | Flash memory (User ROM area)   | 60 Kbytes                                                                                                                  |  |  |  |

|                                | RAM                            | 3072 bytes                                                                                                                 |  |  |  |

|                                | Flash memory (Boot ROM area)   | 8 Kbytes                                                                                                                   |  |  |  |

| Programmable input/output      | P1, P2                         | 8-bit × 2                                                                                                                  |  |  |  |

| ports                          | P5                             | 3-bit × 1                                                                                                                  |  |  |  |

|                                | P6                             | 6-bit X 1                                                                                                                  |  |  |  |

|                                | P7                             | 5-bit X 1                                                                                                                  |  |  |  |

| Multi-functional timers        | ТАО-ТА9                        | 16-bit × 10                                                                                                                |  |  |  |

|                                | ТВ0-ТВ2                        | 16-bit X 3                                                                                                                 |  |  |  |

| Serial I/O UART0 and UART1     |                                | (UART or Clock synchronous serial I/O) X 2                                                                                 |  |  |  |

| A-D converter                  |                                | 10-bit successive approximation method X 1 (5 channels)                                                                    |  |  |  |

| D-A converter                  |                                | 8-bit X 2                                                                                                                  |  |  |  |

| Dead-time timer                |                                | 8-bit X 3                                                                                                                  |  |  |  |

| Watchdog timer                 |                                | 12-bit X 1                                                                                                                 |  |  |  |

| Interrupts Maskable interrups  |                                | 5 external sources, 18 internal sources. Each interrupt can be se to a priority level within the range of 0–7 by software. |  |  |  |

|                                | Non-maskable interrups         | 3 internal sources                                                                                                         |  |  |  |

| Clock generating circuit       |                                | Incorporated (externally connected to a ceramic resonator or<br>quartz-crystal resonator).                                 |  |  |  |

| PLL frequency multiplier       |                                | The following multiplication ratios are available: $\times$ 2, $\times$ 3, $\times$ 4                                      |  |  |  |

| Power supply voltage           |                                | 5 V±0.5 V                                                                                                                  |  |  |  |

| Power dissipation              |                                | 125 mW (at f(fsys) = 20 MHz, Typ.; the PLL frequency multiplier is inactive.)                                              |  |  |  |

| Ports' input/output            | Input/Output withstand voltage | 5 V                                                                                                                        |  |  |  |

| characteristics Output current |                                | 5 mA                                                                                                                       |  |  |  |

| Memory expansion               |                                | Not available (single-chip mode only).                                                                                     |  |  |  |

| Operating ambient temperatur   | e range                        | -20 to 85 °C                                                                                                               |  |  |  |

| Device structure               |                                | CMOS high-performance silicon gate process                                                                                 |  |  |  |

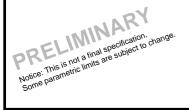

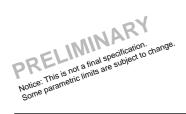

| Package                        |                                | (Note)                                                                                                                     |  |  |  |

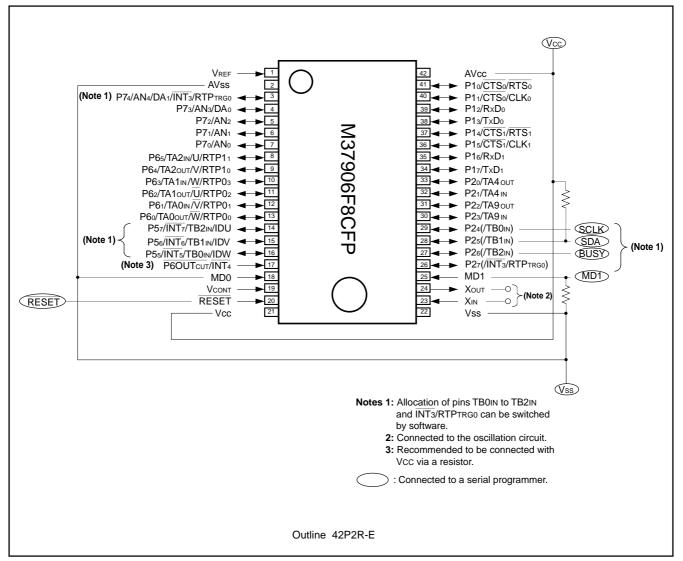

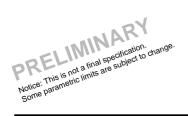

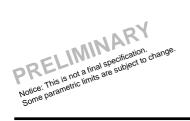

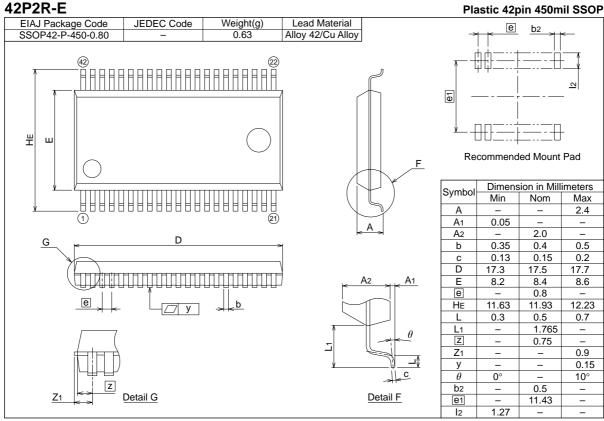

| Note: | Packages M37906F8CFP |             | 42-pin plastic molded SSOP (42P2R-E)     |  |  |

|-------|----------------------|-------------|------------------------------------------|--|--|

|       |                      | M37906F8CSP | 42-pin shrink plastic molded DIP (42P4B) |  |  |

**16-BIT CMOS MICROCOMPUTER**

## FUNCTIONS (Flash memory mode)

|                                     | Parameter                           | Functions                                                                    |  |  |

|-------------------------------------|-------------------------------------|------------------------------------------------------------------------------|--|--|

| Power supply voltage                |                                     | 5 V±0.5 V                                                                    |  |  |

| Programming/Erase voltage           |                                     | 5 V±0.5 V                                                                    |  |  |

| Flash memory mode                   |                                     | 3 modes: parallel I/O, serial I/O, and CPU reprogramming modes               |  |  |

| Block division for erasure          | User ROM area                       | 4 blocks (8 Kbytes X 2, 16 Kbytes X 1, 28 Kbytes X 1); total of<br>60 Kbytes |  |  |

|                                     | Boot ROM area                       | 1 block (8 Kbytes X 1) (Note)                                                |  |  |

| Programming method                  |                                     | Programmed per word                                                          |  |  |

|                                     | Flash memory parallel I/O mode      | User ROM area + Boot ROM area                                                |  |  |

|                                     | Flash memory serial I/O mode        | User ROM area                                                                |  |  |

| Flash memory CPU reprogramming mode |                                     | User ROM area                                                                |  |  |

| Erase method                        |                                     | Total erase/Block erase                                                      |  |  |

|                                     | Flash memory parallel I/O mode      | User ROM area + Boot ROM area                                                |  |  |

|                                     | Flash memory serial I/O mode        | User ROM area                                                                |  |  |

|                                     | Flash memory CPU reprogramming mode | User ROM area                                                                |  |  |

| Programming/Erase control           |                                     | Programming/Erase control by software commands                               |  |  |

| Number of commands                  |                                     | 6 commands                                                                   |  |  |

| Maximum number of reprograms        |                                     | 100                                                                          |  |  |

Note: On shipment, our reprogramming control firmware for the flash memory serial I/O mode has been stored into the boot ROM area.

16-BIT CMOS MICROCOMPUTER

### PIN DESCRIPTION (MICROCOMPUTER MODE)

| Pin           | Name                      | Input/<br>Output | Functions                                                                                                                                                                                                                                                                                                    |  |

|---------------|---------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Vcc, Vss      | Power supply input        | —                | Apply 5 V±0.5 V to Vcc, and 0 V to Vss.                                                                                                                                                                                                                                                                      |  |

| MD0           | MD0                       | Input            | Connect this pin to Vss.                                                                                                                                                                                                                                                                                     |  |

| MD1           | MD1                       | Input            | Connect this pin to Vss.                                                                                                                                                                                                                                                                                     |  |

| RESET         | Reset input               | Input            | The microcomputer is reset when "L" level is applied to this pin.                                                                                                                                                                                                                                            |  |

| XIN           | Clock input               | Input            | These are input and output pins of the internal clock generating circuit. Connect a                                                                                                                                                                                                                          |  |

| Хоит          | Clock output              | Output           | ceramic or quartz-crystal oscillator between the XIN and XOUT pins. When an external clock is used, the clock source should be connected to the XIN pin, and the XOUT pin should be left open.                                                                                                               |  |

| VCONT         | Filter circuit connection | —                | When using the PLL frequency multiplier, connect this pin to the filter circuit. When not using the PLL frequency multiplier, this pin should be left open.                                                                                                                                                  |  |

| AVcc,<br>AVss | Analog power supply input | —                | Power supply input pins for the A-D converter and the D-A converter. Connect AVcc to Vcc, and AVss to Vss externally.                                                                                                                                                                                        |  |

| Vref          | Reference voltage input   | Input            | This is the reference voltage input pin for the A-D converter and the D-A converter.                                                                                                                                                                                                                         |  |

| P10-P17       | I/O port P1               | I/O              | Port P1 is an 8-bit I/O port. This port has an I/O direction register, and each pin can be programmed for input or output. These pins enter the input mode at reset. These pins also function as I/O port pins of UART0 and UART1.                                                                           |  |

| P20-P27       | I/O port P2               | I/O              | In addition to having the same functions as port P1, these pins also function as I/O pins for timers A4 and A9. By software setting, these pins also function as input pins for timers B0–B2, an input pin for INT3, and a trigger input pin in the pulse output port mode.                                  |  |

| P50-P57       | I/O port P5               | I/O              | In addition to having the same functions as port P1, these pins also function as input pins for $\overline{INT5}$ – $\overline{INT7}$ , input pins for timers B0–B2, and input pins for position-data-input pins in the three-phase waveform mode.                                                           |  |

| P60-P65       | I/O port P6               | I/O              | In addition to having the same functions as port P1, these pins also function as I/O pins for timers A0–A2, and output pins for the motor drive waveform.                                                                                                                                                    |  |

| P70–P74       | I/O port P7               | I/O              | In addition to having the same functions as port P1, these pins also function as input pins for the A-D converter. P73 functions as an output pin for the D-A converter; P74 functions as an output pin for the D-A converter, an input pin for INT3, and a trigger input pin in the pulse output port mode. |  |

| P6OUTcut      | P6OUTcut input            | Input            | This pin has the function to forcibly place port P6 pins in the input mode. Also, this pin functions as an input pin for $\overline{INT4}$ ; and this pin is used to input a signal, which forcibly cuts off a motor drive waveform output.                                                                  |  |

16-BIT CMOS MICROCOMPUTER

### PIN DESCRIPTION (FLASH MEMORY SERIAL I/O MODE)

| Pin          | Name                      | Input<br>/Output | Functions                                                                                                               |

|--------------|---------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------|

| Vcc, Vss     | Power supply input        | —                | Apply 5 V $\pm$ 0.5 V to Vcc, and 0 V to Vss.                                                                           |

| MD0          | MD0                       | Input            | Connect this pin to Vss.                                                                                                |

| MD1          | MD1                       | Input            | Connect this pin to Vss via a resistor of 10 k $\Omega$ to 100 k $\Omega$ .                                             |

| RESET        | Reset input               | Input            | The reset input pin.                                                                                                    |

| Xin          | Clock input               | Input            | Connect a ceramic oscillator between the XIN and XOUT pins, or input an external                                        |

| Хоит         | Clock output              | Output           | clock from the XIN pin with the XOUT pin left open.                                                                     |

| AVcc, AVss   | Analog supply input       | —                | Connect AVcc to Vcc, and AVss to Vss.                                                                                   |

| Vref         | Reference voltage input   | Input            | Input an arbitrary level within the range of Vss-Vcc. (This is not used in the flash memory serial I/O mode.)           |

| P10-P17      | Input port P1             | Input            | Input "H" or "L", or leave them open. (This is not used in the flash memory serial I/O mode.)                           |

| P20-P23, P27 | Input port P2             | Input            | Input "H" or "L", or leave them open. (This is not used in the flash memory serial I/O mode.)                           |

| P24          | SCLK input                | Input            | This is an input pin for a serial clock                                                                                 |

| P25          | SDA I/O                   | I/O              | This is an I/O pin for serial data. Connect this pin to VCC via a resistor (about 1 k $\Omega$ ).                       |

| P26          | BUSY output               | Output           | This is an output pin for the BUSY signal.                                                                              |

| P6OUTcut     | P6OUTCUT input            | Input            | Input "H".                                                                                                              |

| P55-P57      | Input port P5             | Input            | Input "H" or "L", or leave them open. (This is not used in the flash memory serial I/O mode.)                           |

| P60-P65      | Input port P6             | Input            | Input "H" or "L", or leave them open. (This is not used in the flash memory serial I/O mode.)                           |

| P70–P74      | Input port P7             | Input            | Input "H" or "L", or leave them open. (This is not used in the flash memory serial I/O mode.)                           |

| VCONT        | Filter circuit connection |                  | Connect this pin to the filter circuit, or leave this pin open. (This is not used in the flash memory serial I/O mode.) |

**16-BIT CMOS MICROCOMPUTER**

### **BASIC FUNCTION BLOCKS**

Each of the M37906F8CFP and M37906F8CSP has the same function as that of the M37906M4C-XXXFP except for the following. Therefore, for details except for the following, refer to the datasheet of the M37906M4C-XXXFP.

- Flash memory size

- RAM size

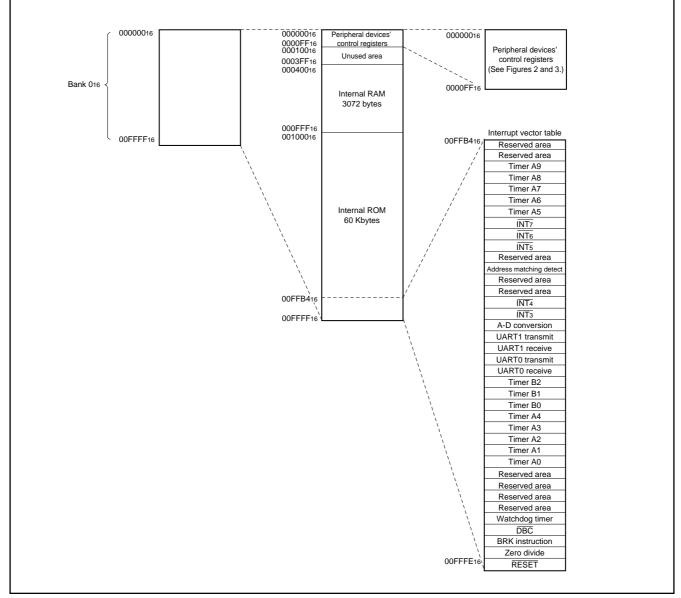

#### MEMORY

Figure 1 shows the memory map.

Fig. 1 Memory map of M37906F8CFP, M37906F8CSP (Single-chip mode)

**16-BIT CMOS MICROCOMPUTER**

| Address (H           | lexadecimal notation)                                     |

|----------------------|-----------------------------------------------------------|

| 00000016             | Reserved area (Note)                                      |

| 00000116             | Reserved area (Note)                                      |

| 00000216             | Reserved area (Note)                                      |

| 00000316             | Port P1 register                                          |

| 00000416             | Reserved area (Note)                                      |

| 00000516             | Port P1 direction register                                |

| 00000616             | Port P2 register                                          |

| 00000716             | Reserved area (Note)                                      |

| 00000816             | Port P2 direction register                                |

| 00000916             | Reserved area (Note)                                      |

| 00000A16             | Reserved area (Note)                                      |

| 00000B16             | Port P5 register                                          |

| 00000C16             | Reserved area (Note)                                      |

| 00000D16             | Port P5 direction register                                |

| 00000E16             | Port P6 register                                          |

| 00000F16             | Port P7 register                                          |

| 00001016             | Port P6 direction register                                |

| 00001116             | Port P7 direction register                                |

| 00001216             | Reserved area (Note)                                      |

| 00001316             |                                                           |

| 00001416             | Reserved area (Note)                                      |

| 00001516             |                                                           |

| 00001616             | Reserved area (Note)                                      |

| 00001716             | Reserved area (Note)                                      |

| 00001816             | Reserved area (Note)                                      |

| 00001916             | Reserved area (Note)                                      |

| 00001A16             |                                                           |

| 00001B16             |                                                           |

| 00001C16             |                                                           |

| 00001D16             |                                                           |

| 00001E16             | A-D control register 0                                    |

| 00001F16             | A-D control register 1                                    |

| 00002016             | A-D register 0                                            |

| 00002116             |                                                           |

| 00002216             | A-D register 1                                            |

| 00002316             |                                                           |

| 00002416             | A-D register 2                                            |

| 00002516             |                                                           |

| 00002616             | A-D register 3                                            |

| 00002716             |                                                           |

| 00002816             | A-D register 4                                            |

| 00002916             |                                                           |

| 00002A16             | Reserved area (Note)                                      |

| 00002B16             | Reserved area (Note)                                      |

| 00002C16             | Reserved area (Note)                                      |

| 00002D16<br>00002E16 | Reserved area (Note)                                      |

|                      | Reserved area (Note)                                      |

| 00002F16<br>00003016 | Reserved area (Note) UART0 transmit/receive mode register |

| 00003016             | UARTO baud rate register (BRG0)                           |

|                      |                                                           |

| 00003216<br>00003316 | UART0 transmit buffer register                            |

| 00003316             | UART0 transmit/receive control register 0                 |

| 00003418             | UART0 transmit/receive control register 0                 |

| 00003516             |                                                           |

| 00003016             | UART0 receive buffer register                             |

| 00003716             | UART1 transmit/receive mode register                      |

| 00003916             | UART1 baud rate register (BRG1)                           |

| 00003916<br>00003A16 |                                                           |

| 00003A16             | UART1 transmit buffer register                            |

| 00003D16             | UART1 transmit/receive control register 0                 |

| 00003C18             | UART1 transmit/receive control register 0                 |

| 00003D16             |                                                           |

| 00003E16             | UART1 receive buffer register                             |

|                      | L                                                         |

| Address (H                       | lexadecimal notation)                                       |

|----------------------------------|-------------------------------------------------------------|

| 00004016                         | Count start register 0                                      |

| 00004116                         | Count start register 1                                      |

| 00004110                         | One-shot start register 0                                   |

| 00004216                         | One-shot start register 0                                   |

|                                  | Up-down register 0                                          |

| 00004416                         |                                                             |

| 00004516                         | Timer A clock division select register                      |

| 00004616                         | Timer A0 register                                           |

| 00004716                         |                                                             |

| 00004816                         | Timer A1 register                                           |

| 00004916                         |                                                             |

| 00004A16                         | Timer A2 register                                           |

| 00004B16                         |                                                             |

| 00004C16                         | Timer A3 register                                           |

| 00004D16                         |                                                             |

| 00004E16                         | Timer A4 register                                           |

| 00004F16                         |                                                             |

| 00005016                         | Timer B0 register                                           |

| 00005116                         |                                                             |

| 00005216                         | Timor P1 register                                           |

| 00005316                         | Timer B1 register                                           |

| 00005416                         | Timer B2 register                                           |

| 00005516                         | Timer B2 register                                           |

| 00005616                         | Timer A0 mode register                                      |

| 00005716                         | Timer A1 mode register                                      |

| 00005816                         | Timer A2 mode register                                      |

| 00005916                         | Timer A3 mode register                                      |

| 00005A16                         | Timer A4 mode register                                      |

| 00005B16                         | Timer B0 mode register                                      |

| 00005C16                         | Timer B1 mode register                                      |

| 00005D16                         | Timer B2 mode register                                      |

| 00005E16                         | Processor mode register 0                                   |

| 00005F16                         | Processor mode register 1                                   |

| 00006016                         | Watchdog timer register                                     |

| 00006116                         | Watchdog timer frequency select register                    |

| 00006216                         | Particular function select register 0                       |

| 00006316                         | Particular function select register 1                       |

| 00006416                         | Particular function select register 2                       |

| 00006516                         | Reserved area (Note)                                        |

| 00006616                         | Debug control register 0                                    |

| 00006716                         | Debug control register 1                                    |

| 00006816                         |                                                             |

| 00006916                         | Address comparison register 0                               |

| 00006916<br>00006A16             | Address comparison register 0                               |

| 00006A16                         |                                                             |

|                                  | Address comparison register 1                               |

| 00006C16                         | Address comparison register 1                               |

| 00006D16                         | INITE interment constraits                                  |

| 00006E16                         | INT3 interrupt control register                             |

| 00006F16                         | INT4 interrupt control register                             |

| 00007016                         | A-D conversion interrupt control register                   |

| 00007116                         | UARTO transmit interrupt control register                   |

| 00007216                         | UARTO receive interrupt control register                    |

| 00007316                         | UART1 transmit interrupt control register                   |

| 00007416                         | UART1 receive interrupt control register                    |

| 00007516                         | Timer A0 interrupt control register                         |

| 00007616                         | Timer A1 interrupt control register                         |

| 00007716                         | Timer A2 interrupt control register                         |

| 00007816                         | Timer A3 interrupt control register                         |

| 00007916                         | Timer A4 interrupt control register                         |

| 00007A16                         | Timer B0 interrupt control register                         |

| 00007A16                         | Timer D1 interrupt control register                         |

| 00007A16<br>00007B16             | Timer B1 interrupt control register                         |

|                                  | Timer B2 interrupt control register                         |

| 00007B16<br>00007C16<br>00007D16 | Timer B2 interrupt control register<br>Reserved area (Note) |

| 00007B16<br>00007C16             | Timer B2 interrupt control register                         |

Note: Do not write to this address.

Fig. 2 Location of SFRs (1)

PRELIMINARY Notice: This is not a final specification. Some parametric limits are subject to change.

16-BIT CMOS MICROCOMPUTER

| Address (H           | lexadecimal notation)                          |

|----------------------|------------------------------------------------|

| 00008016             | Reserved area (Note)                           |

| 00008116             | Reserved area (Note)                           |

| 00008216             | Reserved area (Note)                           |

| 00008316             | Reserved area (Note)                           |

| 00008416             | Reserved area (Note)                           |

| 00008516             | Reserved area (Note)                           |

| 00008616             | Reserved area (Note)                           |

| 00008716             | Reserved area (Note)                           |

| 00008816             |                                                |

| 00008916<br>00008A16 | Posonyad area (Nata)                           |

| 00008A16<br>00008B16 | Reserved area (Note)                           |

| 00008C16             | Reserved area (Note)                           |

| 00008D16             |                                                |

| 00008E16             | Reserved area (Note)                           |

| 00008F16             |                                                |

| 00009016             | Reserved area (Note)                           |

| 00009116             |                                                |

| 00009216             | Reserved area (Note)                           |

| 00009316             |                                                |

| 00009416             |                                                |

| 00009516             | External interrupt input read-out register     |

| 00009616             | D-A control register                           |

| 00009716             |                                                |

| 00009816             | D-A register 0                                 |

| 00009916             | D-A register 1                                 |

| 00009A16             |                                                |

| 00009B16<br>00009C16 | Reserved area (Note)                           |

| 00009C16<br>00009D16 | Reserved area (Note)                           |

| 00009E16             | Flash memory control register                  |

| 00009E16             |                                                |

| 0000A016             | Reserved area (Note)                           |

| 0000A116             |                                                |

| 0000A216             | Reserved area (Note)                           |

| 0000A316             |                                                |

| 0000A416             | Reserved area (Note)                           |

| 0000A516             |                                                |

| 0000A616             | Waveform output mode register                  |

| 0000A716             | Dead-time timer                                |

| 0000A816             | Three-phase output data register 0             |

| 0000A916             | Three-phase output data register 1             |

| 0000AA16             | Position-data-retain function control register |

| 0000AB16             |                                                |

| 0000AC16             | Serial I/O pin control register                |

| 0000AD16<br>0000AE16 | Port P2 pin function control register          |

| 0000AE16<br>0000AF16 | Port P2 pin function control register          |

| 0000Ai 16            | Reserved area (Note)                           |

| 0000B116             | Reserved area (Note)                           |

| 0000B216             | Reserved area (Note)                           |

| 0000B316             | Reserved area (Note)                           |

| 0000B416             | Reserved area (Note)                           |

| 0000B516             | Reserved area (Note)                           |

| 0000B616             | Reserved area (Note)                           |

| 0000B716             | Reserved area (Note)                           |

| 0000B816             | Reserved area (Note)                           |

| 0000B916             |                                                |

| 0000BA16             | Reserved area (Note)                           |

| 0000BB16             | Reserved area (Note)                           |

| 0000BC16             | Clock control register 0                       |

| 0000BD16             | Reserved area (Note)                           |

| 0000BE16<br>0000BF16 | Reserved area (Note)                           |

| 000000016            | Reserved area (Note)                           |

|                      |                                                |

| Address (H           | exadecimal notation)                                                    |

|----------------------|-------------------------------------------------------------------------|

| 0000C016             |                                                                         |

| 0000C116             |                                                                         |

| 0000C216             |                                                                         |

| 0000C316             |                                                                         |

| 0000C416             | Up-down register 1                                                      |

| 0000C516             |                                                                         |

| 0000C616             |                                                                         |

| 0000C716             | Timer A5 register                                                       |

| 0000C816             |                                                                         |

| 0000C916             | Timer A6 register                                                       |

| 0000CA16             |                                                                         |

| 0000CB16             | Timer A7 register                                                       |

| 0000CC16             | T' AD I'                                                                |

| 0000CD16             | Timer A8 register                                                       |

| 0000CE16             | Timer A0 register                                                       |

| 0000CF16             | Timer A9 register                                                       |

| 0000D016             | Timor A04 register                                                      |

| 0000D116             | Timer A01 register                                                      |

| 0000D216             | Timer A14 register                                                      |

| 0000D316             | Timer A11 register                                                      |

| 0000D416             | Timor A21 registor                                                      |

| 0000D516             | Timer A21 register                                                      |

| 0000D616             | Timer A5 mode register                                                  |

| 0000D716             | Timer A6 mode register                                                  |

| 0000D816             | Timer A7 mode register                                                  |

| 0000D916             | Timer A8 mode register                                                  |

| 0000DA16             | Timer A9 mode register                                                  |

| 0000DB16             | Reserved area (Note)                                                    |

| 0000DC16             | Comparator function select register 0                                   |

| 0000DD16             | Reserved area (Note)                                                    |

| 0000DE16             | Comparator result register 0                                            |

| 0000DF16             | Reserved area (Note)                                                    |

| 0000E016             | Reserved area (Note)                                                    |

| 0000E116             | Reserved area (Note)                                                    |

| 0000E216             | Reserved area (Note)                                                    |

| 0000E316             | Reserved area (Note)                                                    |

| 0000E416             | Reserved area (Note)                                                    |

| 0000E516             | Reserved area (Note)                                                    |

| 0000E616             | Reserved area (Note)                                                    |

| 0000E716             | Reserved area (Note)                                                    |

| 0000E816             | Reserved area (Note)                                                    |

| 0000E916             | Reserved area (Note)                                                    |

| 0000EA16             | Reserved area (Note)                                                    |

| 0000EB16             | Reserved area (Note)                                                    |

| 0000EC16             | Reserved area (Note)                                                    |

| 0000ED16             | Reserved area (Note)                                                    |

| 0000EE16             | Reserved area (Note)                                                    |

| 0000EF16             | Reserved area (Note)                                                    |

| 0000F016             | Papartiad area (Nata)                                                   |

| 0000F116             | Reserved area (Note)                                                    |

| 0000F216             | Reserved area (Note)                                                    |

| 0000F316<br>0000F416 |                                                                         |

| 0000F416<br>0000F516 | Timor AE interrupt control register                                     |

| 0000F516<br>0000F616 | Timer A5 interrupt control register                                     |

| 0000F016<br>0000F716 | Timer A6 interrupt control register                                     |

| 0000F716<br>0000F816 | Timer A7 interrupt control register Timer A8 interrupt control register |

| 0000F816<br>0000F916 | Timer A8 Interrupt control register                                     |

| 0000F916<br>0000FA16 |                                                                         |

| 0000FA16             |                                                                         |

| 0000FC16             |                                                                         |

| 0000FD16             | INT5 interrupt control register                                         |

| 0000FE16             | INT6 interrupt control register                                         |

|                      | INT7 interrupt control register                                         |

| 0000FF16             |                                                                         |

Note: Do not write to this address.

Fig. 3 Location of SFRs (2)

**16-BIT CMOS MICROCOMPUTER**

### FLASH MEMORY MODE

These microcomputers contain the flash memory; and single-powersupply reprogramming is available to this. These microcomputers have the following three modes, enabling reading/programming/erasure for the flash memory:

- Flash memory parallel I/O mode and Flash memory serial I/O mode, where the flash memory is handled by using an external programmer.

- CPU reprogramming mode, where the flash memory is handled by the central processing unit (CPU).

As shown in Figure 4, the flash memory is divided into several blocks, and erasure per block is possible.

This internal flash memory has the boot ROM area storing the reprogramming control software for reprogramming in the CPU reprogramming mode and flash memory serial I/O mode, as well as the user ROM area storing a certain control software for the normal operation in the microcomputer mode.

Although our reprogramming control firmware for the flash memory serial I/O mode has been stored into this boot ROM area on shipment, the user-original reprogramming control software which is more appropriate for the user's system is reprogrammable into this area, instead. Note that the reprogramming for the boot ROM area is enabled only in the flash memory parallel I/O mode.

Fig. 4 M37906F8CFP, M37906F8CSP: block configuration of internal flash memory

**16-BIT CMOS MICROCOMPUTER**

#### Flash Memory Parallel I/O Mode

The flash memory parallel I/O mode is used to manipulate the internal flash memory with a parallel programmer. This parallel programmer uses the software commands listed in Table 1 to do the flash memory manipulations, such as read/programming/erase operations.

Table 1. Software commands (flash memory parallel I/O mode)

| Soltware Command      |

|-----------------------|

| Read Array            |

| Read Status Register  |

| Clear Status Register |

| Programming           |

| Block Erase           |

| Erase All Block       |

Addresses FF9016 to FF9F16 are the reserved area for the parallel programmer. Therefore, when the user uses the flash memory parallel I/O mode, do not program to this area.

#### **User ROM Area and Boot ROM Area**

The user ROM area and boot ROM area can be reprogrammed in the flash memory parallel I/O mode.

The programming and block erase operations can be performed only to these areas.

The boot ROM area, 8 Kbytes in size, is assigned to addresses 000016–1FFF16, so that programming and block erase operations can be performed only to this area. (Access to any address out of this area is prohibited).

The erasable block in the boot ROM area is only one block, consisting of 8 Kbytes. The reprogramming control firmware to be used in the flash memory serial I/O mode has been stored to this boot ROM area on our shipment. Therefore, do not reprogram the boot ROM area if the user uses the flash memory serial I/O mode.

Do not program to addresses FF9016 to FF9F16 because this area is the reserved area for the programmer.

Note that, when the boot ROM area is read out from the CPU in the CPU reprogramming mode, described later, its addresses will be shifted to E00016—FFFF16.

16-BIT CMOS MICROCOMPUTER

#### Flash Memory Serial I/O Mode

In the flash memory serial I/O mode, addresses, data, and software commands, which are required to read/program/erase the internal flash memory, are serially input and output with a fewer pins and the dedicated serial programmer.

In this mode, being different from the flash memory parallel I/O mode, the CPU controls reprogramming of the flash memory (using the CPU reprogramming mode), serial input of the reprogramming data, etc.

The reprogramming control firmware for the flash memory serial I/O mode has been stored in the boot ROM area on shipment of the product from us. Note that, then, the flash memory serial I/O mode will become unavailable if the boot ROM area has been reprogrammed in the flash memory parallel I/O mode.

Note that, also, this reprogramming control firmware for the flash memory serial I/O mode is subject to change.

Figures 5 and 6 show the pin connections in the flash memory serial  $\ensuremath{\mathrm{I/O}}$  mode.

The three pins, SCLK, SDA, and BUSY, are used to input and output serial data.

The SCLK pin is the input pin of external transfer clocks. The SDA pin is the I/O pin of transmit and receive data, and its output acts as the N-channel open-drain output. To the SDA pin, connect an external pullup resistor (about 1 k $\Omega$ ). The BUSY pin is the output pin of the BUSY flag (CMOS output) and goes "H" during BUSY periods owing to a certain operation, such as transmit, receive, erase, programming, etc.

Transmit and receive data are serially transferred 8 bits at a time. In the flash memory serial I/O mode, only the user ROM area can be reprogrammed; the boot ROM area is not accessible.

Addresses FF9016 to FF9F16 are the reserved area for the serial programmer. Therefore, when the user uses the flash memory serial I/O mode, do not program to this area.

**16-BIT CMOS MICROCOMPUTER**

Fig. 5 Pin connection of M37906F8CFP in flash memory serial I/O mode (outline: 42P2R-E)

PRELIMINARY Notice: This is not a final specification. Some parametric limits are subject to change.

Fig. 6 Pin connection of M37906F8CSP in flash memory serial I/O mode (outline: 42P4B)

**16-BIT CMOS MICROCOMPUTER**

#### **CPU Reprogramming Mode**

The CPU reprogramming mode is used to perform the operations for the internal flash memory (reading, programming, erasing) under control of the CPU.

In this mode, only the user ROM area can be reprogrammed; the boot ROM area cannot be reprogrammed.

The user-original reprogramming control software for the CPU reprogramming mode can be stored in either the user ROM area or the boot ROM area.

Because the CPU cannot read out the flash memory in the CPU reprogramming mode, the above software must be transferred to the internal RAM in advance to be executed.

### **Boot Mode**

The user-original reprogramming control software for the CPU reprogramming mode must be stored into the user ROM area or the boot ROM area in the flash memory parallel I/O mode in advance. (If this program has been stored into the boot ROM area, the flash memory serial I/O mode will become unavailable). Note that addresses of the boot ROM area depend on the accessing ways to the boot ROM area, When accessing in the flash memory parallel I/O mode, these addresses will be shifted to 000016 to 1FFF16. On the other hand, when accessing with the CPU, these addresses will be shifted to E00016 to FFFF16.

Reset removal with both of the MD0 and MD1 pins held "L" invokes the normal microcomputer mode, and the CPU operates using the control software stored in the user ROM area. In this case, the boot ROM area is not accessible.

Removing reset with the MD0 pin held "L" and the MD1 pin "H", the CPU starts its operation using the reprogramming control software stored in the boot ROM area. This mode is called the boot mode. The reprogramming control software in the boot ROM area can also reprogram the user ROM area.

After reset removal, be sure not to change the status at pins MD0 and MD1.

**16-BIT CMOS MICROCOMPUTER**

#### Function overview (CPU reprogramming mode)

The CPU reprogramming mode is available in the single-chip mode, memory expansion mode, and boot mode to reprogram the user ROM area only.

In the CPU reprogramming mode, the CPU erases, programs, and reads the internal flash memory by writing software commands. Note that the user-original reprogramming control software must be transferred to the internal RAM in advance to be executed.

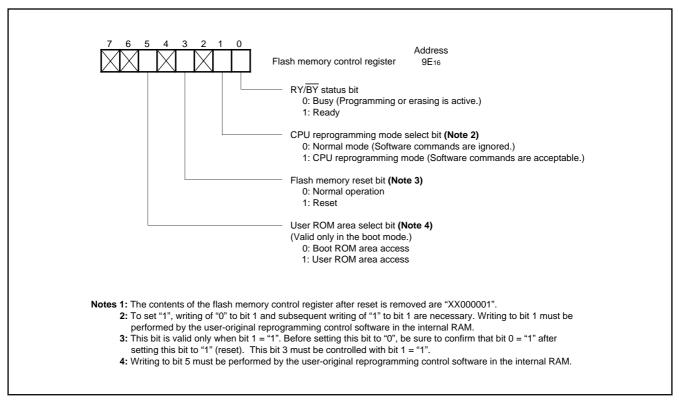

The CPU reprogramming mode becomes active when "1" is written into the flash memory control register's bit 1 (the CPU reprogramming mode select bit) shown in Figure 7, and software commands become acceptable.

In the CPU reprogramming mode, software commands and data are all written to and read from even addresses (Note that address Ao in byte addresses = "0".) 16 bits at a time. Therefore, a software command consisting of 8 bits must be written to an even address; therefore, any command written to an odd address will be invalid. Since the write data at the 2nd cycle of a programming command consists of 16 bits, this data must be written to even and odd addresses.

The seaquencer in the flash memory controls the erase and programming operations. What the status of the seaquencer operation is and whether the programming or erase operation has been completed normally or terminated by an error can be examined by reading the flash memory control register.

Figure 7 shows the bit configuration of the flash memory control register.

Bit 0 (the RY/BY status bit) is a read-only bit for indicating the seaquencer operation. This bit goes to "0" (BUSY) while the automatic programming/erase operation is active and goes to "1" (READY) during the other operations.

Bit 1 serves as the CPU reprogramming mode select bit. Writing of "1" to this bit selects the CPU reprogramming mode, and software commands will be acceptable. Because the CPU cannot directly access the internal flash memory in the CPU reprogramming mode, writing to this bit 1 must be performed by the user-original reprogramming control software which has been transferred to the internal RAM in advance. To set bit 1 to "1", it is necessary to write "0" and "1" to this bit 1 successively. On the other hand, to clear this bit to "0", it is sufficient only to write "0".

Bit 3 (the flash memory reset bit) resets the control circuit of the internal flash memory and is used when the CPU reprogramming mode is terminated or when an abnormal access to the flash memory happens. Writing of "1" to bit 3 with the CPU reprogramming mode select bit = "1" preforms the reset operation. To remove the reset, write "0" to bit 3 after confirming bit 0 (the RY/ $\overline{BY}$  status bit) becomes "1".

Bit 5 serves as the user ROM area select bit and is valid only in the boot mode. Setting this bit to "1" in the boot mode switches an accessible area from the boot ROM area to the user ROM area. To use the CPU reprogramming mode in the boot mode, set this bit to "1". Note that when the microcomputer is booted up in the user ROM area, only the user ROM area is accessible and bit 5 is invalid; on the other hand, when the microcomputer is in the boot mode, bit 5 is valid independent of the CPU reprogramming mode. To rewrite bit 5, execute the user-original reprogramming control software transferred to the internal RAM in advance.

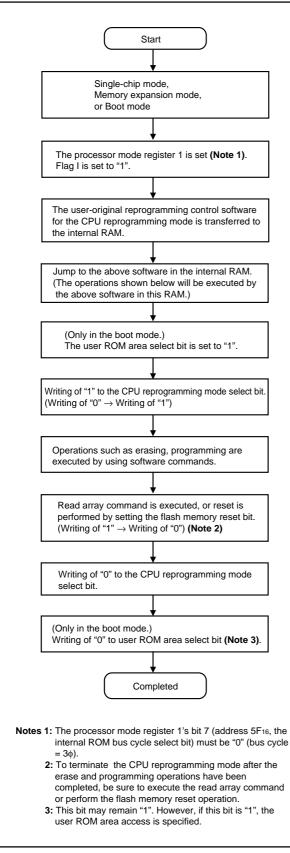

Figure 8 shows the CPU reprogramming mode set/termination flow-

chart, and be sure to follow this flowchart. As shown in Note 1 of Figure 8, before selecting the CPU reprogramming mode, set "0" to the processor mode register 1's bit 7 (the internal ROM bus cycle select bit) and set flag I to "1" to avoid an interrupt request input.

When a watchdog timer interrupt request is generated in the CPU reprogramming mode, when an input to the  $\overline{\text{RESET}}$  pin is "L", or when the software reset is performed, the flash memory control circuit and flash memory control register will be reset.

When the flash memory is reset during the erase or programming operation, this operation is cancelled and the target block's data will be invalid. Just before writing a software command related to the erase/programming operation, be sure to write to the watchdog timer. In the CPU reprogramming mode, be sure not to use the **STP** and **WIT** instructions.

#### 16-BIT CMOS MICROCOMPUTER

Fig. 8 CPU reprogramming mode set/termination flowchart

#### Software Commands

Table 2 lists the software commands.

By writing a software command after the CPU reprogramming mode select bit has been set to "1", erasing, programming, etc. can be specified. Note that, at software commands' input, the high-order byte (D8–D15) is ignored. (Except for the write data at the 2nd cycle of a programming command.)

Software commands are explained as below.

#### Read Array Command (FF16)

By writing command code "FF16" at the 1st bus cycle, the microcomputer enters the read array mode. If an address to be read is input in the next or the following bus cycles, the contents at the specified address are output to the data bus (D0 to D15) in a unit of 16 bits. The read array mode is maintained until writing of another software

command.

#### Read Status Register Command (7016)

Writing command code "7016" at the 1st bus cycle outputs the contents of the status register to the data bus (D0-D7) by a read at the 2nd bus cycle.

The status register is explained later.

#### Clear Status Register Command (5016)

This command clears two status bits (SR.4, 5) each of which is set to "1" to indicate that the operation has been terminated by an error. To clear these bits, write command code "5016" at the 1st bus cycle.

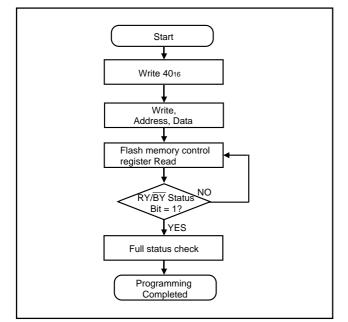

#### Programming Command (4016)

This command facilitates programming of 1 word (2 bytes) at a time. To initiate programming, write command code "4016" at the 1st bus cycle; when write data is written in a unit of 16 bits at the 2nd bus cycle, the address is specified at the same time. Upon completion of data writing, automatic programming (data programming and verification) operation is started.

The completion of the automatic programming operation is confirmed by a read of the flash memory control register. The RY/ $\overline{BY}$  status bit of the flash memory control register goes "0" during the automatic programming operation; and also, it goes "1" after the end of it.

Before execution of the next command, be sure to confirm that the  $RY/\overline{BY}$  status bit is set to "1" (READY). During the automatic programming operation, writing of commands and access to the flash memory must not be performed.

When programming continuously, the programming command can be executed with the read status register mode kept if there is no programming error. Simultaneously with start of the automatic programming, the read status register mode is automatically active. In this case, the read status register mode is retained until the next read array command (FF16) is written or until the reset is performed by using the flash memory reset bit.

Reading out the status register after the automatic programming operation is completed reports the result of it. For details, refer to the section on the status register.

Figure 9 shows an example of the programming flowchart.

Additional programming to any word that has already been programmed is prohibited.

#### **16-BIT CMOS MICROCOMPUTER**

#### Table 2. Software commands (CPU reprogramming mode)

|                       | 1st cycle |            |                    | 2nd cycle |             |              |

|-----------------------|-----------|------------|--------------------|-----------|-------------|--------------|

| Command               | Mode      | Address    | Data<br>(Do to D7) | Mode      | Address     | Data         |

| Read Array            | Write     | X (Note 2) | FF16               | —         | —           | _            |

| Read Status Register  | Write     | X          | 7016               | Read      | Х           | SRD (Note 3) |

| Clear Status Register | Write     | Х          | 5016               | —         | -           | _            |

| Programming           | Write     | Х          | 4016               | Write     | WA (Note 4) | WD (Note 4)  |

| Block Erase           | Write     | Х          | 2016               | Write     | BA (Note 5) | D016         |

| Erase All Block       | Write     | Х          | 2016               | Write     | Х           | 2016         |

Notes 1: At software commands' input, the high-order byte of data (D8-D15) is ignored.

2: X = An arbitrary address in the user ROM area. (Note that A0 = "0".)

3: SRD = Status Register Data

4: WA = Write Address, WD = Write Data (16 bits).

5: Block address: the maximum address of each block must be input. Note that address A0 = "0".

### Block Erase Command (2016/D016)

Writing command code "2016" at the 1st bus cycle and writing confirmation command code "D016" and the maximum address of the block (Note that address  $A_0 =$  "0".) at the subsequent 2nd bus cycle initiate the automatic erase (erasing and erase verification) operation for the specified block.

The completion of the automatic erase operation is confirmed by a read of the flash memory control register. The RY/ $\overline{BY}$  status bit of the flash memory control register goes "0" simultaneously with start of the automatic erase operation; and also, it goes "1" simultaneously with completion of it.

Before execution of the next command, be sure to confirm that the  $RY/\overline{BY}$  status bit is set to "1" (READY). During the automatic erase operation, writing of commands and access to the flash memory must not be performed.

Simultaneously with start of the automatic erase, the read status register mode is automatically active. In this case, the read status register mode is retained until the next read array command (FF16) is written or until the reset is performed by using the flash memory reset bit.

Reading out the status register after the automatic erase operation is completed reports the result of it. For details, refer to the section on the status register.

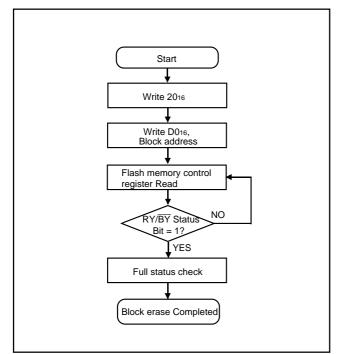

Figure 10 shows an example of the block erase flowchart.

16-BIT CMOS MICROCOMPUTER

Fig. 9 Programming flowchart

Fig. 10 Block erase flowchart

### Erase All Block Command (2016/2016)

Writing command code "2016" at the 1st bus cycle and writing command code "2016" at the subsequent 2nd bus cycle initiate the continuous block erase (chip erase) operations for all the blocks.

The completion of the chip erase operation, as well as of the block erase operation, is confirmed by a read of the flash memory control register. The result of the automatic erase operation is also reported by a read of the status register.

During the automatic erase operation (when the RY/BY status bit = "0"), writing of commands and access to the flash memory must not be performed.

### **Status Register**

The status register is used to indicate whether the programming/ erase operation has been completed normally or terminated by an error. By writing the read status register command (7016), the contents of the status register can be read out; by writing the clear status register command (5016), the contents of the status register can be cleared.

Table 3 lists the definition of each bit of the status register. The status register outputs "8016" after reset is removed. The status of each bit is described below.

#### **16-BIT CMOS MICROCOMPUTER**

### Erase Status Bit (SR.5)

This bit reports the status of the automatic erase operation. This bit is set to "1" if an erase error occurs and returns to "0" if the clear status register command (5016) is written.

### **Programming Status Bit (SR.4)**

This bit reports the status of the automatic programming operation. This bit is set to "1" if a programming error occurs and returns to "0" if the clear status register command (5016) is written.

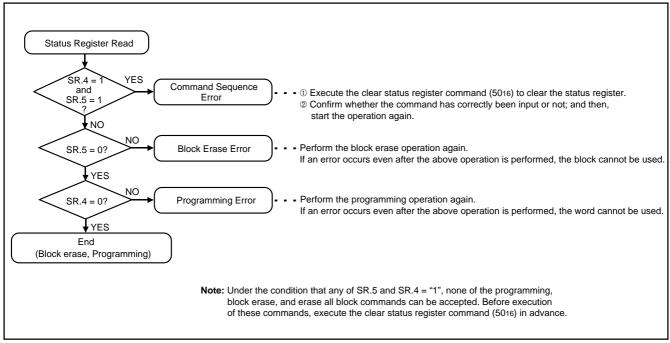

Under the condition that any of SR.5, SR.4 = "1", none of the programming, block erase, and erase all block commands can be accepted. Before execution of these commands, execute the clear status register command (5016), in advance, to clear these status bits.

Both of SR.4, SR.5 are set to "1" under the following conditions (Command Sequence Error):

- (1) when data other than "D016" and "FF16" is written to the data in the 2nd bus cycle of the block erase command (2016/D016)

- (2) when data other than "2016" and "FF16" is written to the data in the 2nd bus cycle of the erase all block command (2016/2016)

Note that, writing of "FF16" forces the microcomputer into the read array mode. Simultaneously with this, the command written in the 1st bus cycle will be canceled.

### **Full Status Check**

The full status check reports the results of the erase or programming operation.

Figure 11 shows the full status check flowchart and actions to be taken if an error has occurred.

#### Table 3. Bit definition of status register

| Cumbol    | Status             | Definition           |                      |  |

|-----------|--------------------|----------------------|----------------------|--|

| Symbol    |                    | "1"                  | "O"                  |  |

| SR.7 (D7) | Reserved           |                      |                      |  |

| SR.6 (D6) | Reserved           |                      |                      |  |

| SR.5 (D5) | Erase Status       | Terminated by error. | Terminated normally. |  |

| SR.4 (D4) | Programming Status | Terminated by error. | Terminated normally. |  |

| SR.3 (D3) | Reserved           |                      |                      |  |

| SR.2 (D2) | Reserved           |                      |                      |  |

| SR.1 (D1) | Reserved           |                      |                      |  |

| SR.0 (D0) | Reserved           |                      |                      |  |

**16-BIT CMOS MICROCOMPUTER**

Fig. 11 Full status check flowchart and actions to be taken if an error has ocurred

#### DC Electrical Characteristics (Vcc = 5 V $\pm$ 0.5 V, Ta = 0 to 60 °C, f(fsys) = 20 MHz (Note))

| Symbol | Parameter                                 | Limits |      |      | 1.1  |

|--------|-------------------------------------------|--------|------|------|------|

|        |                                           | Min.   | Тур. | Max. | Unit |

| lcc1   | Vcc power source current (at read)        |        | 30   | 48   | mA   |

| lcc2   | Vcc power source current (at write)       |        |      | 48   | mA   |

| lcc3   | Vcc power source current (at programming) |        |      | 54   | mA   |

| Icc4   | VCC power source current (at erasing)     |        |      | 54   | mA   |

Limits of VIH, VIL, VOH, VOL, IIH, and IIL for each pin are the same as those in the microcomputer mode. Note:  $f(f_{sys})$  indicates the system clcok (fsys) frequency.

### AC Electrical Characteristics (Vcc = 5 V ± 0.5 V, Ta = 0 to 60 °C, f(fsys) = 20 MHz (Note))

| Parameter                 |  | Limits  |       |      |

|---------------------------|--|---------|-------|------|

|                           |  | Тур.    | Max.  | Unit |

| 256-byte programming time |  | 4       | 40    | ms   |

| Block erase time          |  | 0.6     | 8     | S    |

| Erase all block time      |  | 0.6 X n | 8 X n | S    |

n = Number of blocks to be erased

The limits of parameters other than the above are same as those in the microcomputer mode.

Note: f(fsys) indicates the system clock (fsys) frequency.

**16-BIT CMOS MICROCOMPUTER**

### **ABSOLUTE MAXIMUM RATINGS**

| Symbol | Parameter                                                                                                       | Ratings         | Unit |

|--------|-----------------------------------------------------------------------------------------------------------------|-----------------|------|

| Vcc    | Power source voltage                                                                                            | -0.3 to 6.5     | V    |

| AVcc   | Analog power source voltage                                                                                     | -0.3 to 6.5     | V    |

| VI     | Input voltage P10–P17, P20–P27, P55–P57, P60–P65, P70–P74,<br>P6OUTcut, Vcont, Vref, XIN, RESET, BYTE, MD0, MD1 | -0.3 to Vcc+0.3 | V    |

| Vo     | Output voltage P10-P17, P20-P27, P55-P57, P60-P65, P70-P74, XOUT                                                | -0.3 to Vcc+0.3 | V    |

| Pd     | Power dissipation                                                                                               | 300             | mW   |

| Topr   | Operating ambient temperature                                                                                   | -20 to 85       | °C   |

| Tstg   | Storage temerature                                                                                              | -40 to 150      | °C   |

### RECOMMENDED OPERATING CONDITIONS (Vcc = 5 V, Ta = -20 to 85 °C, unless otherwise noted)

|           | Parameter                                                                                               |         | Limits |         |      |  |

|-----------|---------------------------------------------------------------------------------------------------------|---------|--------|---------|------|--|

| Symbol    |                                                                                                         |         | Тур.   | Max.    | Unit |  |

| Vcc       | Power source voltage                                                                                    | 4.5     | 5.0    | 5.5     | V    |  |

| AVcc      | Analog power source voltage                                                                             |         | Vcc    |         | V    |  |

| Vss       | Power source voltage                                                                                    |         | 0      |         | V    |  |

| AVss      | Analog power source voltage                                                                             |         | 0      |         | V    |  |

| Viн       | High-level input voltage P10–P17, P20–P27, P55–P57, P60–P65, P70–P74,<br>P6OUTcut, XIN, RESET, MD0, MD1 | 0.8 Vcc |        | Vcc     | V    |  |

| VIL       | Low-level input voltage P10–P17, P20–P27, P55–P57, P60–P65, P70–P74,<br>P6OUTcut, XIN, RESET, MD0, MD1  | 0       |        | 0.2 Vcc | V    |  |

| IOH(peak) | High-level peak output current P10–P17, P20–P27, P55–P57, P60–P65, P70–P74                              |         |        | -10     | mA   |  |

| IOH(avg)  | High-level average output current P10–P17, P20–P27, P55–P57, P60–P65, P70–P74                           |         |        | -5      | mA   |  |

| IOL(peak) | Low-level peak output current P10–P17, P20–P27, P55–P57, P70–P74                                        |         |        | 10      | mA   |  |

| IOL(peak) | Low-level peak output current P60–P65                                                                   |         |        | 20      | mA   |  |

| IOL(avg)  | Low-level average output current P10-P17, P20-P27, P55-P57, P70-P74                                     |         |        | 5       | mA   |  |

| IOL(avg)  | Low-level average output current P60-P65                                                                |         |        | 15      | mA   |  |

| f(XIN)    | External clock input frequency (Note 1)                                                                 |         |        | 20      | MHz  |  |

| f(fsys)   | System clock frequency                                                                                  |         |        | 20      | MHz  |  |

Notes 1: When using the PLL frequency multiplier, be sure that  $f(f_{sys}) = 20$  MHz or less.

2: The average output current is the average value of an interval of 100 ms.

3: The sum of IOL(peak) must be 110 mA or less, the sum of IOH(peak) must be 80 mA or less.

16-BIT CMOS MICROCOMPUTER

| Symbol   | Parameter                                                                                                                                                      | Test conditions                                                                                               |      | Limits |      | 1.1.4.14 |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------|--------|------|----------|

| Symbol   | Parameter                                                                                                                                                      | Test conditions                                                                                               | Min. | Тур.   | Max. | Unit     |