## 4096-BIT DYNAMIC RANDOM ACCESS MEMORY

- POWER SUPPLY  $V_{DD}$  = 12V,  $V_{CC}$  = 5V,  $V_{BB}$  = -5V (ALL WITH ± 10% TOLERANCE)

- ALL INPUTS ARE LOW CAPACITANCE AND TTL COMPATIBLE

- INPUT LATCHES FOR ADDRESSES, CHIP SELECT AND DATA IN

- INPUTS PROTECTED AGAINST STATIC CHARGE

- THREE-STATE TTL COMPATIBLE OUTPUT

- OUTPUT DATA LATCHED AND VALID INTO NEXT CYCLE

- ECL COMPATIBLE ON VBB POWER SUPPLY (-5.7V)

- LOW POWER CONSUMPTION: ACTIVE POWER UNDER 470 mW

STANDBY POWER UNDER 27 mW

- ORGANIZATION 4096 x 1 BIT IN 16-PIN STD PACKAGE

- FUNCTIONAL AND PIN COMPATIBLE WITH MK4027

- ACCESS TIME: TYPE M 4027-2 150 ns

- TYPE M 4027-3 200 ns

- TYPE M 4027-4 250 ns

The M 4027 is a 4096 word by 1 bit dynamic N-channel silicon gate MOS RAM. The M 4027 uses a single transistor cell utilizing a dynamic storage technique and dynamic control circuitry with low power dissipation. A unique multiplexing and latching technique for the address inputs permits the M 4027 to be mounted in a standard 16-pin package. The M 4027 incorporates several flexible operating modes. In addition to the usual read and write cycles, read modify write, page mode and RAS-only refresh cycles are available with the M 4027. Page-mode timing is very useful in systems requiring Direct Memory Access (DMA). The device is available in 16-lead dual in-line plastic or ceramic package (metal-seal), and ceramic package (frit-seal).

## **ABSOLUTE MAXIMUM RATINGS\***

|                  | Voltage on any pin relative to V <sub>BB</sub>                           | -0.5 to +20 | v  |

|------------------|--------------------------------------------------------------------------|-------------|----|

|                  | Voltage on V <sub>DD</sub> , V <sub>CC</sub> relative to V <sub>SS</sub> | -1 to +15   | v  |

|                  | $V_{BB} - V_{SS} (V_{DD} - V_{SS} > 0)$                                  | 0           | v  |

| Top              | Operating temperature                                                    | 0 to +70    | °C |

| T <sub>stq</sub> | Storage temperature for ceramic package                                  | -65 to +150 | °C |

|                  | for plastic package                                                      | -55 to +125 | °C |

| I.               | Short circuit output current                                             | 50          | mΑ |

| P <sub>tot</sub> | Total power dissipation                                                  | 1           | w  |

|                  |                                                                          |             |    |

Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

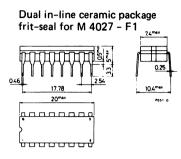

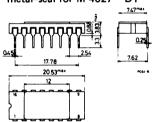

| ORDERING NUMBERS: | M 4027-2/3/4 | B1 | for dual in-line plastic package             |

|-------------------|--------------|----|----------------------------------------------|

|                   | M 4027-2/3/4 | D1 | for dual in-line ceramic package, metal-seal |

|                   | M 4027-2/3/4 | F1 | for dual in-line ceramic package, frit-seat  |

## MECHANICAL DATA (dimensions in mm)

Dual in-line ceramic package metal-seal for M 4027 - D1

## **PIN CONNECTIONS**

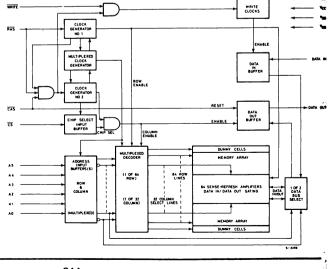

### **BLOCK DIAGRAM**

|                 | Parameter                                             |           |    |      |      |       |

|-----------------|-------------------------------------------------------|-----------|----|------|------|-------|

|                 | rarameter                                             | Min. Typ. |    | Max. | Unit | Notes |

| V <sub>DD</sub> | Supply voltage                                        | 10.8      | 12 | 13.2 | V    | 2     |

| V <sub>cc</sub> | Supply voltage                                        | 4.5       | 5  | 5.5  | V    | 2,3   |

| V <sub>SS</sub> | Supply voltage                                        | 0         | 0  | 0    | V    | 2     |

| VBB             | Supply voltage                                        | -4.5      | -5 | -5.7 | V    | 2     |

| VIHC            | Input high voltage on RAS, CAS, WRITE                 | 2.4       |    | 7    | V    | 2     |

| V <sub>IH</sub> | Input high voltage, all inputs except RAS, CAS, WRITE | 2.2       |    | 7    | V    | 2     |

| VIL             | Input low voltage, all inputs                         | -1        |    | 0.8  | v    | 2     |

## RECOMMENDED DC OPERATING CONDITIONS<sup>1</sup> (T<sub>amb</sub>= 0 to 70°C)<sup>4</sup>

Series Land

**DC ELECTRICAL CHARACTERISTICS** <sup>1</sup>  $(T_{amb} = 0 \text{ to } 70^{\circ}\text{C})^4$   $(V_{DD} = 12V \pm 10\%, V_{CC} = 5V \pm 10\%, V_{SS} = 0V, V_{BB} = -5.7 \text{ to } -4.5V)$

|                   | Parameter                                                             |      | Values |      |      | Notes |

|-------------------|-----------------------------------------------------------------------|------|--------|------|------|-------|

|                   | rarameter                                                             | Min. | Typ.   | Max. | Unit | NOTes |

| I <sub>DD1</sub>  | Average V <sub>DD</sub> power supply current                          |      |        | 35   | mA   | 5     |

| IDD2              | Standby V <sub>DD</sub> power supply current                          |      |        | 2    | mA   | 8     |

| I <sub>DD3</sub>  | Average V <sub>DD</sub> power supply current during "RAS only" cycles |      |        | 25   | mA   |       |

| lcc               | V <sub>CC</sub> power supply current                                  |      |        |      | mA   | 6     |

| Івв               | Average V <sub>BB</sub> power supply current                          |      |        | 150  | μA   |       |

| 1 <sub>1(L)</sub> | Input leakage current (any input)                                     |      |        | 10   | μA   | 7     |

| 10(L)             | Output leakage current                                                |      |        | 10   | μA   | 8,9   |

| V <sub>он</sub>   | Output high voltage (I <sub>SOURCE</sub> = -5 mA)                     | 2.4  |        |      | v    |       |

| V <sub>OL</sub>   | Output low voltage (I <sub>SINK</sub> = 3.2 mA)                       |      |        | 0.4  | v    |       |

# AC CHARACTERISTICS AND RECOMMENDED OPERATING CONDITIONS<sup>1,10,15</sup> $(T_{amb}=0 \text{ to } 70^{\circ}\text{C})^4$ , $(V_{DD}=12V \pm 10\%, V_{CC}=5V \pm 10\%, V_{SS}=0V, V_{BB}=-5.7 \text{ to } -4.5V)$

|                  |                                            |      |                   | т    | /pes     |      |       |       |       |

|------------------|--------------------------------------------|------|-------------------|------|----------|------|-------|-------|-------|

|                  | Parameter                                  |      | M 4027-2 M 4027-3 |      | M 4027-4 |      | Unit  | Notes |       |

|                  |                                            | Min. | Max.              | Min. | Max.     | Min. | Max.  | 1     |       |

| <sup>t</sup> RC  | Random read or write cycle time            | 320  |                   | 375  |          | 380  |       | ns    |       |

| <sup>t</sup> RWC | Read write cycle time                      | 320  |                   | 375  |          | 395  |       | ns    |       |

| tRMW             | Read modify write cycle time               | 320  |                   | 405  |          | 470  |       | ns    |       |

| <sup>t</sup> RAC | Access time from row address strobe        |      | 150               |      | 200      |      | 250   | ns    | 11-13 |

| <sup>t</sup> CAC | Access time from column address strobe     |      | 100               |      | 135      |      | 165   | ns    | 12-13 |

| toff             | Output buffer turn-off delay               |      | 40                |      | 50       |      | 60    | ns    |       |

| t <sub>RP</sub>  | Row address strobe precharge time          | 100  |                   | 120  |          | 120  | _     | ns    |       |

| <sup>t</sup> RAS | Row address strobe pulse width             | 150  | 10000             | 200  | 10000    | 250  | 10000 | ns    |       |

| tRSH             | Row address strobe hold time               | 100  |                   | 135  |          | 165  |       | ns    |       |

| tCAS             | Column address strobe pulse width          | 100  |                   | 135  |          | 165  |       | ns    |       |

| <sup>t</sup> csн | Column address strobe hold time            | 150  |                   | 200  |          | 250  |       | ns    |       |

| tRCD             | Row to column strobe delay                 | 20   | 50                | 25   | 65       | 35   | 85    | ns    | 14    |

| tASR             | Row address set-up time                    | 0    |                   | 0    |          | 0    |       | ns    |       |

| tRAH             | Row address hold time                      | 20   |                   | 25   |          | 35   |       | ns    |       |

| tASC             | Column address set-up time                 | -10  |                   | -10  |          | -10  |       | ns    |       |

| <sup>t</sup> CAH | Column address hold time                   | 45   |                   | 55   |          | 75   |       | ns    |       |

| <sup>t</sup> AR  | Column address hold time referenced to RAS | 95   |                   | 120  |          | 160  |       | ns    |       |

| tcsc             | Chip select set-up time                    | -10  |                   | -10  |          | -10  |       | ns    |       |

| <sup>t</sup> СН  | Chip select hold time                      | 45   |                   | 55   |          | 75   |       | ns    |       |

| tchr             | Chip select hold time referenced to RAS    | 95   |                   | 120  |          | 160  |       | ns    |       |

| t <sub>T</sub>   | Transition time (rise and fall)            | 3    | 35                | 5    | 50       | 5    | 50    | ns    | 15    |

| tRCS             | Read command set-up time                   | 0    |                   | 0    |          | 0    |       | ns    |       |

| tRCH             | Read command hold time                     | 0    |                   | 0    |          | 0    |       | ns    |       |

| <sup>t</sup> wch | Write command hold time                    | 45   |                   | 55   |          | 75   |       | ns    |       |

| twcr             | Write command hold time referenced to RAS  | 95   |                   | 120  |          | 160  |       | ns    |       |

| twp              | Write command pulse width                  | 45   |                   | 55   |          | 75   |       | ns    |       |

| <sup>t</sup> RWL | Write command to row strobe lead time      | 50   |                   | 70   |          | 85   |       | ns    |       |

| <sup>t</sup> cw∟ | Write command to column strobe lead time   | 50   |                   | 70   |          | 85   |       | ns    |       |

| tDS              | Data in set-up time                        | 0    |                   | 0    |          | 0    |       | ns    | 16    |

|                  |                                     |          |      | Ту       | pes  |          |      |      |       |

|------------------|-------------------------------------|----------|------|----------|------|----------|------|------|-------|

|                  | Parameter                           | M 4027-2 |      | M 4027-3 |      | M 4027-4 |      | Unit | Notes |

|                  |                                     | Min.     | Max. | Min.     | Max. | Min.     | Max. |      |       |

| t <sub>DH</sub>  | Data in hold-time                   | 45       |      | 55       |      | 75       |      | ns   | 16    |

| <sup>t</sup> DHR | Data in hold time referenced to RAS | 95       |      | 120      |      | 160      |      | ns   |       |

| t <sub>CRP</sub> | Column to row strobe precharge time | 0        |      | 0        |      | 0        |      | ns   |       |

| t <sub>CP</sub>  | Column precharge time               | 60       |      | 80       |      | 110      |      | ns   |       |

| tRFSH            | Refresh period                      |          | 2    |          | 2    |          | 2    | ms   |       |

| twcs             | Write command set-up time           | 0        |      | 0        |      | 0        |      | ns   | 17    |

| tcwD             | CAS to WRITE delay                  | 60       |      | 80       |      | 90       |      | ns   | 17    |

| tRWD             | RAS to WRITE delay                  | 110      |      | 145      |      | 175      |      | ns   | 17    |

| t <sub>DOH</sub> | Data out hold time                  | 10       |      | 10       |      | 10       |      | μs   |       |

#### AC CHARACTERISTICS AND RECOMMENDED OPERATING CONDITIONS (cont.)

#### **CAPACITANCES** ( $T_{amb} = 0$ to 70°C, $V_{DD} = 12V \pm 10\%$ ; $V_{SS} = 0V$ ; $V_{BB} = -5.7$ to -4.5V)

|                 | Parameter                                                                            | Va   | lues | Unit | Notes |

|-----------------|--------------------------------------------------------------------------------------|------|------|------|-------|

|                 |                                                                                      | Тур. | Max. |      |       |

| C11             | Input capacitance (A <sub>0</sub> -A <sub>5</sub> ), D <sub>IN</sub> , <del>CS</del> | 4    | 5    | pF   | 18    |

| C <sub>12</sub> | Input capacitance RAS, CAS, WRITE                                                    | 8    | 10   | pF   | 18    |

| Co              | Output capacitance (D <sub>OUT</sub> )                                               | 5    | 7    | pF   | 8-18  |

1. Several cycles are required after power-up before proper device operation is achieved. Any 8 cycles which perform refresh are adequate for this purpose.

2.All voltages referenced to V<sub>SS</sub>. V<sub>BB</sub> must be applied before and removed after other supply voltages.

3.Output voltage will swing from V<sub>SS</sub> to V<sub>CC</sub> when enabled, with no output load. For purposes of maintaining data in standby mode, V<sub>CC</sub> may be reduced to V<sub>SS</sub> without affecting refresh operations or data retention. However, the V<sub>OH</sub> (min) specification is not guaranteed in this mode.

4. This manifold for operation at forguarantee to the point to the point (min). Operation at history with reduced to the point of the point of

4.T<sub>amb</sub> is specified for operation at frequencies to  $t_{RC} \ge t_{RC}$  (min). Operation at higher cycle rates with reduced ambient temperatures and higher power dissipation is permissible provided that all AC parameters are met.

5. Current is proportional to cycle rate.  $I_{DD1}$  (max) is measured at the cycle rate specified by  $t_{RC}$  (min).

6.1<sub>CC</sub> depends on output loading. The V<sub>CC</sub> supply is connected to the output buffer only. 7.All device pins at 0 volts except  $V_{BB}$  which is at -5<u>V</u> and the pin under test which is at +10V.

8. Output is disabled (high-impedance) and RAS and CAS are both at a logic 1. Transient stabilization is required prior to measurement of this parameter.

9.0V ≤ V<sub>out</sub> ≤ +10V.

10.AC measurements assume t<sub>T</sub>= 5 ns.

- 11. Assumes that  $t_{RCD} \le t_{RCD}$  (max). 12. Assumes that  $t_{RCD} \ge t_{RCD}$  (max).

- 13. Measured with a load circuit equivalent to 2 TTL loads and 100 pF.

- 14.Operation within the  $t_{RCD}$  (max) limit insures that  $t_{RAC}$  (max) can be met.  $t_{RCD}$  (max) is specified as a reference point only; if t<sub>RCD</sub> is greater than the specified t<sub>RCD</sub> (max) limit, then access time is controlled exclusively by t<sub>CAC</sub>.

15. V<sub>IHC</sub> (min) or V<sub>IH</sub> (min) and V<sub>IL</sub> (max) are reference levels for measuring timing of input signals. Also, transition times are measured between V<sub>IHC</sub> or V<sub>IH</sub> and V<sub>IL</sub>.

16. These parameters are referenced to CAS leading edge in random write cycles and to WRITE leading edge in delayed

- write or read-modify-write cycles.

- 17.twcs, t<sub>CWD</sub>, and t<sub>RWD</sub> are restrictive operating parameters in a read/write or read/modify/write cycle only. If twcs > twcs (min), the cycle is an early write cycle and Data Out will contain the data written into the selected cell. If t<sub>CWD</sub> > t<sub>CWD</sub> (min) and t<sub>RWD</sub> > t<sub>RWD</sub> (min), the cycle is a read-write cycle and Data Out will contain data read from the selected cell. If neither of the above sets of conditions is satisfied, the condition of Data Out (at access time) is indeterminate.

access time) is indeterminate. **18.** Effective capacitance is calculated from the equation:  $C = \frac{\Delta Q}{\Delta V}$  with  $\Delta V = 3$  volts.

## M 4027

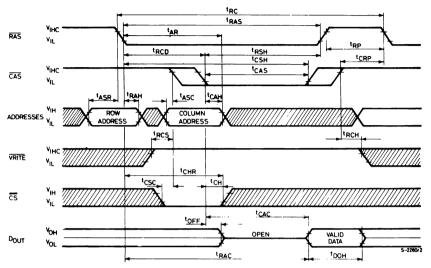

**READ CYCLE**

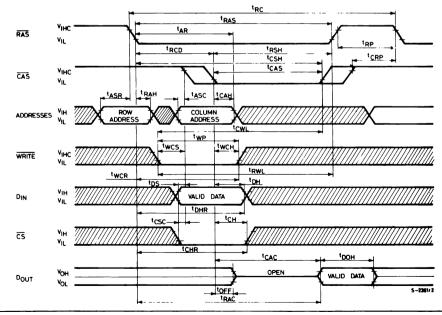

### WRITE CYCLE (early write)

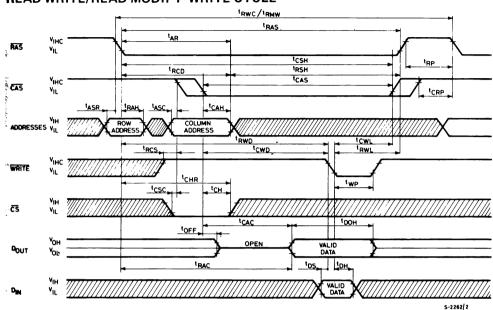

### **READ WRITE/READ MODIFY-WRITE CYCLE**

į.

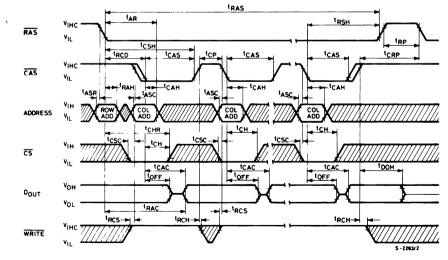

## PAGE MODE READ CYCLE

## **M** 4027

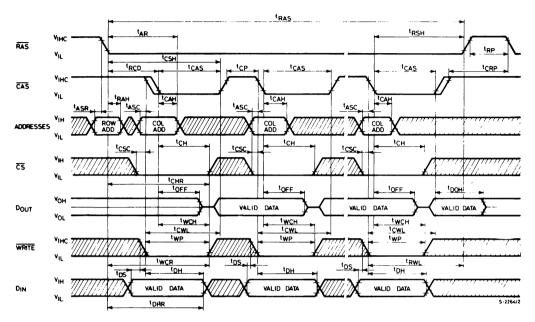

PAGE MODE WRITE CYCLE

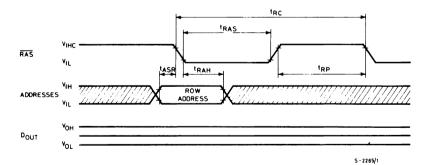

**RAS** ONLY REFRESH CYCLE

## ADDRESSING

The 12 address bits required to decode one of 4096 cell locations within the M 4027 are multiplexed onto the 6 address inputs and latched into the on-chip row and column address latches.

Row Address Strobe (RAS) latches the six row address bits onto the chip. Column Address Strobe  $\overline{(CAS)}$  latches the six column address bits plus Chip Select ( $\overline{CS}$ ) onto the chip.

Since the internal circuitry allows the columns information to be externally applied to the chip before it is actually required, the hold time requirements for column address and CS are also referenced to RAS. However this gated CAS feature allows the systems designer to compensate for timing skews that may be encountered in the multiplexing operation.

Since the Chip Select signal is not required until  $\overline{CAS}$  time, which is well into the memory cycle, its decoding time does not add to system access or cycle time.

Additional timing margin is gained because column address is not required until CAS makes its negative transition.

The timing is further simplified by the positive transition of CAS not being referenced to the positive transition of RAS. In fact, CAS need not go HIGH until the beginning of the next cycle.

## DATA INPUT/OUTPUT

Data to be written into selected storage cell of the memory chip is first stored in the on-chip data latch. The gating of this latch is performed with a combination of WRITE and CAS while RAS is active.

The later of this signals (WRITE or  $\overline{CAS}$ ) to make its negative transition is the strobe for the Data In into the latch. This permits several options in the write cycle timing. In a write cycle, if the WRITE input is activated prior to  $\overline{CAS}$ , the Data In is strobe by  $\overline{CAS}$ , and set-up time and hold time are referenced to CAS. If the Data In input is not available at CAS time or the cycle is a read-write or readmodify-write, the WRITE signal must be delayed until after CAS. In this "delayed write cycle" the data input set-up and hold times are referenced to the negative edge of WRITE rather than to CAS. (To illustrate this feature, Data In is referenced to WRITE in the timing diagram depicting the read-write and page mode write cycles while the "early write" cycle diagram shows Data In referenced to CAS) Note that if the chip is unselected (CS high at CAS time) WRITE commands are not executed and, consequently, data stored in the memory is unaffected. Data is retrieved from the memory in read cycle by maintaining WRITE in the inactive or high state throughout the portion of memory cycle in which CAS is active. Data read from the selected cell will be available at the output within the specified access time.

## DATA OUTPUT CONTROL

At the beginning of a memory cycle, the state of the Data Out latch and buffer depend on the previous memory cycle.

Changes in the condition of Data Out latch are initiated by CAS. The negative transition of CAS causes the Data Output  $(D_{OUT})$  to unconditionally go to its open-circuit state. If will remain open-circuited until after the access  $D_{OUT}$  time, the will assume the proper state for the type of cycle performed.

If the cycle is a read; read-modify-write, or a delayed write and the chip is selected, then the  $D_{OUT}$ latch and buffer will contain the data from the selected cell. This output data is the same polarity (not inverted) as the input data. If the cycle is a write cycle (WRITE active low before CAS goes low) and the chip is selected, then DOUT will contain the input data.

Once the  $D_{OUT}$  goes active, it will remain active until the next negative transition of  $\overline{CAS}$ .

If the cycle is a CAS only cycle (no RAS signal), then  $D_{OUT}$  will assume the open - circuit state. The same istrue for normal cycles (both RAS and CAS present-when the chip is unselected  $D_{OUT}$ remains in the open-circuit state until the next negative transition of CAS.

**RAS** only refresh cycles (no  $\overline{CAS}$ ) have no effect on the D<sub>OUT</sub>.

However, when RAS only refresh cycles are continued for extended periods of time, DOUT may eventually go open-circuit.

If the chip unselected, it will not accept a write command and the  $D_{OUT}$  will remain in the open-circuit state.

### INPUT/OUTPUT LEVELS

All inputs, including the two address strobes, interface directly with TTL.

The high-impedance, low-capacitance input characteristics simplify input driver selection by allowing use of standard logic elements rather than specially designed driver elements.

The 3-state output buffer is a low impedance to  $V_{CC}$  for a logic "1" and a low impedance to  $V_{SS}$  for a logic "0".

The output resistance to V<sub>CC</sub> (logic "1" state) is 420 ohm maximum and 135 ohm tipically.

The output resistance to V<sub>SS</sub> (logic "0" state) is 125 ohm maximum and 35 ohm tipically.

The separate  $V_{CC}$  pin allows the output buffer to be powered from supply voltage of the logic to which chip is interfaced.

During battery stand-by operation, the  $V_{CC}$  pin may be unpowered without effecting the M 4027 refresh operation.

This allows all system logic, except RAS timing circuitry and refresh address logic, to be turned off during battery stand-by to save power.

#### REFRESH

Refresh of the dynamic cell matrix is accomplished by performing a memory cycle at each of the 64 row address every two millisecond or less.

Any cycle in which a  $\overline{RAS}$  signal occurs, accomplished a refresh operation. A read cycle will refresh the selected row, regardless of the state of the Chip Select ( $\overline{CS}$ ) input.

A write or read-modify-write cycle also refreshes the selected row, but the chip should be unselected to prevent writing data into the selected cell.

If, during a refresh cycle, the M 4027 receives a  $\overline{RAS}$  signal but no  $\overline{CAS}$  signal, the state of the output will not be affected. However, if " $\overline{RAS}$ -only" refresh cycles (when  $\overline{RAS}$  is the only signal applied to the chip) are contained for extended periods, the output buffer may eventually lose proper data and go open-circuit.

The output buffer will regain activity with the first cycle in which a CAS signal is applied to the chip.

#### POWER DISSIPATION/STANDBY MODE

Most of the circuitry used in the M 4027 and most of the power drawn is the result of an address strobe edge. Because the power is not drawn during the time the strobe is active, the dynamic power is a function of operating frequency rather than active duty cycle.

Tipically, the power is 170 mW at 1  $\mu$ sec cycle rate for M 4027 with a worse case power of less than 470 mW at 320  $\mu$ sec cycle time.

To reduce the overall system power, the Row Address Strobe (RAS) should be decoded and supplied to only the selected chips.

The  $\overline{CAS}$  must be supplied to all chips (to turn off the unselected output).

Those chips that did not receive a RAS, however, will not dissipate any power on the CAS edges, except for that required to turn off the outputs.

If the  $\overline{RAS}$  signal is decoded and supplied only the selected chips, then the chip select ( $\overline{CS}$ ) input of all chips can be at a logic 0.

Then chips that receive a CAS but no RAS will be unselected (output open-circuited) regardless of the Chip Select input.

For refresh cycles, however, either the  $\overline{\text{CS}}$  input for all chips must be high or the  $\overline{\text{CAS}}$  input must be held high to prevent several "wire-OR" outputs from turning on with opposing force. Note that the M 4027 will dissipate considerably less power when the refresh operation is accomplished with a "RAS-only" cycle as opposed to a normal RAS/CAS memory cycle.

#### PAGE MODE OPERATION

The "Page mode" feature of the M 4027 allows for successive memory operations at multiple column location of the same row address with increased speed without an increase in power.

This is done by strobing the row address into the chip and keeping the RAS signal at logic 0 throughout all successive memory cycles in which the row address is common.

This "Page Mode" of operation will not dissipate the power associated with the negative going edge of RAS. The time required for strobing in a new row address is eliminated, thereby decreasing the access and cycle times. The chip select input  $(\overline{CS})$  is operative in page made cycles just as in normal cycles. It is not necessary that the chip be selected during the first operation in sequence of page cycles. Likewise, the  $\overline{CS}$  input can be used to select or disable any cycle(s) in a series of page cycles.

This feature allows the page boundary to be extended beyond the 64 column location in a single chip. The page boundary can be extended by applying RAS to multiple 4K memory blocks and deconding CS to select the proper block.

#### POWER UP

A Distant

The M 4027 requires no particular power supply sequencing so long as the Absolute Maximum Rating Conditions are observed. However, in order to insure compliance with the Absolute Maximum Ratings, SGS-ATES recommends sequencing of power supplies such that  $V_{BB}$  is applied first and removed last.  $V_{BB}$  should never be more positive than  $V_{SS}$  when power is applied to  $V_{DD}$ .

Under system failure condiction in which one or more supplied exceed the specified limits significant additional margin against catastrophic device failure may be achieved by forcing RAS and Data Out to the inactive state. After power is applied to the device, the M 4027 requires several cycles before proper device operation is achieved.

Any 8 cycles which perform refresh are adequate for this purpose.