## **Revision History:**

Revision 1.0 (Oct. 31, 2006)

- Original

Revision 1.1 (Dec. 29, 2006)

- Add -6 spec

Revision 1.2 (Mar. 02, 2007)

- Modify VOH and VOL- Delete BGA ball name of packing dimensions

Revision 1.3 (May. 14,2007)

- Modify tSS (1.5ns => 2ns) and tSH(1ns => 1.5ns)

Revision 1.4 (Jul. 10,2007)

- Modify type error

Publication Date: Jul. 2007 Revision: 1.4 1/29

## **SDRAM**

## 512K x 32Bit x 2Banks

# Synchronous DRAM

#### **FEATURES**

- 2.5V power supply

- LVCMOS compatible with multiplexed address

- Dual banks operation

- MRS cycle with address key programs

- CAS Latency (1, 2 & 3)

- Burst Length (1, 2, 4, 8 & full page)

- Burst Type (Sequential & Interleave)

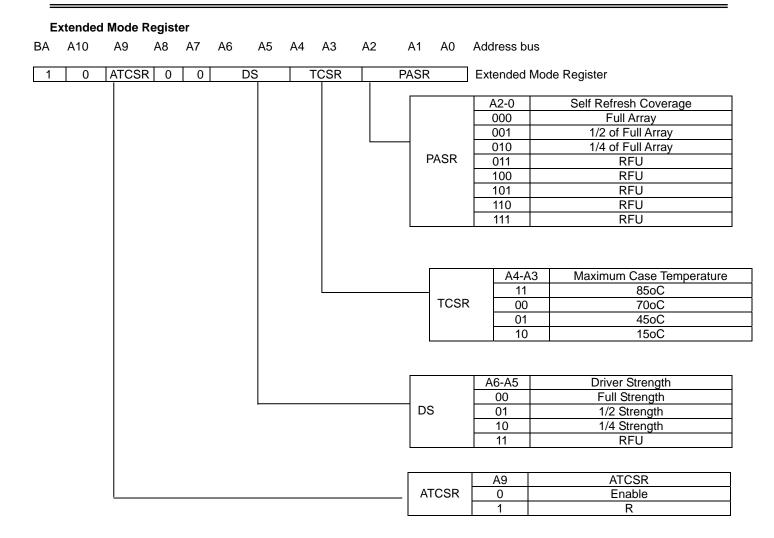

- EMRS cycle with address key programs.

- All inputs are sampled at the positive going edge of the system clock

- Burst Read Single-bit Write operation

- Special Function Support.

- PASR (Partial Array Self Refresh )

- TCSR (Temperature compensated Self Refresh)

- DS (Driver Strength)

- DQM for masking

- Auto & self refresh

- 64ms refresh period (4K cycle)

### **GENERAL DESCRIPTION**

The M52S32321A is 33,554,432 bits synchronous high data rate Dynamic RAM organized as 2 x 524,288 words by 32 bits, fabricated with high performance CMOS technology. Synchronous design allows precise cycle control with the use of system clock I/O transactions are possible on every clock cycle. Range of operating frequencies, programmable burst length and programmable latencies allow the same device to be useful for a variety of high bandwidth, high performance memory system applications.

### **ORDERING INFORMATION**

| Part NO.          | MAX<br>Freq. | Package       | Comments |

|-------------------|--------------|---------------|----------|

| M52S32321A -10BG  | 100MHz       | 90 Ball VFBGA | Pb-free  |

| M52S32321A -7.5BG | 133MHz       | 90 Ball VFBGA | Pb-free  |

| M52S32321A -6BG   | 166MHz       | 90 Ball VFBGA | Pb-free  |

## **PIN CONFIGURATION (TOP VIEW)**

#### 90 Ball FBGA

|   | 1    | 2    | 3    | 4 | 5 | 6 | 7    | 8    | 9    |

|---|------|------|------|---|---|---|------|------|------|

| Α | DQ26 | DQ24 | vss  |   |   |   | VDD  | DQ23 | DQ21 |

| В | DQ28 | VDDQ | VSSQ |   |   |   | VDDQ | VSSQ | DQ19 |

| С | VSSQ | DQ27 | DQ25 |   |   |   | DQ22 | DQ20 | VDDQ |

| D | VSSQ | DQ29 | DQ30 |   |   |   | DQ17 | DQ18 | VDDQ |

| E | VDDQ | DQ31 | NC   |   |   |   | NC   | DQ16 | VSSQ |

| F | VSS  | DQM3 | А3   |   |   |   | A2   | DQM2 | VDD  |

| G | A4   | A5   | A6   |   |   |   | A10  | A0   | A1   |

| Н | A7   | A8   | NC   |   |   |   | NC   | NC   | NC   |

| J | CLK  | CKE  | A9   |   |   |   | ВА   | cs   | RAS  |

| K | DQM1 | NC   | NC   |   |   |   | CAS  | WE   | DQM0 |

| L | VDDQ | DQ8  | VSS  |   |   |   | VDD  | DQ7  | VSSQ |

| М | VSSQ | DQ10 | DQ9  |   |   |   | DQ6  | DQ5  | VDDQ |

| N | VSSQ | DQ12 | DQ14 |   |   |   | DQ1  | DQ3  | VDDQ |

| Р | DQ11 | VDDQ | VSSQ |   |   |   | VDDQ | VSSQ | DQ4  |

| R | DQ13 | DQ15 | VSS  |   |   |   | VDD  | DQ0  | DQ2  |

Publication Date: Jul. 2007 Revision: 1.4 2/29

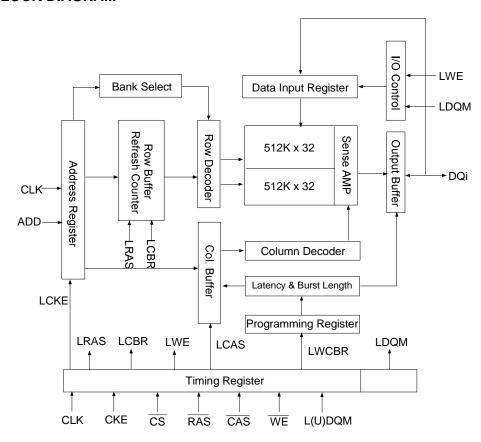

### **FUNCTIONAL BLOCK DIAGRAM**

## **PIN FUNCTION DESCRIPTION**

| Pin           | Name                     | Input Function                                                                                                                                                                      |

|---------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK           | System Clock             | Active on the positive going edge to sample all inputs.                                                                                                                             |

| <del>CS</del> | Chip Select              | Disables or enables device operation by masking or enabling all inputs except CLK, CKE and L(U)DQM.                                                                                 |

| CKE           | Clock Enable             | Masks system clock to freeze operation from the next clock cycle.  CKE should be enabled at least one cycle prior to new command.  Disable input buffers for power down in standby. |

| A0 ~ A10      | Address                  | Row / column addresses are multiplexed on the same pins. Row address: RA0 ~ RA10, column address: CA0 ~ CA7                                                                         |

| BA            | Bank Select Address      | Selects bank to be activated during row address latch time.  Selects bank for read/write during column address latch time.                                                          |

| RAS           | Row Address Strobe       | Latches row addresses on the positive going edge of the CLK with $\overline{RAS}$ low. Enables row access & precharge.                                                              |

| CAS           | Column Address Strobe    | Latches column addresses on the positive going edge of the CLK with CAS low.  Enables column access.                                                                                |

| WE            | Write Enable             | Enables write operation and row precharge.  Latches data in starting from CAS, WE active.                                                                                           |

| L(U)DQM       | Data Input / Output Mask | Makes data output Hi-Z, tSHZ after the clock and masks the output.  Blocks data input when L(U)DQM active.                                                                          |

Publication Date: Jul. 2007 Revision: 1.4 3/29

| DQ0 ~ 31  | Data Input / Output                       | Data inputs/outputs are multiplexed on the same pins.                                       |

|-----------|-------------------------------------------|---------------------------------------------------------------------------------------------|

| VDD/VSS   | Power Supply/Ground                       | Power and ground for the input buffers and the core logic.                                  |

| VDDQ/VSSQ | Data Output Power/Ground                  | Isolated power supply and ground for the output buffers to provide improved noise immunity. |

| N.C/RFU   | No Connection/<br>Reserved for Future Use | This pin is recommended to be left No Connection on the device.                             |

### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                             | Symbol   | Value              | Unit |

|---------------------------------------|----------|--------------------|------|

| Voltage on any pin relative to Vss    | VIN,VOUT | -1.0 ~ 3.6         | V    |

| Voltage on VDD supply relative to Vss | Vdd,Vddq | -1.0 ~ 3.6         | V    |

| Storage temperature                   | Тѕтс     | -55 ~ <b>+</b> 150 | °C   |

| Power dissipation                     | Po       | 0.7                | W    |

| Short circuit current                 | los      | 50                 | MA   |

Note: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded.

Functional operation should be restricted to recommended operating condition.

Exposure to higher than recommended voltage for extended periods of time could affect device reliability.

### **DC OPERATING CONDITIONS**

Recommended operating conditions (Voltage referenced to Vss = 0V, TA= 0  $^{\circ}$ C ~ 70  $^{\circ}$ C )

| Parameter                 | Symbol    | Min        | Тур | Max      | Unit | Note        |

|---------------------------|-----------|------------|-----|----------|------|-------------|

| Supply voltage            | VDD, VDDQ | 2.3        | 2.5 | 2.7      | V    |             |

| Input logic high voltage  | Vih       | 0.8 x VDDQ | 2.5 | VDDQ+0.3 | V    | 1           |

| Input logic low voltage   | VIL       | -0.3       | 0   | 0.3      | V    | 2           |

| Output logic high voltage | Voн       | VDDQ -0.2  | -   | -        | V    | Iон =-0.1mA |

| Output logic low voltage  | Vol       | -          | -   | 0.2      | V    | IoL = 0.1mA |

| Input leakage current     | lı∟       | -5         | -   | 5        | uA   | 3           |

| Output leakage current    | lol       | -5         | -   | 5        | uA   | 4           |

**Note:** 1.ViH (max) = 3.0V AC for pulse width  $\leq$  3ns acceptable.

2.V<sub>IL</sub> (min) = -1.0V AC for pulse width  $\leq$  3ns acceptable.

3.Any input  $0V \le V_{IN} \le V_{DDQ} + 0.3V$ , all other pins are not under test = 0V.

4.Dout is disabled,  $0V \le V_{OUT} \le V_{DDQ}$ .

## **CAPACITANCE** (VDD = 2.5V, TA = $25 \,^{\circ}$ C , f = 1MHz)

| Pin                               | Symbol | Min | Max | Unit |

|-----------------------------------|--------|-----|-----|------|

| CLOCK                             | Cclk   | -   | 4.0 | pF   |

| RAS, CAS, WE, CS, CKE, LDQM, UDQM | Cin    | -   | 4.0 | pF   |

| ADDRESS                           | CADD   | -   | 4.0 | pF   |

| DQ0 ~DQ31                         | Соит   | -   | 6.0 | pF   |

Publication Date: Jul. 2007 Revision: 1.4 4/29

### **DC CHARACTERISTICS**

(Recommended operating condition unless otherwise noted,  $T_A = 0 \, ^{\circ}C \sim 70 \, ^{\circ}C$ )

|                                          |        | Total Occupied                                                                                              |                                                                                                                                                                      | CAS      |     | Version | n   |      |      |

|------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----|---------|-----|------|------|

| Parameter                                | Symbol | Test Condition                                                                                              |                                                                                                                                                                      | Latency  | -6  | -7.5    | -10 | Unit | Note |

| Operating Current<br>(One Bank Active)   | Icc1   | Burst Length = 1<br>trc≥ trc (min), tcc≥ tcc (min)                                                          | , lot= 0                                                                                                                                                             | )mA      | 100 | 80      | 60  | mA   | 1    |

| Precharge Standby                        | ICC2P  | CKE ≤ Vı∟(max), tcc =15ns                                                                                   |                                                                                                                                                                      |          | 0.3 |         |     | mA   |      |

| Current in power-down mode               | ICC2PS | CKE ≤ VIL(max), CLK ≤ VIL(max                                                                               | ), tcc =                                                                                                                                                             | · ∞      |     | 0.2     |     | mA   |      |

| Precharge Standby Current in non         | ICC2N  | CKE ≥ V <sub>IH</sub> (min),  CS ≥ V <sub>IH</sub> (min)<br>Input signals are changed one                   |                                                                                                                                                                      | 9        |     | mA      |     |      |      |

| power-down mode                          | Icc2NS | CKE $\geq$ V <sub>IH</sub> (min), CLK $\leq$ V <sub>IL</sub> (max), tcc = $\infty$ Input signals are stable |                                                                                                                                                                      | $\infty$ | 8   |         |     | mA   |      |

| Active Standby Current                   | Іссзр  | $CKE \le V_{IL}(max), tcc = 15ns$ 2mA $CKE \le V_{IL}(max), CLK \le V_{IL}(max), tcc = \infty$ 1.5          |                                                                                                                                                                      |          |     |         |     |      |      |

| in power-down mode                       | Іссзрѕ | CKE ≤ VIL(max), CLK≤ VIL(r                                                                                  | $CKE \leq V_{IL}(max), CLK \leq V_{IL}(max), tcc = \infty$                                                                                                           |          |     |         | 1.5 |      |      |

| Active Standby Current in non power-down | Іссзи  |                                                                                                             | $KE \le VIL(max)$ , $CLK \le VIL(max)$ , $tcc = \infty$ $KE \ge VIH(min)$ , $\overline{CS} \ge VIH(min)$ , $tcc=15$ ns uput signals are changed one time during 30ns |          |     |         | 15  |      |      |

| mode<br>(One Bank Active)                | Іссзиѕ | CKE ≥ V <sub>IH</sub> (min), CLK ≤ V <sub>IL</sub> (max<br>Input signals are stable                         | (), tcc=                                                                                                                                                             | ∞        |     | 8       |     | mA   |      |

| Operating Current<br>(Burst Mode)        | Icc4   | IoL= 0Ma, Page Burst<br>All Band Activated, tCCD = tCC                                                      | D (mir                                                                                                                                                               | n)       | 100 | 80      | 60  | mA   | 1    |

| Refresh Current                          | Icc5   | trc≥trc(min)                                                                                                |                                                                                                                                                                      |          | 40  | 40      | 40  | mA   | 2    |

|                                          |        |                                                                                                             | TCS                                                                                                                                                                  | SR range | 45  |         | 70  | °C   |      |

| Self Refresh Current                     | Icc6   | CKE≤0.2V                                                                                                    |                                                                                                                                                                      | Banks    | 180 |         | 200 | uA   |      |

|                                          |        |                                                                                                             | 1                                                                                                                                                                    | Bank     | 160 |         | 180 |      |      |

| Deep Power Down<br>Current               | Ісст   | CKE≤0.2V                                                                                                    |                                                                                                                                                                      |          |     | 15      |     | uA   |      |

Note: 1.Measured with outputs open. Addresses are changed only one time during tcc(min).

Publication Date: Jul. 2007 Revision: 1.4 5/29

<sup>2.</sup>Refresh period is 64ms. Addresses are changed only one time during tcc(min).

### AC OPERATING TEST CONDITIONS (VDD= $2.5V \pm 0.2V$ , TA= $0 \, ^{\circ}C \sim 70 \, ^{\circ}C$ )

| Parameter                                 | Value            | Unit |

|-------------------------------------------|------------------|------|

| Input levels (Vih/Vil)                    | 0.9 x VDDQ / 0.2 | V    |

| Input timing measurement reference level  | 0.5 x Vddq       | V    |

| Input rise and fall time                  | tr / tf = 1 / 1  | ns   |

| Output timing measurement reference level | 0.5 x Vddq       | V    |

| Output load condition                     | See Fig.2        |      |

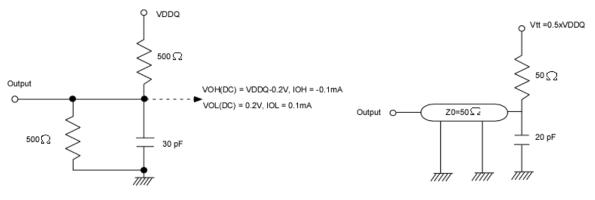

(Fig.1) DC Output Load circuit

(Fig.2) AC Output Load Circuit

#### **OPERATING AC PARAMETER**

(AC operating conditions unless otherwise noted)

| Parameter                              | Symbol        |       | Version | Unit  | Note       |      |

|----------------------------------------|---------------|-------|---------|-------|------------|------|

| Farameter                              | Symbol        | -6    | -7.5    | -10   | Onit       | Note |

| Row active to row active delay         | trrd(min)     | 12    | 15      | 20    | ns         | 1    |

| RAS to CAS delay                       | trcd(min)     | 18    | 22.5    | 30    | ns         | 1    |

| Row precharge time                     | trp(min)      | 18    | 22.5    | 30    | ns         | 1    |

| Row active time                        | tras(min)     | 36 45 |         | 45 50 |            | 1    |

| Now active time                        | tras(max)     |       | 100     |       | ns 1<br>us |      |

| Row cycle time                         | trc(min)      | 54    | 67.5    | 90    | ns         | 1    |

| Last data in to new col. Address delay | tcdl(min)     |       | 1       | •     | CLK        | 2    |

| Last data in to row precharge          | trdl(min)     |       | 2       |       | CLK        | 2    |

| Last data in to burst stop             | tBDL(min)     |       | 1       |       | CLK        | 2    |

| Col. Address to col. Address delay     | tccp(min)     |       | 1       |       | CLK        | 3    |

| Number of valid output data            | CAS latency=3 | 2     |         |       | ea         | 4    |

| ivallibel of valid output data         | CAS latency=2 |       | 1       |       | - Ga       | 4    |

**Note:** 1. The minimum number of clock cycles is determined by dividing the minimum time required with clock cycle time and then rounding off to the next higher integer.

- 2. Minimum delay is required to complete write.

- 3. All parts allow every cycle column address change.

- 4. In case of row precharge interrupt, auto precharge and read burst stop.

The earliest a precharge command can be issued after a Read command without the loss of data is CL+BL-2 clocks.

Publication Date: Jul. 2007 Revision: 1.4 6/29

## AC CHARACTERISTICS (AC operating conditions unless otherwise noted)

| Dow              | ameter                 | Symbol | -   | 6    | -7.5 |      | -10 |      | Unit | Note |

|------------------|------------------------|--------|-----|------|------|------|-----|------|------|------|

| Para             | ameter                 | Зушьы  | Min | Max  | Min  | Max  | Min | Max  | Unit | Note |

| CLK cycle time   | CAS Latency =3         | tcc    | 6   | 1000 | 7.5  | 1000 | 9   | 1000 | ns   | 1    |

| CLK Cycle time   | CAS Latency =2         | icc    | 10  | 1000 | 12   | 1000 | 15  | 1000 | 115  | '    |

| CLK to valid     | CAS Latency =3         | tsac   | -   | 5.5  | -    | 7    | -   | 8    | ns   | 1    |

| output delay     | CAS Latency =2         | ISAC   | -   | 10   | •    | 10   |     | 10   | 115  | 1    |

| Output data hold | time                   | tон    | 2.0 | -    | 2.0  | -    | 2.0 | -    | ns   | 2    |

| CLK high pulse v | CLK high pulse width   |        | 2.0 | -    | 2.5  | -    | 2.5 | -    | ns   | 3    |

| CLK low pulse w  | idth                   | tcL    | 2.0 | -    | 2.5  | -    | 2.5 | -    | ns   | 3    |

| Input setup time |                        | tss    | 2.0 | -    | 2.0  | -    | 2.0 | -    | ns   | 3    |

| Input hold time  |                        | tsн    | 1.5 | -    | 1.5  | -    | 1.5 | -    | ns   | 3    |

| CLK to output in | CLK to output in Low-Z |        | 1   | -    | 1    | -    | 1   | -    | ns   | 2    |

| CLK to output in | CAS Latency =3         | tsHz   | -   | 5    | -    | 6    | -   | 7    | 200  |      |

| Hi-Z             | CAS Latency =2         | I ISHZ | -   | 8    | -    | 9    | -   | 10   | ns   | -    |

\*All AC parameters are measured from half to half.

Note: 1. Parameters depend on programmed CAS latency.

- 2.If clock rising time is longer than 1ns,(tr/2-0.5)ns should be added to the parameter.

- 3. Assumed input rise and fall time (tr & tf)=1ns.

If tr & tf is longer than 1ns, transient time compensation should be considered, i.e., [(tr+ tf)/2-1]ns should be added to the parameter.

Publication Date: Jul. 2007 Revision: 1.4 **7/29**

### MODE REGISTER FIELD TABLE TO PROGRAM MODES

### Register Programmed with MRS

| Address  | BA | A10/AP | A9    | A8 | A7 | A6 | A5     | A4  | А3 | A2 | A1      | A0  |

|----------|----|--------|-------|----|----|----|--------|-----|----|----|---------|-----|

| Function | 0  | RFU    | W.B.L | Т  | М  | CA | S Late | ncy | ВТ | Bu | rst Len | gth |

| Test Mode |    |                   | CAS Latency |    |    | Burst Type |    | Burst Length |    |    |    |           |          |

|-----------|----|-------------------|-------------|----|----|------------|----|--------------|----|----|----|-----------|----------|

| A8        | A7 | Туре              | A6          | A5 | A4 | Latency    | А3 | Туре         | A2 | A1 | A0 | BT = 0    | BT = 1   |

| 0         | 0  | Mode Register Set | 0           | 0  | 0  | Reserved   | 0  | Sequential   | 0  | 0  | 0  | 1         | 1        |

| 0         | 1  | Reserved          | 0           | 0  | 1  | 1          | 1  | Interleave   | 0  | 0  | 1  | 2         | 2        |

| 1         | 0  | Reserved          | 0           | 1  | 0  | 2          |    |              | 0  | 1  | 0  | 4         | 4        |

| 1         | 1  | Reserved          | 0           | 1  | 1  | 3          |    |              | 0  | 1  | 1  | 8         | 8        |

| <b>F</b>  |    |                   | 1           | 0  | 0  | Reserved   |    |              | 1  | 0  | 0  | Reserved  | Reserved |

|           |    |                   | 1           | 0  | 1  | Reserved   |    |              | 1  | 0  | 1  | Reserved  | Reserved |

|           |    |                   | 1           | 1  | 0  | Reserved   |    |              | 1  | 1  | 0  | Reserved  | Reserved |

|           |    |                   | 1           | 1  | 1  | Reserved   |    |              | 1  | 1  | 1  | Full Page | Reserved |

Full Page Length: 256

Publication Date: Jul. 2007 Revision: 1.4 **8/29**

### **TRUTH TABLE (Deep Power Down Mode)**

| COMMAND              | CKEn-1 | CKEn | CS | RAS | CAS | WE | DQM | ВА | A10/AP | A9~A0 |  |

|----------------------|--------|------|----|-----|-----|----|-----|----|--------|-------|--|

| Deep Power Down Mode | Entry  | Н    | L  | L   | Н   | Н  | L   | Х  |        |       |  |

| ·                    | Exit   | L    | Н  | Х   | Х   | Х  | Х   | Х  |        | Х     |  |

(V= Valid, X= Don't Care, H= Logic High , L = Logic Low)

Publication Date: Jul. 2007 Revision: 1.4 9/29

### **Burst Length and Sequence**

(Burst of Two)

| Starting Address<br>(column address A0 binary) | Sequential Addressing<br>Sequence (decimal) | Interleave Addressing<br>Sequence (decimal) |

|------------------------------------------------|---------------------------------------------|---------------------------------------------|

| 0                                              | 0,1                                         | 0,1                                         |

| 1                                              | 1,0                                         | 1,0                                         |

### (Burst of Four)

| Starting Address<br>(column address A1-A0, binary) | Sequential Addressing<br>Sequence (decimal) | Interleave Addressing<br>Sequence (decimal) |

|----------------------------------------------------|---------------------------------------------|---------------------------------------------|

| 00                                                 | 0,1,2,3                                     | 0,1,2,3                                     |

| 01                                                 | 1,2,3,0                                     | 1,0,3,2                                     |

| 10                                                 | 2,3,0,1                                     | 2,3,0,1                                     |

| 11                                                 | 3.0.1.2                                     | 3.2.1.0                                     |

### (Burst of Eight)

| Starting Address               | Sequential Addressing | Interleave Addressing |

|--------------------------------|-----------------------|-----------------------|

| (column address A2-A0, binary) | Sequence (decimal)    | Sequence (decimal)    |

| 000                            | 0,1,2,3,4,5,6,7       | 0,1,2,3,4,5,6,7       |

| 001                            | 1,2,3,4,5,6,7,0       | 1,0,3,2,5,4,7,6       |

| 010                            | 2,3,4,5,6,7,0,1       | 2,3,0,1,6,7,4,5       |

| 011                            | 3,4,5,6,7,0,1,2       | 3,2,1,0,7,6,5,4       |

| 100                            | 4,5,6,7,0,1,2,3       | 4,5,6,7,0,1,2,3       |

| 101                            | 5,6,7,0,1,2,3,4       | 5,4,7,6,1,0,3,2       |

| 110                            | 6,7,0,1,2,3,4,5       | 6,7,4,5,2,3,0,1       |

| 111                            | 7,0,1,2,3,4,5,6       | 7,6,5,4,3,2,1,0       |

Full page burst is an extension of the above tables of Sequential Addressing, with the length being 256 for 1Mx32 device.

### **POWER UP SEQUENCE**

- 1. Apply power and start clock, attempt to maintain CKE= "H", L(U)DQM = "H" and the other pin are NOP condition at the inputs.

- 2. Maintain stable power, stable clock and NOP input condition for a minimum of 200us.

- 3.Issue precharge commands for all banks of the devices.

- 4.Issue 2 or more auto-refresh commands.

- 5.Issue mode register set command to initialize the mode register.

- Cf.)Sequence of 4 & 5 is regardless of the order.

Publication Date: Jul. 2007 Revision: 1.4 10/29

#### **SIMPLIFIED TRUTH TABLE**

| CC                                   | CKEn-1                                       | CKEn       | CS   | RAS | CAS | WE       | DQM | ВА       | A10/AP | A9~A0   | Note  |                   |     |

|--------------------------------------|----------------------------------------------|------------|------|-----|-----|----------|-----|----------|--------|---------|-------|-------------------|-----|

|                                      | Mode Register Set Extended Mode Register Set |            | Н    | Χ   | L   | L        | L   | L        | Х      |         | OP CO | DE                | 1,2 |

| Register                             |                                              |            | H    | Х   | Ш   | Ш        | L   | <b>ا</b> | Х      | OP CODE |       | 1,2               |     |

|                                      | Auto Refresh                                 |            | Н    | Н   | L   | _        | L   | Η        | Х      |         | Х     |                   | 3   |

| Refresh                              |                                              | Entry      | П    | L   | L   |          |     |          | ^      |         | ^     |                   | 3   |

| 110110011                            | Self Refresh                                 | Exit       | L    | Н   | L   | Н        | Н   | Н        | Х      |         | Х     |                   | 3   |

|                                      |                                              | LXII       |      |     | Н   | Χ        | Х   | Х        |        |         |       |                   | 3   |

| Bank Active & Rov                    | v Addr.                                      |            | Н    | X   | L   | L        | Н   | Н        | Х      | V       | Row A |                   |     |

| Read &                               | Auto Precharg                                | ge Disable | Н    | Х   | L   | Н        | L   | Н        | Х      | ٧       | L     | Column<br>Address | 4   |

| Column Address                       | Auto Precharge Enable                        |            |      |     |     |          |     |          |        |         | Н     | (A0~A7)           | 4,5 |

| Write & Column                       | Auto Precharge Disable Auto Precharge Enable |            | Н    | Х   | L   | Н        | L   | L        | Х      | V       | L     | Column            | 4   |

| Address                              |                                              |            | ]    |     |     |          |     | _        |        |         | Н     | Address (A0~A7)   | 4,5 |

| Burst Stop                           |                                              |            | Н    | Χ   | L   | Н        | Н   | L        | Х      |         | Х     | ,                 | 6   |

| Danahanan                            | Bank Selection                               | n          |      | V   |     |          |     |          | V      | V       | L     | V                 | 4   |

| Precharge                            | Both Banks                                   |            | H    | Х   | L   | L        | Н   | L        | Х      | Χ       | Н     | Х                 | 4   |

| Clock Suspend or                     |                                              | Entry      | Н    |     | Τ   | Χ        | Χ   | Χ        | Х      |         |       |                   |     |

| Clock Suspend or<br>Active Power Dow |                                              | Entry      |      | L   | لــ | <b>V</b> | V   | V        |        | X       |       |                   |     |

| Active Fower Dow                     | /11                                          | Exit       | L    | Н   | Χ   | Χ        | Χ   | Χ        | Χ      |         |       |                   |     |

| I                                    |                                              | Entry      | Н    | L   | Н   | Χ        | Χ   | X        | Х      |         |       |                   |     |

| Precharge Power                      | Down Mode                                    | Lilliy     | - 11 |     | L   | Ι        | Н   | Η        | ^      |         | V     |                   |     |

|                                      |                                              | Exit       | L    | Н   | Н   | Χ        | Χ   | X        | Х      |         | Х     |                   |     |

|                                      |                                              | L          | - 11 | L   | V   | V        | V   |          |        |         |       |                   |     |

| DQM                                  |                                              |            | Н    |     |     | Х        |     |          | V      |         | Х     |                   | 7   |

| No Operation Command                 |                                              | Н          | X    | Н   | Χ   | Χ        | Х   | Х        |        | Х       |       |                   |     |

| •                                    |                                              |            | Н    | ^   | L   | Н        | Н   | Н        |        |         |       |                   |     |

| Deep Power Dow                       | Deep Power Down Mode Entry                   |            | Н    | L   | L   | Н        | Н   | L        | Х      |         | Х     |                   |     |

| Exit                                 |                                              |            | L    | Н   | Χ   | Χ        | Χ   | Χ        | Х      |         |       |                   |     |

(V= Valid, X= Don't Care, H= Logic High, L = Logic Low)

#### Note:

1. OP Code: Operation Code

A0~A10, BA: Program keys.(@MRS). BA=0 for MRS and BA=1 for EMRS.

2. MRS/EMRS can be issued only at both banks precharge state.

A new command can be issued after 2 clock cycle of MRS.

3. Auto refresh functions are as same as CBR refresh of DRAM.

The automatical precharge without row precharge command is meant by "Auto". Auto / self refresh can be issued only at both banks precharge state.

4. BA: Bank select address.

If "Low": at read, write, row active and precharge, bank A is selected. If "High": at read, write, row active and precharge, bank B is selected. If A10/AP is "High" at row precharge, BA ignored and both banks are selected.

5. During burst read or write with auto precharge, new read/write command can not be issued.

Another bank read /write command can be issued after the end of burst. New row active of the associated bank can be issued at trp after the end of burst.

- 6. Burst stop command is valid at every burst length.

- 7. DQM sampled at positive going edge of a CLK masks the data-in at the very CLK (Write DQM latency is 0), but makes

Hi-Z state the data-out of 2 CLK cycles after. (Read DQM latency is 2)

Publication Date: Jul. 2007 Revision: 1.4 11/29

## Single Bit Read-Write-Read Cycle (Same Page) @CAS Latency=3, Burst Length=1

:Don't Care

Publication Date: Jul. 2007 Revision: 1.4 12/29

\*Note: 1. All inputs expect CKE & DQM can be don't care when  $\overline{\text{CS}}$  is high at the CLK high going edge.

2. Bank active & read/write are controlled by BA.

| ВА | Active & Read/Write |

|----|---------------------|

| 0  | Bank A              |

| 1  | Bank B              |

3. Enable and disable auto precharge function are controlled by A10/AP in read/write command.

| A10/AP | ВА | Operation                                                    |

|--------|----|--------------------------------------------------------------|

| 0      | 0  | Disable auto precharge, leave bank A active at end of burst. |

|        | 1  | Disable auto precharge, leave bank B active at end of burst. |

| 1      | 0  | Enable auto precharge, precharge bank A at end of burst.     |

|        | 1  | Enable auto precharge, precharge bank B at end of burst.     |

4.A10/AP and BA control bank precharge when precharge command is asserted.

| A10/AP | ВА | precharge  |  |  |  |

|--------|----|------------|--|--|--|

| 0      | 0  | Bank A     |  |  |  |

| 0      | 1  | Bank B     |  |  |  |

| 1      | Χ  | Both Banks |  |  |  |

Publication Date: Jul. 2007 Revision: 1.4 13/29

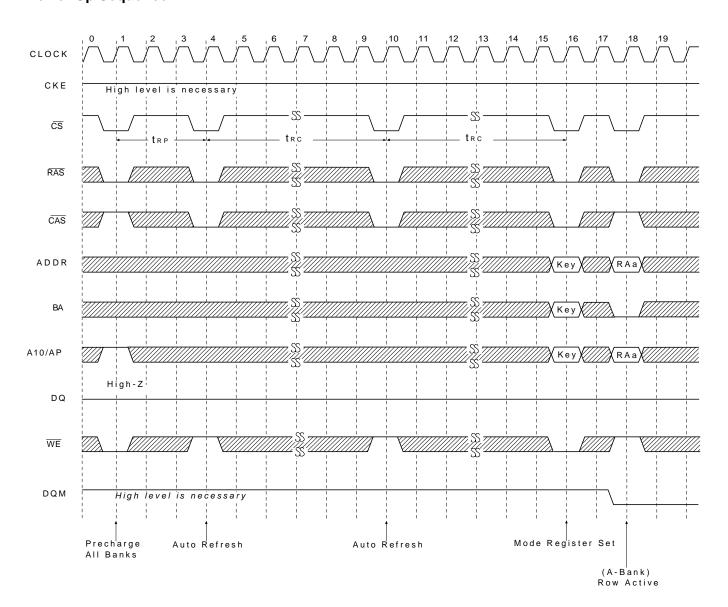

## **Power Up Sequence**

: Don't care

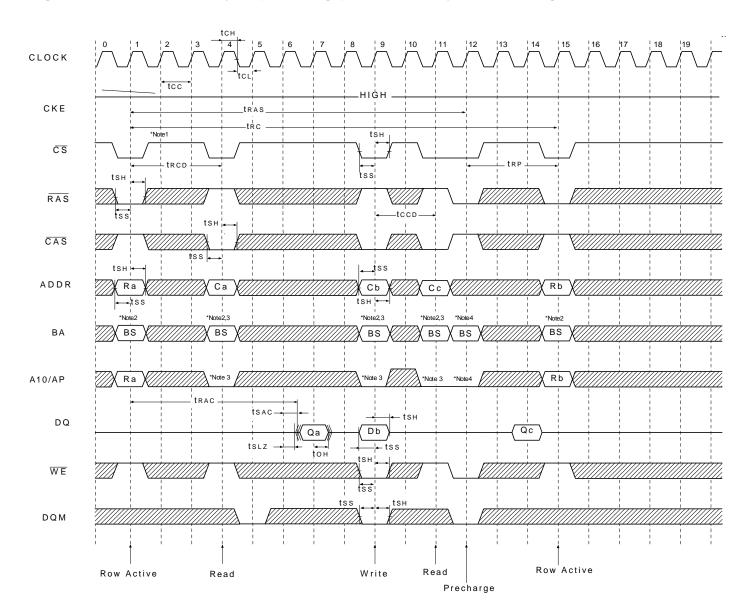

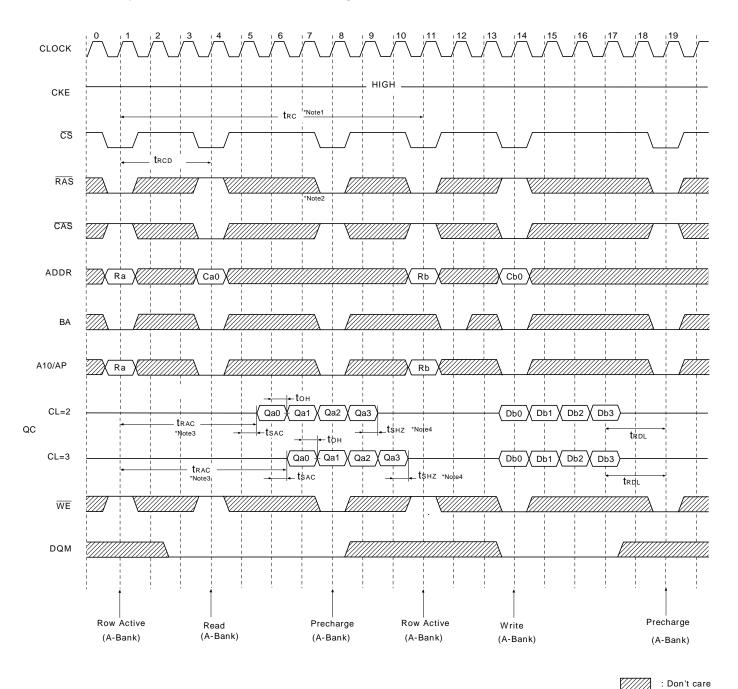

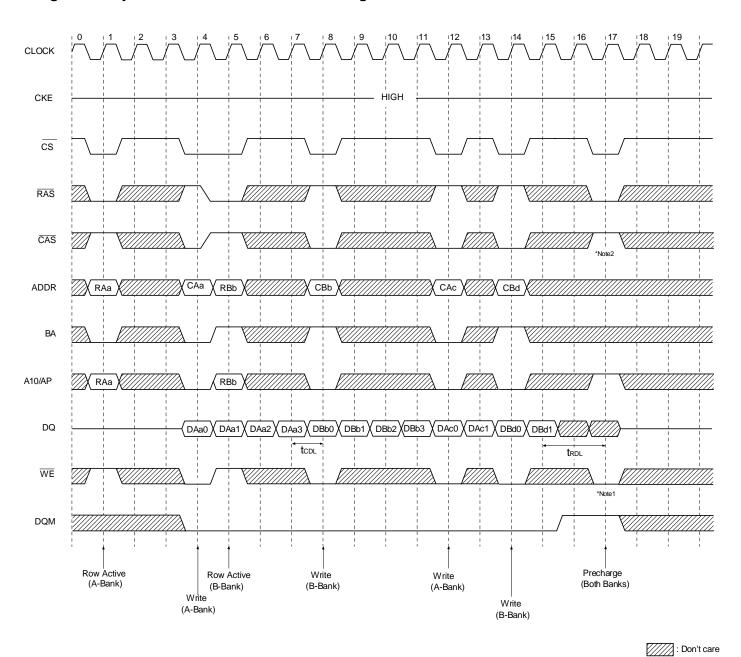

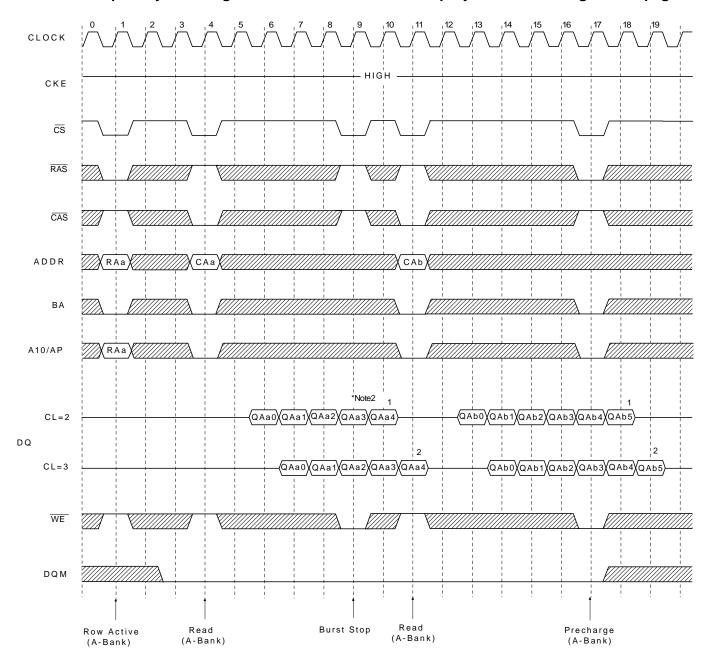

## Read & Write Cycle at Same Bank @Burst Length = 4

\*Note: 1.Minimum row cycle times is required to complete internal DRAM operation.

- 2.Row precharge can interrupt burst on any cycle. [CAS Latency-1] number of valid output data is available after Row precharge. Last valid output will be Hi-Z(tsHz) after the clock.

- 3.Access time from Row active command. tcc\*(trcd +CAS latency-1)+tsac

- 4.Ouput will be Hi-Z after the end of burst.(1,2,4,8 bit burst)

Burst can't end in Full Page Mode.

Publication Date: Jul. 2007 Revision: 1.4 15/29

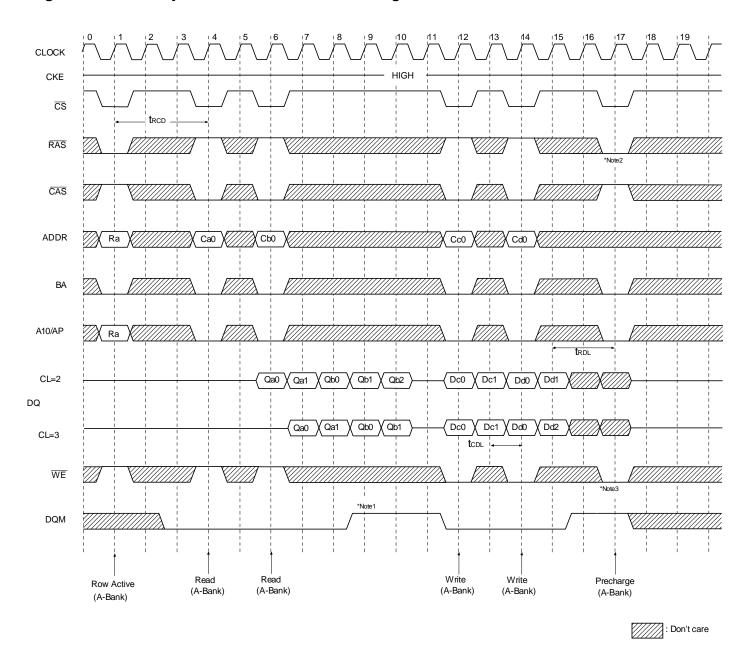

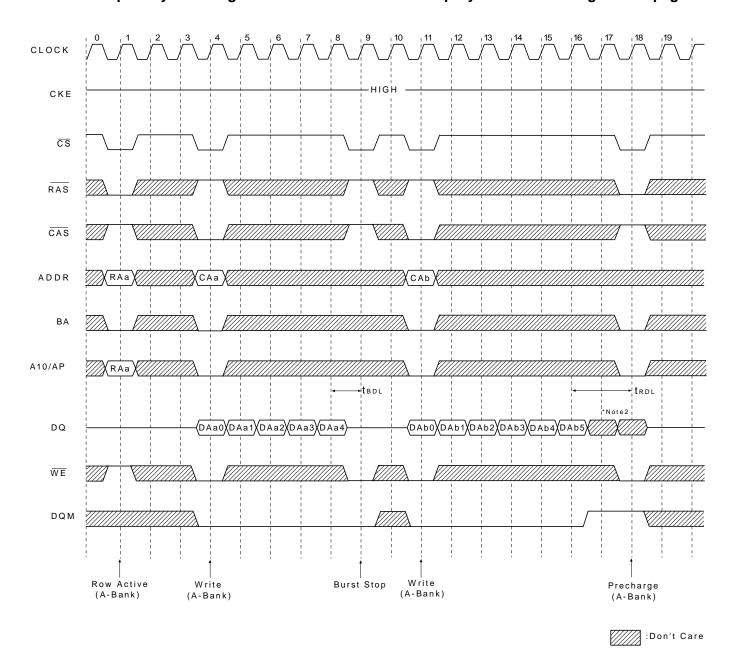

### Page Read & Write Cycle at Same Bank @ Burst Length=4

- \*Note :1.To write data before burst read ends, DQM should be asserted three cycle prior to write command to avoid bus contention.

- 2.Row precharge will interrupt writing. Last data input, trol before Row precharge, will be written.

- 3.DQM should mask invalid input data on precharge command cycle when asserting precharge before end of burst. Input data after Row precharge cycle will be masked internally.

Publication Date: Jul. 2007 Revision: 1.4 16/29

Elite Semiconductor Memory Technology Inc.

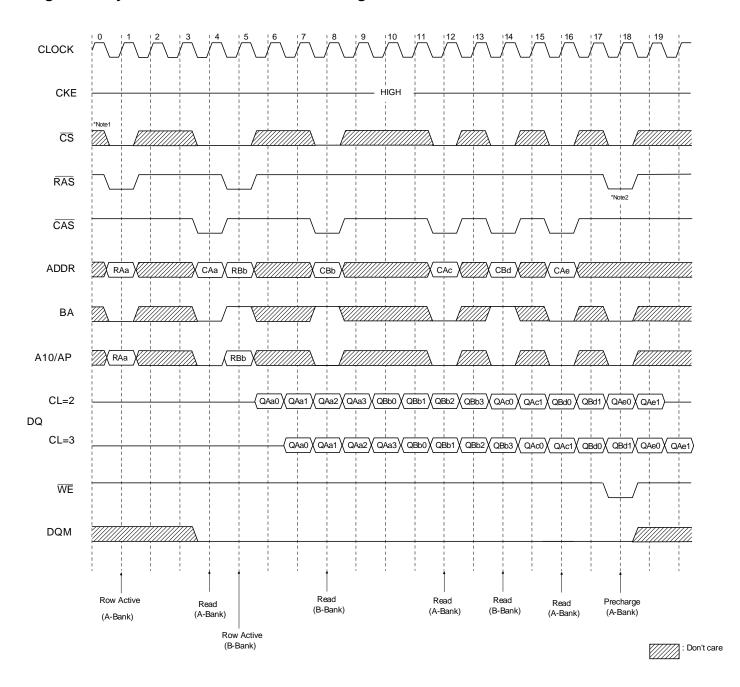

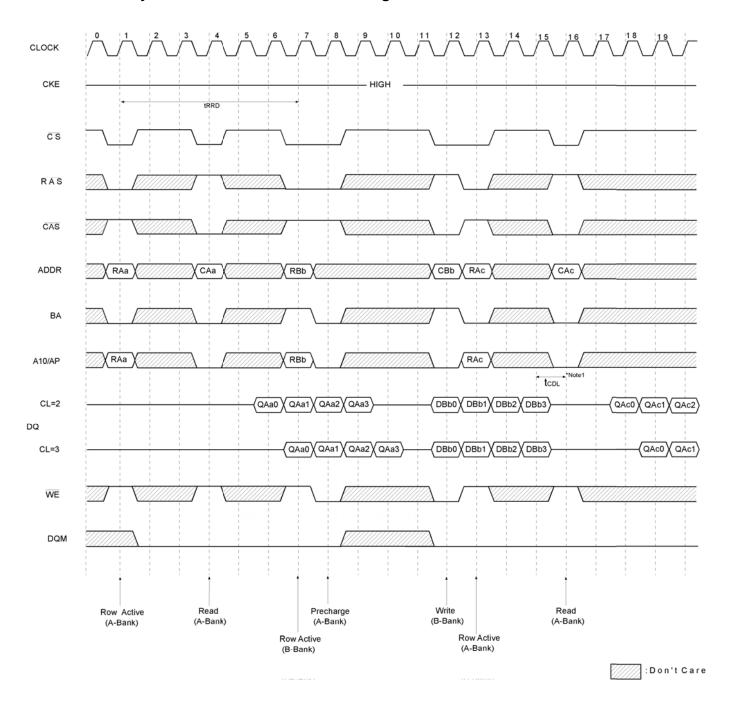

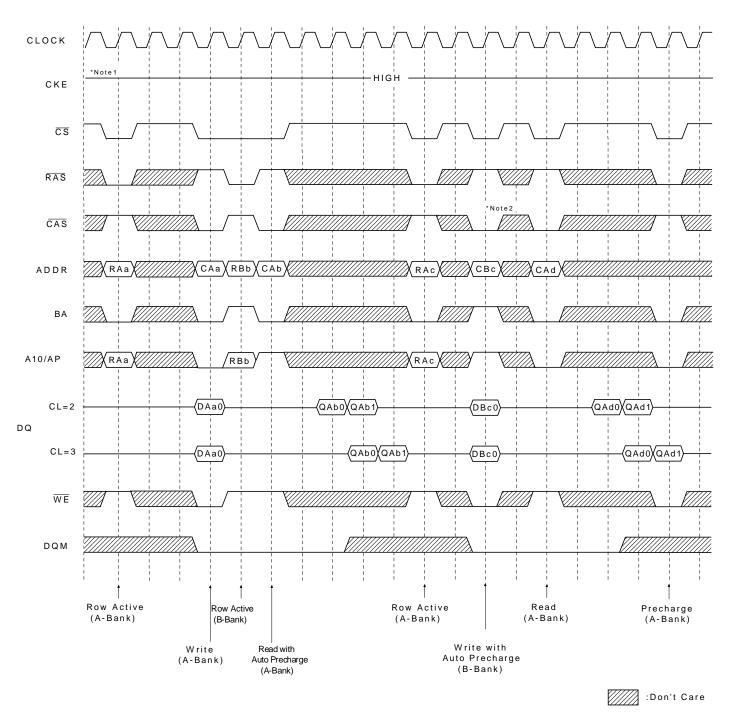

## Page Read Cycle at Different Bank @ Burst Length=4

<sup>\*</sup>Note: 1.  $\overline{\text{CS}}$  can be don't cared when  $\overline{\text{RAS}}$ ,  $\overline{\text{CAS}}$  and  $\overline{\text{WE}}$  are high at the clock high going dege.

2.To interrupt a burst read by row precharge, both the read and the precharge banks must be the same.

Publication Date: Jul. 2007 Revision: 1.4 17/29

## Page Write Cycle at Different Bank @Burst Length = 4

\*Note: 1.To interrupt burst write by Row precharge, DQM should be asserted to mask invalid input data.

2.To interrupt burst write by row precharge, both the write and the precharge banks must be the same.

## Read & Write Cycle at Different Bank @ Burst Length = 4

<sup>\*</sup>Note: 1.tcpl should be met to complete write.

Publication Date: Jul. 2007 Revision: 1.4 19/29

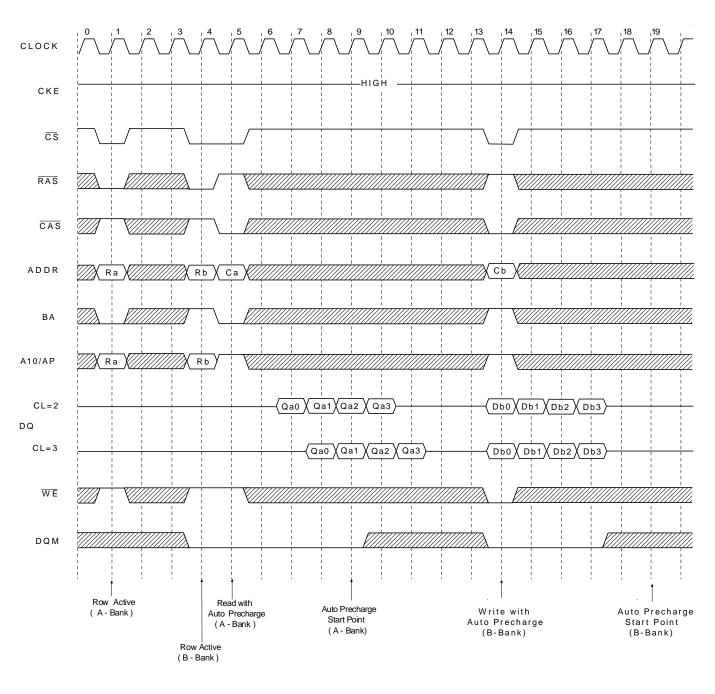

## Read & Write Cycle with auto Precharge @ Burst Length =4

:Don't Care

\*Note: 1.tcpl Should be controlled to meet minimum tras before internal precharge start (In the case of Burst Length=1 & 2 and BRSW mode)

Publication Date: Jul. 2007 Revision: 1.4 **20/29**

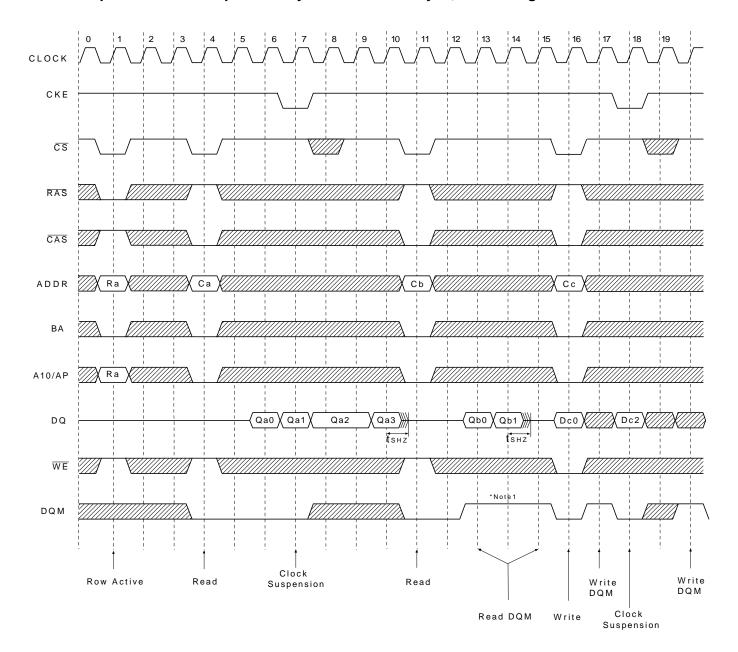

## Clock Suspension & DQM Operation Cycle @CAS Latency=2, Burst Length=4

:Don't Care

\*Note:1.DQM is needed to prevent bus contention.

Publication Date: Jul. 2007 Revision: 1.4 21/29

### Read Interrupted by Precharge Command & Read Burst Stop Cycle @Burst Length =Full page

:Don't Care

\*Note: 1.Burst can't end in full page mode, so auto precharge can't issue.

2. About the valid DQs after burst stop, it is same as the case of  $\overline{\text{RAS}}$  interrupt.

Both cases are illustrated above timing diagram. See the label 1,2 on them.

But at burst write, burst stop and RAS interrupt should be compared carefully.

Refer the timing diagram of "Full page write burst stop cycle".

3. Burst stop is valid at every burst length.

Publication Date: Jul. 2007 Revision: 1.4 **22/29**

## Write Interrupted by Precharge Command & Write Burst stop Cycle @ Burst Length =Full page

\*Note: 1. Burst can't end in full page mode, so auto precharge can't issue.

2.Data-in at the cycle of interrupted by precharge can not be written into the corresponding memory cell. It is defined by AC parameter of trade.

DQM at write interrupted by precharge command is needed to prevent invalid write.

Input data after Row precharge cycle will be masked internally.

3. Burst stop is valid at every burst length.

Publication Date: Jul. 2007 Revision: 1.4 23/29

## Burst Read Single bit Write Cycle @Burst Length=2

\*Note:1.BRSW modes is enabled by setting A9 "High" at MRS(Mode Register Set).

At the BRSW Mode, the burst length at write is fixed to "1" regardless of programmed burst length.

2. When BRSW write command with auto precharge is executed, keep it in mind that tras should not be violated.

Auto precharge is executed at the next cycle of burst-end, so in the case of BRSW write command, the precharge command will be issued after two clock cycles.

> Publication Date: Jul. 2007 Revision: 1.4

Elite Semiconductor Memory Technology Inc.

24/29

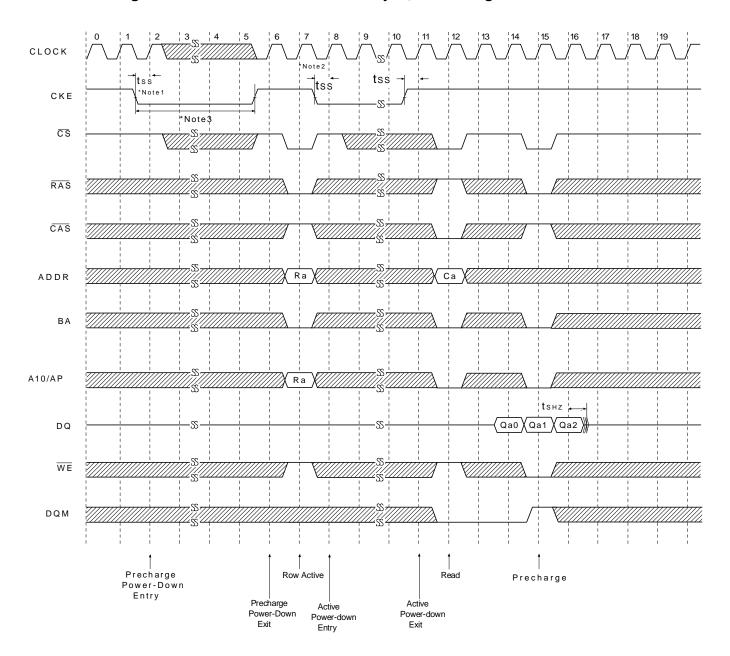

## Active/Precharge Power Down Mode @CAS Latency=2, Burst Length=4

: Don't care

\*Note:1.Both banks should be in idle state prior to entering precharge power down mode.

2.CKE should be set high at least 1CLK+tss prior to Row active command.

3.Can not violate minimum refresh specification. (64ms)

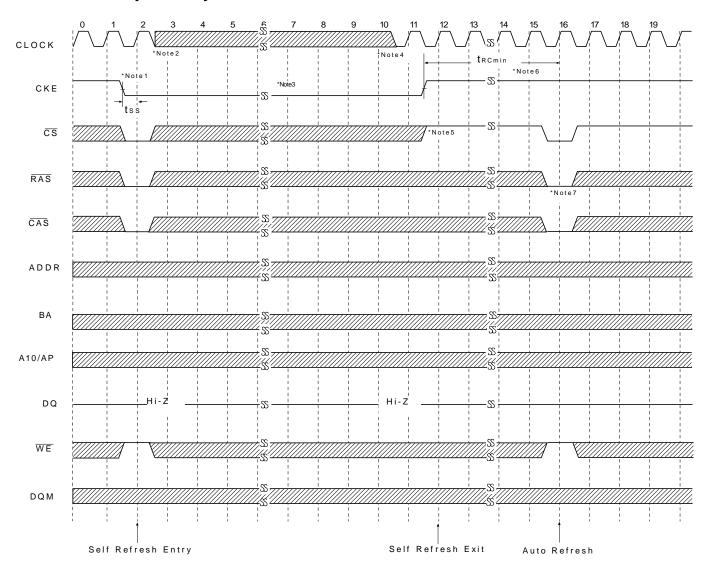

### Self Refresh Entry & Exit Cycle

: Don't care

### \*Note: TO ENTER SELF REFRESH MODE

- 1.  $\overline{\text{CS}}$ ,  $\overline{\text{RAS}}$  &  $\overline{\text{CAS}}$  with CKE should be low at the same clock cycle.

- 2. After 1 clock cycle, all the inputs including the system clock can be don't care except for CKE.

- 3. The device remains in self refresh mode as long as CKE stays "Low".

- cf.) Once the device enters self refresh mode, minimum tras is required before exit from self refresh.

### TO EXIT SELF REFRESH MODE

- 4. System clock restart and be stable before returning CKE high.

- 5. CS Starts from high.

- 6. Minimum tRC is required after CKE going high to complete self refresh exit.

- 7. 4K cycle of burst auto refresh is required before self refresh entry and after self refresh exit if the system uses burst refresh.

Publication Date: Jul. 2007 Revision: 1.4 **26/29**

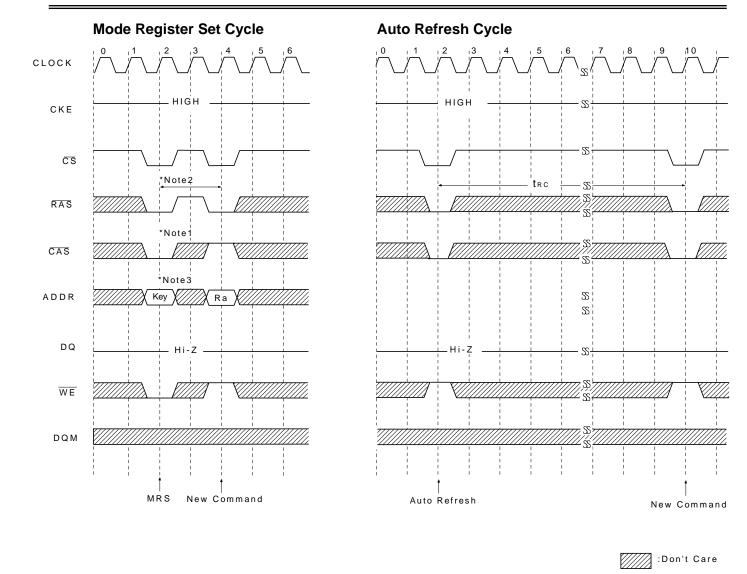

\*Both banks precharge should be completed before Mode Register Set cycle and auto refresh cycle.

### **MODE REGISTER SET CYCLE**

\*Note: 1.  $\overline{\text{CS}}$ ,  $\overline{\text{RAS}}$ ,  $\overline{\text{CAS}}$  &  $\overline{\text{WE}}$  activation at the same clock cycle with address key will set internal mode register.

- 2.Minimum 2 clock cycles should be met before new  $\overline{RAS}$  activation.

- 3.Please refer to Mode Register Set table.

Publication Date: Jul. 2007 Revision: 1.4 **27/29**

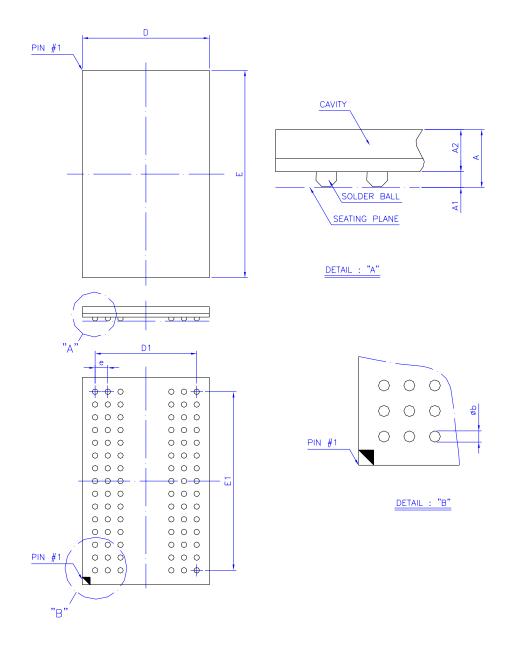

## PACKING 90-BALL

# DIMENSIONS SDRAM (8x13 mm)

| Symbol                | Dim   | ension in | mm    | Dimension in inch |       |       |  |  |

|-----------------------|-------|-----------|-------|-------------------|-------|-------|--|--|

|                       | Min   | Norm      | Max   | Min               | Norm  | Max   |  |  |

| Α                     |       |           | 1.40  |                   |       | 0.055 |  |  |

| <b>A</b> <sub>1</sub> | 0.30  |           | 0.40  | 0.012             |       | 0.016 |  |  |

| $A_2$                 | 0.84  | 0.89      | 0.94  | 0.033             | 0.035 | 0.037 |  |  |

| Øb                    | 0.40  |           | 0.50  | 0.016             |       | 0.020 |  |  |

| D                     | 7.90  | 8.00      | 8.10  | 0.311             | 0.315 | 0.319 |  |  |

| Е                     | 12.90 | 13.00     | 13.10 | 0.508             | 0.512 | 0.516 |  |  |

| D <sub>1</sub>        |       | 6.40      |       |                   | 0.252 |       |  |  |

| E <sub>1</sub>        |       | 11.20     |       |                   | 0.441 |       |  |  |

| е                     |       | 0.80      |       |                   | 0.031 |       |  |  |

Controlling dimension: Millimeter.

Publication Date: Jul. 2007 Revision: 1.4 **28/29**

## **Important Notice**

All rights reserved.

No part of this document may be reproduced or duplicated in any form or by any means without the prior permission of ESMT.

The contents contained in this document are believed to be accurate at the time of publication. ESMT assumes no responsibility for any error in this document, and reserves the right to change the products or specification in this document without notice.

The information contained herein is presented only as a guide or examples for the application of our products. No responsibility is assumed by ESMT for any infringement of patents, copyrights, or other intellectual property rights of third parties which may result from its use. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of ESMT or others.

Any semiconductor devices may have inherently a certain rate of failure. To minimize risks associated with customer's application, adequate design and operating safeguards against injury, damage, or loss from such failure, should be provided by the customer when making application designs.

ESMT's products are not authorized for use in critical applications such as, but not limited to, life support devices or system, where failure or abnormal operation may directly affect human lives or cause physical injury or property damage. If products described here are to be used for such kinds of application, purchaser must do its own quality assurance testing appropriate to such applications.

Publication Date: Jul. 2007 Revision: 1.4 29/29