# UNISONIC TECHNOLOGIES CO., LTD

# M54123L

# LINEAR INTEGRATED CIRCUIT

# **EARTH LEAKAGE CURRENT DETECTOR**

#### DESCRIPTION

The UTC M54123L is a semiconductor integrated circuit with amplifier for a high-speed earth leakage circuit breaker.

For the amplifying parts of earth leakage circuit breaker, the UTC M54123L consists of differential amplifier, latch circuit and voltage regulator.

In normal operating, the UTC M54123L should be connected to the secondary side of the ZCT (zero current transformers). Here the ZCT detects leakage current different amplifiers' both input.

Then the signals which have been amplified are integrated by an external capacitor. The integrated signal connects to the input terminal of latch circuit whose output is suitable for the characteristics of high-speed earth leakage circuit breaker.

Until the input voltage reaches the fixed level, latch circuit doesn't become high. Then drives a thyristor which is connected to latch circuit's output terminal. Once the trigger latch circuit, only the power on again to reset.

#### **FEATURES**

- \* With good input sensitivity current temperature characteristics

- \* High input sensitivity :V<sub>T</sub>=6.1mV (Typ.)

- \* Only need low external component count

- \* High noise and surge-proof

- \* Low power dissipation :P<sub>D</sub>=5mW (Typ.)

- \* May be used both as 100V and 200V.

- \* Wide temperature range : from -20 °C to +80°C

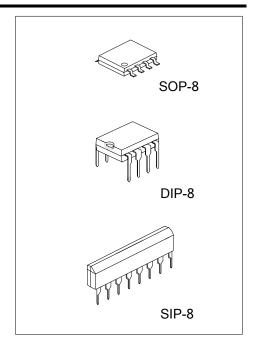

#### ORDERING INFORMATION

| Order Nu       | mber           | Deekees | Packing   |  |

|----------------|----------------|---------|-----------|--|

| Lead Free      | Halogen Free   | Package |           |  |

| M54123LK-D08-T | M54123LG-D08-T | DIP-8   | Tube      |  |

| M54123LK-G08-T | M54123LG-G08-T | SIP-8   | Tube      |  |

| M54123LK-S08-R | M54123LG-S08-R | SOP-8   | Tape Reel |  |

www.unisonic.com.tw 1 of 9

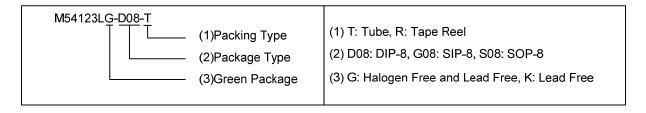

## ■ MARKING

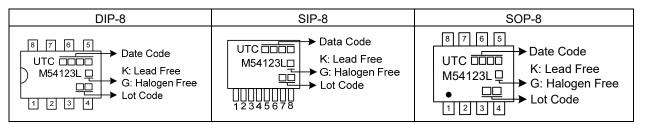

## **■ PIN CONFIGURATIONS**

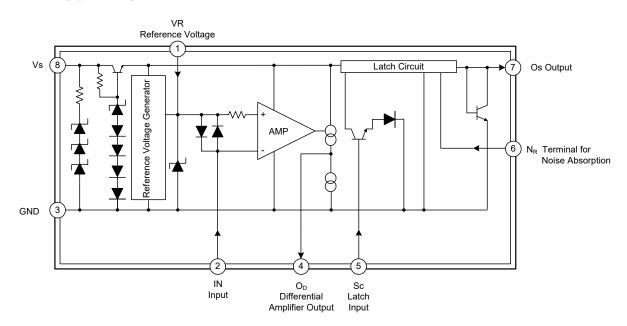

# ■ PIN DESCRIPTION

| PIN NO. | PIN NAME       | DESCRIPTION                            |  |  |

|---------|----------------|----------------------------------------|--|--|

| 1       | VR             | Reference voltage terminal             |  |  |

| 2       | IN             | Input terminal                         |  |  |

| 3       | GND            | Ground                                 |  |  |

| 4       | O <sub>D</sub> | Differential amplifier output terminal |  |  |

| 5       | Sc             | Latch input terminal                   |  |  |

| 6       | N <sub>R</sub> | Terminal for noise absorption          |  |  |

| 7       | Os             | Output terminal                        |  |  |

| 8       | Vs             | Supply voltage terminal                |  |  |

# **■ BLOCK DIAGRAM**

# ■ ABSOLUTE MAXIMUM RATING (unless otherwise specified)

| PARA                            | METER                               | SYMBOL           | RATINGS   | UNIT |

|---------------------------------|-------------------------------------|------------------|-----------|------|

| Supply Current                  |                                     | ls               | 8         | mA   |

|                                 | Between V <sub>R</sub> -IN (Note 2) |                  | 250       | mA   |

| V <sub>R</sub> Pin Current      | Between V <sub>R</sub> -GND         | Ivr              | 30        | mA   |

|                                 | Between IN-V <sub>R</sub> (Note 2)  |                  | -250      | mA   |

|                                 | Between IN-V <sub>R</sub> (Note 2)  |                  | 250       | mA   |

| IN Terminal Current             | Between IN-GND                      | lin              | 30        | mA   |

|                                 | Between V <sub>R</sub> -IN (Note 2) |                  | -250      | mA   |

| S <sub>C</sub> Terminal Current |                                     | Isc              | 5         | mA   |

| Power Dissipation               |                                     | $P_D$            | 200       | mW   |

| Operating Temperature           |                                     | T <sub>OPR</sub> | -20~ +80  | °C   |

| Storage Temperature             | ·                                   | $T_{STG}$        | -55~ +125 | °C   |

- Notes: 1. Absolute maximum ratings are those values beyond which the device could be permanently damaged.

Absolute maximum ratings are stress ratings only and functional device operation is not implied.

- 2. Current value between  $V_R$  and IN, and between IN and  $V_R$  is less than 1ms in the pulse width, and duty cycle is less than 12%, In applying AC current continuously, it is 100 mA in the off-state.

# ■ RECOMMENDED OPERATING CONDITIONS (unless otherwise specified)

| PARAMETER                                      | SYMBOL          | MIN | TYP | MAX | UNIT |

|------------------------------------------------|-----------------|-----|-----|-----|------|

| Supply Voltage When Latch Circuit Is Off-State | Vs              | 12  |     |     | V    |

| External Capacitor Between Vs and GND          | C <sub>VS</sub> | 1   |     |     | μF   |

| External Capacitor Between Os and GND          | Cos             |     |     | 1   | μF   |

# ■ **ELECTRICAL CHARACTERISTICS** (T<sub>A</sub>=-20~+80°C, unless otherwise specified)

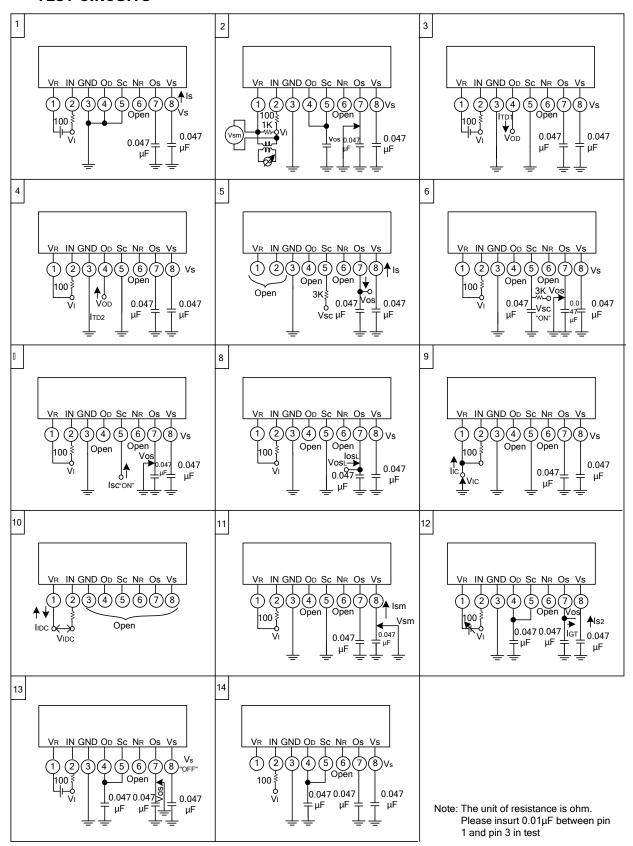

| PARAMETER                                            | SYMBOL              | TEST CONDITIONS                                                                                                             |                                               | MIN  | TYP | MAX        | UNIT     |

|------------------------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------|-----|------------|----------|

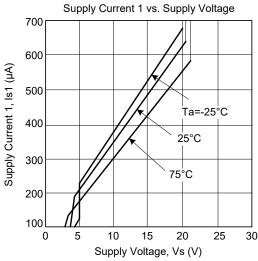

| Supply Current                                       | I <sub>S1</sub>     | V <sub>S</sub> =12V,V <sub>R</sub> -V <sub>I</sub> =30mV                                                                    | T <sub>A</sub> =-20°C<br>T <sub>A</sub> =25°C |      | 400 | 580<br>530 | μA<br>μA |

|                                                      |                     | (See Test Circuit 1)                                                                                                        | T <sub>A</sub> =80°C                          |      |     | 480        | μA       |

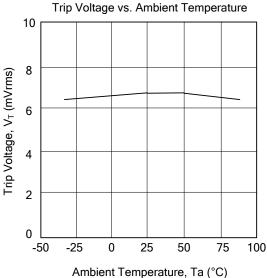

| Trip Voltage                                         | V <sub>T</sub>      | V <sub>S</sub> =16V, V <sub>R</sub> -V <sub>I</sub> , T <sub>A</sub> =-20~+80°C<br>(Note2) (See Test Circuit 2)             |                                               | 4    | 6.1 | 9          | mVrms    |

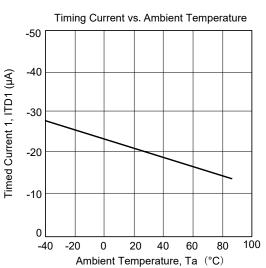

| Timed Current1                                       | I <sub>TD1</sub>    | V <sub>S</sub> =16V, V <sub>R</sub> -V <sub>I</sub> =30mV, V <sub>OD</sub> =1.2V, T <sub>A</sub> =25°C (See Test Circuit 3) |                                               | -12  |     | -30        | μA       |

| Timed Current2                                       | I <sub>TD2</sub>    | $V_S$ =16V, short circuit between $V_R$ and $V_I$ , $V_{OD}$ =0.8V, $T_A$ =25°C (See Test Circuit 4)                        |                                               | 17   |     | 37         | μA       |

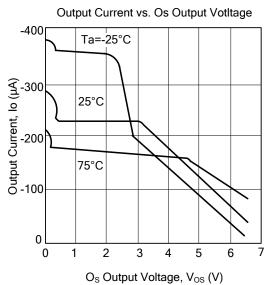

|                                                      | lo                  | V <sub>SC</sub> =1.4V,V <sub>OS</sub> =0.8V                                                                                 | I <sub>S1</sub> =580μA,T <sub>A</sub> =-20°C  | -200 |     |            | μA       |

| Output Current                                       |                     |                                                                                                                             | I <sub>S1</sub> =530μA,T <sub>A</sub> =25°C   | -100 |     |            | μA       |

|                                                      |                     |                                                                                                                             | I <sub>S1</sub> =480μA,T <sub>A</sub> =80°C   | -75  |     |            | μA       |

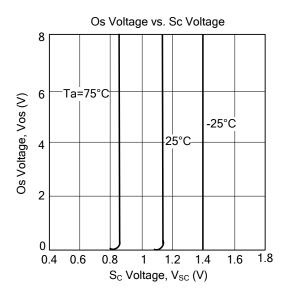

| S <sub>C</sub> "ON" Voltage (Note3)                  | V <sub>SC(ON)</sub> | V <sub>S</sub> =16V, T <sub>A</sub> =25°C (See Test Circuit 6)                                                              |                                               | 0.7  |     | 1.4        | V        |

| S <sub>C</sub> Input Current                         | I <sub>SC(ON)</sub> | V <sub>S</sub> =12V, T <sub>A</sub> =25°C (See Test Circuit 7)                                                              |                                               |      |     | 5          | μΑ       |

| Output Low-Level Current                             | losL                | V <sub>S</sub> =12V,V <sub>OSL</sub> =0.2V, T <sub>A</sub> =-20~+80°C<br>(See Test Circuit 8)                               |                                               | 200  |     |            | μΑ       |

| Input Clamp Voltage                                  | V <sub>IC</sub>     | V <sub>S</sub> =12V, I <sub>IC</sub> =20mA, T <sub>A</sub> =-20~+80°C<br>(See Test Circuit 9)                               |                                               | 4.3  |     | 6.7        | ٧        |

| Differential Input Clamp<br>Voltage                  | V <sub>IDC</sub>    | I <sub>IDC</sub> =100mA, T <sub>A</sub> =-20~+80°C<br>(See Test Circuit 10)                                                 |                                               | 0.4  |     | 2          | V        |

| Maximum Current Voltage                              | $V_{\text{SM}}$     | I <sub>SM</sub> =7mA, T <sub>A</sub> =25°C (See Test Circuit 11)                                                            |                                               |      |     | 28         | V        |

| Supply Current 2(Note 4)                             | ls2                 | V <sub>R</sub> -V <sub>I</sub> , V <sub>OS</sub> =0.6V, T <sub>A</sub> =-20~+80°C<br>(Note 5) (See Test Circuit 12)         |                                               |      |     | 1100       | μA       |

| Latch Circuit is Off-State<br>Supply Voltage (Note6) | V <sub>S(OFF)</sub> | T <sub>A</sub> =25°C (See Test Circuit 13)                                                                                  |                                               | 0.5  |     |            | V        |

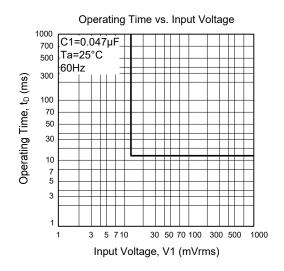

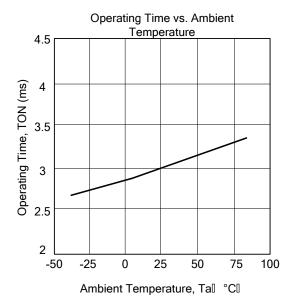

| Operating Time (Note 7)                              | Ton                 | V <sub>S</sub> =16V,V <sub>R</sub> -V <sub>I</sub> =0.3V, T <sub>A</sub> =25°C<br>(See Test Circuit 14)                     |                                               | 2    |     | 4          | ms       |

# ■ ELECTRICAL CHARACTERISTICS (Cont.)

Notes: 1. Typical values are at TA=25°C

- 2. When standard value of voltage (60Hz) between  $V_R$  and  $V_I$  is minimum, and output  $O_S$  is low-level, or when standard value of voltage (60Hz) between  $V_R$  and  $V_I$  is maximum, and output  $O_S$  is high-level, it is considered as a good one.

- 3. When standard value of voltage  $V_{SC(ON)}$  is minimum, and output  $O_S$  is low-level, or when standard value of voltage  $V_{SC(ON)}$  is maximum, and output  $O_S$  is high-level, it is considered as a good one.

- 4. Supply current 2 is necessary to keep high in output Os.

- 5. After applying 30mV between V<sub>R</sub> and V<sub>I</sub> and shorting between them, it is considered as a good one if standard value of IGT flows out of output O<sub>S</sub>.

- 6. After supply voltage applies 12V and output O<sub>S</sub> is high-level, it is considered as a good one in the standard value of supply voltage and in the low-level of output O<sub>S</sub>.

- 7. Operating time is a time from applying fixed input till operating latch circuit in  $0.047\mu F$  between  $O_D$  and GND.

## ■ TEST CIRCUITS

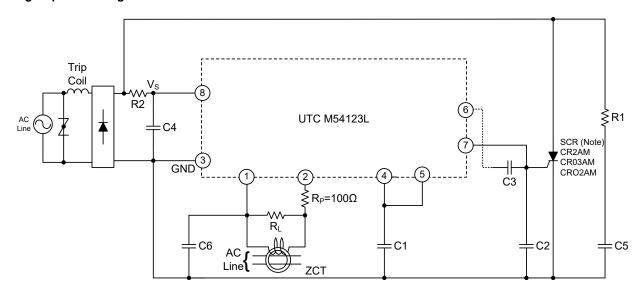

#### TYPICAL APPLICATION CIRCUIT

## High-Speed Leakage Circuit Breaker With UTC M54123L

Note: Gate current must be selected.

Please select voltage resistance by AC supply voltage

Note: The value of R1, R2, C4, and C5 should be chosen in order to keep at least 12V in Vs.

Please connect C4 (>1µF) and C2 (<1µF).

ZCT and load resistance R<sub>L</sub> of ZCT are connected between input pin 1 and 2.

Protective resistance (R<sub>P</sub>=100 $\Omega$ ) must be insurted.

R<sub>L</sub> and amplifier's output (in Pin 4) regulates sensitivity current

External capacitor C1 between pin 4 and GND is used for noise removal.

Please connect a varistor or a diode (2 pcs.) to ZCT in parallel, because of when large current is grounded in the primary side (AC line) of ZCT, the following situation can be abandoned: The wave form in the secondary side of ZCT is distorted and some signals do not appear in the output of amplifier.

Please connect capacitor (about 0.047  $\mu F)$  between pin 6 and pin 7.

Capacitor C6 between pin 1 and GND is about 0.047µF for removing noise.

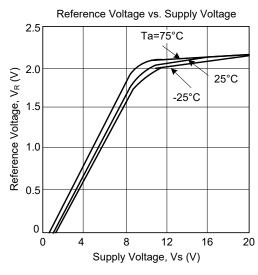

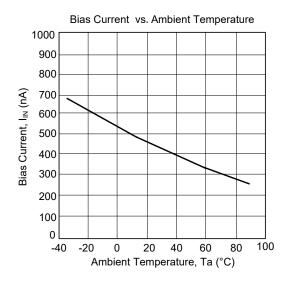

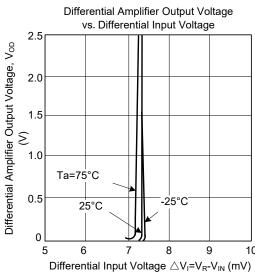

## **■ TYPICAL CHARACTERISTICS**

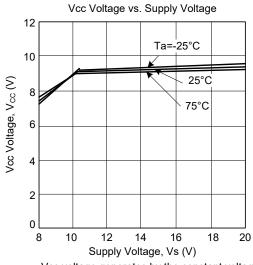

Vcc voltage generates by the constant voltage circuit in IC. This is measured not by M54123L but by a special element.

## **■ TYPICAL CHARACTERISTICS(Cont.)**

UTC assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all UTC products described or contained herein. UTC products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. UTC reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.