# M5K4164AP-12, -15

65 536-BIT (65 536-WORD BY 1-BIT) DYNAMIC RAM

#### DESCRIPTION

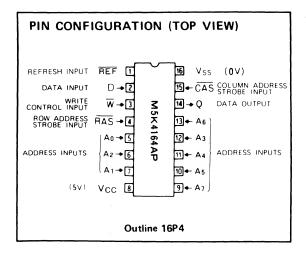

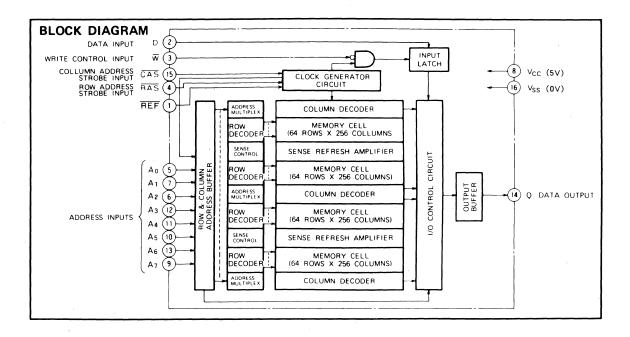

This is a family of 65 536-word by 1-bit dynamic RAMs, fabricated with the high performance N-channel silicongate MOS process, and is ideal for large-capacity memory systems where high speed, low power dissipation, and low costs are essential. The use of double-layer polysilicon process technology and a single-transistor dynamic storage cell privide high circuit density at reduced costs, and the use of dynamic circuitry including sense amplifiers assures low power dissipation. Multiplexed address inputs permit both a reduction in pins to the standard 16-pin package configuration and an increase in system densities. The M5K4164AP operates on a 5V power supply using the on-chip substrate bias generator.

#### **FEATURES**

#### High speed

| Type name    | Access time<br>(max)<br>(ns) | Cycle time<br>(min)<br>(ns) | Power dissipation<br>(typ)<br>(mW) |

|--------------|------------------------------|-----------------------------|------------------------------------|

| M5K4164AP-12 | 120                          | 220                         | 175                                |

| M5K4164AP-15 | 150                          | 260                         | 150                                |

- Single 5V±10% supply

- Low standby power dissipation: 22mW (max)

- Low operating power dissipation: 300mW (max)

- Unlatched output enables two-dimensional chip selection and extended page boundary

- Early-write operation gives common I/O capability

- Read-modify-write, RAS-only refresh, and page-mode capabilities

- All input terminals have low input capaciatance and are directly TTL-compatible

- Output is three-state and directly TTL-compatible

- 128 refresh cycles every 2ms

(16K dynamic RAMs M5K4116P, S compatible)

- CAS controlled output allows hidden refresh

- Output data can be held infinitely by CAS

- Pin 1 controls automatic- and Self-refresh mode.

- Interchangeable with Fujitsu MB8265A and Motorola's MCM6664 in pin configuration

#### APPLICATION

Main memory unit for computers

#### **FUNCTION**

The M5K4164AP provides, in addition to normal read, write, and read-modify-write operations, a number of other functions, e.g., page mode, RAS-only refresh, and delayed-write. The input conditions for each are shown in Table 1.

Table 1 Input conditions for each mode

|                          |       |     |     | Inputs |                |                   |     | Output |         |                  |

|--------------------------|-------|-----|-----|--------|----------------|-------------------|-----|--------|---------|------------------|

| Operation.               | RAS   | CAS | w   | D      | Row<br>address | Column<br>address | REF | Q      | Refresh | Remarks          |

| Read                     | ACT   | ACT | NAC | DNC    | APD            | APD               | NAC | VLD    | YES     | Page mode        |

| Write                    | ACT.  | ACT | ACT | VLD    | APD            | APD               | NAC | OPN    | YES     | identical except |

| Read-modify-write        | ACT   | ACT | ACT | VLD    | APD            | APD               | NAC | VLD    | YES     | réfresh is NO.   |

| RAS-only refresh         | ACT   | NAC | DNC | DNC    | APD            | DNC               | NAC | OPN    | YES     |                  |

| Hidden refresh           | ACT   | ACT | DNC | DNC    | APD            | DNC               | NAC | VLD    | YES     |                  |

| Automatic refresh        | NAC   | DNC | DNC | DNC    | DNC            | DNC               | ACT | OPN    | YES     |                  |

| Self refresh             | NAC   | DNC | DNC | DNC    | DNC            | DNC               | ACT | OPN    | . YES   |                  |

| Hidden automatic refresh | . NAC | ACT | DNC | DNC    | DNC            | DNC               | ACT | VLD    | YES     |                  |

| Hidden self refresh      | NAC   | ACT | DNC | DNC    | DNC            | DNC               | ACT | VLD    | YES     |                  |

| Standby                  | NAC   | DNC | DNC | DNC    | DNC            | DNC               | NAC | OPN    | NO      | 8                |

Note: ACT : active, NAC : nonactive, DNC : don't care, VLD : valid, APD : applied, OPN : open

# SUMMARY OF OPERATIONS Addressing

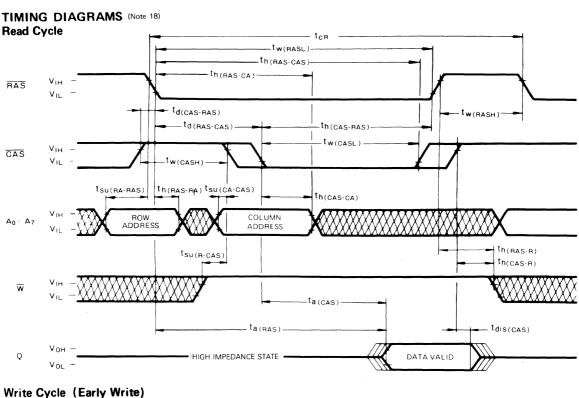

To select one of the 65536 memory cells in the M5K4164AP the 16-bit address signal must be multiplexed into 8 address signals, which are then latched into the on-chip latch by two externally-applied clock pulses. First, the negative-going edge of the row-address-strobe pulse (RAS) latches the 8 row-address bits; next, the negative-going edge of the column-address-strobe pulse (CAS) latches the 8 column-address bits. Timing of the RAS and CAS clocks can be selected by either of the following two methods:

- The delay time from RAS to CAS t<sub>d (RAS-CAS)</sub> is set between the minimum and maximum values of the limits. In this case, the internal CAS control signals are inhibited almost until t<sub>d(RAS-CAS)</sub> max ('gated CAS' operation). The external CAS signal can be applied with a margin not affecting the on-chip circuit operations, e.g. access time, and the address inputs can be easily changed from row address to column address.

- The delay time t<sub>d(RAS-CAS)</sub> is set larger than the maximum value of the limits. In this case the internal inhibition of CAS has already been released, so that the internal CAS control signals are controlled by the externally applied CAS, which also controls the access time.

#### **Data Input**

Data to be written into a selected cell is strobed by the later of the two negative transistons of  $\overline{W}$  input and  $\overline{CAS}$  input. Thus when the  $\overline{W}$  input makes its negative transition prior to  $\overline{CAS}$  input (early write), the data input is strobed by  $\overline{CAS}$ , and the negative transition of  $\overline{CAS}$  is set as the

reference point for set-up and hold times. In the read-write or read-modify-write cycles, however, when the  $\overline{W}$  input makes its negative transition after  $\overline{CAS}$ , the  $\overline{W}$  negative transition is set as the reference point for setup and hold times

# **Data Output Control**

The output of the M5K4164AP is in the high-impedance state when  $\overline{\text{CAS}}$  is high. When the memory cycle in progress is a read, read-modify-write, or a delayed-write cycle, the data output will go from the high-impedance state to the active condition, and the data in the selected cell will be read. This data output will have the same polarity as the input data. Once the output has entered the active condition, this condition will be maintained until  $\overline{\text{CAS}}$  goes high, irrespective of the condition of  $\overline{\text{RAS}}$ .

The output will remain in the high-impedance state throughout the entire cycle in an early-write cycle.

These output conditions, of the M5K4164AP, which can readily be changed by controlling the timing of the write pulse in a write cycle, and the width of the  $\overline{\text{CAS}}$  pulse in a read cycle, offer capabilities for a number of applications, as follows.

### 1. Common I/O Operation

If all write operations are performed in the early-write mode, input and output can be connected directly to give a common I/O data bus.

#### 2 Data Output Hold

The data output can be held between read cycles, without lengthening the cycle time. This enables extremely flexible clock-timing settings for  $\overline{RAS}$  and  $\overline{CAS}$ .

#### 3. Two Methods of Chip Selection

Since the output is not latched,  $\overline{CAS}$  is not required to keep the outputs of selected chips in the matrix in a high-impedance state. This means that  $\overline{CAS}$  and/or  $\overline{RAS}$  can both be decoded for chip selection.

#### 4. Extended-Page Boundary

By decoding  $\overline{CAS}$ , the page boundary can be extended beyond the 256 column locations in a single chip. In this case,  $\overline{RAS}$  must be applied to all devices.

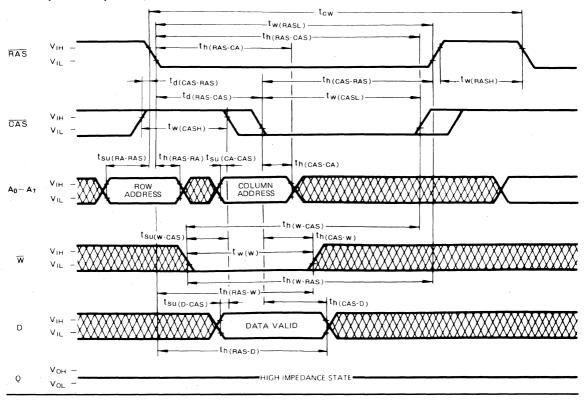

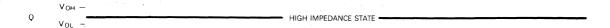

#### Page-Mode Operation

This operation allows for multiple-column addressing at the same row address, and eliminates the power dissipation associated with the negative-going edge of  $\overline{RAS}$ , because once the row address has been strobed,  $\overline{RAS}$  is maintained. Also, the time required to strobe in the row address for the second and subsequent cycles is eliminated, thereby decreasing the access and cycle times.

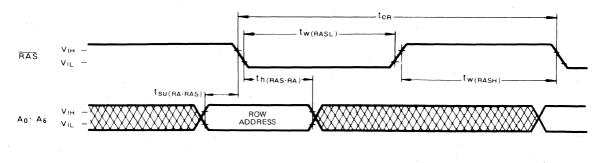

#### Refresh

Each of the 128 rows ( $A_0 \sim A_6$ ) of the M5K4164AP must be refreshed every 2 ms to maintain data. The methods of refreshing for the M5K4164AP are as follows.

#### 1. Normal Refresh

Read cycle and Write cycle (early write, delayed write or read-modify-write) refresh the selected row as defined by the low order (RAS) addresses. Any write cycle, of course, may change the state of the selected cell. Using a read, write, or read-modify-write cycle for refresh is not recommended for systems which utilize "wire-OR" outputs since output bus contention will occur.

# 2. RAS Only Refresh

A RAS-only refresh cycle is the recommended technique for most applications to provide for data retention. A RAS-only refresh cycle maintains the output in the high-impedance state with a typical power reduction of 20% over a read or write cycle.

#### 3. Automatic Refresh

Pin 1 (REF) has two special functions. The M5K4164AP has a refresh address counter, refresh address multiplexer and refresh timer for these operations. Automatic refresh is initiated by bringing REF low after RAS has precharged and is used during standard operation just like RAS-only refresh, except that sequential row addresses from an external counter are no longer necessary.

At the end of automatic refresh cycle, the internal refresh address counter will be automatically incremented. The output state of the refresh address counter is initiated by some eight REF, RAS or RAS/CAS cycle after power is applied. Therefore, a special operation is not necessary to initiate it.

RAS must remain inactive during REF activated cycles. Likewise, REF must remain inactive during RAS generated cycle.

#### 4. Self-Refresh

The other function of pin 1 ( $\overline{REF}$ ) is self-refresh. Timing for self-refresh is quite similar to that for automatic refresh. As long as  $\overline{RAS}$  remains high and  $\overline{REF}$  remains low, the M5K4164AP will refresh itself. This internal sequence repeats asynchronously every 12 to 16  $\mu$ s. After 2 ms, the on-chip refresh address counter has advanced through all the row addresses and refreshed the entire memory. Self-refresh is primarily intended for trouble free power-down operation.

For example, when battery backup is used to maintained data integrity in the memory.  $\overline{\text{REF}}$  may be used to place the device in the self-refresh mode with no external timing signals necessary to keep the information alive.

In summary, the pin 1 (REF) refresh function gives the user a feature that is free, save him hardware on the board, and in fact, will simplify his battery backup procedures, increase his battery life, and save him overall cost while giving him improved system performance.

There is an internal pullup resister ( $\approx$  3M $\Omega$ ) on pin 1, so if the pin 1. (REF) function is not used, pin 1 may be left open (not connect) without affecting the normal operations.

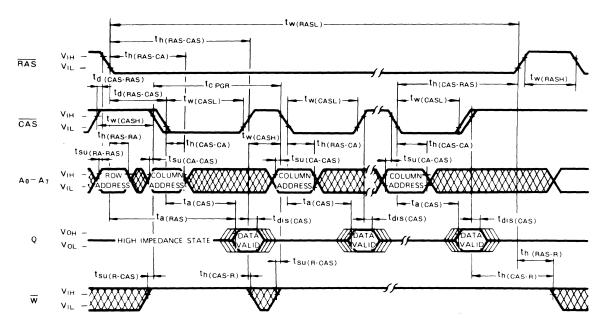

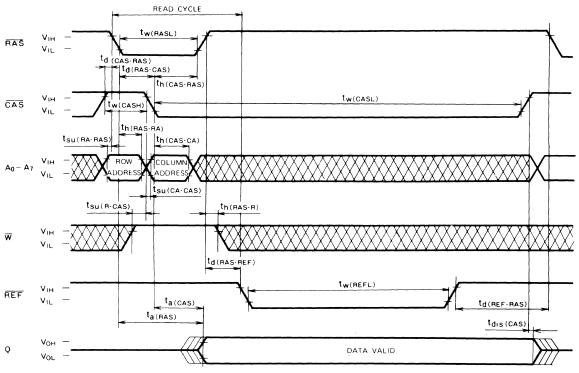

#### 5. Hidden Refresh

A features of the M5K4164AP is that refresh cycle may be performed while maintaining valid data at the output pin by extending the  $\overline{\text{CAS}}$  active time from a previous memory read cycle. This feature is refered to as hidden refresh.

Hidden refresh is performed by holding  $\overline{CAS}$  at  $V_{1L}$  and taking  $\overline{RAS}$  high and after a specified precharge period, executing a  $\overline{RAS}$ -only cycling, automatic refresh and self-refresh, but with  $\overline{CAS}$  held low.

The advantage of this refresh mode is that data can be held valid at the output data port indefinitely by leaving the CAS asserted. In many applications this eliminates the need for off-chip latches.

#### **Power Dissipation**

Most of the circuitry in the M5K4164AP is dynamic, and most of the power is dissipated when addresses are strobed. Both  $\overline{RAS}$  and  $\overline{CAS}$  are decoded and applied to the M5K4164AP as chip-select in the memory system, but if  $\overline{RAS}$  is decoded, all unselected devices go into stand-by independent of the  $\overline{CAS}$  condition, minimizing system power dissipation.

#### **Power Supplies**

The M5K4164AP operates on a single 5V power supply.

A wait of some  $500\mu s$  and eight or more dummy cycle is necessary after power is applied to the device before memory operation is achieved.

# **ABSOLUTE MAXIMUM RATINGS**

| Symbol | Parameter                            | Conditions                      | Limits     | Unit |

|--------|--------------------------------------|---------------------------------|------------|------|

| Vcc    | Supply voltage                       |                                 | -1~7       | V    |

| Vı     | Input voltage                        | With respect to V <sub>SS</sub> | -1~7       | V    |

| Vo     | Output voltage                       |                                 | -1~7       | V    |

| 10     | Output current                       |                                 | 50         | mA   |

| Pd .   | Power dissipation                    | Ta = 25°C                       | 700        | mW   |

| Topr   | Operating free-air temperature range |                                 | 0~70       | .c   |

| Tstq   | Storage temperature range            |                                 | - 65 ~ 150 | ·c   |

# **RECOMMENDED OPERATING CONDITIONS** ( $Ta = 0 \sim 70^{\circ}C$ , unless otherwise noted) (Note. 1)

| Symbol | Parameter                            |     | Limits |     |      |  |  |

|--------|--------------------------------------|-----|--------|-----|------|--|--|

|        | Farameter                            | Min | Nom    | Max | Unit |  |  |

| Vcc    | Supply voltage                       | 4.5 | 5      | 5.5 | ٧    |  |  |

| Vss    | Supply voltage                       | 0   | 0      | 0   | V    |  |  |

| ViH    | High-level input voltage, all inputs | 2.4 |        | 6.5 | ٧    |  |  |

| VIL    | Low-level input voltage, all inputs  | -2  |        | 0.8 | V    |  |  |

Note 1. All voltage values are with respect to V<sub>SS</sub>

# $\textbf{ELECTRICAL CHARACTERISTICS} \ \, (\textbf{T}_a = \textbf{0} \sim 70 \text{°C} \,, \ \textbf{V}_{CC} = \textbf{5} \, \textbf{V} \pm \textbf{10} \, \%, \ \textbf{V}_{SS} = \textbf{0} \, \textbf{V} \,, \ \text{unless otherwise noted)} \, \, (\text{Note 2}) \, \text{(Note 2)} \, , \, \text{(Note 2)}$

| Symbol             | Parameter                                     |                 | Test conditions                                                       |      | Limits |     | Unit |

|--------------------|-----------------------------------------------|-----------------|-----------------------------------------------------------------------|------|--------|-----|------|

| Symbol             | Parameter                                     |                 | rest conditions                                                       | Min  | Тур    | Max | Unit |

| V <sub>OH</sub>    | High-level output voltage                     |                 | I <sub>OH</sub> = -5mA                                                | 2.4  |        | Vcc | ٧    |

| VoL                | Low-level output voltage                      |                 | I <sub>OL</sub> = 4.2 mA                                              | 0    |        | 0.4 | ٧    |

| loz                | Off-state output current                      |                 | Q floating $0V \le V_{OUT} \le 5.5V$                                  | - 10 |        | 10  | μA   |

| 1,                 | Input current                                 |                 | $0V \le V_{IN} \le 6.5V$ , All other pins = $0V$                      | 10   |        | -10 | μΔ   |

| . 1 = =            | Average supply current from V <sub>CC</sub> , | M5K4164AP-12    | RAS, CAS cycling                                                      |      |        | 50  | mA . |

| ICC1(AV)           | operating (Note 3, 4)                         | M5K4164AP-15    | t CR = t CW = min output open                                         |      |        | 45  | ""   |

| I CC2              | Supply current from V <sub>CC</sub> , standby | /               | RAS = VIH output open                                                 |      |        | 4   | mΑ   |

| 1                  | Average supply current from V <sub>CC</sub> , | M5K4164AP-12    | RAS cycling CAS = VIH                                                 |      |        | 40  | mA.  |

| CC3(AV)            | refreshing (Note 3)                           | M5K4164AP-15    | t <sub>C(REF)</sub> = min, output open                                | i    |        | 35  | ""   |

| ICC4(AV)           | Average supply current from V <sub>CC</sub> , | M5K4164AP-12    | RAS = VIL, CAS cycling                                                |      |        | 40  | mA.  |

| 1004(AV)           | page mode (Note 3, 4)                         | M5K4164AP-15    | t CPG = min, output open                                              |      |        | 35  | IIIA |

| CC5(AV)            | Average supply current from V <sub>CC</sub> , | M5K4164AP-12    | RAS = VIH, REF cycling                                                |      |        | 40  | mA   |

| · CCS(AV)          | automatic refreshing (Note 3)                 | M5K4164AP-15    | t <sub>C(REF)</sub> =min, output open                                 |      |        | 35  |      |

| CC6 (AV)           | Average supply current from V <sub>CC</sub>   | self refreshing | RAS = V <sub>IH</sub> , REF = V <sub>IL</sub> output open             |      |        | 8   | mA   |

| C <sub>I</sub> (A) | Input capacitance, address inputs             |                 |                                                                       |      |        | . 5 | pF   |

| C <sub>I (D)</sub> | Input capacitance, data input                 |                 | V <sub>I</sub> =V <sub>SS</sub>                                       |      |        | 5   | pF   |

| C <sub>I</sub> (w) | Input capacitance, write control in           | put             | f=1MHz                                                                |      |        | . 7 | pF   |

| Ci (RAS)           | Input capacitance, RAS input                  |                 | V <sub>I</sub> =25mVrms                                               |      |        | 10  | pF   |

| CI (CAS)           | Input capacitance, CAS input                  |                 | 1                                                                     |      |        | 10  | pF   |

| CI(REF)            | Input capacitance, REF input                  |                 | 1                                                                     |      |        | 10  | pF   |

| Co                 | Output capacitance                            |                 | V <sub>O</sub> = V <sub>SS</sub> , f = 1MHz, V <sub>I</sub> = 25mVrms |      |        | 7   | pF   |

Note 2: Current flowing into an IC is positive, out is negative.

3: ICC1(AV), ICC3(AV), ICC4(AV) and ICC5(AV) are dependent on cycle rate. Maximum current is measured at the fastest cycle rate.

4: I<sub>CC1(AV)</sub> and I<sub>CC4(AV)</sub> are dependent on output loading. Specified values are obtained with the output open.

### TIMING REQUIREMENTS (For Read, Write, Read-Modify-Write, Refresh, and Page-Mode Cycle)

(  $T_a=\,0\,\sim70\,^{\circ}\text{C}$  ,  $\,$  V  $_{CC}=\,5\,\text{V}\pm10\,\%$  ,  $\,$  V  $_{SS}=\,0\,\text{V}$  , unless otherwise noted, See notes 5, 6 and 7)

|                                      |                                                 |           |                       | M5K41       | 64AP-12 | M5K41 | 64AP-15 |      |

|--------------------------------------|-------------------------------------------------|-----------|-----------------------|-------------|---------|-------|---------|------|

| Symbol                               | Parameter                                       |           | Alternative<br>Symbol | Li          | imits   | Lir   | mits    | Unit |

|                                      |                                                 |           | 0,55                  | Min         | Max     | Min   | Max     |      |

| t <sub>C</sub> RF                    | Refresh cycle time                              |           | tREF                  |             | 2       |       | 2       | ms   |

| tw(RASH)                             | RAS high pulse width                            |           | t <sub>RP</sub>       | 90          |         | 100   |         | ns   |

| tw(RASL)                             | RAS low pulse width                             |           | t RAS                 | 120         | 10000   | 150   | 10000   | ns   |

| tw(CASL)                             | CAS low pulse width                             |           | t <sub>CAS</sub>      | 60          |         | 75    | ∞       | ns   |

| tw(CASH)                             | CAS high pulse width                            | (Note 8)  | t <sub>CPN</sub>      | 30          |         | 35    |         | ns   |

| tn(RAS-CAS)                          | CAS hold time after RAS                         |           | t <sub>CSH</sub>      | 120         |         | 150   |         | ns   |

| t n (CAS-RAS)                        | RAS hold time after CAS                         |           | t <sub>RSH</sub>      | 60          |         | 75    |         | ns   |

| td (CAS RAS)                         | Delay time, CAS to RAS                          | (Note 9)  | t <sub>CRP</sub>      | <b>— 20</b> |         | -20   |         | ns   |

| td(RAS-CAS)                          | Delay time, RAS to CAS                          | (Note 10) | t <sub>RCD</sub>      | 25          | 60      | 30    | 75      | ns   |

| t su(RA-RAS)                         | Row address setup time before RAS               |           | t ASR                 | 0           |         | 0     |         | ns   |

| t su(CA-CAS)                         | Column address setup time before CA             | <u>vs</u> | tasc                  | 0           |         | 0     |         | ns   |

| tn(RAS-RA)                           | Row address hold time after RAS                 |           | t <sub>RAH</sub>      | 15          |         | 20    |         | ns   |

| t n (CAS-CA)                         | Column address hold time after CAS              |           | t <sub>CAH</sub>      | 20          |         | 25    |         | ns   |

| t <sub>h(RAS-CA)</sub>               | Column address hold time after $\overline{RAS}$ |           | t AR                  | 90          |         | 95    |         | ns   |

| t <sub>THL</sub><br>t <sub>TLH</sub> | Transition time                                 |           | t <sub>T</sub>        | 3           | 35      | 3     | 35      | ns   |

Note 5: An initial pause of 500 ns is required after power-up followed by any eight RAS or RAS/CAS cycles before proper device operation is achieved.

6: The switching characteristics are defined as  $t_{THL}\!=\!t_{TLH}\!=\!5\text{ns}$ .

7: Reference levels of input signals are VIH min and VIL max. Reference levels for transition time are also between VIH and VIL.

8: Except for page-mode.

9: td(cas-ras) requirement is only applicable for RAS/CAS cycles preceded by a CAS only cycle (i.e., For systems where CAS has not been decoded with RAS.)

10: Operation within the td(ras-cas) max limit insures that ta(ras) max can be met. td(ras-cas) max is specified reference point only; if td(ras-cas) is greater than the specified td (ras-cas) max limit, then access time is controlled exclusively by ta(cas).

td(ras-cas)min = th(ras-ray)min + 2t\_THL(t\_{TH}) + tsu(ca-cas)min.

# SWITCHING CHARACTERISTICS ( $T_a = 0 \sim 70^{\circ}\text{C}$ , $V_{CC} = 5V \pm 10\%$ , $V_{SS} = 0V$ , unless otherwise noted) Read Cycle

|                  |                            |           |                    | M5K41 | 64AP-12 | M5K4164AP-15 |      |      |

|------------------|----------------------------|-----------|--------------------|-------|---------|--------------|------|------|

| Symbol           | Parameter                  |           | Alternative Symbol | Lir   | mits    | Lir          | nits | Unit |

|                  |                            |           | 3ymboi -           | Min   | Max     | Min          | Max  | 7    |

| t <sub>C</sub> R | Read cycle time            |           | t <sub>RC</sub>    | 220   |         | 260          |      | ns   |

| tsu (R-CAS)      | Read setup time before CAS |           | t ACS              | 0     |         | 0            |      | ns   |

| th (CAS-R)       | Read hold time after CAS   | (Note 11) | t <sub>RCH</sub>   | 0     |         | 0            |      | ns   |

| th(RAS-R)        | Read hold time after RAS   | (Note 11) | t <sub>RRH</sub>   | 10    |         | 20           |      | ns   |

| tdis(CAS)        | Output disable time        | (Note 12) | t <sub>OFF</sub>   | 0     | 35      | 0            | 40   | . ns |

| ta (CAS)         | CAS access time            | (Note 13) | t CAC              |       | 60      |              | 75   | ns   |

| ta (RAS)         | RAS access time            | (Note 14) | t RAC              |       | 120     |              | 150  | ns   |

Note 11: Either th (RAS-R) or th (CAS-R) must be satisfied for a read cycle

Note 12: tdis(CAS) max defines the time at which the output achieves the open circuit condition and is not reference to VoH or VoL

Note 13: This is the value when td (RAS-CAS)  $\geq td$  (RAS-CAS) max. Test conditions; Load=2T TL, CL=100pF

Note 14: This is the value when td (RAS-CAS) < td (RAS-CAS) max. When td (RAS-CAS)  $\ge td$  (RAS-CAS) max, ta (RAS) will increase by the amount that td (RAS-CAS) exceeds the value shown. Test conditions;Load=2T TL,  $C_L$ =100pF

#### **Write Cycle**

|                   |                                       |                    | M51    | K4164AP-12 | M5K4164AP-15 |     |      |

|-------------------|---------------------------------------|--------------------|--------|------------|--------------|-----|------|

| Symbol            | Parameter                             | Alternative Symbol | Limits |            | Limits       |     | Unit |

|                   |                                       | Symbol [           | Min    | Max        | Min          | Max |      |

| t <sub>cw</sub>   | Write cycle time                      | t <sub>RC</sub>    | 220    |            | 260          |     | ns   |

| tsu(w·CAS)        | Write setup time before CAS (Note 17) | t wcs              | -5     |            | <b>-10</b>   |     | ns   |

| th (CAS-W)        | Write hold time after CAS             | t wch              | 40     |            | 45           |     | ns   |

| th (RAS-W)        | Write hold time after RAS             | t wcn              | 90     |            | 95           |     | ns   |

| th (W-RAS)        | RAS hold time after write             | t <sub>RWL</sub>   | 40     |            | 45           |     | ns   |

| th (w-CAS)        | CAS hold time after write             | t <sub>CWL</sub>   | 40     |            | 45           |     | ns   |

| tw <sub>(W)</sub> | Write pulse width                     | t we               | 40     |            | 45           |     | ns   |

| tsu (D-CAS)       | Data-in setup time before CAS         | t <sub>DS</sub>    | 0      |            | , 0          |     | ns   |

| th(CAS-D)         | Data-in hold time after CAS           | t <sub>DH</sub>    | 40     |            | 45           |     | ns   |

| th (RAS-D)        | Data-in hold time after RAS           | t <sub>DHR</sub>   | 90     |            | 95           |     | ns   |

# Read-Write and Read-Modify-Write Cycles

|                   |                                 |           | Alternative<br>Symbol | M5K41 | M5K4164AP-12<br>Limits |     | 84AP-15 |    |

|-------------------|---------------------------------|-----------|-----------------------|-------|------------------------|-----|---------|----|

| Symbol            | Parameter                       |           |                       | Li    |                        |     | Limits  |    |

|                   |                                 |           |                       | Min   | Max                    | Min | Max     | S  |

| tonw              | Read-write cycle time           | (Note 15) | tRWC                  | 245   |                        | 295 |         | ns |

| t <sub>CRMW</sub> | Read-modify-write cycle time    | (Note 16) | t <sub>RMWC</sub>     | 265   |                        | 310 |         | ns |

| th (W-RAS)        | RAS hold time after write       |           | tRWL                  | 40    |                        | 45  |         | ns |

| th (W-CAS)        | CAS hold time after write       |           | t <sub>CWL</sub>      | 40    |                        | 45  |         | ns |

| tw(w)             | Write pulse width               |           | t <sub>wp</sub>       | 40    |                        | 45  |         | ns |

| tsu (R-CAS)       | Read setup time before CAS      | -         | t <sub>BCS</sub>      | 0     |                        | 0   |         | ns |

| td (RAS-W)        | Delay time, RAS to write        | (Note 17) | t <sub>RWD</sub>      | 100   |                        | 120 |         | ns |

| td (CAS-W)        | Delay time, CAS to write        | (Note 17) | t <sub>CWD</sub>      | 40    |                        | 60  |         | ns |

| tsu (D-w)         | Data-in setup time before write |           | t <sub>DS</sub>       | 0     |                        | 0   |         | ns |

| th:(w-D)          | Data-in hold time after write   |           | t <sub>DH</sub>       | 40    |                        | 45  |         | ns |

| tdis (CAS)        | Output disable time             |           | t <sub>OFF</sub>      | 0     | 35                     | 0   | 40      | ns |

| ta (CAS)          | CAS access time                 | (Note 13) | t <sub>CAC</sub>      |       | 60                     |     | 75      | ns |

| ta (RAS)          | RAS access time                 | (Note 14) | . t <sub>RAC</sub>    |       | 120                    |     | 150     | ns |

Note 15:  $t_{CRW}$  min is defined as  $t_{CRW}$  min =  $t_{CRW}$  min =  $t_{CRW}$  min =  $t_{CRW}$  min is defined as  $t_{CRW}$  min =  $t_{CRW}$

16:  $t_{CRMW}$  min is defined as  $t_{CRMW}$  min =  $ta_{CRMS}$  max +  $th_{(W-RAS)}$  +  $tw_{(RAS H)}$  +  $3t_{TLH(t_{THL})}$

17: tsu (w-cas), td (RAS-w), and td (CAS-w) do not define the limits of operation, but are included as electrical characteristics only.

When tsu(w-cas)≥tsu(w-cas)min, an early-write cycle is performed, and the data output keeps the high-impedance state

When td (RAS-W)≥td (RAS-W)min\_ and td (CAS-W)≥tsu (W-CAS)min\_a read-write cycle is performed, and the data of the selected address will be read out on the data output.

For all conditions other than those described above, the condition of data output (at access time and until CAS goes back to VIH) is not defined.

#### Page-Mode Cycle

| Symbol              |                                        |                    | M5K4164AP-12<br>Limits |     | M5K4164AP-15<br>Limits |     | Unit |

|---------------------|----------------------------------------|--------------------|------------------------|-----|------------------------|-----|------|

|                     | Parameter                              | Alternative Symbol |                        |     |                        |     |      |

|                     |                                        | Symbol             | Min                    | Max | Min                    | Max |      |

| t <sub>C PGR</sub>  | Page-mode read cycle time              | t <sub>PC</sub>    | 140                    |     | 145                    |     | ns   |

| t <sub>c PGW</sub>  | Page-Mode write cycle time             | t <sub>PC</sub>    | 140                    |     | 145                    |     | ns   |

| t <sub>c PGRW</sub> | Page-Mode read-write cycle time        | _                  | 150                    |     | 180                    |     | ns   |

| topgrmw             | Page-Mode read-modify-write cycle time | -                  | 170                    |     | 195                    |     | ns   |

| tw (CASH)           | CAS high pulse width                   | t <sub>CP</sub>    | 55                     |     | 60                     |     | ns   |

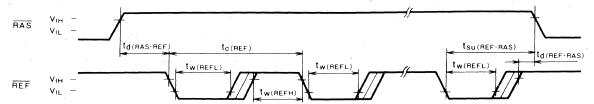

### **Automatic Refresh Cycle**

|               | Parameter                       |                       | M5K41  | 64AP-12 | M5K4164AP-15 |      |      |

|---------------|---------------------------------|-----------------------|--------|---------|--------------|------|------|

| Symbol        |                                 | Alternative<br>Symbol | Limits |         | Limits       |      | Unit |

|               |                                 | Symbol                | Min    | Max     | Min          | Max  |      |

| tc (REF)      | Automatic Refresh cycle time    | t <sub>FC</sub>       | 220    |         | 260          |      | ns   |

| td (RAS-REF)  | Delay time, RAS to REF          | t <sub>RFD</sub>      | 90     |         | 100          |      | ns   |

| tw (REFL)     | REF low pulse width             | t <sub>FP</sub>       | 60     | 8000    | 60           | 8000 | ns   |

| tw (REFH)     | REF high pulse width            | t <sub>FI</sub>       | 30     |         | 30           |      | ns   |

| td (REF-RAS)  | Delay time, REF to RAS          | tFSR                  | 30     |         | 30           |      | ns   |

| tsu (REF-RAS) | REF pulse setup time before RAS | terd                  | 250    |         | 295          |      | ns   |

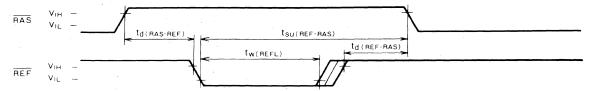

# Self-Refresh Cycle

| Symbol       |                        | Alternative<br>Symbol | M5K41  | 64AP-12 | M5K416 |     |        |

|--------------|------------------------|-----------------------|--------|---------|--------|-----|--------|

|              | Parameter              |                       | Limits |         | Limits |     | Unit . |

|              |                        |                       | Min    | Max     | Min    | Max |        |

| td (RAS-REF) | Delay time, RAS to REF | t <sub>RFD</sub>      | 90     |         | 100    |     | ns     |

| tw (REFL)    | REF low pulse width    | t <sub>FBP</sub>      | 8000   | ∞       | 8000   | ∞   | ns     |

| td (REF-RAS) | Delay time, REF to RAS | t <sub>FBR</sub>      | 310    |         | 345    |     | ns     |

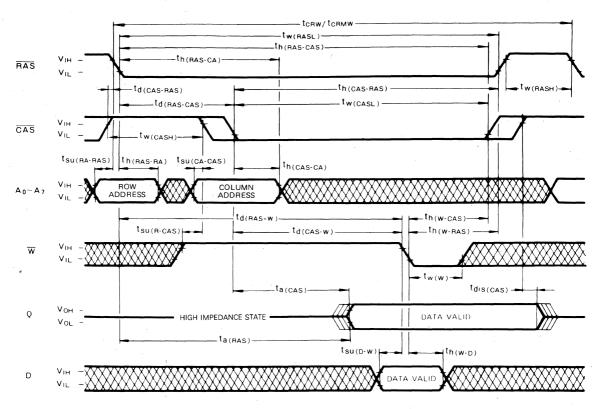

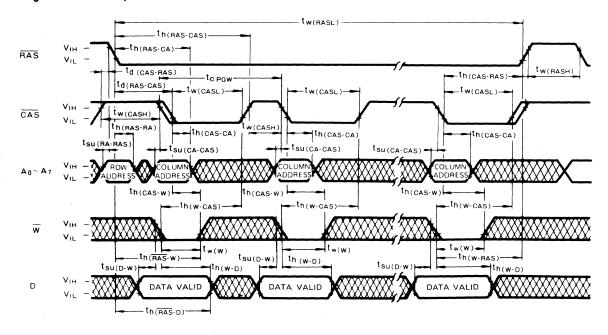

# Read-Write and Read-Modify-Write Cycles

#### RAS-Only Refresh Cycle (Note 19)

Note 18 Indicates the don't care input

Note 19.  $\overline{CAS} = V_{IH}$ ,  $\overline{W}$ ,  $A_7$ , D = don't care.

The center-line indicates the high-impedance state

# Page-Mode Read Cycle

# Page-Mode Write Cycle

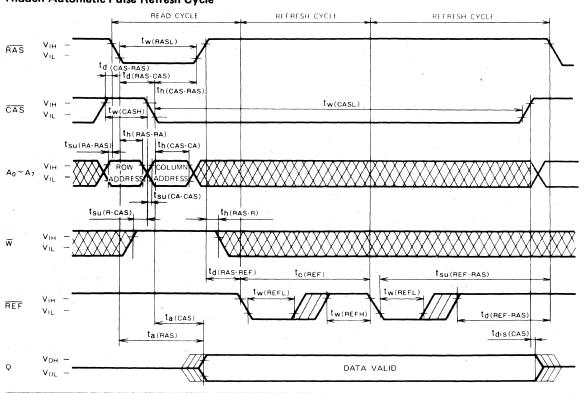

#### Automatic Pulse Refresh Cycle (Multiple Pulse) (Note 20)

### Automatic Pulse Refresh Cycle (Single Pulse) (Note 20)

# Self-Refresh Cycle (Note 20)

# Hidden Automatic Pulse Refresh Cycle

# Hidden Self-Refresh Cycle (Note 21)

. Note 21: If the pin 1 (REF) function is not used, pin 1 may be left open (not connect).

#### Hidden Refresh Cycle (Note 19) READ CYCLE REFRESH CYCLE REFRESH CYCLE tos ton tcR tw(RASL) tw(RASL) tw(RASL) $V_{\mathsf{1H}}$ RAS $V_{\mathsf{IL}}$ tw(RASH) td(cas-ras) td(RAS-CAS) th (CAS-RAS) tw (RASH) tw(CASL) Vін CAS tw(cash) th(CAS-CA) th(RAS-RA) tsu(RA-RAS) th (RAS-RA) tsu(RA-RAS) th(RAS-RA) ADDRESS tsu (CA-CAS) th.(RAS-R) tsu(R-CAS) ta(CAS) tdis (CAS) ta (RAS) $V_{OH}$ DATA VALID $V_{OL}$