MITSUBISHI LSIS

## 2048-BIT STATIC RAM WITH I/O PORTS AND TIMER

## DESCRIPTION

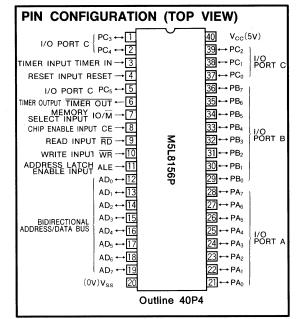

The M5L8156P is a 2K-bit RAM (256-word by 8-bit) fabricated with the N-channel silicon-gate ED-MOS technology. This IC has 3 I/O ports and a 14-bit counter/timer which make it a good choice to extend the functions of an 8-bit microcomputer. It is incased in a 40-pin plastic DIL package and operates with a single 5V power supply.

#### FEATURES

- Single 5V supply voltage

- TTL compatible

- Compatible with MELPS 85 devices

- Static RAM: 256 words by 8 bits

- Programmable 8-bit I/O port: 2

- Programmable 6-bit I/O port: 1

- Programmable counter/timer: 14 bits

- Multiplexed address/data bus

## APPLICATION

Extension of I/O ports and timer function for MELPS 85 and MELPS 8-48 devices

## **FUNCTION**

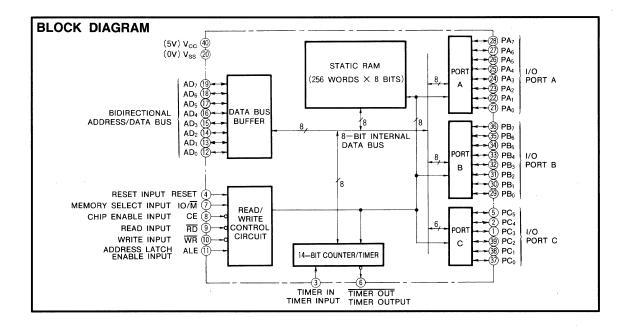

The M5L8156P is composed of RAM, I/O ports and counter/ timer. The RAM is a 2K-bit static RAM organized as 256 words by 8 bits. The I/O ports consist of 2 programmable 8bit ports and 1 programmable 6-bit port. The terminals of the 6-bit port can be programmed to function as control terminals for the 8-bit ports, so that the 8-bit ports can be operated

in a handshake mode. The counter/timer is composed of 14 bits that can be used to count down (events or time) and it can generate square wave pulses that can be used for counting and timing.

4

## 2048-BIT STATIC RAM WITH I/O PORTS AND TIMER

## OPERATION

## Data Bus Buffer

This 3-state bidirectional 8-bit buffer is used to transfer the data while input or output instructions are being executed by the CPU. Command and address information is also transferred through the data bus buffer.

#### **Read/Write Control Logic**

The read/write control logic controls the transfer of data by interpreting I/O control bus output signals ( $\overline{RD}$ ,  $\overline{WR}$ ,  $IO/\overline{M}$  and ALE) along with CPU signal ( $\overline{CE}$ ). RESET signal is also used to control the transfer of data and commands.

#### Bidirectional Address/Data Bus (AD<sub>0</sub>~AD<sub>7</sub>)

The bidirectional address/data bus is a 3-state 8-bit bus. The 8-bit address is latched in the internal latch by the falling edge of ALE. Then if  $IO/\overline{M}$  input signal is at high-level, the address of I/O port, counter/timer, or command register is selected. If it is at low-level, memory address is selected.

The 8-bit address data is transferred by read input  $(\overline{RD})$  or write input  $(\overline{WR})$ .

#### Chip Enable Input (CE)

When CE is at high-level, the address information on address/data bus is stored in the M5L8156P

#### Read Input (RD)

When  $\overline{RD}$  is at low-level the data bus buffer is active. If IO/ $\overline{M}$  input signal is at low-level, the contents of RAM are read through the address/data bus. If IO/ $\overline{M}$  input is at high-level, the selected contents of I/O port or counter/timer are read through the address/data bus.

#### Write Input (WR)

When  $\overline{XR}$  is at low-level, the data on the address/data bus are written into RAM if  $IO/\overline{M}$  is at low-level, or if  $IO/\overline{M}$  is at high-level they are written into I/O port, counter/timer or command register.

#### Address Latch Enable Input (ALE)

An address on the address/data bus along with the levels of CE and  $IO/\overline{M}$  are latched in the M5L8156P on the falling edge of ALE.

#### IO/Memory Input (IO/M)

When  $IO/\overline{M}$  is at low-level, the RAM is selected, while at high-level the I/O port, counter/timer or command register are selected.

#### I/O Port A (PA<sub>0</sub>~PA<sub>1</sub>)

Port A is an 8-bit general-purpose I/O port. Input/output setting is controlled by the system software.

#### I/O Port B (PB<sub>0</sub>~PB<sub>7</sub>)

Port B is an 8-bit general-purpose I/O port. Input/output setting is controlled by the system software.

## I/O Port C (PC<sub>0</sub>~PC<sub>5</sub>)

Port C is a 6-bit I/O port that can also be used to output control signals of port A (PA) or port B (PB). The functions of port C are controlled by the system software. When port C is used to output control signals of ports A or B the assignment of the signals to the pins is as shown in Table 1.

#### Table 1 Pin assignment of control signals of port C

| Pin              |        | Function             |

|------------------|--------|----------------------|

| PC <sub>5</sub>  | B STB  | (port B strobe)      |

| PC4              | B BF   | (port B buffer full) |

| PC <sub>3</sub>  | B INTR | (port B interrupt)   |

| PC <sub>2</sub>  | A STB  | (port A strobe)      |

| PC <sub>1'</sub> | A BF   | (port A buffer full) |

| PC <sub>0</sub>  | A INTR | (port A interrupt)   |

#### Timer Input (TIMER IN)

The signal at this input terminal is used by the counter/timer for counting events or time. (3MHz max.)

#### Timer Output (TIMER OUT)

A square wave signal or pulse from the counter/timer is output through this pin when in the operation mode.

### Command Register (8 bits)

The command register is an 8-bit latched register. The loworder 4 bits (bits  $0 \sim 3$ ) are used for controlling and determination of the mode of the ports. Bits 4 and 5 are used as interrupt enable flags for ports A and B when port C is used as a control port. Bits 6 and 7 are used for controlling the counter/timer. The contents of the command register are rewritten by output instructions (address I/O XXXX000).

Details of the functions of the individual bits of the command register are shown in Table 2.

| Table | 2 | Bit | functions | of | the | command | register |

|-------|---|-----|-----------|----|-----|---------|----------|

|-------|---|-----|-----------|----|-----|---------|----------|

| Bit | Symbol          | F                               | unction                                              |

|-----|-----------------|---------------------------------|------------------------------------------------------|

| 0   | PA              | PORT A I/O FLAG                 | 1: OUTPUT PORT A<br>0: INPUT PORT A                  |

| 1   | РВ              | PORT B I/O FLAG                 | 1: OUTPUT PORT B<br>0: INPUT PORT B                  |

| 2   | PC <sub>1</sub> | PORT C FLAG                     | 00: ALT1<br>11: ALT2                                 |

| 3   | PC <sub>2</sub> |                                 | 01: ALT3<br>10: ALT4                                 |

| 4   | IEA             | PORT A INTERRUPT<br>ENABLE FLAG | 1: ENABLE INTERRUPT<br>0: DISABLE INTERRUPT          |

| 5   | IEB             | PORT B INTERRUPT<br>ENABLE FLAG | 1: ENABLE INTERRUPT<br>0: DISABLE INTERRUPT          |

| 6   | тм1             |                                 | COUNTER/TIMER OPERATION<br>PERATION DISCONTINUED (IF |

| 7   | TM2             | 10: COUNTER/TIMER O             | PERATION DISCONTINUED AF-<br>COUNTER/TIMER OPERATION |

## 2048-BIT STATIC RAM WITH I/O PORTS AND TIMER

#### Status Register (7 bits)

The status register is a 7-bit latched register. The loworder 5 bits (bits  $0\sim4$ ) are used as status flags for the I/O ports. Bit 6 is as a status flag for the counter/timer. The contents of

the status register are transferred into the CPU by reading (INPUT instruction, address I/O XXXXX000). Details of the functions of the individual bits of the status register are shown in Table 3.

Table 3 Bit functions of the status register

| Bit | Symbol |                          | Function                                                                                                           |

|-----|--------|--------------------------|--------------------------------------------------------------------------------------------------------------------|

| 0   | INTR A | PORT A INTERRUPT REQUEST |                                                                                                                    |

| 1   | A BF   | PORT A BUFFER FULL FLAG  |                                                                                                                    |

| 2   | INTE A | PORT A INTERRUPT ENABLE  |                                                                                                                    |

| 3   | INTR B | PORT B INTERRUPT REQUEST |                                                                                                                    |

| 4   | B BF   | PORT B BUFFER FULL FLAG  |                                                                                                                    |

| 5   | INTE B | PORT B INTERRUPT ENABLE  |                                                                                                                    |

| 6   | TIMER  | COUNTER/TIMER INTERRUPT  | (SET TO 1 WHEN THE FINAL LIMIT<br>OF THE COUNTER/TIMER IS REACHED<br>AND IS RESET TO 0 WHEN THE<br>STATUS IS READ) |

| 7   | -      | THIS BIT IS NOT USED     |                                                                                                                    |

## I/O Ports

#### Command/status registers (8 bits/7 bits)

These registers are assigned address XXXXX000. When executing an OUTPUT instruction, the contents of the command register are rewritten. When executing an INPUT instruction the contents of the status register are read.

## Port A Register (8 bits)

Port A Register is assigned address XXXX001. This register can be programmed as an input or output by setting the appropriate bits of the command register as shown in Table 2.

Port A can be operated in basic or strobe made and is assigned I/O terminal  $PA_0 \sim PA_7$ .

#### Port B Register (8 bits)

Port B register is assigned address XXXXX010. As with Port A register, this register can be programmed as an input or output by setting the appropriate bits of the command register as shown in Table 2. Port B can be operated in basic or strobe mode and is assigned I/O terminals  $PB_0 \sim PB_7$ .

### Port C Register (6 bits)

Port C register is assigned address XXXXX011. This port is used for controlling input/output operations of ports A and B by selectively setting bits 2 and 3 of the command register as shown in Table 2. Details of the functions of the various setting of bits 2 and 3 are shown in Table 4. Port C is assigned I/O terminals  $PC_0 \sim PC_5$  and when used as port control signals, the 3 low-order bits are assigned for port A while the 3 high-order bits are assigned for port B.

#### Table 4 Functions of port C

| State<br>Terminal | ALT 1 | ALT 2  | ALT 3                     | ALT 4                     |

|-------------------|-------|--------|---------------------------|---------------------------|

| PC₅               | Input | Output | Output                    | B STB (port B strobe)     |

| PC₄               | Input | Output | Output                    | B BF (port buffer full)   |

| PC <sub>3</sub>   | Input | Output | Output                    | B INTR (port B interrupt) |

| PC <sub>2</sub>   | Input | Output | A STB (port A strobe)     | A STB (port A strobe)     |

| PC <sub>1</sub>   | Input | Output | A BF (port A buffer full) | A BF (port A buffer full) |

| PC <sub>0</sub>   | Input | Output | A INTR (port A interrupt) | A INTR (port A interrupt) |

# M5L8156P

## 2048-BIT STATIC RAM WITH I/O PORTS AND TIMER

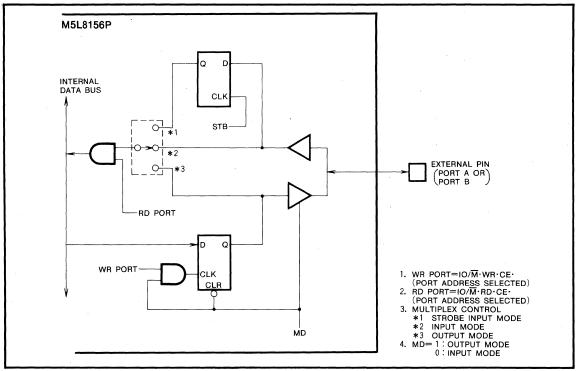

## Configuration of ports

A block diagram of 1 bit of ports A and B is shown in Fig. 1. While port A or B is programmed as an output port, if the port is addressed by an input instruction, the contents of the selected port can be read. When a port is put in input mode, the output latch is cleared and writing into the output latch is disabled. Therefore when a port is changed to output mode from input mode, low-level signals are output through the port. When a reset signal is applied, all 3 ports (PA, PB, and PC) will be input ports and their output latches are cleared. Port C has the same configuration as ports A and B in modes ALT1 and ALT2.

Fig. 1 Configuration for 1 bit of port A or B

|  | Table | 5 | Basic | functions | of | 1/0 | ports |

|--|-------|---|-------|-----------|----|-----|-------|

|--|-------|---|-------|-----------|----|-----|-------|

| Address   | RD                                                  | WR                                                                                                                                      | Function                  |

|-----------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| XXXXX000  | 0                                                   | 1                                                                                                                                       | AD bus ← status register  |

| ********* | 1                                                   | 0                                                                                                                                       | Command register - AD bus |

| WWWWW001  | 0                                                   | 1                                                                                                                                       | AD bus ← port A           |

| ********* | 1                                                   | 1 0 Command reg   0 1 AD bus ← port   1 0 Port A ← AD b   0 1 AD bus ← port   1 0 Port A ← AD b   0 1 AD bus ← port   1 0 Port B ← AD b | Port A ← AD bus           |

| WWWW010   | 0                                                   | 1                                                                                                                                       | AD bus ← port B           |

| XXXXX010  | 1                                                   | 0                                                                                                                                       | Port B ← AD bus           |

|           | 0                                                   | 1                                                                                                                                       | AD bus ← port C           |

| KXXXXX011 | xx001 0<br>xx010 0<br>xx010 1<br>xx011 0<br>xx011 1 | 0                                                                                                                                       | Port C ← AD bus           |

#### Table 6 Port control signal levels at ALT3 and ALT4

| Control Signal | Output mode | Input mode | ]  |

|----------------|-------------|------------|----|

| STB            | Input       | Input      | 1. |

| BF             | · "L"       | "L"        | 1  |

| INTR           | "H"         | "L"        | 1  |

The basic functions of the I/O ports are shown in Table 5. The control signal levels to ports A and B, when port C is programmed as a control port, are shown in Table 6.

#### Counter/Timer

The counter/timer is a 14-bit counting register plus 2 mode flags. The register has two sections: address I/O XXXXX100 is assigned to the low-order 8 bits and address I/O XXXXX101 is assigned to the high-order 8 bits. The low-order bits  $0\sim13$  are used for counting or timing. The counter is initialized by the program and then counted down to zero. The initial setting can range from  $2_{16}$  to  $3FF_{16}$ . Bits 14 and 15 are used as mode flags.

The mode flags select 1 of 4 modes with functions as follow:

Mode 0: Outputs high-level signal during the former half of the counter operation

Outputs low-level signal during the latter half of the counter operation

## 2048-BIT STATIC RAM WITH I/O PORTS AND TIMER

## Table 7 Format of counter/timer

|          | Bit Number |    |             |                 |             |                |    |                | E                                                                                                                          |  |

|----------|------------|----|-------------|-----------------|-------------|----------------|----|----------------|----------------------------------------------------------------------------------------------------------------------------|--|

| Address  | 7          | 6  | 5           | 4               | 3           | 2              | 1  | 0              | Function                                                                                                                   |  |

| XXXXX100 | Т7         | Т6 | Т5          | T₄              | Тз          | T <sub>2</sub> | T1 | т              | THE LOW-ORDER 8 BITS<br>OF THE COUNTER REGISTER                                                                            |  |

| xxxxx101 | M2         | Μı | <b>T</b> 13 | T <sub>12</sub> | <b>T</b> 11 | T10            | Т9 | Т <sub>8</sub> | $\begin{array}{c} \text{M1,M2: TIMER MODE} \\ \text{T}_8 \sim \text{T}_{13}: \\ \text{OF THE OUNTER REGISTER} \end{array}$ |  |

## Table 8 Timer mode

| $M_2$ | <b>M</b> 1 | Timer operation                                                                                                                                                   |

|-------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | 0          | Outputs high-level signal during the former half of the counter operation<br>Outputs low-level signal during the latter half of the counter operation<br>(mode 0) |

| 0     | 1          | Outputs square wave signals as in mode 0 (mode 1)                                                                                                                 |

| 1     | 0          | Outputs a low-level pulse during the final count dowm (mode 2)                                                                                                    |

| 1     | 1          | Outputs a low-level pulse during each final count down (mode 3)                                                                                                   |

## **ABSOLUTE MAXIMUM RATINGS**

- Mode 1: Outputs square wave signals as in mode 0

- Mode 2: Outputs a low-level pulse during the final count down

- Mode 3: Outputs a low-level pulse during each final count down

Starting and stopping the counter/timer is controlled by bits 6 and 7 of the command register (see Table 2 for details). The format and timer modes of the counter/timer register are shown in Table 7 and Table 8.

The counter/timer is not influenced by a reset, but counting is discontinued. To resume counting, a start command must be written into the command register as shown in Table 2. While operating 2n+1 count down in mode 0, a high-level signal is output during the n+1 counting and a low-level signal is output during the n counting.

| Symbol         | Parameter                            | Conditions                      | Limits  | Unit |

|----------------|--------------------------------------|---------------------------------|---------|------|

| $v_{\rm cc}$   | Supply voltage                       |                                 | -0.5~7  | v    |

| V <sub>1</sub> | input voltage                        | With respect to V <sub>SS</sub> | -0.5~7  | v    |

| Vo             | Output voltage                       |                                 | -0.5~7  | v    |

| Pd             | Maximum power dissipation            | T <sub>a</sub> =25℃             | 1.5     | w    |

| Topr           | Operating free-air temperature range |                                 | -20~75  | °C   |

| Tstg           | Storage temperature range            |                                 | -65~150 | °C   |

## **RECOMMENDED OPERATING CONDITIONS** $(T_a = -20 \sim 75^{\circ}C, unless otherwise noted)$

| Cumb al         | Deventer                 |      |     | 11-14                |      |

|-----------------|--------------------------|------|-----|----------------------|------|

| Symbol          | Parameter                | Min  | Nom | Max                  | Unit |

| $v_{\rm cc}$    | Supply voltage           | 4.75 | 5   | 5.25                 | v    |

| V <sub>ss</sub> | Power-supply voltage     |      | 0   |                      | v    |

| VIL             | Low-level input voltage  | -0.5 |     | 0.8                  | v    |

| VIH             | High-level input voltage | 2    |     | V <sub>cc</sub> +0.5 | v    |

## **ELECTRICAL CHARACTERISTICS** ( $T_a = -20 \sim 75$ °C, $V_{cc} = 5 V + 5 \%$ , unless otherwise noted)

| Symbol          | Parameter                           | Test and divisor                                          | Limits |     |      | Unit |

|-----------------|-------------------------------------|-----------------------------------------------------------|--------|-----|------|------|

|                 |                                     | Test conditions                                           | Min    | Тур | Max  | Unit |

| V <sub>он</sub> | High-level output voltage           | V <sub>SS</sub> =0V, I <sub>OH</sub> =-400µA              | 2.4    |     |      | v    |

| Vol             | Low-level output voltage            | $V_{SS}=0V, I_{OL}=2mA$                                   |        |     | 0.45 | v    |

| I <sub>1</sub>  | Input leak current                  | $V_{SS}=0V,V_{I}=0\sim V_{CC}$                            | -10    |     | 10   | μA   |

| II(CE)          | Input leak current, CE pin          | $V_{SS}=0V, V_{I}=0\sim V_{CC}$                           | -100   |     | 100  | μA   |

| loz             | Output floating leak current        | V <sub>SS</sub> =0V, V <sub>I</sub> =0.45~V <sub>CC</sub> | -10    |     | 10   | μA   |

| Ci              | Input capacitance                   | $V_{IL}=0V$ , f=1MHz, 25mVrms, Ta=25°C                    |        |     | 10   | pF   |

| Ci/o            | Input/output terminal capacitance   | $V_{I/OL}=0V$ , f=1MHz, 25mVrms, T <sub>a</sub> =25°C     |        |     | 20   | pF   |

| Icc             | Supply current from V <sub>CC</sub> | V <sub>SS</sub> =0V                                       |        |     | 180  | mA   |

Note 1 : Current flowing into an IC is positive, out is negative.

# M5L8156P

## 2048-BIT STATIC RAM WITH I/O PORTS AND TIMER

| Symbol               | Parameter                          | Alternative<br>symbol | Test conditions | Limits |     |     |      |

|----------------------|------------------------------------|-----------------------|-----------------|--------|-----|-----|------|

|                      |                                    |                       |                 | Min    | Тур | Max | Unit |

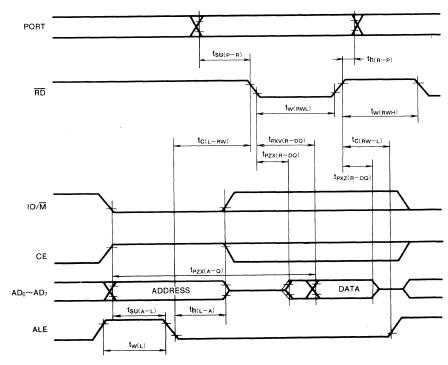

| tsu(A-L)             | Address setup time before latch    | t <sub>AL</sub>       |                 | 50     |     |     | ns   |

| th(L-A)              | Address hold time after latch      | t <sub>LA</sub>       |                 | 80     |     |     | ns   |

| th(L-RWH)            | Read/write hold time after latch   | t <sub>LC</sub>       |                 | 100    |     |     | ns   |

| t <sub>W(L)</sub>    | Latch pulse width                  | t <sub>LL</sub>       |                 | 100    |     |     | ns   |

| th(RW-L)             | Latch hold time after read/write   | t <sub>CL</sub>       |                 | 20     |     |     | ns   |

| t <sub>W(RWL)</sub>  | Read/write low-level pulse width   | t <sub>cc</sub>       |                 | 250    |     |     | ns   |

| t <sub>su(D-w)</sub> | Data setup time before write       | t <sub>DW</sub>       |                 | 150    |     |     | ns   |

| th(w-D)              | Data hold time after write         | t <sub>WD</sub>       |                 | 0      |     |     | ns   |

| t <sub>w(RWH)</sub>  | Read/write high-level pulse width  | t <sub>RV</sub>       |                 | 300    |     |     | ns   |

| t <sub>su(P-R)</sub> | Port setup time before read        | t <sub>PR</sub>       |                 | 70     |     |     | ns   |

| th(R-P)              | Port hold time after read          | t <sub>RP</sub>       |                 | 50     |     |     | ns   |

| t <sub>w(stb)</sub>  | Strobe pulse width                 | t <sub>ss</sub>       |                 | 200    |     |     | ns   |

| tsu(p-STB)           | Port setup time before strobe      | t <sub>PSS</sub>      |                 | 50     |     |     | ns   |

| th(stb-p)            | Port hold time after strobe        | t <sub>PHS</sub>      |                 | 120    |     |     | ns   |

| t <sub>w(∳H)</sub>   | Timer input high-level pulse width | t <sub>2</sub>        |                 | 120    |     |     | ns   |

| t <sub>w(∳L)</sub>   | Timer input low-level pulse width  | t <sub>1</sub>        |                 | 80     |     |     | ns   |

| t <sub>c(≠)</sub>    | Timer input cycle time             | t <sub>CYC</sub>      |                 | 320    |     |     | ns   |

| t <sub>r(≠)</sub>    | Timer input rise time              | tr                    |                 |        |     | 30  | ns   |

| t <sub>f(∳)</sub>    | Timer input fall time              | tf                    |                 |        |     | 30  | ns   |

## TIMING REQUIREMENTS ( $T_a = -20 \sim 75$ °C, $V_{cc} = 5 V \pm 5 \%$ , unless otherwise noted)

## SWITCHING CHARACTERISTICS ( $T_a = -20 \sim 75$ °C, $V_{cc} = 5 V \pm 5 \%$ , unless otherwise noted.)

| Symbol                    | Parameter                                            | Alternative<br>symbol |                 | Limits |     |     |      |

|---------------------------|------------------------------------------------------|-----------------------|-----------------|--------|-----|-----|------|

|                           |                                                      |                       | lest conditions | Min    | Тур | Max | Unit |

| $t_{PXV(R-DQ)}$           | Propagation time from read to data output            | t <sub>RD</sub>       |                 |        |     | 170 | ns   |

| t <sub>PZX(A-DQ)</sub>    | Propagation time from address to data output         | t <sub>AD</sub>       |                 |        |     | 400 | ns   |

| t <sub>PVZ(R-DQ)</sub>    | Propagation time from read to data floating (Note 7) | t <sub>RDF</sub>      |                 | 0      | 5   | 100 | ns   |

| t <sub>PHL(W-P)</sub>     | Propagation time from write to data output           | t <sub>WP</sub>       |                 |        |     | 400 | ns   |

| t <sub>PLH(W-P)</sub>     |                                                      | twe                   |                 |        |     |     |      |

| t <sub>PLH(STB-BF)</sub>  | Propagation time from strobe to BF flag              | t <sub>SBF</sub>      |                 |        |     | 400 | ns   |

| t <sub>PHL(R-BF)</sub>    | Propagation time from read to BF flag                | t <sub>RBE</sub>      |                 |        |     | 400 | ns   |

| tplh(stb-intr)            | Propagation time from strobe to interrupt            | t <sub>SI</sub>       |                 |        |     | 400 | ns   |

| t <sub>PHL(R-INTR)</sub>  | Propagation time from read to interrupt              | t <sub>RDI</sub>      |                 |        |     | 400 | ns   |

| t <sub>PHL(STB-BF</sub> ) | Propagation time from strobe to BF flag              | t <sub>SBE</sub>      |                 |        |     | 400 | ns   |

| t <sub>PLH(W-BF)</sub>    | Propagation time from write to BF flag               | t <sub>WBF</sub>      |                 |        |     | 400 | ns   |

| t <sub>PHL(W-INTR)</sub>  | Propagation time from write to interrupt             | t <sub>wi</sub>       |                 | 1      |     | 400 | ns   |

| t <sub>PHL</sub> ( #-OUT) | _                                                    | t <sub>TL</sub>       |                 |        |     |     |      |

| t <sub>PLH</sub> (∮-OUT)  | Propagation time from timer input to timer output    | t <sub>TH</sub>       |                 |        |     | 400 | ns   |

| t <sub>PZX(R-DQ)</sub>    | propagation time from read to data enable            | t <sub>RDE</sub>      |                 | 10     |     |     | ns   |

Note 1 : Measurement conditions C=150pF 2 : Measurement conditions of note 6 are not applied.

# M5L8156P

2048-BIT STATIC RAM WITH I/O PORTS AND TIMER

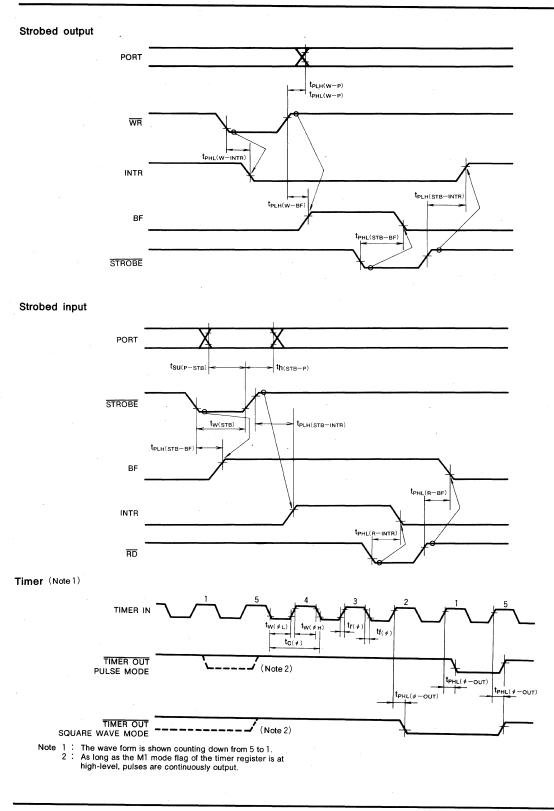

PORT  $\substack{t_{\mathsf{PHL}(\mathbf{W}-\mathbf{P})}\\t_{\mathsf{PLH}(\mathbf{W}-\mathbf{P})}}$ WR  $t_{W(RWH)}$  $t_{W(RWL)}$  $t_{h(L-RWH)}$ th(w-D) 10/M CE AD<sub>0</sub>~AD<sub>7</sub> ADDRESS DATA t<sub>su(D-W)</sub> th(RW-L)  $t_{SU(A-L)}$  $t_{h(L-A)}$ ALE t<sub>W(L)</sub>

$\label{eq:time_state} \textbf{TIMING DIAGRAM} \hspace{0.1in} (reference \hspace{0.1in} \mathsf{level} \hspace{-0.1in}, \hspace{-0.1in} \mathsf{high-level} \hspace{-0.1in} = \hspace{-0.1in} 2V \hspace{0.1in}, \hspace{0.1in} \mathsf{low-level} \hspace{-0.1in} = \hspace{-0.1in} 0.8V)$

## Basic output

Basic input

## **MITSUBISHI LSIs**

# M5L8156P