# M61044FP

# 3-Battery Version, Reset Pin

REJ03F0066-0100Z Rev.1.0 Sep.19.2003

## **Description**

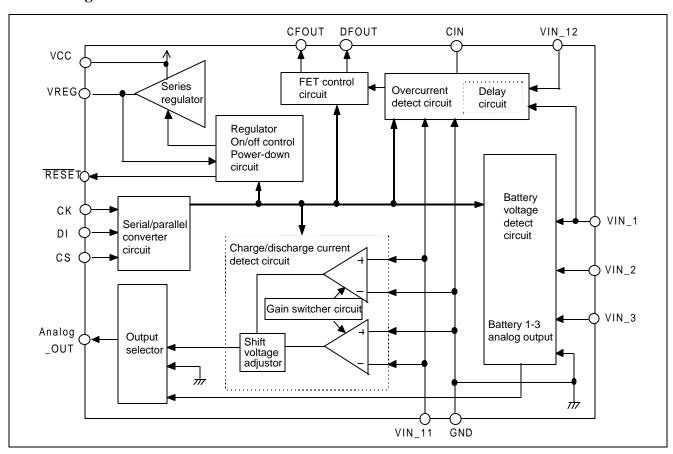

The M61044FP is an semiconductor IC device developed for smart battery packs. It incorporates all the analog circuitry required by smart batteries in a single chip. When used in conjunction with a microprocessor, it allows the implementation of a variety of functions, such as battery capacity detection, through the addition of minimal peripheral devices and is ideal for smart battery system (SBS) battery packs.

The M61044FP also has an on-chip overcurrent detect circuit so that the FET for controlling battery charging and discharging is protected regardless of the processing speed of the microprocessor.

The microprocessor can change the amplifier gain of the charge/discharge current detect circuit, so battery capacity detection accuracy is increased. In addition, the M61044FP incorporates a linear regulator that allows it to function as the power supply for the microprocessor, thereby simplifying power supply block design.

#### **Features**

- · On-chip high-gain op-amp for monitoring charge and discharge current.

- On-chip overcurrent detect circuit to protect FET.

- Charge/discharge FET can be controlled from microprocessor.

- Power-save function for reducing current consumption.

- 3.3 V operation to reduce microprocessor current consumption.

- High-voltage device (absolute maximum rating: 33 V).

#### Application

Smart battery system (SBS) battery packs

This product is currently under development, and its specifications, pin assignments, etc., are subject to change.

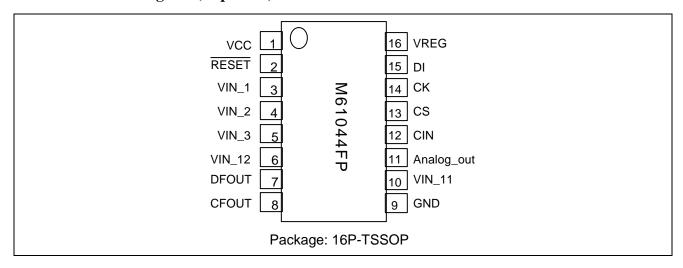

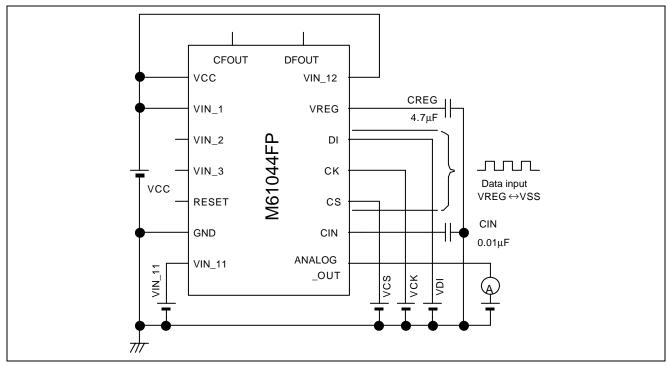

#### **Pin Connection Diagram (Top View)**

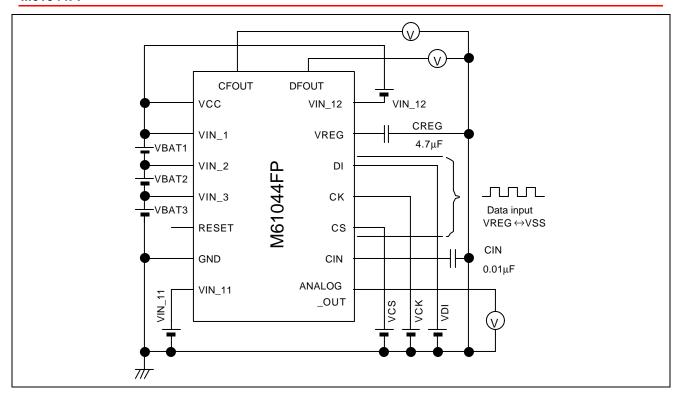

## **Block Diagram**

## **Pin Function**

Table 1

| Pin No. | Symbol     | Function                                                                                                                                                                                   |

|---------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | Vcc        | The chip's power supply pin. Power is supplied by the charger or the battery.                                                                                                              |

| 2       | RESET      | Output pin for microprocessor reset signal.                                                                                                                                                |

| 3       | VIN_1      | Positive input pin for lithium ion battery 1.                                                                                                                                              |

| 4       | VIN_2      | Negative input pin for lithium ion battery 1. Positive input pin for lithium ion battery 2.                                                                                                |

| 5       | VIN_3      | Negative input pin for lithium ion battery 2. Positive input pin for lithium ion battery 3.                                                                                                |

| 6       | VIN_12     | Charger connect monitor pin. Detects changes from power-down status.                                                                                                                       |

| 7       | DFOUT      | Output pin for discharge FET on/off signals. Also turns off when overcurrent detected.                                                                                                     |

| 8       | CFOUT      | Output pin for charge FET on/off signals.                                                                                                                                                  |

| 9       | GND        | Ground pin. Negative input pin for lithium ion battery 3. Connected to charge/discharge current sensor resistor.                                                                           |

| 10      | VIN_11     | Charge/discharge current monitor pin. Connected to charge/discharge current sensor resistor.                                                                                               |

| 11      | Analog_OUT | Output pin for analog signals.                                                                                                                                                             |

| 12      | CIN        | Capacity connection pin for setting overcurrent prevention delay time.                                                                                                                     |

| 13      | CS         | When this pin is low level, data input is accepted and data can be stored in a 6-bit shift register. At the rising edge from low to high the value in the 6-bit shift register is latched. |

| 14      | СК         | Shift clock input pin. At the rising edge to high the input signal from the DI pin is input to the 6-bit shift register.                                                                   |

| 15      | DI         | Shift data input pin. Serial data with a data length of 6 bits may be input via this pin.                                                                                                  |

| 16      | Vreg       | Power supply pin for microprocessor. Power can be shut off using a signal from the microprocessor.                                                                                         |

## **Operation**

The M61044FP is an semiconductor IC device developed for smart battery packs. It is ideal for smart battery system (SBS) battery packs that consist of four lithium ion batteries connected in series. A high-voltage device, it is suitable for use with a wide variety of charger systems.

It incorporates all the analog circuitry required by smart batteries in a single chip. When used in conjunction with a microprocessor, it allows the implementation of a variety of functions, such as battery capacity detection, through the addition of minimal peripheral devices. The functions of the M61044FP are described below.

#### 1. Battery Voltage Detect Circuit

The M61044FP can output the voltage levels of the batteries connected in series via the Analog\_out pin. An on-chip buffer amplifier monitors the pin voltages of the batteries. Offset voltage correction using adjustment by the microprocessor is also supported. The M61044FP is configured to detect the battery voltage using a microprocessor driven using a power supply voltage of 5.2 V.

#### 2. Charge/Discharge Current Detect Circuit

SBS requires a function for monitoring the battery capacity. The M61044FP uses an on-chip amplifier to monitor battery capacity based on a drop in the voltage of an external sensor resistor. In this way, the charge/discharge current is converted into a voltage.

The voltage amplification ratio can be adjusted from the microprocessor. In addition, the current output shift voltage can be adjusted from the microprocessor, widening the allowable dynamic range of the A/D converter.

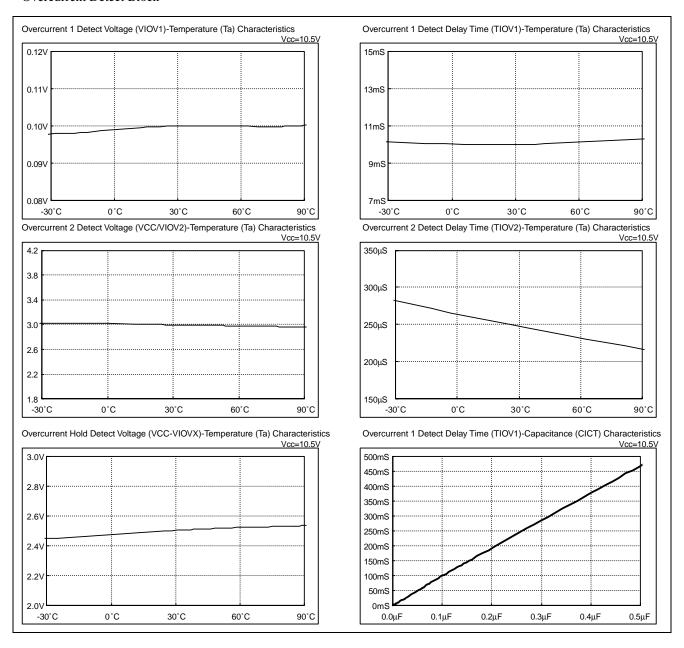

#### 3. Overcurrent Detect Circuit

The M61044FP has an on-chip overcurrent detect circuit. If an excessive current flows from the lithium ion batteries, the discharge control FET is shut off after a set delay time, halting discharge. This makes the battery pack safer. The delay time can be set using an external capacitor. It is possible to determine the overcurrent detect status by monitoring the CIN pin. The overcurrent detect circuit provides protection regardless of the processing speed of the microprocessor.

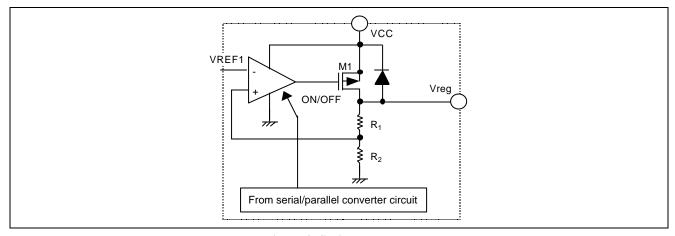

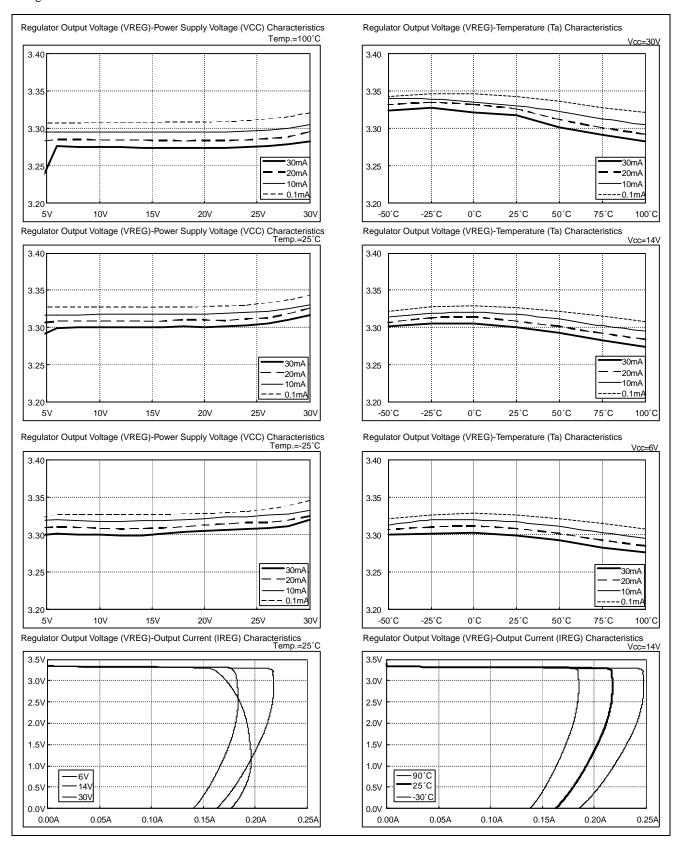

#### 4. Series Regulator

The M61044FP has an on-chip low-dropout series regulator. It can be used as the power supply for the microprocessor, thereby simplifying power supply block design.

Figure 3 Series Regulator

#### 5. Reset Circuit

The reset circuit of the M61041FP monitors the voltage of the Vreg pin. If the power supply voltage of the microprocessor drops the reset circuit operates, preventing microprocessor runaway. Microprocessor runaway is avoided because the microprocessor is reset if the battery pack left standing and the battery voltage is allowed to drop. This enhances the safety of battery packs that are left unused.

In addition, reset circuit monitors the voltage of the Vreg pin when the battery pack is connected to the charger, ensuring that a reset will be applied if the voltage supplied to the microprocessor becomes excessively small. This helps to guarantee reliable operation.

#### 6. Power-Save Function

The M61044FP is equipped with a power-save function.

When the battery voltage is being monitored a portion of the charge/discharge current monitor circuit automatically stops operating, and when the charge/discharge current is being monitored the battery voltage monitor circuit automatically stops operating. This helps prevent unnecessary power consumption. In addition, current consumption is further reduced by setting the analog output selector to ground potential output when in the standby mode.

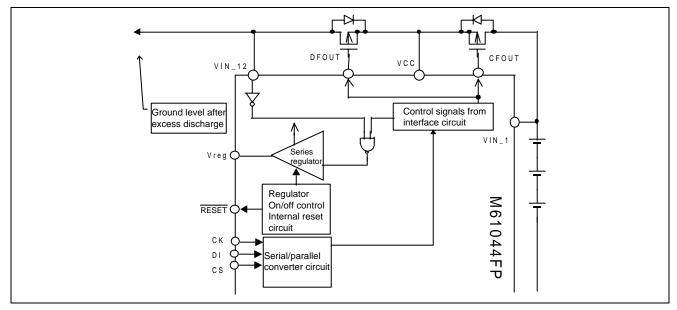

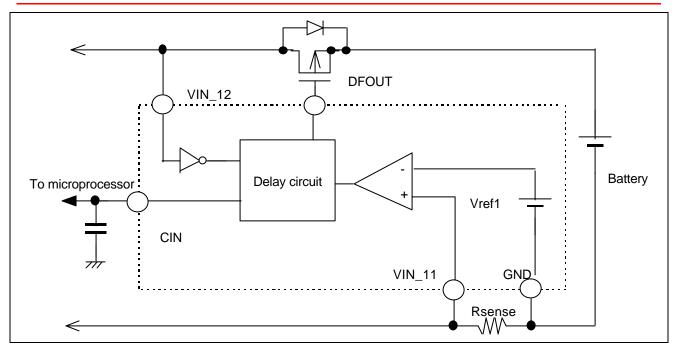

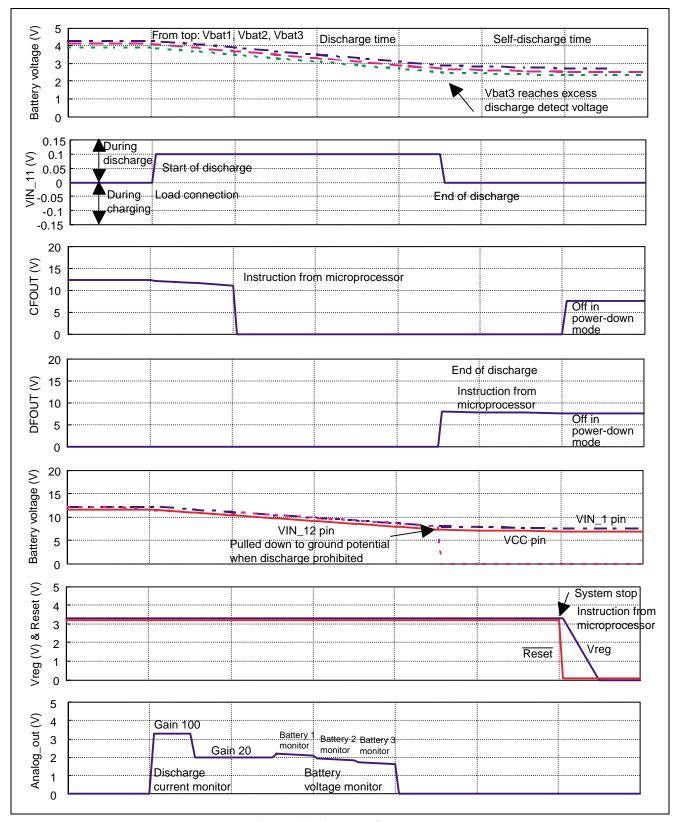

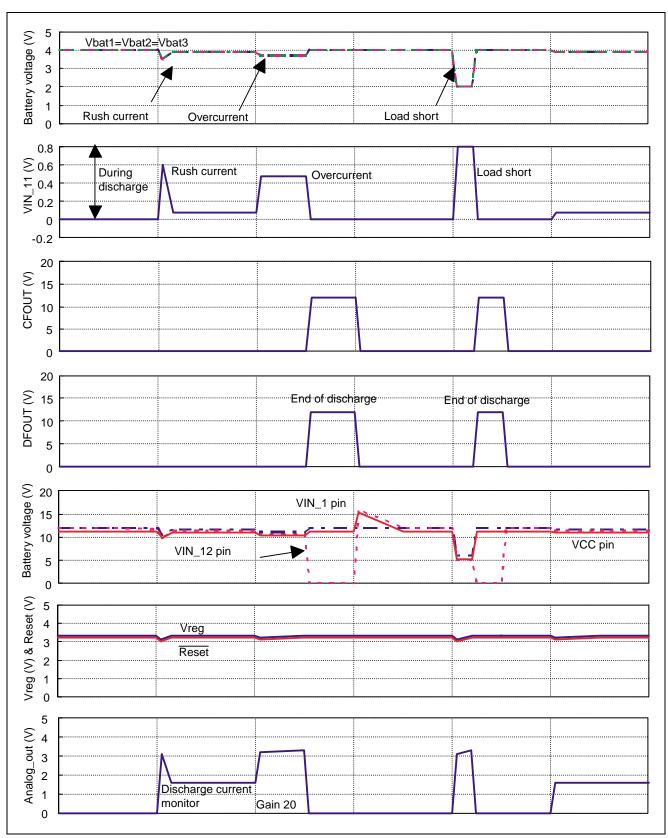

#### **Transition to Power-Down Mode**

When the microprocessor determines that the battery voltage has dropped it sends a power-down instruction via the interface circuit. When it receives the instruction, the M61044FP's DFOUT pin switches to high voltage. In addition, the VIN\_12 pin is pulled down to low level by an internal resistor. When the VIN\_12 pin goes to low potential after reception of the power-down instruction, output from the series regulator stops, switching the M61044FP into power-down mode.

At this point the operation of the circuitry is completely halted. In this status CFOUT is high level and DFOUT is high level (external charge/discharge prohibited status). The maximum current consumption of the M61044FP is  $1.0~\mu A$  in order to prevent any further drop in the battery voltage.

Figure 4 Operation After Excess Discharge Detection

#### **Cancellation of Power-Down Mode**

If the battery pack is connected to a charger when the M61044FP is in the power-down mode (VIN\_12 becomes high level), the series regulator immediately begins to operate. The power-down mode is canceled, and once again the M61044FP is ready to receive instructions from the microprocessor.

## **Absolute Maximum Ratings**

Table 2

| Item                          | Symbol | Rated Value | Unit | Conditions |

|-------------------------------|--------|-------------|------|------------|

| Absolute maximum rating       | Vabs   | 33          | V    |            |

| Power supply voltage          | Vcc    | 30          | V    |            |

| Allowable loss                | PD     | 500         | mW   |            |

| Ambient operating temperature | Topr   | -20 to +85  | °C   |            |

| Storage temperature           | Tstg   | -40 to +125 | °C   |            |

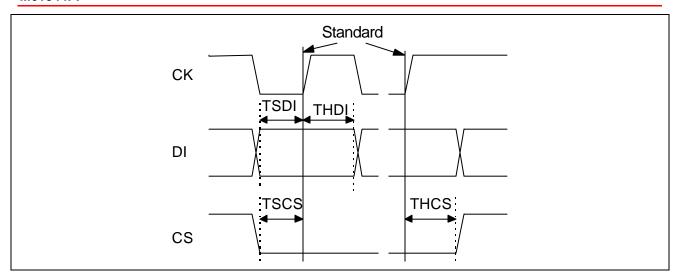

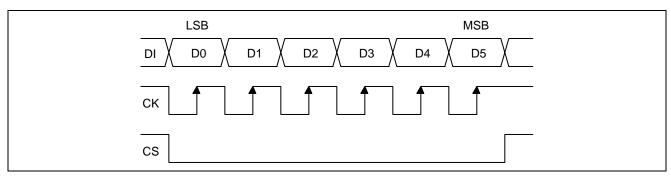

**Figure 5 Interface Block Timing Definitions**

# **Electrical Characteristics**

Table 3

$(Ta = 25^{\circ}C, Vcc = 14 \text{ V unless otherwise specified})$

|                    | Item                                    |          | Rated Value   |       |               | _    |         |         |                                            |

|--------------------|-----------------------------------------|----------|---------------|-------|---------------|------|---------|---------|--------------------------------------------|

| Block              |                                         | Symbol   | Min.          | Тур.  | Max.          | Unit | Circuit | Command | Conditions                                 |

| All                | Power supply voltage                    | Vsup     | _             | _     | 30            | V    | 1       | _       |                                            |

|                    | Circuit current 1                       | Isup1    | 60            | 150   | 215           | μА   | 1       | 1       | During charge/discharge current monitoring |

|                    | Circuit current 2                       | Isup2    | 55            | 140   | 200           | μА   | 1       | 2       | During battery voltage monitoring          |

|                    | Circuit current 3                       | Isup3    | 25            | 80    | 115           | μА   | 1       | 3       | During ground output (initial status)      |

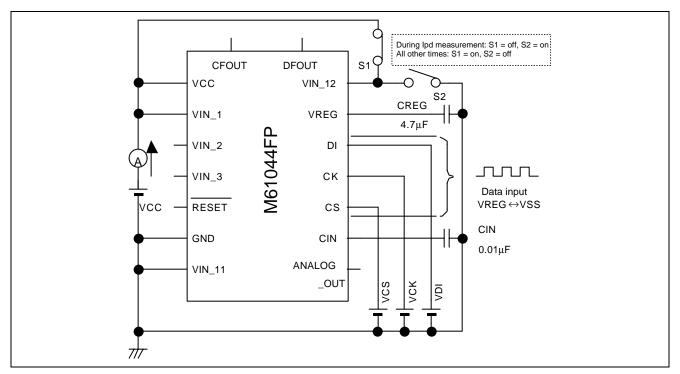

|                    | Circuit current<br>(power-down<br>mode) | lpd      | _             | _     | 0.5           | μА   | 1       | 4       | All circuits halted,<br>VIN_12 = GND       |

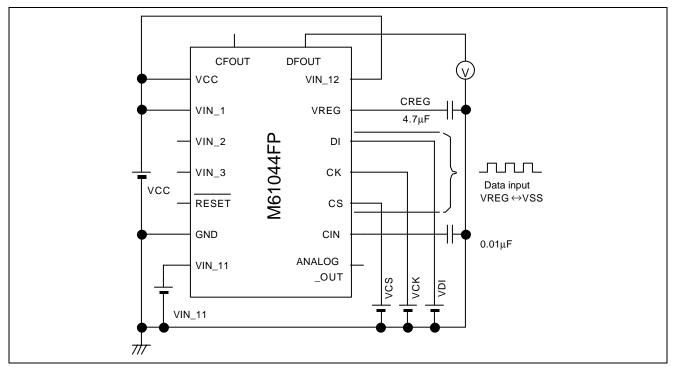

| Regulator          | Output voltage                          | Vreg     | 3.220         | 3.3   | 3.380         | V    | 2       | _       | Vcc = 10.5V, lout = 30mA                   |

|                    | Input stability                         | ∆Vout10  | _             | 60    | 100           | mV   | 2       | _       | Vcc = 6.0V to 24V, lout = 30mA             |

|                    | Load stability                          | ∆Vout20  | _             | 30    | 50            | mV   | 2       | _       | Vcc = 6.0V, lout = 0.1mA to 30mA           |

|                    | Input voltage<br>(VCC pin)              | VIN0     | 6.0           | _     | 30            | V    | 2       | _       |                                            |

|                    | Reset detect voltage 1                  | Vdet-    | 2.600         | 2.750 | 2.900         | V    | 2       | _       |                                            |

|                    | Reset cancel voltage 1                  | Vdet+    | 2.900         | 2.975 | 3.050         | V    | 2       | _       |                                            |

| Overcurrent detect | Overcurrent prevention voltage 1        | Vd1      | 0.08          | 0.1   | 0.12          | V    | 3       | 5       |                                            |

|                    | Overcurrent prevention voltage 2        | Vd2      | Vcc/3<br>×0.6 | Vcc/3 | Vcc/3<br>×1.4 | V    | 4       | 5       | Load short detected                        |

|                    | Overcurrent prevention delay time 1     | Tvd1     | 7             | 10    | 15            | ms   | 3       | 5       | CICT = 0.01μF                              |

|                    | Overcurrent prevention delay time 2     | Tvd2     | 150           | 250   | 350           | μs   | 4       | 5       |                                            |

| Battery<br>voltage | Input offset voltage 1                  | Voff1    | 31            | 206   | 385           | mV   | 5       | 6       |                                            |

| detect             | Voltage<br>amplification<br>ratio 1     | Gamp1    | 0.594         | 0.600 | 0.606         | _    | 5       | 7       |                                            |

|                    | Output source current capacity          | Isource1 | 150           | _     | _             | μА   | 6       | 8       |                                            |

|                    | Output sink current capacity            | Isink1   | 150           | _     | _             | μА   | 6       | 9       |                                            |

|                    | Maximum<br>detect battery<br>voltage    | Vmo_max  | 4.64          | _     | _             | V    | 5       | _       | (Vreg-Voff1)/Gamp1                         |

RENESAS

|                      |                                      |          | Rated Value |      |      |      |         |         |            |

|----------------------|--------------------------------------|----------|-------------|------|------|------|---------|---------|------------|

| Block                | Item                                 | Symbol   | Min.        | Тур. | Max. | Unit | Circuit | Command | Conditions |

| Charge/disc<br>harge | Input offset voltage                 | Voff2    | 0.5         | 1.2  | 1.9  | V    | 7       | 10*     | Gain = 100 |

| current<br>detect    | Voltage<br>amplification<br>ratio 21 | Gain21   | 19.2        | 20   | 20.8 |      | 7       | 11*     |            |

|                      | Voltage<br>amplification<br>ratio 22 | Gain22   | 38.4        | 40   | 41.6 |      | 7       | 12*     |            |

|                      | Voltage<br>amplification<br>ratio 23 | Gain23   | 96          | 100  | 104  |      | 7       | 13*     |            |

|                      | Current output shift voltage 1       | Vios1    | 0.36        | 0.41 | 0.46 | V    | 7       | 14*     |            |

|                      | Current output shift voltage 2       | Vios2    | 0.76        | 0.83 | 0.90 | V    | 7       | 15*     |            |

|                      | Current output shift voltage 3       | Vios3    | 1.14        | 1.24 | 1.34 | V    | 7       | 16*     |            |

|                      | Current output shift voltage 4       | Vios4    | 1.53        | 1.65 | 1.77 | V    | 7       | 17*     |            |

|                      | Output source current capacity       | Isource2 | 150         | _    | _    | μΑ   | 8       | 18*     |            |

|                      | Output sink current capacity         | Isink2   | 150         | _    | _    | μΑ   | 8       | 18*     |            |

| Interface            | DI input H<br>voltage                | VDIH     | Vreg-0.5    | _    | Vreg | V    | 9       | _       |            |

|                      | DI input L<br>voltage                | VDIL     | 0           | _    | 0.5  | V    | 9       | _       |            |

|                      | CS input H<br>voltage                | VCSH     | Vreg-0.5    | _    | Vreg | V    | 9       | _       |            |

|                      | CS input L<br>voltage                | VCSL     | 0           | _    | 0.5  | V    | 9       | _       |            |

|                      | CK input H<br>voltage                | VCKH     | Vreg-0.5    | _    | Vreg | V    | 9       | _       |            |

|                      | CK input L voltage                   | VCKL     | 0           |      | 0.5  | V    | 9       | _       |            |

|                      | DI setup time                        | TSDI     | 600         | _    | _    | ns   | 9       | _       |            |

|                      | DI hold time                         | THDI     | 600         | _    |      | ns   | 9       | _       |            |

|                      | CS setup time                        | TSCS     | 600         | _    | _    | ns   | 9       | _       |            |

|                      | CS hold time                         | THCS     | 600         | _    |      | ns   | 9       | _       |            |

Refer to figures 1 to 9 for the circuits and to table 4 for the command sequences used for measurement.

<sup>\*</sup> For the charge/discharge current detect block, different command sequences are used during charging and discharging.

# **Measurement Circuit Diagrams**

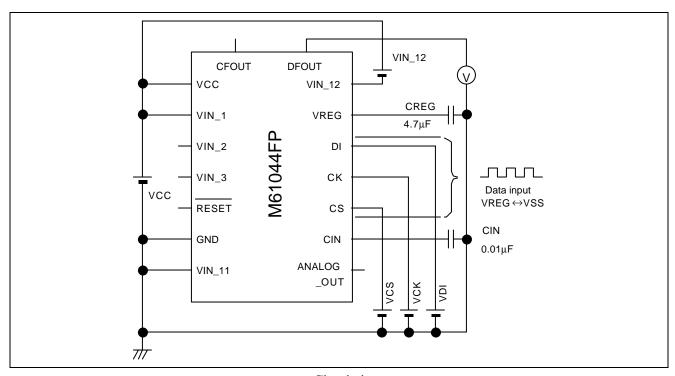

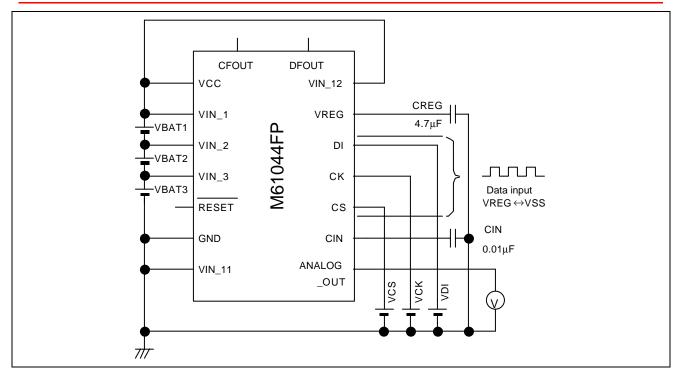

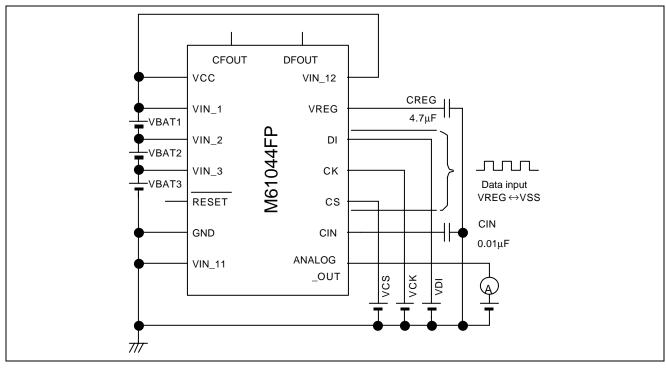

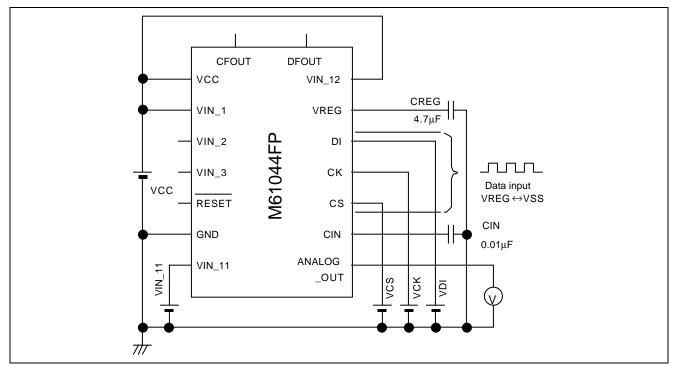

Circuit 1

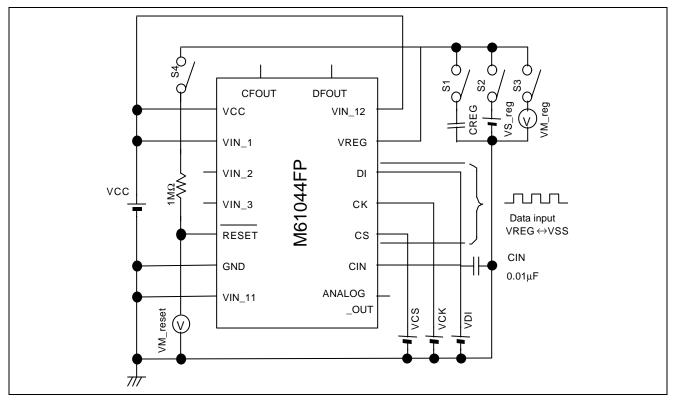

Circuit 2

Circuit 3

Circuit 4

Circuit 5

Circuit 6

Circuit 7

**Circuit 8**

Circuit 9

**Table 4 Command Sequences Used for Measuring Rated Values**

| No | Command Sequence                                                                                        | VIN_11 Input |

|----|---------------------------------------------------------------------------------------------------------|--------------|

| 1  | $(00)_{_8} \rightarrow (24)_{_8} \rightarrow (31)_{_8} \rightarrow (43)_{_8} \rightarrow (52)_{_8}$     | 90mV         |

| 2  | $(00)_{_8} \rightarrow (10)_{_8} \rightarrow (43)_{_8} \rightarrow (51)_{_8}$                           | 0mV          |

| 3  | (00) <sub>8</sub>                                                                                       | 0mV          |

| 4  | $(00)_{8} \rightarrow (71)_{8}$                                                                         | 0mV          |

| 5  | $(00)_{_8} \rightarrow (43)_{_8}$                                                                       | 0mV          |

| 6  | $(00)_8 \rightarrow (51)_8 \rightarrow (14)_8 \rightarrow (15)_8 \rightarrow (16)_8 \rightarrow (17)_8$ | 0mV          |

| 7  | $(00)_8 \rightarrow (51)_8 \rightarrow (10)_8 \rightarrow (11)_8 \rightarrow (12)_8 \rightarrow (13)_8$ | 0mV          |

| 8  | $(00)_{_8} \rightarrow (51)_{_8} \rightarrow (13)_{_8}$                                                 | 0mV          |

| 9  | $(00)_{_8} \rightarrow (51)_{_8} \rightarrow (17)_{_8}$                                                 | 0mV          |

| 10 | $(00)_{_8} \rightarrow (43)_{_8} \rightarrow (52)_{_8} \rightarrow (37)_{_8}$                           | 0mV          |

| 11 | $(00)_{_8} \rightarrow (43)_{_8} \rightarrow (52)_{_8} \rightarrow (31)_{_8} \rightarrow (35)_{_8}$     | 90mV         |

| 12 | $(00)_{_8} \rightarrow (43)_{_8} \rightarrow (52)_{_8} \rightarrow (32)_{_8} \rightarrow (36)_{_8}$     | 45mV         |

| 13 | $(00)_{_8} \rightarrow (43)_{_8} \rightarrow (52)_{_8} \rightarrow (33)_{_8} \rightarrow (37)_{_8}$     | 7mV          |

| 14 | $(00)_{_8} \rightarrow (43)_{_8} \rightarrow (52)_{_8} \rightarrow (31)_{_8} \rightarrow (24)_{_8}$     | 90mV         |

| 15 | $(00)_{_8} \rightarrow (43)_{_8} \rightarrow (52)_{_8} \rightarrow (31)_{_8} \rightarrow (25)_{_8}$     | 90mV         |

| 16 | $(00)_{_8} \rightarrow (43)_{_8} \rightarrow (52)_{_8} \rightarrow (31)_{_8} \rightarrow (26)_{_8}$     | 90mV         |

| 17 | $(00)_{_8} \rightarrow (43)_{_8} \rightarrow (52)_{_8} \rightarrow (31)_{_8} \rightarrow (27)_{_8}$     | 90mV         |

| 18 | $(00)_8 \rightarrow (43)_8 \rightarrow (52)_8 \rightarrow (31)_8$                                       | 45mV         |

Notes: 1. Indications such as (00)<sub>8</sub> show the address and data, in that order, of the serial data from the microprocessor in octal notation.

- 2. Numbers 10 to 17 are command sequences used during charging. For the commands used during discharging, substitute (53), for (52),

- 3. During measurement, the voltage listed in table 4 should be input to VIN\_11. When measuring during charging, the specified voltage should be input to VIN\_11 as a negative voltage. The specified voltage should be input to VIN\_11 as a positive voltage during discharging.

## **Description of Circuit Blocks**

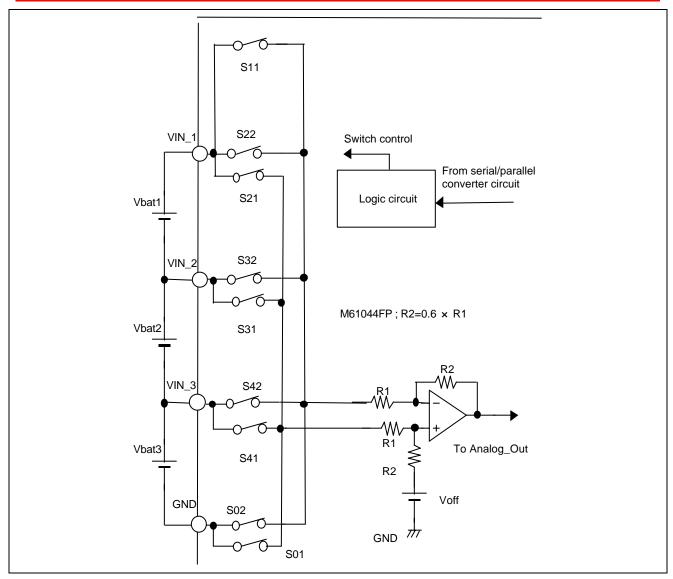

#### (1) Battery Voltage Detect Circuit

As shown in figure 6, the battery voltage detect circuit block of the M61044FP consists of switches, a buffer amplifier, a reference voltage circuit, and a logic circuit.

When the voltage to be detected is selected, based on serial data from the microprocessor, the appropriate switch connections are determined by the logic circuit. The voltages Vbat1, Vbat2, and Vbat3 from the batteries connected to the M61044FP, multiplied by Gamp1 (0.6), are output from the Analog\_out pin. It is also possible to output an offset voltage.

In the power-save mode all the switches are turned off, so the current consumption of this circuit block is zero.

Note: The settling time of this circuit block after voltage changes is about 50 µs.

Figure 6 Battery Voltage Detect Circuit

#### Battery Voltage Monitoring Method

To select battery voltage detection, serial data  $(51)_8$  is sent from reset status  $(00)_8$ . The V1 battery voltage (Vin1) is output from the analog output pin by sending  $(10)_8$ . Next,  $(15)_8$  is sent to switch the analog output pin from the V1 battery voltage to the V1 offset voltage (Voff1). The actual voltage (Vbat1) can be obtained by the microprocessor by calculating  $\underline{\text{Vbat1}} = \underline{(\text{Vin1} - \text{Voff1}) / \text{Gamp}}$ . The same method can be used for Vbat2 and Vbat3 in order to monitor the battery voltage with a high degree of accuracy.

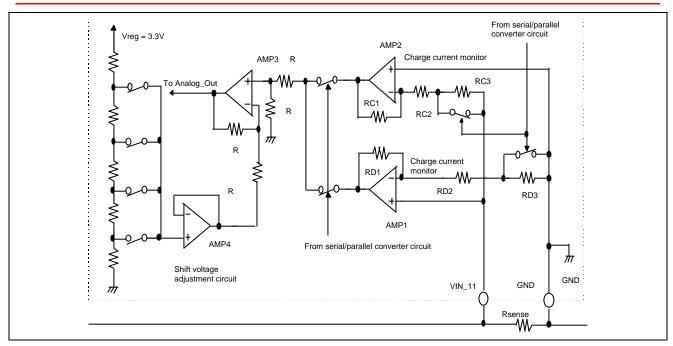

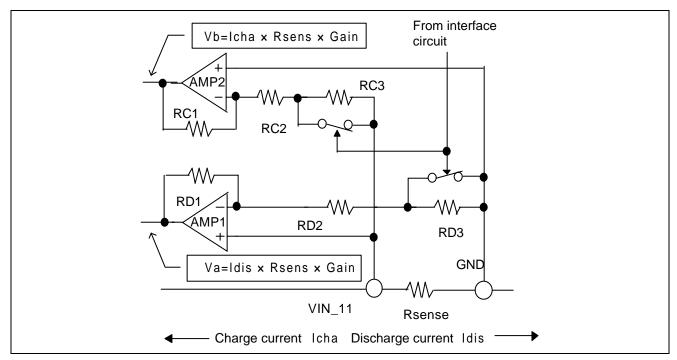

#### (2) Charge/Discharge Current Detect Block

As shown in figure 7, the charge/discharge current detect block of the M61044FP consists of a preamplifier current output shift voltage adjustment circuit, a buffer amplifier, and dividing resistors.

The voltage difference indicated by the sensor resistor is amplified to the ground reference voltage by the preamplifier. The gain can be switched using serial signals from the microprocessor. The output is impedance converted by the buffer amplifier.

It is also possible to switch the current detect shift voltage using the microprocessor.

Figure 7 Charge/Discharge Current Detect Block

Figure 8 illustrates the circuit block's operation during discharge current detection. The discharge current flows into Rsense, and any voltage drop that occurs is applied to the positive terminal of the amplifier (AMP1). The amplifier's gain can be increased by an instruction from the microprocessor, making it possible to monitor even minute discharge currents with high accuracy.

To allow monitoring of the charge current, the voltage generated by VIN\_11 is inverted and amplified before being output. The other aspects use the same operating principle as that described above.

Figure 8 Charge/Discharge Current Detect Explanation Diagram

#### Charge Current Monitoring Method

Serial data (43)<sub>8</sub> is sent from reset status to turn on the discharge control FET. When the charger is connected in this status a current flows between the VIN\_11 pin and the GND pin (across the RSENSE sensor transistor), causing the voltage Vin1 to be generated. Sending (52)<sub>8</sub> switches the output of the analog output pin to charge current output. At this point the amplifier used for monitoring the charge current is still off, so the analog output pin outputs ground potential. Next, a value between (35)<sub>8</sub> and (37)<sub>8</sub> is selected to switch the amplifier's amplification ratio. In this way the amplification ratio of the amplifier used for monitoring the charge current is switched to GainC. At this point the voltage of the analog output pin is the offset voltage of the charge current monitor amplifier (VoffC).

If the offset voltage VoffC is higher than the value listed in table 5, the shift voltage select command between (24)<sub>8</sub> and (27)<sub>8</sub> that corresponds to VoffC is sent and once again the offset voltage is measured, this time as VoffC\_S. Next, a value between (31)<sub>8</sub> and (33)<sub>8</sub> is selected to switch the current monitor amplifier's amplification ratio. At this point the voltage of the analog output pin is VaoutC. It is possible to calculate the charge current based on the analog output pin voltages resulting from the above settings. When calculating the current value, VoffC\_S offset and VaoutC current monitor values measured using the same amplification ratio should be used. Table 6 is a list of the measurable current values.

```

Icha (charge current) = Vin1 \div RSENSE (sensor resistor value) ... (1)

VaoutC - VoffC_S = Vin1 \times GainC ... (2)

Based on (1) and (2) it is possible to calculate the charge current.

Icha (charge current) = (VaoutC - VoffC_S) \div GainC \div RSENSE

```

#### Discharge Current Monitoring Method

Serial data (43)<sub>8</sub> is sent from reset status to turn on the discharge control FET. When a load is connected in this status a current flows between the VIN\_11 pin and the GND pin (across the RSENSE sensor transistor), causing the voltage Vin1 to be generated. Sending (53)<sub>8</sub> switches the output of the analog output pin to discharge current output. At this point the amplifier used for monitoring the discharge current is still off, so the analog output pin outputs ground potential. Next, a value between (35)<sub>8</sub> and (37)<sub>8</sub> is selected to switch the amplifier's amplification ratio. In this way the amplification ratio of the amplifier used for monitoring the discharge current is switched to GainD. At this point the voltage of the analog output pin is the offset voltage of the discharge current monitor amplifier (VoffD).

If the offset voltage VoffD is higher than the value listed in table 5, the shift voltage select command between (24)<sub>8</sub> and (27)<sub>8</sub> that corresponds to VoffD is sent and once again the offset voltage is measured, this time as VoffD\_S. Next, a value between (31)<sub>8</sub> and (33)<sub>8</sub> is selected to switch the current monitor amplifier's amplification ratio. At this point the voltage of the analog output pin is VaoutD. It is possible to calculate the discharge current based on the analog output pin voltages resulting from the above settings. When calculating the current value, VoffD\_S offset and VaoutD current monitor values measured using the same amplification ratio should be used. Table 6 is a list of the measurable current values.

```

Idis (discharge current) = Vin1 \div RSENSE (sensor resistor value) ... (1)

VaoutD – VoffD_S = Vin1 \times GainD ... (2)

Based on (1) and (2) it is possible to calculate the discharge current.

Idis (discharge current) = (VaoutD – VoffD_S) \div GainD \div RSENSE

```

#### Discharge Current Measurable Range

The range of discharge current values that can be measured is determined by the sensor resistor value, the Vreg voltage, and the amplification ratio of the current monitor amplifier. Refer to table 6 for details. The current value is proportional to the sensor resistor value, so if the sensor resistor value changes it is possible to determine the new measurable range of current values by multiplying the sensor resistor value by the current coefficient value listed in table 6.

Table 5 Shift Voltage Switching Offset Voltage

| Vreg Voltage | Measurement Offset Value | Shift Setting Voltage | Select Command    |

|--------------|--------------------------|-----------------------|-------------------|

| 3.3V         | 0.55V or higher          | -0.4V                 | (24) <sub>8</sub> |

| 3.3V         | 1.00V or higher          | -0.8V                 | (25) <sub>8</sub> |

| 3.3V         | 1.45V or higher          | -1.2V                 | (26) <sub>8</sub> |

| 3.3V         | 1.90V or higher          | -1.6V                 | (27) <sub>8</sub> |

**Table 6 Measurable Current Values**

|              |                                                  | Maximum Measurable Cur  |                                      |                                |

|--------------|--------------------------------------------------|-------------------------|--------------------------------------|--------------------------------|

| Vreg Voltage | Current Monitor Amplifier<br>Amplification Ratio | 20 mΩ Sensor Resistor∗¹ | Current<br>Coefficient* <sup>2</sup> | Minimum Resolution (10bit A/D) |

| 3.3V         | 20×                                              | 6.6A (Vcc = 7.0V)       | 0.131                                | 7.3mA                          |

| 3.3V         | 40×                                              | 3.3A (Vcc = 7.0V)       | 0.065                                | 3.6mA                          |

| 3.3V         | 100×                                             | 1.3A (Vcc = 7.0V)       | 0.027                                | 1.5mA                          |

Note \*1 The maximum measurable current value is dependent on the Vcc voltage. If the Vcc voltage drops the maximum measurable current value also drops.

Example: If the sensor resistor value = 15 m $\Omega$ , Vreg = 3.3 V, and the amplification ratio is  $20 \times ...$  Maximum measurable current value = 0.131(current coefficient)  $\div$  0.015 [ $\Omega$ ] = 8.73 [A] (sensor resistor value)

#### (3) Overcurrent Detect Circuit Block

As shown in figure 9, the overcurrent detect circuit block of the M61044FP consists of a comparator, a reference voltage circuit, and a delay circuit.

The detection voltage can be adjusted by trimming, making possible highly accurate voltage detection in conjunction with a sensor resistor. In addition, it is possible to determine when the M61044FP is in overcurrent detect status by monitoring the CIN pin using the microprocessor.

The M61044FP is also equipped with a simplified load detect circuit. Based on the status of the Vin12 pin it is possible to provide protection with a shorter delay time than when using overcurrent detection.

RENESAS

<sup>\*2</sup> If the sensor resistor value changes the current coefficient becomes the maximum measurable current value divided by the new sensor resistor value.

Figure 9 Overcurrent Detect Circuit Block

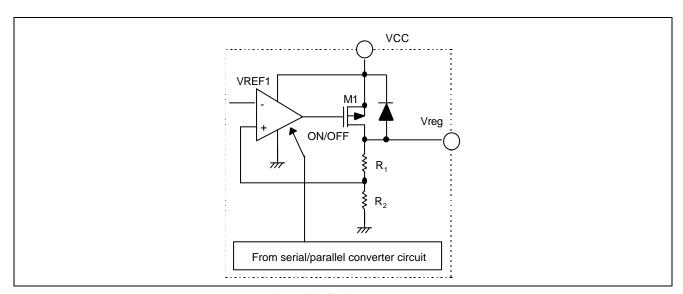

## (4) Series Regulator

The series regulator circuit is shown in figure 10. A Pch MOS transistor is used as the output control transistor. The output voltage is adjusted by the M61044FP internally, so no external devices, such as resistors, are required.

Note: Due to the structure of the control transistor a parasite diode is formed between VCC and Vreg. This means that the M61044FP can be destroyed by reverse current if the Vreg potential exceeds VCC. Consequently, Vreg should be limited to VCC + 0.3 V or less.

Figure 10 Series Regulator

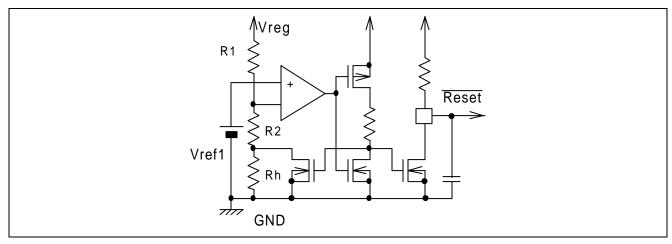

## (5) Reset Circuit Block

As shown in figure 11, the reset circuit block of the M61041FP consists of a converter, a reference voltage circuit, and bleeder resistors.

Output is via the Nch open drain circuit, so an external CR can be connected to specify the cancel delay time.

The reset circuit monitors the Vreg output and prevents microprocessor runaway if the power supply voltage should drop do to some sort of malfunction.

Figure 11 Reset Circuit Block

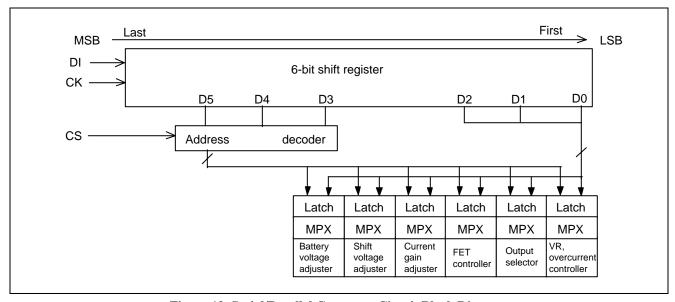

#### **Digital Data Format**

Figure 12 Serial/Parallel Converter Circuit Block Diagram

## **Data Timing Diagram (Model)**

Figure 13 Serial/Parallel Converter Circuit Timing Chart

#### **Data Content**

Table 7

|                                       | Addre | ess  |    | Data |    |    | <br>Content  |

|---------------------------------------|-------|------|----|------|----|----|--------------|

| Setting Data                          | D5    | 5 D4 | D3 | 3 D2 | D1 | D0 |              |

| Reset                                 | 0     | 0    | 0  | _    |    | _  |              |

| Battery voltage selector              | 0     | 0    | 1  | _    | _  | _  | See table 8  |

| Current output shift voltage adjuster | 0     | 1    | 0  | _    | _  | _  | See table 9  |

| Current monitor gain adjuster         | 0     | 1    | 1  | _    | _  | _  | See table 10 |

| FET controller                        | 1     | 0    | 0  | _    | _  | _  | See table 11 |

| Output selector                       | 1     | 0    | 1  | _    | _  | _  | See table 12 |

| Regulator                             | 1     | 1    | 1  | _    | _  | _  | See table 13 |

| Overcurrent detection controller      |       |      |    |      |    |    |              |

#### **Data Content**

**Table 8 Battery Voltage Selector**

| D5 to D3 | D2 | D1 | D0 | Output Voltage         | Note                 |  |  |

|----------|----|----|----|------------------------|----------------------|--|--|

| 001      | 0  | 0  | 0  | 0 V (no shift voltage) | Selected after reset |  |  |

| 001      | 0  | 0  | 1  | V1 voltage             |                      |  |  |

| 001      | 0  | 1  | 0  | V2 voltage             |                      |  |  |

| 001      | 0  | 1  | 1  | V3 voltage             |                      |  |  |

| 001      | 1  | 0  | 0  | 0 V (no shift voltage) |                      |  |  |

| 001      | 1  | 0  | 1  | V1 offset voltage      |                      |  |  |

| 001      | 1  | 1  | 0  | V2 offset voltage      |                      |  |  |

| 001      | 1  | 1  | 1  | V3 offset voltage      |                      |  |  |

Note: V1 voltage is selected after reset.

The V0 offset voltage should not be used.

Table 9 Current Output Shift Voltage Adjuster

| D5 to D3 | D2 | D1 | D0 | <b>Current Output Shift Voltage Value</b> | Note                 |  |  |

|----------|----|----|----|-------------------------------------------|----------------------|--|--|

| 010      | 0  | 0  | 0  | 0 V (no shift voltage)                    | Selected after reset |  |  |

| 010      | 0  | 0  | 1  | 0 V (no shift voltage)                    |                      |  |  |

| 010      | 0  | 1  | 0  | 0 V (no shift voltage)                    |                      |  |  |

| 010      | 0  | 1  | 1  | 0 V (no shift voltage)                    |                      |  |  |

| 010      | 1  | 0  | 0  | 0.4V                                      | Vreg/8×1             |  |  |

| 010      | 1  | 0  | 1  | 0.8V Vreg/8×2                             |                      |  |  |

| 010      | 1  | 1  | 0  | 1.2V Vreg/8×3                             |                      |  |  |

| 010      | 1  | 1  | 1  | 1.6V Vreg/8×4                             |                      |  |  |

Note: No current output shift voltage after reset.

Table 10 Charge/Discharge Current Detector

| D5 to D3 | D2 | D1 | D0 | Output Gain Switch          | Note                 |  |

|----------|----|----|----|-----------------------------|----------------------|--|

| 011      | 0  | 0  | 0  | Amplifier off               | Selected after reset |  |

| 011      | 0  | 0  | 1  | 20x (current value output)  |                      |  |

| 011      | 0  | 1  | 0  | 40x (current value output)  |                      |  |

| 011      | 0  | 1  | 1  | 100x (current value output) |                      |  |

| 011      | 1  | 0  | 0  | Amplifier off               | Same as after reset  |  |

| 011      | 1  | 0  | 1  | 20x (offset output)         |                      |  |

| 011      | 1  | 1  | 0  | 40x (offset output)         |                      |  |

| 011      | 1  | 1  | 1  | 100x (offset output)        |                      |  |

Note: Amplifier off after reset.

**Table 11 FET Controller**

| D5 to D3 | D2 | D1 | D0 | CFOUT      | DFOUT      | Note                 |

|----------|----|----|----|------------|------------|----------------------|

| 100      | 0  | 0  | 0  | High       | High       | Selected after reset |

| 100      | 0  | 0  | 1  | Low        | High       |                      |

| 100      | 0  | 1  | 0  | High       | Low        |                      |

| 100      | 0  | 1  | 1  | Low        | Low        |                      |

| 100      | 1  | 0  | 0  | Don't care | Don't care |                      |

| 100      | 1  | 0  | 1  | Don't care | Don't care |                      |

| 100      | 1  | 1  | 0  | Don't care | Don't care |                      |

| 100      | 1  | 1  | 1  | Don't care | Don't care |                      |

Note: DFOUT and CFOUT pins set to off after reset. (Current control FET is off when output is high level.)

**Table 12 Output Selector**

| D5 to D3 | D2 | D1 | D0 | Output Selection               | Note                 |

|----------|----|----|----|--------------------------------|----------------------|

| 101      | 0  | 0  | 0  | Ground output                  | Selected after reset |

| 101      | 0  | 0  | 1  | Battery voltage value output   |                      |

| 101      | 0  | 1  | 0  | Charge current value output    |                      |

| 101      | 0  | 1  | 1  | Discharge current value output |                      |

| 101      | 1  | 0  | 0  | Don't care                     |                      |

| 101      | 1  | 0  | 1  | Don't care                     |                      |

| 101      | 1  | 1  | 0  | Don't care                     |                      |

| 101      | 1  | 1  | 1  | Don't care                     |                      |

RENESAS

Note: Ground potential output after reset.

**Table 13 Regulator, Overcurrent Detection Controller**

| D5 to D3 | D2 | D1 | D0 | Voltage Regulator Output | <b>Overcurrent Detect Circuit</b> | Note                    |

|----------|----|----|----|--------------------------|-----------------------------------|-------------------------|

| 111      | 0  | 0  | 0  | ON                       | ON                                | Selected after reset    |

| 111      | 0  | 0  | 1  | OFF                      | OFF                               | Both circuits off       |

| 111      | 0  | 1  | 0  | ON                       | CIN pin fixed low                 | Overcurrent circuit off |

| 111      | 0  | 1  | 1  | ON                       | CIN pin fixed high                | Overcurrent circuit off |

| 111      | 1  | 0  | 0  | Don't care               | Don't care                        |                         |

| 111      | 1  | 0  | 1  | Don't care               | Don't care                        |                         |

| 111      | 1  | 1  | 0  | Don't care               | Don't care                        |                         |

| 111      | 1  | 1  | 1  | Don't care               | Don't care                        |                         |

Note: Regulator output and overcurrent circuit both on after reset.

Note: A setting of 111001 caused the M61042FP to transition to the power-down mode. However, transition to the power-down mode does not occur when connected to a charger (VIN\_12 is high level).

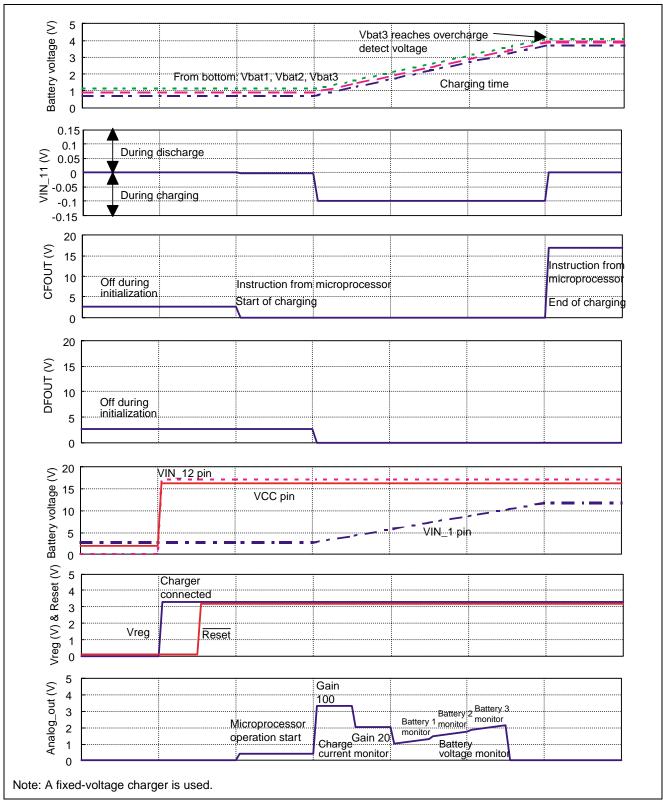

## **Timing Charts**

#### **Charging Sequence**

Figure 15 Charging Sequence

#### **Discharge Sequence**

Figure 16 Discharge Sequence

## **Overcurrent Sequence**

Figure 17 Overcurrent Sequence

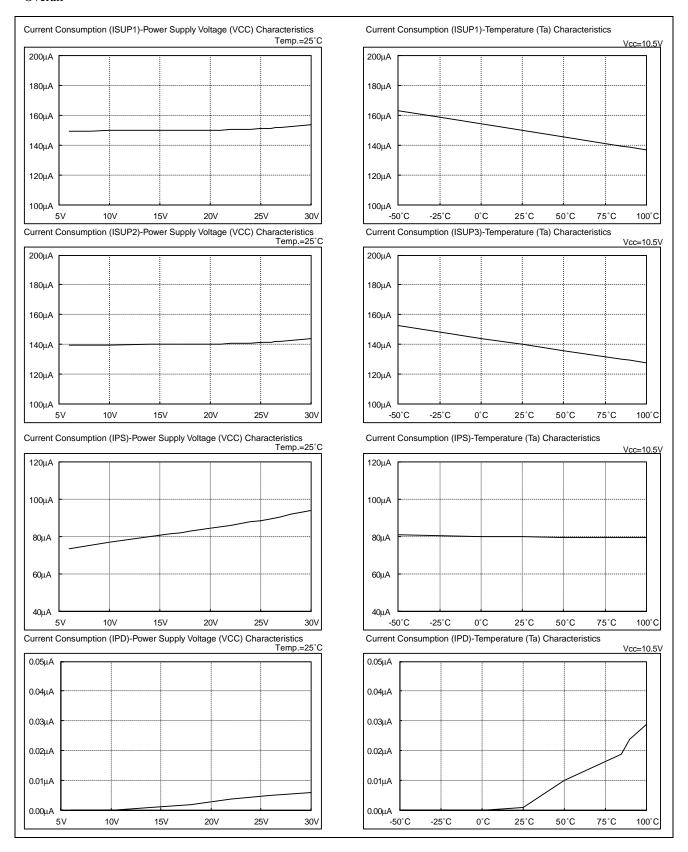

#### **Principal Item Characteristics**

#### Overall

#### Regulator Block

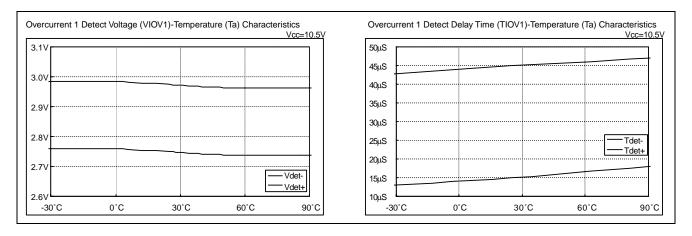

#### Overcurrent Detect Block

## Reset Block

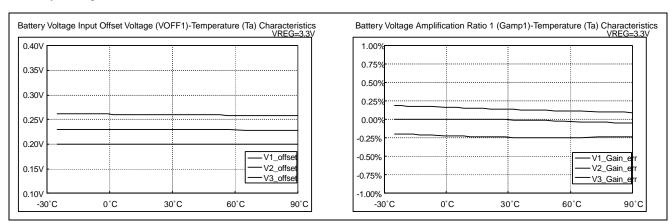

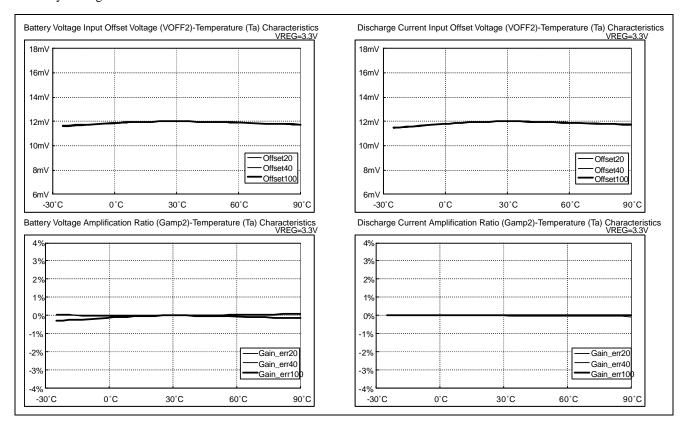

#### Battery Voltage Detect Block

## Battery Voltage Detect Block

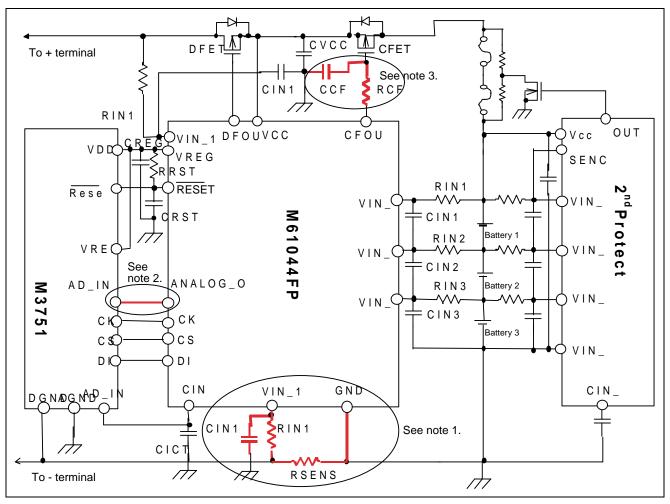

## **Sample Application Circuit**

Figure 18 Sample Application Circuit

#### **Notes on Circuit Board Design**

- 1. The current sensor resistor (RSENSE) should be located adjacent to the VSS and VIN\_11 pins of the M61042FP. In addition, no circuitry other than that recommended above should be added between the M61042FP and RSENSE. Any extraneous current flow in this channel could result in errors when measuring the charge and discharge currents.

- 2. The load capacitance of the ANALOG\_OUT pin, including parasite capacitance, should be no more than 10 pF. If a capacitor of more than 10 pF is connected, the output from ANALOG\_OUT may begin to oscillate.

- 3. Power supply fluctuations during overcurrent detection and when connected to a charger may cause the M61042FP to reset. It is possible to prevent incorrect operation by connecting a CR filter to the control signal of the charge control FET.

**Table 14 External Device Constants**

| Device             | Symbol | Purpose                                   | Recommen ded Value | Min.    | Max.        | Notes                                                                                                                  |  |

|--------------------|--------|-------------------------------------------|--------------------|---------|-------------|------------------------------------------------------------------------------------------------------------------------|--|

| Pch MOSFET         | DFET   | Discharge control                         | _                  | _       | _           | _                                                                                                                      |  |

| Pch MOSFET         | CFET   | Charge control                            | _                  | _       | _           | _                                                                                                                      |  |

| Resistor           | RIN1   | ESD countermeasure                        | 10Ω                | _       | 1kΩ         | 1) Values differ among RIN2 to RIN3.                                                                                   |  |

| Capacitor          | CIN1   | Power supply fluctuation countermeasure   | 0.22μF             | _       | 1.0μF       | <del>-</del>                                                                                                           |  |

| Resistor           | RIN2   | ESD countermeasure                        | 1kΩ                | _       | 1ΜΩ         | _                                                                                                                      |  |

| Capacitor          | CIN2   | Power supply fluctuation countermeasure   | 0.22μF             | _       | 1.0μF       |                                                                                                                        |  |

| Resistor           | RIN3   | ESD countermeasure                        | 1kΩ                | _       | $1 M\Omega$ | 2) RIN2 and CIN2 should be set to the                                                                                  |  |

| Capacitor          | CIN3   | Power supply fluctuation countermeasure   | 0.22μF             | _       | 1.0μF       | same value.                                                                                                            |  |

| Resistor           | RIN12  | Charger reverse connection countermeasure | 10kΩ               | 300Ω    | 100kΩ       | <ol> <li>The upper value for confirmation of<br/>overcurrent operation should be adjusted<br/>as necessary.</li> </ol> |  |

| Capacitor          | CIN12  | Power supply fluctuation countermeasure   | 0.01μF             | _       | 0.1μF       |                                                                                                                        |  |

| Resistor           | RIN11  | Power supply fluctuation countermeasure   | 100Ω               | _       | 200Ω        | <ol> <li>The upper value for confirmation of<br/>overcurrent operation should be adjusted<br/>as necessary.</li> </ol> |  |

| Capacitor          | CIN11  | Power supply fluctuation countermeasure   | 0.1μF              | _       | 1.0μF       | -                                                                                                                      |  |

| Capacitor          | CVCC   | Power supply fluctuation countermeasure   | 0.22μF             | _       | _           | _                                                                                                                      |  |

| Sensor<br>resistor | RSENSE | Charge/discharge current monitoring       | 20mΩ               | _       | _           | _                                                                                                                      |  |

| Capacitor          | CICT   | Delay time setting                        | 0.01μF             | _       | 0.47μF      | _                                                                                                                      |  |

| Capacitor          | CREG   | Output voltage fluctuation countermeasure | 4.7μF              | 0.47μF  | _           | _                                                                                                                      |  |

| Resistor           | RRST   | Delay time setting                        | 47kΩ               | 10kΩ    | 10ΜΩ        | 5) Adjustment should be performed in                                                                                   |  |

| Capacitor          | CRST   | Delay time setting                        | 0.1μF              |         |             | conjunction with the microprocessor.                                                                                   |  |

| Resistor           | RCF    | Power supply fluctuation countermeasure   | 1kΩ                | 500Ω    | _           | The upper value for confirmation of overcurrent operation should be adjusted as necessary.                             |  |

| Capacitor          | CCF    | Power supply fluctuation countermeasure   | 0.1μF              | 0.047μF | _           | - '                                                                                                                    |  |

Note: When designing applications, due consideration should be given to safety.

# **Package Dimensions**

16P2X

Note: Please contact Renesas Technology Corporation for further details.

Renesas Technology Corp. Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

The pastery in a survival circula designs; and the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage.

Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

Notes regarding these materials

1. These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corp. product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corp. or a third party.

2. Renesas Technology Corp. assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corp. without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor for the latest product information before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors.

Renesas Technology Corp. assumes no responsibility for any damage, liability, or other loss resident product product of the responsibility of the information of the Renesas Technology Corp. Semiconductor home page (http://www.renesas.com).

4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corp. assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

5. Renesas Technology Corp. semiconductors are not designed or manufactured for use in a device or system that is used under circumstances i

- use.

6. The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduce in whole or in part these materials.

7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

8. Please contact Renesas Technology Corp. for further details on these materials or the products contained therein.

**RENESAS SALES OFFICES**

http://www.renesas.com

**Renesas Technology America, Inc.** 450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500 Fax: <1> (408) 382-7501

Renesas Technology Europe Limited.

Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, United Kingdom Tel: <44> (1628) 585 100, Fax: <44> (1628) 585 900

Renesas Technology Europe GmbH Dornacher Str. 3, D-85622 Feldkirchen, Germany Tel: <49> (89) 380 70 0, Fax: <49> (89) 929 30 11

Renesas Technology Hong Kong Ltd. 7/F., North Tower, World Finance Centre, Harbour City, Canton Road, Hong Kong Tel: <852> 2265-6688, Fax: <852> 2375-6836

Renesas Technology Taiwan Co., Ltd. FL 10, #99, Fu-Hsing N. Rd., Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 2713-2999

Renesas Technology (Shanghai) Co., Ltd. 26/F., Ruijin Building, No.205 Maoming Road (S), Shanghai 200020, China Tel: <86> (21) 6472-1001, Fax: <86> (21) 6415-2952

Renesas Technology Singapore Pte. Ltd.

1, Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65> 6213-0200, Fax: <65> 6278-8001