# M64898GP

# PLL Frequency Synthesizer with DC/DC Converter for PC

REJ03F0168-0201 Rev.2.01 Jan 25, 2008

#### **Description**

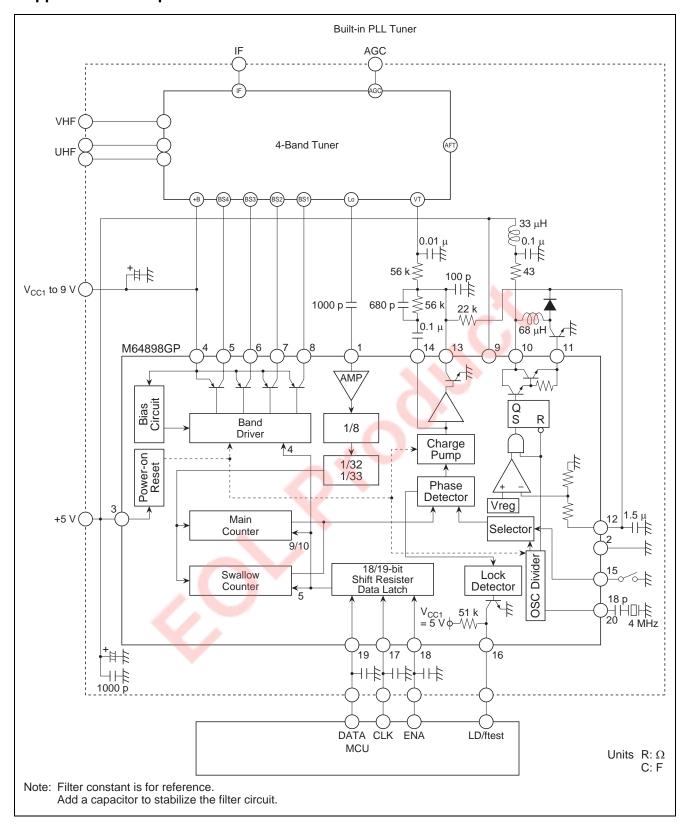

The M64898GP is a semiconductor integrated circuit consisting of PLL frequency synthesizer for TV/VCR /PC.

It contains the prescaler with operating up to 1.3 GHz, 4 band drivers and DC/DC converter for Tuning voltage.

#### **Features**

- Built-in DC/DC converter for Tuning voltage

- 4 integrated PNP band drivers ( $I_0 = 30 \text{ mA}$ ,  $V_{\text{sat}} = 0.2 \text{ V Typ } @V_{\text{CC1}} \text{ to } 10 \text{ V}$ )

- Built-in prescaler with input amplifier (max = 1.3 GHz)

- PLL lock/unlock status display out put (Built-in pull up resistor)

- X'tal 4 MHz is used to realize 3 type of tuning steps (Divider ratio 1/512, 1/640, 1/1024)

- Software compatible with M64892/M64893

- Automatic switching of tuning step according to the number of data bits (62.5 kHz at 18 bits, 32.25 kHz at 19 bits)

- Built-in Power on reset system

- Small package (SSOP)

#### **Application**

PC, TV, VCR tuners

## **Recommended Operating Condition**

- Supply voltage range

- V<sub>CC1</sub> = 4.5 to 5.5 V

- $V_{CC2} = V_{CC1}$  to 10 V

- Rated supply voltage

- $--- V_{CC1} = 5 V$

- --  $V_{CC2} = V_{CC1}$

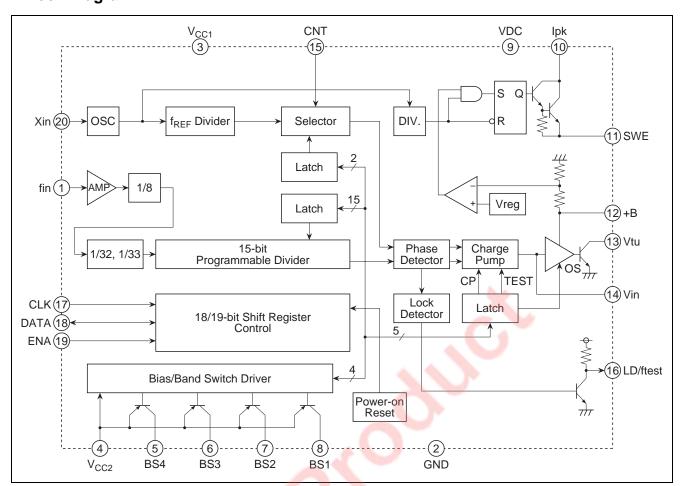

### **Block Diagram**

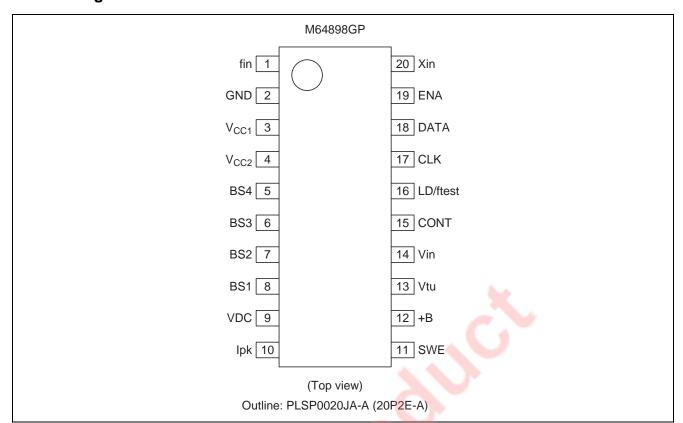

# **Pin Arrangement**

# **Pin Description**

| Pin |                  |                                              |                                                                                                                                                                                                                                                                                                                                                                         |

|-----|------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No. | Symbol           | Pin Name                                     | Function                                                                                                                                                                                                                                                                                                                                                                |

| 1   | fin              | Prescaler input                              | Input for the VCO frequency.                                                                                                                                                                                                                                                                                                                                            |

| 2   | GND              | GND                                          | Ground to 0 V.                                                                                                                                                                                                                                                                                                                                                          |

| 3   | V <sub>CC1</sub> | Power supply voltage 1                       | Power supply voltage terminal. 5.0 V $\pm$ 0.5 V                                                                                                                                                                                                                                                                                                                        |

| 4   | V <sub>CC2</sub> | Power supply voltage 2                       | Power supply for band switching, V <sub>CC1</sub> to 10 V                                                                                                                                                                                                                                                                                                               |

| 5   | BS4              | Band switching outputs                       | PNP open collector method is used.                                                                                                                                                                                                                                                                                                                                      |

| 6   | BS3              |                                              | When the band switching data is "H", the output is ON.                                                                                                                                                                                                                                                                                                                  |

| 7   | BS2              |                                              | When it is "L", the output is OFF.                                                                                                                                                                                                                                                                                                                                      |

| 8   | BS1              |                                              |                                                                                                                                                                                                                                                                                                                                                                         |

| 9   | VDC              | DC/DC power supply voltage                   | DC/DC power supply voltage terminal. 5.0 V $\pm$ 0.5V                                                                                                                                                                                                                                                                                                                   |

| 10  | lpk              | Peak current detect                          | When potential difference with VDC terminal becomes more than 0.33 V by current limiting detector of DC/DC converter, the listing rises with off.                                                                                                                                                                                                                       |

| 11  | SWE              | Switching output                             | DC/DC converter oscillator output.                                                                                                                                                                                                                                                                                                                                      |

| 12  | +B               | Power supply voltage                         | Power supply voltage for tuning voltage.                                                                                                                                                                                                                                                                                                                                |

| 13  | Vtu              | Tuning output                                | This supplies the tuning voltage.                                                                                                                                                                                                                                                                                                                                       |

| 14  | Vin              | Filter input (charge pump output)            | This is the output terminal for the LPF input and charge pump output. When the phase of the programmable divider output (f 1/N) is ahead compared to the reference frequency (f <sub>REF</sub> ), the "source" current state becomes active.  If it is behind, the "sink" current becomes active.  If the phases are the same, the high impedance state becomes active. |

| 15  | LD/ftest         | Lock detect/Test port                        | Lock detector output. When loop of phase locked loop locked it, it rise with "H" level in "L" level or unlock.  In control byte data input, the programmable freq. divider output and reference freq. output is selected by the test mode.                                                                                                                              |

| 16  | CONT             | f <sub>REF</sub> switch                      | Set up reference frequency divider ratio. In "L" level, set it up in 1/640 (19 bit) in setting "opening" in 1/1024 (19 bit) or 1/512 (18 bit).                                                                                                                                                                                                                          |

| 17  | CLOCK            | Clock input                                  | Data is read into the shift register when the clock signal falls.                                                                                                                                                                                                                                                                                                       |

| 18  | DATA             | Data input                                   | Input for band SW and programmable freq. divider set up.                                                                                                                                                                                                                                                                                                                |

| 19  | ENABLE           | Enable input                                 | This normally at a "L". When this is at "H", data and clock signals are received. Data is read into the latch when the enable signal after the 18th signal of the clock signal falls or when the 19th pulse of the clock signal falls.                                                                                                                                  |

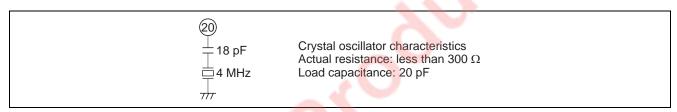

| 20  | Xin              | This is connected to the crystal oscillator. | 4.0 MHz crystal oscillator is connected.                                                                                                                                                                                                                                                                                                                                |

# **Absolute Maximum Ratings**

(Ta = -20°C to +75°C, unless otherwise noted)

| Item                                        | Symbol             | Ratings     | Unit | Conditions                                                      |

|---------------------------------------------|--------------------|-------------|------|-----------------------------------------------------------------|

| Supply voltage 1                            | V <sub>CC1</sub>   | 6.0         | V    | Pin 3                                                           |

| Supply voltage 2                            | V <sub>CC2</sub>   | 10.8        | V    | Pin 4                                                           |

| Input voltage                               | Vı                 | 6.0         | V    | Not to exceed V <sub>CC1</sub>                                  |

| Output voltage                              | Vo                 | 6.0         | V    | f <sub>REF</sub> output                                         |

| Voltage applied when the band output is OFF | V <sub>BSOFF</sub> | 10.8        | V    |                                                                 |

| Band output current                         | I <sub>BSON</sub>  | 40.0        | mA   | per 1 band output circuit                                       |

| ON the time when the band output is ON      | t <sub>BSON</sub>  | 10          | s    | 40 mA per 1 band output circuit 3 circuits are pn at same time. |

| Power dissipation                           | Pd                 | 255         | mW   | Ta = 75°C                                                       |

| Operating temperature                       | Topr               | -20 to +75  | °C   |                                                                 |

| Storage temperature                         | Tstg               | -40 to +125 | °C   |                                                                 |

# **Recommended Operating Conditions**

$(Ta = -20^{\circ}C \text{ to } +75^{\circ}C, \text{ unless otherwise noted})$

| Item                       | Symbol            | Ratings                  | Unit | Conditions                                                                                                                               |

|----------------------------|-------------------|--------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------|

| Supply voltage 1           | V <sub>CC1</sub>  | 4.5 to 5.5               | V    | Pin 3                                                                                                                                    |

| Supply voltage 2           | V <sub>CC2</sub>  | V <sub>CC1</sub> to 10.0 | V    | Pin 4                                                                                                                                    |

| Operating frequency (1)    | f <sub>opr1</sub> | 4.0                      | V    | Crystal oscillation circuit                                                                                                              |

| Operating frequency (2)    | f <sub>opr2</sub> | 80 to 1300               | MHz  |                                                                                                                                          |

| Band output current 5 to 8 | I <sub>BDL</sub>  | 0 to 30                  | mA   | Normally 1 circuit is on. 2 circuits on at the same time is max. It is prohibited to have 3 or more circuits turned on at the same time. |

# **Electrical Characteristics**

(Ta = -20°C to +75°C, unless otherwise noted,  $V_{CC1} = 5.0 \text{ V}$ ,  $V_{CC2} = 9.0 \text{ V}$ )

| Item                    |                              |                   | Test     |              | Limit | ts                     |      |                                                              |

|-------------------------|------------------------------|-------------------|----------|--------------|-------|------------------------|------|--------------------------------------------------------------|

|                         |                              | Symbol            | Pin      | Min.         | Тур.  | Max.                   | Unit | Test Conditions                                              |

| Input                   | "H" input voltage            | V <sub>IH</sub>   | 17 to 19 | 3.0          | _     | V <sub>CC1</sub> + 0.3 | V    |                                                              |

| termina                 | "L" input voltage            | V <sub>IL1</sub>  | 15       | _            | _     | 0.4                    | V    |                                                              |

| ls                      | "L" input voltage            | V <sub>IL2</sub>  | 17 to 19 | _            | _     | 1.5                    | V    |                                                              |

|                         | "H" input current            | I <sub>IH</sub>   | 17 to 19 | _            | _     | 10                     | μΑ   | $V_{CC1} = 5.5 \text{ V}, \text{ Vi} = 4.0 \text{ V}$        |

|                         | "L" input current            | I <sub>IL1</sub>  | 15       | _            | -50   | -80                    | μΑ   | $V_{CC1} = 5.5 \text{ V}, \text{ Vi} = 0 \text{ V}$          |

|                         | "L" input current            | I <sub>IL2</sub>  | 17, 19   | _            | -6    | -10                    | μΑ   | $V_{CC1} = 5.5 \text{ V}, \text{ Vi} = 0.5 \text{ V}$        |

|                         | "L" input current            | I <sub>IL3</sub>  | 18       | _            | -18   | -30                    | μΑ   | $V_{CC1} = 5.5 \text{ V}, \text{ Vi} = 0.5 \text{ V}$        |

| Lock<br>output          | "H" output<br>voltage        | V <sub>OH</sub>   | 16       | 5.0          | _     | _                      | ٧    | V <sub>CC1</sub> = 5.5 V                                     |

|                         | "L" output voltage           | V <sub>OL</sub>   | 16       | _            | 0.3   | 0.5                    | V    | V <sub>CC1</sub> = 5.5 V                                     |

| Band                    | Output voltage               | V <sub>BS</sub>   | 5 to 8   | 11.6         | 11.8  | _                      | V    | $V_{CC2} = 9 \text{ V}, I_0 = -30 \text{ mA}$                |

| SW                      | Leak current                 | I <sub>Olk1</sub> | 5 to 8   | _            | _     | -10                    | μΑ   | $V_{CC2} = 9 \text{ V}$ , Band SW is OFF $V_O = 0 \text{ V}$ |

| Tuning output           | Output voltage "H"           | V <sub>toH</sub>  | 13       | 30.5         | _     | _                      | V    | +B = 31 V                                                    |

|                         | Output voltage "L"           | V <sub>toL</sub>  | 13       | _            | 0.2   | 0.4                    | V    | +B = 31 V                                                    |

| Charge pump             | "H" output<br>current        | I <sub>cpo</sub>  | 14       | _            | 270   | 370                    | μΑ   | $V_{CC1} = 5.0 \text{ V}, V_O = 2.5 \text{ V}$               |

|                         | Leak current                 | I <sub>cpLK</sub> | 14       | _            | _     | 50                     | nA   | $V_{CC1} = 5.0 \text{ V}, V_O = 2.5 \text{ V}$               |

| Supply c                | urrent 1                     | I <sub>CC1</sub>  | 3        | _            | 20    | 30                     | mA   | V <sub>CC1</sub> = 5.5 V                                     |

| Supply                  | 4 circuits OFF               | I <sub>CC2A</sub> | 4        | _            | A .   | 0.3                    | mA   | V <sub>CC2</sub> = 9 V                                       |

| current<br>2            | 1 circuit ON,<br>Output open | I <sub>CC2B</sub> | 4        |              | 4.0   | 6.0                    | mA   | V <sub>CC2</sub> = 9 V                                       |

|                         | Output current 30 mA         | I <sub>CC2C</sub> | 4        | $\checkmark$ | 34.0  | 36.0                   | mA   | $V_{CC2} = 9 \text{ V}, I_0 = -30 \text{ mA}$                |

| DC/DC Converter         |                              |                   |          |              |       |                        |      | •                                                            |

| Supply current (action) |                              | I <sub>CCdc</sub> | 9        | _            | 1.3   | 3.0                    | mA   | V <sub>CC1</sub> = 5.5 V                                     |

| Output v                | oltage                       | Vdo               | 12       | 28           | 31    | 35                     | V    | V <sub>CC1</sub> = 5.5 V                                     |

| OSC free                | quency                       | fosc              | 11       | _            | 571   | _                      | kHz  | V <sub>CC1</sub> = 5.5 V                                     |

| Current I               | imit detect voltage          | Vipk              | 10       | _            | 330   | _                      | mV   | V <sub>CC1</sub> = 5.5 V                                     |

Note: The typical values are at  $V_{CC1} = 5.0 \text{ V}$ ,  $V_{CC2} = 9.0 \text{ V}$ ,  $Ta = +25^{\circ}C$ .

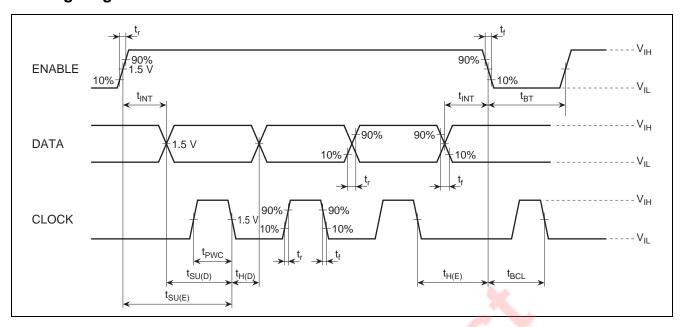

# **Switching Characteristics**

(Ta = -20 °C to +75 °C, unless otherwise noted,  $V_{CC1} = 5.0 \text{ V}$ ,  $V_{CC2} = 9.0 \text{ V}$ )

|                               |                     | Test          | Limits |      |      |      |                                                           |                 |

|-------------------------------|---------------------|---------------|--------|------|------|------|-----------------------------------------------------------|-----------------|

| Item                          | Symbol              | Pin           | Min.   | Тур. | Max. | Unit | Test Conditions                                           |                 |

| Prescaler operating frequency | f <sub>opr</sub>    | 1             | 80     | _    | 1300 | MHz  | V <sub>CC1</sub> = 4.5 to 5.5 V<br>Vin = Vinmin to Vinmax |                 |

| Operating input voltage       | V <sub>in</sub>     | 1             | -24    | _    | 4    | dBm  | $V_{CC1} = 4.5 \text{ to}$                                | 80 to 100 MHz   |

|                               |                     |               | -27    | _    | 4    | 1    | 5.5 V                                                     | 100 to 950 MHz  |

|                               |                     |               | -15    | _    | 4    |      |                                                           | 950 to 1300 MHz |

| Clock pulse width             | t <sub>PWC</sub>    | 17            | 1      | _    | _    | μS   | $V_{CC1} = 4.5 \text{ to } 5$                             | .5 V            |

| Data setup time               | t <sub>SU (D)</sub> | 18            | 2      | _    | _    | μS   | V <sub>CC1</sub> = 4.5 to 5.5 V                           |                 |

| Data hold time                | t <sub>H (D)</sub>  | 18            | 1      | _    | _    | μS   | V <sub>CC1</sub> = 4.5 to 5.5 V                           |                 |

| Enable setup time             | t <sub>SU (E)</sub> | 18            | 3      | _    | _    | μS   | V <sub>CC1</sub> = 4.5 to 5.5 V                           |                 |

| Enable hold time              | t <sub>H (E)</sub>  | 18            | 3      | _    | _    | μS   | $V_{CC1} = 4.5 \text{ to } 5$                             | .5 V            |

| Enable data interval time     | t <sub>INT</sub>    | 19, 18        | 1      | _    | _    | μS   | V <sub>CC1</sub> = 4.5 to 5.5 V                           |                 |

| Rise time                     | t <sub>R</sub>      | 17, 18,<br>19 | _      | _    | 1    | μS   | $V_{CC1} = 4.5 \text{ to } 5$                             | .5 V            |

| Fall time                     | t <sub>F</sub>      | 17, 18,<br>19 | _      |      | 1    | μS   | $V_{CC1} = 4.5 \text{ to } 5$                             | .5 V            |

| Next enable prohibit time     | t <sub>BT</sub>     | 19            | 5      | _    |      | μЅ   | $V_{CC1} = 4.5 \text{ to } 5$                             | .5 V            |

| Next clock prohibit time      | t <sub>BCL</sub>    | 17, 19        | 5      | _    | _    | μS   | $V_{CC1} = 4.5 \text{ to } 5$                             | .5 V            |

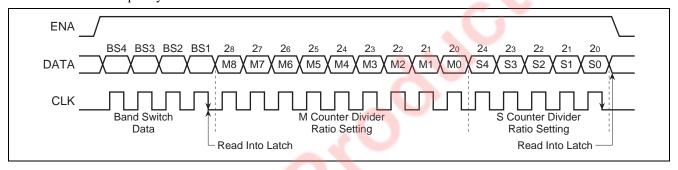

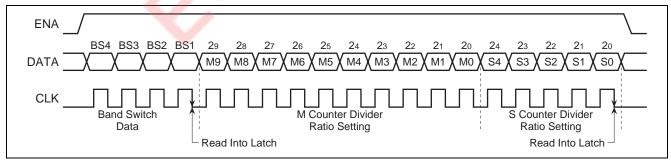

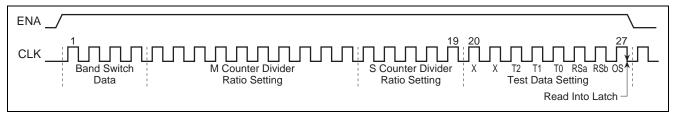

#### **Method of Setting Data**

The programmable divider ratio uses 15 bits. Setting up the band switching output uses 4 bits.

The test mode data uses 8 bits. The total bits used are 27 bits. Data is read in when the enable signal is "H" and the clock signal falls.

The band switching data is read in at the 4th pulse of the clock signal. The programmable counter data is read into the latch by the fall of the enable signal after the 18th pulse of the clock signal or the fall of the 19th pulse of the clock signal. When the enable signal goes to "L" before the 18th pulse of the enable signal, only the band SW data is updated and other data is ignored.

Automatic judgment facility comes being it, and, as for Shift resister, CONT terminal rises by 18/19 bits at the time of "L". At the time of data of 18 bits, M9 bit of Programmable divider is done reset of, and it is established in reference frequency divider ratio is established 1/512.

At the time of 19 bits, reference frequency divider ratio is established in 1/1024.

When reference frequency divider ratio was established in 1/640 by 19 bits at the time if "opening" CONT terminal, and it became "L" before 19 pulses enable signal, only band SW data are renewed, and other data are ignored.

1. Transfer of the 18th bit data (CONT terminal is "L")

Data is latched by the fall of the enable signal after the 18th clock signal. At this time, the divider of the 1/512 of the reference frequency is used.

2. Transfer of the 19th bit data (CONT terminal is "L" or "open")

The data is latched at the 19th pulse of the clock signal.

Reference frequency divider ratio is established in 1/1024 in case of "L" CONT terminal at this time.

Reference frequency divider ratio is established in 1/640 in case of "opening" CONT terminal.

Invalid the clock signal after 19th pulse.

Note: When CONT terminal is "L", to change reference frequency, set up as ENA in "L" after 19th pulse of clock signal by all means.

## How to Set the Dividing Ratio of the Programmable Divider

1. Transfer of the 18th bit data (CONT terminal is "L")

Total divider N is given by the following formulas in addition to the prescaler used in the previous stage.

$$N = 8 \cdot (32 M + S)$$

M: 9 bit main counter divider

S: 5 bit swallow counter divider

The M and S counters are binary the possible ranges of divider are as follows.

$$32 \cdot M \cdot 511$$

$$0 \cdot S \cdot 31$$

Therefore, the range of divider N is 8,192 to 131,064.

The tuning frequency  $f_{VCO}$  is given in the following equations.

$$\begin{split} f_{VCO} &= f_{REF} \cdot N \\ &= 7.8125 \cdot 8 \cdot (32 \text{ M} + \text{S}) \\ &= 62.5 \cdot (32 \text{ M} + \text{S}) \text{ (kHz)} \end{split}$$

Therefore, the tuning frequency range is 64 MHz to 1023.9375 MHz.

2. Transfer of the 19th bit data (CONT terminal is "L")

Total divider N is given by the following formulas in addition to the prescaler used in the previous stage.

$$N = 8 \cdot (32 \text{ M} + \text{S})$$

M: 10 bit main counter divider S: 5 bit swallow counter divider

The M and S counters are binary the possible ranges of divider are as follows.

$$32\cdot M\cdot 1023$$

$$0 \cdot S \cdot 31$$

Therefore, the range of divider N is 8,192 to 262,136.

The tuning frequency  $f_{VCO}$  is given in the following equations.

$$f_{VCO} = f_{REF} \cdot N$$

= 3.90625 · 8 · (32 M + S)

= 31.25 · (32 M + S) (kHz)

Therefore, the tuning frequency range is 32 MHz to 1023.96875 MHz.

3. Transfer of the 19th data (CONT terminal is "open")

Total divider N is given by the following formulas in addition to the prescaler used in the previous stage.

$$N = 8 \cdot (32M + S)$$

M: 10 bit main counter divider S: 5 bit swallow counter divider

The M and S counters are binary the possible ranges of divider are as follows.

$$32\cdot M\cdot 1023$$

Therefore, the range of divider N is 8,192 to 262,136.

The tuning frequency  $f_{VCO}$  is given in the following equations.

$$f_{VCO} = f_{REF} \cdot N$$

= 6.25 \cdot 8 \cdot (32 M + S)

= 50.0 \cdot (32 M + S) (kHz)

But, the tuning frequency range is 51.2 MHz to 1300 MHz from the maximum prescaler operating frequency.

### **Test Mode Data Set up Method**

The data for the test mode uses 20 to 27 bits. Data is latched when the 27th clock signal falls.

1. When transferring 3-wire 27 bit data

2. Test mode bit set up

X : Random, 0 or 1 normal "0"

T0, T1 & T2 : Set up test modes

RSa, Rsa : Set the frequency divider of the reference frequency

OS : Set up the tuning amplifier

#### **Setting up for the Test Mode**

| T2 | T1 | T0 | Charge Pump      | Pin 12 Output    | Mode             |

|----|----|----|------------------|------------------|------------------|

| 0  | 0  | Х  | Normal operation | LD               | Normal operation |

| 0  | 1  | Х  | High impedance   | LD               | Test mode        |

| 1  | 1  | 0  | Sink             | LD               | Test mode        |

| 1  | 1  | 1  | Source           | LD               | Test mode        |

| 1  | 0  | 0  | High impedance   | f <sub>REF</sub> | Test mode        |

| 1  | 0  | 1  | High impedance   | f1/N             | Test mode        |

### RSa, RSb: Set up for the Reference Frequency Divider Ratio

| RSa | RSb | Divider Ratio |

|-----|-----|---------------|

| 1   | 1   | 1/512         |

| 0   | 1   | 1/1024        |

| X   | 0   | 1/640         |

### OS: Set up the Tuning Amplifier

| os | Tuning Voltage Output | Mode   |

|----|-----------------------|--------|

| 0  | ON                    | Normal |

| 1  | OFF                   | Test   |

### **Power on Reset Operation**

(Initial state the power is turned ON)

BS4 to BS1 : OFF

Charge pump : High impedance

Tuning amplifier : OFF

Charge pump current : 270  $\mu$ A

Frequency divider ratio : 1/1024

Lock detect : H

Charge pump current is replaced by 70 µA when locks it by automatic change facility.

# **Timing Diagram**

# **Crystal Oscillator Connection Diagram**

### **Application Example**

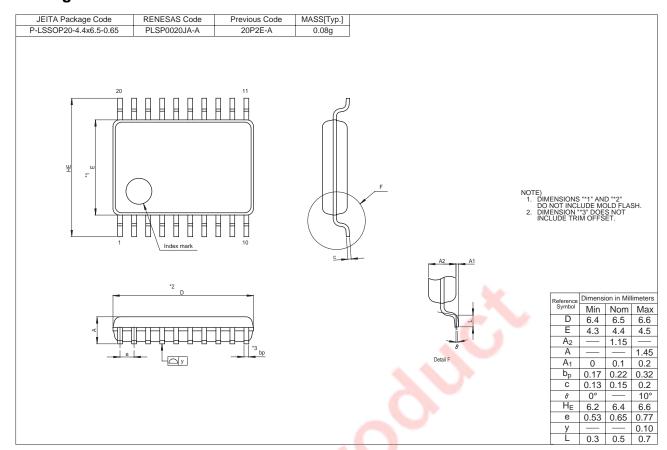

### **Package Dimensions**

Renesas Technology Corp. sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

- Renesas lechnology Corp. Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Notes:

1. This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warrantes or representations with respect to the accuracy or completeness of the information in this document nor grants any license to any intellectual property girbs to any other rights of representations with respect to the information in this document in this document of the purpose of the respect of the information in this document in the product data, diagrams, charts, programs, algorithms, and application critical expensions of the purpose of any other military use. When exporting the products or technology described in this document for the purpose of military use. When exporting the products or technology described herein, you should follow the applicable export control laws and regulations, and procedures required by such laws and regulations, and procedures required to the date this document, including the suitability of the such and the procedure of the date this document, and the procedure of the procedure of the procedure of the procedure of the date this document, an

#### **RENESAS SALES OFFICES**

http://www.renesas.com

Refer to "http://www.renesas.com/en/network" for the latest and detailed information.

#### Renesas Technology America, Inc

450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500, Fax: <1> (408) 382-7501

Renesas Technology Europe Limited

Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K.

Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900

Renesas Technology (Shanghai) Co., Ltd. Unit 204, 205, AZIACenter, No.1233 Lujiazui Ring Rd, Pudong District, Shanghai, China 200120 Tel: <86> (21) 5877-1818, Fax: <86> (21) 6887-7858/7898

Renesas Technology Hong Kong Ltd.

7th Floor, North Tower, World Finance Centre, Harbour City, Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel: <852> 2265-6688, Fax: <852> 2377-3473

**Renesas Technology Taiwan Co., Ltd.** 10th Floor, No.99, Fushing North Road, Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 3518-3399

Renesas Technology Singapore Pte. Ltd.

1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65> 6213-0200, Fax: <65> 6278-8001

Renesas Technology Korea Co., Ltd. Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, Korea Tel: <82> (2) 796-3115, Fax: <82> (2) 796-2145

Renesas Technology Malaysia Sdn. Bhd

Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: <603> 7955-9390, Fax: <603> 7955-9510