# GEC PLESSEY semiconductors

# **MA2901** RADIATION HARD 4-BIT MICROPROCESSOR SLICE

The MA2901 is an industry standard 4-bit microprocessor slice It provides a set of ALU functions selected by microcode data applied to the inputs. The device is cascadable to handle any word length. It can be used as a building block in the construction of microcomputers and controllers tailored to meet specialised applications.

#### **Dual Address Architecture**

Machine cycles are saved by simultaneous, independent access to two working registers.

#### **ALU has Eight Functions**

Operations performed are addition, two subtractions and five logic functions on two source operands.

#### Four State Flags

Zero, negative, carry and overflow.

#### Left / Right Shift is Independent of ALU

Only one cycle taken for add and shift operations.

#### Expandable

Any number of MA2901 units can be connected together to achieve longer word lengths.

#### **Micro Programmable**

Three groups, each of three bits, for ALU function, source operand and destination control.

## FEATURES

- Fully Compatible with Industry Standard 2901

- CMOS SOS Technology

- High SEU Immunity and Latch-up Free

- High Speed

- Low Power

### OPERATION

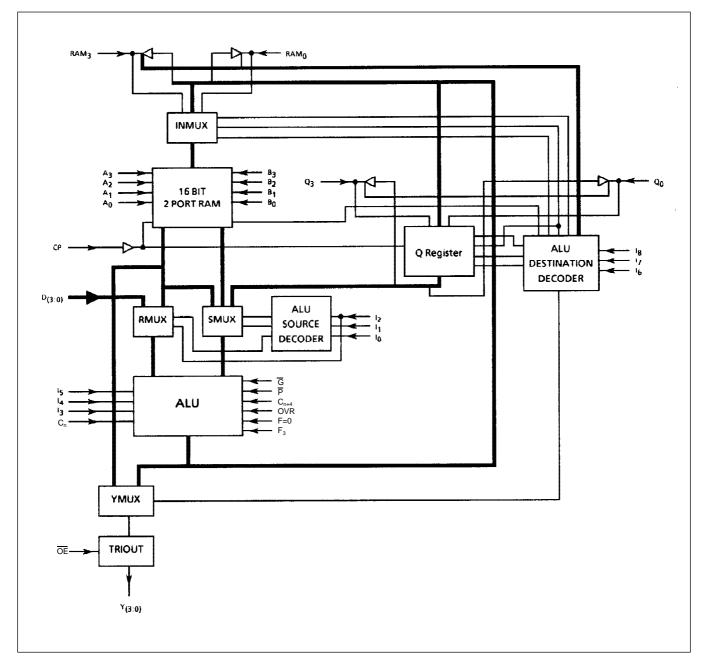

A detailed block diagram of the microprogrammable microprocessor structure is shown in figure 1. The circuit is a four-bit slice, cascadable to any number of bits. Therefore, all data paths within the circuit are four bits wide. The two key elements in the figure 1 are the 16-word by 4-bit 2-port RAM and the high speed ALU.

Data from any of the 16 words of the Random Access Memory (RAM) can be read from the A-port of the RAM as controlled by the 4-bit A-address field input. Likewise, data from any of the 16 words of the RAM as defined by the Baddress field input can be simultaneously read from the B-port of the RAM. The same code can be applied to the A-select field and B-select field in which case the identical file data will appear at both the RAM A-port and B-port outputs simultaneously.

When enabled by the RAM write enable (RAM EN), new data is always written into the file (word) defined by the B-address field of the RAM. The RAM data input field is driven by a 3-input multiplexer. This configuration is used to shift the ALU output data (F) if desired. This three-input multiplexer scheme allows the data to be shifted up one bit position, shifted down one bit position, or not shifted in either direction.

The RAM A-port data outputs and RAM B-port data outputs drive separate 4-bit latches. These latches hold the RAM data while the clock input is LOW. This eliminates any possible race conditions that could occur while new data is being written into the RAM.

The high-speed Arithmetic Logic Unit (ALU) can perform three binary arithmetic and five logic operations on the two 4bit input words R and S. The R input field is driven from a 2input multiplexer, while S input field is driven from a 3-input multiplexer. Both multiplexers also have an inhibit capability; that is, no data is passed. This is equivalent to a "zero" source operand.

The ALU R-input multiplexer has the RAM A-port and the direct data inputs (D) connected as inputs. Likewise, the ALU S-input multiplexer has the RAM A-port, the RAM B-port and the Q register connected as inputs.

Figure 1: Block Diagram

This multiplexer scheme gives the capability of selecting various pairs of the A, B, D, Q and "0" inputs as source operands to the ALU. These five inputs, when taken two at a time, result in ten possible combinations of source operand pairs. These combinations include AB, AD, AQ, AO, BD, BQ, BO, DQ, D0 and Q0. It is apparent the AD, AQ and A0 are somewhat redundant with BD, BQ and B0 in that if the A address and B address are the same, the identical function results. Thus, there are only seven completely non-redundant sourced operand pairs for the ALU. The MA2901 microprocessor implements eight of these pairs. The microinstruction inputs used to select the ALU source operands are the  $I_0$ ,  $I_1$ , and  $I_2$  inputs. The definition of  $I_0$ ,  $I_1$ , and  $I_2$  for the eight source operand combinations are as shown in figure 2. Also shown is the octal code for each selection.

The two source operands not fully described as yet are the D input and Q input. The D input is the four-bit wide direct data field input. This port is used to insert all data into the working registers inside the device. Likewise this input can be used in the ALU to modify any of the internal data files. The Q register is a separate 4-bit file intended primarily for multiplication and division routines but it can also be used as an accumulator or holding register for some applications.

The ALU itself is a high speed arithmetic/logic operator capable of performing three binary arithmetic and five logic functions. The  $I_3$ ,  $I_4$ , and  $I_5$  microinstruction inputs are used to select the ALU function. The definition of these inputs is shown in Figure 3. The octal code is also shown for reference. The normal technique for cascading ALU of several devices is in a look-ahead carry mode. Carry generate, GN, and carry propagate, PN, are outputs of the device for use with a carry-look-ahead-generator. A carry-out Cn + 4, is also generated and is available as an output for use as the carry flag in a status register. Both carry-in (Cn) and carry-out (Cn+4) are active HIGH.

The ALU has three other status-oriented outputs. These are  $F_3$ , F=0, and overflow (OVR). The  $F_3$  output is the most significant (sign) bit of the ALU and can be used to determine positive or negative results without enabling the three-state data outputs.  $F_3$  is non-inverted with respect to the sign bit output Y3. The F = 0 output is used for zero detect. It is an open-collector output and can be wire OR'ed between microprocessor slices. F = 0 is HIGH when all F outputs are LOW. The overflow output (OVR) is used to flag arithmetic operations that exceed the available two's complement number range. The overflow output (OVR) is HIGH when overflow exists. That is when Cn + 3 and Cn + 4 are not the same polarity.

The ALU data output is routed to several destinations. It can be a data output of the device and it can also be stored in the RAM or the Q register. Eight possible combinations of ALU destination functions are available as defined by the  $I_6$ ,  $I_7$ , and  $I_8$  microinstruction inputs. These combinations are shown in figure 4.

The four-bit data output field (Y) features three-state outputs and can be directly bus organised. An output control (OEN) is used to enable the three-state outputs. When OEN is HIGH, the Y outputs are in the high impedance state.

A two-input multiplexer is also used at the data output such that either the A-port of the RAM or the ALU outputs (F) are selected at the device Y outputs. This selection is controlled by the  $I_6$ ,  $I_7$ , and  $I_8$  microinstruction inputs.

As was discussed previously, the RAM inputs are driven from a three-input multiplexer. This allows the ALU outputs to be entered non-shifted, shifted up one position (x 2) or shifted down one position ( $\div$  2). The shifter has two ports; labeled RAM<sub>0</sub> and RAM<sub>3</sub>. Both of these ports consist of a buffer-driver with a three-state output and an input to the multiplexer.

|                | Microo         |                | Source<br>erands             |   |   |

|----------------|----------------|----------------|------------------------------|---|---|

| l <sub>2</sub> | I <sub>1</sub> | I <sub>O</sub> | l <sub>0</sub> Octal<br>Code |   | S |

| L              | L              | L              | 0                            | А | С |

| L              | L              | н              | 1                            | А | В |

| L              | н              | L              | 2                            | 0 | Q |

| L              | н              | н              | 3                            | 0 | В |

| н              | L              | L              | 4                            | 0 | А |

| н              | L              | н              | 5                            | D | А |

| н              | н              | L              | 6                            | D | Q |

| Ιн             | н              | н              | 7                            | р | 0 |

Figure 2: ALU Source Operand Control

|                | Micro          | ocode          |               | ALU        | Symbol |

|----------------|----------------|----------------|---------------|------------|--------|

| ۱ <sub>5</sub> | I <sub>4</sub> | ١ <sub>3</sub> | Octal<br>Code | Function   | Symbol |

| L              | L              | L              | 0             | R plus S   | R + S  |

| L              | L              | н              | 1             | S minus R  | S - R  |

| L              | н              | L              | 2             | R minus S  | R - S  |

| L              | н              | н              | 3             | R OR S     | R S    |

| н              | L              | L              | 4             | RN AND S   | RN S   |

| н              | L              | н              | 5             | R AND S    | R S    |

| н              | н              | L              | 6             | R EX-OR S  | R S    |

| Н              | Н              | н              | 7             | R EX-NOR S | RN SN  |

+ = plus; - = minus;  $\gamma$  = OR; = AND; = EX-OR

Figure 2: ALU Function Control

In the shift up mode, the RAM<sub>3</sub> buffer is enabled and the RAM<sub>0</sub> multiplexer input is enabled. Likewise, in the shift down mode, the RAM<sub>0</sub> buffer and RAM<sub>3</sub> input are enabled. In the no-shift mode, both buffers are in the high-impedance state and the multiplexer inputs are not selected. The shifter is controlled from the I<sub>6</sub>, I<sub>7</sub> and I<sub>8</sub> microinstruction inputs as defined in Figure 4.

Similarly, the Q register is driven from a 3-input multiplexer. In the non-shift mode, the multiplexer enters the ALU data into the Q register. In either the shift-up or shift-down mode, the multiplexer selects the Q register data appropriately shifted up or down. The Q shifter also has two ports; one is labeled  $Q_0$  and the other is  $Q_3$ . The operation of these two ports is similar to the RAM shifter and is also controlled from  $I_6$ ,  $I_7$  and  $I_8$  as shown in Figure 4.

The clock input shown in Figure 1 controls the RAM, the Q resister and the A and B data latches. When enabled, data is clocked into the Q register on the LOW-to-HIGH transition of the clock. When the clock input is HIGH, the A and B latches are open and will pass whatever data is present at the RAM outputs. When the clock input is LOW, the latches are closed and will retain the last data entered. If the RAM-EN is enabled new data will be written into the RAM file (word) defined by the B address field when the clock input is LOW.

#### SOURCE OPERANDS & ALU FUNCTION

Any one of eight source operand pairs can be selected by instruction inputs lo,  $I_1$  and  $I_2$  for use by the ALU; instruction inputs  $I_3$ ,  $I_4$ , and  $I_5$  then control function selection for the ALU - five logic and three arithmetic functions. In the arithmetic mode, the carry input (Cn) also affects the ALU functions; the carry input has no effect on the 'F' result in the logic mode. These control parameters ( $I_6 - I_0$  and Cn) are summarised in Figure 5 to completely define the ALU/source operand functions.

The ALU functions can also be examined on a task basis: that is, add, subtract, AND, OR, and so on. Again, in the arithmetic mode, the carry input still affects the result, whereas in the logic mode it will not. Figures 6 and 7, respectively, define the various logic and arithmetic functions of the ALU; both carry states (Cn = 0 / Cn = 1) are defined in the function matrices.

|                | Microcode RAM I |                | RAM F         | 1 Function Q-Reg Function |       | Y     | RAM  | Shifter | Q SI             | nifter          |                 |                 |

|----------------|-----------------|----------------|---------------|---------------------------|-------|-------|------|---------|------------------|-----------------|-----------------|-----------------|

| I <sub>8</sub> | I <sub>7</sub>  | I <sub>6</sub> | Octal<br>Code | Shift                     | Load  | Shift | Load | Output  | RAM <sub>0</sub> | RAM3            | Q <sub>0</sub>  | Q3              |

| L              | L               | L              | 0             | Х                         | None  | None  | FQ   | F       | Х                | Х               | X               | Х               |

| L              | L               | Н              | 1             | Х                         | None  | Х     | None | F       | Х                | Х               | Х               | Х               |

| L              | Н               | L              | 2             | None                      | FΒ    | Х     | None | A       | Х                | Х               | Х               | Х               |

| L              | Н               | Н              | 3             | None                      | FΒ    | Х     | None | F       | Х                | Х               | Х               | Х               |

| H              | L               | L              | 4             | Down                      | F/2 B | Q/2 Q | F    | -       | F0               | IN <sub>3</sub> | Q <sub>0</sub>  | IN <sub>3</sub> |

| Н              | L               | Н              | 5             | Down                      | F/2 B | Х     | None | F       | F <sub>0</sub>   | IN <sub>3</sub> | Q <sub>0</sub>  | Х               |

| Н              | Н               | L              | 6             | Up                        | 2F B  | Up    | 2Q Q | F       | IN <sub>0</sub>  | F <sub>3</sub>  | IN <sub>3</sub> | Q3              |

| Н              | Н               | Н              | 7             | Up                        | 2F B  | Х     | None | F       | IN <sub>0</sub>  | F <sub>3</sub>  | X               | Q <sub>3</sub>  |

X = Don't Care. Electrically, the shift pin is a TTL input internally connected to a TRI-STATE output which is in the high-impedance state.

B = Register addressed by 8 inputs. Up is towards MSB, Down is towards LSB.

Figure 4: ALU Destination Control

|                             | I <sub>2,1,0</sub> Octal       | 0                | 1                | 2    | 3       | 4       | 5                | 6                | 7      |

|-----------------------------|--------------------------------|------------------|------------------|------|---------|---------|------------------|------------------|--------|

| Octal<br>I <sub>5,4,3</sub> | ALU Source<br>/ALU<br>Function | A,Q              | A,B              | 0,Q  | 0,B     | 0,A     | D,A              | D,Q              | D,0    |

| _                           | C <sub>n</sub> =L              | A+Q              | A+B              | Q    | В       | A       | D + A            | D + Q            | D      |

| 0                           | R plus S<br>C <sub>n</sub> =H  | A+Q+1            | A+B+1            | Q +1 | B + 1   | A + 1   | D + A + 1        | D + Q + 1        | D + 1  |

|                             | Cn=L                           | Q-A-1            | B-A-1            | Q -1 | B - 1   | A - 1   | A - D1           | Q - D - 1        | -D - 1 |

| 1                           | S minus R<br>C <sub>n</sub> =H | Q-A              | B-A              | Q    | В       | А       | A - D            | Q - D            | - D    |

|                             | C <sub>n</sub> =L              | A-Q-1            | A-B-1            | -Q-1 | - B - 1 | - A - 1 | D - A -1         | D - Q - 1        | D - 1  |

| 2                           | R minus S<br>C <sub>n</sub> =H | A-Q              | A-B              | - Q  | - B     | - A     | D - A            | D-Q              | D      |

| 3                           | R or S                         | A <sub>V</sub> Q | Α <sub>V</sub> Β | Q    | В       | A       | D <sub>V</sub> A | D <sub>V</sub> Q | D      |

| 4                           | R and S                        | AQ               | A B              | 0    | 0       | 0       | DA               | DQ               | 0      |

| 5                           | RN and S                       | AN Q             | AN B             | Q    | В       | A       | DN A             | DN Q             | 0      |

| 6                           | R EX-OR S                      | AQ               | AB               | Q    | В       | A       | DA               | DQ               | D      |

| 7                           | R EX NOR S                     | AN QN            | AN BN            | Q    | B       | A       | DN AN            | DN QN            | DN     |

+ = plus; - = minus; y = OR; = AND; = EX-OR

Figure 5: Source Operand and ALU Function Matrix

| Octal                        | Group        | Function         |

|------------------------------|--------------|------------------|

| I 5,4,3 /I 2,1,0             | Group        | - unction        |

| 40                           |              | A Q              |

| 41                           |              | A B              |

| 45                           | AND          | DA               |

| 46                           |              | DQ               |

| 30                           |              | A <sub>V</sub> Q |

| 31                           |              | AVB              |

| 35                           | OR           | D <sub>V</sub> A |

| 36                           |              | D <sub>V</sub> Q |

| 60                           |              | A Q              |

| 61                           |              | A B              |

| 65                           | EX-OR        | DA               |

| 66                           |              | DQ               |

| 70                           |              | AN QN            |

| 71                           | EV NOD       | AN BN            |

| 75                           | EX-NOR       | DN AN            |

| 76                           |              | DN QN            |

| 72<br>73                     |              | Q                |

| 73                           | INVERT       | B                |

| 77                           | INVERI       | A                |

|                              |              | <u>D</u>         |

| 62                           |              | Q                |

| 63                           |              | В                |

| 64                           | PASS         | A                |

| 67                           |              | D                |

| 32                           |              | Q                |

| 33                           | <b>B</b> 400 | В                |

| 34<br>37                     | PASS         | A<br>D           |

| 40                           |              | 0                |

| 40                           |              | 0                |

| 43                           | 'ZERO'       | 0                |

| 44 47                        | ZENU         | 0                |

| 50                           |              | AN Q             |

| 51                           |              | AN B             |

| 55                           | AND          | DN A             |

| 56                           | ,            | DN Q             |

| $r = p u_0; = minu_0; y = C$ |              | ii               |

+ = plus; - = minus; V = OR; = AND; = EX-OR

Figure 6: ALU Logic Mode Functions (C<sub>n</sub> Irrelevant)

| Octal           | Cn=0      | (Low)    | Cn = 1    | (High)    |

|-----------------|-----------|----------|-----------|-----------|

| I 5,4,3/I 2,1,0 | Group     | Function | Group     | Function  |

| 00              |           | A + Q    |           | A + Q +1  |

| 01              |           | A + B    | ADD       | A + B +1  |

| 05              | ADD       | D + A    | plus one  | D + A +1  |

| 06              |           | D + Q    |           | D + Q + 1 |

| 02              |           | Q        |           | Q +1      |

| 03              |           | B<br>A   |           | B+1       |

| 04              | PASS      |          | Increment | A + 1     |

| 07              |           | D        |           | D + 1     |

| 12              |           | Q - 1    |           | Q         |

| 13              |           | B - 1    |           | В         |

| 14              | Decrement | A - 1    | PASS      | A         |

| 27              |           | D - 1    |           | D         |

| 22              |           | - Q - 1  |           | - Q       |

| 23              |           | - B - 1  | 2s comp   | - B       |

| 24              | 1s comp   | - A - 1  | (negate)  | - A       |

| 17              |           | - D - 1  |           | - D       |

| 10              |           | Q - A -1 |           | Q - A     |

| 11              |           | B - A-1  |           | B - A     |

| 15              | SUBTRACT  | A - D-1  |           | A - D     |

| 16              | (1s comp) | Q - D-1  | SUBTRACT  | Q - D     |

| 20              |           | A - Q-1  | (2s comp) | A - Q     |

| 21              |           | A - B-1  |           | A - B     |

| 25              |           | D - A-1  |           | D - A     |

| 26              |           | D - Q-1  |           | D - Q     |

Figure 7: ALU Arithmetic Mode Functions

# **PIN DESCRIPTION**

| Name                               | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>0-3</sub>                   |     | The four address inputs to the register stack used to select one register whose contents are displayed through the A port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| B <sub>0-3</sub>                   | 1   | The four address inputs to the register stack used to select one register whose contents are displayed through the B port and into which new data can be written when the clock goes LOW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| I <sub>0-8</sub>                   | I   | The nine instruction control lines. Used to determine what data sources will be applied to the ALU( $I_{0,1,2}$ ), what function the ALU will perform ( $I_{3,4,5}$ ), and what data is to be deposited in the Q-register or the register stack ( $I_{6.7,8}$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Q <sub>3</sub><br>RAM <sub>3</sub> | I/O | The shift line at the MSB of the Q-register (Q <sub>3</sub> ) and the register stack (RAM <sub>3</sub> ).<br>Electrically these lines are three-state outputs connected to TTL inputs internal to<br>the device. When the destination code on $I_{6,7,8}$ indicates an up shift (Octal 6 or 7)<br>the three state outputs are enabled and the MSB of the Q-register is available on<br>the Q <sub>3</sub> pin and the MSB of the ALU output is available on the RAM <sub>3</sub> pin.<br>Otherwise, the three state outputs are electrically OFF (high impedance) and the<br>pins are electrically LS-TTL inputs. When the destination code calls for a down<br>shift, the pins are used as the data inputs to the MSB of the Q-register (Octal 4)<br>and RAM (Octal 4 or 5) |

| Q <sub>0</sub><br>RAM <sub>0</sub> | I/O | Shift lines like $Q_3$ and RAM $_3$ , but at the LSB of the Q-register and RAM. These pins are tied to the $Q_3$ and RAM $_3$ pins of the adjacent device to transfer data between devices for up and down shifts of the Q-register and ALU data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| D <sub>0-3</sub>                   | I   | Direct data inputs. A four-bit data field which may be selected as one of the ALU data sources for entering data into the device D <sub>0</sub> is the LSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Y <sub>0-3</sub>                   | 0   | The four data outputs. These are three-state output lines. When they are enabled, they display either the four outputs of the ALU or the data on the A-port of the register stack, as determined by the destination code I $_{6.7.8.}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| OEN                                | I   | Output enable. When OEN is HIGH, the Y outputs are OFF; when OEN is LOW, the Y outputs are active (HIGH or LOW)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| GN,PN                              | 0   | The carry generate and propagate outputs of the internal ALU. These signals are used with the MA2901 for carry lookahead.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| OVR                                | 0   | Overflow. This pin is logically the Exclusive OR of the carry-in and carry-out of the MSB of the ALU. At the most significant end of the word, this pin indicates that the result of an arithmetic two's complement operation has overflowed into the sign-bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| F = 0                              | 0   | This is an open collector output which goes HIGH(OFF) if the data on the four ALU outputs $F_{0-3}$ are all LOW. In positive logic, it indicates that the result of the ALU operation is zero                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| F <sub>3</sub>                     | 0   | The most significant ALU output bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| C <sub>n</sub>                     | l   | The carry-in to the internal ALU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| C <sub>n</sub> + 4                 | 0   | The carry-out of the ALU internal ALU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| CP                                 | 1   | The clock input. The Q-register and register stack outputs change on the clock LOW - to HIGH transition. The clock LOW time is internally the write enable to the 16 x 4 RAM which compromises the "master" latches of the register stack. While the clock is LOW, the "slave" latches on the RAM outputs are closed, storing the data previously on the RAM outputs. This allows synchronous master-slave operation of the register stack.                                                                                                                                                                                                                                                                                                                                  |

Figure 8: Pin Description

# DC CHARACTERISTICS AND RATINGS

| Parameter               | Min  | Max                  | Units |

|-------------------------|------|----------------------|-------|

| Supply Voltage          | -0.5 | 7                    | V     |

| Input Voltage           | -0.3 | V <sub>DD</sub> +0.3 | V     |

| Current Through Any Pin | -20  | +20                  | mA    |

| Operating Temperature   | -55  | 125                  | °C    |

| Storage Temperature     | -65  | 150                  | °C    |

**Note:** Stresses above those listed may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these conditions, or at any other condition above those indicated in the operations section of this specification, is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Figure 9: Absolute Maximum Ratings

| Subgroup | Definition                                                             |

|----------|------------------------------------------------------------------------|

| 1        | Static characteristics specified in Figure 11 at +25°C                 |

| 2        | Static characteristics specified in Figure 11 at +125°C                |

| 3        | Static characteristics specified in Figure 11 at -55°C                 |

| 7        | Functional characteristics at +25°C                                    |

| 8A       | Functional characteristics at +125°C                                   |

| 8B       | Functional characteristics at -55°C                                    |

| 9        | Switching characteristics specified in Figures 12, 13 and 14 at +25°C  |

| 10       | Switching characteristics specified in Figures 12, 13 and 14 at +125°C |

| 11       | Switching characteristics specified in Figures 12, 13 and 14 at -55°C  |

#### Figure 10: Definition of Subgroups

|                 |                                 |                                                          | Total dose radiation not exceeding 3x10 <sup>5</sup> Rad(Si) |     |     |       |

|-----------------|---------------------------------|----------------------------------------------------------|--------------------------------------------------------------|-----|-----|-------|

| Symbol          | Parameter                       | Conditions                                               | Min                                                          | Тур | Мах | Units |

| V <sub>DD</sub> | Supply Voltage                  | -                                                        | 4.5                                                          | 5.0 | 5.5 | V     |

| VIH             | Input High Voltage              | -                                                        | 2.4                                                          | -   | -   | V     |

| V <sub>IL</sub> | Input Low Voltage               | -                                                        | -                                                            | -   | 0.8 | V     |

| V <sub>OH</sub> | Output High Voltage             | I <sub>OH</sub> = -6mA                                   | 2.4                                                          | -   | -   | V     |

| V <sub>OL</sub> | Output Low Voltage              | I <sub>OL</sub> = 10mA                                   | -                                                            | -   | 0.4 | V     |

| I <sub>IN</sub> | Input Leakage Current (Note 1)  | $V_{DD} = 5.5V,$<br>$V_{IN} = V_{SS} \text{ or } V_{DD}$ | -                                                            | -   | ±10 | μA    |

| I <sub>oz</sub> | Output Leakage Current (Note 1) | $V_{DD} = 5.5V,$<br>$V_{IN} = V_{SS} \text{ or } V_{DD}$ | -                                                            | -   | ±50 | μA    |

| I <sub>DD</sub> | Power Supply Current            | Static, $V_{DD} = 5.5V$                                  | -                                                            | 0.1 | 10  | mA    |

$V_{DD} = 5V \pm 10\%$ , over full operating temperature range.

Mil-Std-883, method 5005, subgroups 1, 2, 3

Notes: 1. Guaranteed but not measured at -55°C

Figure 11: Operating Electrical Characteristics

# AC ELECTRICAL CHARACTERISTICS

| Read-Modify-Write Cycle (from selection of A,B registers to end of a cycle | 40ns  |

|----------------------------------------------------------------------------|-------|

| Maximum Clock Frequency to shift Q(50% duty cycle, I = 432 or 632)         | 25MHz |

| Minimum Clock LOW time                                                     | 20ns  |

| Minimum Clock HIGH time                                                    | 20ns  |

| Minimum Clock Period                                                       | 40ns  |

Note: 1. These timings are applied during functional tests and are not routinely measured.

Figure 12: Cycle Time and Clock Characteristics

|                     | To Output |    |                    |     |       |     |                  |                |

|---------------------|-----------|----|--------------------|-----|-------|-----|------------------|----------------|

| From Input          | Y         | F3 | C <sub>n</sub> + 4 | G,P | F = 0 | OVR | RAM <sub>0</sub> | QO             |

|                     |           |    |                    |     |       |     | RAM <sub>3</sub> | Q <sub>3</sub> |

| A,B Address         | 65        | 55 | 60                 | 55  | 70    | 65  | 65               | -              |

| D                   | 55        | 40 | 50                 | 50  | 65    | 55  | 55               | -              |

| C <sub>n</sub>      | 60        | 40 | 35                 | -   | 55    | 35  | 50               | -              |

| I <sub>0,1,2</sub>  | 70        | 50 | 55                 | 55  | 70    | 55  | 65               | -              |

| I <sub>3,4,5</sub>  | 60        | 45 | 50                 | 45  | 65    | 50  | 65               | -              |

| I <sub>6,7,8</sub>  | 45        | -  | -                  | -   | -     | -   | 30               | 30             |

| A Bypass ALU(I=2xx) | 45        | -  | -                  | -   | -     | -   | -                | -              |

| Clock               | 55        | 50 | 55                 | 50  | 50    | 55  | 55               | 35             |

Note: All timings in ns

| Figure 1  | 13: Combinational   | Propagation Delays  |  |

|-----------|---------------------|---------------------|--|

| i iguio i | 0. 0011101101101101 | r lopugution Doluyo |  |

| Input                                | CP:<br>Set-up Time<br>Before H L | Hold Time<br>After H L | Set-up Time<br>Before L H | Hold Time<br>After L H |

|--------------------------------------|----------------------------------|------------------------|---------------------------|------------------------|

| A,B Source Address                   | 25                               | 5                      | 30                        | -                      |

| B Destination Address                | 25                               | No change              | No change                 | 5                      |

| D                                    | -                                | -                      | 40                        | 0                      |

| Cn                                   | -                                | -                      | 40                        | 0                      |

| I <sub>0,1,2</sub>                   | -                                | -                      | 45                        | 0                      |

| I <sub>3,4,5</sub>                   | -                                | -                      | 45                        | 0                      |

| I <sub>6,7,8</sub>                   | 10                               | No change              | No change                 | 10                     |

| RAM <sub>0,3</sub> ,Q <sub>0,3</sub> | -                                | -                      | 15                        | 10                     |

MIL-STD-883, method 5005, subgroups 9, 10, 11

Note: 1.  $V_{DD} = 5V \pm 10\%$ , over full operational temperature range

2. CL = 50 pF

Figure 14: Set-up and Hold Times Relative to Clock (CP) Input

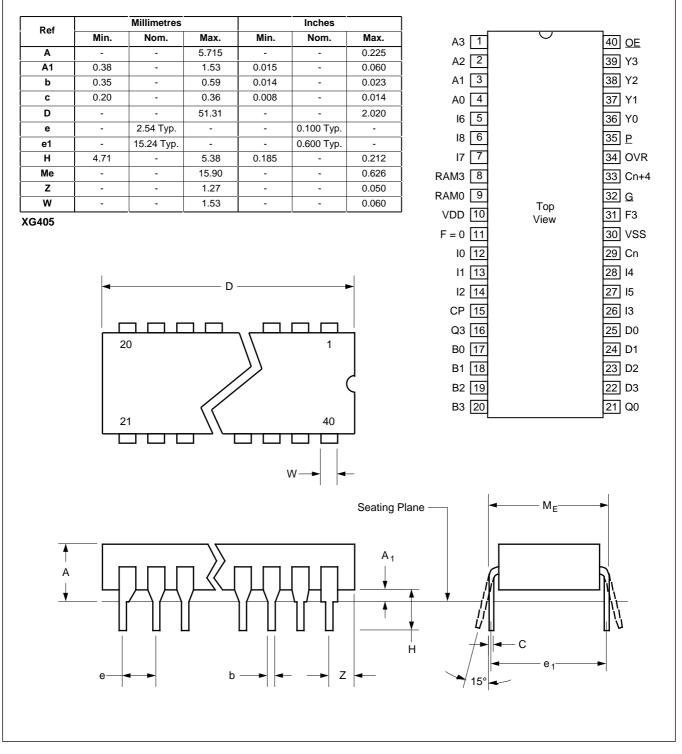

# **OUTLINES AND PIN ASSIGNMENTS**

Figure 15: 40-Lead Ceramic DIL (Solder Seal) - Package Style C

| Ref   | Millimetres |       | Inches |       |

|-------|-------------|-------|--------|-------|

| rer   | Min.        | Max.  | Min.   | Max.  |

| Α     | 1.75        | 2.49  | 0.070  | 0.098 |

| b     | 0.43        | 0.53  | 0.017  | 0.023 |

| С     | 0.15        | 0.25  | 0.006  | 0.010 |

| D     | 26.67       | 27.69 | 1.050  | 1.080 |

| E     | 15.75       | 16.76 | 0.620  | 0.660 |

| E1    | -           | 17.27 | -      | 0.630 |

| E2    | 13.21       | -     | 0.520  | -     |

| E3    | 0.76        | -     | 0.030  | -     |

| е     | 1.14        | 1.40  | 0.045  | 0.055 |

| L     | 7.87        | 9.40  | 0.310  | 0.370 |

| L1    | 32.51       | 34.54 | 1.250  | 1.360 |

| Q     | 0.76        | 1.52  | 0.030  | 0.060 |

| S     | -           | 1.14  | -      | 0.045 |

| S1    | 0.13        | -     | 0.005  | -     |

| XG136 | *           |       |        |       |

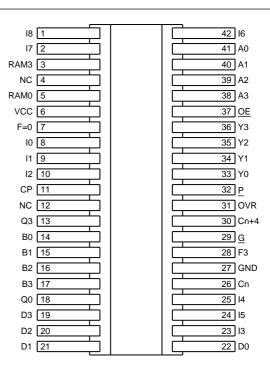

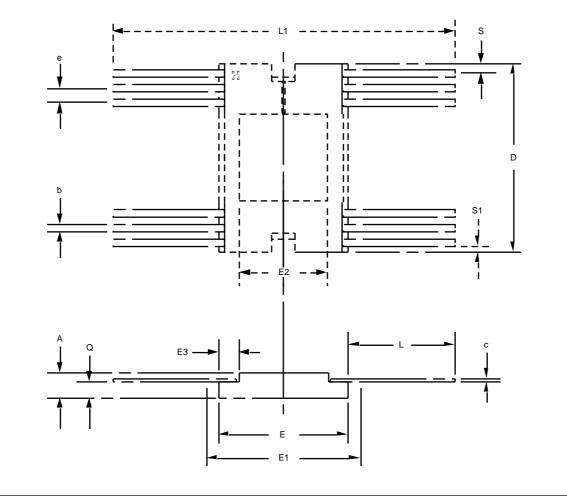

Figure 16: 42-Lead Flatpack (Solder Seal)

## **RADIATION TOLERANCE**

#### **Total Dose Radiation Testing**

For product procured to guaranteed total dose radiation levels, each wafer lot will be approved when all sample devices from each lot pass the total dose radiation test.

The sample devices will be subjected to the total dose radiation level (Cobalt-60 Source), defined by the ordering code, and must continue to meet the electrical parameters specified in the data sheet. Electrical tests, pre and post irradiation, will be read and recorded.

GEC Plessey Semiconductors can provide radiation testing compliant with Mil-Std-883 method 1019 Ionizing Radiation (total dose) test.

| Total Dose (Function to specification)*      | 3x10 <sup>5</sup> Rad(Si)             |  |

|----------------------------------------------|---------------------------------------|--|

| Transient Upset (Stored data loss)           | 5x10 <sup>10</sup> Rad(Si)/sec        |  |

| Transient Upset (Survivability)              | >1x10 <sup>12</sup> Rad(Si)/sec       |  |

| Neutron Hardness (Function to specification) | >1x10 <sup>15</sup> n/cm <sup>2</sup> |  |

| Single Event Upset**                         | 1x10 <sup>-10</sup> Errors/bit day    |  |

| Latch Up                                     | Not possible                          |  |

\* Other total dose radiation levels available on request

\*\* Worst case galactic cosmic ray upset - interplanetary/high altitude orbit

#### Figure 17: Radiation Hardness Parameters

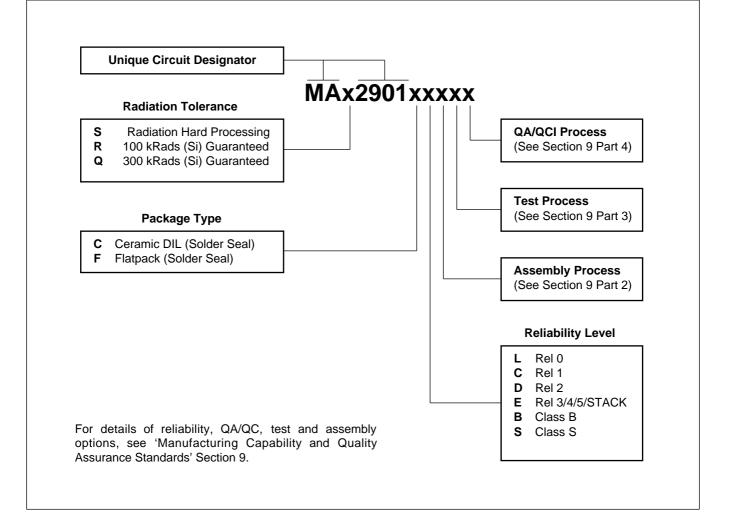

# **ORDERING INFORMATION**

#### HEADQUARTERS OPERATIONS

#### **GEC PLESSEY SEMICONDUCTORS**

Cheney Manor, Swindon, Wiltshire, SN2 2QW, United Kingdom. Tel: (01793) 518000 Fax: (01793) 518411

# GEC PLESSEY SEMICONDUCTORS

P.O. Box 660017, 1500 Green Hills Road, Scotts Valley, California 95067-0017, United States of America. Tel: (408) 438 2900 Fax: (408) 438 5576

#### CUSTOMER SERVICE CENTRES

- FRANCE & BENELUX Les Ulis Cedex Tel: (1) 64 46 23 45 Fax: (1) 64 46 06 07

- GERMANY Munich Tel: (089) 3609 06-0 Fax: (089) 3609 06-55

- ITALY Milan Tel: (02) 66040867 Fax: (02) 66040993

- JAPAN Tokyo Tel: (03) 5276-5501 Fax: (03) 5276-5510

- NORTH AMERICA Scotts Valley, USA Tel: (408) 438 2900 Fax: (408) 438 7023

- SOUTH EAST ASIA Singapore Tel: (65) 3827708 Fax: (65) 3828872

- SWEDEN Stockholm Tel: 46 8 702 97 70 Fax: 46 8 640 47 36

- TAIWAN, ROC Taipei Tel: 886 2 5461260 Fax: 886 2 7190260 • UK, EIRE, DENMARK, FINLAND & NORWAY Swindon, UK

- Tel: (01793) 518527/518566 Fax: (01793) 518582

These are supported by Agents and Distributors in major countries world-wide.

© GEC Plessey Semiconductors 1995 Publication No. DS3576-3.3 February 1995

TECHNICAL DOCUMENTATION - NOT FOR RESALE. PRINTED IN UNITED

This publication is issued to provide information only which (unless agreed by the Company in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. No warranty or guarantee express or implied is made regarding the capacity performance or suitability of any product or service. The Company reserves the right to alter without prior knowledge the specification, design or price of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to the Company's conditions of sale, which are available on request.