# Power Management Bias Controller/Sequencer Supply :-6V, +5V

#### MABC-11040B Rev V2

#### **Features**

- Quad Output I<sup>2</sup>C programmable analogue outputs using 12bit DACs with rail to rail output voltage range

- · High output current capability +100mA / -60mA

- · Programmable gate-current limit

- I<sup>2</sup>C clock rates up to 400kHz

- Internal and external temperature sensor supporting temperature compensation in application

- · Built in sequencing with drain bias control support

- · Sequenced auxiliary current source

- Internal EEPROM for autonomous operation

- Two 12bit Telemetry ADC inputs

- · General purpose GPIO interface

- Optional internal negative voltage generator, generating –5V from the positive 5V supply

- Supply voltage range -6V, 5V

#### **Applications**

- · GaN FET bias Controller

- HEMT bias Controller

- · Circuit Temperature Compensation

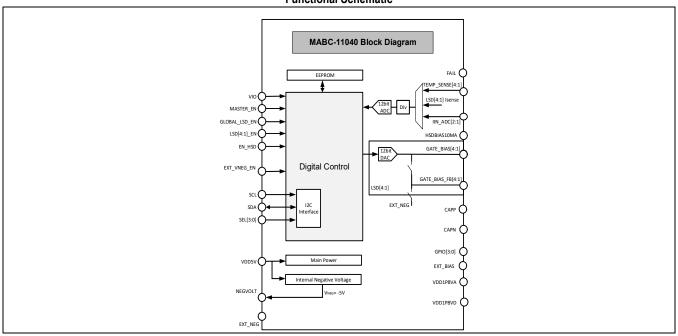

The MABC-11040 is a flexible bias generation and temperature supervision IC.

The MABC-11040 contains four highly integrated, temperature-controlled DACs that support a negative output range from -6V to 0V and are capable of handling large output currents. The four DACs can be programmed independently by four separate user-defined temperature-to-voltage functions stored in the internal EEPROM, allowing any temperature effects to be corrected without additional external circuitry. Each output can be switched to the load individually through the use of dedicated control pins.

The MABC-11040 provides bias sequencing for safe power up and power down. The drain voltage may be applied with a control signal via the internal drain bias control once the IC has powered up and correct biasing has been asserted.

Once powered up, the device operates autonomously, without intervention from the system controller, providing a complete solution for setting and compensating bias voltages and currents in control applications. Additionally, the device supports up to four thermistors placed closely to the PAs for more accurate temperature reading.

The digital interface allows control and monitoring of all four Low side drivers, gate current, and temperature of the PA. In addition, the drain current of the PA can be monitored via an external high-side current sense amplifier and an internal ADC.

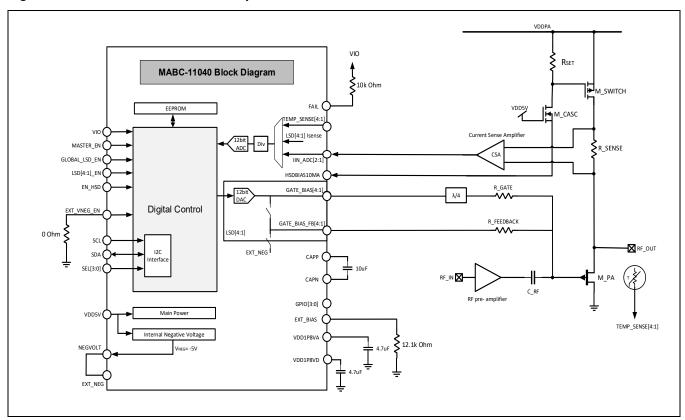

#### **Functional Schematic**

1

MACOM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice.

MABC-11040B Rev V2

### **Ordering Information**

| Part Number        | Package         | Operating Temperature |  |  |

|--------------------|-----------------|-----------------------|--|--|

| MABC-11040B        | 6 x 6 mm PQFN48 | -40°C to +125°C       |  |  |

| MABC-11040B-SB1PPR | EVM Kit         | -40°C to +125°C       |  |  |

### **Revision History**

| Revision             | Level                | Date Description                                                 |                                                                      |  |  |

|----------------------|----------------------|------------------------------------------------------------------|----------------------------------------------------------------------|--|--|

| V2 Release Oct, 2022 |                      |                                                                  | Updated pinout and function description; Removed application chapter |  |  |

| V1                   | V1 Release May, 2022 |                                                                  | Updated Pin-out diagram, Updated electrical specifications           |  |  |

| V5P                  | Preliminary          | ary May, 2021 Updated LSD Current Limit. and Application diagram |                                                                      |  |  |

| V1P                  | Preliminary          | May, 2021                                                        | Preliminary Initial release                                          |  |  |

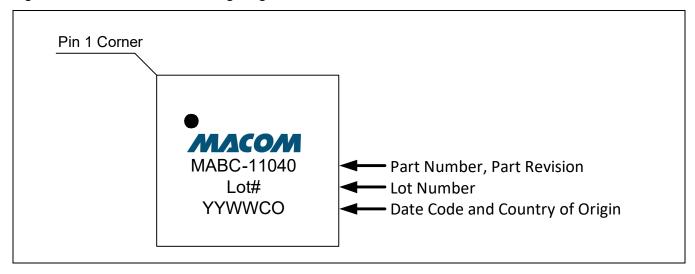

Figure 1-1. MABC-11040 Marking Diagram

# Power Management Bias Controller/Sequencer Supply :-6V, +5V

MARC-11040R

|     |     |                                                            | Rev V2 |

|-----|-----|------------------------------------------------------------|--------|

| 1.0 | Ele | ctrical Characteristics                                    |        |

| 2.0 | Pac | kage Outline Drawing, Pinout Diagram, and Pin Descriptions |        |

|     | 2.1 | MABC-11040 Pinout                                          |        |

|     | 2.2 | Package Outline Drawing                                    |        |

| 3.0 | Fun | nctional Description                                       |        |

|     | 3.1 | Overview                                                   |        |

|     | 3.2 | Device Power up/down                                       | 16     |

|     |     | 3.2.1 Power up Sequence                                    |        |

|     |     | 3.2.2 Power Down Sequence                                  |        |

|     |     | 3.2.3 Initial Register Settings                            | 17     |

|     |     | 3.2.4 Negative Charge Pump                                 | 17     |

|     | 3.3 | Low Side Driver (LSD)                                      |        |

|     |     | 3.3.1 12-bit DAC                                           | 19     |

|     |     | 3.3.2 12-bit ADC                                           | 20     |

|     |     | 3.3.3 Gate Bias Close Loop                                 | 25     |

|     |     | 3.3.4 LSD Headroom                                         | 26     |

|     | 3.4 | High Side Driver                                           | 27     |

|     | 3.5 | Look up Table                                              | 28     |

|     |     | 3.5.1 Look Up Table for Temperature                        | 29     |

|     |     | 3.5.2 Look Up Table for Voltage                            |        |

|     | 3.6 | Addition features                                          |        |

|     |     | 3.6.1 EEPROM Programming Procedure                         |        |

Control Registers Map and Descriptions......40

3.6.2

3.6.3 3.6.4

3.6.5

3.7

4.0

# **5G GaN FEM Power Management Controller Supply :-6V, +5V**

MABC-11040B Rev V2

## 1.0 Electrical Characteristics

Unless noted otherwise, specifications in this section are valid with VDD5V = 5 V, VDD1P8V = 1.8 V, EXT\_NEG = -5 V, and an ambient temperature of 25°C.

Table 1-1. Absolute Maximum Ratings

| Symbol             | Parameter                              | Notes   | Min.  | Тур. | Max.  | Units |

|--------------------|----------------------------------------|---------|-------|------|-------|-------|

| VDD5V              | Positive Supply Voltage (5V)           | 1,2     |       |      | 5.5   | V     |

| VIO                | Digital Power Supply                   | 1,2     |       |      | 3.6   | V     |

| EXT_NEG            | Negative Analog Voltage Input          | 1,2     | -6.05 |      |       | V     |

| T <sub>sold</sub>  | Lead Soldering Temperature             | 1,2     |       |      | 260   | °C    |

| T <sub>J,ABS</sub> | Junction Temperature                   | 1,2,3,4 |       |      | 140   | °C    |

| C_ldo              | Output Capacitor on Pin 23, Pin 43     | 5       |       |      | 1     | uF    |

| T <sub>Store</sub> | Storage Temperature                    | 1,2,3,4 |       |      | 140   | °C    |

| V <sub>HBM</sub>   | Human-body model                       |         | -2000 | _    | +2000 | V     |

| V <sub>CDM</sub>   | Charged-device model                   |         | -500  | _    | +500  | V     |

| $\theta_{\sf JC}$  | Thermal resistance junction to paddle  | 6       |       | 2    |       | °C/W  |

| $\vartheta_{JA}$   | Thermal resistance ambient to junction | 6       |       | 15.7 |       | °C/W  |

#### NOTE:

- 1. Exceeding any one or a combination of these parameter limits may cause permanent damage to the device and cause the device to not function properly.

- 2. MACOM does not recommend sustained operation near these survivability limits

- 3. Operating with normal conditions with TJ ≤ 150°C will ensure MTTF > TBD hours.

- 4. Tj, Junction temperature is based on Theta JC (bottom) = 2°C/W.

- 5. If use internal LDO for 1.8V supply.

- 6. No airflow

# **5G GaN FEM Power Management Controller Supply :-6V, +5V**

MABC-11040B Rev V2

#### Table 1-2. Recommended Operating Conditions

| Symbol             | Parameter                                               | Notes | Min. | Тур. | Max. | Units |

|--------------------|---------------------------------------------------------|-------|------|------|------|-------|

| VDD5V              | Positive Supply Voltage (5V)                            |       | 4.75 | 5    | 5.25 | V     |

| VIO                | Digital Power Supply                                    |       | 1.65 |      | 3.6  | V     |

| EXT_NEG            | Negative Analog Voltage Input                           |       | -6   | -5   | -4.5 | V     |

| I <sub>VDD5V</sub> | Current consumption in low power mode (MASTER_EN = Low) |       |      |      | 9    | mA    |

|                    | Charge pump enable (default setting)                    | 1     |      | 26   |      | mA    |

|                    | Charge pump disabled                                    | 3     | -    | 10   |      | mA    |

| I <sub>VIO</sub>   | Current consumption for VIO                             |       | 0    | 0.5  | 1    | mA    |

| I <sub>NEG</sub>   | Supply Current from Negative Supply                     | 4     | -    | 16   |      | mA    |

| T <sub>j</sub>     | Operating Junction Temperature                          | 2     | -40  |      | 125  | °C    |

#### NOTE:

- 1. Quiescent current for charge pump is ~2mA/Mhz based on the working frequency. Pin 16 and 17 shorted. Mid code for all LSD,no load, the current on all 5V and VIO. With internal 1.8V Supply.Current sense of LSD off

- 2. Tj, Junction temperature is based on Theta JC (bottom) = 2°C/W.

- 3. Charge pump is disabled. Pin 16 and Pin 17 is opened. Mid code and no load on LSD. Measure the current to all positive supply. With internal 1.8V Supply

- 4. Typical current on EXT\_NEG when for MABC11040 With internal 1.8V Supply

# **5G GaN FEM Power Management Controller Supply :-6V, +5V**

MABC-11040B Rev V2

Table 1-3. Electrical Characteristics

| Symbol                       | Parameter                                                                                      | Notes | Min | Тур | Max | Unit |  |  |  |

|------------------------------|------------------------------------------------------------------------------------------------|-------|-----|-----|-----|------|--|--|--|

| Low Side Driver              |                                                                                                |       |     |     |     |      |  |  |  |

| R <sub>STAB</sub>            | Stability Resistance                                                                           |       |     | 0.5 |     | Ω    |  |  |  |

| TLSD_RDY                     | Response time from power on to all LSD_rdy with load capacitor=10uF                            |       |     | 10  |     | msec |  |  |  |

| VCPRI                        | Output Voltage Ripple on charge pump                                                           | 2     |     | 50  |     | mV   |  |  |  |

| VLDRI                        | Output Voltage Ripple on charge pump                                                           | 1     |     | 0.2 | 150 | mV   |  |  |  |

| BW_LSD                       | -3 dB Bandwidth of LSD                                                                         | 3     | 72  |     |     | KHz  |  |  |  |

| Cstab                        | Stability capacitance                                                                          | 1     | 1   | 10  |     | uF   |  |  |  |

| GERR_SOURCE_<br>M1V          | Gate Control Voltage Error Over iload sourcing current, process & mismatch variation @ -1V     |       | -49 |     |     | mV   |  |  |  |

| GERR_SOURCE_V<br>NEG_PLUS_1V | Gate Control Voltage Error Over iload sourcing current, process & mismatch variation @ VNEG+1V |       | -62 |     |     | mV   |  |  |  |

| GERR_SINK_M1V                | Gate Control Voltage Error Over iload sinking current, process & mismatch variation @ -1V      |       |     |     | 27  | mV   |  |  |  |

| GERR_SINK_VNE<br>G_PLUS_1V   | Gate Control Voltage Error Over iload sinking current, process & mismatch variation @ VNEG+1V  |       |     |     | 44  | mV   |  |  |  |

| VLD_RES                      | Adjustable Gate Control Voltage Resolution                                                     | 3,4   |     | 1.2 |     | mV   |  |  |  |

#### NOTE:

- 1. -10mA to 6mA load.

- 2. Cfly=1uF, Cout=22uF, load of charge pump<150mA.

- 3. Clsd=10uF.

- 4. Minimum capacitance required for on-chip OPAMP stability/

- 5.  $10\mu F$  at FAST\_CHARGEx /10nF at GATE\_BIASx, measured from GLOBAL\_LSD\_EN or LSD\_EN pin transitions to gate bias pin rising from -5V to -1V.

- 6. 12-bit DAC, depends on feedback resistor accuracy in note 4.

- 7. 0.1% resistor tolerance between the feedback resistor of LSD versus the resistor on ext\_bias pin.

|                       | LSD Driver Chara                                     | cteristics       |   |                 |   |   |

|-----------------------|------------------------------------------------------|------------------|---|-----------------|---|---|

| V <sub>GATE_INT</sub> | Adjustable Gate Voltage using integrated charge-pump | 0mA<br>Sourced   | 1 | -VDD5V          | 0 | V |

|                       |                                                      | 100mA<br>Sourced |   | -1              |   |   |

|                       |                                                      | 60mA<br>Sunk     |   | -4.2            |   |   |

| V <sub>GATE_EXT</sub> | Adjustable Gate Voltage using external charge-pump   | 0mA<br>Sourced   | 2 | EXT_NEG         | 0 | V |

|                       |                                                      | 100mA<br>Sourced |   | -1              |   |   |

|                       |                                                      | 60mA<br>Sunk     |   | EXT_NEG+<br>0.8 |   |   |

6

MACOM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice.

# **5G GaN FEM Power Management Controller Supply :-6V, +5V**

MABC-11040B Rev V2

#### Table 1-3. Electrical Characteristics

| Symbol     | Parameter                                                 | Notes            | Min | Тур | Max | Unit |

|------------|-----------------------------------------------------------|------------------|-----|-----|-----|------|

| $V_{HRMN}$ | Headroom voltage from LSD_DRV/LSD_DAC to negative voltage | 0mA<br>Sourced   |     | 10  |     | mV   |

|            |                                                           | 100mA<br>Sourced | 3   | 400 |     |      |

|            |                                                           | 60mA<br>Sunk     |     | 400 |     |      |

| $V_{HRMP}$ | Headroom voltage from GND to LSD_DRV/LSD_DAC, source      | 0mA<br>Sourced   |     | 10  |     | mV   |

|            |                                                           | 100mA<br>Sourced | 3   | 400 |     |      |

|            |                                                           | 60mA<br>Sunk     |     | 400 |     |      |

#### NOTE:

- 1. VDD5V = 5V; Rgate =  $6\Omega$

- 2. External negative supply = EXT\_NEG

- 3. Including bond wire loss, the chip need such minimum headroom for output to meet the spec

|              | LSD_DRV Current Characteristics                |   |    |    |     |      |  |  |  |  |

|--------------|------------------------------------------------|---|----|----|-----|------|--|--|--|--|

| ILIMIT       | Adjustable Gate Current sourcing Typical Limit |   | 20 |    | 110 | mA   |  |  |  |  |

| ILIMITRES_ER | Current Limit Resolution Error                 |   |    | 10 |     | mA   |  |  |  |  |

| LSD_SSD      | Slow Shutdown Response Time                    | 1 |    | 10 |     | msec |  |  |  |  |

| LSD_LRT      | Limiter response time (Time constant)          |   |    | 20 |     | usec |  |  |  |  |

#### NOTE:

10uF output capacitor.

| LSD_DRV Current Sense  |                                                        |   |       |    |      |    |  |  |

|------------------------|--------------------------------------------------------|---|-------|----|------|----|--|--|

| LSD_CUR                | Gate Current from LSD1_DRV- LSD4_DRV, Source / Sinking | 1 | -60   |    | 100  | mA |  |  |

| LSD_IRES               | Gate Current Digitised Readout Resolution (12-bit)     |   |       | 24 |      | uA |  |  |

| LSD_IRES_SINK_E<br>R1  | Gate Current Measurement Error                         | 2 | -10   | 0  | 10   | %  |  |  |

| LSD_IRES_SINK_E<br>R2  | Gate Current Measurement Error                         | 3 | -1000 | 0  | 1000 | uA |  |  |

| SD_IRES_SINK_E<br>R3   | Gate Current Measurement Error                         | 4 | -6    | 0  | 6    | mA |  |  |

| SD_IRES_SOURC<br>E_ER1 | Gate Current Measurement Error                         | 2 | -10   | 0  | 10   | %  |  |  |

| SD_IRES_SOURC<br>E_ER2 | Gate Current Measurement Error                         | 3 | -1000 | 0  | 1000 | uA |  |  |

| SD_IRES_SOURC<br>E_ER3 | Gate Current Measurement Error                         | 5 | -10   | 0  | 10   | mA |  |  |

# **5G GaN FEM Power Management Controller Supply :-6V, +5V**

MABC-11040B Rev V2

#### Table 1-3. Electrical Characteristics

|   | Symbol     | Parameter                      | Notes | Min | Тур | Max | Unit |

|---|------------|--------------------------------|-------|-----|-----|-----|------|

| ĺ | LSD_CUR_RT | Gate Current Measurement Error |       |     | 750 |     | usec |

#### NOTE:

- 1. Max total gate current from each LSD drivers

- 2. System errors all added together, Absolute value of (LSD\_CUR)>10mA, output range between (-1V, EXT\_NEG+1V)

- 3. System errors all added together, Absolute value of (LSD\_CUR)<10mA,output range between (-1V, EXT\_NEG+1V)

- 4. System errors all added together, LSD\_CUR=-60mA,output range between (-1V, EXT\_NEG+1V)

- 5. System errors all added together, LSD\_CUR=+100mA,output range between (-1V, EXT\_NEG+1V).

| LSD Temperature Sense              |                                                 |   |    |   |     |      |  |  |  |  |

|------------------------------------|-------------------------------------------------|---|----|---|-----|------|--|--|--|--|

| THERM_VRANGE                       | Input Voltage range for TEMP_SENSEx pins        |   | 0  |   | 2   | V    |  |  |  |  |

|                                    | Fail Alert                                      |   |    |   |     |      |  |  |  |  |

| FAIL_RT                            | Fail alert response time                        |   |    |   | 2   | msec |  |  |  |  |

| HSD Driver Current Characteristocs |                                                 |   |    |   |     |      |  |  |  |  |

| HSD_CUR_ON                         | Typical Current bias range for high side driver | 1 | 3  |   | 10  | mA   |  |  |  |  |

| HSD_CUR_STEP                       | Eight Steps                                     | 1 |    | 1 |     | mA   |  |  |  |  |

| HSD_CUR_OFF                        | Current sunk at "OFF" state                     | 2 |    |   | 0.1 | mA   |  |  |  |  |

| HSD_SW                             | HSD turn on time                                | 3 |    |   | 10  | msec |  |  |  |  |

| HSD_CAP                            | PFET capacitance allowed                        | 4 |    |   | 20  | uF   |  |  |  |  |

| HSD_accuracy                       | Current accuracy                                |   | -5 |   | 5   | %    |  |  |  |  |

#### NOTE:

- Current sunk in on state

- 2. Current sunk in off state

- 3. Configurable; From EN\_HSD pin to voltage on gate bias pin settle

- 4. no data sheet of PMIC, application note only

| ADC Electrical Specification |                                 |   |     |       |   |      |  |

|------------------------------|---------------------------------|---|-----|-------|---|------|--|

| ADC_RANGE                    | Input Range                     |   | 0   |       | 1 | V    |  |

| ADC_RES                      | ADC resolution                  |   |     | 0.244 |   | mV   |  |

| ADC_DNL                      | DNL                             |   |     | 1     | 1 | LSB  |  |

| ADC_INL                      | INL                             |   |     | 10    |   | LSB  |  |

| ADC_IMP                      | Input impedance                 |   | 600 |       |   | ΚΩ   |  |

| ADC_RT                       | Response time                   |   |     | 1     |   | msec |  |

| ADC_SR_single                | Conversion time, single channel | 1 |     | 0.05  |   | msec |  |

| ADC_SR_Row                   | Conversion time, whole channel  | 2 |     | 0.75  |   | msec |  |

# **5G GaN FEM Power Management Controller Supply :-6V, +5V**

MABC-11040B Rev V2

#### Table 1-3. Electrical Characteristics

| Symbol       | Parameter                          |  | Min  | Тур | Max | Unit |

|--------------|------------------------------------|--|------|-----|-----|------|

| ADC_OFF      | Input offset                       |  |      | 1   |     | mV   |

| ADC_ERROR_FS | ADC error at full scale excitation |  | -1.5 |     | 1.5 | %    |

#### NOTE:

- Sample rate for each channel

- 2. Sample rate for whole channel

Table 1-4. Control/Interface Logic Static Specifications (EN\_HSD, GLOBAL\_LSD\_EN, MASTER\_EN, EXT\_VNEG\_EN, LSDx\_EN, GPIO-3,FAIL)

| Symbol          | Parameter                                   | Notes | Min.     | Тур.    | Max.     | Units |

|-----------------|---------------------------------------------|-------|----------|---------|----------|-------|

| VIH             | Input Logic High Threshold                  |       | 0.65*VIO |         |          | V     |

| VIL             | Input Logic Low Threshold                   |       |          |         | 0.35*VIO | V     |

| Vhyst1          | hysteresis of Schmit trigger input(VIH-VIL) |       | 0.05*VIO | 0.1*VIO |          | V     |

| VOH             | VOH Output Logic High                       | 1     | VIO-0.4  |         |          | V     |

| VOL             | VOL Output Logic Low                        | 2,3   |          |         | 0.4      | V     |

| Tdhl            | delay from pad to core, high to low         | 4     |          | 8       | 12       | nS    |

| Tdlh            | delay from pad to core, low to high         | 4     |          | 8       | 12       | nS    |

| C <sub>IN</sub> | I/O pins internal capacitance               |       |          | 1.5     |          | pF    |

| I2C_CAP         | Board capacitance on I2C nodes              | 5     |          | 65      |          | pF    |

#### NOTE:

- 1. With 3mA sinking load

- 2. with 3mA source load

- 3. Fail pin is open drain so only VOL applied to it

- 4. run with Trise=Tfall=6ns input signal, measure between middle points

- 5. Total capacitor on the bus should not be higher than 65pF

MABC-11040B Rev V2

# 2.0 Package Outline Drawing, Pinout Diagram, and Pin Descriptions

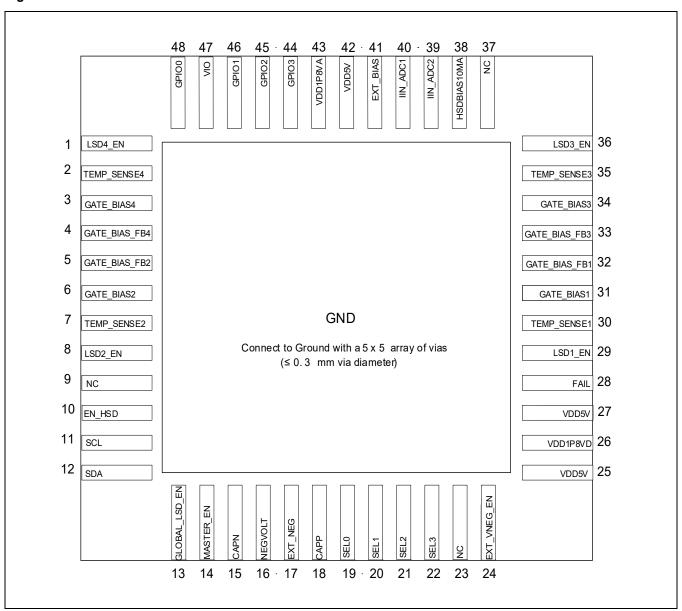

### 2.1 MABC-11040 Pinout

Figure 2-1. MABC-11040 Pinout

10

MACOM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice.

# Power Management Bias Controller/Sequencer Supply :-6V, +5V

MABC-11040B Rev V2

Table 2-1. Pin Configuration

| Pin Name          | Pin Number     | Туре          | Description                                                                                                                                                                                                                                            |

|-------------------|----------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD5V             | 25, 27, 42     | Power         | 5V Power Supply.                                                                                                                                                                                                                                       |

| VIO               | 47             | Power         | GPIO power supply, 1.8V or 3.3V.                                                                                                                                                                                                                       |

| EXT_NEG           | 17             | Power         | External negative input power supply -6V to -4.5V.                                                                                                                                                                                                     |

| IIN_ADC[2:1]      | 39, 40         | Analog Input  | Inputs to internal ADC                                                                                                                                                                                                                                 |

| EXT_BIAS          | 41             | Analog Input  | Connected to external 12.1Kohm 0.1% resistor to Ground.                                                                                                                                                                                                |

| CAPN              | 15             | Analog Input  | Negative terminal for Charge pump capacitor. A 10uF capacitor needed between CAPP and CAPN, 400mA                                                                                                                                                      |

| CAPP              | 18             | Analog Input  | Positive terminal for Charge pump capacitor. A 10uF capacitor needed between CAPP and CAPN, 400mA                                                                                                                                                      |

| TEMP_SENSE[4:1]   | 2, 35, 7, 30   | Analog Input  | LSD driver[4:1] positive pin for thermistor                                                                                                                                                                                                            |

| NEGVOLT           | 16             | Analog Output | Negative voltage output, -5V typ. Connect to EXT_NEG if internal Charge Pump is used.                                                                                                                                                                  |

| VDD1P8VA          | 43             | Analog Output | 1.8V internal supply, connect 4.7uF to Ground                                                                                                                                                                                                          |

| VDD1P8VD          | 26             | Analog Output | 1.8V internal supply, connect 4.7uF to Ground                                                                                                                                                                                                          |

| GATE_BIAS[4:1]    | 3, 34, 6, 31   | Analog Output | LSD DAC [4:1] 60mA                                                                                                                                                                                                                                     |

| GATE_BIAS_FB[4:1] | 4, 33, 5, 32   | Analog Output | LSD feedback                                                                                                                                                                                                                                           |

| HSDBIAS10mA       | 38             | Analog Output | Predriver current bias pin, 10mA. NMOS Open Drain, cannot exceed +5VDC.                                                                                                                                                                                |

| MASTER_EN         | 14             | Digital Input | Master enable signal, internal 85K ohm pull-down. Referred to VIO. H: Normal operation. L: Device in Standby Mode.                                                                                                                                     |

| EN_HSD            | 10             | Digital Input | External enable pin to enable high side driver, Internal 85K ohm pull-down. Referred to VIO. H: HSD Enabled L: HSD Disabled                                                                                                                            |

| GLOBAL_LSD_EN     | 13             | Digital Input | Global LSD Output Enabled, internal 60K ohm pull-up. H: LSD Drivers Enabled L: LSD Drivers Disabled                                                                                                                                                    |

| LSD[4:1]_EN       | 1, 36, 8, 29   | Digital Input | Enable signal of LSD drivers, internal 60K ohm pull-up. This pins overrides pin GLOBAL_LSD_EN H: LSD Driver Enabled L: LSD Driver Disabled                                                                                                             |

| EXT_NEG_EN        | 24             | Digital Input | Enables internal negative supply voltage, internal 60K ohm pull-down. Referred to VIO. H: Internal negative voltage disabled, use external negative power supply to pin EXT_NEG L: Internal negative voltage enabled, internal Charge Pump is enabled. |

| GPIO[3:0]         | 44, 45, 46, 48 | Digital I/O   | General purpose I/O, internal 100k ohm pull up to VIO.                                                                                                                                                                                                 |

# Power Management Bias Controller/Sequencer Supply :-6V, +5V

MABC-11040B Rev V2

Table 2-1. Pin Configuration

| Pin Name | Pin Number     | Туре           | Description                                                                    |

|----------|----------------|----------------|--------------------------------------------------------------------------------|

| Fail     | 28             | Digital Output | Fail alarm status, Open drain, needs a 10k ohm external pull. Referred to VIO. |

| SCL      | 11             | Digital Input  | I2C Interface SLCK                                                             |

| SDA      | 12             | Digital I/O    | I2C Interface SDA                                                              |

| SEL[3:0] | 22, 21, 20, 19 | Digital Input  | I2C slave address selection pin, internal 100k ohm pull-up to VDD5V.           |

| NC       | 9, 23, 37      | No connect     | Do not connect, leave floating.                                                |

MABC-11040B Rev V2

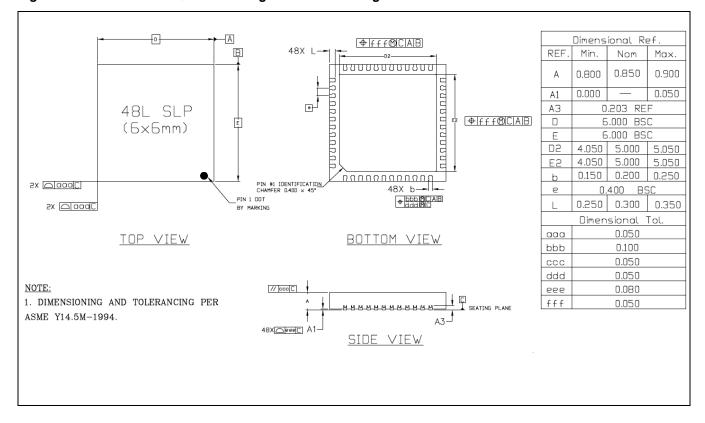

## 2.2 Package Outline Drawing

Figure 2-2. 6 x 6 mm PQFN48 Package Outline Drawing

# Power Management Bias Controller/Sequencer Supply :-6V, +5V

MABC-11040B Rev V2

## 3.0 Functional Description

### 3.1 Overview

The MABC-11040 is a highly integrated Power Management Integrated Circuit (PMIC) which provides all the features necessary to safely and intelligently sequence and bias a multi-stage GaN Power Amplifier. It consists of a single High Side Driver (HSD), four Low Side Drivers (LSDs), an internal negative charge pump, four general purpose GPIO pins, an integrated temperature sensor, four external temperature sensors, and ADC.

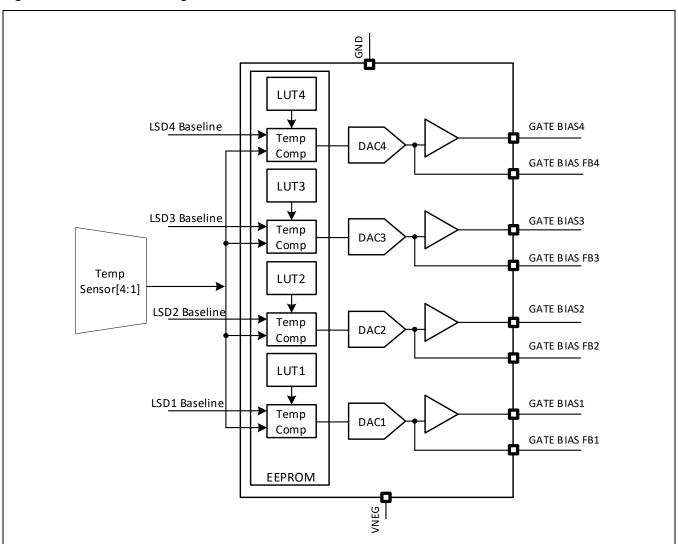

At its core the MABC-11040 is a quad temperature-dependent low side bias generator and drivers (LSD) whose temperature-to-voltage transfer functions are user-defined. This device contains a digitized temperature sensor that addresses four independently programmable look-up tables (LUTs). The outputs of LUTs are sent on to their respective 12-bit DACs to produce four independent output voltages.

As well as providing four independent LSDs, the MABC-11040 also includes an HSD. The HSD enables an off-chip pass gate, which can be used to correctly sequence all PA biasing.

In applications requiring rapid ON/OFF switching of the bias voltage, the MABC-11040 provides asynchronous control over its outputs. Dedicated digital input pins control analogue output switching. Each LSD can be independently controlled with its dedicated control pin or alternatively all four LSDs can be switched together by a single enable pin. When this pin is set to low then all four LSDs are turned off, and when this pin is set to high, then each LSD is controlled by its own enable control.

All aspects of the device functionality are controlled through internal registers. These registers, and the LUTs, are accessible through the I<sup>2</sup>C-compatible interface.

The MABC-11040 can operate autonomously of the system controller, once LUT coefficients have been committed to its EEPROM's non-volatile memory. Upon power up the EEPROM content is automatically transferred to the operating memory, and the device begins to produce the required bias voltages.

MABC-11040B Rev V2

Figure 3-1. Functional Block Description

MABC-11040B Rev V2

### 3.2 Device Power up/down

#### 3.2.1 Power up Sequence

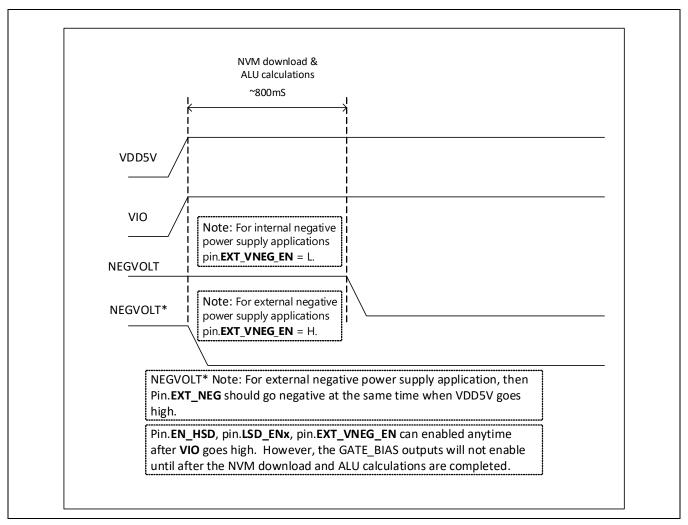

Figure 3-2 shows the recommended power up sequence

VIO should be become enabled at the same time that VDD5V is turned on.

If the external negative enable pin is low, the negative supply will turn on after about 800ms the **VDD5V** supplies are turned on.

If an external negative power supply applications, pin.**EXT\_VNEG\_EN** should be set to High and -5V should be applied to pin.**NEGVOLT** after VDD5V and VIO are enabled. The pin.**EXT\_VNEG\_EN** should be high and the negative supply will go negative after **VDD5V** is turned on.

Figure 3-2. Power-up Sequencing

16

MABC-11040B Rev V2

#### 3.2.2 Power Down Sequence

It's recommended that the device is disabled with pin.MASTER EN = LOW before VDD5V and VIO are turned off.

### 3.2.3 Initial Register Settings

The 50V supply for the GaN (VDD\_GaN) should be turned on first, followed by the power up sequence for the MABC-11040(refer to 3.2.1) while pin.**EN\_HSD** must be kept low. After power up, load the following passwords to the MABC-11040:

Password for Page0x00h: write Page 0x00h Register 0xFAh with value 0x20h;

Password for Page0x01h/02h: write Page 0x00h Register 0xFBh with value 0x19h;

Password for Page0x80h/ 0x81h: write Page 0x00h Register 0xFCh with value 0x07h;

Password for Page0x90h/91h/92h/93h: write Page 0x00h Register 0xFDh with value 0x04h;

Pin.EN\_HSD and pin.EN\_LSD[1:4] should be set to High to enable the LSDs.

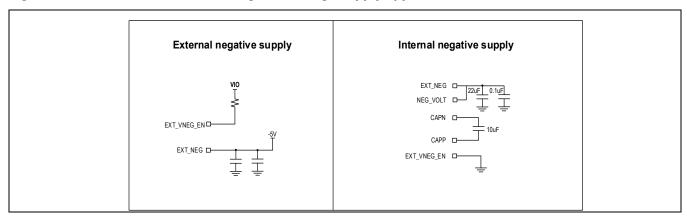

#### 3.2.4 Negative Charge Pump

For applications where there is no negative voltage on the board, MABC-11040B includes a negative charge pump which can invert the positive supply voltage provided to **VDD5V** (the input to the charge pump). The negative pin.internal charge pump requires external bypassing of 22 uF on pin.**NEGVOLT**, and a 10uF fly-back capacitor between **CAPN** and pin.**CAPP**. There is a dedicated external pin.**EXT\_VNEG\_EN**, which enables or disables the internal charge pump. In the case of using the negative charge pump, **NEGVOLT** and **EXT\_NEG** need to be shorted on the PCB.

If an external negative voltage supply is to be used, VDD5V should be applied to the pin.**EXT\_VNEG\_EN** to disable the internal charge pump and pin.**NEGVOLT** should be connected to GND. If the external negative voltage is used as a supply for LSDs, the negative voltage should turn on at the same time when the **VDD5V** is applied. The pin.**MASTER EN** will be pulled low at start-up, disabling the internal negative supply.

See Figure 3-3 for the application schematic.

Figure 3-3. Internal and External Negative voltage supply application schematic

17

MACOM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice.

MABC-11040B Rev V2

### 3.3 Low Side Driver (LSD)

The Low Side Driver is a DAC that provides a negative voltage for the gate of a GaN device. The Low Sides Drivers are compensated over temperature by means of Look-Up Tables (LUTs), which are stored in an on-chip EEPROM. The negative voltage can be an external power supply or an internal negative charge pump (refer to Section 3.2.4). The LSD can source up to 100mA and sink up to 60mA load with a configurable current limiting threshold.

Figure 3-4. LSD Block Diagram

MABC-11040B Rev V2

#### 3.3.1 12-bit DAC

Each LSD has a 12-bit resolution. The output range is equal to the 4\*1.22\*Rfb/Rext\_bias where Rfb is an internal 12.4kohms, Rext\_bias is an external 12.1k resistor to ground on pin.EXT\_BIAS and 1.22mV is the DAC resolution. The typical output range is 0V to –5V with no resistive load.

For any input DAC word D<sub>in</sub> in decimal, the ideal output voltage with no resistive load is given by the following equation:

$$V_{OUT} = -5 \cdot \frac{D_{in}}{2^{12} - 1} (V)$$

The upper and lower voltage limits can be programmed by using two registers. For example, LSD1 the upper limit is controlled by registers 0xAA Bits[7:0](MSB) and 0xAC Bits[7:4](LSB); The bottom limit is controlled by registers 0xAE Bits[7:0](MSB) and 0xAF Bits[7:4](LSB)

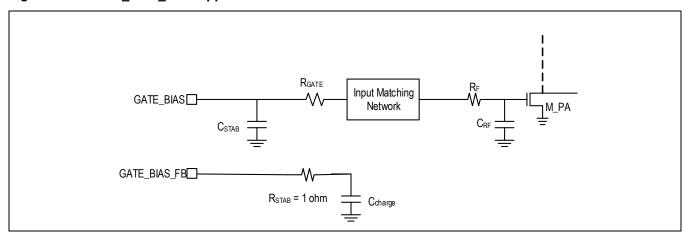

The LSD is configured as below. The capacitor  $C_{STAB}$ , is a stability capacitor, typically around 1-10  $\mu$ F. The current limiter is also set by the user. Current limit Resistor  $R_{GATE}$  should be between 5-10  $\Omega$  in value.

The specification for minimum capacitance on the **GATE\_BIAS** nodes ( $C_{STAB}$ ) is associated with the stability of the Low Side Driver. This capacitor also serves in decoupling the Low Side Driver from the RF gate. The default option is to open the integrated feedback resistor loop and use an external feedback resistor. This is done in order to allow the loop to correct the IR drop on resistor  $R_{GATF}$ .

Figure 3-5. LSD DAC OUT Application Schematic

MABC-11040B Rev V2

#### 3.3.2 12-bit ADC

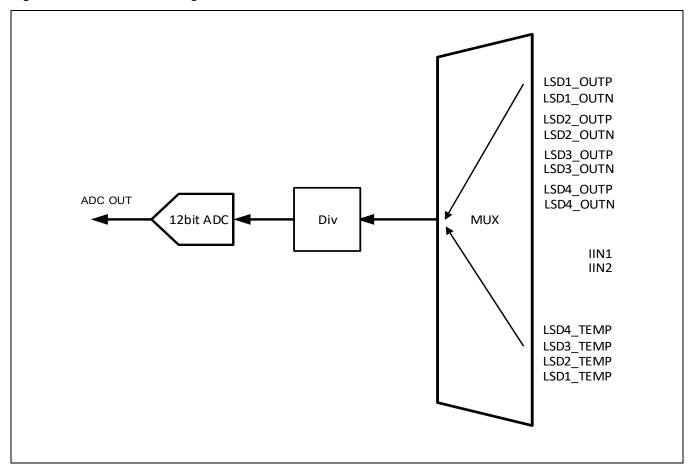

The device integrates a 12-bit SAR ADC which inputs are configurable by the I<sup>2</sup>C. The ADC allows monitoring of the internal temperature sensor, 2 external input pins.**IIN\_ADC[2:1]**, all four low side driver gate-currents and all four thermistor input pins.**TEMP\_SENSE[4:1]**. The cycling mux has a frequency at 0.75ms.

Figure 3-6. ADC Block Diagram

MABC-11040B Rev V2

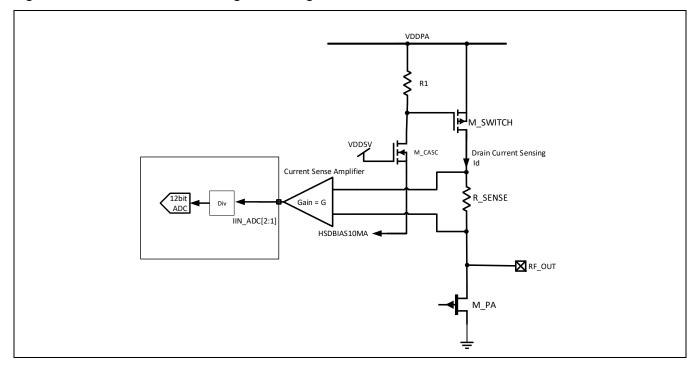

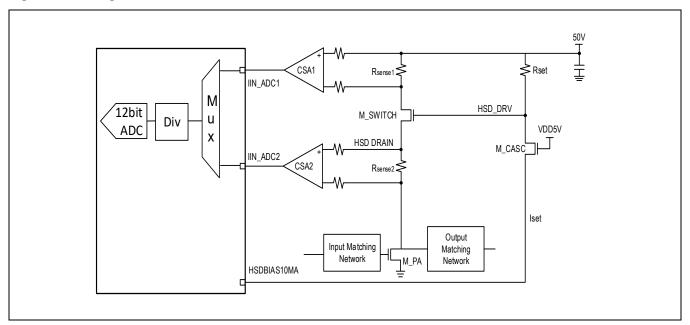

#### 3.3.2.1 LSD Drain Current Sensing Using ADC

The drain current  $I_d$  comes out from M\_Switch and fed to the 12-bit ADC. A drain current going through R\_sense and current sense amplifier to generate the 12bits ADC code. The user needs to ensure that the voltage range at the output of the current-sense amplifier is within the specifications for the ADC input range **IIN\_ADC1** and **IIN\_ADC2**. This range corresponds to the range of currents, which are expected to be sensed. The voltage range for ADC is 0 to 1V, so  $I_d*R_sense*G$  should not be larger than 1V. The resolution for 12-bit ADC is 2.44mV/LSB. The gain for CSA should be 0.5.

Figure 3-7. Drain Current Sensing Block Diagram

MABC-11040B Rev V2

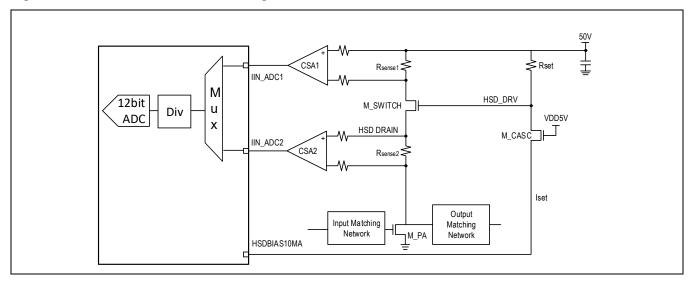

#### 3.3.2.2 LSD Drain Current Sensing Example

A source-sense resistor, R<sub>sense2</sub>, is placed on the board on the drain of M\_SWITCH. This allows the monitoring of the PA current of the output stage, M\_PA. An external current-sense amplifier is used to provide a voltage into the IC, which is fed to the ADC and converted to digital signal. A secondary resistor, R<sub>sense1</sub>, is be placed at the drain of the first two amplifier stages to provide a more accurate current reading.(See Figure 3-8)

There is flexibility in the selection of the current-sense amplifiers and the current-sense resistors. The user needs to ensure that the voltage range at the output of the current-sense amplifier is within the specifications for the ADC input range **IIN\_ADC1** and **IIN\_ADC2**. This range corresponds to the range of currents, which are expected to be sensed.

Figure 3-8. LSD Drain Current Sensing Schematic

# Power Management Bias Controller/Sequencer Supply :-6V, +5V

MABC-11040B Rev V2

#### **Example of LSD Current-Sense Resistors & Current-Sense Amplifiers**

In the table Table 3-1, an example is given that includes a  $0.1\Omega$  sense resistor with a maximum drain current of 16 A, and a minimum drain current of 1A. Then the input range of current sense amplifier is Id \* R<sub>sense</sub> from 0.1V to 1.6V. And the gain required from current sense amplifier should be 0.5. The ADC voltage range is from 0V to 1V. As ADC is 12-bit, the voltage resolution is 2.44mV/LSB.

Table 3-1. Example Calculations for HSD Current-Sense Resistors and Current-Sense Amplifiers

| Parameter                             | Variable               | Equation                                        | Value | Unit |

|---------------------------------------|------------------------|-------------------------------------------------|-------|------|

| Id <sub>MAX</sub>                     | Id <sub>MAX</sub>      |                                                 | 16.00 | Α    |

| Id <sub>MIN</sub>                     | Id <sub>MIN</sub>      |                                                 | 1.00  | Α    |

| Resistor                              | R <sub>sense</sub>     |                                                 | 0.10  | Ω    |

| CSA Input voltage for minimum current | V <sub>MIN,CSA</sub>   | Id <sub>MIN</sub> *R <sub>sense</sub>           | 0.10  | V    |

| CSA Input voltage for maximum current | V <sub>MAX,CSA</sub>   | Id <sub>MAX</sub> *R <sub>sense</sub>           | 1.60  | V    |

| CSA input voltage range               | V <sub>range,CSA</sub> | V <sub>MAX,CSA</sub> -V <sub>MIN,CSA</sub>      | 1.50  | V    |

| Gain required from CSA                | Gain <sub>CSA</sub>    | V <sub>range,ADC</sub> / V <sub>range,CSA</sub> | 0.500 | V/V  |

| ADC minimum voltage                   | $V_{MIN,ADC}$          |                                                 | 0     | V    |

| ADC maximum voltage                   | V <sub>MAX,ADC</sub>   |                                                 | 1.0   | V    |

| ADC input voltage range               | V <sub>range,ADC</sub> | V <sub>MAX,ADC</sub> - V <sub>MIN,ADC</sub>     | 1.0   | V    |

| 12-bit ADC - voltage resolution       | V <sub>res</sub>       | (V <sub>range,ADC</sub> / 2^12)*1000            | 2.44  | mV   |

| Recommend ADC minimum voltage         | V <sub>MIN,ADC_r</sub> |                                                 | 0.125 | V    |

| Recommend ADC maximum voltage         | V <sub>MAX,ADC_r</sub> |                                                 | 0.875 | V    |

MABC-11040B Rev V2

#### 3.3.2.3 LSD Gate current sensing Using ADC

The gate current is sensed by integrated current sensors and fed to the 12-bit ADC via the multiplexer. A current reading is provided to the system in the range of –60 to 100 mA.

There are two currents stored for each measurement: the currents in the PMOS and the currents in the NMOS. The output current is the current in the PMOS minus the current in the NMOS. There are four channels of the LSD gate drive currents that are measured. The currents, which are 12 bits, are stored in two registers where the 8 most significant bits are measured in one register, and the four least significant bits are stored in another register.

For example, the 12 bits for the LSD1 PMOS are stored in the 2 registers named CHNL1\_MSB and CHNL1\_LSB. The 12 bits for the LSD1 NMOS are stored in the 2 registers named CHNL5\_MSB and CHNL5\_LSB. The total current sent to the LSD1 gate is the difference between the current stored in the 12-bit PMOS registers (I<sub>PMOS</sub>) and the current stored in the 12-bit NMOS registers (I<sub>NMOS</sub>).

The accurate current calculation takes into account an adjustment for the internal DAC current, the formula to calculate  $I_{load}$  is shown in Figure 3-9.

Figure 3-9. Formula for Calculating Gate Currents

$$||_{PMOS} = \begin{cases} \frac{ADC\ Code - 403}{3.2\ x\ 10} & , ADC\ Code \geq 706 \\ \frac{ADC\ Code - 447}{3.2\ x\ 8.55} & , ADC\ Code < 706 \end{cases}$$

$$||_{NMOS} = \begin{cases} \frac{ADC\ Code - 420}{3.2\ x\ 10} & , ADC\ Code \geq 825 \\ \frac{ADC\ Code - 450}{3.2\ x\ 9.26} & , ADC\ Code < 825 \end{cases}$$

$$||_{DAC} = \frac{ADC\ Code}{4095\ x\ 0.4\ mA}$$

MABC-11040B Rev V2

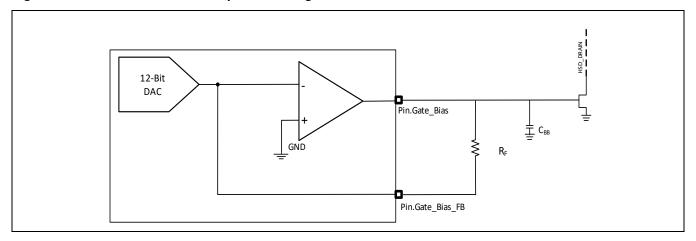

#### 3.3.3 Gate Bias Close Loop

In order to have the gate voltage constant, the DAC current  $I_{DAC}(0-400\text{mA})$  provided to the LSD is generated on an external feedback resistor  $R_F$ . Pin.**Gate\_Bias** is connected to an internal amplifier output and provides the negative voltage directly to the gate of the GaN device, while pin **Gate\_Bias\_FB** is used to connect an external feedback resistor  $R_F$  to the negative input of the amplifier.The capacitor  $C_{BB}$  connected to node **GATE\_BIAS** according to the DAC input control. The equation for voltage at pin.**GATE\_BIAS** is  $V_{GB} = -I_{DAC}^*$   $R_F$ . The typical  $R_F$  resistor value is 12.5k  $\pm$  1% ohms to get the full range of  $V_{GB}(0-5V)$ .

Figure 3-10. Gate Bias Close Loop Circuit diagran

MABC-11040B Rev V2

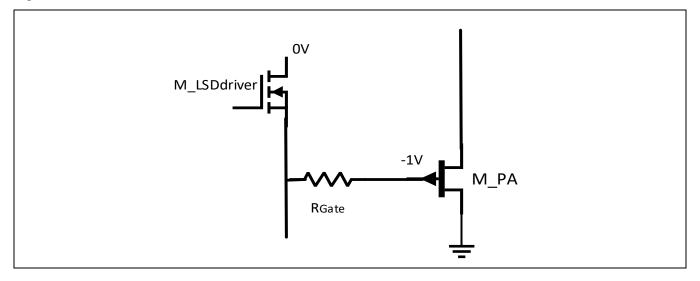

#### 3.3.4 LSD Headroom

Resistor  $R_{GATE}$  should be between 5-10  $\Omega$  in value.  $R_{GATE}$  should be designed to allow for some gate voltage headroom (Figure 3-11).

- Example 1: With 100mA current and  $4.99\Omega$  R<sub>gate</sub>, the voltage on gate resistor is 0.499V. As V<sub>gate</sub> is 1V. There will be 0.501V on non-gate side of R<sub>gate</sub>. With 0.4V max LSD headroom. The margin for headroom is 0.101V.

- Example 2: With 100mA current and  $5.6\Omega$  R<sub>gate</sub>, the voltage on gate resistor is 0.56V. As V<sub>gate</sub> is 1V. There will be 0.44V on non-gate side of R<sub>gate</sub>. With 0.4V max LSD headroom. The margin for headroom is 0.04V.

Figure 3-11. LSD Headroom with 100 mA Sourced

MABC-11040B Rev V2

### 3.4 High Side Driver

**EN\_HSD** is used to enable to high side driver. There is an internal pull-down for pin.**EN\_HSD**, so that the high side driver is disabled during start-up.

The HSD provides the control for an external high voltage Pass Gate Power FET (M\_SWITCH), typically used to connect the high voltage supply to the Power Amplifier stages. In addition to the pass gate, the MABC-11040 also requires an off chip resistor and FET M\_CASC to protect it from the high drain voltage. To turn on the external pass gate FET, the HSD turns on a programmable current source  $I_{SET}$  at **HSDBIAS10MA**, which pulls a current through  $R_{SET}$  (see Figure 3-12), such that the **HSD\_DRV** voltage is dropped by  $I_{SET}*R_{SET}$ . For example, if  $I_{SET}$  is 10mA and  $R_{SET}$  is 1k ohms leading to a voltage drop across  $R_{SET}$  of 10 V to turn on the pass gate FET(M\_SWITCH). With the 10V drop across  $R_{SET}$  the voltage at the **HSD\_DRV** location becomes 40V (a 10 V drop from 50V). Note that the resistor selection /required voltage drop is application specific.

When pin.**EN\_HSD** is pulled high, a 10 mA current will be drawn from pin.**HSDBIAS10MA** and will turn on the M\_CASC after t<sub>SWON</sub> (Page 00h, Address 80h[7:4]). After the M\_CASC is on, LSD will then provide the voltages from the internal LUT, based on the multiple temperature inputs. Setting the pin.**EN\_HSD** down will turn the GaN device off. After a delay of t<sub>SWOFF</sub> (Page 00h, Address 80h[3:0]), the M2 will turn off.

Figure 3-12. High Side Driver Schematic

MABC-11040B Rev V2

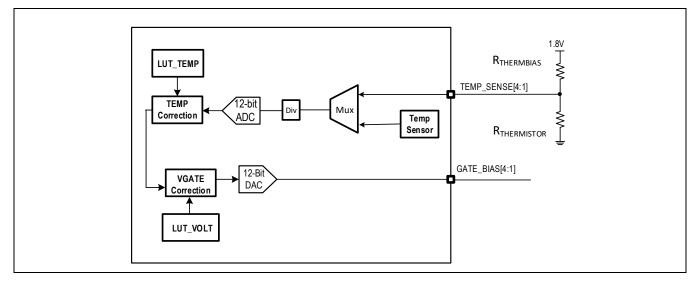

### 3.5 Look up Table

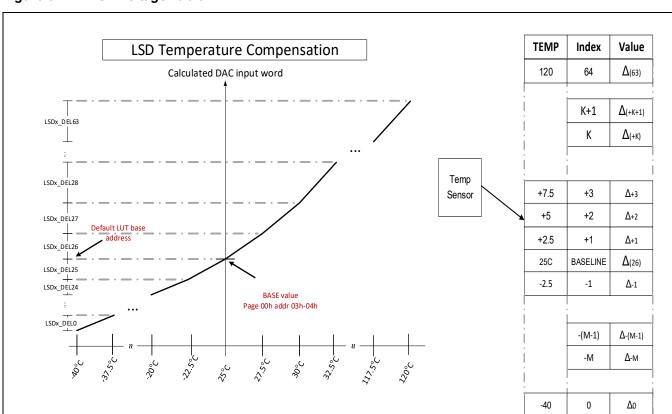

The current going to the power amplifier has to be carefully sustain over temperature. For this compensation, the MABC-11040 features two Look Up Tables that compensates for nonlinearities in the external thermistor used and the gate current going to the Power Amplifier. The LSD\_DAC\_OUT temperature compensation using an external thermistor will be done in two steps as follows:

- Temperature LUT, reg.LUT\_TEMP: Compensates for the external thermistor or internal temperature sensor nonlinearities.

- 2. Gate Bias LUT, reg.LUT\_VOLT: Provides a current vs. temperature profile to the power amplifier, user defined.

Figure 3-13 shows the temperature compensation circuitry using an external thermistor.

Figure 3-13. LSD\_DAC\_OUT Temperature Compensation using an external thermistor

MABC-11040B Rev V2

### 3.5.1 Look Up Table for Temperature

The temperature linearizion uses the 256 words stored in the TEMP LUT (Register page 0x80h and 0x81h). For example, given the temperature range from –40°C to 120°C with 256 steps, the step size is 0.625°C. When using an external thermistor, the ADC codes must be re-defined over temperature by LSDx\_TEMP output voltage and mapped to the LUT\_TEMP having a resolution up to 0.625°C/ADC code. The temperature readings are taken either from an integrated temperature sensor or an external thermistor placed close to the power amplifier device(s).

Two different methods are specified for temperature sensing and readout. In both cases, a 12-bit temperature reading is obtained based on a total range of 160°C, -40°C to +120°C, 0.04°C steps. Note that, in the case of the external thermistor, the temperature calibration is done using 8 bits, i.e. every 256 steps, while a linear interpolation is performed between the 1/256 steps. The MABC-11040 will monitor the four pins.**LSD\_TEMP[4:1]** and continue to update each temperature reading from the temperature calibration registers for each LSD temperature sensor based on the voltage reading.

Note: If no thermistor is used, pins.**TEMP\_SENSE[4:1]** should be tied to **VIO**. This would prevent over temperature faults from occurring.

The temperature BASELINE at which extracted LUT\_TEMP is defined in LUT\_TEMP\_BS\_MSB and LUT\_TEMP\_BS\_LSB as 12bit data from -40C to 120C. LSDx\_TS\_BS\_MSB/LSB give the ADC reading of LSDx\_TEMP pin as the BASE value. LUT\_TEMP\_BS\_ADDRESS give the address in the LUT\_TEMP that BASE is stored. The overall transfer function is stored in the LUT as a set of unsigned 12-bit increments from the base value, that is, each LUT location stores the value of the decrement  $\Delta 1$  per 0.625C.

### 3.5.2 Look Up Table for Voltage

The gate voltage temperature calibration uses only the 6 most significant bits of the 12-bit temperature reading. which is typically defined for a temperature range from -40°C to 120°C, therefore the step is typically 2.5C and a total of 64 steps within the voltage look-up table. This range can be adjusted, according to the users' needs, and the MABC-11040 is functional and operational within the required range of the use case. Between each 2.5C step within the VOLT LUT, a linear interpolation is applied using the remaining 6 bits of the temperature reading. The linear interpolation step is 0.04°C.

#### 3.5.2.1 Offset voltage correction

The calibration procedure described above is using look-up values from VOLT LUT, which have been measured over temperature and are assumed to be the same for all devices of the same type. When a new device is used in the system, these look-up values need updating. Also each GaN device needs to be calibrated for  $V_{th}$  offset. This is one more look-up value, unique for each GaN device, which is added to the gate voltage correction values of its family.

#### 3.5.2.2 Register Settings to use LUT Voltage

- Enable look up tables by writing Page0x02h, Register0x08h Bit[2] with Value 1.

- Load the desired settings to each page and register.

- Terminate NVM control and reflect the changes by writing Page0x02h, Register0x08h Bit[2] with Value 0.

MABC-11040B Rev V2

#### 3.5.2.3 LUT Voltage Calculation

In order to minimize the storage requirements, MABC-11040 LUTs are indexed in 2.5°C increments. Also, the stored values are only the increments, or first derivatives (Δs) of the modeled transfer function. The internal ALU reconstructs the original transfer function by integrating the coefficients stored in the LUTs. The errors due to the coarseness of the temperature quantization are significantly reduced through the use of linear interpolation, which is also implemented in the ALU. ALU output will be limited to{000, FFF}. Consider the example shown in Figure 3-14. The target output vs temperature is shown in the top graph. VDACx is a smooth, monotonic function with, ideally, infinite precision. The LUT stores only the increments, or the rise, within each 2.5°C interval.

In order to recreate the original transfer function, the series of increments must be summed together and added to the constant BASE value. This process must also be referenced to the common temperature point. This reference temperature is called BASELINE and is defined in TS\_PTAT\_BS\_TEMP<11:0> and LUT\_TEMP\_BS\_TEMP<11:0> depends on internal (TS\_PTAT, TS\_VBG) or external temperature sensor (TS1/2/3/4)used.

MABC-11040 has VOLT LUTs for each LSD driver defined in page 90h/91h/92h/93h. The VOLT LUTs start from the BASE address and extend to 64 steps. Each step of data shows the differential DAC code between previous temperature and current temperature. The base voltage value in hexadecimal is calculated by: Dec to Hex[ Gate Voltage/1.22mV]; The base temp value in hexadecimal is calculated by: Dec to Hex[ (Temp(°C)+40°C) /0.625°C]. For more details, please contact MACOM team.

Figure 3-14. LUT Voltage Table

MABC-11040B Rev V2

### 3.6 Addition features

### 3.6.1 EEPROM Programming Procedure

The following are the instructions to program the EEPROM.

- 1. Enable Look up table: write Page 0x02h Register 0x08h with value 0x04h.

- 2. Clear the trim and the test bits: write Page 0x00h Register 0x7Fh with value 0x00h; write Page 0x01h Register 0x00h with value 0x00h; write Page 0x01h Register 0x01h with value 0x00h; write Page 0x01h Register 0x02h with value 0x00h;

- 3. Write password to enable each page: write Page 0x00h Register 0xFAh with value 0x20h; write Page 0x00h Register 0xFCh with value 0x07h; write Page 0x00h Register 0xFCh with value 0x07h; write Page 0x00h Register 0xFDh with value 0x04h;

- 4. Enable look up table: write Page 0x02h Register 08h with value 0x04h.

- 5. Write the desired setting to each page and registers.

- 6. To permanently program in the settings: write Page 0x02h Register 0x03h with value 0xFFh; write Page 0x02h Register 0x06h with value 0x01h; write Page 0x02h Register 0x08h with value 0x00h

### 3.6.2 GPIO pins

There are four general purpose CMOS output pins, **GPIO[3:0]**, available to the user. They can be used to adjust the attenuation setting of a Digital Step Attenuator (DSA), which can be used to control the gain in a power amplifier lineup or they can be used in order to set the phase of a digital phase shifter. Since the step attenuator is set during initial calibration, the GPIO signal can be treated as low frequency, such as 1 KHz.

The status of the GPIO pins will be controlled by the internal GPIO\_CTRL0 register.

The logic level of these pins is determined by pin **VIO**. Depending on the voltage provided at pin **VIO**, the logic level can be between 1.8 and 3.3V.

### 3.6.3 Internal Temperature Sensor

There is an internal temperature sensor available. There is a set alarm threshold value ("TS\_PTAT\_OT\_S\_THD") and reset alarm threshold value ("TS\_PTAT\_OT\_R\_THD") based on the internal temperature sensor. If an alarm does assert, the faults can be can also be masked (disabled) using "ALARM MASK2" (Page 02h, Address A5h).

Set bit [4] to 1 to mask "TS\_PTAT\_Alarm".

### 3.6.4 External Temperature Sensors

External temperature sensor pins (**TEMP\_SENSE[4:1]**) are available for users to place thermistors to monitor external temperature. The threshold set value ("TEMP[4:1]\_OT\_THD") and reset value ("TEMP[4:1]\_OT\_R\_THD") must be programmed into the chip based on the thermistor characteristics. If the temperature exceeds the threshold temperature, the over-temperature alarm asserts (sets). If the temperature falls below the reset tlf an alarm does assert, the faults can be can also be masked (disabled) using "ALARM\_MASK2" (Page 02h, Address A5h).:

# Power Management Bias Controller/Sequencer Supply :-6V, +5V

MABC-11040B Rev V2

- Set bit [3] to 1 to mask "LSD4\_TS\_Alarm".

- Set bit [2] to 1 to mask "LSD3\_TS\_Alarm".

- Set bit [1] to 1 to mask "LSD2\_TS\_Alarm".

Set bit [0] to 1 to mask "LSD1\_TS\_Alarm".emperature threshold, the alarm de-asserts (resets).

## Power Management Bias Controller/Sequencer Supply :-6V, +5V

MABC-11040B Rev V2

#### 3.6.5 Fail Alert

A fail alert mechanism provides an output to alert the system that there are certain operating conditions found to be outside the defined acceptable range. There are two types of alarms, the real-time and latched alarm. The difference between the alarms is a reset is required to clear the latch alarm. The real time alarm outputs are used so that faults are captured as they occur. Latched alarms assert when an alarm event occurs and must be reset to check if the alarm event is still occurring. Below is a summary of the alarm types on the MABC-11040

The **FAIL** pin output is active low to indicate an alarm condition. This alert can be used by the system in order to turn off the power amplifier and protect it from being damaged. The polarity of the alarm bit can be changed by using the "Fail\_flip\_polar" register bit (Page 00h, Address A2h[4]). If this bit is change to "1", the Fail alarm output will become active high to indicate an alarm condition.

The **FAIL** pin is open drain, and is internally pulled down so that the FAIL pin is low at turn-on. The "Fail\_out\_cmos" register bit (**Page 00h**, **Address A2h[5**]) can be used to convert this pin from open-drain, "0", to a CMOS output < "1". When the **FAIL** pin is open-drain, a 4.7k external pull-up resistor to VIO is required but a CMOS output does not require an external pull up resistor.

The "FAIL\_PIN\_MODE" register bit (Page 00h, Address A2h[0]) controls the behavior of the **FAIL** pin between. Trigger lock and interrupt mode. The duration that the **FAIL** pin is indicates an alarm condition is defined by "Fail\_interrupt\_duration" (**Page 00h**, **Register A2h[3:1]**) and can be set between 12 and 84 clock cycles.

"alarm\_clear" is used to clear all the latched alarms in the following registers, "TEMP\_ALARM", "ALARM0", and "ALARM1", by setting this bit "1" and then back to "0

- "ALARM\_MASK0" is used to mask (disable) all the alarm statuses in the "ALARM0" register (Page 00h, reg.A3h).

- "ALARM\_MASK1" is used to mask (disable) all the alarm statuses in the "ALARM1" register(Page 00h, reg.A4h).

- "ALARM\_MASK2" is used to mask (disable) all the alarm statuses in the "TEMP\_ALARM" register(Page 00h, reg.A5h).

- "ALARM\_MASK3" is used to mask (disable) all the alarm statuses in the "TEMP\_ALARM" register(Page 00h, reg.A6h).

The logic block diagram of the fail circuitry can be found in Figure 3-16.

#### 3.6.5.1 Drain Current Alarms

The drain current limit is predefined. If the drain current seen at **IIN\_ADC1** or **IIN\_ADC2** exceeds the current limit, the alarm bit will assert.

- "iin1 cl lt", Page 02h, Address 3Fh[7], is associated to the **IIN ADC1** pin.

- "iin2 cl It", Page 02h, Address 3Fh[6], is associated to the IIN\_ADC2 pin.

#### 3.6.5.2 Gate Current Alarms

The gate current limit is predefined. If the gate current seen at the GATE\_BIAS pin exceeds the predefined limit, the alarm bit will assert.

- "Isd1 cl rt", Page 02h, Address 40h[6], is associated to the GATE\_BIAS1 pin.

- "Isd2\_cl\_rt", Page 02h, Address 40h[5], is associated to the GATE\_BIAS2 pin.

33

MACOM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice.

# Power Management Bias Controller/Sequencer Supply :-6V, +5V

MABC-11040B Rev V2

- "Isd3 cl rt", Page 02h, Address 40h[4], is associated to the GATE\_BIAS3 pin.

- "Isd4 cl rt", Page 02h, Address 40h[3], is associated to the GATE\_BIAS4 pin.

#### 3.6.5.2.1 Voltage Alarms

There are four under-voltage alarms addressing all four voltage supply pins, **V\_NEG**, **VDD5A**, **VDD1P8VA**, and **VDD1P8VD**. If the predefined threshold is less negative for **V\_NEG** or less positive for the other three supplies, the resulting fault condition will disable the **GATE\_BIAS** and HSD. There is a predefined amount of hysteresis and low pass filtering to prevent false triggering of the fault condition.

**V\_NEG** is monitored by the alarm bit "neg\_uv\_rt". This alarm bit will go high, "1", when V\_NEG is less negative than the voltage threshold defined by "vneg\_rdy\_vth".

**VDD5A** is monitored by "undervoltage\_alarm\_rt". This alarm bit will go high, "1", when VDD5A is less positive than the voltage threshold defined by "UV\_alarm\_vth".

**VDD1P8VA** is monitored by the alarm bit "v1p8a\_uv\_rt". This alarm bit will go high, "1", when VDD1P8VA is less positive than 1.44V.

**VDD1P8VD** is monitored by the alarm bit "v1p8d\_uv\_rt". The alarm bit will go high, "1", when VDD1P8VD is less positive than 1.44V.

#### 3.6.5.3 Thermal Shutdown

The thermal shutdown circuitry uses a BJT on the die. VBE on the BJT is compared with predefined voltages to sense if the temperature has reached the shutdown thresholds of 130°C, 140°C, or 150°C. If the temperature has reached the selected thermal shutdown temperature, the low side drivers (LSDs) and high side driver (HSD) will be disabled.

There is an option to disable thermal shutdown for HTOL testing. "OT\_Shutdown\_Threshold" by setting both bits in page 00h, address 93h[5:4]) = 1.

MABC-11040B Rev V2

Figure 3-15. Fail Circuitry Logic

MABC-11040B Rev V2

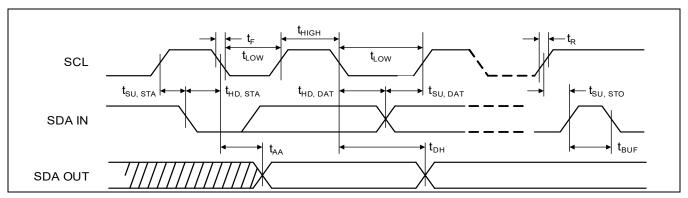

## 3.7 Digital Interface

Using the **SEL[3:0]** pin, a static I<sup>2</sup>C address can be used to identify individual MABC-11040 devices in a system so that a controller can write to or read from each device. There are three available addresses for each device (Table 3-2). There is also a broadcast address common to all devices so a controller can communicate with all devices at the same time.

Table 3-2. I<sup>2</sup>C Timing Characteristics

| Symbol   | Parameter                                                | Notes | Min | Тур | Max | Unit |

|----------|----------------------------------------------------------|-------|-----|-----|-----|------|

| fscl     | Clock Frequency, SCL                                     |       |     |     | 400 | KHz  |

| tlow     | Clock Pulse Width Low                                    |       | 160 |     |     | ns   |

| thigh    | Clock Pulse Width High                                   |       | 60  |     |     | ns   |

| tAA      | Clock Low to Data Out Valid                              |       | 0   |     | 70  | ns   |

| tHD,STA  | Start Hold Time                                          |       | 160 |     |     | ns   |

| tSU,STA  | Start Set-up Time                                        |       | 160 |     |     | ns   |

| tHD,DAT  | Data In Hold Time                                        |       | 0   |     |     | ns   |

| RPULL-UP | Outputs (SDA,SCL) internal pull-up resistor value to VIO |       |     | 250 |     | ΚΩ   |

| tSU,STO  | Stop Set-up Time                                         |       | 160 |     |     | ns   |

| tDH      | Data Out Hold Time                                       |       | 5   |     |     | ns   |

Figure 3-16. I<sup>2</sup>C Timing Characteristics

# Power Management Bias Controller/Sequencer Supply :-6V, +5V

Table 3-3. I<sup>2</sup>C Address Table

| I2C Addr | ess (Hex) |      | Input | Setting |       | I2C Addr | ess (Hex) |      | Input S | Setting |       |

|----------|-----------|------|-------|---------|-------|----------|-----------|------|---------|---------|-------|

| MSB      | LSB       | SEL3 | SEL2  | SEL1    | SEL0  | MSB      | LSB       | SEL3 | SEL2    | SEL1    | SEL0  |

| 0        | 0         |      | RESE  | RVED    |       | 1        | D         | GND  | VIO     | VDD5V   | VIO   |

| 0        | 1         | GND  | GND   | GND     | VIO   | 1        | Е         |      |         |         | N/C   |

| 0        | 2         |      |       |         | N/C   | 1        | F         |      |         |         | VDD5V |

| 0        | 3         |      |       |         | VDD5V | 2        | 0         |      | N/C     | GND     | GND   |

| 0        | 4         |      |       | VIO     | GND   | 2        | 1         |      |         |         | VIO   |

| 0        | 5         |      |       |         | VIO   | 2        | 2         |      |         |         | N/C   |

| 0        | 6         |      |       |         | N/C   | 2        | 3         |      |         |         | VDD5V |

| 0        | 7         |      |       |         | VDD5V | 2        | 4         |      |         | VIO     | GND   |

| 0        | 8         |      |       | N/C     | GND   | 2        | 5         |      |         |         | VIO   |

| 0        | 9         |      |       |         | VIO   | 2        | 6         |      |         |         | N/C   |

| 0        | Α         |      |       |         | N/C   | 2        | 7         |      |         |         | VDD5V |

| 0        | В         |      |       |         | VDD5V | 2        | 8         |      |         | N/C     | GND   |

| 0        | С         |      |       | VDD5V   | GND   | 2        | 9         |      |         |         | VIO   |

| 0        | D         |      |       |         | VIO   | 2        | Α         |      |         |         | N/C   |

| 0        | Е         |      |       |         | N/C   | 2        | В         |      |         |         | VDD5V |

| 0        | F         |      |       |         | VDD5V | 2        | С         |      |         | VDD5V   | GND   |

| 1        | 0         |      | VIO   | GND     | GND   | 2        | D         |      |         |         | VIO   |

| 1        | 1         |      |       |         | VIO   | 2        | Е         |      |         |         | N/C   |

| 1        | 2         |      |       |         | N/C   | 2        | F         |      |         |         | VDD5V |

| 1        | 3         |      |       |         | VDD5V | 3        | 0         |      | VDD5V   | GND     | GND   |

| 1        | 4         |      |       | VIO     | GND   | 3        | 1         |      |         |         | VIO   |

| 1        | 5         |      |       |         | VIO   | 3        | 2         |      |         |         | N/C   |

| 1        | 6         |      |       |         | N/C   | 3        | 3         |      |         |         | VDD5V |

| 1        | 7         |      |       |         | VDD5V | 3        | 4         |      |         | VIO     | GND   |

| 1        | 8         |      |       | N/C     | GND   | 3        | 5         |      |         |         | VIO   |

| 1        | 9         |      |       |         | VIO   | 3        | 6         |      |         |         | N/C   |

| 1        | А         |      |       |         | N/C   | 3        | 7         |      |         |         | VDD5V |

| 1        | В         |      |       |         | VDD5V | 3        | 8         |      |         | N/C     | GND   |

| 1        | С         |      |       | VDD5V   | GND   | 3        | 9         |      |         |         | VIO   |

# Power Management Bias Controller/Sequencer Supply :-6V, +5V

Table 3-3. I<sup>2</sup>C Address Table

| I2C Addr | ess (Hex) |      | Input S | Setting |       | I2C Addr | ess (Hex) |      | Input \$ | Setting |       |

|----------|-----------|------|---------|---------|-------|----------|-----------|------|----------|---------|-------|

| MSB      | LSB       | SEL3 | SEL2    | SEL1    | SEL0  | MSB      | LSB       | SEL3 | SEL2     | SEL1    | SEL0  |

| 3        | Α         | GND  | VDD5V   | N/C     | N/C   | 5        | 7         | VIO  | VIO      | VIO     | VDD5V |

| 3        | В         |      |         |         | VDD5V | 5        | 8         |      |          | N/C     | GND   |

| 3        | С         |      |         | VDD5V   | GND   | 5        | 9         |      |          |         | VIO   |

| 3        | D         |      |         |         | VIO   | 5        | Α         |      |          |         | N/C   |

| 3        | Е         |      |         |         | N/C   | 5        | В         |      |          |         | VDD5V |

| 3        | F         |      |         |         | VDD5V | 5        | С         |      |          | VDD5V   | GND   |

| 4        | 0         | VIO  | GND     | GND     | GND   | 5        | D         |      |          |         | VIO   |

| 4        | 1         |      |         |         | VIO   | 5        | E         |      |          |         | N/C   |

| 4        | 2         |      |         |         | N/C   | 5        | F         |      |          |         | VDD5V |

| 4        | 3         |      |         |         | VDD5V | 6        | 0         |      | N/C      | GND     | GND   |

| 4        | 4         |      |         | VIO     | GND   | 6        | 1         |      |          |         | VIO   |

| 4        | 5         |      |         |         | VIO   | 6        | 2         |      |          |         | N/C   |

| 4        | 6         |      |         |         | N/C   | 6        | 3         |      |          |         | VDD5V |

| 4        | 7         |      |         |         | VDD5V | 6        | 4         |      |          | VIO     | GND   |

| 4        | 8         |      |         | N/C     | GND   | 6        | 5         |      |          |         | VIO   |

| 4        | 9         |      |         |         | VIO   | 6        | 6         |      |          |         | N/C   |

| 4        | Α         |      |         |         | N/C   | 6        | 7         |      |          |         | VDD5V |

| 4        | В         |      |         |         | VDD5V | 6        | 8         |      |          | N/C     | GND   |

| 4        | С         |      |         | VDD5V   | GND   | 6        | 9         |      |          |         | VIO   |

| 4        | D         |      |         |         | VIO   | 6        | А         |      |          |         | N/C   |

| 4        | E         |      |         |         | N/C   | 6        | В         |      |          |         | VDD5V |

| 4        | F         |      |         |         | VDD5V | 6        | С         |      |          | VDD5V   | GND   |

| 5        | 0         |      | VIO     | GND     | GND   | 6        | D         |      |          |         | VIO   |

| 5        | 1         |      |         |         | VIO   | 6        | Е         |      |          |         | N/C   |

| 5        | 2         |      |         |         | N/C   | 6        | F         |      |          |         | VDD5V |

| 5        | 3         |      |         |         | VDD5V | 7        | 0         |      | VDD5V    | GND     | GND   |

| 5        | 4         |      |         | VIO     | GND   | 7        | 1         |      |          |         | VIO   |

| 5        | 5         |      |         |         | VIO   | 7        | 2         |      |          |         | N/C   |

| 5        | 6         |      |         |         | N/C   | 7        | 3         |      |          |         | VDD5V |

# Power Management Bias Controller/Sequencer Supply :-6V, +5V

MABC-11040B Rev V2

#### Table 3-3. I<sup>2</sup>C Address Table

| I2C Addr | ess (Hex) |      | Input S | Setting |       | I2C Addr | ess (Hex) | Input Setting |       |       |       |

|----------|-----------|------|---------|---------|-------|----------|-----------|---------------|-------|-------|-------|

| MSB      | LSB       | SEL3 | SEL2    | SEL1    | SEL0  | MSB      | LSB       | SEL3          | SEL2  | SEL1  | SEL0  |

| 7        | 4         | VIO  | VDD5V   | VIO     | GND   | 7        | С         | VIO           | VDD5V | VDD5V | GND   |

| 7        | 5         |      |         |         | VIO   | 7        | D         |               |       |       | VIO   |

| 7        | 6         |      |         |         | N/C   | 7        | Е         |               |       |       | N/C   |

| 7        | 7         |      |         |         | VDD5V | 7        | F         |               |       |       | VDD5V |

### Power Management Bias Controller/Sequencer Supply :-6V, +5V

MABC-11040B Rev V2

### 4.0 Control Registers Map and Descriptions

### 4.1 Register Map General Overview

The MABC-11040 has a lot of functions that can be controlled via registers, the register map is divided with several register pages to help distribute these functions as described in the following

#### Register Map Description Summary

| Function                      |     | Comment                                |

|-------------------------------|-----|----------------------------------------|

| Low Side Driver               | 00h | LSD Control, DAC, ADC mux, Alarm Masks |

| EEPROM                        | 01h | EEPROM, user defined information       |

| Global                        | 02h | Global control, ADC, Alarm calibration |

| Look Up Table for Temperature | 80h | LUT Temp[0:127]                        |

|                               | 81h | LUT Temp[128:255]                      |

| Look Up Table for Voltage     | 90h | LSD1 LUT Voltage[0:63]                 |

|                               | 91h | LSD2 LUT Voltage[0:63]                 |

|                               | 92h | LSD3 LUT Voltage[0:63]                 |

|                               | 93h | LSD4 LUT Voltage[0:63]                 |

#### NOTES:

- · After power up or software reset, the default page in 00h.

- Write the password to switch pages (refer to section3-2-1 for password)

- · Write page number to register0xFE to select page. Register 0xFEis accessible from any page.

Table 4-1 shows the register map for the MABC-11040. Should any reserved registers or bits need to be written, use with their default value listed. Registers not listed in Table 4-1 are reserved with default value of 00h.

# Power Management Bias Controller/Sequencer Supply :-6V, +5V

MABC-11040B Rev V2

#### Table 4-1. Register Summary

| Page | Addr | Register                   | Bit 7            | Bit 6            | Bit 5            | Bit 4            | Bit 3            | Bit 2            | Bit 1            | Bit 0       | Default | R/W |

|------|------|----------------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|-------------|---------|-----|

| 00h  | 00h  | CHECKSUMSEED               | 5.0.1            | 2.0              | 5.0              | -                | seed<7:0>        | 5,12             | J                | 5.0         | 55'h    |     |

|      |      |                            |                  | 1.15             | 1004.04          | 1                | seeu<7.0>        | 1001.0           |                  |             |         | R/W |

| 00h  | 03h  | LSD1_LUTV_BS_LSB           | RS               | VD               | LSD1_BY-<br>PASS | LSD1_POL         |                  | LSD1_BA          | ASE<3:0>         |             | 10'h    | R/W |

| 00h  | 04h  | LSD1_LUTV_BS_MSB           |                  |                  |                  | LSD1_BA          | SE<11:4>         |                  |                  |             | 00'h    | R/W |

| 00h  | 05h  | LSD1_LUTV_BS_ADD           |                  |                  |                  | LSD1_LUTV_       | BS_ADD<7:0>      |                  |                  |             | 17'h    | R/W |

| 00h  | 06h  | LSD2_LUTV_BS_LSB           | RS               | VD               | LSD2_BY-<br>PASS | LSD2_POL         |                  | LSD2_BA          | ASE<3:0>         |             | 10'h    | R/W |