## MagnaChip

# **MAP3201**

#### General Description

The MAP3201 is a high efficiency current mode PWM driver. It is designed for LED driver that is used as the light source of LCD panel. The controller can achieve efficiency higher than 90% for buck and boost applications.

The MAP3201 for accurate LED dimming control use external PWMI signal and set internal frequency by external resistor which is programmable.

The MAP3201 has a stable operation with wide input voltage because it can be operated as separated Vcc with input voltage It has a auto-restart recovery protection if the system occur fault signal. it can provide a good safety features.

Multiple MAP3201 have synchronized to each others or to other external clock which is generated by Sync Pin.

The MAP3201 provide a 0.4A source current and 0.8A Sink current gate driver. This can be suitable for high power application. Using BCD process, the MAP3201 has a good immunity at switching noise.

The MAP3201' application can be so easy to making lowest cost system.

The MAP3201 is available in 16-Lead SOIC package and it is offered in Halogen-free (fully RoHS compliant).

For more information, please contact local MagnaChip sales office in world-wide or visit MagnaChip's website at www.magnachip.com.

#### High current switch mode PWM LED Driver

#### **Features**

- PWM Interface LED Driver

- Current Mode Control Type

- Auto Restart Mode Protection

- **Output Over Voltage Protection**

- Programmable LED Short Current Protection

- Power Supply Vcc=12V (Max 20V)

- Programmable LED Current Set (FBP)

- Programmable Boost switch current limit

- Synchronization to peer-to-peer or external clock

- п Fully RoHS Compliant

#### Application

RGB and White LED Backlighting applications General LED lighting applications

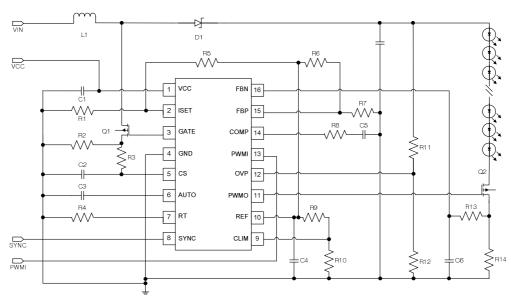

#### **Typical Application Circuit**

|   | MAP3201 – High current switch mode PWM LED Driver |

|---|---------------------------------------------------|

| _ | node l                                            |

|   | MA<br>M                                           |

|   | Ē                                                 |

|   | DD                                                |

|   | rive                                              |

|   |                                                   |

## **Ordering Information**

| Part Number | Part Marking | Junction<br>Temperature Range | Packado       |              |

|-------------|--------------|-------------------------------|---------------|--------------|

| MAP3201SIH  | SELC2010M    | -40 ℃ to +125 ℃               | 16 Leads SOIC | Halogen Free |

#### Absolute Maximum Ratings

| PARAMETER                                            | VALUE     | UNIT |

|------------------------------------------------------|-----------|------|

| VCC                                                  | -0.3 ~ 20 | V    |

| GATE, PWMO                                           | -0.3 ~ 20 | V    |

| AUTO,CS, ISET,RT,SYNC,CLIM,REF,OVP,PWMI,COMP,FBP,FBN | -0.3 ~ 5  | V    |

| Operating Junction Temperature Range                 | -40 ~ 125 | C    |

| Storage Temperature Range                            | -65 ~ 150 | C    |

| Lead temperature(soldering, 10sec )                  | 260       | °C   |

| Thermal Resistance (θJA)                             | 105       | °C/W |

| SYMBOL        | PARAMETER                              | TEST CONDITION                                 | MIN  | ТҮР  | МАХ  | UNIT |

|---------------|----------------------------------------|------------------------------------------------|------|------|------|------|

| SUPPLY        |                                        |                                                |      |      |      |      |

| Vcc,op        | Input voltage range                    | Ta=-40℃ ~ 85℃                                  | 8.5  |      | 18   | V    |

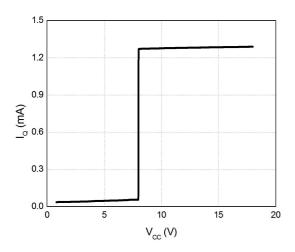

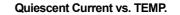

| la            | Operation quiescent current            | PWMI =0V                                       | _    | 1.2  | 2    | mA   |

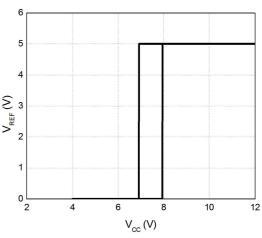

| Vuvlo_r       | Under-voltage lockout threshold        | VCC rising                                     | 7.5  | 8    | 8.5  | V    |

| VUVLO_F       | Under-voltage lockout hysteresis       | VCC falling                                    | -    | 1    | -    | V    |

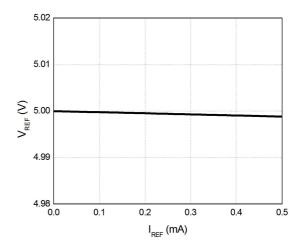

| REFERENCE     |                                        |                                                |      | •    | •    |      |

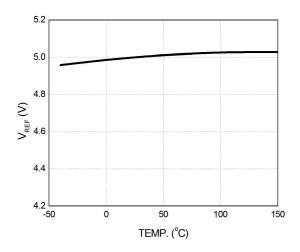

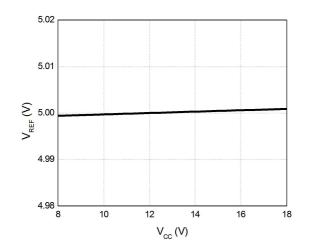

| \/            |                                        | Ta=-40 ℃ ~ 85 ℃                                | 4.90 | 5.00 | 5.10 | V    |

| Vref          | Reference pin voltage                  | Ta=25℃                                         | 4.95 | 5.00 | 5.05 | V    |

| Vrefli        | Line regulation                        | IREF=0uA, VPWMI=0V,<br>CREF=0.1uF              | -    | -    | 0.02 | %N   |

| Vreflo        | Load regulation                        | IREF=0~500uA, VREF=0V,<br>CREF=0.1uF           | -    | -    | 1    | %/mA |

| GATE          |                                        |                                                |      |      |      |      |

| Isour         | Gate short circuit current             | VGATE=0, VCC =12V                              | 0.4  | -    | -    | А    |

| Isink         | Gate sink current                      | VGATE=12V, VCC =12V                            | 0.8  | -    | -    | A    |

| Trise         | GATE output rise time                  | CGATE=1nF, Vcc=12V                             | -    | 50   | 85   | ns   |

| TFALL         | GATE output fall time                  | CGATE=1nF, Vcc =12V                            | -    | 25   | 45   | ns   |

| Current Sens  | Se                                     |                                                |      |      |      |      |

| TBLANK        | Leading Edge Blanking                  |                                                | 100  | -    | 375  | ns   |

| TDELAY1       | Delay to output of CS comparator(2)    | Vcomp=5V, Vclim=5V,<br>Vcs=0V to 600mV step    |      | -    | 180  | ns   |

| TDELAY2       | Delay to output of CLIMT comparator(2) | VCOMP =5V, CLIM=300mV,<br>VCS=0V to 400mV step | -    | -    | 180  | ns   |

| Internal Tran | sconductance Opamp                     |                                                |      |      |      |      |

| Av            | Open loop DC Gain(2)                   | -                                              | -    | 50   | -    | dB   |

| Vсм           | Input common-mode range                |                                                | -0.3 | -    | 3    | V    |

| Vo            | Output Voltage range                   | VCC=12V                                        | 0.6  | -    | 2.75 | V    |

| gm            | Transconductance(2)                    |                                                | 400  | 670  | 1000 | uA/V |

| Voffset       | Input offset voltage                   |                                                | -5   | -    | 5    | mV   |

| BIAS          | Input Bias current                     |                                                | -    | 0.5  | 1    | nA   |

|                         | I Characteristics (Contin                            |                                    |      |     |               |      |

|-------------------------|------------------------------------------------------|------------------------------------|------|-----|---------------|------|

| Vcc=12V, Vpwn<br>SYMBOL | и=5V, CGATE=CPWMO=1nF, Ta=25 °С, unless<br>PARAMETER | otherwise specified TEST CONDITION | MIN  | ТҮР | MAX           | UNIT |

| Oscillator              | 1                                                    |                                    |      |     |               |      |

|                         |                                                      | Ta=25 ℃, RT=500kΩ                  | 95   | 100 | 105           | kHz  |

| Fosc                    | Oscillator frequency<br>( 100KHz ~ 400KHz )          | Ta=-40℃~85℃, RT=500kΩ              | 90   | 100 | 110           | kHz  |

|                         |                                                      | Ta=-40 ℃ ~ 85 ℃, RT=110kΩ          | 340  | 400 | 460           | kHz  |

| Dмах                    | Maximum duty cycle                                   |                                    | -    | 90  | -             | %    |

| Synchronizi             | ng ( External Input )                                |                                    | 1    | 1   | 1             |      |

| VIL_SYNC                | SYNC Input voltage Low level                         | -                                  |      | -   | 0.8           | V    |

| VIH_SYNC                | SYNC Input voltage high level                        | -                                  | 2.0  | -   | -             | V    |

| Tsync_min               | SYNC minimum input pulse width                       | VSYNC = 0V to 5V                   | 20   | -   | -             | ns   |

| TSYNC_MAX               | SYNC maximum input pulse width                       | VSYNC = 0V to 5V                   | -    | -   | 0.05<br>/Fosc | ns   |

| PWM Input               |                                                      |                                    |      |     |               |      |

| VPWMI(LO)               | PWMI input Low voltage                               | -                                  | -    | -   | 0.8           | V    |

| VPWMI(HI)               | PWMI input High voltage                              | -                                  | 2.0  | -   |               | V    |

| Rpwmi                   | PWMI pull-down resistance                            | VPWMI=5V                           | 50   | 100 | 150           | kΩ   |

| PWM Output              | t                                                    |                                    |      |     |               |      |

| Trise,pwmo              | PWM Output rise time                                 | 1nF capacitance at PWMO            | -    | -   | 300           | ns   |

| Tfall,pwmo              | PWM Output fall time                                 | 1nF capacitance at PWMO            |      | -   | 200           | ns   |

| Auto Restart            | Protection ( AUTO )                                  |                                    | ·    |     |               |      |

| Iso,auto                | Current source at AUTO Pin                           | -                                  | 3    | 5   | 8             | uA   |

| VTH(H)                  | High threshold at AUTO Pin                           | -                                  | 2.7  | 3   | 3.3           | V    |

| VTH(L)                  | Low threshold at AUTO Pin                            | -                                  | 0.9  | 1   | 1.1           | V    |

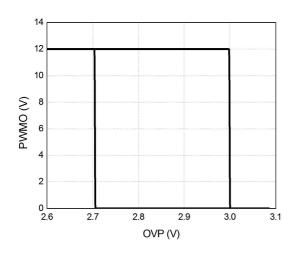

| Over Voltage            | Protection ( OVP )                                   |                                    | ·    |     |               |      |

| VOVP                    | Over voltage protection                              |                                    | 2.94 | 3.0 | 3.06          | V    |

| Vovph                   | Over voltage protection hysteresis                   | -                                  | -    | 0.3 | -             | V    |

| Tovp                    | OVP Filtering time(2)                                |                                    | -    | 200 | -             | ns   |

MagnaChip\* MagnaChip Semiconductor Ltd.

| Programma               | able Short current protection ( ISET )                                                                                                                                         |                                                                                              |      |   |     |    |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------|---|-----|----|

| CM,ISET                 | Input common-mode range of comparator                                                                                                                                          | -                                                                                            | -0.3 | - | 3   | V  |

| <b>V</b> OFF,ISET       | Input offset voltage of comparator                                                                                                                                             | VISET=1V                                                                                     | -20  | - | 20  | mV |

| Toff                    | Propagation time for short current detection (2)                                                                                                                               | VISET=1V,<br>VFBN=0.9 to 1.1V step<br>VPWMO goes from high to low                            | -    | - | 250 | ns |

| ditions for<br>ommended | beyond the maximum ratings listed above<br>extended time may stress the device ar<br>operating conditions. These are stress ratir<br>parameters, although guaranteed by design | e may incur permanent damage to the<br>ad affect device reliability. Also the a<br>ngs only. |      |   |     |    |

### **Pin Description**

| Р  | PIN NO | Description                                           |  |

|----|--------|-------------------------------------------------------|--|

| 1  | VCC    | Power Supply Input                                    |  |

| 2  | ISET   | Programmable Short Current Protection Set             |  |

| 3  | GATE   | Gate drive Output for Boost Convert                   |  |

| 4  | GND    | GND                                                   |  |

| 5  | CS     | Current sense of the Boost Convert                    |  |

| 6  | AUTO   | Auto Restart mode control for protection              |  |

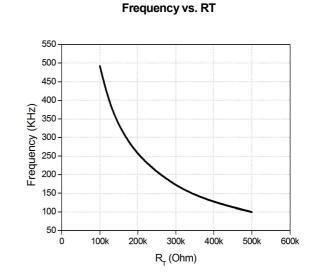

| 7  | RT     | Oscillator frequency set of the Boost Converter       |  |

| 8  | SYNC   | Oscillators to lock to the highest frequency          |  |

| 9  | CLIM   | Programmable Boost Input current limit                |  |

| 10 | REF    | Reference voltage                                     |  |

| 11 | PWMO   | PWM Gate Driver Output                                |  |

| 12 | OVP    | Over voltage protection                               |  |

| 13 | PWMI   | PWM Gate Driver Input                                 |  |

| 14 | COMP   | Error Amp. Compensation                               |  |

| 15 | FBP    | Error Amp. Non-inverting Input/Positive Current Sense |  |

| 16 | FBN    | Error Amp. Inverting Input/Negative Current Sense     |  |

| 1 | VCC  |             | FBN  | 16 |

|---|------|-------------|------|----|

| 2 | ISET | S           | FBP  | 15 |

| 3 | GATE | E<br>L      | COMP | 14 |

| 4 | GND  | -<br>C<br>2 | PWMI | 13 |

| 5 | CS   | -<br>0<br>1 | OVP  | 12 |

| 6 | Αυτο | 0<br>M      | PWMO | 11 |

| 7 | RT   |             | REF  | 10 |

| 8 | SYNC |             | CLIM | 9  |

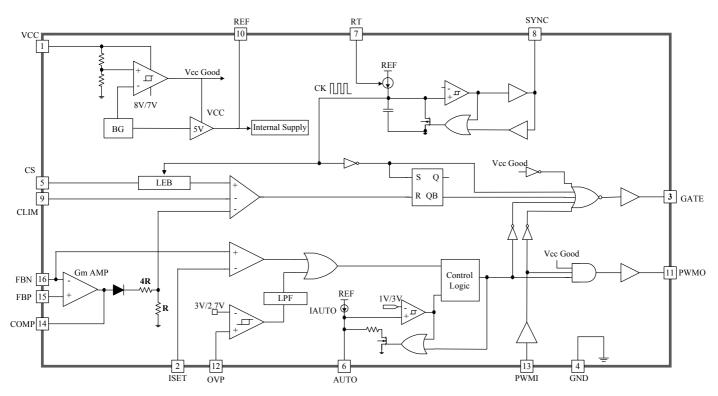

### **Functional Block Diagram**

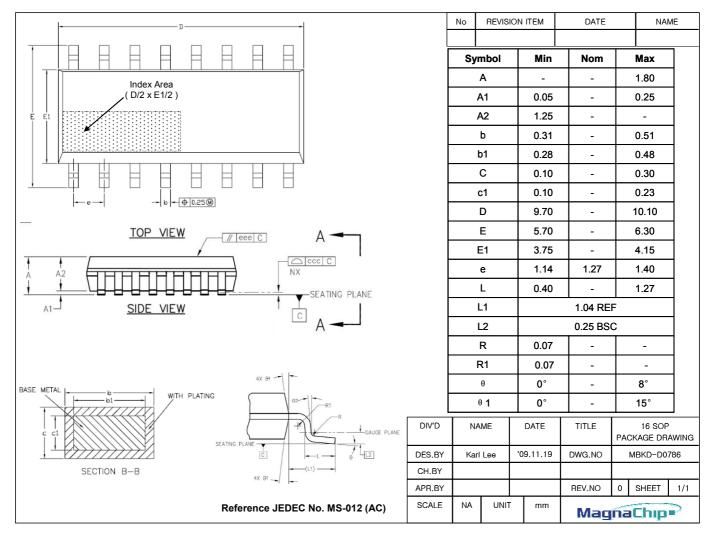

#### **Physical Dimensions**

# **Typical Operating Characteristics** The following conditions apply: VCC =12V, RRT = 500 kΩ, VPWMI = 5V

#### Quiescent Current vs. Vcc

**VREF Line Regulation Voltage**

**VREF Load Regulation Voltage**

Under Voltage Lock Out

MagnaChip•

# **Typical Operating Characteristics** The following conditions apply: VCC =12V, RRT = 500 kΩ, VPWMI = 5V

#### **Over Voltage Protection**

# MAP3201 – High current switch mode PWM LED Driver

#### Current Mode Boost switching regulator operation

The MAP 3201 is operated in current mode PWM Boost regulation method, which shows fast frequency response while maintaining stable output voltage.

It features stable response by using the recommended combination of resistor and capacitor at COMP and GND pin for specific condition of wide input voltage, Output voltage and variable Load condition.

#### Internal 5V Low Dropout Regulator

The MAP3201 has LDO embedded in it to supply Internal analog, logic circuit and external REF Pin. This LDO operates at a voltage level where Vcc is higher than the UVLO voltage. It provides maximum 10mA of output current through regulator which has 2% accuracy of performance.

To stabilize the voltage of REF Pin, it is recommended to use low ESR capacitor which is as low as 1uF and connect it between REF and GND Pin, and install it as close as to Pin.

#### Boost Converter Switching Frequency

The MAP3201 can set the switching frequency of Boost converter by connecting external resistor between RT and GND Pin. Recommended switching frequency is 100 KHz to 400 KHz. See Figure 1 for switching frequency adjustment resistor (RT)

Figure 1 Boost switching frequency vs. RT

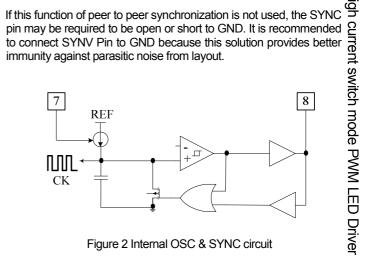

#### SYNCHRONIZATION

The MAP3201 can not only operate constant frequency internally, but also control switching frequency externally by using external master clock signal through SYNC Pin. The clock signal of SYNC Pin needs to be faster than internal Oscillator clock to ensure normal switching operation.

When synchronizing multiple MAP3201 on single board, all SYNC Pin ICs of each device should be short to make all devices in sync on the Oscillator clock of the fastest device.

In this case, the number of synchronized devices differs depending on the operation frequency of Oscillator.

If this function of peer to peer synchronization is not used, the SYNC

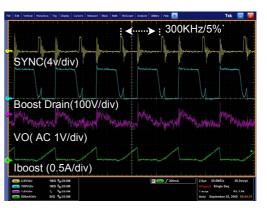

Figure 3 Synchronization by external clock (Fixed 100 KHz  $\rightarrow$  300 KHz)

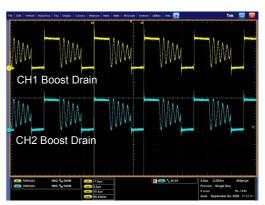

Figure 4 Peer -- to -peer synchronization (Fixed 100 KHz)

#### PROTECTION

The MAP3201 offers the features such as UVLO, Boost current limit, Over Voltage Protection and Short Circuit Protection of LED (SCP). OVP and SCP are operated in auto restart protection mode.

#### 1. Under-Voltage Lock-Out (UVLO)

When VCC voltage reaches over 8V, UVLO starts operating which enables Internal 5V Regulator, making all internal control circuits including oscillator, gate driver and protection circuit ready for operation and output pin of GATE, PWMO and COMP starts operating depending on the input status of PWMI.

If VCC voltage drops below 7V during normal operation, UVLO starts operating, shutting down Internal Control Circuit and stopping operation of GATE, PWMO and COMP. It is followed by disabling of internal 5V regulator, and shut off of all IC operation.

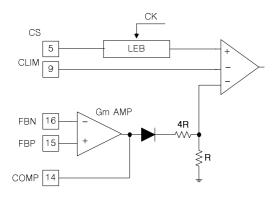

#### 2. Pulse by Pulse Current Limit

It will operate Pulse by Pulse current limit as voltage ratio between COMP Pin Voltage which is controlled by Gm Amp of Boost converter and CS Pin voltage which will be caused by external Boost FET.

#### 3. Maximum Current Limit

Maximum current that is driven into Boost FET through CLIM Pin voltage can be set up as in Figure 5

Figure 5 Current Sense and Maximum current limit

VC, MAX: Maximum output voltage of Gm Amp VOFF: Offset voltage of PWM comparator

$$V_{CS} = \frac{V_{C,MAX} - 0.6V}{5} - V_{OFF}$$

$$V_{CS} = V_{CLM}$$

The equation above can be used to set up Maximum boost current when VCLIM is VCS.

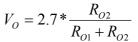

#### 4. Over Voltage Protection (OVP)

The MAP3201 offers over voltage protection in order to protect MOSFET of boost converter and external component connected to Output pin when output voltage is in abnormal condition.

If OVP Pin voltage reaches threshold condition (typical 3V), it can shut off the switching of GATE and PWMO and then output voltage is falling as much as the leakage current time. If the voltage of OVP Pin reaches OVP falling threshold (typical 2.7V), IC releases protection mode. In this time, protection releasing can be decided as value of capacitor with the longer discharge between auto restart time and the time of leakage current connected to output. The over voltage protection can be decided in the following equation. - Protection voltage:  $V_O = 3.0 * \frac{R_{O2}}{R_{O1} + R_{O2}}$ OVP Circuit monitors whether output voltage is stable level or not

$$V_o = 3.0 * \frac{R_{o2}}{R_{o1} + R_{o2}}$$

Protection release voltage:

Figure 6 Over voltage protection circuit

The MAP3201 included LPF(low pass filter) of typical 200nS in OVP circuit for better noise immunity. It may need a high noise margin when Ro1 and Ro2 use high resistance value in order to minimize Power loss

In this case, it is recommended to add Capacitor.

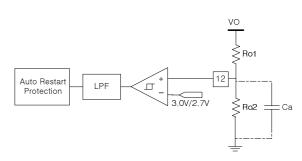

#### Programmable Short Current Protection of LED (SCP)

The MAP3201 offers protection circuit to prevent short current when LED string is shorted

In Figure 7 when LED string is shorted, the voltage of FBN Pin can be calculated in the following equation

$$V_{FBN} = I_{LED} * R_{LED}$$

MAP3201 – High current switch mode PWM LED Driver

The programmable SCP voltage can be set up in reference to 5V VREF in the equation below.

$$V_{ISET} = \frac{5*R2}{R1+R2}$$

Therefore, the SCP level can be decided by selecting the resistor value of RLED, R1 and R2.

Figure 7 Programmable short current protections

SCP Circuit uses very fast comparator in order to turn off MOSFET when the abnormal condition of SCP Level is detected. Because high current can be driven into channel of MOSFET when LED string is shorted.

It is recommended to use additional ISET Cs capacitor in order to prevent abnormal SCP which is caused by noise

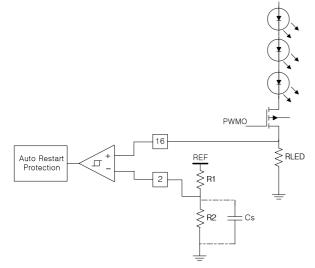

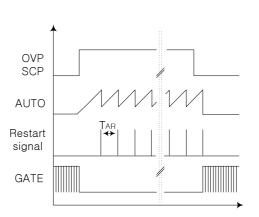

#### 6. Auto-Restart Protection

The MAP3201 offers Auto Restart protection function which is recovered into normal operation mode when protection condition is cleared

Figure 8 Auto Restart Protection circuit

Figure 8 shows auto restart protection circuit that shuts off the output of GATE switching and PWMO if protection signal is assigned to control logic circuit under OVP or SCP condition.

The timer circuit operates as the configuration of both comparator of 21V/3V Input, IAUTO=5uA (typical) and external capacitor CAUTO and the restart time can be calculated in the following equation.

$$T_{AR} = \frac{2 * C_{AUTO}}{I_{AUTO}} = 4e + 5 * C_{AUTO}$$

Figure 9 Auto Restart Protection timing diagram

On Auto-Restart Protection status, it makes restart signal of internal single pulse when the voltage of AUTO Pin is high threshold. In this case, it is recovered to normal operating mode if SCP or OVP condition is cleared. While charging AUTO pin, it recover protection when next restart signal occurs even though protection condition is cleared.

#### **Dimming Control**

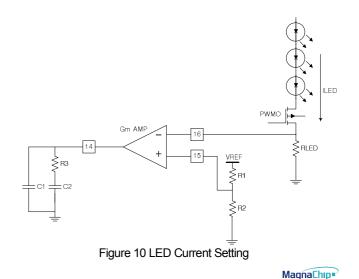

#### 1. LED Current

The MAP3201 decides LED Current setting by the value of RLED resistance which has been sensing the voltage of positive input FBP Pin of gm Amp. and LED current ( $V_{FBP}$ )

In figure 10

$$V_{FBP} = \frac{V_{REF} * R2}{R1 + R2}$$

$$V_{FBN} = I_{LED} * R_{LED}$$

$$5 * R2$$

$$\therefore I_{LED} = \frac{3 R_2}{(R1 + R2) * R_{LED}}$$

#### 2. PWM Dimming

The MAP3201 makes same phase PWMO output from logic PWM signal of PWMI using intenral Level shift. PWMO of operating voltage level is between GND and VCC.

#### Inductor Selection

Inductor value should be decided before system design.

Because the selection of the inductor affects the operating mode of CCM (Continuous current mode) or DCM (Discontinuous current mode).

In CCM operation, indutor size should be bigger, even though the ripple current and peak current of inductor can be small.

In DCM operation, even ripple current and peak current of inductor should be large while the inductor size can be smaller so that it is more effective in BLU of TV and Notebook application.

The MAP3201 was designed for DCM operation.

In CCM operation, sub-harmonic oscillation may occur if duty cycle exceeds over 50%. Because there is no slope compensation functions.

The following is the equation to calculate Max.Value of Inductor in DCM operation.

$$L_{(\max)} = \frac{\left[ (1-D)^2 * D * R_{O(\max)} * T_{s(\min)} \right]}{2}$$

\* $R_{O(\max)} = Maximum \_Output \_Im pedance$ \* $T_{S(\min)} = Minimum \_Switching \_period$

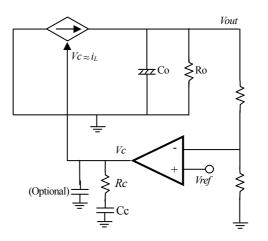

#### **Closed Loop Network Selection**

The MAP3201 controls in peak current mode. Current mode easily achieves compensation by consisting simple single Pole from Double Pole that LC filer makes at Voltage mode

Figure 11 Current mode Loop Compensation

#### 1. Select fc (Crossover frequency)

In general, crossover frequency is selected from  $1/3 \sim 1/6$  range of the switching frequency. If fc is large, there is possibility of oscillation to occur, although time response gets better.

On the other hand, if fc is small, time response will be bad, while it has improved stability, which may cause over shoot or under shoot in abnormal condition.

It should be noted that  $\ensuremath{\mathsf{fc}}$  should be set at smaller location than RHP Zero.

$$f_{RHP} = \frac{Ro*(1-D)^2}{2\pi*L}$$

(Boost)

2. Select fpo

$$f_{\scriptscriptstyle PO} = f_{\scriptscriptstyle C} \ast G_{\scriptscriptstyle O} \label{eq:GO}$$

$G_{\scriptscriptstyle O} = DC$  Gain of plant =  $\frac{A}{B}$  )

$$A = \frac{1}{\frac{2}{R} + \frac{(m - 0.5) * (1 - D)^{3}}{L * F}}$$

Selecting approximately m = 1.4

$$B = R_s * (1 - D)$$

$R_{\scriptscriptstyle S}=$  Sensing Resistor

#### 3. Select Pole and Zero

$$f_{PO} = \frac{1}{2\pi * \frac{C_C}{Y * G_{FA}}}$$

$G_{\rm EA} = {\rm ~Gm-Amp~Transconductance}$

$$Y = Attenuation - Ratio = \frac{V_{FPN}}{V_o}$$

$$f_{Z1} = \frac{1}{2\pi * R_c * C_c}$$

Zero is set at the same location of output pole. In system design, if ESR of output capacitor is large, Pole should be set at same frequency in order to compensate The Zero of ESR.

$$f_{P1(OP)} = \frac{1}{2\pi * R_C * C_{OP}}$$

#### **Worldwide Sales Support Locations**

U.S.A Sunnyvale Office 787 N. Mary Ave. Sunnyvale CA 94085 U.S.A Tel : 1-408-636-5200 Fax : 1-408-213-2450 E-Mail : americasales@magnachip.com

Chicago Office 2300 Barrington Road, Suite 330 Hoffman Estates, IL 60195 U.S.A Tel : 1-847-882-0951 Fax :1-847-882-0998

U.K Knyvett House The Causeway, Staines Middx, TW18 3BA,U.K. Tel : +44 (0) 1784-898-8000 Fax : +44 (0) 1784-895-115 E-Mail : europesales@magnachip.com

Japan Tokyo Office Shinbashi 2-chome MT bldg 4F 2-5-5 Shinbashi, Minato-ku Tokyo, 105-0004 Japan Tel : 81-3-3595-0632 Fax : 81-3-3595-0671 E-Mail : japansales@magnachip.com

Osaka Office 3F, Shin-Osaka MT-2 Bldg 3-5-36 Miyahara Yodogawa-Ku Osaka, 532-0003 Japan Tel : 81-6-6394-8224 Fax : 81-6-6394-8282 E-Mail : osakasales@magnachip.com Taiwan R.O.C 2F, No.61, Chowize Street, Nei Hu Taipei,114 Taiwan R.O.C Tel : 886-2-2657-7898 Fax : 886-2-2657-8751 E-Mail : taiwansales@magnachip.com

China Hong Kong Office Office 03, 42/F, Office Tower Convention Plaza 1 Harbour Road, Wanchai, Hong Kong Tel : 852-2828-9700 Fax : 852-2802-8183 E-Mail : chinasales@magnachip.com

Shenzhen Office Room 1803, 18/F International Chamber of Commerce Tower Fuhua 3Road, Futian District ShenZhen, China Tel : 86-755-8831-5561 Fax : 86-755-8831-5565

Shanghai Office Ste 1902, 1 Huaihai Rd. (C) 20021 Shanghai, China Tel : 86-21-6373-5181 Fax : 86-21-6373-6640

Korea 891, Daechi-Dong, Kangnam-Gu Seoul, 135-738 Korea Tel : 82-2-6903-3451 Fax : 82-2-6903-3668 ~9 Email : koreasales@magnachip.com

#### DISCLAIMER:

The products are not designed for use in hostile environments, including, without limitation, aircraft, nuclear power generation, medical appliances, and devices or systems in which malfunction of any product can reasonably be expected to result in a personal injury. Seller's customers using or selling Seller's products for use in such applications do so at their own risk and agree to fully defend and indemnify Seller.