# **MAS9316**

# 16-BIT DAC

- · +/- 0.006% DNL and INL

- · No Laser Trimming

- · Fast Interface Timing

#### **DESCRIPTION**

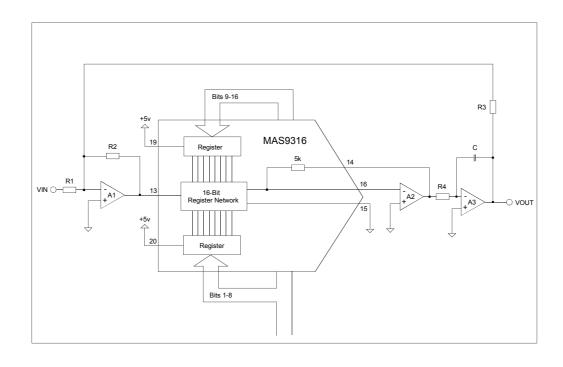

The MAS9316 is a 16-bit, monolithic CMOS, multiplying digital-to-analog converter (DAC) designed for direct microprocessor interface. Its high relative accuracy and monotonicity is achieved without laser trimming. This is made possible by the use of highly accurate, low TCR thin film resistor process and a 4 MSB to 15 decoding design technique. Hidden errors are eliminated by testing all the 65536 different input codes. The device

offers advantages like high stability over time and temperature and low sensitivity to output amplifier offset combined to excellent performance-to-cost ratio. The fast input data latches are designed as two 8-bit segments providing data storage when latched or transparent operation when unlatched. All digital inputs have high ESD protection up to 2 kV.

### **FEATURES**

- · Linearity TC 0.5 ppm/C

- · 2 kV ESD Protection on Digital Inputs

- · D4 MSB's Decoded

- · All 65536 Codes Tested

- · Monolithic CMOS Replacement for SIPEX

- DAC 9331-16-4 and SP9316C-4

- · 24-pin PDIP Package

#### **APPLICATION**

- · Audio applications

- · Instrumentation

- · uP Controlled systems

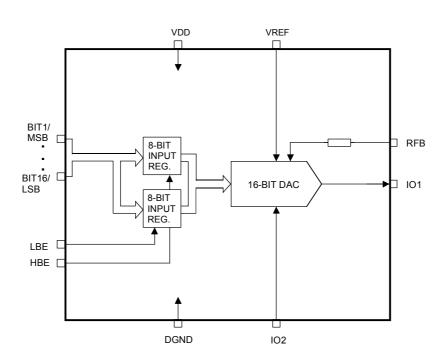

#### **BLOCK DIAGRAM**

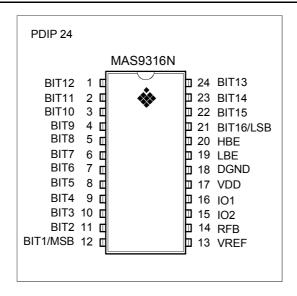

# **PIN CONFIGURATION**

### **PIN DESCRIPTION**

| Pin name | PDIP | I/O | Function                |  |

|----------|------|-----|-------------------------|--|

| BIT 12   | 1    | I   | Data bit 12, MSB        |  |

| BIT 11   | 2    | ı   | Data bit 11             |  |

| BIT 10   | 3    | I   | Data bit 10             |  |

| BIT 9    | 4    | I   | Data bit 9              |  |

| BIT 8    | 5    | I   | Data bit 8              |  |

| BIT 7    | 6    | I   | Data bit 7              |  |

| BIT 6    | 7    | I   | Data bit 6              |  |

| BIT 5    | 8    | I   | Data bit 5              |  |

| BIT 4    | 9    | I   | Data bit 4              |  |

| BIT 3    | 10   | I   | Data bit 3              |  |

| BIT 2    | 11   | I   | Data bit 2              |  |

| BIT 1    | 12   | ı   | Data bit 1              |  |

| VREF     | 13   | I   | Reference voltageilnput |  |

| RFB      | 14   | I   | Feedback resistor       |  |

| 102      | 15   | 0   | Current output          |  |

| IO1      | 16   | 0   | Current output          |  |

| VDD      | 17   | Р   | Positive Supply voltage |  |

| DGND     | 18   | G   | Digital ground          |  |

| LBE      | 19   | I   | Low byte enable         |  |

| HBE      | 20   | I   | High byte enable        |  |

| BIT 16   | 21   | I   | Data bit 16, LSB        |  |

| BIT 15   | 22   | I   | Data bit 15             |  |

| BIT 14   | 23   | I   | Data bit 14             |  |

### **PIN DESCRIPTION**

| Pin name | PDIP | I/O | Function    |

|----------|------|-----|-------------|

| BIT 13   | 24   | I   | Data bit 13 |

#### **ABSOLUTE MAXIMUM RATINGS**

(Ta = 25°C unless otherwise noted)

| Parameter                   | Symbol | Conditions          | Min  | Max     | Unit   |

|-----------------------------|--------|---------------------|------|---------|--------|

| Supply Voltage              | VDD    |                     | -0.3 | +17     | V      |

| Vref or RFB to DGND         |        |                     | -25  | +25     | V      |

| Output Voltage (Pin 15, 16) |        |                     | -0.3 | VDD+0.3 | V      |

| Power Dissipation           | PD     | Any package at 75°C |      | 459     | mW     |

| Derates above 75°C by       |        |                     |      | 6       | mW/ °C |

| Die Junction Temperature    |        |                     |      | +150    | °C     |

| Storage Temperature         | Ts     |                     |      |         | °C     |

#### **CAUTION:**

1.Do not apply voltages higher than VDD or less than GND potential on any terminal other than VREF or RFB. 2.The digital inputs are diode clamp protected against ESD damage. However, permanent damage may occur on unprotected units from high-energy electrostatic fields. Use proper anti-static handling procedures.

3.Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation at or above this specification is not implied.

### **RECOMMEDED OPERATION CONDITIONS**

(conditions)

| Parameter           | Symbol | bol Conditions                |    | Тур | Max | Unit |

|---------------------|--------|-------------------------------|----|-----|-----|------|

| Supply Voltage      | VDD    |                               | +5 | +15 | +16 | V    |

| Supply Current      | IDD    | All digital inputs VIL or VIH |    | 2.0 | 4.0 | mA   |

| Supply Current      | IDD    | All digital inputs 0V or 5V   |    | 0.2 | 1.0 | mA   |

| Power Dissipation   | Pd     |                               |    |     | 60  | mW   |

| Storage Temperature | Ts     |                               | 0  |     | +70 | °C   |

### **ELECTRICAL CHARACTERISTICS**

#### **♦** Static Performance

(test conditions Ta=+25C)

|                                        |        |                                                 |     |        | 3t Conditions | /         |

|----------------------------------------|--------|-------------------------------------------------|-----|--------|---------------|-----------|

| Parameter                              | Symbol | Conditions                                      | Min | Тур    | Max           | Unit<br>s |

| Resolution                             | N      |                                                 | 16  |        |               | Bits      |

| Integral Nonlinearity <sup>1</sup>     | INL    |                                                 |     | ±0.004 | ±0.006        | %         |

| Differential Nonlinearity <sup>2</sup> | DNL    | Relative accuracy 13 bits  Monotonic to 14 bits |     | ±0.003 | ±0.006        | %         |

| Gain error                             | Gfse   | Measured Using Internal Rfb DAC                 |     | ±0.1   | ±0.2          | %         |

| Output Leakage Current at IO1 (pin 16) | lilk   | Register Loaded With All 1s                     |     |        | 10            | nA        |

| Offset Error                           |        |                                                 |     |        | ±0.0005       | %         |

### **◆** Temperature Stability

(test conditions Ta=+25C)

|                              |          |            |     | (1031 | Conditions | 1a-1230)  |

|------------------------------|----------|------------|-----|-------|------------|-----------|

| Parameter                    | Symbol   | Conditions | Min | Тур   | Max        | Unit<br>s |

| Gain error                   | TCTCGFSE |            |     | ±1.0  | ±2.0       | pm/C      |

| Integral Nonlinearity TC     | TCINL    |            |     | ±0.1  | ±0.5       | pm/C      |

| Differential Nonlinearity TC | TCDNL    |            |     | ±0.1  | ±0.5       | pm/C      |

#### **♦** Reference Input

(test conditions Ta=+25C)

| Parameter                  | Symbol | Conditions | Min | Тур | Max | Unit<br>s |

|----------------------------|--------|------------|-----|-----|-----|-----------|

| Input Resistance           | Rref   |            | 2.5 | 5   | 7.5 | kΩ        |

| Voltage Range <sup>3</sup> |        |            |     |     | ±25 | ٧         |

#### **♦** Switching Characteristics

(test conditions Ta=+25C)

|                 |                 |                    |    | (1001 | CONTUNIONS | <u>.u .zoo,</u> |

|-----------------|-----------------|--------------------|----|-------|------------|-----------------|

| Parameter       | Symbol          | Symbol Conditions  |    | Тур   | Max        | Unit<br>s       |

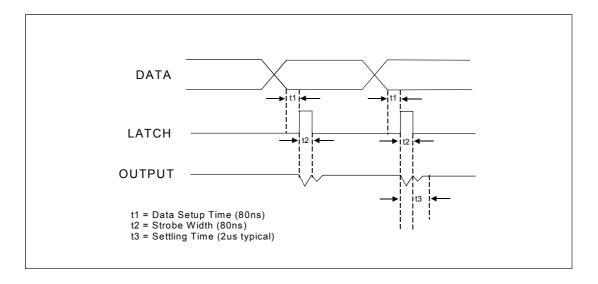

| Strobe Width    | t <sub>sw</sub> | HBE and LBE Inputs | 80 | 60    |            | ns              |

| Data Setup Time | t <sub>DS</sub> | Bit 1 to Bit 16    | 80 | 70    |            | ns              |

| Data Hold Time  | t <sub>DH</sub> | Bit 1 to Bit 16    | 40 | 20    |            | ns              |

#### NOTES:

- 1. Integral Nonlinearity is measured as the arithmetic mean value of magnitudes of the greatest positive deviation and the greatest negative deviation from the theoretical value of any given input combination.

- 2. Differential Nonlinearity DNL is the deviation of an output step from the theoretical value of 1 LSB for any two adjacent digital input codes.

- 3.Guaranteed by design but not production tested. 4.Logic inputs are MOS gates. Iin typical is less than 1 nA at 25C.

# **AC PERFORMANCE CHARACTERISTICS**

These characteristics are included for design guidance only and are subject to sample testing only. VDD=+15V, VREF=10V, IO1=IO2=DGND=0V except where stated. Output Amp is HOS-050.

(test conditions Ta=+25C)

|                                                                                           | ı               | T                                                                                                                                                       |     | (188                   | t conditions | 1a-+250)             |

|-------------------------------------------------------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------|--------------|----------------------|

| Parameter                                                                                 | Symbol          | Conditions                                                                                                                                              | Min | Тур                    | Max          | Units                |

| Propagation Delay                                                                         | t <sub>PD</sub> | IO1 load R=100Ω, Cext=13pF<br>All Data Inputs 0V to VDD or<br>VDD to 0V<br>From 50% digital input change<br>to 90% of final analog output.              |     | 300                    |              | ns                   |

| CURRENT SETTLING Major Code Transition  Full Scale Transition                             | ts              | TIMESettling to +0.01% FSR (strobed). 0111111111111111 to 1000000000000000 or 100000000000000 to 011111111111111 All Data Inputs 0V to VDD or VDD to 0V |     | 3.0                    |              | μS<br>μs             |

| OUTPUT CAPACITANCE<br>CIO1 (Pin 16)170<br>CIO2 (Pin 15)<br>CIO1 (Pin 16)<br>CIO2 (Pin 15) | Со              | Digital inputs VIH<br>Digital inputs VIH<br>Digital inputs VIL<br>Digital inputs VIL                                                                    |     | 170<br>30<br>80<br>100 |              | pF<br>pF<br>pF<br>pF |

| Digital to Analog Glitch<br>Energy                                                        | Q               | VREF =0V<br>DAC register alternately loaded<br>with all 0s and all 1s                                                                                   |     | 250                    |              | nVs                  |

| Multiplying Feedthrough<br>Error at IO1                                                   | FT              | VREF=20Vpp; f=10kHz sine wave VREF=20Vpp, f=1kHz sine wave                                                                                              |     | 3.0<br>0.3             |              | mVpp<br>mVpp         |

| Power Supply Rejection<br>Ratio                                                           | PSRR            | VDD = 14 to 16V                                                                                                                                         |     | ±0.0001                | ±0.002       | %/%                  |

### **TIMING DIAGRAM**

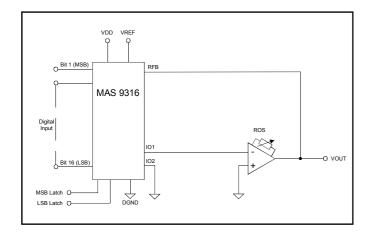

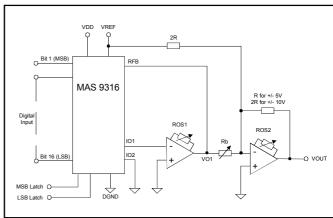

### **APPLICATION INFORMATION**

### UNIPOLAR OPERATION, Transfer Characteristics

| BINARY INPUT                                             | ANALOG OUTPUT                                                                                                                       |

|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 111111<br>100001<br>100000<br>011111<br>000001<br>000000 | -VREF (1-2 <sup>-N</sup> )<br>-VREF (1/2-2 <sup>-N</sup> )<br>-VREF 1/2<br>-VREF (1/2-2 <sup>-N</sup> )<br>-VREF (2 <sup>-N</sup> ) |

#### Note:

To maintain specified linearity, the external amplifier (A) must be nulled. Apply an 'all zeroes' digital input and adjust ROS for VOUT = 0 + -1 mv.

### **BIPOLAR OPERATION Transfer Characteristics**

| OFFSET BINARY INPUT | ANALOG OUTPUT                  |

|---------------------|--------------------------------|

| 111111              | -VREF (1-2 <sup>-(N-1)</sup> ) |

| 100001              | -VREF (2- <sup>-(N-1)</sup> )  |

| 100000              | 0                              |

| 011111              | +VREF (2 <sup>(N-1)</sup> )    |

| 000001              | -VREF (1-2 <sup>-(N-1)</sup> ) |

| 000000              | +VREF                          |

#### Note:

To maintain specified linearity, the external amplifier (A1 and A2) must be nulled. With a digital input of 10...0 and VREF set to zero:

a) set ROS1 for VO1 =0, b) set ROS2 for VOUT = 0 c) set VREF to +10v and adjust Rb for VOUT to be 0 volts.

### **DIGITALLY CONTROLLED LOW PASS FILTER**

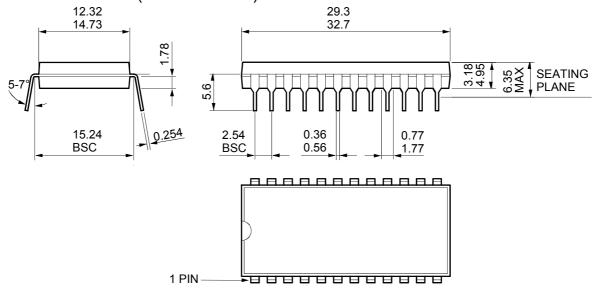

# **PACKAGE OUTLINES**

# 24 LEAD PDIP OUTLINE (600 MIL BODY)

ALL MEASUREMENTS IN mm

### ORDERING INFORMATION

| Product Code  | Product    | Package     | Comments                |

|---------------|------------|-------------|-------------------------|

| MAS9316N      | 16-bit DAC | 24 Pin PDIP |                         |

| MAS9316A1ND08 | 16-bit DAC | 24 Pin PDIP | Pb free, RoHS compliant |

| LOCAL DISTRIBUTOR           |                     |  |

|-----------------------------|---------------------|--|

|                             |                     |  |

| Г                           |                     |  |

|                             |                     |  |

|                             |                     |  |

|                             |                     |  |

|                             |                     |  |

|                             |                     |  |

|                             |                     |  |

|                             |                     |  |

|                             |                     |  |

|                             |                     |  |

|                             |                     |  |

| THORO ANALOG OVETEME OV     |                     |  |

| MICRO ANALOG SYSTEMS OY O   | ONTACTS             |  |

| Micro Analog Systems Oy     | Tel. +358 9 80 521  |  |

| Kamreerintie 2, P.O. Box 51 | Fax +358 9 805 3213 |  |

#### **NOTICE**

FIN-02771 Espoo, FINLAND

Micro Analog Systems Oy reserves the right to make changes to the products contained in this data sheet in order to improve the design or performance and to supply the best possible products. Micro Analog Systems Oy assumes no responsibility for the use of any circuits shown in this data sheet, conveys no license under any patent or other rights unless otherwise specified in this data sheet, and makes no claim that circuits are free from patent infringement. Applications for any devices shown in this data sheet are for illustration only and Micro Analog Systems Oy makes no claim or warranty that such applications will be suitable for the use specified without further testing or modification

http://www.mas-oy.com