## **General Description**

The MAX1338 14-bit, analog-to-digital converter (ADC) offers four simultaneously sampled, fully differential input channels, with independent track-and-hold (T/H) circuitry for each channel. The input channels are individually software programmable for input ranges of  $\pm 10V$ ,  $\pm 5V$ ,  $\pm 2.5V$ , and  $\pm 1.25V$ . The input channels feature fault tolerance to  $\pm 17V$ . The internal T/H circuits have a 16ns aperture delay and 100ps aperture-delay matching.

A 14-bit parallel bus provides the conversion result with a maximum per-channel output rate of 150ksps (600ksps for all four channels). The MAX1338 has an on-board oscillator and 2.5V internal reference. An external clock and/or reference can also be used.

The MAX1338 operates from a +5V supply for analog inputs and digital core. The device operates from a +2.7V to +5.25V supply for the digital I/O lines. The MAX1338 features two power-saving modes: standby mode and shutdown mode. Standby mode allows rapid wake-up and reduces quiescent current to 4mA (typ), and shutdown mode reduces sleep current to less than 10 $\mu$ A (typ).

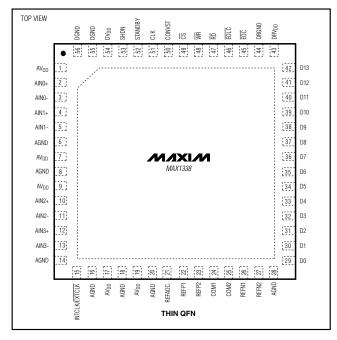

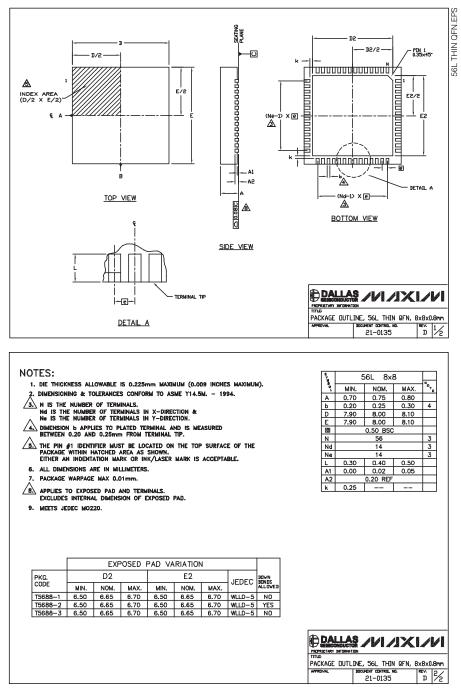

The MAX1338 is available in an 8mm x 8mm x 0.8mm, 56-pin, thin QFN package. The device operates over the extended -40°C to +85°C temperature range.

## **Applications**

Multiple-Channel Data Recorders

Vibration Analysis

Motor Control: 3-Phase Voltage, Current, and Power Measurement

Optical Communication Equipment

## **Features**

- 150ksps Sample Rate per Channel

- All Four Input Channels Simultaneously Sampled 16ns Aperture Delay 100ps Aperture-Delay Matching

- Channel-Independent Software-Selectable Input Range: ±10V, ±5V, ±2.5V, ±1.25V

- ±17V Fault-Tolerant Inputs

- Dynamic Performance at 10kHz Input SNR: 77dB SINAD: 76dB SFDR: 98dBc THD: -83dBc

- DC Performance

INL: ±2 LSB

DNL: ±1 LSB

Offset Error: ±4 LSB

Gain Error: ±0.1% FSR

- ♦ 14-Bit Parallel Interface

- Internal Clock and Reference Voltage

- +5V Analog and Digital Supplies

- ♦ +2.7V to +5.25V Digital I/O Supply

- 56-Pin Thin QFN Package (8mm x 8mm x 0.8mm)

## **Ordering Information**

| PART       | TEMP RANGE     | PIN-PACKAGE     |

|------------|----------------|-----------------|

| MAX1338ETN | -40°C to +85°C | 56 Thin QFN-EP* |

\*EP = Exposed pad.

#### Pin Configuration appears at end of data sheet.

##

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

## **ABSOLUTE MAXIMUM RATINGS**

| AV <sub>DD</sub> to AGND             | 0.3V to +6V                        |

|--------------------------------------|------------------------------------|

| DV <sub>DD</sub> to DGND             | 0.3V to +6V                        |

| DRV <sub>DD</sub> to DRGND           | 0.3V to +6V                        |

| AV <sub>DD</sub> to DV <sub>DD</sub> | 0.3V to +0.3V                      |

| DGND to DRGND                        | 0.3V to +0.3V                      |

| AGND to DGND                         | 0.3V to +0.3V                      |

| AGND to DRGND                        | 0.3V to +0.3V                      |

| AIN0+, AIN0-, AIN1+, AIN1-, AIN2+    | ⊦, AIN2-, AIN3+,                   |

| AIN3- to AGND                        | 17V to +17V                        |

| D0–D13 to DRGND                      | 0.3V to (DRV <sub>DD</sub> + 0.3V) |

| REFADC, REFP1, REFP2, REFN1, F       | REFN2, COM1, COM2 to               |

| AGND                                 |                                    |

| INTCLK/EXTCLK to AGND                | 0.3V to (AV <sub>DD</sub> + 0.3V)  |

| $\overline{CS}$ , $\overline{RD}$ , $\overline{WR}$ , CONVST, to DRGND0.3V to (DRV <sub>DD</sub> + 0.3V)<br>SHDN, STANDBY, CLK, $\overline{EOC}$ , |

|----------------------------------------------------------------------------------------------------------------------------------------------------|

| EOLC to DRGND0.3V to (DRV <sub>DD</sub> + 0.3V)                                                                                                    |

| Maximum Current into Any Pin±50mA                                                                                                                  |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )                                                                                              |

| 56-Pin Thin QFN (derate 31.3mW /°C above +70°C)2500mW                                                                                              |

| Operating Temperature Range40°C to +85°C                                                                                                           |

| Storage Temperature Range65°C to +150°C                                                                                                            |

| Maximum Junction Temperature+150°C                                                                                                                 |

| Lead Temperature (soldering, 10s)+300°C                                                                                                            |

| Junction to Ambient Thermal Resistance 0JA                                                                                                         |

| Junction to Case Thermal Resistance $\theta_{JC}$                                                                                                  |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS**

$(AV_{DD} = DV_{DD} = +5.0V, DRV_{DD} = +3.0V, AGND = DGND = DRGND = 0, INTCLK/EXTCLK = AGND, f<sub>CLK</sub> = 5MHz, input range = ±10V, REFP2 = REFP1, REFN2 = REFN1, COM1 = COM2, 1.0nF from REFADC to AGND, 1.0µF and 0.1µF from COM1 to AGND, 0.1µF from REFP1 to AGND, 0.1µF from REFN1 to AGND, 1.0µF from REFP1 to REFN1. Typical values are at T<sub>A</sub> = +25°C. T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted.)$

| PARAMETER                               | SYMBOL       | CONDITIONS                   | MIN   | ТҮР   | MAX   | UNITS  |

|-----------------------------------------|--------------|------------------------------|-------|-------|-------|--------|

| STATIC PERFORMANCE                      |              |                              |       |       |       |        |

| Resolution                              | Ν            |                              | 14    |       |       | Bits   |

| Integral Nonlinearity                   | INL          | (Note 1)                     |       | ±1    | ±3    | LSB    |

| Differential Nonlinearity               | DNL          | No missing codes (Note 1)    |       | ±0.25 | ±1    | LSB    |

| Offset Error                            |              | (Note 1)                     |       | ±4    | ±16   | LSB    |

| Offset-Error Temperature<br>Coefficient |              |                              |       | 5     |       | ppm/°C |

| Offset-Error Matching                   |              |                              |       | ±10   |       | LSB    |

| Gain Error                              |              | Offset nulled (Notes 1, 2)   |       | ±0.1  | ±0.35 | %FSR   |

| Channel Gain-Error Matching             |              | Offset nulled                |       | ±20   |       | LSB    |

| Gain-Error Temperature<br>Coefficient   |              | Offset nulled                |       | 10    |       | ppm/°C |

| DYNAMIC PERFORMANCE (at f               | N = 10kHz, A | N = -0.2dBFS)                | •     |       |       | •      |

| Sampling Rate Per Channel               |              | Simultaneous on all channels |       |       | 150   | ksps   |

| Signal-to-Noise Ratio                   | SNR          | (Note 1)                     | 75    | 77    |       | dB     |

| Signal-to-Noise Plus Distortion         | SINAD        | (Note 1)                     | 74    | 76    |       | dB     |

| Total Harmonic Distortion               | THD          | (Note 1)                     |       | -83   | -80   | dBc    |

| Spurious-Free Dynamic Range             | SFDR         | Range 0 (Note 1)             | 85    |       |       | dBc    |

| Channel-to-Channel Isolation            |              | (Note 1)                     | 80    |       |       | dB     |

| ANALOG INPUTS (AIN_)                    |              |                              |       |       |       |        |

|                                         |              | Range set bits = $(0,0)$     | -10   |       | +10   |        |

| Input Differential Valtage Dense        |              | Range set bits = (0,1)       | -5    |       | +5    | N N    |

| Input Differential Voltage Range        |              | Range set bits = (1,0)       | -2.5  |       | +2.5  | V      |

|                                         |              | Range set bits = (1,1)       | -1.25 |       | +1.25 |        |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(AV_{DD} = DV_{DD} = +5.0V, DRV_{DD} = +3.0V, AGND = DGND = DRGND = 0, INTCLK/EXTCLK = AGND, f_{CLK} = 5MHz, input range = ±10V, REFP2 = REFP1, REFN2 = REFN1, COM1 = COM2, 1.0nF from REFADC to AGND, 1.0µF and 0.1µF from COM1 to AGND, 0.1µF from REFP1 to AGND, 0.1µF from REFN1 to AGND, 1.0µF from REFP1 to REFN1. Typical values are at T<sub>A</sub> = +25°C. T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted.)$

| PARAMETER                                 | SYMBOL           | CONDITIONS                       | MIN                        | ΤΥΡ  | MAX                        | UNITS  |

|-------------------------------------------|------------------|----------------------------------|----------------------------|------|----------------------------|--------|

|                                           |                  | Range set bits = (0,0)           | -5                         |      | +5                         |        |

| hand Original Maria David                 |                  | Range set bits = (0,1)           | -2.5                       |      | +2.5                       |        |

| Input Common-Mode Range                   |                  | Range set bits = (1,0)           | -1.25                      |      | +1.25                      | V      |

|                                           |                  | Range set bits = (1,1)           | -0.625                     |      | +0.625                     |        |

| Input Resistance                          |                  | All settings                     |                            | 6.25 |                            | kΩ     |

| Input Capacitance                         |                  |                                  |                            | 15   |                            | pF     |

| Small-Signal Bandwidth                    | SSBW             | (Note 1)                         |                            | 1    |                            | MHz    |

| Full-Power Bandwidth                      | FPBW             | (Note 1)                         |                            | 75   |                            | kHz    |

| INTERNAL REFERENCE (REFA                  | DC)              |                                  |                            |      |                            |        |

| Output Voltage                            |                  |                                  | 2.475                      | 2.5  | 2.525                      | V      |

| Differential Reference Voltage            | REFP–<br>REFN    |                                  |                            | 2.5  |                            | V      |

| Output-Voltage Temperature<br>Coefficient |                  |                                  |                            | 50   |                            | ppm/°C |

| Load Regulation                           |                  |                                  |                            | 5    |                            | V/mA   |

| EXTERNAL REFERENCE                        | •                |                                  | •                          |      |                            |        |

| REFADC Voltage Input Range                |                  |                                  | 2.0                        | 2.5  | 3.0                        | V      |

| REFADC Input Current                      |                  | (Note 3)                         | -250                       |      | +250                       | μA     |

| REFADC Input Resistance                   | R <sub>REF</sub> |                                  |                            | 5    |                            | kΩ     |

| REFADC Input Capacitance                  |                  |                                  |                            | 15   |                            | pF     |

| TRACK/HOLD (T/H)                          |                  |                                  |                            |      |                            |        |

| Aperture Delay                            | t <sub>AD</sub>  | (Note 1)                         |                            | 16   |                            | ns     |

| Aperture-Delay Matching                   |                  |                                  |                            | 100  |                            | ps     |

| Aperture Jitter                           | t <sub>AJ</sub>  | (Note 1)                         |                            | 50   |                            | psrms  |

| <b>CLOCK-SELECT INPUT (INTCL</b>          | K/EXTCLK)        |                                  |                            |      |                            |        |

| Input-Voltage High                        | VIH              |                                  | 0.7 x<br>AV <sub>DD</sub>  |      |                            | V      |

| Input-Voltage Low                         | VIL              |                                  |                            |      | 0.3 x<br>AV <sub>DD</sub>  | V      |

| DIGITAL INTERFACE AND CON                 | ITROL INPUTS     | S (CS, RD, WR, CONVST, SHDN, CLK | , STANDBY)                 |      |                            |        |

| Input-Voltage High                        | VIH              |                                  | 0.7 x<br>DRV <sub>DD</sub> |      |                            | V      |

| Input-Voltage Low                         | VIL              |                                  |                            |      | 0.3 x<br>DRV <sub>DD</sub> | V      |

| Input Hysteresis                          |                  |                                  |                            | 50   |                            | mV     |

| Input Capacitance                         | CIN              |                                  |                            | 15   |                            | pF     |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(AV_{DD} = DV_{DD} = +5.0V, DRV_{DD} = +3.0V, AGND = DGND = DRGND = 0, INTCLK/EXTCLK = AGND, f_{CLK} = 5MHz, input range = ±10V, REFP2 = REFP1, REFN2 = REFN1, COM1 = COM2, 1.0nF from REFADC to AGND, 1.0µF and 0.1µF from COM1 to AGND, 0.1µF from REFP1 to AGND, 0.1µF from REFN1 to AGND, 1.0µF from REFP1 to REFN1. Typical values are at T<sub>A</sub> = +25°C. T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted.)$

| PARAMETER                           | SYMBOL            | CONDITIONS                                                      | MIN                        | ТҮР    | MAX                        | UNITS  |

|-------------------------------------|-------------------|-----------------------------------------------------------------|----------------------------|--------|----------------------------|--------|

| Input Current                       | I <sub>IN</sub>   | $V_{IN} = 0 \text{ or } DRV_{DD}$                               |                            |        | ±1                         | μA     |

| DIGITAL INTERFACE AND CONT          | ROL OUTPL         | ITS (EOC, EOLC)                                                 |                            |        |                            |        |

| Output-Voltage High                 | VOH               | Sourcing 0.8mA                                                  | DRV <sub>DD</sub><br>- 0.6 |        |                            | V      |

| Output-Voltage Low                  | Vol               | Sinking 1.6mA                                                   |                            |        | 0.4                        | V      |

| PARALLEL DIGITAL I/O (D0-D7)        |                   |                                                                 |                            |        |                            |        |

| Output-Voltage High                 | VOH               | Sourcing 0.8mA                                                  | DRV <sub>DD</sub> -<br>0.6 |        |                            | V      |

| Output-Voltage Low                  | Vol               | Sinking 1.6mA                                                   |                            |        | 0.4                        | V      |

| Leakage Current                     |                   |                                                                 |                            |        | 1                          | μA     |

| Tristate Output Capacitance         |                   | $\overline{\text{RD}} = 1 \text{ or } \overline{\text{CS}} = 1$ |                            | 15     |                            | pF     |

| Input-Voltage High                  | VIH               |                                                                 | 0.7 x<br>DRV <sub>DD</sub> |        |                            | V      |

| Input-Voltage Low                   | VIL               |                                                                 |                            |        | 0.3 x<br>DRV <sub>DD</sub> | V      |

| Input Hysteresis                    |                   |                                                                 |                            | 50     |                            | mV     |

| Input Capacitance                   | CIN               |                                                                 |                            | 15     |                            | рF     |

| Input Current                       | l <sub>IN</sub>   | $V_{IN} = 0 \text{ or } DRV_{DD}$                               |                            |        | ±1                         | μΑ     |

| PARALLEL DIGITAL OUTPUTS (I         | D8–D13)           |                                                                 |                            |        |                            |        |

| Output-Voltage High                 | V <sub>OH</sub>   | Sourcing 0.8mA                                                  | DRV <sub>DD</sub> -<br>0.6 |        |                            | V      |

| Output-Voltage Low                  | VOL               | Sinking 1.6mA                                                   |                            |        | 0.4                        | V      |

| Leakage Current                     |                   |                                                                 |                            |        | 1                          | μA     |

| Tristate Output Capacitance         |                   |                                                                 |                            | 15     |                            | pF     |

| POWER SUPPLIES                      | 0                 | 1                                                               |                            |        |                            |        |

| Analog Supply Voltage               | AVDD              |                                                                 | 4.75                       | 5      | 5.25                       | V      |

| Digital Supply Voltage              | DVDD              |                                                                 | 4.75                       | 5      | 5.25                       | V      |

| Parallel Digital I/O Supply Voltage | DRV <sub>DD</sub> |                                                                 | 2.70                       |        | 5.25                       | V      |

|                                     |                   |                                                                 |                            | 41     | 60                         |        |

| Analog Supply Current               | AI <sub>DD</sub>  | SHDN = 1                                                        |                            | 0.005  | 0.1                        | mA     |

|                                     |                   | STANDBY = 1, SHDN = 0                                           |                            | 4.2    | 5                          |        |

| Digital Supply Current              | DI                |                                                                 |                            | 0.001  | 3                          | μ. Λ   |

| Digital Supply Current              | DI <sub>DD</sub>  | SHDN = 1<br>STANDBY = 1, SHDN = 0                               |                            | 0.001  | 0.05<br>0.05               | mA     |

|                                     |                   |                                                                 |                            | U.UU I | 0.05                       |        |

| Digital Driver Supply Current       | DRI <sub>DD</sub> | SHDN = 1                                                        |                            | 0      | 0.05                       | mA     |

| Eignal Envol Supply Surront         |                   | STANDBY = 1, SHDN = 0                                           |                            | 0      | 0.05                       | 111/ \ |

| Analog Power-Supply Rejection       |                   | 4.75V to 5.25V (Note 1)                                         |                            | 75     |                            | dB     |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(AV_{DD} = DV_{DD} = +5.0V, DRV_{DD} = +3.0V, AGND = DGND = DRGND = 0, INTCLK/EXTCLK = AGND, f<sub>CLK</sub> = 5MHz, input range = ±10V, REFP2 = REFP1, REFN2 = REFN1, COM1 = COM2, 1.0nF from REFADC to AGND, 1.0µF and 0.1µF from COM1 to AGND, 0.1µF from REFP1 to AGND, 0.1µF from REFN1 to AGND, 1.0µF from REFP1 to REFN1. Typical values are at T<sub>A</sub> = +25°C. T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted.)$

| PARAMETER                                                  | SYMBOL            | CONDITIONS                       | MIN | ТҮР | MAX | UNITS         |  |  |

|------------------------------------------------------------|-------------------|----------------------------------|-----|-----|-----|---------------|--|--|

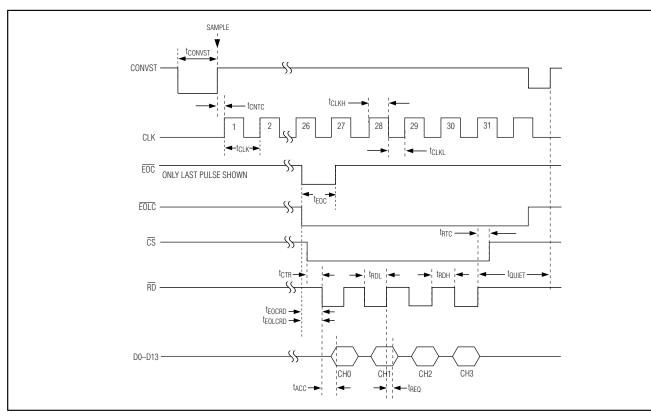

| TIMING CHARACTERISTICS (Figures 4, 5, and 6)               |                   |                                  |     |     |     |               |  |  |

|                                                            |                   | Internal clock                   | 2.9 | 3.2 | 3.5 | μs            |  |  |

| Time to First Conversion Result                            | tEOC1             | External clock                   |     | 16  |     | CLK<br>Cycles |  |  |

|                                                            |                   | Internal clock                   |     | 600 |     | ns            |  |  |

| Time to Subsequent Conversions                             | t <sub>NEXT</sub> | External clock                   |     | 3   |     | CLK<br>Cycles |  |  |

| CONVST Pulse-Width Low                                     | to 01 11 107      | Internal clock                   | 0.2 |     |     |               |  |  |

| CONVST Fulse-width Low                                     | <b>t</b> CONVST   | External clock                   | 0.1 |     |     | μs            |  |  |

| CS Pulse Width                                             | tcs               |                                  | 30  |     |     | ns            |  |  |

| RD Pulse-Width Low                                         | t <sub>RDL</sub>  |                                  | 30  |     |     | ns            |  |  |

| RD Pulse-Width High                                        | t <sub>RDH</sub>  |                                  | 30  |     |     | ns            |  |  |

| WR Pulse-Width Low                                         | twrl              |                                  | 30  |     |     | ns            |  |  |

| CS to WR Setup Time                                        | tCTW              |                                  | 0   |     |     | ns            |  |  |

| $\overline{\text{WR}}$ to $\overline{\text{CS}}$ Hold Time | twrc              |                                  | 0   |     |     | ns            |  |  |

| CS to RD Setup Time                                        | tCTR              |                                  | 0   |     |     | ns            |  |  |

| $\overline{RD}$ to $\overline{CS}$ Hold Time               | t <sub>RTC</sub>  |                                  | 0   |     |     | ns            |  |  |

| Data Access Time<br>(RD Low to Valid Data)                 | tacc              | Figure 1                         |     |     | 30  | ns            |  |  |

| Bus Relinquish Time<br>(RD High to D_ High-Z)              | treq              | Figure 1                         | 5   |     | 30  | ns            |  |  |

| CLK Rise to End-of-Conversion<br>(EOC) Rise/Fall Delay     | teocd             |                                  |     | 20  |     | ns            |  |  |

| CLK Rise to End-of-Last-<br>Conversion (EOLC) Fall Delay   | teolcd            |                                  |     | 20  |     | ns            |  |  |

| CONVST Rise to EOLC Fall Delay                             | <b>t</b> CVEOLCD  |                                  |     | 20  |     | ns            |  |  |

|                                                            | Ì                 | Internal clock                   | 180 | 200 |     | ns            |  |  |

| EOC Pulse-Width Low                                        | teoc              | External clock                   |     | 1   |     | CLK<br>Cycle  |  |  |

| Wake-Up Time From Standby                                  |                   |                                  |     | 7   |     | μs            |  |  |

| Wake-Up Time From Shutdown                                 |                   | All bypass capacitors discharged |     | 5   |     | ns            |  |  |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(AV_{DD} = DV_{DD} = +5.0V, DRV_{DD} = +3.0V, AGND = DGND = DRGND = 0, INTCLK/EXTCLK = AGND, f_{CLK} = 5MHz, input range = ±10V, REFP2 = REFP1, REFN2 = REFN1, COM1 = COM2, 1.0nF from REFADC to AGND, 1.0µF and 0.1µF from COM1 to AGND, 0.1µF from REFP1 to AGND, 0.1µF from REFN1 to AGND, 1.0µF from REFP1 to REFN1. Typical values are at T<sub>A</sub> = +25°C. T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted.)$

| PARAMETER                       | SYMBOL            | CONDITIONS                      | MIN | ТҮР  | МАХ | UNITS |

|---------------------------------|-------------------|---------------------------------|-----|------|-----|-------|

| EOC Fall to RD Fall Setup Time  | <b>t</b> EOCRD    |                                 | 0   |      |     | ns    |

| EOLC Fall to RD Fall Setup Time | <b>t</b> EOLCRD   |                                 | 0   |      |     | ns    |

| Input Data Setup Time           | t <sub>DTW</sub>  |                                 | 10  |      |     | ns    |

| Input Data Hold Time            | twtd              |                                 | 10  |      |     | ns    |

| External CLK Period             | <b>t</b> CLK      |                                 | 166 | 200  |     | ns    |

| External CLK High Period        | t <sub>CLKH</sub> | Logic sensitive to rising edges | 60  |      |     | ns    |

| External CLK Low Period         | <b>t</b> CLKL     | Logic sensitive to rising edges | 60  |      |     | ns    |

| External Clock Frequency        | fCLK              | (Note 4)                        | 1   |      | 6   | MHz   |

| Internal Clock Frequency        | fint              |                                 | 5.0 | 5.25 | 5.5 | MHz   |

| CONVST High to CLK Edge         | <b>t</b> CNTC     |                                 | 30  |      |     | ns    |

| Quiet Time                      | <b>t</b> QUIET    |                                 | 600 |      |     | ns    |

Note 1: See definition for this parameter in the *Definitions* section.

Note 2: Differential reference voltage (REFP-REFN) error nulled.

Note 3: This is the load the MAX1338 presents to an external reference at REFADC.

**Note 4:** Minimum CLK frequency is limited only by the internal T/H droop rate. Limit the time between the rising edge of CONVST to the falling edge of EOLC to a maximum of 0.25ms.

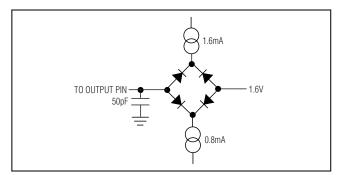

Figure 1. Load Circuit for Data Access Time and Bus-Relinquish Time

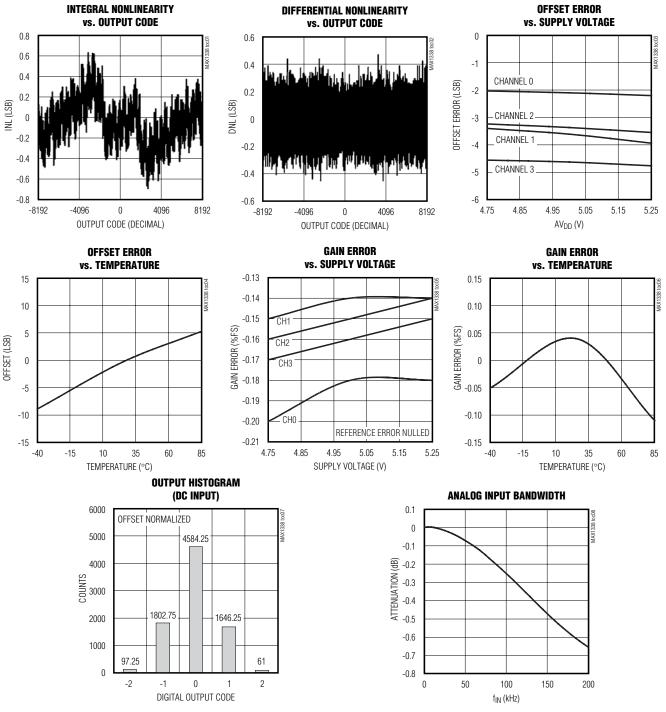

## \_Typical Operating Characteristics

$(AV_{DD} = DV_{DD} = +5.0V, DRV_{DD} = +3.0V, AGND = DGND = DRGND = 0, INTCLK/EXTCLK = AGND, f_{CLK} = 5MHz, input range = ±10V, REFP2 = REFP1, REFN2 = REFN1, COM1 = COM2, 1.0nF from REFADC to AGND, 1.0µF and 0.1µF from COM1 to AGND, 0.1µF from REFP1 to AGND, 0.1µF from REFN1 to AGND, 1.0µF from REFP1 to REFN1.)$

7

**MAX1338**

0.1µF from REFP1 to AGND, 0.1µF from REFN1 to AGND, 1.0µF from REFP1 to REFN1.)

(AV<sub>DD</sub> = DV<sub>DD</sub> = +5.0V, DRV<sub>DD</sub> = +3.0V, AGND = DGND = DRGND = 0, INTCLK/EXTCLK = AGND, f<sub>CLK</sub> = 5MHz, input range = ±10V, REFP2 = REFP1, REFN2 = REFN1, COM1 = COM2, 1.0nF from REFADC to AGND, 1.0µF and 0.1µF from COM1 to AGND,

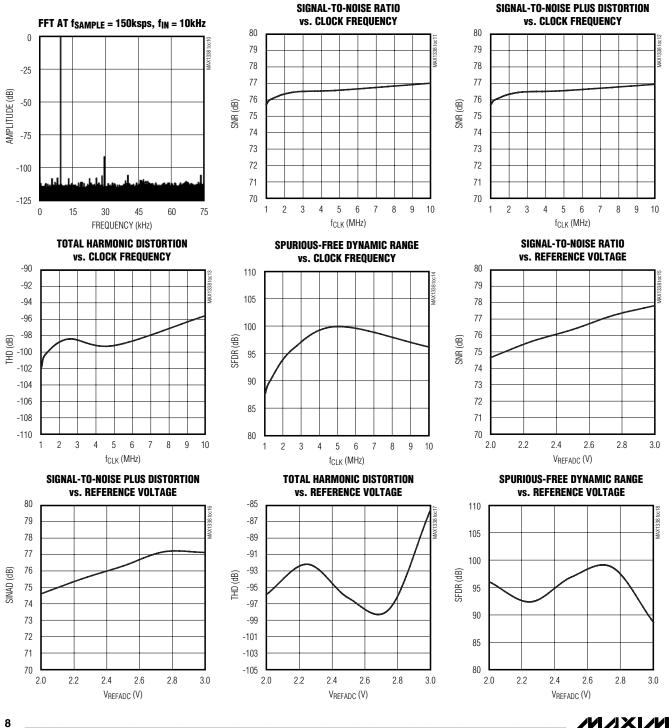

**Typical Operating Characteristics (continued)**

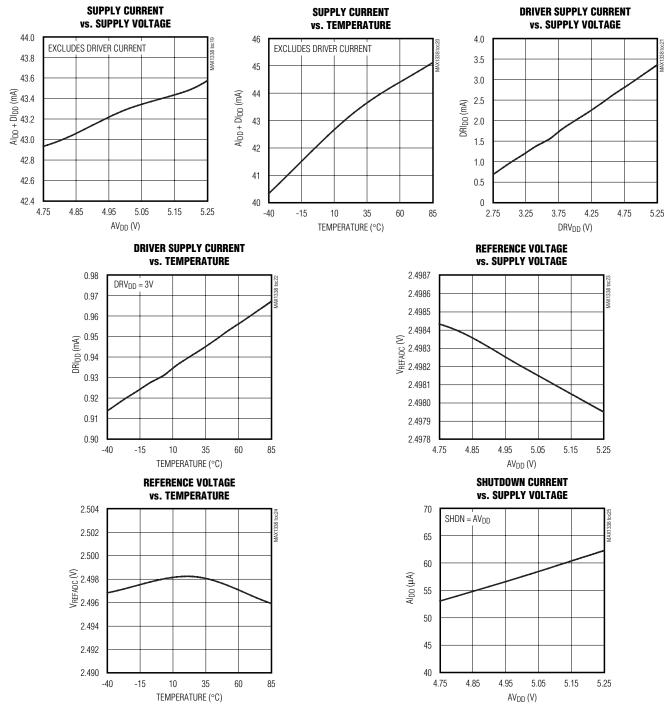

## **Typical Operating Characteristics (continued)**

$(AV_{DD} = DV_{DD} = +5.0V, DRV_{DD} = +3.0V, AGND = DGND = DRGND = 0, INTCLK/EXTCLK = AGND, f<sub>CLK</sub> = 5MHz, input range = ±10V, REFP2 = REFP1, REFN2 = REFN1, COM1 = COM2, 1.0nF from REFADC to AGND, 1.0µF and 0.1µF from COM1 to AGND, 0.1µF from REFN1 to AGND, 1.0µF from REFP1 to REFN1.)$

MAX1338

///XI/M

#### SHUTDOWN CURRENT **STANDBY CURRENT** vs. TEMPERATURE vs. SUPPLY VOLTAGE 70 4.30 SHDN = AV<sub>DD</sub> $\dot{STANDBY} = AV_{DD}$ 65 4.25 60 4.20 (W) 001 (W) 00 Alpp (µA) 55 50 4.10 45 4.05 40 4.00 -40 -15 85 10 35 60 4.85 5.05 5.15 5.25 4.75 4.95 TEMPERATURE (°C) $AV_{DD}(V)$ **STANDBY CURRENT CONVERSION TIME** vs. TEMPERATURE vs. SUPPLY VOLTAGE 4.30 5.8 STANDBY = AV<sub>DD</sub> INTERNAL CLOCK 4.25 5.6 CONVERSION TIME (µs) 4 20 (YW) 0014.15 5.4 5.2 4.10 5.0 4.05 4.00 4.8 -40 -15 10 35 60 85 4.85 4.75 4.95 5.05 5.15 5.25 TEMPERATURE (°C) AV<sub>DD</sub> (V) ANALOG INPUT CURRENT **CONVERSION TIME** vs. TEMPERATURE vs. ANALOG INPUT VOLTAGE 4 5.8 INTERNAL CLOCK 3 5.6 2 CONVERSION TIME (µs) INPUT CURRENT (mA) 1 5.4 0 5.2 -1 -2 5.0 -3 4.8 -4 -40 -17.0 -8.5 0 -15 10 35 60 85 8.5 17.0 INPUT VOLTAGE (V) TEMPERATURE (°C)

## **Typical Operating Characteristics (continued)**

$(AV_{DD} = DV_{DD} = +5.0V, DRV_{DD} = +3.0V, AGND = DGND = DRGND = 0, INTCLK/EXTCLK = AGND, f_{CLK} = 5MHz, input range = ±10V, REFP2 = REFP1, REFN2 = REFN1, COM1 = COM2, 1.0nF from REFADC to AGND, 1.0µF and 0.1µF from COM1 to AGND, 0.1µF from REFN1 to AGND, 1.0µF from REFP1 to REFN1.)$

10

## \_Pin Description

| PIN                         | NAME                                                                                                                                                                                                                                                                                                               | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 7, 9, 17,<br>19          | AV <sub>DD</sub>                                                                                                                                                                                                                                                                                                   | Analog Power Input. AV <sub>DD</sub> is the power input for the analog section of the converter. Connect a +4.75V to +5.25V power supply to AV <sub>DD</sub> . Bypass each AV <sub>DD</sub> to AGND with a 0.1 $\mu$ F capacitor very close to the device. Bypass AV <sub>DD</sub> to AGND with a bulk capacitor of at least 4.7 $\mu$ F where power enters the board. Connect all AV <sub>DD</sub> pins to the same potential. |

| 2                           | AIN0+                                                                                                                                                                                                                                                                                                              | Channel 0 Differential Analog Input                                                                                                                                                                                                                                                                                                                                                                                             |

| 3                           | AIN0-                                                                                                                                                                                                                                                                                                              | Channel 0 Differential Analog Input                                                                                                                                                                                                                                                                                                                                                                                             |

| 4                           | AIN1+                                                                                                                                                                                                                                                                                                              | Channel 1 Differential Analog Input                                                                                                                                                                                                                                                                                                                                                                                             |

| 5                           | AIN1-                                                                                                                                                                                                                                                                                                              | Channel 1 Differential Analog Input                                                                                                                                                                                                                                                                                                                                                                                             |

| 6, 8, 14, 16,<br>18, 20, 28 | AGND                                                                                                                                                                                                                                                                                                               | Analog Ground. AGND is the power return for AV <sub>DD</sub> . Connect all AGNDs to the same potential.                                                                                                                                                                                                                                                                                                                         |

| 10                          | AIN2+                                                                                                                                                                                                                                                                                                              | Channel 2 Differential Analog Input                                                                                                                                                                                                                                                                                                                                                                                             |

| 11                          | AIN2-                                                                                                                                                                                                                                                                                                              | Channel 2 Differential Analog Input                                                                                                                                                                                                                                                                                                                                                                                             |

| 12                          | AIN3+                                                                                                                                                                                                                                                                                                              | Channel 3 Differential Analog Input                                                                                                                                                                                                                                                                                                                                                                                             |

| 13                          | AIN3-                                                                                                                                                                                                                                                                                                              | Channel 3 Differential Analog Input                                                                                                                                                                                                                                                                                                                                                                                             |

| 15                          | INTCLK/<br>EXTCLK                                                                                                                                                                                                                                                                                                  | Clock-Select Input. Force INTCLK/EXTCLK high for internal clock mode. Force INTCLK/EXTCLK low for external clock mode.                                                                                                                                                                                                                                                                                                          |

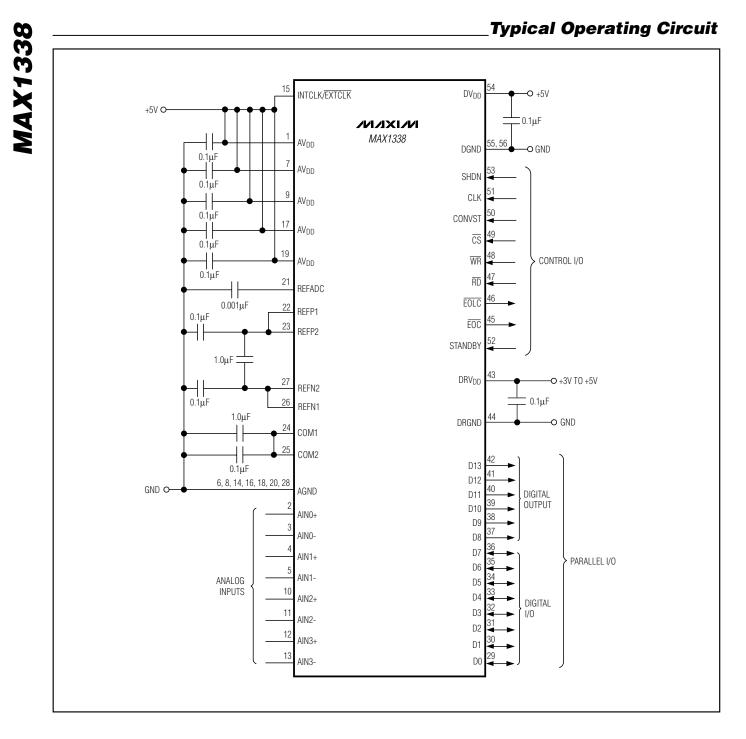

| 21                          | ADC Reference Bypass or Input. REFADC is the bypass point for an internally generated refere<br>REFADC voltage. Bypass REFADC with a 1.0nF capacitor to AGND. REFADC can be driven externally by<br>precision external voltage reference. See the <i>Reference</i> section and the <i>Typical Operating Circle</i> |                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 22                          | REFP1                                                                                                                                                                                                                                                                                                              | Positive Differential Reference Bypass Point 1. Connect REFP1 to REFP2.                                                                                                                                                                                                                                                                                                                                                         |

| 23                          | REFP2                                                                                                                                                                                                                                                                                                              | Positive Differential Reference Bypass Point 2. Connect REFP2 to REFP1. Bypass REFP2 with a 0.1µF capacitor to AGND. Also bypass REFP2 to REFN2 with a 0.1µF capacitor.                                                                                                                                                                                                                                                         |

| 24                          | COM1                                                                                                                                                                                                                                                                                                               | Common-Mode Voltage Bypass Point 1. Connect COM1 to COM2.                                                                                                                                                                                                                                                                                                                                                                       |

| 25                          | COM2                                                                                                                                                                                                                                                                                                               | Common-Mode Voltage Bypass Point 2. Connect COM2 to COM1. Connect a 1.0µF capacitor from COM2 to AGND.                                                                                                                                                                                                                                                                                                                          |

| 26                          | REFN1                                                                                                                                                                                                                                                                                                              | Negative Differential Reference Bypass Point 1. Connect REFN1 to REFN2.                                                                                                                                                                                                                                                                                                                                                         |

| 27                          | REFN2                                                                                                                                                                                                                                                                                                              | Negative Differential Reference Bypass Point 2. Connect REFN2 to REFN1. Bypass REFN2 with a 0.1µF capacitor to AGND. Also bypass REFN2 to REFP2 with a 0.1µF capacitor.                                                                                                                                                                                                                                                         |

| 29                          | D0                                                                                                                                                                                                                                                                                                                 | Data Input/Output Bit 0 (LSB)                                                                                                                                                                                                                                                                                                                                                                                                   |

| 30                          | D1                                                                                                                                                                                                                                                                                                                 | Data Input/Output Bit 1                                                                                                                                                                                                                                                                                                                                                                                                         |

| 31                          | D2                                                                                                                                                                                                                                                                                                                 | Data Input/Output Bit 2                                                                                                                                                                                                                                                                                                                                                                                                         |

| 32                          | D3                                                                                                                                                                                                                                                                                                                 | Data Input/Output Bit 3                                                                                                                                                                                                                                                                                                                                                                                                         |

| 33                          | D4                                                                                                                                                                                                                                                                                                                 | Data Input/Output Bit 4                                                                                                                                                                                                                                                                                                                                                                                                         |

| 34                          | D5                                                                                                                                                                                                                                                                                                                 | Data Input/Output Bit 5                                                                                                                                                                                                                                                                                                                                                                                                         |

| 35                          | D6                                                                                                                                                                                                                                                                                                                 | Data Input/Output Bit 6                                                                                                                                                                                                                                                                                                                                                                                                         |

| 36                          | D7                                                                                                                                                                                                                                                                                                                 | Data Input/Output Bit 7                                                                                                                                                                                                                                                                                                                                                                                                         |

| 37                          | D8                                                                                                                                                                                                                                                                                                                 | Data Output Bit 8                                                                                                                                                                                                                                                                                                                                                                                                               |

| 38                          | D9                                                                                                                                                                                                                                                                                                                 | Data Output Bit 9                                                                                                                                                                                                                                                                                                                                                                                                               |

| 39                          | D10                                                                                                                                                                                                                                                                                                                | Data Output Bit 10                                                                                                                                                                                                                                                                                                                                                                                                              |

| 40                          | D11                                                                                                                                                                                                                                                                                                                | Data Output Bit 11                                                                                                                                                                                                                                                                                                                                                                                                              |

## **Pin Description (continued)**

| PIN    | NAME              | FUNCTION                                                                                                                                                                                                                                                                             |  |  |  |  |

|--------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 41     | D12               | Data Output Bit 12                                                                                                                                                                                                                                                                   |  |  |  |  |

| 42     | D13               | Data Output Bit 13 (MSB)                                                                                                                                                                                                                                                             |  |  |  |  |

| 43     | DRV <sub>DD</sub> | Digital I/O Power-Supply Input. DRV <sub>DD</sub> is the power input for the digital I/O buffers and drivers. Connect a +2.7V to +5.25V power supply to DRV <sub>DD</sub> . Bypass DRV <sub>DD</sub> to DRGND with a $0.1\mu$ F capacitor very close to the device.                  |  |  |  |  |

| 44     | DRGND             | Driver Ground. DRGND is the power-supply return for DRV <sub>DD</sub> .                                                                                                                                                                                                              |  |  |  |  |

| 45     | EOC               | End-of-Conversion Output. EOC goes low to indicate the end of a conversion. EOC returns high after one clock period.                                                                                                                                                                 |  |  |  |  |

| 46     | EOLC              | End-of-Last-Conversion Output. EOLC goes low to indicate the end of the last conversion. EOLC returns high when CONVST goes low for the next conversion sequence.                                                                                                                    |  |  |  |  |

| 47     | RD                | Read Input. Forcing $\overline{RD}$ low initiates a read command of the parallel data bus, D0–D13. D0–D13 are high impedance while either $\overline{RD}$ or $\overline{CS}$ is high.                                                                                                |  |  |  |  |

| 48     | WR                | Write Input. Forcing WR low initiates a write command for configuring the device through D0-D7.                                                                                                                                                                                      |  |  |  |  |

| 49     | CS                | Chip-Select Input. Forcing $\overline{CS}$ low activates the digital interface. D0–D13 are high impedance while either $\overline{CS}$ or $\overline{RD}$ is high.                                                                                                                   |  |  |  |  |

| 50     | CONVST            | Convert Start Input. CONVST initiates the conversion process. The analog inputs are sampled on the rising edge of CONVST.                                                                                                                                                            |  |  |  |  |

| 51     | CLK               | External-Clock Input. CLK accepts a 1MHz to 6MHz external clock signal. For externally clocked conversions, apply the clock signal to CLK and force INTCLK/EXTCLK low. For internally clocked conversions, connect CLK to DGND and force INTCLK/EXTCLK high.                         |  |  |  |  |

| 52     | STANDBY           | Standby-Control Input. Forcing STANDBY high partially powers down the device but leaves all the reference-related circuitry alive. Use STANDBY instead of SHDN when quick wake-up is required.                                                                                       |  |  |  |  |

| 53     | SHDN              | Shutdown-Control Input. Force SHDN high to place the device into full shutdown. When in full shutdown, all circuitry within the device is powered down and all reference capacitors are allowed to discharge. Allow 1ms for wake-up from full shutdown before starting a conversion. |  |  |  |  |

| 54     | DV <sub>DD</sub>  | Digital Power-Supply Input. DV <sub>DD</sub> is the power input for the digital circuitry. Connect a +4.75V to +5.25V power supply to DV <sub>DD</sub> . Bypass DV <sub>DD</sub> to DGND with a $0.1\mu$ F capacitor very close to the device.                                       |  |  |  |  |

| 55, 56 | DGND              | Digital Ground. Power return for DV <sub>DD</sub> .                                                                                                                                                                                                                                  |  |  |  |  |

| _      | EP                | Exposed Pad. Connect to AGND.                                                                                                                                                                                                                                                        |  |  |  |  |

## **Detailed Description**

The MAX1338 simultaneously samples four differential analog inputs with internal T/H circuits, and sequentially converts them to a digital code with a 14-bit ADC. Output data is provided by a 14-bit parallel interface. At power-up, all channels default to a  $\pm$ 10V input range. Program different input ranges ( $\pm$ 10V,  $\pm$ 5V,  $\pm$ 2.5V, or  $\pm$ 1.25V) using the configuration register. Different input ranges between  $\pm$ 12V and  $\pm$ 1.0V are realized using an

external reference. All channels offer input protection to  $\pm 17V$ , independent of the selected input range.

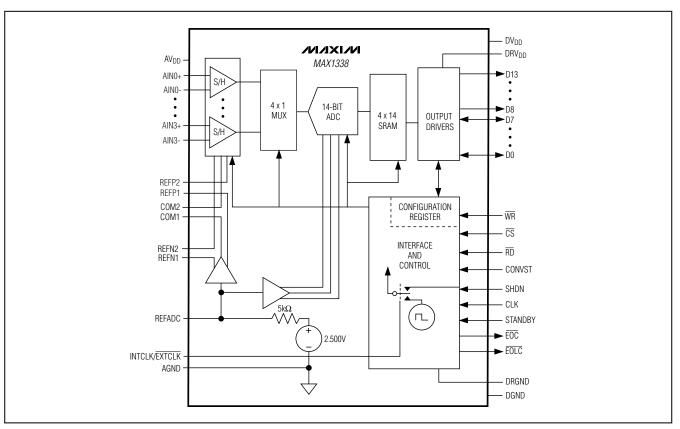

The internal clock operates the ADC at 5MHz, or uses an external conversion clock from 1MHz to 6MHz. EOC goes low when the result of each conversion is available, and EOLC goes low when the last conversion result is available. Standby and shutdown modes, selectable through logic-control inputs, save power between conversions. Figure 2 shows a block diagram of the MAX1338.

Figure 2. Functional Diagram

#### **Power-Supply Inputs**

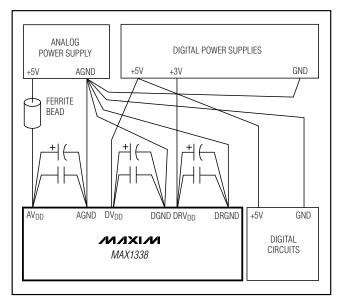

Three separate power supplies power the MAX1338. A +5V analog supply, AV<sub>DD</sub>, powers the analog input and converter sections. A +5V digital supply, DV<sub>DD</sub>, powers the internal logic circuitry, and a +2.7V to +5V digital supply (DRV<sub>DD</sub>), powers the parallel I/O and the control I/O (see the *Typical Operating Circuit*). Bypass the power supplies as indicated in the *Layout, Grounding, and Bypassing* section. Power-supply sequencing is not required for the MAX1338.

#### **Analog Inputs**

#### Software-Selectable Input Range

The MAX1338 provides four independent, softwareselectable, analog input voltage ranges for each channel. The selectable input ranges are  $\pm V_{REF} \times 4$  (the power-up default condition),  $\pm V_{REF} \times 2$ ,  $\pm V_{REF}$ , and  $\pm V_{REF} \times 0.5$ . Using the 2.5V internal reference, the selectable input ranges are  $\pm 10V$  (power-up default),  $\pm 5V$ ,  $\pm 2.5V$ , and  $\pm 1.25V$ . Program the analog input ranges with the configuration register through the

parallel I/O. See the *Configuration Register* section for programming details.

#### Input Protection

MAX1338

Protection at the analog inputs provides  $\pm 17V$  fault immunity for the MAX1338. This protection circuit limits the current at the analog inputs to less than  $\pm 2mA$ . Input fault protection is active in standby, in shutdown, during normal operation, and over all input ranges.

#### Track and Hold (T/H)

To preserve relative phase information between input channels, each input channel has a dedicated T/H amplifier. The rising edge of CONVST represents the sampling instant for all channels. All samples are taken within an aperture delay ( $t_{AD}$ ) of 16ns. The aperture delay of all channels is matched to within 100ps.

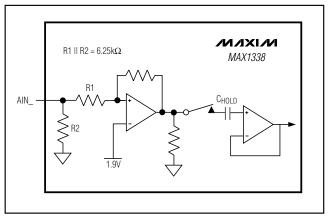

Figure 3 shows the equivalent analog input T/H circuit for one analog input.

As conversion begins, the T/H circuits hold the analog signals. After the 12th clock cycle (or  $2.4\mu s$  in internal clock mode) into the conversion process, the last analog input sample begins shifting through the converter, and the T/H circuits begin to track the analog inputs again in preparation for the next CONVST rising edge.

Due to the resistive load presented by the analog inputs, any significant analog input source resistance, RSOURCE, increases gain error. Limit RSOURCE to a maximum of  $20\Omega$  to limit the effect to less than 0.1%. Drive the input with a wideband buffer (>1MHz) that can drive the ADC's input impedance.

#### Selecting an Input Buffer

Most applications require an input buffer to achieve 14bit accuracy. Although slew rate and bandwidth are important, the most critical specification is output impedance. Use a low-noise, low-distortion amplifier with low output impedance, for best gain-accuracy performance.

#### Input Bandwidth

The input-tracking circuitry has a 1MHz small-signal bandwidth. To avoid high-frequency signals being aliased into the frequency band of interest, anti-alias filtering is recommended.

#### **Data Throughput**

The data throughput ( $f_{TH}$ ) of the MAX1338 is a function of the clock speed ( $f_{CLK}$ ). The MAX1338 operates from a 5MHz internal clock or an external clock between 1MHz and 6MHz. For fastest throughput, read the conversion result during conversion (Figure 5), and calculate data throughput using:

$$f_{TH} = \frac{1}{t_{QUIET} + \frac{26}{f_{CLK}}}$$

where  $t_{\mbox{QUIET}}$  is the period of bus inactivity before the rising edge of CONVST.

#### Clock Modes

The MAX1338 provides an internal clock of 5MHz. Alternatively, use an external clock of 1MHz to 6MHz.

Figure 3. Simplified Typical Input Circuit

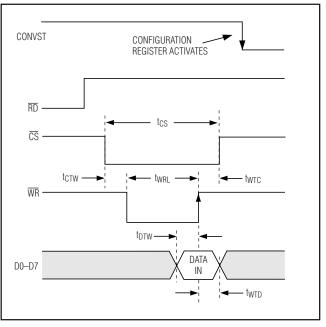

Figure 4. Write Timing

#### Internal Clock

Internal clock mode frees the microprocessor from the burden of running the ADC conversion clock. For internal-clock operation, connect INTCLK/ $\overline{\text{EXTCLK}}$  to AV<sub>DD</sub> and CLK to DRGND. Note that INTCLK/ $\overline{\text{EXTCLK}}$  is referenced to the analog power supply, AV<sub>DD</sub>. Total conversion time for all four channels using the internal clock is 6µs (typ).

#### External Clock

For external clock operation, force INTCLK/EXTCLK low and connect an external clock source to CLK. Use an external clock frequency from 1MHz to 6MHz with a duty cycle between 40% and 60%. Choose a minimum clock frequency of 1MHz to prevent linearity errors caused by excessive droop in the T/H circuits.

## Applications Sections

#### **Power-On Reset**

At power-up, all channels default to a  $\pm 10V$  input range. After applying power, allow a 1ms wake-up time to elapse and perform one dummy conversion before initiating first conversion.

#### **Power Saving**

#### Full Shutdown

During shutdown, the analog and digital circuits in the MAX1338 power down and the device draws less than 0.06mA from  $AV_{DD}$ , and less than 10µA from  $DV_{DD}$ . Select shutdown mode using the SHDN input. Force SHDN high to enter shutdown mode. When coming out of shutdown, allow the 1ms wake-up and then perform one dummy conversion before making the first conversion.

#### Standby

Standby is similar to shutdown but the reference circuits remain powered up, allowing faster wake-up. Enter standby by forcing STANDBY high. After coming out of standby, perform a dummy conversion before making the first conversion.

#### **Digital Interface**

The digital interface consists of two sections: a control I/O section and a parallel I/O section. The control I/O section includes the following control signals: chip select  $(\overline{CS})$ , read  $(\overline{RD})$ , write  $(\overline{WR})$ , end of conversion  $(\overline{EOC})$ , end of last conversion  $(\overline{EOLC})$ , convert start (CONVST), power-down (SHDN), standby (STANDBY), and external-clock input (CLK).

The bidirectional parallel I/O section sets the 8-bit input range configuration register using D0–D7 (see the *Configuration Register* section) and outputs the 14-bit conversion result using D0–D13. The I/O operations are controlled by the control I/O signals  $\overline{RD}$ ,  $\overline{WR}$ , and  $\overline{CS}$ . All parallel I/O bits are high impedance when either  $\overline{RD} = 1$  or  $\overline{CS} = 1$ . Figures 4, 5, and 6 and the *Timing Characteristics* section detail the operation of the digital interface.

## Table 1. Configuration Register

| I/O LINE | REGISTER<br>NAME | FUNCTION                            |  |

|----------|------------------|-------------------------------------|--|

| D0       | CH0R0            | Channel 0 input range setting bit 0 |  |

| D1       | CH0R1            | Channel 0 input range setting bit 1 |  |

| D2       | CH1R0            | Channel 1 input range setting bit 0 |  |

| D3       | CH1R1            | Channel 1 input range setting bit 1 |  |

| D4       | CH2R0            | Channel 2 input range setting bit 0 |  |

| D5       | CH2R1            | Channel 2 input range setting bit 1 |  |

| D6       | CH3R0            | Channel 3 input range setting bit 0 |  |

| D7       | CH3R1            | Channel 3 input range setting bit 1 |  |

#### **Table 2. Input-Range Register Settings**

|       | STER<br>TING | SELECTED INPUT<br>RANGE | ALLOWABLE<br>COMMON-MODE |

|-------|--------------|-------------------------|--------------------------|

| CH_R0 | CH_R1        | Incide                  | RANGE                    |

| 0     | 0            | -10V to +10V            | ±5V                      |

| 0     | 1            | -5V to +5V              | ±2.5V                    |

| 1     | 0            | -2.5V to +2.5V          | ±1.25V                   |

| 1     | 1            | -1.25V to +1.25V        | ±0.625V                  |

#### **Configuration Register**

The MAX1338 uses an 8-bit configuration word to set the input range for each channel. Table 1 and Table 2 describe the configuration word and the input-range settings.

Write to the configuration register by forcing  $\overline{CS}$  and  $\overline{WR}$  low, loading bits D0–D7 onto the parallel bus, and then forcing  $\overline{WR}$  high. The configuration bits are latched on the rising edge of  $\overline{WR}$  (Figure 4). It is possible to write to the configuration register at any point during the conversion sequence. However, it will not be active until the next convert-start signal. At power-up, the configuration register contains all zeros, making all channels default to the maximum input range, -10V to +10V. Shutdown and standby do not change the configuration register, but the configuration register can be programmed while the MAX1338 is in shutdown or standby modes.

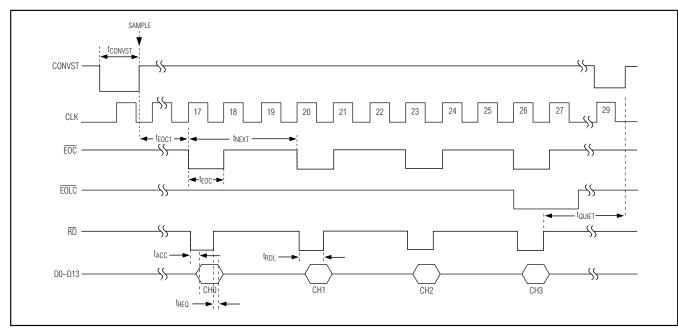

Figure 5. Reading During a Conversion—Internal or External Clock

## Starting a Conversion

#### Internal Clock

For internal clock operation, force INTCLK/EXTCLK high. To start a conversion using internal clock mode, pull CONVST low for at least t<sub>CONVST</sub>. The T/H acquires the signal while CONVST is low. An EOC signal pulses low when the first result becomes available, and for each subsequent result until the end of the conversion cycle. The EOLC signal goes low when the last conversion result becomes available (Figure 6).

#### External Clock

For external clock operation, force INTCLK/EXTCLK low. To start a conversion using external clock mode, pull CONVST low for at least t<sub>CONVST</sub>. The T/H circuits track the input signal while CONVST is low. Conversion begins on the rising edge of CONVST. Apply an external clock to CLK. To avoid T/H droop degrading the sampled analog input signals, the first CLK pulse must occur within 10µs after the rising edge of CONVST and have a minimum 1MHz clock frequency. The first conversion result is available for read on the rising edge of the 17th clock cycle, and subsequent conversions on every 3rd clock cycle thereafter, as indicated by EOC and EOLC.

#### **Reading a Conversion Result**

#### Reading During a Conversion

Figure 5 shows the interface signals to initiate a read operation during a conversion cycle. CS can be held low permanently, low during the RD cycles, or it can be the same as RD. After initiating a conversion by bringing CONVST high, wait for EOC to go low (about 3.4µs in internal clock mode) or 17 clock cycles (external clock mode) before reading the first conversion result. Read the conversion result by bringing RD low, which latches the data to the parallel digital output bus. Bring RD high to release the digital bus. Wait for the next falling edge of EOC (about 600ns in internal clock mode or three clock cycles in external clock mode) before reading the next result. When the last result is available, EOLC goes low, along with EOC. Wait three clock cycles, tQUIET, before starting the next conversion cycle.

#### **Reading After a Conversion**

Figure 6 shows the interface signals for a read operation after a conversion using an external clock. At the falling of EOLC, on the 26th clock pulse after the initiation of a conversion, driving  $\overline{CS}$  and  $\overline{RD}$  low places the first conversion result onto the parallel I/O bus. Read the conversion result on the rising edge of  $\overline{RD}$ . Successive low pulses of  $\overline{RD}$  place the successive conversion results

Figure 6. Reading After a Conversion—External Clock

onto the bus. After reading all four channels, bring  $\overline{CS}$  high to release the parallel I/O. After waiting tquiet, pulse CONVST low to initiate the next conversion.

#### Reference

Bypass the reference inputs as indicated in Table 3.

#### Internal Reference

The internal reference supports all input ranges for the MAX1338.

#### External Reference

Implement external-reference operation by overdriving the internal reference voltage. Override the internal reference voltage by connecting a 2.0V to 3.0V external reference at REF. The REF input impedance is typically  $5k\Omega$ . For more information about using an external reference, see the *Transfer Functions* section.

## **Table 3. Reference Bypass Capacitors**

| LOCATION                        | BYPASS<br>CAPACITORS |

|---------------------------------|----------------------|

| REFADC bypass capacitor to AGND | 1nF                  |

| REFP1 bypass capacitor to AGND  | 0.1µF                |

| REFN1 bypass capacitor to AGND  | 0.1µF                |

| REFP1 to REFN1 capacitor        | 1.0µF                |

| COM1 bypass capacitor to AGND   | 1.0µF    0.1µF       |

#### **Transfer Functions**

#### **Digital Correction**

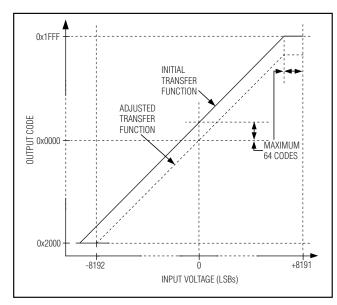

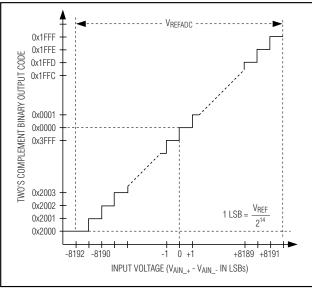

Factory trim procedures digitally shift the transfer function to reduce bipolar zero-code offset to less than  $\pm 4$  LSBs (typ). Depending on initial conditions, the transfer function is shifted up or down, as required. The maximum shift that any transfer function experiences is 64 codes, which can have a small effect at the extremes of the transfer function, as shown in Figure 7.

# MAX1338

Figure 7. Example of Digitally Adjusted Transfer Function— Shifted Down to Minimize Zero-Code Offset

#### Input Range Settings

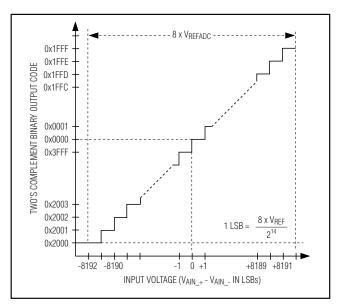

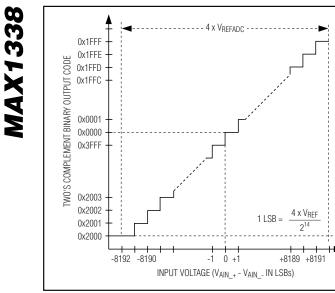

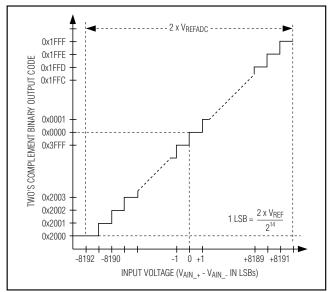

Table 4 shows the two's complement output for a selection of inputs.

The full-scale input range (FSR) depends on the selected range, and the voltage at REF, as shown in Table 5. Also shown in Table 5 are the allowable common-mode ranges for the differential inputs.

Calculate the LSB size using:

$$1 \text{ LSB} = \frac{A \times V_{\text{REFADC}}}{2^{14}}$$

where A = gain multiplier for the selected input range, from Table 6.

Determine the input voltage as a function of  $\mathsf{V}_{\mathsf{REF}},$  and the output code using:

$$V_{AIN_{+}} - V_{AIN_{-}} = V_{REFADC} \times A \times \frac{CODE}{2^{14}}$$

where A = gain multiplier for the selected input range, from Table 6.

Figures 8, 9, 10, and 11 show the transfer functions for the four selectable input ranges.

Figure 8. ±10V Transfer Function

## Applications Information

#### Layout, Grounding, and Bypassing

For best performance, the board layout must follow some simple guidelines. Separate the control I/O and parallel I/O signals from the analog signals, and run the clock signals separate from everything. Do not run analog and digital (especially clock) lines parallel to one another, or digital lines underneath the ADC package. Run the parallel I/O signals together as a bundle.