19-5293; Rev 1; 3/11

EVALUATION KIT AVAILABLE

# **USB Host Charger Identification Analog Switches**

## **General Description**

The MAX14566E/MAX14566AE/MAX14566BE are sec-

ond-generation USB devices that combine Hi-Speed

USB analog switches with a USB host charger (dedicated

charger) identification circuit. These devices support both

the latest USB Battery Charging Specification Revision 1.2 including data contact detection and a set resistor bias

for Apple-compliant devices as well as legacy USB D+/D-

short detection using data line pullup. The MAX14566E

has a pMOSFET open-drain control output (CEN) and the MAX14566AE has an nMOSFET open-drain control output

(CEN) to restart the peripheral connected to the USB host.

These devices feature high-performance Hi-Speed USB

switches with low 4pF (typ) on-capacitance and low  $4.0\Omega$

(typ) on-resistance. In addition, the devices feature a single digital input (CB) to switch between pass-through

mode and autodetection charger mode. The USB host charger identification circuit allows a host USB port to

support USB chargers with shorted DP/DM detection

and to provide support for Apple-compliant devices

using a resistor bias on USB data lines. When an Applecompliant device is attached to the port in autodetection

charger mode, the devices supply the voltage to the DP

and DM lines from the internal resistor-divider. If a USB Revision 1.2-compliant device is attached, the devices short DP and DM to allow correct charger detection. The MAX14566BE features an additional digital input (CB1)

These devices have enhanced, high electrostatic discharge (ESD) protection on the DP and DM inputs up

to ±15kV Human Body Model (HBM). All the devices

are available in an 8-pin (2mm x 2mm) TDFN package,

and are specified over the -40°C to +85°C extended

to allow forced charger mode.

temperature range.

### **Features**

- Hi-Speed USB Switching

- Low 4.0pF (typ) On-Capacitance

- + Low 4.0Ω (typ) On-Resistance

- Ultra-Low 0.1Ω (typ) On-Resistance Flatness

- + +2.8V to +5.5V Supply Range

- Ultra-Low 3µA (typ) Supply Current

- Automatic Current-Limit Switch Control

- Automatic USB Charger Identification Circuit

- ◆ ±15kV High ESD HBM Protection On DP/DM

- 2mm x 2mm, 8-Pin TDFN Package

- ♦ -40°C to +85°C Operating Temperature Range

#### Applications

#### Laptops

Netbooks

Universal Charger including iPod®/iPhone® Chargers

#### Ordering Information/ Selector Guide

| PART           | PIN-<br>PACKAGE | CLS<br>CONTROL | TOP<br>MARK |

|----------------|-----------------|----------------|-------------|

| MAX14566EETA+  | 8 TDFN-EP*      | CEN            | ADJ         |

| MAX14566AEETA+ | 8 TDFN-EP*      | CEN            | ADK         |

| MAX14566BEETA+ | 8 TDFN-EP*      |                | BMR         |

**Note:** All devices are specified over the -40°C to +85°C operating temperature range.

+Denotes a lead(Pb)-free/RoHS-compliant package.

\*EP = Exposed pad.

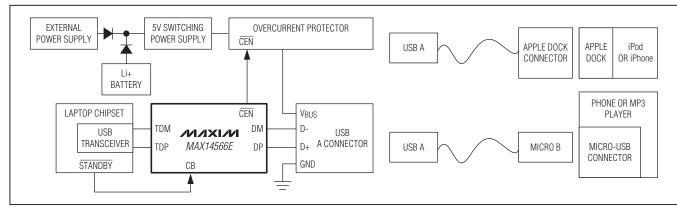

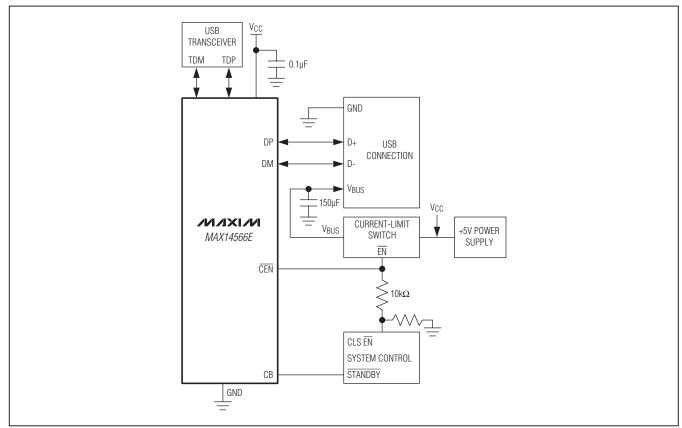

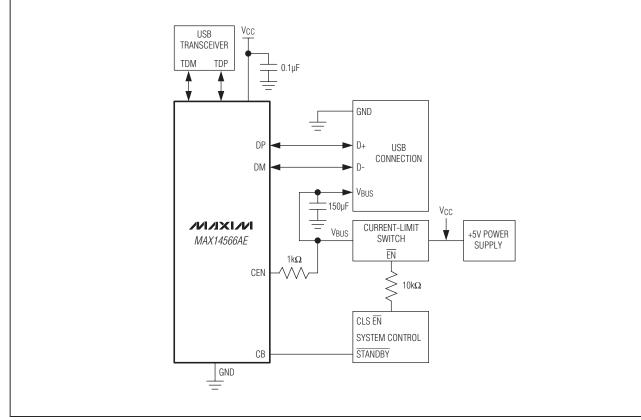

## **Typical Operating Circuit**

iPhone and iPod are registered trademarks of Apple, Inc.

####

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

2,

### **ABSOLUTE MAXIMUM RATINGS**

(All voltages referenced to GND.)

| o +6.0V |

|---------|

| ±30mA   |

|         |

| 954mW   |

|         |

| Operating Temperature Range       | 40°C to +85°C  |

|-----------------------------------|----------------|

| Junction Temperature              | +150°C         |

| Storage Temperature Range         | 65°C to +150°C |

| Lead Temperature (soldering, 10s) | +300°C         |

| Soldering Temperature (reflow)    | +260°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## PACKAGE THERMAL CHARACTERISTICS (Note 1)

TDFN

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a fourlayer board. For detailed information on package thermal considerations, refer to <u>www.maxim-ic.com/thermal-tutorial</u>.

## **ELECTRICAL CHARACTERISTICS**

(VCC = 2.8V to 5.5V, TA = TMIN to TMAX, unless otherwise noted. Typical values are at VCC = 5.0V, TA = +25°C.) (Note 2)

| PARAMETER               | SYMBOL        | CONDITIONS                                                                             |                                                    | MIN  | ТҮР | MAX  | UNITS |

|-------------------------|---------------|----------------------------------------------------------------------------------------|----------------------------------------------------|------|-----|------|-------|

| POWER SUPPLY (MAX14566  | E/MAX14566AE) |                                                                                        |                                                    |      |     |      |       |

| Power Supply Popgo      | Vee           | V <sub>CB</sub> > V <sub>IH</sub>                                                      |                                                    | 2.8  |     | 5.5  | V     |

| Power-Supply Range      | Vcc           | VCB = 0V (Note 3)                                                                      |                                                    | 4.75 |     | 5.25 | V     |

|                         |               |                                                                                        | V <sub>CC</sub> = 3.3V                             |      |     | 2    |       |

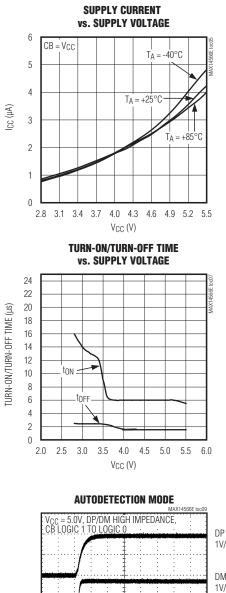

| Supply Current          |               | VCB = VCC                                                                              | $V_{CC} = 5.5V$                                    |      |     | 7    |       |

| Supply Current          | ICC           | VCB = 0V                                                                               | $V_{CC} = 4.75V$                                   |      | 110 | 200  | μA    |

|                         |               | ACB = 0A                                                                               | $V_{CC} = 5.25V$                                   |      | 120 | 200  |       |

| Supply Current Increase | ΔICC          | $0 \le V_{CB} \le V_{IL}$ or V                                                         | $IH \le VCB \le VCC$                               |      |     | 2    | μA    |

| POWER SUPPLY (MAX14566  | BE)           |                                                                                        |                                                    |      |     |      |       |

| Power-Supply Range      | Vcc           | $V_{CB} = V_{CC}$ and $V_{CB1}$<br>and $V_{CB1} = 0V$ or $V_{CB1} = V_{CC}$            | B1 = VCC or VCB = VCC<br>VCB = 0V and              | 2.8  |     | 5.5  | V     |

|                         |               | $V_{CB} = 0V$ and $V_{CB1} = 0V$ (Note 3)                                              |                                                    | 4.75 |     | 5.25 | V     |

|                         |               | $V_{CB} = V_{CC}$ and $V_{CB1} = V_{CC}$ or                                            | $V_{CC} = 3.3V$                                    |      |     | 2    |       |

|                         |               | $V_{CB} = V_{CC}$ and $V_{CB1} = 0V$                                                   | $V_{CC} = 5.5V$                                    |      |     | 7    | μΑ    |

| Supply Current          | ICC           | $V_{CB} = 0V$ and                                                                      | $V_{CC} = 4.75V$                                   |      | 110 | 200  |       |

|                         |               | VCB1 = 0V                                                                              | $V_{CC} = 5.25V$                                   |      | 120 | 200  |       |

|                         |               | VCB = 0V and<br>VCB1 = VCC                                                             | $V_{CC} = 5.0V$ for TYP<br>$V_{CC} = 5.5V$ for MAX |      | 3   | 7    |       |

|                         | 4100          | $V_{CB1} = 0V; 0 \le V_{CB} \le V_{IL}$<br>and $V_{IH} \le V_{CB} \le V_{CC}$ (Note 4) |                                                    |      | 1   |      |       |

| Supply Current Increase | ΔICC          | $V_{CB} = 0V; 0 \le V_{CE}$<br>and $V_{IH} \le V_{CB1} \le$                            |                                                    |      | 1   |      | μA    |

### ELECTRICAL CHARACTERISTICS (continued)

(VCC = 2.8V to 5.5V, TA = TMIN to TMAX, unless otherwise noted. Typical values are at VCC = 5.0V, TA = +25°C.) (Note 2)

| PARAMETER                                              | SYMBOL                           | CONDITIONS                                                                                                            | MIN   | TYP  | MAX   | UNITS |

|--------------------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------|-------|------|-------|-------|

| ANALOG SWITCH                                          | ·                                | •                                                                                                                     |       |      |       |       |

| Analog-Signal Range                                    | V <sub>DP</sub> ,V <sub>DM</sub> |                                                                                                                       | 0     |      | Vcc   | V     |

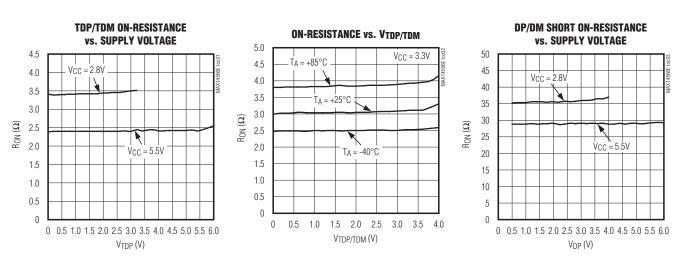

| On-Resistance TDP/TDM Switch                           | Ron                              | $V_{DP} = V_{DM} = 0V$ to $V_{CC}$ , $I_{DP} = I_{DM} = 10$ mA                                                        |       | 4.0  | 6.5   | Ω     |

| On-Resistance Match Between<br>Channels TDP/TDM Switch | ΔR <sub>ON</sub>                 | $V_{CC} = 5.0V, V_{DP} = V_{DM} = 400mV,$<br>$I_{DP} = I_{DM} = 10mA$                                                 |       | 0.1  |       | Ω     |

| On-Resistance Flatness TDP/<br>TDM Switch              | RFLAT                            | $V_{CC} = 5.0V$ , $V_{DP} = V_{DM} = 0$ to $V_{CC}$ ,<br>$I_{DP} = I_{DM} = 10$ mA                                    |       | 0.1  |       | Ω     |

| On-Resistance of DP/DM Short                           | RSHORT                           | $V_{CB} = 0V, V_{DP} = 1V, I_{DP} = I_{DM} = 10mA$                                                                    |       | 40   | 70    | Ω     |

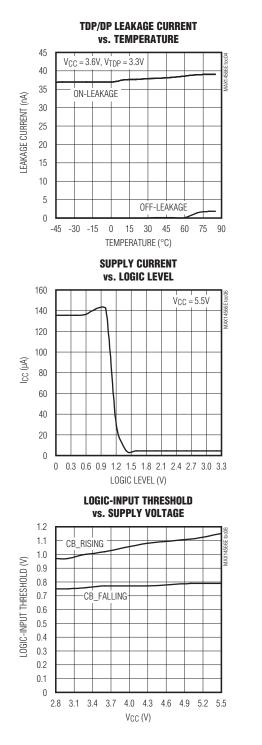

| Off-Leakage Current                                    | ITDPOFF,<br>ITDMOFF              | $V_{CC} = 3.6V, V_{DP} = V_{DM} = 0.3V \text{ to } 3.3V,$<br>$V_{TDP} = V_{TDM} = 3.3V \text{ to } 0.3V, V_{CB} = 0V$ | -250  |      | +250  | nA    |

| On-Leakage Current                                     | IDPON, IDMON                     | $V_{CC} = 3.6V$ , $V_{DP} = V_{DM} = 3.3V$ to 0.3V,<br>$V_{CB} = V_{CC}$                                              | -250  |      | +250  | nA    |

| DYNAMIC PERFORMANCE                                    |                                  |                                                                                                                       |       |      |       |       |

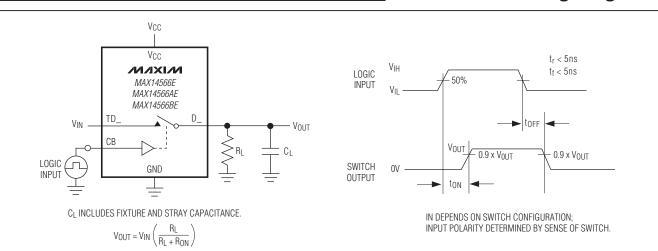

| Turn-On Time                                           | ton                              | VTDP or VTDM = 1.5V, R <sub>L</sub> = $300\Omega$ , C <sub>L</sub> = $35pF$ , Figure 1                                |       | 20   | 100   | μs    |

| Turn-Off Time                                          | tOFF                             | VTDP or VTDM = 1.5V, R <sub>L</sub> = $300\Omega$ , C <sub>L</sub> = $35pF$ , Figure 1                                |       | 1    | 5     | μs    |

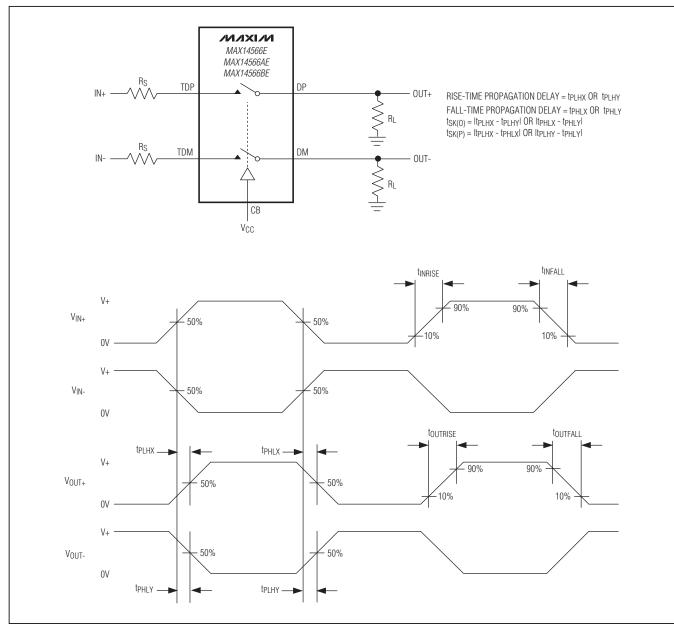

| TDP, TDM Switch Propagation<br>Delay                   | tplh, tphl                       | $R_L = R_S = 50\Omega$                                                                                                |       | 60   |       | ps    |

| Output Skew                                            | tsk(O)                           | Skew between DP and DM when connected to TDP and TDM, $R_L = R_S = 50\Omega$ , Figure 2                               |       | 40   |       | ps    |

| TDP, TDM Off-Capacitance                               | COFF                             | f = 1MHz                                                                                                              |       | 2.0  |       | рF    |

| DP, DM On-Capacitance<br>(Connected to TDP, TDM)       | CON                              | f = 240MHz                                                                                                            |       | 4.0  | 5.5   | pF    |

| -3dB Bandwidth                                         | BW                               | $R_L = R_S = 50\Omega$ (Note 4)                                                                                       |       | 1000 |       | MHz   |

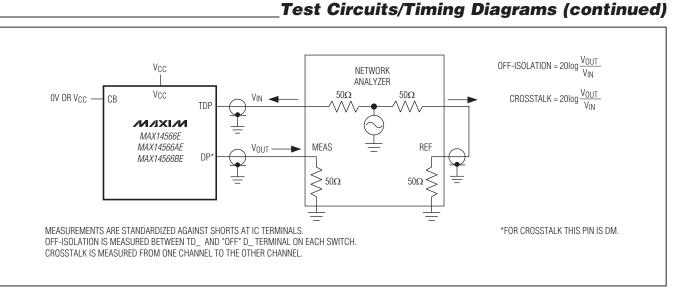

| Off-Isolation                                          | Viso                             | $V_{TDP}$ , $V_{DP} = 0$ dBm, $R_L = R_S = 50\Omega$ ,<br>f = 250MHz, Figure 3 (Note 4)                               |       | -20  |       | dB    |

| Crosstalk                                              | VCT                              | $V_{TDP}$ , $V_{DP} = 0$ dBm, $R_L = R_S = 50\Omega$ ,<br>f = 250MHz, Figure 3 (Note 4)                               |       | -25  |       | dB    |

| INTERNAL RESISTORS                                     |                                  |                                                                                                                       |       |      |       |       |

| DP/DM Short Pulldown                                   | R <sub>PD</sub>                  |                                                                                                                       | 335   | 500  | 710   | kΩ    |

| RP1/RP2 Ratio                                          | RT <sub>RP</sub>                 |                                                                                                                       | 1.485 | 1.5  | 1.515 | Ratio |

| RP1 + RP2 Resistance                                   | R <sub>RP</sub>                  |                                                                                                                       | 95    | 126  | 176   | kΩ    |

| RM1/RM2 Ratio                                          | RT <sub>RM</sub>                 |                                                                                                                       | 0.843 | 0.85 | 0.865 | Ratio |

| RM1 + RM2 Resistance                                   | R <sub>RM</sub>                  |                                                                                                                       | 70    | 94   | 132   | kΩ    |

| COMPARATORS                                            |                                  |                                                                                                                       |       |      |       |       |

| DM1 Comparator Threshold                               | VDM1F                            | DM falling                                                                                                            | 45    | 46   | 47    | %Vcc  |

| DM1 Comparator Hysteresis                              |                                  |                                                                                                                       |       | 1    |       | %     |

| DM2 Comparator Threshold                               | VDM2F                            | DM falling                                                                                                            | 6.31  | 7    | 7.6   | %Vcc  |

| DM2 Comparator Hysteresis                              |                                  |                                                                                                                       |       | 1    |       | %     |

| DP Comparator Threshold                                | VDPR                             | DP rising                                                                                                             | 45    | 46   | 47    | %Vcc  |

### **ELECTRICAL CHARACTERISTICS (continued)**

(V<sub>CC</sub> = 2.8V to 5.5V,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at V<sub>CC</sub> = 5.0V,  $T_A = +25^{\circ}$ C.) (Note 2)

| PARAMETER                                               | SYMBOL          | CONDITIONS                                                                                                                                    | MIN                      | TYP | MAX | UNITS |

|---------------------------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----|-----|-------|

| DP Comparator Hysteresis                                |                 |                                                                                                                                               |                          | 1   |     | %     |

| LOGIC INPUT (CB, CB1)                                   |                 |                                                                                                                                               |                          |     |     |       |

| CB/CB1 Input Logic-High                                 | VIH             |                                                                                                                                               | 1.4                      |     |     | V     |

| CB/CB1 Input Logic-Low                                  | VIL             |                                                                                                                                               |                          |     | 0.4 | V     |

| CB/CB1 Input Leakage Current                            | I <sub>IN</sub> | $\label{eq:VC} \begin{array}{l} V_{CC} = 5.5 V, \mbox{ 0V} \leq V_{CB} \leq V_{IL} \mbox{ or } \\ V_{IH} \leq V_{CB} \leq V_{CC} \end{array}$ | -1                       |     | +1  | μA    |

| CEN/CEN OUTPUTS                                         |                 |                                                                                                                                               |                          |     |     |       |

| V <sub>BUS</sub> Toggle Time (MAX14566E/<br>MAX14566AE) | tvbt            | CB = logic 0 to logic 1 or logic 1 to logic 0                                                                                                 | 0.5                      | 1   | 2   | s     |

| CEN Output Logic-High Voltage                           |                 | CB = logic 0 to logic 1, I <sub>SOURCE</sub> = 2mA<br>(MAX14566E only)                                                                        | V <sub>CC</sub> -<br>0.4 |     |     | V     |

| CEN Output Leakage Current                              |                 | $V_{CC} = 5.5V, V_{\overline{CEN}} = 0V, \overline{CEN}$ deasserted (MAX14566E only)                                                          |                          |     | 1   | μA    |

| CEN Output Logic-Low Voltage                            |                 | CB = logic 0 to logic 1, I <sub>SINK</sub> = 2mA<br>(MAX14566AE only)                                                                         |                          |     | 0.4 | V     |

| CEN Output Leakage Current                              |                 | V <sub>CC</sub> = V <sub>CEN</sub> = 5.5V, CEN deasserted<br>(MAX14566AE only)                                                                |                          |     | 1   | μA    |

| ESD PROTECTION                                          |                 |                                                                                                                                               |                          |     |     |       |

| ESD Protection Level<br>(DP and DM Only)                | Vesd            | НВМ                                                                                                                                           |                          | ±15 |     | kV    |

| ESD Protection Level<br>(All Other Pins)                | VESD            | НВМ                                                                                                                                           |                          | ±2  |     | kV    |

**Note 2:** All units are 100% production tested at  $T_A = +25^{\circ}$ C. Specifications over temperature are guaranteed by design.

**Note 3:** The part is operational from +2.8V to +5.5V. However, in order to have the valid Apple resistor-divider network, the V<sub>CC</sub> supply must stay within the range of +4.75V to +5.25V.

Note 4: Guaranteed by design.

## Test Circuits/Timing Diagrams

Figure 1. Switching Time

## \_Test Circuits/Timing Diagrams (continued)

Figure 2. Output Signal Skew

MAX14566E/MAX14566AE/MAX14566BE

Figure 3. Off-Isolation and Crosstalk

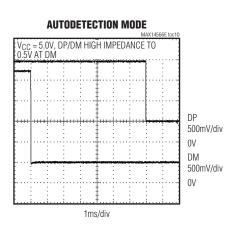

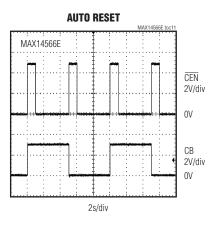

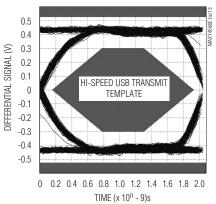

(VCC = 5V, TA =  $+25^{\circ}$ C, unless otherwise noted.)

## **Typical Operating Characteristics**

## **Typical Operating Characteristics (continued)**

$(V_{CC} = 5V, T_A = +25^{\circ}C, unless otherwise noted.)$

10µs/div

## **Typical Operating Characteristics (continued)**

(V<sub>CC</sub> = 5V,  $T_A$  = +25°C, unless otherwise noted.)

AUTO RESET MAX14566AE **USB EYE DIAGRAM**

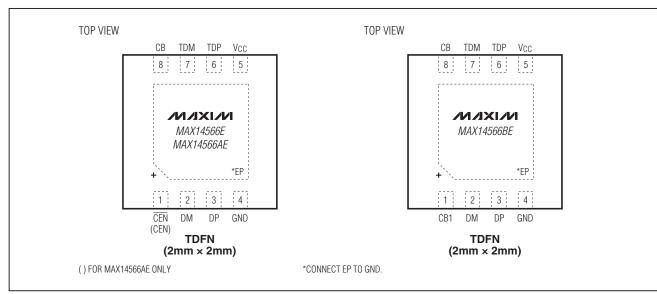

## \_Pin Configuration

## \_Pin Description

|           | PIN        |            | NAME | FUNCTION                                                                                                                                                                |  |

|-----------|------------|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MAX14566E | MAX14566AE | MAX14566BE | NAME | FUNCTION                                                                                                                                                                |  |

| _         | 1          |            | CEN  | nMOSFET Open-Drain Output, Current-Limit Switch (CLS) Control<br>Output. If CB changes from logic 0 to logic 1 or from logic 1 to<br>logic 0, CEN is low for 1s (typ).  |  |

| 1         |            |            | CEN  | Active-Low pMOSFET Open-Drain Output, Current-Limit Switch (CLS) Control Output. If CB changes from logic 0 to logic 1 or logic 1 to logic 0, CEN is high for 1s (typ). |  |

|           | —          | 1          | CB1  | Switch Control Bit. See Table 2.                                                                                                                                        |  |

| 2         | 2          | 2          | DM   | USB Connector D- Connection                                                                                                                                             |  |

| 3         | 3          | 3          | DP   | USB Connector D+ Connection                                                                                                                                             |  |

| 4         | 4          | 4          | GND  | Ground                                                                                                                                                                  |  |

| 5         | 5          | 5          | VCC  | Power Supply. Connect a 0.1µF capacitor between VCC and GND as close as possible to the device.                                                                         |  |

| 6         | 6          | 6          | TDP  | Host USB Transceiver D+ Connection                                                                                                                                      |  |

| 7         | 7          | 7          | TDM  | Host USB Transceiver D- Connection                                                                                                                                      |  |

| 8         | 8          | 8          | СВ   | Switch Control Bit. See Table 1.<br>CB = logic 0, charger mode<br>CB = logic 1 (PM), pass-through mode active, DP/DM connected<br>to TDP/TDM                            |  |

| _         | _          | _          | EP   | Exposed Pad. Connect EP to ground. Do not use EP as the only ground connection.                                                                                         |  |

MAX14566E/MAX14566AE/MAX14566BE

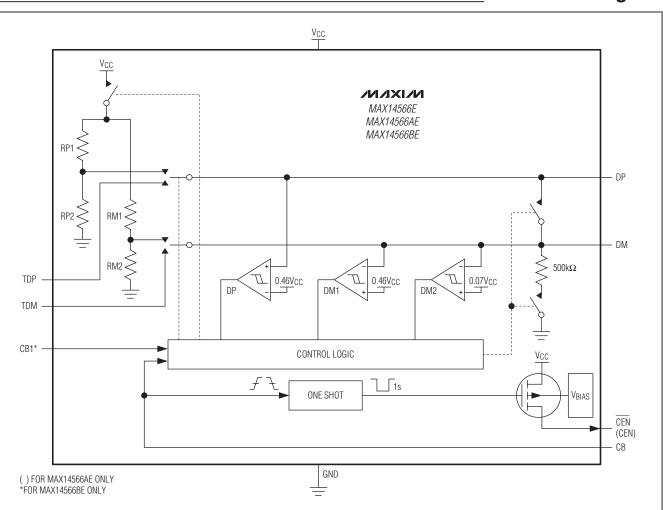

Functional Diagram

## **Detailed Description**

The MAX14566E/MAX14566AE/MAX14566BE are Hi-Speed USB analog switches that support USB hosts to identify the USB port as a charger port when the USB host is in a low-power mode and cannot enumerate USB devices. These devices feature high-performance Hi-Speed USB switches with low 4pF (typ) on-capacitance and low 4 $\Omega$  (typ) on-resistance. DP and DM can handle signals between 0V and 6V with any supply voltage.

#### **Resistor-Dividers**

All the devices feature an internal resistor-divider for biasing data lines to provide support for Apple-compliant devices. When these devices are not operated with the resistor-divider, they disconnect the resistor-dividers from the supply voltage to minimize supply current requirements. The resistor-dividers are not connected in pass-through mode.

#### Switch Control

The MAX14566E/MAX14566AE feature a single digital input, CB, for mode selection (Table 1). Connect CB to a logic-level low voltage for autodetection charger mode (AM). See the *Autodetection* section for more information. Connect CB to a logic-level high voltage for normal high-speed pass-through mode (PM). The MAX14566BE features dual digital inputs, CB and CB1, for mode selection (Table 2). Connect CB to a logic-level high for normal high-speed pass-through mode (PM). Connect CB to a logic-level high for normal high-speed pass-through mode (PM).

with CB1. Connect CB1 to a logic-level low for auto mode (AM) or connect CB1 to a logic-level high for forced dedicated-charger mode (FM).

#### Autodetection

All the devices feature autodetection charger mode for dedicated chargers and USB masters. CB must be set low to activate autodetection charger mode.

In autodetection charger mode, the MAX14566E monitors the voltages at DM and DP to determine the type of the device attached. If the voltage at DM is +2.3V (typ) or higher and the voltage at DP is +2.3V (typ) or lower, the voltage stays unchanged.

If the voltage at DM is forced below the +2.3V (typ) threshold, the internal switch disconnects DM and DP

from the resistor-divider and DP and DM are shorted together for dedicated charging mode.

If the voltage at DP is forced higher than the +2.3V (typ) threshold, the internal switch disconnects DM and DP from the resistor-divider and DP and DM are shorted together for dedicated charging mode.

Once the charging voltage is removed, the short between DP and DM is disconnected for normal operation.

#### **Automatic Peripheral Reset**

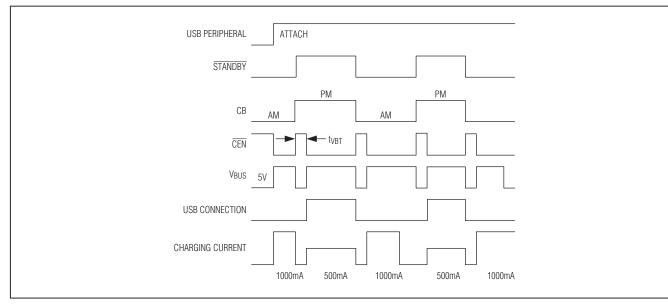

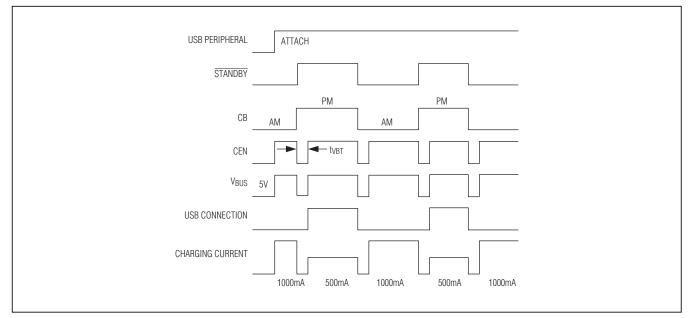

The MAX14566E/MAX14566AE feature automatic currentlimit switch control output. This feature resets the peripheral connected to V<sub>BUS</sub> in the event the USB host switches to or from standby mode.  $\overline{CEN}/CEN$  provide a 1s (typ) pulse on the rising or falling edge of CB (Figures 4, 5, and 6).

#### Table 1. Digital Input State (MAX14566E/MAX14566AE)

| СВ | MODE | DP/DM                        | COMMENT            | INTERNAL RESISTOR-DIVIDER |

|----|------|------------------------------|--------------------|---------------------------|

| 0  | AM   | Autodetection Circuit Active | Auto Mode          | Connected                 |

| 1  | PM   | Connected to TDP/TDM         | USB Traffic Active | Not Connected             |

#### Table 2. Digital Input State (MAX14566BE)

| СВ | CB1 | MODE | STATUS                                            |  |

|----|-----|------|---------------------------------------------------|--|

| 0  | 0   | AM   | Auto Mode                                         |  |

| 0  | 1   | FM   | Forced Dedicated-Charger Mode: DP/DM Shorted      |  |

| 1  | Х   | PM   | Pass-Through (USB) Mode: Connect DP/DM to TDP/TDM |  |

X = Don't care.

Figure 4. MAX14566E Peripheral Reset Timing Diagram

Figure 5. MAX14566E Peripheral Reset Applications Diagram

Figure 6. MAX14566AE Peripheral Reset Timing Diagram

Figure 7. MAX14566AE VBUS Discharge Circuit

#### **Bus Voltage Discharge**

The MAX14566AE automatic current-limit switch control output can be used to discharge the V<sub>BUS</sub> during V<sub>BUS</sub> reset. When the system controls the current-limit switch for V<sub>BUS</sub> toggle, the output capacitor can be discharged slowly depending upon the load. If fast discharge of the V<sub>BUS</sub> capacitor is desired, the CEN output can be used to achieve the fast discharge as shown in Figure 7.

#### **Data Contact Detect**

All the devices support USB devices that require detecting the USB data lines prior to charging. When a USB Revision 1.2-compliant device is attached, the USB data lines DP and DM are shorted together. The short remains until it is detected by the USB device. This feature guarantees appropriate charger detection if a USB Revision 1.2-compliant device is attached. The autodetection charger mode is activated after the data contact detect is established. CB must be set low to activate data contact detect.

#### **ESD Test Conditions**

ESD performance depends on a variety of conditions. Contact Maxim for a reliability report that documents test setup, test methodology, and test results.

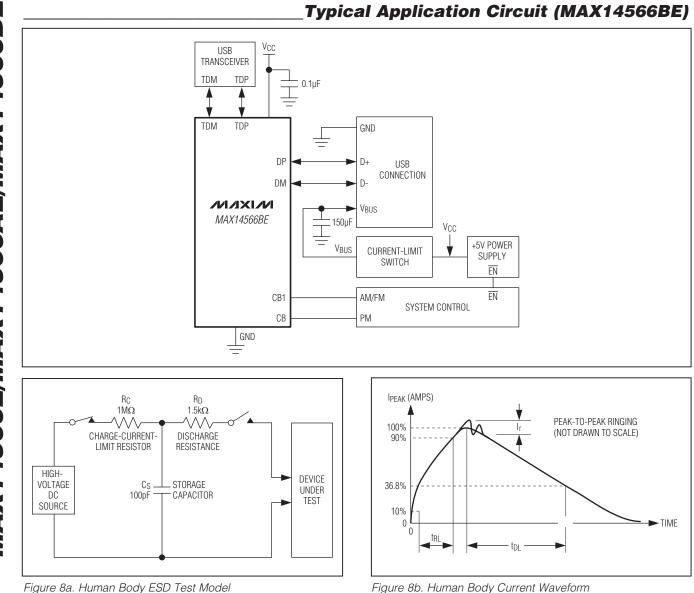

#### Extended ESD Protection (Human Body Model)

ESD-protection structures are incorporated on all pins to protect against electrostatic discharges up to  $\pm 2kV$ (HBM) encountered during handling and assembly. DP and DM are further protected against ESD up to  $\pm 15kV$ (HBM) without damage. The ESD structures withstand high ESD both in normal operation and when the device is powered down. After an ESD event, the device continues to function without latchup (Figure 8).

Figure 8a. Human Body ESD Test Model

**Chip Information**

PROCESS: BICMOS

For the latest package outline information and land patterns (footprints), go to www.maxim-ic.com/packages. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE   | PACKAGE | OUTLINE        | LAND           |

|-----------|---------|----------------|----------------|

| TYPE      | CODE    | NO.            | PATTERN NO.    |

| 8 TDFN-EP | T822+1  | <u>21-0168</u> | <u>90-0064</u> |

### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                 | PAGES<br>CHANGED |

|--------------------|------------------|-----------------------------------------------------------------------------|------------------|

| 0                  | 10/10            | Initial release                                                             | —                |

| 1                  | 3/11             | Changed the USB Battery Charging Specification Revision 1.1 to Revision 1.2 | 1, 13            |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 \_\_\_

© 2011 Maxim Integrated Products

Maxim is a registered trademark of Maxim Integrated Products, Inc.

15