#

## **Dual-Pair LLT with Charge Pump and High-ESD Protection**

### **General Description**

The MAX14569 is a dedicated dual-pair unidirectional logic-level translator that is ideal for industrial and metering applications. Voltages V<sub>CC</sub> and V<sub>L</sub> set the logic levels on either side of the device. Logic-high signals present on the V<sub>L</sub> side of the device appear as high-voltage logic signals on the V<sub>CC</sub> side of the device and vice versa.

The device has two pairs of logic-level translators in back-to-back configuration: one logic-level translator from a low voltage to a high voltage and the other logic-level translator from a high voltage to a low voltage. The device also features a high-efficiency charge pump to boost the battery input, V<sub>BAT</sub>, to V<sub>CC</sub> (5V).

The device features an extreme power-saving mode that reduces supply current to a typical  $0.01\mu$ A. The device also features thermal short-circuit protection for enhanced protection in applications that route signals externally.

In addition, the device features enhanced high electrostatic discharge (ESD) Human Body Model (HBM) protection on OUTAVCC, INBVCC, OUTCVCC, and INDVCC ports up to ±25kV. The MAX14569 is available in a 16-pin QSOP package, and is specified over the -40°C to +85°C extended temperature range.

### Features

- Ultra-Low Shutdown Supply Current, 0.01µA (typ)

- ◆ Ultra-Low VL Supply Current, 1µA (max)

- Operates Down to 1.6V on VL

- Continuous Current Drive Capability > 10mA

- Extended ESD Protection on V<sub>CC</sub> Input and Output Lines

±25kV Human Body Model

±15kV IEC 61000-4-2 Air-Gap Discharge

±12kV IEC 61000-4-2 Contact Discharge

- 16-Pin QSOP Package

- -40°C to +85°C Extended Operating Temperature Range

#### Applications

Automatic Meter Reader Remote Communications System Industrial Networking

### **Ordering Information**

| PART          | TEMP RANGE     | PIN-PACKAGE |

|---------------|----------------|-------------|

| MAX14569EEE+T | -40°C to +85°C | 16 QSOP     |

+Denotes a lead(Pb)-free/RoHS-compliant package. T = Tape and reel.

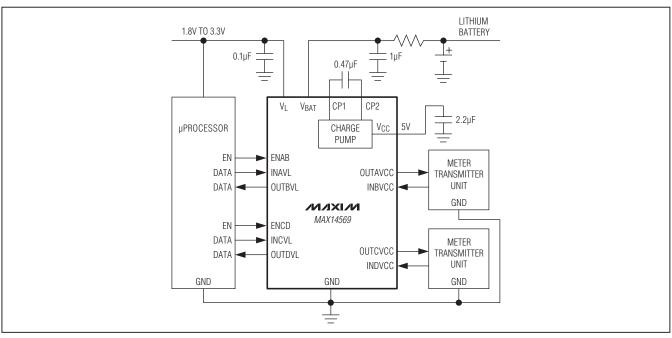

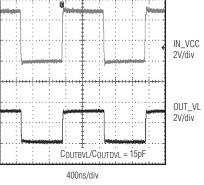

## **Typical Operating Circuit**

####

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### **ABSOLUTE MAXIMUM RATINGS**

(All voltages referenced to GND.)

| VBAT, VL                       | 0.3V to +6V           |

|--------------------------------|-----------------------|

| VCC (no shutdown condition)    | (VBAT - 0.3V) to +6V  |

| VCC (shutdown condition)       | 0.3V to +6V           |

| CP1                            | 0.3V to (VBAT + 0.3V) |

| CP2                            | 0.3V to +6V           |

| ENAB, ENCD                     | 0.3V to +6V           |

| INAVL, INCVL                   | 0.3V to +6V           |

| OUTBVL, OUTDVL                 | 0.3V to (VL + 0.3V)   |

| INBVCC, INDVCC                 | 0.3V to (VCC + 0.3V)  |

| OUTAVCC, OUTCVCC               | 0.3V to (VCC + 0.3V)  |

| Short-Circuit Current OUTAVCC, |                       |

| OUTCVCC, OUTBVL, OUTDVL to     | GNDContinuous         |

|                                |                       |

| Short-Circuit Duration OUTAVCC, OUTCVCC,                                                           |

|----------------------------------------------------------------------------------------------------|

| OUTBVL, OUTDVL to GNDContinuous                                                                    |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C)<br>QSOP (derate 9.6mW/°C above +70°C)771.5mW |

| Junction-to-Ambient Thermal Resistance (Note 1)                                                    |

| θJA103.7°C/W                                                                                       |

| Junction-to-Case Thermal Resistance (Note 1)                                                       |

| θJC                                                                                                |

| Operating Temperature Range40°C to +85°C                                                           |

| Storage Temperature Range65°C to +150°C                                                            |

| Junction Temperature+150°C                                                                         |

| Lead Temperature (soldering, 10s)+300°C                                                            |

| Soldering Temperature (reflow)+260°C                                                               |

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a fourlayer board. For detailed information on package thermal considerations, refer to <u>www.maxim-ic.com/thermal-tutorial</u>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

(VBAT = 2.3V to 5.5V, V<sub>L</sub> = 1.6V to 5.5V, C<sub>VBAT</sub> = 1 $\mu$ F, C<sub>VCC</sub> = 2.2 $\mu$ F, C<sub>VL</sub> = 0.1 $\mu$ F, TA = -40°C to +85°C, unless otherwise noted. Typical values are at V<sub>BAT</sub> = 3.6V, V<sub>L</sub> = 3.0V, and T<sub>A</sub> = +25°C.) (Notes 2, 3, 4)

| PARAMETER                                                     | SYMBOL                       | CONDITIONS                                                                                                                                                | MIN | ТҮР  | MAX | UNITS |

|---------------------------------------------------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| POWER SUPPLIES                                                |                              |                                                                                                                                                           |     |      |     |       |

| VBAT Supply Range                                             | VBAT                         |                                                                                                                                                           | 2.3 |      | 5.5 | V     |

| VL Supply Range                                               | VL                           |                                                                                                                                                           | 1.6 |      | 5.5 | V     |

| Supply Current from $V_L$                                     | IQVL                         | $\label{eq:INBVCC} \begin{split} \text{INBVCC} &= \text{INDVCC} = \text{V}_{\text{CC}},\\ \text{INAVL} &= \text{INCVL} = \text{V}_{\text{L}} \end{split}$ |     |      | 1   | μA    |

| VBAT Shutdown Supply<br>Current                               | ISHDN-VBAT                   | $V_{INAVL} = V_{INCVL} = 0V,$<br>$V_{ENAB} = V_{ENCD} = 0V$                                                                                               |     | 0.01 | 0.5 | μA    |

| V <sub>L</sub> Shutdown Supply<br>Current                     | ISHDN-VL                     | VENAB = VENCD = 0V                                                                                                                                        |     | 0.01 | 0.5 | μA    |

| VBAT Change in Supply<br>Current with ENAB and<br>ENCD at VIL | ΔΙνβάτ                       | VENAB = VENCD = VIL<br>(Notes 2, 4, 5)                                                                                                                    |     |      | 1   | μA    |

| OUTAVCC Shutdown<br>Mode Leakage Current                      | IOUTAVCC_LEAK                | VENAB = 0V, VENCD = VIH,<br>VOUTAVCC = 5V                                                                                                                 |     | 0.01 | 1   | μA    |

| OUTCVCC Shutdown<br>Mode Leakage Current                      | IOUTCVCC_LEAK                | VENAB = VIH, VENCD = 0V,<br>VOUTCVCC = 5V                                                                                                                 |     | 0.01 | 1   | μA    |

| OUTBVL, OUTDVL<br>Shutdown Mode<br>Leakage Current            | Ioutbvl_leak<br>Ioutdvl_leak | VENAB = VENCD = 0V,<br>VOUTBVL = VOUTDVL = 0V                                                                                                             |     | 0.01 | 1   | μA    |

| INBVCC Shutdown Mode<br>Leakage Current                       | INBVCC_LEAK                  | VENAB = 0V, VENCD = VIH,<br>VINBVCC = 5V                                                                                                                  |     | 0.01 | 1   | μA    |

| INDVCC Shutdown Mode<br>Leakage Current                       | INDVCC_LEAK                  | VENAB = VIH, VENCD = 0V,<br>VINDVCC = 5V                                                                                                                  |     | 0.01 | 1   | μA    |

### ELECTRICAL CHARACTERISTICS (continued)

(VBAT = 2.3V to 5.5V, V<sub>L</sub> = 1.6V to 5.5V, C<sub>VBAT</sub> = 1 $\mu$ F, C<sub>VCC</sub> = 2.2 $\mu$ F, C<sub>VL</sub> = 0.1 $\mu$ F, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted. Typical values are at V<sub>BAT</sub> = 3.6V, V<sub>L</sub> = 3.0V, and T<sub>A</sub> = +25°C.) (Notes 2, 3, 4)

| PARAMETER                                           | SYMBOL                   | CONDITIONS                                                                                                                                                                                              | MIN                  | TYP  | MAX              | UNITS |

|-----------------------------------------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------|------------------|-------|

| INAVL, INCVL Leakage<br>Current                     | INAVL_LEAK<br>INCVL_LEAK | VINAVL = VINCVL = VL                                                                                                                                                                                    |                      | 0.01 | 1                | μA    |

| ENAB, ENCD Input<br>Leakage Current                 | IENAB_LEAK<br>IENCD_LEAK | VENAB = VENCD = 5V                                                                                                                                                                                      |                      | 0.01 | 1                | μA    |

| OUTAVCC, OUTCVCC<br>Short-Circuit Output<br>Current | ISH                      | $V_{OUTAVCC} = 0V \text{ or}$<br>$V_{OUTCVCC} = 0V,$<br>$V_{BAT} \ge 2.7V$                                                                                                                              | 100                  | 250  |                  | mA    |

| LOGIC LEVELS                                        | 1                        |                                                                                                                                                                                                         | 1                    |      |                  |       |

| INAVL, INCVL Input-<br>Voltage High                 | VIHL                     |                                                                                                                                                                                                         | $0.7 \times V_{L}$   |      |                  | V     |

| INAVL, INCVL Input-<br>Voltage Low                  | VILL                     |                                                                                                                                                                                                         |                      |      | $0.3 \times V_L$ | V     |

| INBVCC, INDVCC Input-<br>Voltage High               | VIHC                     |                                                                                                                                                                                                         | 0.7 x Vcc            |      |                  | V     |

| INBVCC, INDVCC Input-<br>Voltage Low                | VILC                     |                                                                                                                                                                                                         |                      |      | 0.3 x VCC        | V     |

| ENAB, ENCD Input-<br>Voltage High                   | Vih                      |                                                                                                                                                                                                         | 1.2                  |      |                  | V     |

| ENAB, ENCD Input-<br>Voltage Low                    | VIL                      |                                                                                                                                                                                                         |                      |      | 0.4              | V     |

| ENAB, ENCD Input-<br>Voltage Hysteresis             | V <sub>HYS</sub>         |                                                                                                                                                                                                         |                      | 120  |                  | mV    |

| OUTBVL, OUTDVL                                      | Vou                      | OUTBVL or OUTDVL source<br>current = 100µA, INBVCC or<br>INDVCC > VIHC                                                                                                                                  | V <sub>L</sub> - 0.1 |      |                  | V     |

| Output-Voltage High                                 |                          | OUTBVL or OUTDVL source<br>current = 4mA, INBVCC or<br>INDVCC > VIHC                                                                                                                                    | VL - 0.4             |      |                  | v     |

| OUTBVL, OUTDVL                                      | Voll                     | OUTBVL or OUTDVL sink<br>current = 100µA, INBVCC or<br>INDVCC < VILC                                                                                                                                    |                      |      | 0.1              | V     |

| Output-Voltage Low                                  | VOLL                     | OUTBVL or OUTDVL sink<br>current = 4mA,<br>INBVCC or INDVCC < VILC                                                                                                                                      |                      |      | 0.4              | V     |

| OUTAVCC, OUTCVCC                                    | Veue                     | $\label{eq:constraint} \begin{array}{ c c } \mbox{OUTAVCC or OUTCVCC} \\ \mbox{source current} = 100 \mu A, \\ \mbox{INAVL or INCVL} > V_{IHL}, \mbox{2.7V} \leq \\ \mbox{VBAT} \leq 4.5 V \end{array}$ |                      | 4.6  |                  | ~     |

| Output-Voltage High                                 |                          | OUTAVCC or OUTCVCC<br>source current = 20mA,<br>INAVL or INCVL > VIHL,<br>$2.7V \le V_{BAT} \le 4.5V$                                                                                                   |                      | 4.3  |                  | V     |

3

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{BAT} = 2.3V \text{ to } 5.5V, V_L = 1.6V \text{ to } 5.5V, C_{VBAT} = 1\mu\text{F}, C_{VCC} = 2.2\mu\text{F}, C_{VL} = 0.1\mu\text{F}, T_A = -40^{\circ}\text{C}$  to +85°C, unless otherwise noted. Typical values are at V<sub>BAT</sub> = 3.6V, V<sub>L</sub> = 3.0V, and T<sub>A</sub> = +25°C.) (Notes 2, 3, 4)

| PARAMETER                                                    | SYMBOL       | CONDITIONS                                                                                                                                                          | MIN        | ТҮР       | MAX        | UNITS |

|--------------------------------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------|------------|-------|

| OUTAVCC, OUTCVCC                                             | Vere         | $\begin{array}{l} \mbox{OUTAVCC or OUTCVCC} \\ \mbox{sink current} = 100 \mu A, \\ \mbox{INAVL or INCVL} < V_{ILL,} 2.7V \leq \\ \mbox{VBAT} \leq 4.5V \end{array}$ |            |           | 0.1        | V     |

| Output-Voltage Low                                           | Volc         | $\begin{array}{l} \mbox{OUTAVCC or OUTCVCC} \\ \mbox{sink current} = 20mA, \\ \mbox{INAVL or INCVL} < VILL, \\ \mbox{2.7V} \leq V_{BAT} \leq 4.5V \end{array}$      |            |           | 0.4        |       |

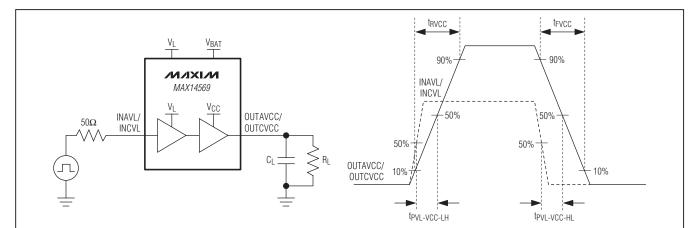

| TIMING CHARACTERIST                                          | ICS (Note 6) |                                                                                                                                                                     |            |           |            |       |

| OUTAVCC, OUTCVCC<br>Rise Time                                | tRVCC        | Figure 1                                                                                                                                                            |            |           | 25         | ns    |

| OUTAVCC, OUTCVCC<br>Fall Time                                | tFVCC        | Figure 1                                                                                                                                                            |            |           | 25         | ns    |

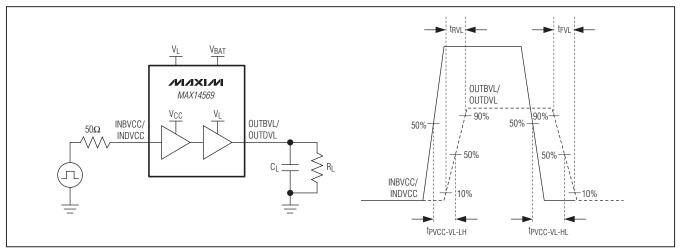

| OUTBVL, OUTDVL Rise<br>Time                                  | trvl         | Figure 2                                                                                                                                                            |            |           | 25         | ns    |

| OUTBVL, OUTDVL Fall<br>Time                                  | tfvl         | Figure 2                                                                                                                                                            |            |           | 25         | ns    |

| Propagation Delay<br>(Driving INAVL, INCVL)<br>Low-to-High   | tpvl-vcc-lh  | Figure 1                                                                                                                                                            |            |           | 30         | ns    |

| Propagation Delay<br>(Driving INAVL, INCVL)<br>High-to-Low   | tPVL-VCC-HL  | Figure 1                                                                                                                                                            |            |           | 30         | ns    |

| Propagation Delay<br>(Driving INBVCC,<br>INDVCC) Low-to-High | tpvcc-vl-lh  | Figure 2                                                                                                                                                            |            |           | 30         | ns    |

| Propagation Delay<br>(Driving INBVCC,<br>INDVCC) High-to-Low | tpvcc-vl-hl  | Figure 2                                                                                                                                                            |            |           | 30         | ns    |

| Maximum Data Rate                                            |              |                                                                                                                                                                     | 12         |           |            | Mbps  |

| CHARGE PUMP                                                  |              | · · ·                                                                                                                                                               |            |           |            |       |

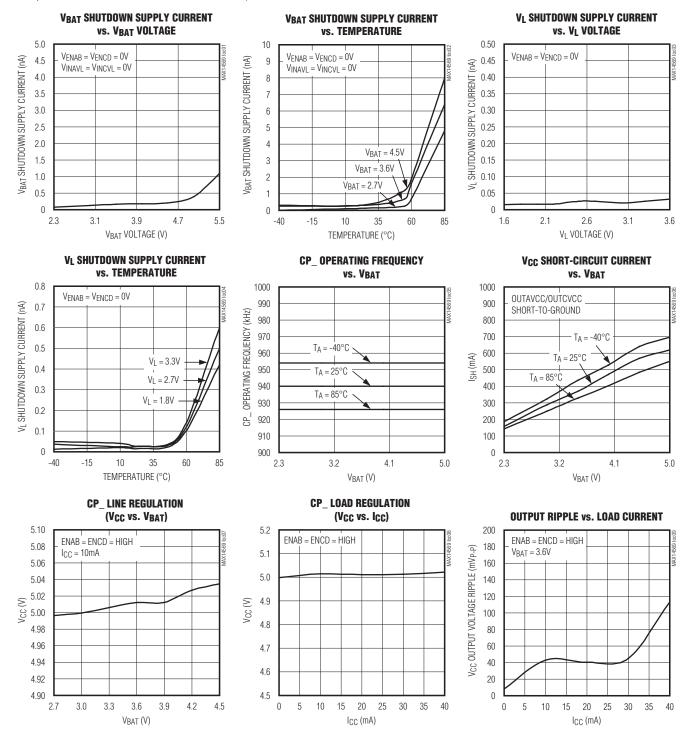

| VCC Output Voltage                                           | Vcc          | $I_{CC} = 10 \text{mA}, 2.7 \text{V} \le \text{V}_{BAT} \le 4.5 \text{V}$                                                                                           | 4.7<br>4.7 | 5.0       | 5.3<br>5.3 | - V   |

| V <sub>CC</sub> Output Voltage<br>Ripple                     |              | $I_{CC} = 40 \text{mA}, 3.0 \text{V} \le \text{V}_{BAT} \le 4.5 \text{V}$ $I_{CC} = 40 \text{mA}$                                                                   | 4./        | 5.0<br>45 | 0.0        | mVp-p |

| VCC Line Regulation                                          |              | $I_{CC} = 10 \text{mA},$<br>2.7V $\leq V_{BAT} \leq 4.5 \text{V}$                                                                                                   | -1         |           | +1         | %     |

| V <sub>CC</sub> Load Regulation                              | ΔVCC         | $0 \le I_{CC} \le 40$ mA, V <sub>BAT</sub> = 3.6V                                                                                                                   |            | -1        |            | %     |

| Quiescent Current                                            | IQ           | $I_{CC} = 0 \text{mA}, V_{BAT} = 3.6 \text{V}$                                                                                                                      |            |           | 200        | μA    |

| CP_ Leakage Current                                          | ICP_LEAK     | $V_{BAT} = 3.6V, V_{CC} = 0V$<br>$V_{ENAB} = V_{ENCD} = 0V$                                                                                                         |            | 0.01      | 0.5        | μA    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{BAT} = 2.3V \text{ to } 5.5V, V_L = 1.6V \text{ to } 5.5V, C_{VBAT} = 1\mu\text{F}, C_{VCC} = 2.2\mu\text{F}, C_{VL} = 0.1\mu\text{F}, T_A = -40^{\circ}\text{C}$  to +85°C, unless otherwise noted. Typical values are at V<sub>BAT</sub> = 3.6V, V<sub>L</sub> = 3.0V, and T<sub>A</sub> = +25°C.) (Notes 2, 3, 4)

| PARAMETER                           | SYMBOL            | CONDITIONS                                                                                                                                          | MIN | TYP  | MAX | UNITS |

|-------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| CP_ Switching Frequency             | fCP               | No capacitor between CP1 and CP2, 2.7V $\leq$ VBAT $\leq$ 4.5V                                                                                      | 0.5 | 1    | 1.5 | MHz   |

| Efficiency                          | η                 | $\label{eq:lcc} \begin{array}{l} \text{ICC} = 10\text{mA},  \text{V}_{\text{BAT}} = 2.7\text{V}, \\ \text{V}_{\text{CC}} = 5.0\text{V} \end{array}$ |     | 90   |     | %     |

| THERMAL PROTECTION                  |                   |                                                                                                                                                     |     |      |     |       |

| Thermal Shutdown                    | TSHDN             |                                                                                                                                                     |     | +150 |     | °C    |

| Thermal Hysteresis                  | T <sub>HYST</sub> |                                                                                                                                                     |     | +20  |     | °C    |

| ESD PROTECTION                      |                   |                                                                                                                                                     |     |      |     |       |

|                                     |                   | Human Body Model                                                                                                                                    |     | ±25  |     |       |

| OUTAVCC, INBVCC,<br>OUTCVCC, INDVCC |                   | IEC 61000-4-2 Air Gap<br>Discharge                                                                                                                  |     | ±15  |     | kV    |

|                                     |                   | IEC 61000-4-2 Contact<br>Discharge                                                                                                                  |     | ±12  |     |       |

| All Other Pins                      |                   | Human Body Model                                                                                                                                    |     | ±2   |     | kV    |

Note 2: V<sub>L</sub> must be less than or equal to V<sub>CC</sub> during normal operation. However, V<sub>L</sub> can be greater than V<sub>CC</sub> during startup and shutdown conditions.

Note 3: All units are 100% production tested at  $T_A = +25^{\circ}C$ . Limits over the operating temperature range are guaranteed by design and not production tested.

Note 4: Connect a  $0.47\mu F$  capacitor between CP1 and CP2.

**Note 5:**  $\Delta I_{VBAT} = [I_{VBAT}(V_{ENAB} = V_{ENCD} = V_{IL}) - I_{VBAT}(V_{ENAB} = V_{ENCD} = 0V)]$ . Guaranteed by design and not production tested.

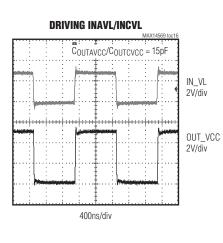

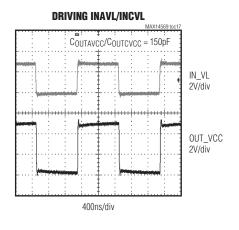

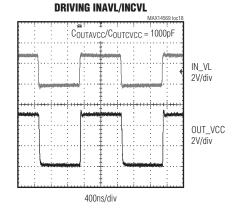

Note 6:  $V_{CC} = 5.0V$ ,  $V_L = 1.6V$  to  $V_{CC}$ ,  $V_{BAT} = 2.7V$  to 3.6V,  $V_{ENAB} = V_{ENCD} > V_{IH}$ ,  $R_S = 50\Omega$ ,  $R_L = 1M\Omega$ ,  $C_L = 15pF$ ,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $V_{BAT} = 3.6V$ ,  $V_L = 3.0V$ , and  $T_A = +25^{\circ}C$ .

Figure 1. Push-Pull Driving INAVL/INCVL Test Circuit and Timing

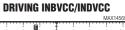

Figure 2. Push-Pull Driving INBVCC/INDVCC Test Circuit and Timing

MAX14569

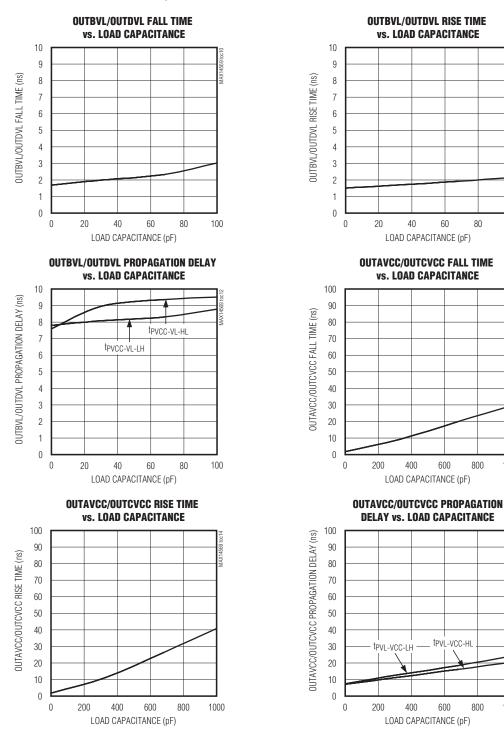

$(V_{BAT} = 3.6V, V_L = 3V, C_{VBAT} = 1\mu F, C_{VCC} = 2.2\mu F, C_{VL} = 0.1\mu F$ , connect 0.47 $\mu$ F capacitor between CP1 and CP2, data rate = 1Mbps, T<sub>A</sub> = +25°C, unless otherwise noted.)

**MAX14569**

### **Typical Operating Characteristics (continued)**

80

800

1000

1000

800

100

(VBAT = 3.6V, VL = 3V, CVBAT = 1µF, CVCC = 2.2µF, CVL = 0.1µF, connect 0.47µF capacitor between CP1 and CP2, data rate = 1Mbps,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

### **Typical Operating Characteristics (continued)**

$(V_{BAT} = 3.6V, V_L = 3V, C_{VBAT} = 1\mu F, C_{VCC} = 2.2\mu F, C_{VL} = 0.1\mu F$ , connect 0.47 $\mu$ F capacitor between CP1 and CP2, data rate = 1Mbps, T<sub>A</sub> = +25°C, unless otherwise noted.)

#### Pin Configuration TOP VIEW 16 CP1 V<sub>L</sub> 1 15 VBAT ENAB 2 /M/IXI/M MAX14569 14 CP2 ENCD 3 13 Vcc INAVL 4 12 OUTAVCC OUTBVL 5 11 INBVCC INCVL 6 10 OUTCVCC OUTDVL 7 9 INDVCC GND 8 QSOP

### **Pin Description**

| PIN | NAME    | FUNCTION                                                                                                                                                                                                               |

|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | VL      | Logic Supply Voltage, +1.6V to +5.5V. Bypass VL to GND with a 0.1 $\mu F$ capacitor placed as close as possible to the device.                                                                                         |

| 2   | ENAB    | Enable Input for A and B Ports. Drive ENAB low for shutdown mode, or drive ENAB high for normal operation.                                                                                                             |

| 3   | ENCD    | Enable Input for C and D Ports. Drive ENCD low for shutdown mode, or drive ENCD high for normal operation.                                                                                                             |

| 4   | INAVL   | Input A Port. Referenced to VL.                                                                                                                                                                                        |

| 5   | OUTBVL  | Output B Port. Referenced to VL.                                                                                                                                                                                       |

| 6   | INCVL   | Input C Port. Referenced to VL.                                                                                                                                                                                        |

| 7   | OUTDVL  | Output D Port. Referenced to VL.                                                                                                                                                                                       |

| 8   | GND     | Ground                                                                                                                                                                                                                 |

| 9   | INDVCC  | Input D Port. Referenced to V <sub>CC</sub> .                                                                                                                                                                          |

| 10  | OUTCVCC | Output C Port. Referenced to VCC.                                                                                                                                                                                      |

| 11  | INBVCC  | Input B Port. Referenced to V <sub>CC</sub> .                                                                                                                                                                          |

| 12  | OUTAVCC | Output A Port. Referenced to VCC.                                                                                                                                                                                      |

| 13  | Vcc     | Charge-Pump Output. Bypass V <sub>CC</sub> to GND with a $2.2\mu$ F ceramic capacitor placed as close as possible to the V <sub>CC</sub> pin to have high ESD protection on OUTAVCC, INBVCC, OUTCVCC, and INDVCC pins. |

| 14  | CP2     | External Charge-Pump Capacitor Connection                                                                                                                                                                              |

| 15  | VBAT    | Battery Input, +2.3V to +5.5V. Bypass V <sub>BAT</sub> to GND with a $1\mu$ F capacitor placed as close as possible to the device.                                                                                     |

| 16  | CP1     | External Charge-Pump Capacitor Connection                                                                                                                                                                              |

**MAX14569**

### **Detailed Description**

The MAX14569 is a dedicated dual-pair unidirectional logic-level translator that is ideal for automatic remotemetering applications. Externally applied voltage VL and regulated output voltage V<sub>CC</sub> set the logic levels on either side of the device.

The device boosts the V<sub>BAT</sub> supply input voltage to a charge-pump-regulated output, V<sub>CC</sub>. Logic-high signals present on the V<sub>L</sub> side of the device appear as a high-voltage logic signals on the V<sub>CC</sub> side of the device and vice versa.

The device has two pairs of logic-level translators in back-to-back configuration: one logic-level translator from a low voltage to a high voltage and the other logic-level translator from a high voltage to a low voltage.

The device features an extreme power-saving mode that reduces supply current to a typical  $0.01\mu$ A. The device also features thermal short-circuit protection on the VCC side for enhanced protection in applications that route signals externally.

#### Level Translation

For proper operation, ensure that  $2.3V \le V_{BAT} \le 5.5V$ ,  $1.6V \le V_L \le 5.5V$ . The device enters low-power shutdown mode when ENAB = ENCD = GND (see the *Functional Table*). In shutdown mode, the INAVL, INBVCC, INCVL, INDVCC, OUTAVCC and OUTCVCC are in high-impedance mode and the OUTBVL and OUTDVL are pulled down to GND. The maximum data rate depends heavily on the load capacitance (see the rise/fall times in the *Typical Operating Characteristics*), output impedance of the driver, and the operating voltage range.

#### **Output Load Requirements**

The device is designed to drive a wide variety of load types including a high capacitive load. To protect the VCC outputs (OUTAVCC, OUTCVCC) from a harsh external environment, the VCC outputs are ruggedized with a high ESD-capable output structure. When the high capacitive load is connected to the VCC output side, the current is limited by the charge-pump circuit along with the output driver impedance. The device is also protected by the thermal protection.

#### **Functional Diagram**

| INPUTS |      | DRIVERS OUTPUT EVENTS                                                                        |

|--------|------|----------------------------------------------------------------------------------------------|

| ENAB   | ENCD | DRIVERS OUTPUT EVENTS                                                                        |

| Low    | Low  | Device is in shutdown<br>OUTAVCC, OUTCVCC: high impedance<br>OUTBVL, OUTDVL: pulldown to GND |

| Low    | High | OUTAVCC: high impedance<br>OUTBVL: pulldown to GND<br>INCVL to OUTCVCC<br>INDVCC to OUTDVL   |

| High   | Low  | INAVL to OUTAVCC<br>INBVCC to OUTBVL<br>OUTCVCC: high impedance<br>OUTDVL: pulldown to GND   |

| High   | High | INAVL to OUTAVCC<br>INBVCC to OUTBVL<br>INCVL to OUTCVCC<br>INDVCC to OUTDVL                 |

### **Functional Table**

#### Shutdown Mode

The device features two enable inputs (ENAB, ENCD) that place the device into a low-power shutdown mode when both are driven low. If either ENAB or ENCD is pulled high, the internal charge pump starts working and generates 5V on V<sub>CC</sub>. When both ENAB and ENCD are driven low, the MAX14569 enters shutdown mode and draws a minimum current from V<sub>L</sub> and V<sub>BAT</sub>. To minimize supply current in shutdown mode, connect INAVL and INCVL to ground.

#### **Charge Pump**

The internal charge pump provides 5V on V<sub>CC</sub> when V<sub>BAT</sub> is between 2.7V and 4.5V. When V<sub>BAT</sub> is between 2.3V and 2.7V, V<sub>CC</sub> is twice the voltage of V<sub>BAT</sub>. The output is regulated to 5V as long as the battery voltage supports it.

#### **Thermal Protection**

The device features thermal shutdown function necessary to protect the device. When the junction temperature exceeds  $+150^{\circ}$ C (typ), the charge pump turns off and OUTAVCC, OUTBVL, OUTCVCC, OUTDVL are low. This limits the device temperature from rising further. When the temperature drops  $20^{\circ}$ C (typ) below  $+150^{\circ}$ C (typ), the device resumes normal operation.

### Applications Information

#### **Layout Recommendations**

Use standard high-speed layout practices when laying out a board with the device. For example, to minimize line coupling, place all other signal lines not connected to the device at least 1x the substrate height of the PCB away from the input and output lines of the device.

#### **Power-Supply Decoupling**

To reduce ripple and the chance of introducing data errors, bypass V<sub>L</sub> to ground with a  $0.1\mu F$  ceramic capacitor, V<sub>BAT</sub> to ground with a  $1\mu F$  ceramic capacitor, and V<sub>CC</sub> to ground with a  $2.2\mu F$  ceramic capacitor. Place all capacitors as close as possible to the power-supply inputs.

#### ±25kV ESD Protection

As with all Maxim devices, ESD protection structures are incorporated on all pins to protect against electrostatic

discharges encountered during handling and assembly. The OUTAVCC, INBVCC, OUTCVCC, INDVCC pins have extra protection against static electricity. Maxim's engineers have developed state-of-the-art structures to protect these pins against ESD of ±25kV without damage. The ESD structures withstand high ESD in all states: normal operation, shutdown, and powered down. After an ESD event, the device keeps working without latchup or damage.

ESD protection can be tested in various ways. The OUTAVCC, INBVCC, OUTCVCC, and INDVCC pins are characterized for protection to the following limits:

- ±25kV using the Human Body Model

- ±15kV using the Air-Gap Discharge Method specified in IEC 61000-4-2

- ±12kV using the Contact Discharge Method specified in IEC 61000-4-2

#### **ESD Test Conditions**

ESD performance depends on a variety of conditions. Contact Maxim for a reliability report that documents test setup, test methodology, and test results.

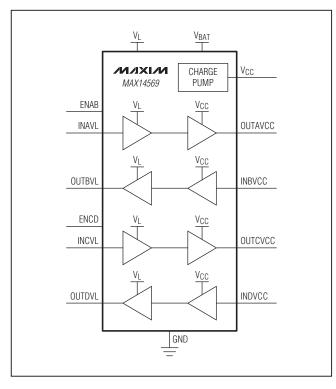

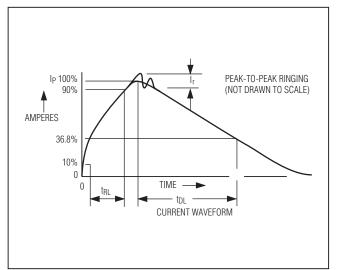

#### Human Body Model

Figure 3 shows the Human Body Model, and Figure 4 shows the current waveform it generates when discharged into a low-impedance state. This model consists of a 100pF capacitor charged to the ESD voltage of interest, which is then discharged into the test device through a  $1.5 \mathrm{k}\Omega$  resistor.

#### IEC 61000-4-2

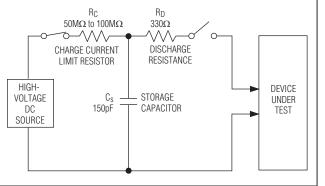

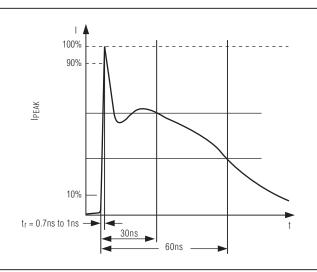

The IEC 61000-4-2 standard covers ESD testing and performance of finished equipment. It does not specifically refer to integrated circuits. The major difference between tests done using the Human Body Model and IEC 61000-4-2 is higher peak current in IEC 61000-4-2, because series resistance is lower in the IEC 61000-4-2 model. Hence, the ESD withstand voltage measured to IEC 61000-4-2 is generally lower than that measured using the Human Body Model. Figure 5 shows the IEC 61000-4-2 model, and Figure 6 shows the current waveform for the  $\pm$ 8kV, IEC 61000-4-2, level 4, ESD Contact Discharge Method.

Figure 3. Human Body ESD Test Model

Figure 4. Human Body Current Waveform

### Chip Information

PROCESS: BICMOS

Figure 5. IEC 61000-4-2 ESD Test Model

Figure 6. IEC 61000-4-2 ESD Generator Current Waveform

### **Package Information**

For the latest package outline information and land patterns, go to **www.maxim-ic.com/packages**. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE | PACKAGE | OUTLINE        | LAND           |

|---------|---------|----------------|----------------|

| TYPE    | CODE    | NO.            | PATTERN NO.    |

| 16 QSOP | E16+4   | <u>21-0055</u> | <u>90-0167</u> |

**Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION     | PAGES<br>CHANGED |

|--------------------|------------------|-----------------|------------------|

| 0                  | 9/10             | Initial release |                  |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

14

\_\_\_\_ Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2010 Maxim Integrated Products

Maxim is a registered trademark of Maxim Integrated Products, Inc.