## **General Description**

The MAX17122 multiple-output power-supply IC generates all the supply rails for thin-film transistor (TFT) liquidcrystal display (LCD) TV panels. It can operate from 8V to 16.5V input voltages and is optimized for LCD TV panel applications running directly from 12V regulated supplies. It includes a 22V internal-switch step-down regulator for digital logic, a 22V internal switch stepup regulator to power the TFT source drivers, and a temperature-compensated 36V internal-switch boostbuck regulator that produces a negative output that can vary according to the temperature sensed by an external NTC thermistor. All three of these regulators feature high-efficiency and fixed-frequency operation. Highfrequency operation allows the use of small inductors and capacitors, resulting in a compact solution.

The MAX17122 includes a positive charge-pump linear regulator controller that uses an external pnp bipolar junction transistor (BJT) to typically form a regulated charge-pump doubler to supply the LCD positive gate-driver supply voltage. A negative gate-driver supply is derived linearly between the boost-buck regulator's output and ground, using an external npn BJT connected to ground and a small bypass capacitor.

Other features include an external-capacitor-timed, open-drain, power-good output that monitors the stepdown regulator's feedback and a simple untimed output that monitors the positive charge-pump linear regulator's feedback. A high-voltage stress function is available for the step-up regulator output. The GATE output directly drives an external p-channel MOSFET to provide True Shutdown<sup>™</sup> of the step-up output.

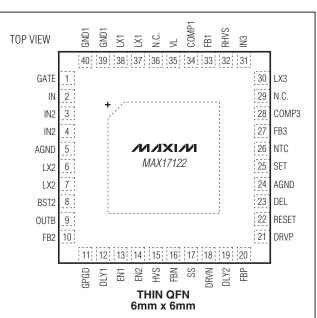

The MAX17122 is available in a 6mm x 6mm, 40-pin thin QFN lead-free package and operates over the -40°C to +85°C temperature range.

## Applications

LCD TV Panels

## \_**Features**

- ♦ 8V to 16.5V Operating Range

- ♦ 750kHz Switching Frequency

- ♦ 22V Internal-Switch High-Performance Step-Up Regulator

Fast Load-Transient ResponseCurrent-Mode PWM Operation100mΩ, 3.9A nMOS SwitchCapacitor-Adjustable Soft-StartHigh-Voltage Stress FunctionDrives External pMOS Shutdown Switch

- ◆ 22V Internal-Switch Step-Down Regulator Preset 1% Accurate 3.3V Output Voltage or Adjustable Output (Dual Mode™) Current-Mode PWM Operation 200mΩ, 2.5A nMOS Switch Capacitor-Adjustable Power-Good Output

- 36V Internal-Switch Boost-Buck Regulator Temperature-Compensated Output Programmable Fixed Levels with Temperature-Controlled Transition Current-Mode PWM Operation 200mΩ, 1.8A pMOS Switch

- Positive Charge-Pump Linear Regulator Controller Adjustable 1% Accurate Output Voltage Uses External pnp Transistor Regulates Switching-Node-Driven Charge-Pump Doubler Power-Good Output

- Negative Linear Regulator Controller Adjustable 1.5% Accurate Output Voltage Uses External npn Transistor

- Soft-Start for All Outputs

- ♦ Adjustable Power-Up Sequence

- Timed-Output Fault Protection with Restart for All Outputs

- Latched Thermal-Shutdown Protection

- 40-Pin, 6mm x 6mm Thin QFN Package

## **Ordering Information**

| PART         | TEMP RANGE     | PIN-PACKAGE |

|--------------|----------------|-------------|

| MAX17122ETL+ | -40°C to +85°C | 40 TQFN-EP* |

+Denotes a lead(Pb)-free/RoHS-compliant package. \*EP = Exposed pad.

*True Shutdown and Dual Mode are trademarks of Maxim Integrated Products, Inc.*

Pin Configuration appears at end of data sheet.

##

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

# MAX17122

## **ABSOLUTE MAXIMUM RATINGS**

IN, IN2, IN3, EN1, EN2, LX1, GATE,

| DRVP, RHVS to AGND                  | 0.3V to +22V                      |

|-------------------------------------|-----------------------------------|

| GATE to IN                          | 6.5V to +0.3V                     |

| GND1 to AGND                        | ±0.3V                             |

| DLY1, DLY2, DEL, VL, RESET, GPGD,   |                                   |

| HVS to AGND                         | 0.3V to +6V                       |

| FBP, FBN, FB1, FB2, FB3, COMP1, COM | 1P3, OUTB                         |

| SET, NTC, SS to AGND                | 0.3V to (V <sub>VL</sub> + 0.3V)  |

| DRVN to VL                          | 36V to +0.3V                      |

| LX2 to GND1                         | 0.3V to (V <sub>IN2</sub> + 0.3V) |

| LX3 to IN3                          | 36V to +0.3V                      |

| BST2 to VL                          | 0.3V to +22V                      |

| BST2 to LX20.3V to +6V<br>RMS LX1, GND1, IN2, IN3, LX3 Current (each pin)1.6A<br>RMS LX2 (total for both pins)2.4A |  |

|--------------------------------------------------------------------------------------------------------------------|--|

| RMS VL, DRVN, DRVP Current50mA                                                                                     |  |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )                                                              |  |

| 40-Pin Thin QFN                                                                                                    |  |

| (derate 35.7mW/°C above +70°C)2857.1mW                                                                             |  |

| Operating Temperature Range40°C to +85°C                                                                           |  |

| Junction Temperature+160°C                                                                                         |  |

| Storage Temperature Range65°C to +165°C                                                                            |  |

| _ead Temperature (soldering, 10s)+300°C                                                                            |  |

| Soldering Temperature (reflow)+260°C                                                                               |  |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS**

(Circuit of Figure 1, VIN = VIN2 = VIN3 = 12V, TA = 0°C to +85°C. Typical values are at TA = +25°C, unless otherwise noted.)

| PARAMETER                                | CONDITION                                                                                     | IS                                  | MIN    | ТҮР   | MAX    | UNITS   |

|------------------------------------------|-----------------------------------------------------------------------------------------------|-------------------------------------|--------|-------|--------|---------|

| GENERAL                                  | ·                                                                                             |                                     |        |       |        |         |

| IN, IN2, IN3<br>Input-Voltage Range      |                                                                                               |                                     | 8      |       | 16.5   | V       |

| IN + IN2 + IN3                           | Only LX2 and LX3 switching (VFB $1.1V$ , VFB3 = $1.8V$ , VFBN = $1.5V$ );                     |                                     |        | 10    | 15     |         |

| Quiescent Current                        | LX2 and LX3 not switching (VFB1 VFBN = $1.5$ V, VFB3 = 0); VEN1 = V                           |                                     |        | 2     | 4      | mA      |

| IN + IN2 + IN3<br>Shutdown Current       | EN1 = EN2 = AGND (shutdown)                                                                   |                                     |        | 0.55  | 1      | mA      |

| SMPS Operating Frequency                 |                                                                                               |                                     | 638    | 750   | 862    | kHz     |

| Phase Difference Between                 | Step-down and boost-buck                                                                      |                                     |        | 180   |        | Degrees |

| Regulators                               | Step-down and step-up                                                                         |                                     |        | 180   | Degree |         |

| IN Undervoltage-Lockout<br>Threshold     | V <sub>IN</sub> rising, 2.5% hysteresis                                                       |                                     | 6      | 7     | 8      | V       |

| VL REGULATOR                             |                                                                                               |                                     |        |       |        |         |

| VL Output Voltage                        | $I_{VL}$ = 10mA, $V_{FB1}$ = $V_{FB2}$ = $V_{FBP}$<br>$V_{FB3}$ = 1.8V (all regulators switch |                                     | 4.9    | 5.0   | 5.1    | V       |

| VL Undervoltage-Lockout<br>Threshold     | VL rising, 2.5% hysteresis                                                                    |                                     | 3.6    | 4.0   | 4.4    | V       |

| STEP-DOWN REGULATOR                      | ·                                                                                             |                                     |        |       |        |         |

| OLITE Voltage in Fixed Made              |                                                                                               | $T_A = +25^{\circ}C$                | 3.267  | 3.300 | 3.333  | V       |

| OUTB Voltage in Fixed Mode               | FB2 = AGND, no load (Note 1)                                                                  | $0^{\circ}C < T_{A} < +85^{\circ}C$ | 3.25   |       | 3.35   | V       |

| EB2 Voltago in Adjustable Mode           | V <sub>OUTB</sub> = 3.3V, no load (Note 1)                                                    | $T_A = +25^{\circ}C$                | 1.2375 | 1.250 | 1.2625 | V       |

| FB2 Voltage in Adjustable Mode           | 1001B - 3.3V, 10 10a0 (100e 1)                                                                | $0^{\circ}C < T_{A} < +85^{\circ}C$ | 1.23   |       | 1.27   | v       |

| FB2 Adjustable-Mode<br>Threshold Voltage | Dual-mode comparator                                                                          |                                     | 0.10   | 0.15  | 0.20   | V       |

## **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1, VIN = VIN2 = VIN3 = 12V, **TA = 0°C to +85°C**. Typical values are at TA = +25°C, unless otherwise noted.)

| PARAMETER                                      | CONDITI                        | ONS                                 | MIN  | TYP  | MAX  | UNITS |

|------------------------------------------------|--------------------------------|-------------------------------------|------|------|------|-------|

| Output Voltage Adjust Range                    | Step-down output               |                                     | 1.5  |      | 3.6  | V     |

| FB2 Fault-Trip Level                           | Falling edge                   |                                     | 0.96 | 1.0  | 1.04 | V     |

| FB2 Input-Bias Current                         | V <sub>FB2</sub> = 1.5V        |                                     | 50   | 125  | 200  | nA    |

| DC Load Regulation                             | 0.4A < ILOAD < 2A              |                                     |      | 0.5  |      | %     |

| DC Line Regulation                             | No load, 10.8V < VIN2 < 13.2V  |                                     |      | 0.1  |      | %/V   |

| LX2-to-IN2 nMOS Switch<br>On-Resistance        |                                |                                     |      | 200  | 400  | mΩ    |

| LX2-to-GND1 nMOS Switch<br>On-Resistance       |                                |                                     | 6    | 10   | 24   | Ω     |

| BST2-to-VL pMOS Switch<br>On-Resistance        |                                |                                     | 6    | 12   | 24   | Ω     |

| Low-Frequency Operation<br>OUTB Threshold      | LX2 only                       |                                     |      | 0.8  |      | V     |

| Low-Frequency Operation<br>Switching Frequency |                                |                                     |      | 188  |      | kHz   |

| LX2 Positive Current Limit                     |                                |                                     | 2.5  | 3.0  | 3.5  | A     |

| Soft-Start Ramp Time                           | Zero to full limit             |                                     |      | 3    |      | ms    |

| Maximum Duty Factor                            |                                |                                     | 68   | 75   | 82   | %     |

| BOOST-BUCK REGULATOR                           | · ·                            |                                     | ·    |      |      | •     |

| EP2 Degulation Valtage                         |                                | $T_A = +25^{\circ}C$                | 1.63 | 1.65 | 1.67 | V     |

| FB3 Regulation Voltage                         | No load, VNTC = 2V             | $0^{\circ}C < T_{A} < +85^{\circ}C$ | 1.62 | 1.65 | 1.68 | V     |

| FB3 Input-Bias Current                         | $V_{FB3} = 0.5V$               |                                     | -50  | -125 | -210 | nA    |

| FB3 Pulldown Resistance                        | EN1 = AGND                     |                                     | 300  |      | 1200 | Ω     |

| FB3 Fault-Trip Level                           | Rising edge                    |                                     | 1.9  | 2.0  | 2.1  | V     |

| DC Load Regulation                             | $0A < I_{LOAD} < 400mA$        |                                     |      | 0.3  |      | %     |

| DC Line Regulation                             | No load, 10.8V < VIN2 < 13.2V  |                                     |      | 0.1  |      | %/V   |

| LX3-to-IN3 pMOS Switch<br>On-Resistance        |                                |                                     |      | 200  | 400  | mΩ    |

| LX3 Positive Current Limit                     | Duty cycle = 60%               |                                     | 1.8  | 2.1  | 2.4  | A     |

| Soft-Start Ramp Time                           | Zero to full limit             |                                     |      | 3    |      | ms    |

| Maximum Duty Factor                            |                                |                                     | 85   | 89   | 94   | %     |

|                                                | 0°C < T <sub>A</sub> < +25°C   |                                     | 98   | 100  | 102  |       |

| NTC, SET Current                               | +25°C < T <sub>A</sub> < +85°C |                                     |      | 100  |      | μΑ    |

| NTC, SET Effective Voltage                     | 0°C < T <sub>A</sub> < +25°C   |                                     | 0.1  |      | 1.65 |       |

| Range                                          | +25°C < TA < +85°C             |                                     | 0.3  |      | 1.65 |       |

## **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1,  $V_{IN} = V_{IN2} = V_{IN3} = 12V$ , **T<sub>A</sub> = 0°C to +85°C**. Typical values are at T<sub>A</sub> = +25°C, unless otherwise noted.)

| PARAMETER                                                 | CONDITIO                                             | NS                           | MIN    | TYP   | MAX        | UNITS |

|-----------------------------------------------------------|------------------------------------------------------|------------------------------|--------|-------|------------|-------|

| STEP-UP REGULATOR                                         |                                                      |                              |        |       |            | 1     |

| Output-Voltage Range                                      |                                                      |                              | Vin    |       | 20         | V     |

| Oscillator Maximum Duty Cycle                             |                                                      |                              | 70     | 76    | 83         | %     |

|                                                           |                                                      | $T_A = +25^{\circ}C$         | 1.2375 | 1.250 | 1.2625     |       |

| FB1 Regulation Voltage                                    | VFB1 = COMP, CCOMP = 1nF                             | 0°C < T <sub>A</sub> < +85°C | 1.23   |       | 1.27       | V     |

| FB1 Output Undervoltage<br>Fault Trip Level               | Falling edge                                         |                              | 0.96   | 1.0   | 1.04       | V     |

| FB1 Output Short Trip Level                               | Falling edge                                         |                              | 0.35   | 0.375 | 0.4        | V     |

| FB1 Load Regulation                                       | $0 < I_{LOAD} < full, transient only$                |                              |        | -1    |            | %     |

| FB1 Line Regulation                                       | 10.8V < VIN < 13.2V                                  |                              |        | 0.08  | 0.15       | %/V   |

| FB1 Input-Bias Current                                    | VFB1 = 2V                                            |                              | 10     | 125   | 200        | nA    |

| FB1 Transconductance                                      | $\Delta I = \pm 2.5 \mu A$ at COMP, FB1 = C0         | OMP                          | 150    | 320   | 560        | μS    |

| FB1 Voltage Gain                                          | FB1 to COMP                                          |                              |        | 3500  |            | V/V   |

| LX1 Bias Current                                          | V <sub>FB1</sub> = 1.5V, V <sub>LX1</sub> = 20V      |                              |        | 10    | 40         | μA    |

| LX1 Current Limit                                         | $V_{FB1} = 1.1V$ , duty cycle = 25%                  |                              | 3.9    | 4.5   | 5.1        | A     |

| Current-Sense Transresistance                             |                                                      |                              | 0.16   | 0.23  | 0.3        | V/A   |

| LX1 On-Resistance                                         |                                                      |                              |        | 100   | 200        | mΩ    |

| SS Full Output Level                                      |                                                      |                              |        | 1.25  |            | V     |

| SS Charge Current                                         |                                                      |                              |        | 9     | 12         | μA    |

| POSITIVE CHARGE-PUMP LINE                                 | AR REGULATOR (DRVP)                                  |                              |        |       |            |       |

|                                                           |                                                      | $T_A = +25^{\circ}C$         | 1.2375 | 1.250 | 250 1.2625 |       |

| FBP Regulation Voltage                                    | $I_{DRVP} = 1.35 \text{mA}$                          | 0°C < T <sub>A</sub> < +85°C | 1.23   |       | 1.27       | V     |

| FBP Input-Bias Current                                    | VFBP = 1.25V                                         |                              | -50    |       | +50        | nA    |

| FBP Effective Load-Regulation<br>Error (Transconductance) | $V_{DRVP} = 15V$ , $I_{DRVP} = 0.6mA$ to             | 6mA                          |        | 15    | 30         | mV    |

| DRVP Sink Current                                         | V <sub>DRVP</sub> = 15V, V <sub>FBP</sub> = 1.1V     |                              | 10     |       | 30         | mA    |

| DRVP Off-Leakage Current                                  | VDRVP = 15V, VFBP = 1.5V                             |                              |        | 0.1   | 10         | μA    |

| FBP Fault-Trip Level                                      | Falling edge                                         |                              | 0.96   | 1.0   | 1.04       | V     |

| Positive Regulator Soft-Start<br>Period                   | 7-bit voltage ramp with filtering to currents        | to prevent high peak         |        | 3     |            | ms    |

| NEGATIVE LINEAR-REGULATO                                  | R CONTROLLER (DRVN)                                  |                              |        |       |            |       |

|                                                           |                                                      | $T_A = +25^{\circ}C$         | 0.985  | 1     | 1.015      |       |

| FBN Regulation Voltage                                    | $I_{DRVN} = 1.35 \text{mA}$                          | 0°C < T <sub>A</sub> < +85°C | 0.98   | 1     | 1.02       | V     |

| FBN Input-Bias Current                                    |                                                      | ·                            | -50    |       | +50        | nA    |

| FBN Pulldown Resistance                                   | EN1 = AGND                                           |                              | 250    |       | 1000       | Ω     |

| FBN Fault-Trip Level                                      | Falling edge                                         |                              | 0.45   | 0.5   | 0.55       | V     |

| FBN Effective Load-Regulation<br>Error (Transconductance) | V <sub>DRVN</sub> = -7.5V, I <sub>DRVN</sub> = 0.6mA | to 6mA                       |        | 23    | 46         | mV    |

| DRVN Source Current                                       | V <sub>DRVN</sub> = -7.5V, V <sub>FBN</sub> = 0.85V  |                              | 10     |       |            | mA    |

| DRVN Off-Leakage Current                                  | VDRVN = -7.5V, VFBN = 1.15V                          |                              |        |       | 40         | μA    |

## **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1, VIN = VIN2 = VIN3 = 12V, **TA = 0°C to +85°C**. Typical values are at TA = +25°C, unless otherwise noted.)

| PARAMETER                                         | CONDITIONS                 | MIN   | TYP  | MAX   | UNITS |

|---------------------------------------------------|----------------------------|-------|------|-------|-------|

| POWER-GOOD BLOCKS                                 |                            |       |      |       |       |

| FB2 Power-Good Threshold                          | FB2 rising                 | 0.975 | 1.00 | 1.025 | V     |

| FB2 Threshold Hysteresis                          |                            |       | 12   |       | mV    |

| RESET Output Low Voltage                          | IRESET = 1mA               |       |      | 0.4   | V     |

| RESET Leakage Current                             | V <sub>RESET</sub> = 3V    |       |      | 1     | μA    |

| FBP Power-Good Threshold                          | FBP rising                 | 1.1   | 1.15 | 1.2   | V     |

| FBP Threshold Hysteresis                          |                            |       | 125  |       | mV    |

| GPGD Output Low Voltage                           | IGPGD = 1mA                |       |      | 0.4   | V     |

| GPGD Leakage Current                              | VGPGD = 3V                 |       |      | 1     | μA    |

| GATE FUNCTION                                     |                            |       |      |       |       |

|                                                   | GATE charging current      |       | 0.15 |       | mA    |

| GATE Pulldown Current                             | Gate done current          |       | 0.62 |       |       |

| GATE Drive Voltage                                | VIN2 - VGATE, GATE enabled | 5.0   | 5.35 | 5.65  | V     |

| GATE Pullup Resistance                            | GATE off, to IN2           |       | 25   |       | Ω     |

| HVS BLOCK                                         |                            |       |      |       |       |

| HVS Input Low Voltage                             |                            |       |      | 0.6   | V     |

| HVS Input High Voltage                            |                            | 1.85  |      |       | V     |

| HVS Input Pulldown Resistance                     |                            |       | 1    |       | MΩ    |

| RHVS Output Resistance                            | I <sub>RHVS</sub> = 4mA    |       | 25   |       | Ω     |

| SEQUENCE CONTROL                                  |                            |       |      |       |       |

| EN1, EN2, DLY1, DLY2, DEL<br>Charge Current       | Measured at 1V             | 6     | 8.5  | 11    | μA    |

| EN1, EN2, DLY1, DLY2, DEL<br>Turn-On Threshold    |                            |       | 1.25 | 1.30  | V     |

| EN1, EN2 Discharge Switch<br>On-Resistance        | VL < UVLO or fault tripped |       | 50   |       | Ω     |

| DLY1, DLY2, DLP Discharge<br>Switch On-Resistance | EN1 = low or fault tripped |       | 10   |       | Ω     |

| FAULT DETECTION                                   | •                          |       |      |       |       |

| Duration to Trigger Fault                         |                            |       | 50   |       | ms    |

| Duration to Restart After Fault                   |                            |       | 160  |       | ms    |

| Thermal-Shutdown Threshold                        | Typical hysteresis = 15°C  |       | +160 |       | °C    |

### **ELECTRICAL CHARACTERISTICS**

(Circuit of Figure 1,  $V_{IN} = V_{IN2} = V_{IN3} = 12V$ , **TA = -40°C to +85°C**.) (Note 2)

| PARAMETER                                | CONDITIO                                                                                                                 | NS                                                                                                                                                                                              | MIN  | TYP | MAX  | UNITS |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|-------|

| GENERAL                                  | L                                                                                                                        |                                                                                                                                                                                                 |      |     |      |       |

| IN, IN2, IN3<br>Input-Voltage Range      |                                                                                                                          |                                                                                                                                                                                                 | 8    |     | 16.5 | V     |

| IN + IN2 + IN3<br>Quiescent Current      |                                                                                                                          | Dnly LX2 and LX3 switching (V <sub>FB1</sub> = V <sub>FBP</sub> = 1.5V, V <sub>FB2</sub> =<br>1.1V, V <sub>FB3</sub> = 1.8V, V <sub>FBN</sub> = 1.5V); V <sub>EN1</sub> = V <sub>EN2</sub> = 5V |      |     | 15   | mA    |

| IN + IN2 + IN3<br>Quiescent Current      | LX2 and LX3 not switching (V <sub>FB1</sub> V <sub>FBN</sub> = $1.5V$ , V <sub>FB3</sub> = 0); V <sub>EN1</sub> = $1.5V$ |                                                                                                                                                                                                 |      |     | 4    | mA    |

| IN + IN2 + IN3<br>Shutdown Current       | EN1 = EN2 = AGND (shutdown)                                                                                              |                                                                                                                                                                                                 |      |     | 1    | mA    |

| SMPS Operating Frequency                 |                                                                                                                          |                                                                                                                                                                                                 | 638  |     | 862  | kHz   |

| IN Undervoltage-Lockout<br>Threshold     | VIN rising, 2.5% hysteresis                                                                                              |                                                                                                                                                                                                 | 6    |     | 8    | V     |

| VL REGULATOR                             | 1                                                                                                                        |                                                                                                                                                                                                 |      |     |      |       |

| VL Output Voltage                        | $V_{FB3} = 1.8V$ (all regulators switch                                                                                  |                                                                                                                                                                                                 | 4.9  |     | 5.1  | V     |

| VL Undervoltage-Lockout<br>Threshold     | VL rising, 2.5% hysteresis                                                                                               |                                                                                                                                                                                                 | 3.6  |     | 4.4  | V     |

| STEP-DOWN REGULATOR                      |                                                                                                                          |                                                                                                                                                                                                 |      |     |      |       |

| OUTB Voltage in Fixed Mode               | FB2 = AGND, no load (Note 1)                                                                                             | -40°C < TA < +85°C                                                                                                                                                                              | 3.25 |     | 3.35 | V     |

| FB2 Voltage in Adjustable Mode           | V <sub>OUTB</sub> = 3.3V, no load (Note 1)                                                                               | -40°C < T <sub>A</sub> < +85°C                                                                                                                                                                  | 1.23 |     | 1.27 | V     |

| FB2 Adjustable-Mode<br>Threshold Voltage | Dual-mode comparator                                                                                                     |                                                                                                                                                                                                 | 0.10 |     | 0.20 | V     |

| Output Voltage Adjust Range              | Step-down output                                                                                                         |                                                                                                                                                                                                 | 1.5  |     | 3.6  | V     |

| FB2 Fault-Trip Level                     | Falling edge                                                                                                             |                                                                                                                                                                                                 | 0.96 |     | 1.04 | V     |

| FB2 Input-Bias Current                   | VFB2 = 1.5V                                                                                                              |                                                                                                                                                                                                 | 50   |     | 200  | nA    |

| LX2-to-IN2 nMOS Switch<br>On-Resistance  |                                                                                                                          |                                                                                                                                                                                                 |      |     | 400  | mΩ    |

| LX2-to-GND1 nMOS Switch<br>On-Resistance |                                                                                                                          |                                                                                                                                                                                                 | 6    |     | 24   | Ω     |

| BST2-to-VL pMOS Switch<br>On-Resistance  |                                                                                                                          |                                                                                                                                                                                                 | 6    |     | 24   | Ω     |

| LX2 Positive Current Limit               |                                                                                                                          |                                                                                                                                                                                                 | 2.5  |     | 3.5  | A     |

| Maximum Duty Factor                      |                                                                                                                          |                                                                                                                                                                                                 | 68   |     | 82   | %     |

| BUCK-BOOST REGULATOR                     |                                                                                                                          |                                                                                                                                                                                                 |      |     |      |       |

| FB3 Regulation Voltage                   | No load, $V_{NTC} = 2V$                                                                                                  | $-40^{\circ}C < T_A < +85^{\circ}C$                                                                                                                                                             | 1.62 |     | 1.68 | V     |

| FB3 Input-Bias Current                   | VFB3 = 0.5V                                                                                                              |                                                                                                                                                                                                 | -50  |     | -210 | nA    |

| FB3 Pulldown Resistance                  | EN1 = AGND                                                                                                               |                                                                                                                                                                                                 |      |     | 1200 | Ω     |

| FB3 Fault-Trip Level                     | Rising edge                                                                                                              |                                                                                                                                                                                                 | 1.9  |     | 2.1  | V     |

| LX3-to-IN3 pMOS Switch<br>On-Resistance  |                                                                                                                          |                                                                                                                                                                                                 |      |     | 400  | mΩ    |

## **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1, VIN = VIN2 = VIN3 = 12V, **TA = -40°C to +85°C**.) (Note 2)

| PARAMETER                                                 | CONDITI                                              | ONS                                             | MIN  | TYP | MAX  | UNITS |

|-----------------------------------------------------------|------------------------------------------------------|-------------------------------------------------|------|-----|------|-------|

| LX3 Positive Current Limit                                | Duty cycle = 60%                                     |                                                 | 1.8  |     | 2.4  | A     |

| Maximum Duty Factor                                       |                                                      |                                                 |      |     | 94   | %     |

| NTC, SET Current                                          | -40°C < T <sub>A</sub> < +25°C                       |                                                 | 97   |     | 104  | μA    |

| NTC, SET Effective Voltage                                | 0°C < T <sub>A</sub> < +25°C                         |                                                 | 0.1  |     | 1.65 |       |

| Range                                                     | +25°C < T <sub>A</sub> < +85°C                       |                                                 | 0.3  |     | 1.65 | V     |

| STEP-UP REGULATOR                                         |                                                      |                                                 |      |     |      |       |

| Output-Voltage Range                                      |                                                      |                                                 | VIN  |     | 20   | V     |

| Oscillator Maximum Duty Cycle                             |                                                      |                                                 | 70   |     | 83   | %     |

| FB1 Regulation Voltage                                    | FB1 = COMP, C <sub>COMP</sub> = 1nF                  | -40°C < T <sub>A</sub> < +85°C                  | 1.23 |     | 1.27 | V     |

| FB1 Output Undervoltage<br>Fault-Trip Level               | Falling edge                                         |                                                 | 0.96 |     | 1.04 | V     |

| FB1 Output Short-Trip Level                               | Falling edge                                         |                                                 | 0.35 |     | 0.4  | V     |

| FB1 Line Regulation                                       | 10.8V < V <sub>IN</sub> < 13.2V                      |                                                 |      |     | 0.15 | %/V   |

| FB1 Input-Bias Current                                    | $V_{FB1} = 2V$                                       |                                                 | 10   |     | 200  | nA    |

| FB1 Transconductance                                      | $\Delta I = \pm 2.5 \mu A$ at COMP, FB1 = C          | COMP                                            | 150  |     | 560  | μS    |

| LX1 Bias Current                                          | V <sub>FB1</sub> = 1.5V, V <sub>LX1</sub> = 20V      |                                                 |      |     | 40   | μA    |

| LX1 Current Limit                                         | VFB1 = 1.1V, duty cycle = 25%                        |                                                 | 3.9  |     | 5.1  | A     |

| Current-Sense Transresistance                             |                                                      |                                                 | 0.16 |     | 0.3  | V/A   |

| LX1 On-Resistance                                         |                                                      |                                                 |      |     | 200  | mΩ    |

| SS Charge Current                                         |                                                      |                                                 | 6    |     | 12   | μA    |

| POSITIVE CHARGE-PUMP LINE                                 | EAR REGULATOR (DRVP)                                 |                                                 |      |     |      |       |

| FBP Regulation Voltage                                    | I <sub>DRVP</sub> = 1.35mA                           | -40°C < T <sub>A</sub> < +85°C                  | 1.23 |     | 1.27 | V     |

| FBP Input-Bias Current                                    | VFBP = 1.25V                                         |                                                 | -50  |     | +50  | nA    |

| FBP Effective Load-Regulation<br>Error (Transconductance) | $V_{DRVP} = 15V$ , $I_{DRVP} = 0.6mA$ t              | o 6mA                                           |      |     | 30   | mV    |

| DRVP Sink Current                                         | V <sub>DRVP</sub> = 15V, V <sub>FBP</sub> = 1.1V     |                                                 | 10   |     | 30   | mA    |

| DRVP Off-Leakage Current                                  | V <sub>DRVP</sub> = 15V, V <sub>FBP</sub> = 1.5V     |                                                 |      |     | 10   | μA    |

| FBP Fault-Trip Level                                      | Falling edge                                         |                                                 | 0.96 |     | 1.04 | V     |

| NEGATIVE LINEAR-REGULATO                                  | OR CONTROLLER (DRVN)                                 |                                                 | 1    |     |      | 1     |

| FBN Regulation Voltage                                    | I <sub>DRVN</sub> = 1.35mA                           | -40°C < TA < +85°C                              | 0.98 |     | 1.02 | V     |

| FBN Input-Bias Current                                    |                                                      |                                                 | -50  |     | +50  | nA    |

| FBN Pulldown Resistance                                   | EN1 = AGND                                           |                                                 | 250  |     | 1000 | Ω     |

| FBN Fault-Trip Level                                      | Falling edge                                         |                                                 | 0.45 |     | 0.55 | V     |

| FBN Effective Load-Regulation<br>Error (Transconductance) | V <sub>DRVN</sub> = -7.5V, I <sub>DRVN</sub> = 0.6mA | $V_{DRVN} = -7.5V$ , $I_{DRVN} = 0.6$ mA to 6mA |      |     | 46   | mV    |

| DRVN Source Current                                       | VDRVN = -7.5V, VFBN = 0.85V                          |                                                 | 10   |     |      | mA    |

| DRVN Off-Leakage Current                                  | V <sub>DRVN</sub> = -7.5V, V <sub>FBN</sub> = 1.15V  |                                                 |      |     | 40   | μA    |

## **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1, VIN = VIN2 = VIN3 = 12V, **TA = -40°C to +85°C**.) (Note 2)

| PARAMETER                                      | CONDITIONS                 | MIN TY | P MAX | UNITS |

|------------------------------------------------|----------------------------|--------|-------|-------|

| POWER-GOOD BLOCKS                              |                            | l      |       |       |

| FB2 Power-Good Threshold                       | FB2 rising                 | 0.975  | 1.025 | V     |

| RESET Output Low Voltage                       | IRESET = 1mA               |        | 0.4   | V     |

| RESET Leakage Current                          | V <sub>RESET</sub> = 3V    |        | 1     | μA    |

| FBP Power-Good Threshold                       | FBP rising                 | 1.1    | 1.2   | V     |

| GPGD Output Low Voltage                        | IGPGD = 1mA                |        | 0.4   | V     |

| GPGD Leakage Current                           | VGPGD = 3V                 |        | 1     | μA    |

| GATE FUNCTION                                  |                            |        |       |       |

| GATE-Drive Voltage                             | VIN2 - VGATE, GATE enabled | 5.0    | 5.65  | V     |

| HVS BLOCK                                      |                            | · · ·  |       |       |

| HVS Input Low Voltage                          |                            |        | 0.6   | V     |

| HVS Input High Voltage                         |                            | 1.85   |       | V     |

| SEQUENCE CONTROL                               |                            |        |       |       |

| EN1, EN2, DLY1, DLY2, DEL<br>Charge Current    | Measured at 1V             | 6      | 11    | μA    |

| EN1, EN2, DLY1, DLY2, DEL<br>Turn-On Threshold |                            |        | 1.30  | V     |

**Note 1:** When the inductor is in continuous conduction (EN2 = VL or heavy load), the output voltage has a DC regulation level lower than the error-comparator threshold by 50% of the output-voltage ripple. In discontinuous conduction (light load), the step-down regulator's output voltage has a DC regulation level higher than the error-comparator threshold by up to 50% of the output-voltage ripple.

Note 2: Specifications to -40°C are guaranteed by design, not production tested.

## **Typical Operating Characteristics**

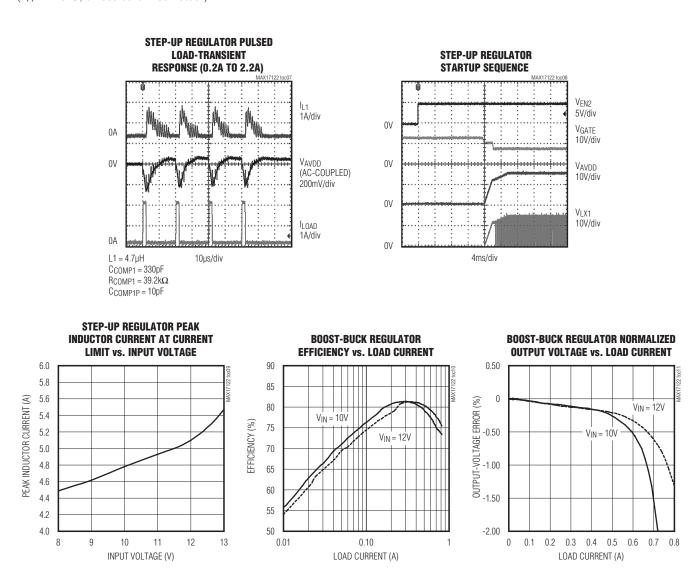

**STEP-DOWN REGULATOR EFFICIENCY STEP-DOWN REGULATOR NORMALIZED** vs. LOAD CURRENT **OUTPUT VOLTAGE vs. LOAD CURRENT** 90 0.6  $V_{IN} = 10V$ 0.4 85 0.2 OUTPUT-VOLTAGE ERROR (%)  $V_{IN} = 12V$ 0 80 EFFICIENCY (%)  $V_{IN} = 12V$ -0.2 -0.4 75 -0.6 70 -0.8  $V_{IN} = 10V$ -1.0 65 -1.2 60 -1.4 0.10 10 2.4 1 0 0.4 0.8 1.2 1.6 2.0 LOAD CURRENT (A) LOAD CURRENT (A) **STEP-DOWN REGULATOR LOAD-TRANSIENT STEP-UP REGULATOR EFFICIENCY RESPONSE (0.2A TO 1.7A)** vs. LOAD CURRENT 96 94 VIN = 12V 112 1A/div 92 0A  $V_{IN} = 10V$ EFFICIENCY (%) 90 V<sub>OUTB</sub> (AC-COUPLED) 88 0V 200mV/div 86 84 II OAD 82 1A/div 0A 80 0.01 0.10 10  $L = 4.7 \mu H$ 20µs/div 1 LOAD CURRENT (A) **STEP-UP REGULATOR NORMALIZED STEP-UP REGULATOR LOAD-TRANSIENT OUTPUT VOLTAGE vs. LOAD CURRENT** RESPONSE (0.2A TO 1.2A) 0.10 0.05 I<sub>L1</sub> 1A/div 0A VAVDD (AC-COUPLED) 0V 200mV/div V<sub>IN</sub> = 10V  $V_{IN} = 12V$ LOAD 0A -0.30 1A/div -0.35 0 0.5 2.5 10 15 20 L1 = 4.7µH 40µs/div C<sub>COMP1</sub> = 330pF LOAD CURRENT (A)  $R_{COMP1} = 39.2 k\Omega$

CCOMP1P = 10pF

$(T_A = +25^{\circ}C, unless otherwise noted.)$

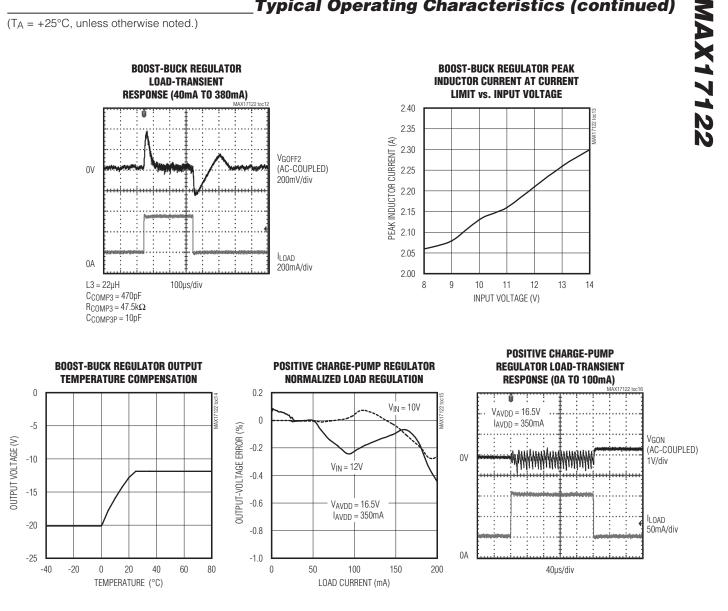

**Typical Operating Characteristics (continued)**

$(T_A = +25^{\circ}C, unless otherwise noted.)$

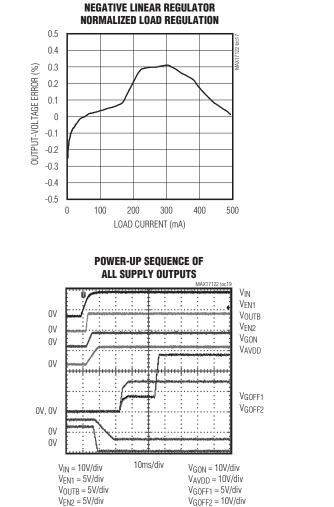

## **Typical Operating Characteristics (continued)**

$(T_A = +25^{\circ}C, unless otherwise noted.)$

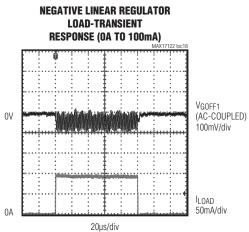

$(T_A = +25^{\circ}C, unless otherwise noted.)$

**Typical Operating Characteristics (continued)**

## Pin Description

| PIN   | NAME | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | GATE | External p-Channel MOSFET Control Output. When the step-up regulator is enabled, GATE pulls down to control the step-up output during its soft-start. Once GATE is fully on, the step-up regulator begins switching to regulate the final portion of its soft-start.                                                                                                                                                                                              |

| 2     | IN   | Input of the Internal 5V Linear Regulator and the Startup Circuitry. Bypass IN to AGND with $0.22 \mu F$ close to the IC.                                                                                                                                                                                                                                                                                                                                         |

| 3, 4  | IN2  | Step-Down Regulator Power Input. Drain of the internal n-channel MOSFET connected between IN2 and LX2.                                                                                                                                                                                                                                                                                                                                                            |

| 5, 24 | AGND | Analog Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6, 7  | LX2  | Step-Down Regulator Switching Node. LX2 is the source of the internal n-channel MOSFET connected between IN2 and LX2. Connect the inductor and Schottky catch diode to LX2 and minimize the trace area for low EMI.                                                                                                                                                                                                                                               |

| 8     | BST2 | Step-Down Regulator Bootstrap Capacitor Connection for High-Side Gate Driver. Connect a 0.1µF ceramic capacitor from BST2 to LX2.                                                                                                                                                                                                                                                                                                                                 |

| 9     | OUTB | Step-Down Regulator Output-Voltage Sense Input. Connect OUTB to the step-down regulator output.                                                                                                                                                                                                                                                                                                                                                                   |

| 10    | FB2  | Step-Down Regulator Feedback Input. Connect FB2 to AGND to select the step-down converter's 3.3V fixed mode. For adjustable mode, connect FB2 to the center of a resistive voltage-divider between the step-down regulator output and AGND to set the step-down regulator output voltage. Place the resistive voltage-divider within 5mm of FB2.                                                                                                                  |

| 11    | GPGD | GON Power-Good Signal Open-Drain Output. GPGD is connected to AGND whenever V <sub>FBP</sub> is less than the V <sub>FBP</sub> power-good threshold. GPGD is high impedance whenever V <sub>FBP</sub> is greater than the threshold.                                                                                                                                                                                                                              |

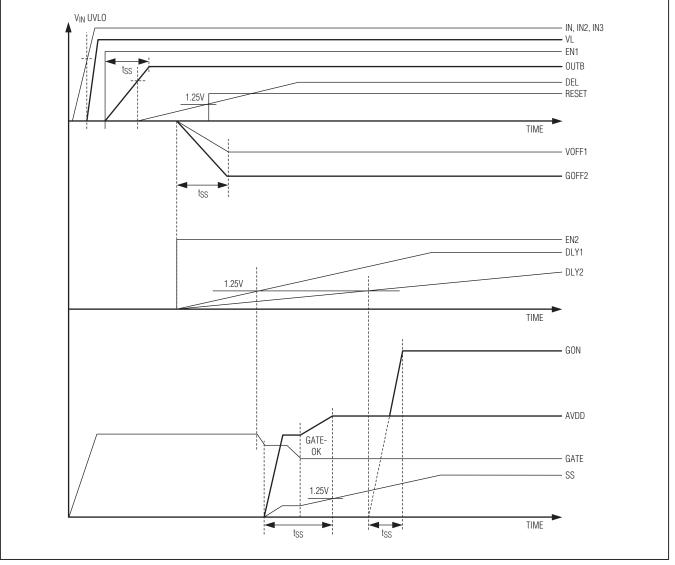

| 12    | DLY1 | Step-Up Regulator Delay Input. Connect a capacitor from DLY1 and AGND to set the delay time between EN2's rise and the step-up regulator's soft-start. An 8 $\mu$ A current source charges C <sub>DLY1</sub> . DLY1 is internally pulled to AGND whenever either EN1 or EN2 is low or VL is below its UVLO threshold.                                                                                                                                             |

| 13    | EN1  | Step-Down Enable Input. An 8µA current source charges the capacitor at EN1. When EN1 is high, the step-down regulator begins operating.                                                                                                                                                                                                                                                                                                                           |

| 14    | EN2  | Step-Up and Positive Charge-Pump Linear Regulator Enable Input. Negative linear regulator and boost-buck regulator enable input. An 8µA current source charges the capacitor at EN2. When EN2 is high, DLY1 and DLY2 begin charging. DLY1 starts GATE, which turns on the external p-channel MOSFET and the step-up regulator. DLY2 starts the positive charge-pump linear regulator. EN2 is inactive until after the step-down regulator soft-start is finished. |

| 15    | HVS  | High-Voltage Stress Mode Control Input. When HVS is high, the RHVS open-drain output connects to AGND. RHVS is high impedance when HVS is low.                                                                                                                                                                                                                                                                                                                    |

| 16    | FBN  | Negative Linear-Regulator Controller Feedback Input. Connect FBN to the center of a resistive voltage-divider between the negative output and a 3.3V reference to set the negative charge-pump regulator output voltage. Place the resistive voltage-divider within 5mm of FBN.                                                                                                                                                                                   |

## \_\_\_\_\_Pin Description (continued)

| PIN    | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                          |

|--------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17     | SS    | Step-Up Regulator Soft-Start Input. Connect a capacitor at SS to control the step-up regulator soft-<br>start ramp time. The capacitor charge current is 10µA and the SS voltage ramps from 0 to 1.25V<br>for a zero-to-full-scale regulated output.                                                                                                                                              |

| 18     | DRVN  | GOFF1 Negative Linear-Regulator Controller Base-Drive Output. Open drain of an internal p-channel MOSFET. Connect DRVN to the base of the external npn output transistor as shown in the typical operating circuit (Figure 1). The buffer can source current from ground to GOFF2 to maintain a regulated voltage on GOFF1 as measured at FBN.                                                    |

| 19     | DLY2  | Positive Charge-Pump Linear-Regulator Delay Input. Connect a capacitor from DLY2 to AGND to set the delay time between the step-up regulator and the startup of the positive charge pump. An $8\mu$ A current source charges C <sub>DLY2</sub> . DLY2 is internally pulled to AGND until the step-down soft-start is finished or when either EN1 or EN2 is low or VL is below its UVLO threshold. |

| 20     | FBP   | Positive Charge-Pump Linear-Regulator Feedback Input. Connect FBP to the center of a resistive voltage-divider between the positive charge-pump output and AGND to set the positive charge-pump output voltage. Place the resistive voltage-divider within 5mm of FBP.                                                                                                                            |

| 21     | DRVP  | Positive Charge-Pump Linear-Regulator Controller Base-Drive Output. Open drain of an internal n-channel MOSFET. Connect DRVP to the base of the external pnp transistor as shown in the typical operating circuit (Figure 1). The buffer can source current from AVDD to the charge-pump diodes to maintain a regulated voltage on GON as measured at FBP.                                        |

| 22     | RESET | Open-Drain Power-Good Output. Monitors the step-down output voltage. RESET is connected to AGND whenever the internal feedback voltage is less than its power-good threshold and DEL is less than 1.25V. RESET is high impedance whenever the internal feedback voltage is greater than the threshold and DEL is greater than 1.25V.                                                              |

| 23     | DEL   | Power-Good Reset Timing Pin. Connect a capacitor from DEL to AGND to set the step-down output-rising RESET delay. An 8µA current source charges C <sub>DEL</sub> .                                                                                                                                                                                                                                |

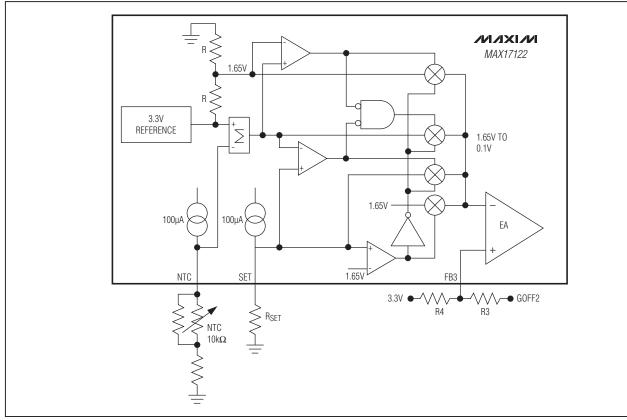

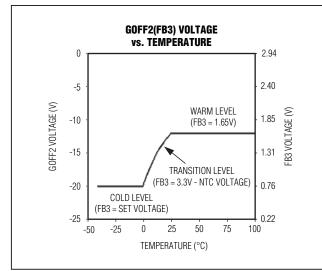

| 25     | SET   | GOFF2 Cold-Temperature Reference-Voltage Input. Connect a resistor from SET to AGND to set the cold-temperature GOFF2 reference level. The SET output current is 100µA (typ). Leave SET unconnected or connect to 3.3V if GOFF2 temperature compensation is not used.                                                                                                                             |

| 26     | NTC   | Thermistor Network Connection Input. Connect a network including a thermistor from NTC to AGND to control the temperature behavior of the GOFF2 output voltage. If thermal compensation is not used, NTC may be left unconnected or connected to AGND.                                                                                                                                            |

| 27     | FB3   | GOFF2 Regulator Feedback Input. FB3 regulates at 1.65V nominal and can vary from 0.1V to 1.65V with temperature according to the voltages on SET and NTC. Connect FB3 to the center of a resistive voltage-divider between the regulator output and a 3.3V reference to set the GOFF2 regulator output voltage.                                                                                   |

| 28     | COMP3 | Compensation Pin for the Boost-Buck Error Amplifier. Connect a series resistor and capacitor from COMP3 to AGND. Typical values are $5k\Omega$ and $4.7nF$ .                                                                                                                                                                                                                                      |

| 29, 36 | N.C.  | No Connection. Not internally connected.                                                                                                                                                                                                                                                                                                                                                          |

| 30     | LX3   | GOFF2 Boost-Buck Regulator Switching Node. LX3 is the source of the internal n-channel MOSFET connected between IN3 and LX3. Connect the inductor and Schottky catch diode to LX3 and minimize the trace area for low EMI.                                                                                                                                                                        |

**MAX17122**

## **Pin Description (continued)**

| PIN    | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                                                     |

|--------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31     | IN3   | Boost-Buck Regulator Power Input. Drain of the internal p-channel MOSFET connected between IN3 and LX3.                                                                                                                                                                                                                                                      |

| 32     | RHVS  | High-Voltage Stress Mode Output. When HVS is high, the RHVS open-drain output connects to AGND. RHVS is high impedance when HVS is low.                                                                                                                                                                                                                      |

| 33     | FB1   | Boost Regulator Feedback Input. Connect FB1 to the center of a resistive voltage-divider between the step-up regulator output and AGND to set the step-up regulator output voltage. Place the resistive voltage-divider within 5mm of FB1.                                                                                                                   |

| 34     | COMP1 | Compensation Pin for the Step-Up Error Amplifier. Connect a series resistor and capacitor from COMP1 to AGND. Typical values are $40k\Omega$ and $330pF$ .                                                                                                                                                                                                   |

| 35     | VL    | 5V Internal Linear-Regulator Output. Bypass VL to AGND with 1µF minimum. Provides power for the internal MOSFET driving circuits, the PWM controllers, charge-pump regulators, logic and references, and other analog circuitry. Provides 25mA load current when all switching regulators are enabled. VL is active whenever IN is above its UVLO threshold. |

| 37, 38 | LX1   | Step-Up Regulator Switching Node. LX1 is the drain of the internal n-channel MOSFET connected between LX1 and PGND. Connect the inductor and Schottky catch diode to both LX1 pins and minimize the trace area for low EMI.                                                                                                                                  |

| 39, 40 | GND1  | Step-Up Regulator Power Ground. Source of the internal power n-channel MOSFET.                                                                                                                                                                                                                                                                               |

| _      | EP    | Exposed Pad. Connect EP to the ground plane to maximize thermal dissipation.                                                                                                                                                                                                                                                                                 |

MAX17122

## **Typical Operating Circuit**

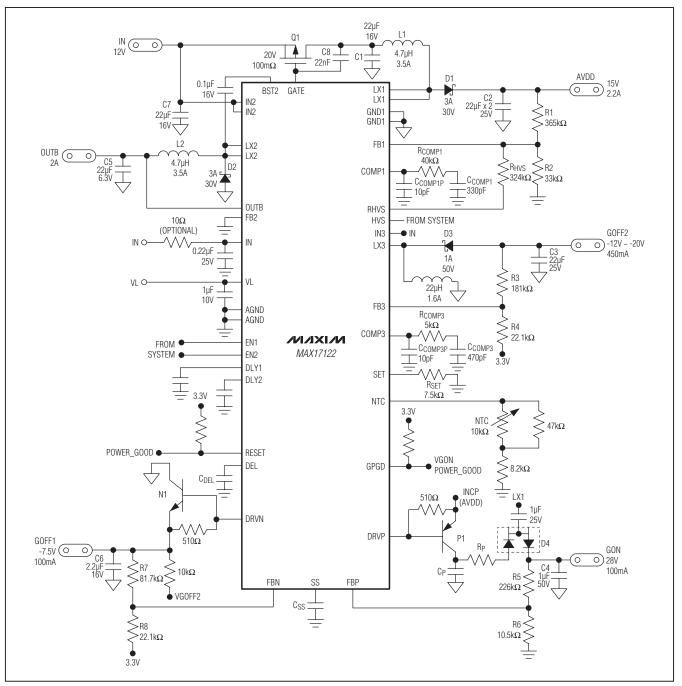

The typical operating circuit (Figure 1) of the MAX17122 is a complete power-supply system for TFT LCD TV panels. The circuit generates a +3.3V logic supply, a

+15V source driver supply, a +28V positive gate-driver supply, and a negative gate-driver supply that is derived linearly between -7.5V and -12V. Table 1 lists some selected components and Table 2 lists the contact information of component suppliers.

Figure 1. Typical Operating Circuit

### Table 1. Component List

| DESIGNATION | DESCRIPTION                                                                                                                     |

|-------------|---------------------------------------------------------------------------------------------------------------------------------|

| C1, C7      | 22μF ±20%, 16V X5R ceramic capaci-<br>tors (1206)<br>Murata GRM31CR61C226M                                                      |

| C2, C3      | Taiyo Yuden EMK316BJ226M<br>22µF ±20%, 25V X5R ceramic capaci-<br>tors (1210)<br>Murata GRM32ER61E226K<br>Murata GRM32ER61E226M |

| C4          | 1μF ±10%, 50V X7R ceramic capacitor<br>(1206)<br>Murata GRM31MR71H105KA<br>TDK C3216X7R1H105K                                   |

| C5          | 22μF ±20%, 6.3V X5R ceramic capacitor<br>(0805)<br>Murata GRM21BR60J226M<br>TDK C2012X5R0J226K                                  |

| C6          | 2.2µF ±10%, 16V X5R ceramic capacitor<br>(0603)<br>Murata GRM188R61C225K<br>TDK C1608Y5V1C225ZT                                 |

| D1, D2      | Schottky diodes 30V, 3A (M Flat)<br>Toshiba CMS02                                                                               |

| DESIGNATION | DESCRIPTION                                                                                 |  |  |

|-------------|---------------------------------------------------------------------------------------------|--|--|

| D3          | Schottky diode 50V, 1A (SMA)<br>Fairchild SS15<br>Diodes Inc. B150                          |  |  |

| D4          | Small-signal diode (SOT23)<br>Fairchild BAT54S<br>Diodes Inc. BAT54S                        |  |  |

| L1, L2      | Inductors, 4.7µH, 3.5A<br>TOKO FDV0620-4R7M<br>Sumida CDRH6D26HPNP-4R7P<br>NEC MPLC0730L4R7 |  |  |

| L3          | Inductor, 22µH, 1.6A<br>Sumida CDRH8D28NP-220N                                              |  |  |

| N1          | High-gain, 25V npn transistor (DPAK)<br>Fairchild KSH200<br>ON Semi MJD200                  |  |  |

| P1          | High gain, -25V pnp transistor (DPAK)<br>Fairchild KSH210<br>ON Semi MJD210                 |  |  |

| Q1          | -30V, 0.056 $\Omega$ p-channel MOSFET (6-pin SC70 PowerPAK)<br>Vishay SiA421DJ              |  |  |

## Table 2. Component Suppliers

| SUPPLIER                                    | PHONE        | FAX          | WEBSITE                     |

|---------------------------------------------|--------------|--------------|-----------------------------|

| Diodes Incorporated                         | 805-446-4800 | 805-446-4850 | www.diodes.com              |

| Fairchild Semiconductor                     | 408-822-2000 | 408-822-2102 | www.fairchildsemi.com       |

| Murata Electronics North America, Inc.      | 770-436-1300 | 770-436-3030 | www.murata-northamerica.com |

| ON Semiconductor                            | 888-743-7826 |              | www.onsemi.com              |

| Sumida Corp.                                | 847-545-6700 | 847-545-6720 | www.sumida.com              |

| TDK Corp.                                   | 847-803-6100 | 847-390-4405 | www.component.tdk.com       |

| Toshiba America Electronic Components, Inc. | 949-455-2000 | 949-859-3963 | www.toshiba.com/taec        |

## **Detailed Description**

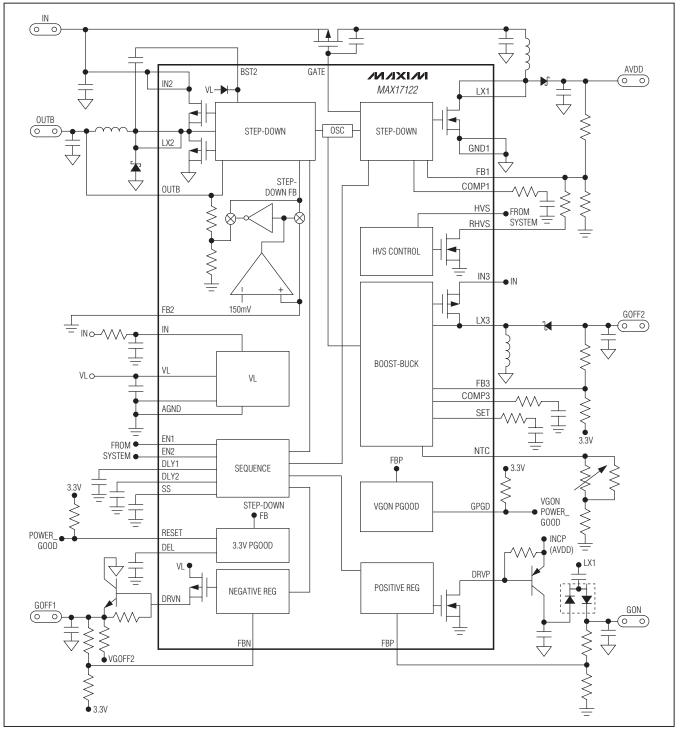

The MAX17122 is a multiple-output power supply designed primarily for TFT LCD TV panels. It contains a step-down switching regulator to generate the supply for system logic, a step-up switching regulator to generate the supply for source-driver ICs, a linear-controlled positive charge-pump regulator to generate the supply for TFT positive gate drivers, a boost-buck regulator, and a negative linear regulator to generate the supply for TFT negative gate drivers.

Each switching regulator features adjustable output voltage, digital soft-start, and timer-delayed fault protection.

They all use fixed-frequency (750kHz) current-mode control architectures. The step-up regulator switches in-phase with a boost-buck regulator while 180° out-of-phase with a step-down regulator to minimize the input ripple and noise coupling.

The boost-buck regulator also features a temperature-compensated output so it can vary according to the temperature sensed by an external NTC thermistor. The step-down regulator also features an adjustable-delay, open-drain, power-good output. A simple untimed output monitors the positive charge-pump linear regulator's feedback.

In addition, the MAX17122 features an internal 5V linear regulator, well-defined power-up and power-down sequences, and fault and thermal-overload protection. Figure 2 shows the MAX17122's functional diagram.

Figure 2. Functional Diagram

MAX17122

# **MAX17122**

# Step-Up, Step-Down Regulator, Gate-On Charge Pump, and Boost-Buck Regulator for TV TFT LCD Display

### **Step-Down Regulator**

The step-down regulator consists of an internal n-channel MOSFET with gate driver, a lossless current-sense network, a current-limit comparator, and a PWM controller block. The external power stage consists of a Schottky diode rectifier, an inductor, and output capacitors. The output voltage is regulated by changing the duty cycle of the high-side MOSFET. A bootstrap circuit that uses a 0.1 $\mu$ F flying capacitor between LX2 and BST provides the supply voltage for the high-side gate driver. Although the MAX17122 also includes a 10 $\Omega$  (typical) low-side MOSFET, this switch is used to charge the bootstrap capacitor during startup and maintains fixed-frequency operation at light load and cannot be used as a synchronous rectifier. An external Schottky diode (D2 in Figure 1) is always required.

### **PWM Controller Block**

The heart of the PWM controller block is a multi-input, open-loop comparator that sums three signals: the output voltage signal with respect to the reference voltage, the current-sense signal, and the slope compensation signal. The PWM controller is a direct-summing type, lacking a traditional error amplifier and the phase shift associated with it. This direct-summing configuration approaches ideal cycle-by-cycle control over the output voltage.

The step-down controller always operates in fixedfrequency PWM mode. Each pulse from the oscillator sets the main PWM latch that turns on the high-side switch until the PWM comparator changes state. As the high-side switch turns off, the low-side switch turns on. The low-side switch stays on until the beginning of the next clock cycle.

### Current Limiting and Lossless Current Sensing

The current-limit circuit turns off the high-side MOSFET switch whenever the voltage across the high-side MOSFET exceeds an internal threshold. The actual current limit is typically 3A.

For current-mode control, an internal lossless sense network derives a current-sense signal from the inductor DCR. The time constant of the current-sense network is not required to match the time constant of the inductor and has been chosen to provide sufficient current-ramp signal for stable operation. The current-sense signal is AC-coupled into the PWM comparator, eliminating most DC output-voltage variation with load current.

### Dual-Mode Feedback

The MAX17122's step-down regulator supports both fixed output and adjustable output. Connect FB2 to

AGND to enable the 3.3V fixed output voltage. Connect a resistive voltage-divider between OUTB and AGND with the center tap connected to FB2 to adjust the output voltage. Choose RB (resistance from FB2 to AGND) to be between 5k $\Omega$  and 50k $\Omega$ , and solve for RA (resistance from OUTB to FB2) using the following equation:

$$RA = RB \times \left(\frac{V_{OUTB}}{V_{FB2}} - 1\right)$$

where  $V_{FB2} = 1.25V$  and  $V_{OUTB}$  may vary from 1.5V to 5V.

### Soft-Start

The step-down regulator includes a 7-bit soft-start DAC that steps its internal reference voltage from 0 to 1.25V in 128 steps. The soft-start period is 3ms (typ) and FB2 fault detection is disabled during this period. The soft-start feature effectively limits the inrush current during startup (see the Step-Down Regulator Soft-Start Waveforms in the *Typical Operating Characteristics*).

### Step-Down Regulator Power Good (RESET)

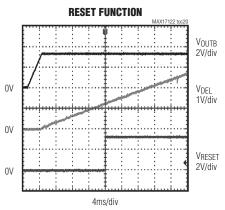

The RESET power-good block is an open-drain-type design with a capacitor-adjustable, active-low, output timing. The block monitors the step-down regulator feed-back node (FB2 in variable mode, or OUTB after divider in fixed mode) with a 1.0V threshold. The threshold has a 12mV (typ) hysteresis. RESET goes low when the monitored voltage is below the threshold. When the feedback node voltage rises above the 1.0V threshold, DEL starts to charge the capacitor connected there. RESET stays low until VDEL exceeds 1.25V.

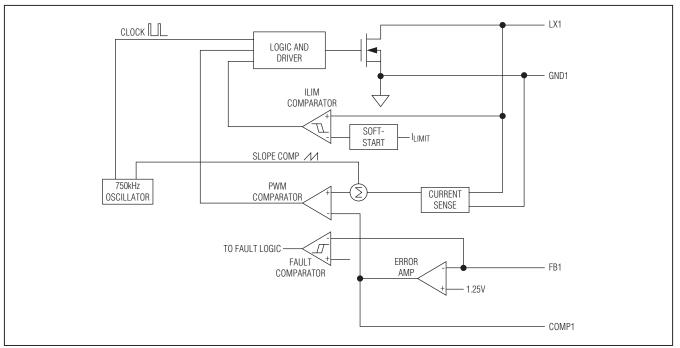

### **Step-Up Regulator**

The step-up regulator employs a current-mode, fixedfrequency PWM architecture to maximize loop bandwidth and provide fast-transient response to pulsed loads typical of TFT LCD panel source drivers. The integrated MOSFET and the built-in digital soft-start function reduce the number of external components required while controlling inrush currents. The output voltage can be set from V<sub>IN</sub> to 20V with an external resistive voltage-divider. (**Note:** If the HVS function is used, AVDD cannot be set to this maximum value under normal operating conditions.) The regulator controls the output voltage and the power delivered to the output by modulating duty cycle  $D_{SU}$  of the internal power MOSFET in each switching cycle. The duty cycle of the MOSFET is approximated by:

$$\mathsf{D}_{SU}\approx\frac{\mathsf{V}_{AVDD}+\mathsf{V}_{D1}-\mathsf{V}_{IN}}{\mathsf{V}_{AVDD}+\mathsf{V}_{D1}-\mathsf{V}_{LX1}}$$

where V<sub>AVDD</sub> is the output voltage of the step-up regulator, V<sub>D1</sub> is the voltage drop across diode D1, and V<sub>LX1</sub> is the voltage drop across the internal MOSFET. Figure 3 shows the step-up regulator block diagram.

### **PWM Controller Block**

An error amplifier compares the signal at FB1 to 1.25V and changes the COMP1 output. The voltage at COMP1 sets the peak inductor current. As the load varies, the error amplifier sources or sinks current to the COMP1 output accordingly to produce the inductor peak current necessary to service the load. To maintain stability at high duty cycles, a slope-compensation signal is summed with the current-sense signal.