# 4.5V–42V, 2.5A, High-Efficiency, Synchronous Step-Down DC-DC Converter with Internal Compensation

## **General Description**

The MAX17543 high-efficiency, high-voltage, synchronous step-down DC-DC converter with integrated MOSFETs operates over a 4.5V to 42V input. The converter can deliver up to 2.5A and generates output voltages from 0.9V up to 0.9 x V<sub>IN</sub>. The feedback (FB) voltage is accurate to within  $\pm$ 1.1% over -40°C to +125°C.

The MAX17543 uses peak current-mode control. The device can be operated in the pulse-width modulation (PWM), pulse-frequency modulation (PFM), or discontinuous conduction mode (DCM) control schemes.

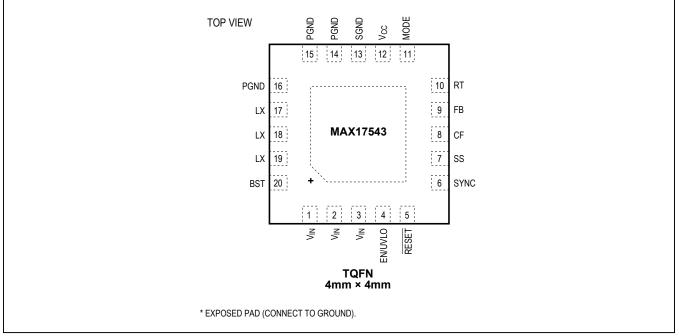

The device is available in a 20-pin (4mm x 4mm) TQFN package. Simulation models are available.

## **Applications**

- Industrial Power Supplies

- Distributed Supply Regulation

- High-Voltage Single-Board Systems

- Base Station Power Supply

- General-Purpose Point-of-Load

Ordering Information appears at end of data sheet.

## **Benefits and Features**

- Reduces External Components and Total Cost

- No Schottky—Synchronous Operation

- Internal Compensation for Any Output Voltage

- Built-In Soft-Start

- All-Ceramic Capacitors, Compact Layout

- Reduces Number of DC-DC Regulators to Stock

- Wide 4.5V to 42V Input

- Adjustable 0.9V to 0.9 x V<sub>IN</sub> Output

- 100kHz to 2.2MHz Adjustable Switching Frequency with External Synchronization

- Reduces Power Dissipation

- Peak Efficiency >90%

- PFM/DCM Enables Enhanced Light-Load Efficiency

- 2.8µA Shutdown Current

- Operates Reliably in Adverse Industrial Environments

Peak Current-Limit Protection

- Built-In Output Voltage Monitoring with RESET

- Programmable EN/UVLO Threshold

- Monotonic Startup into Prebiased Load

- Overtemperature Protection

- High Industrial -40°C to +125°C Ambient Operating Temperature Range/-40°C to +150°C Junction Temperature Range

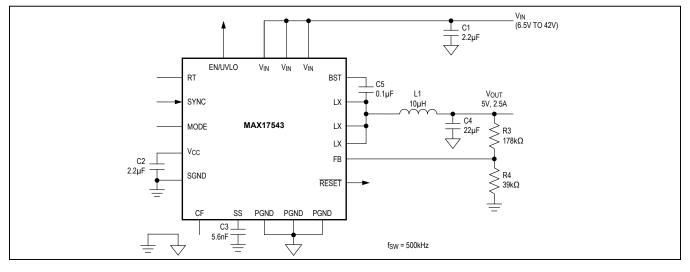

## Typical Application Circuit—5V, 500kHz Switching Frequency

# 4.5V–42V, 2.5A, High-Efficiency, Synchronous Step-Down DC-DC Converter with Internal Compensation

## **Absolute Maximum Ratings**

| V <sub>IN</sub> to PGND    | 0.3V to +48V                     |

|----------------------------|----------------------------------|

| EN/UVLO to SGND            | 0.3V to +48V                     |

| LX to PGND                 | 0.3V to (V <sub>IN</sub> + 0.3V) |

| BST to PGND                | -0.3V to +53V                    |

| BST to LX                  | 0.3V to +6.5V                    |

| BST to V <sub>CC</sub>     | 0.3V to +48V                     |

| CF, RESET, SS, MODE, SYNC, |                                  |

| RT to SGND                 | 0.3V to +6.5V                    |

| FB to SGND                 | 0.3V to +1.5V                    |

| V <sub>CC</sub> to SGND    | 0.3V to +6.5V                    |

| SGND to PGND                                             |                   |

|----------------------------------------------------------|-------------------|

| LX Total RMS Current                                     | ±4A               |

| Output Short-Circuit Duration                            | Continuous        |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) (n | nultilayer board) |

| TQFN (derate 30.3mW/°C above T <sub>A</sub> = +70°       | C)2424.2mW        |

| Junction Temperature                                     | +150°C            |

| Storage Temperature Range                                | -65°C to +160°C   |

| Lead Temperature (soldering, 10s)                        | +300°C            |

| Soldering Temperature (reflow)                           | +260°C            |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Junction temperature greater than +125°C degrades operating lifetimes.

## Package Thermal Characteristics (Note 1)

TQFN

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

## **Electrical Characteristics**

$(V_{IN} = V_{EN/UVLO} = 24V, R_{RT} = 40.2k\Omega$  (500kHz),  $C_{VCC} = 2.2\mu$ F,  $V_{PGND} = V_{SGND} = V_{MODE} = V_{SYNC} = 0V$ , LX = SS = RESET = open,  $V_{BST}$  to  $V_{LX} = 5V$ ,  $V_{FB} = 1V$ ,  $T_A = -40^{\circ}$ C to +125°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}$ C. All voltages are referenced to SGND, unless otherwise noted.) (Note 2)

| PARAMETER                            | SYMBOL               | CONDITIONS                                                | MIN   | TYP   | MAX   | UNITS |

|--------------------------------------|----------------------|-----------------------------------------------------------|-------|-------|-------|-------|

| INPUT SUPPLY (VIN)                   |                      |                                                           |       |       |       |       |

| Input Voltage Range                  | V <sub>IN</sub>      |                                                           | 4.5   |       | 42    | V     |

| Input Shutdown Current               | I <sub>IN-SH</sub>   | V <sub>EN/UVLO</sub> = 0V (shutdown mode)                 |       | 2.8   | 4.5   |       |

|                                      |                      | V <sub>FB</sub> = 1V, MODE = RT = open                    |       | 118   |       | μΑ    |

|                                      | IQ_PFM               | V <sub>FB</sub> = 1V, MODE = open                         |       | 162   |       | ]     |

| Input Quiescent Current              | I <sub>Q-DCM</sub>   | DCM mode, V <sub>LX</sub> = 0.1V                          |       | 1.16  | 1.8   |       |

|                                      | I <sub>Q_PWM</sub>   | Normal switching mode, $f_{SW}$ = 500kHz, $V_{FB}$ = 0.8V |       | 9.5   |       | mA    |

| ENABLE/UVLO (EN/UVLO)                |                      |                                                           |       |       |       |       |

| EN/UVLO Threshold                    | V <sub>ENR</sub>     | V <sub>EN/UVLO</sub> rising                               | 1.19  | 1.215 | 1.26  | v     |

| EN/OVEO Threshold                    | V <sub>ENF</sub>     | V <sub>EN/UVLO</sub> falling                              | 1.068 | 1.09  | 1.131 |       |

| EN/UVLO Input Leakage Current        | I <sub>EN</sub>      | V <sub>EN/UVLO</sub> = 0V, T <sub>A</sub> = +25°C         | -50   | 0     | +50   | nA    |

| LDO                                  |                      |                                                           |       |       |       |       |

|                                      |                      | 6V < V <sub>IN</sub> < 42V, I <sub>VCC</sub> = 1mA        | 4.75  | F     | 5.25  | V     |

| V <sub>CC</sub> Output Voltage Range | V <sub>CC</sub>      | $1mA \le I_{VCC} \le 25mA$                                | 4.75  | 5     |       | V     |

| V <sub>CC</sub> Current Limit        | I <sub>VCC-MAX</sub> | V <sub>CC</sub> = 4.3V, V <sub>IN</sub> = 6V              | 26.5  | 54    | 100   | mA    |

| V <sub>CC</sub> Dropout              | V <sub>CC-DO</sub>   | V <sub>IN</sub> = 4.5V, I <sub>VCC</sub> = 20mA           | 4.2   |       |       | V     |

| V 1040                               | V <sub>CC_UVR</sub>  | V <sub>CC</sub> rising                                    | 4.05  | 4.2   | 4.3   | v     |

| V <sub>CC</sub> UVLO                 | V <sub>CC_UVF</sub>  | V <sub>CC</sub> falling                                   | 3.65  | 3.8   | 3.9   |       |

# 4.5V–42V, 2.5A, High-Efficiency, Synchronous Step-Down DC-DC Converter with Internal Compensation

## **Electrical Characteristics (continued)**

$(V_{IN} = V_{EN/UVLO} = 24V, R_{RT} = 40.2k\Omega$  (500kHz),  $C_{VCC} = 2.2\mu$ F,  $V_{PGND} = V_{SGND} = V_{MODE} = V_{SYNC} = 0$ V, LX = SS =  $\overline{RESET}$  = open,  $V_{BST}$  to  $V_{LX} = 5V$ ,  $V_{FB} = 1V$ ,  $T_A = -40^{\circ}$ C to +125°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}$ C. All voltages are referenced to SGND, unless otherwise noted.) (Note 2)

| PARAMETER                                  | SYMBOL                  | CONDITIONS                                                                                               | MIN                      | TYP                 | MAX                      | UNITS |  |

|--------------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------|--------------------------|---------------------|--------------------------|-------|--|

| POWER MOSFET AND BST DRIV                  | ER                      |                                                                                                          |                          |                     |                          |       |  |

| High-Side nMOS On-Resistance               | R <sub>DS-ONH</sub>     | I <sub>LX</sub> = 0.3A                                                                                   |                          | 165                 | 325                      | mΩ    |  |

| Low-Side nMOS On-Resistance                | R <sub>DS-ONL</sub>     | I <sub>LX</sub> = 0.3A                                                                                   |                          | 80                  | 150                      | mΩ    |  |

| LX Leakage Current                         | I <sub>LX_LKG</sub>     | V <sub>LX</sub> = V <sub>IN</sub> - 1V, V <sub>LX</sub> = V <sub>PGND</sub> + 1V, T <sub>A</sub> = +25°C | -2                       |                     | +2                       | μA    |  |

| SOFT-START (SS)                            |                         |                                                                                                          |                          |                     |                          |       |  |

| Charging Current                           | I <sub>SS</sub>         | V <sub>SS</sub> = 0.5V                                                                                   | 4.7                      | 5                   | 5.3                      | μA    |  |

| FEEDBACK (FB)                              |                         |                                                                                                          |                          |                     |                          |       |  |

|                                            |                         | MODE = SGND or MODE = $V_{CC}$                                                                           | 0.89                     | 0.9                 | 0.91                     |       |  |

| FB Regulation Voltage                      | V <sub>FB_REG</sub>     | MODE = OPEN                                                                                              | 0.89                     | 0.915               | 0.936                    | V     |  |

| FB Input Bias Current                      | I <sub>FB</sub>         | 0 < V <sub>FB</sub> < 1V, T <sub>A</sub> = +25°C                                                         | -50                      |                     | +50                      | nA    |  |

| MODE                                       |                         |                                                                                                          |                          |                     |                          |       |  |

|                                            | V <sub>M-DCM</sub>      | MODE = V <sub>CC</sub> (DCM mode)                                                                        | V <sub>CC</sub> -<br>1.6 |                     |                          |       |  |

| MODE Threshold                             | V <sub>M-PFM</sub>      | MODE = open (PFM mode)                                                                                   |                          | V <sub>CC</sub> / 2 |                          | - V   |  |

|                                            | V <sub>M-PWM</sub>      | MODE = GND (PWM mode)                                                                                    | 1.4                      |                     | 1.4                      | 1     |  |

| CURRENT LIMIT                              | 1                       |                                                                                                          |                          |                     |                          | ,     |  |

| Peak Current-Limit Threshold               | I <sub>PEAK-LIMIT</sub> |                                                                                                          | 3.2                      | 3.7                 | 4.3                      | Α     |  |

| Runaway Current-Limit Threshold            | IRUNAWAY-LIMIT          |                                                                                                          | 3.7                      | 4.3                 | 5                        | Α     |  |

|                                            |                         | MODE = open/V <sub>CC</sub>                                                                              | -0.16                    | 0                   | +0.16                    |       |  |

| Valley Current-Limit Threshold             | ISINK-LIMIT MODI        | MODE = GND                                                                                               |                          | -1.8                |                          | - A   |  |

| PFM Current-Limit Threshold                | I <sub>PFM</sub>        | MODE = open                                                                                              | 0.6                      | 0.75                | 0.9                      | Α     |  |

| RT AND SYNC                                |                         |                                                                                                          |                          |                     |                          |       |  |

|                                            |                         | R <sub>RT</sub> = 210kΩ                                                                                  | 90                       | 100                 | 110                      |       |  |

|                                            |                         | R <sub>RT</sub> = 102kΩ                                                                                  | 180                      | 200                 | 220                      |       |  |

| Switching Frequency                        | f <sub>SW</sub>         | R <sub>RT</sub> = 40.2kΩ                                                                                 | 475                      | 500                 | 525                      | kHz   |  |

|                                            |                         | R <sub>RT</sub> = 8.06kΩ                                                                                 | 1950                     | 2200                | 2450                     | -     |  |

|                                            |                         | R <sub>RT</sub> = open                                                                                   | 460                      | 500                 | 540                      | 1     |  |

| SYNC Frequency Capture Range               |                         | f <sub>SW</sub> set by R <sub>RT</sub>                                                                   | 1.1 x<br>fsw             |                     | 1.4 x<br>f <sub>SW</sub> | kHz   |  |

| SYNC Pulse Width                           |                         |                                                                                                          | 50                       |                     |                          | ns    |  |

|                                            | VIH                     |                                                                                                          | 2.1                      |                     |                          |       |  |

| SYNC Threshold                             | VIL                     |                                                                                                          |                          |                     | 0.8                      | V     |  |

| FB Undervoltage Trip Level to Cause Hiccup | V <sub>FB-HICF</sub>    |                                                                                                          | 0.56                     | 0.58                | 0.65                     | v     |  |

# 4.5V–42V, 2.5A, High-Efficiency, Synchronous Step-Down DC-DC Converter with Internal Compensation

## **Electrical Characteristics (continued)**

$(V_{IN} = V_{EN/UVLO} = 24V, R_{RT} = 40.2k\Omega$  (500kHz),  $C_{VCC} = 2.2\mu$ F,  $V_{PGND} = V_{SGND} = V_{MODE} = V_{SYNC} = 0$ V, LX = SS =  $\overline{RESET}$  = open,  $V_{BST}$  to  $V_{LX} = 5V$ ,  $V_{FB} = 1V$ ,  $T_A = -40^{\circ}$ C to +125°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}$ C. All voltages are referenced to SGND, unless otherwise noted.) (Note 2)

| PARAMETER                                                  | SYMBOL              | CONDITIONS                                              | MIN  | TYP    | MAX  | UNITS                    |

|------------------------------------------------------------|---------------------|---------------------------------------------------------|------|--------|------|--------------------------|

| Hiccup Timeout                                             |                     | (Note 3)                                                |      | 32,768 |      | Cycles                   |

| Minimum On-Time                                            | t <sub>ON-MIN</sub> |                                                         |      |        | 135  | ns                       |

| Minimum Off-Time                                           | toff-min            |                                                         | 140  |        | 160  | ns                       |

| LX Dead Time                                               |                     |                                                         |      | 5      |      | ns                       |

| RESET                                                      |                     |                                                         |      |        |      |                          |

| RESET Output Level Low                                     |                     | I <sub>RESET</sub> = 10mA                               |      |        | 0.4  | V                        |

| RESET Output Leakage Current                               |                     | $T_A = T_J = +25^{\circ}C, V_{\overline{RESET}} = 5.5V$ | -0.1 |        | +0.1 | μA                       |

| FB Threshold for RESET Assertion                           | V <sub>FB-OKF</sub> | V <sub>FB</sub> falling                                 | 90.5 | 92     | 94.6 | %V <sub>FB-</sub><br>REG |

| FB Threshold for RESET<br>Deassertion                      | V <sub>FB-OKR</sub> | V <sub>FB</sub> rising                                  | 93.8 | 95     | 97.8 | %V <sub>FB-</sub><br>REG |

| RESET Deassertion Delay After FB<br>Reaches 95% Regulation |                     |                                                         |      | 1024   |      | Cycles                   |

| THERMAL SHUTDOWN                                           |                     |                                                         |      |        |      |                          |

| Thermal Shutdown Threshold                                 |                     | Temperature rising                                      |      | 165    |      | °C                       |

| Thermal Shutdown Hysteresis                                |                     |                                                         |      | 10     |      | °C                       |

Note 2: All limits are 100% tested at +25°C. Limits over temperature are guaranteed by design.

Note 3: See the Overcurrent Protection/Hiccup Mode section for more details.

# 4.5V–42V, 2.5A, High-Efficiency, Synchronous Step-Down DC-DC Converter with Internal Compensation

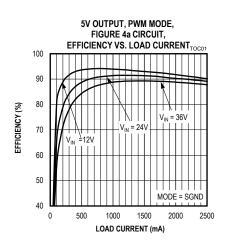

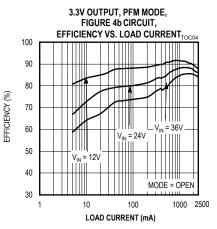

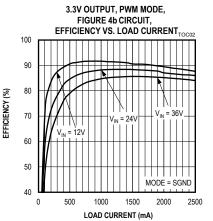

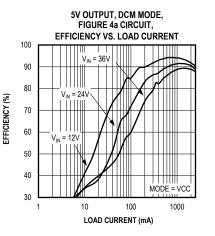

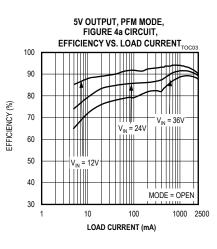

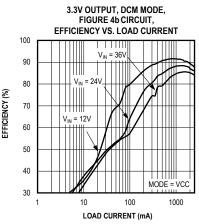

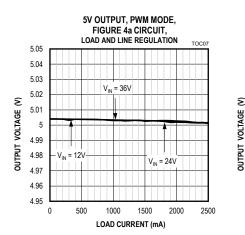

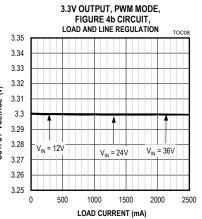

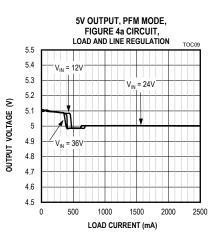

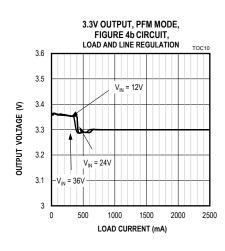

## **Typical Operating Characteristics**

$(V_{IN} = V_{EN/UVLO} = 24V, V_{PGND} = V_{SGND} = 0V, C_{VIN} = C_{VCC} = 2.2\mu$ F, C<sub>BST</sub> = 0.1µF, C<sub>SS</sub> = 5600pF, RT = MODE = open, T<sub>A</sub> = -40°C to +125°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C. All voltages are referenced to GND, unless otherwise noted.)

# 4.5V–42V, 2.5A, High-Efficiency, Synchronous Step-Down DC-DC Converter with Internal Compensation

## **Typical Operating Characteristics (continued)**

$(V_{IN} = V_{EN/UVLO} = 24V, V_{PGND} = V_{SGND} = 0V, C_{VIN} = C_{VCC} = 2.2\mu$ F,  $C_{BST} = 0.1\mu$ F,  $C_{SS} = 5600$ pF, RT = MODE = open,  $T_A = -40^{\circ}$ C to +125°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}$ C. All voltages are referenced to GND, unless otherwise noted.)

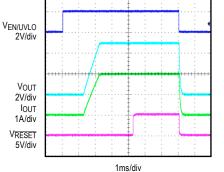

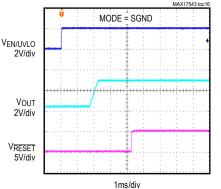

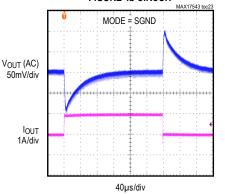

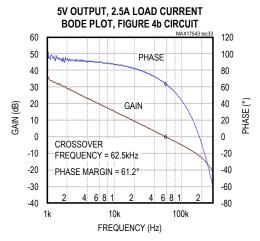

SOFT-START/SHUTDOWN FROM EN/UVLO 5V OUTPUT, 2.5A LOAD CURRENT, FIGURE 4a CIRCUIT

SOFT-START/SHUTDOWN FROM EN/UVLO, 3.3V OUTPUT, PFM MODE, 5mA LOAD CURRENT, FIGURE 4b CIRCUIT

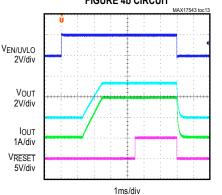

SOFT-START/SHUTDOWN FROM EN/UVLO 3.3V OUTPUT, 2.5A LOAD CURRENT, FIGURE 4b CIRCUIT

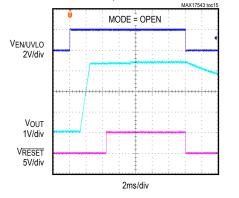

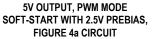

SOFT-START/SHUTDOWN FROM EN/UVLO 5V OUTPUT, PFM MODE, 5mA LOAD CURRENT FIGURE 4a CIRCUIT

3.3V OUTPUT, PFM MODE SOFT-START WITH 2.5V PREBIAS, FIGURE 4b CIRCUIT

# 4.5V–42V, 2.5A, High-Efficiency, Synchronous Step-Down DC-DC Converter with Internal Compensation

## **Typical Operating Characteristics (continued)**

$(V_{IN} = V_{EN/UVLO} = 24V, V_{PGND} = V_{SGND} = 0V, C_{VIN} = C_{VCC} = 2.2\mu$ F,  $C_{BST} = 0.1\mu$ F,  $C_{SS} = 5600$ pF, RT = MODE = open,  $T_A = -40^{\circ}$ C to +125°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}$ C. All voltages are referenced to GND, unless otherwise noted.)

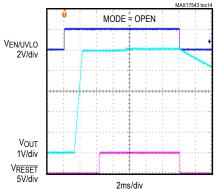

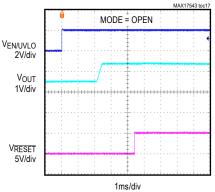

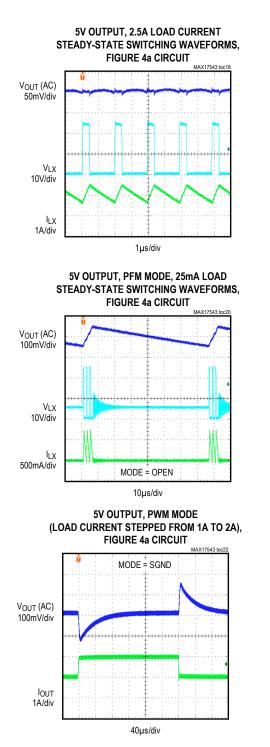

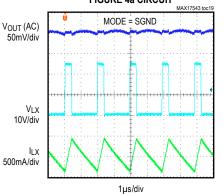

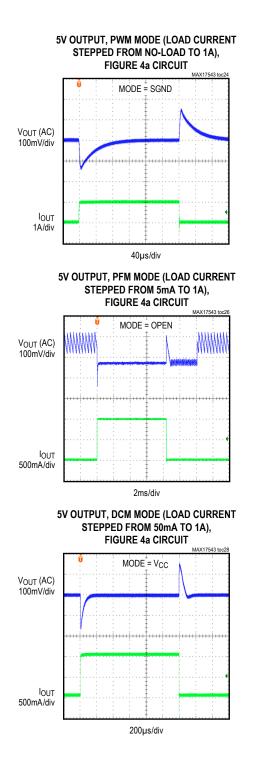

#### 5V OUTPUT, PWM MODE, NO LOAD STEADY-STATE SWITCHING WAVEFORMS, FIGURE 4a CIRCUIT

5V OUTPUT, DCM MODE, 25mA LOAD STEADY-STATE SWITCHING WAVEFORMS, FIGURE 4a CIRCUIT

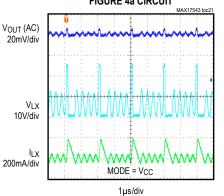

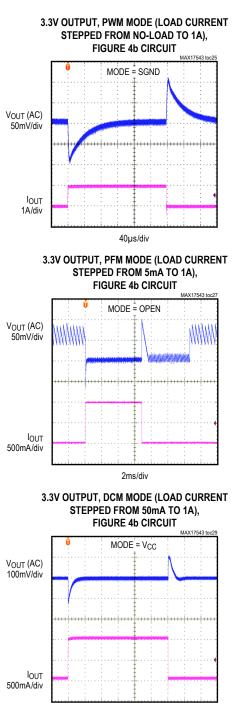

3.3V OUTPUT, PWM MODE (LOAD CURRENT STEPPED FROM 1A TO 2A), FIGURE 4b CIRCUIT

# 4.5V–42V, 2.5A, High-Efficiency, Synchronous Step-Down DC-DC Converter with Internal Compensation

## **Typical Operating Characteristics (continued)**

$(V_{IN} = V_{EN/UVLO} = 24V, V_{PGND} = V_{SGND} = 0V, C_{VIN} = C_{VCC} = 2.2\mu$ F,  $C_{BST} = 0.1\mu$ F,  $C_{SS} = 5600$ pF, RT = MODE = open,  $T_A = -40^{\circ}$ C to +125°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}$ C. All voltages are referenced to GND, unless otherwise noted.)

200µs/div

# 4.5V–42V, 2.5A, High-Efficiency, Synchronous Step-Down DC-DC Converter with Internal Compensation

## **Typical Operating Characteristics (continued)**

$(V_{IN} = V_{EN/UVLO} = 24V, V_{PGND} = V_{SGND} = 0V, C_{VIN} = C_{VCC} = 2.2\mu$ F,  $C_{BST} = 0.1\mu$ F,  $C_{SS} = 5600$ pF, RT = MODE = open,  $T_A = -40^{\circ}$ C to +125°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}$ C. All voltages are referenced to GND, unless otherwise noted.)

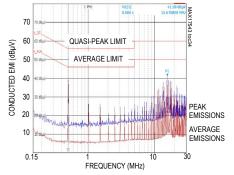

MAX17543, 5V OUTPUT, 2.5A LOAD CURRENT, FIGURE 4a CIRCUIT, CONDUCTED EMI CURVE

Measured on the MAX17543EVKITB with input filter –  $C_{IN}$  = 4.7µF,  $L_{IN}$  = 10µH, the input capacitor for the MAX17543: 4.7µF.

# 4.5V–42V, 2.5A, High-Efficiency, Synchronous Step-Down DC-DC Converter with Internal Compensation

# **Pin Configuration**

## **Pin Description**

| PIN | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                              |

|-----|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1–3 | V <sub>IN</sub> | Power Supply Input. 4.5V to 42V input supply range. Connect the V <sub>IN</sub> pins together. Decouple to PGND with a 2.2 $\mu$ F capacitor; place the capacitor close to the V <sub>IN</sub> and PGND pins. Refer to the MAX17543 EV kit data sheet for a layout example.                                                           |

| 4   | EN/UVLO         | Enable/Undervoltage Lockout. Drive EN/UVLO high to enable the output voltage. Connect to the center of the resistor-divider between $V_{IN}$ and SGND to set the input voltage at which the device turns on. Pull up to $V_{IN}$ for always-on operation.                                                                             |

| 5   | RESET           | Open-Drain RESET Output. The RESET output is driven low if FB drops below 92% of its set value.<br>RESET goes high 1024 clock cycles after FB rises above 95% of its set value.                                                                                                                                                       |

| 6   | SYNC            | The device can be synchronized to an external clock using this pin. See the <i>External Frequency Synchronization</i> section for more details.                                                                                                                                                                                       |

| 7   | SS              | Soft-Start Input. Connect a capacitor from SS to SGND to set the soft-start time.                                                                                                                                                                                                                                                     |

| 8   | CF              | At switching frequencies lower than 500kHz, connect a capacitor from CF to FB. Leave CF open if switching frequency is equal to, or greater than, 500kHz. See the <i>Loop Compensation</i> section for more details.                                                                                                                  |

| 9   | FB              | Feedback Input. Connect FB to the center tap of an external resistor-divider from the output to GND to set the output voltage. See the <i>Adjusting Output Voltage</i> section for more details.                                                                                                                                      |

| 10  | RT              | Connect a resistor from RT to SGND to set the regulator's switching frequency. Leave RT open for the default 500kHz frequency. See the <i>Setting the Switching Frequency (RT)</i> section for more details.                                                                                                                          |

| 11  | MODE            | MODE pin configures the device to operate either in PWM, PFM, or DCM modes of operation. Leave MODE unconnected for PFM operation (pulse-skipping at light loads). Connect MODE to SGND for constant-frequency PWM operation at all loads. Connect MODE to $V_{CC}$ for DCM operation. See the MODE Setting section for more details. |

# 4.5V–42V, 2.5A, High-Efficiency, Synchronous Step-Down DC-DC Converter with Internal Compensation

## **Pin Description (continued)**

| PIN   | NAME            | FUNCTION                                                                                                                                                                                                                                    |

|-------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12    | V <sub>CC</sub> | 5V LDO Output. Bypass $V_{CC}$ with 2.2µF ceramic capacitance to SGND.                                                                                                                                                                      |

| 13    | SGND            | Analog Ground                                                                                                                                                                                                                               |

| 14–16 | PGND            | Power Ground. Connect the PGND pins externally to the power ground plane. Connect the SGND and PGND pins together at the ground return path of the $V_{CC}$ bypass capacitor. Refer to the MAX17543 EV kit data sheet for a layout example. |

| 17–19 | LX              | Switching Node. Connect LX pins to the switching-side of the inductor. Refer to the MAX17543 EV kit data sheet for a layout example.                                                                                                        |

| 20    | BST             | Boost Flying Capacitor. Connect a 0.1µF ceramic capacitor between BST and LX.                                                                                                                                                               |

| _     | EP              | Exposed Pad. Connect to the SGND pin. Connect to a large copper plane below the IC to improve heat dissipation capability. Add thermal vias below the exposed pad. Refer to the MAX17543 EV kit data sheet for a layout example.            |

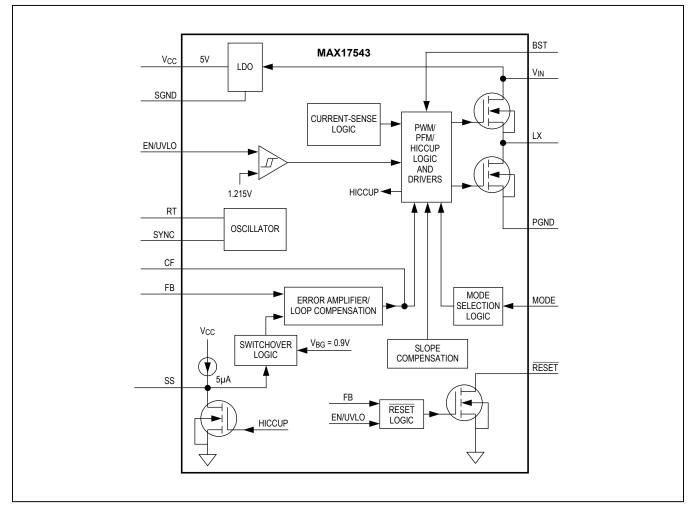

## **Block Diagram**

# 4.5V–42V, 2.5A, High-Efficiency, Synchronous Step-Down DC-DC Converter with Internal Compensation

## **Detailed Description**

The MAX17543 high-efficiency, high-voltage, synchronously-rectified step-down converter with dual integrated MOSFETs operates over a 4.5V to 42V input. It delivers up to 2.5A and 0.9V to  $90\%V_{IN}$  output voltage. Built-in compensation across the output voltage range eliminates the need for external components. The feedback (FB) regulation accuracy over -40°C to +125°C is ±1.1%.

The device features a peak-current-mode-control architecture. An internal transconductance error amplifier produces an integrated error voltage at an internal node, which sets the duty cycle using a PWM comparator, a highside current-sense amplifier, and a slope-compensation generator. At each rising-edge of the clock, the highside MOSFET turns on and remains on until either the appropriate or maximum duty cycle is reached, or the peak current limit is detected. During the high-side MOSFET's on-time, the inductor current ramps up. During the second-half of the switching cycle, the high-side MOSFET turns off and the low-side MOSFET turns on. The inductor releases the stored energy as its current ramps down and provides current to the output.

The device features a MODE pin that can be used to operate the device in PWM, PFM, or DCM control schemes. The device integrates adjustable-input undervoltage lockout, adjustable soft-start, open RESET, and external frequency-synchronization features.

#### Mode Selection (MODE)

The logic state of the MODE pin is latched when V<sub>CC</sub> and EN/UVLO voltages exceed the respective UVLO rising thresholds and all internal voltages are ready to allow LX switching. If the MODE pin is open at power-up, the device operates in PFM mode at light loads. If the MODE pin is grounded at power-up, the device operates in constant-frequency PWM mode at all loads. Finally, if the MODE pin is connected to V<sub>CC</sub> at power-up, the device operates in constant-frequency DCM mode at light loads. State changes on the MODE pin are ignored during normal operation.

#### **PWM Mode Operation**

In PWM mode, the inductor current is allowed to go negative. PWM operation provides constant frequency operation at all loads, and is useful in applications sensitive to switching frequency. However, the PWM mode of operation gives lower efficiency at light loads when compared to PFM and DCM modes of operation.

#### **PFM Mode Operation**

The PFM mode of operation disables negative inductor current and also skips pulses at light loads for high efficiency. In PFM mode, the inductor current is forced to a fixed peak of 750mA every clock cycle until the output rises to 102.3% of the nominal voltage. Once the output reaches 102.3% of the nominal voltage, both the high-side and low-side FETs are turned off and the device enters hibernation mode until the load discharges the output to 101.1% of the nominal voltage. Most of the internal blocks are turned off in hibernation mode to save quiescent current. After the output falls below 101.1% of the nominal voltage, the device comes out of hibernation mode, turns on all internal blocks, and again commences the process of delivering pulses of energy to the output until it reaches 102.3% of the nominal output voltage.

The advantage of PFM mode is higher efficiency at light loads due to lower quiescent current drawn from supply. The disadvantage is that the output voltage ripple is higher than in the PWM or DCM modes of operation, and the switching frequency is not constant at light loads.

#### **DCM Mode Operation**

The DCM mode of operation features constant-frequency operation down to lighter loads than PFM mode by disabling negative inductor current at light loads instead of skipping pulses. DCM operation offers efficiency performance that lies between the PWM and PFM modes.

#### Linear Regulator (V<sub>CC</sub>)

An internal linear regulator (V<sub>CC</sub>) provides a 5V nominal supply to power the internal blocks and the low-side MOSFET driver. The output of the linear regulator (V<sub>CC</sub>) should be bypassed with a  $2.2\mu$ F ceramic capacitor to SGND. The device employs an undervoltage lockout circuit that disables the internal linear regulator when V<sub>CC</sub> falls below 3.8V (typ).

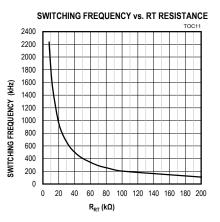

#### Setting the Switching Frequency (RT)

The switching frequency of the device can be programmed from 100kHz to 2.2MHz by using a resistor connected from the RT pin to SGND. The switching frequency ( $f_{SW}$ ) is related to the resistor connected at the RT pin ( $R_{RT}$ ) by the following equation:

$$R_{RT} \cong \frac{21 \times 10^3}{f_{SW}} - 1.7$$

where R<sub>RT</sub> is in kΩ and f<sub>SW</sub> is in kHz. Leaving the RT pin open causes the device to operate at the default switching frequency of 500kHz. See <u>Table 1</u> for RT resistor values for a few common switching frequencies. To operate the MAX17543 at switching frequencies lower than 200kHz, an

# 4.5V–42V, 2.5A, High-Efficiency, Synchronous Step-Down DC-DC Converter with Internal Compensation

# Table 1. Switching Frequency vs. RTResistor

| SWITCHING FREQUENCY (kHz) | RT RESISTOR (kΩ) |

|---------------------------|------------------|

| 500                       | Open             |

| 100                       | 210              |

| 200                       | 102              |

| 400                       | 49.9             |

| 1000                      | 19.1             |

| 2200                      | 8.06             |

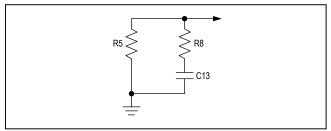

R-C network has to be connected in parallel to the resistor connected from RT to SGND, as shown in Figure 1. The values of the components R8 and C13 are  $90.9k\Omega$  and 220pF, respectively.

Figure 1. Setting the Switching Frequency

#### **Operating Input Voltage Range**

The minimum and maximum operating input voltages for a given output voltage should be calculated as follows:

$$V_{\text{IN(MIN)}} = \frac{V_{\text{OUT}} + (I_{\text{OUT}(\text{MAX})} \times (R_{\text{DCR}} + 0.15))}{1 - (f_{\text{SW}(\text{MAX})} \times t_{\text{OFF}(\text{MAX})})} + (I_{\text{OUT}(\text{MAX})} \times 0.175)$$

$$V_{IN(MAX)} = \frac{V_{OUT}}{f_{SW(MAX)} \times t_{ON(MIN)})}$$

where V<sub>OUT</sub> is the steady-state output voltage, I<sub>OUT (MAX)</sub> is the maximum load current, R<sub>DCR</sub> is the DC resistance of the inductor,  $f_{SW(MAX)}$  is the maximum switching frequency,  $t_{OFF-MAX}$  is the worst-case minimum switch off-time (160ns), and  $t_{ON-MIN}$  is the worst-case minimum switch on-time (135ns).

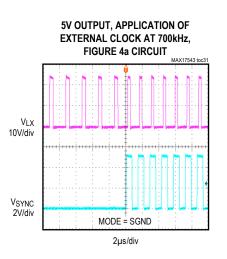

#### **External Frequency Synchronization (SYNC)**

The internal oscillator of the device can be synchronized to an external clock signal on the SYNC pin. The external synchronization clock frequency must be between 1.1 x  $f_{SW}$  and 1.4 x  $f_{SW}$ , where  $f_{SW}$  is the frequency programmed by the RT resistor. The minimum external clock pulse-width high should be greater than 50ns. See the *RTAND SYNC* section of the *Electrical Characteristics* table for details.

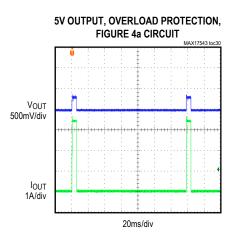

#### **Overcurrent Protection/Hiccup Mode**

The MAX17543 is provided with a robust overcurrent protection scheme that protects the device under overload and output short-circuit conditions. A cycle-by-cycle peak current limit turns off the high-side MOSFET whenever the high-side switch current exceeds an internal limit of 3.7A (typ). A runaway current limit on the high-side switch current at 4.3A (typ) protects the device under high input voltage, short-circuit conditions when there is insufficient output voltage available to restore the inductor current that was built up during the ON period of the step-down converter. One occurrence of runaway current limit triggers a hiccup mode. In addition, if, due to a fault condition, feedback voltage drops to 0.58V (typ) any time after soft-start is complete, hiccup mode is triggered. In hiccup mode, the converter is protected by suspending switching for a hiccup timeout period of 32,768 clock cycles. Once the hiccup timeout period expires, softstart is attempted again. Note that when soft-start is attempted under an overload condition, if the feedback voltage does not exceed 0.58V, the device switches at half the programmed switching frequency. Hiccup mode of operation ensures low power dissipation under output short-circuit conditions.

#### **RESET** Output

The device includes a RESET comparator to monitor the output voltage. The open-drain RESET output requires an external pullup resistor. RESET goes high (high impedance) 1024 switching cycles after the regulator output increases above 95% of the designed nominal regulated voltage. RESET goes low when the regulator output voltage drops to below 92% of the nominal regulated voltage. RESET also goes low during thermal shutdown.

#### **Prebiased Output**

When the device starts into a prebiased output, both the high-side and low-side switches are turned off so that the converter does not sink current from the output. Highside and low-side switches do not start switching until the PWM comparator commands the first PWM pulse, at which point switching commences. The output voltage is then smoothly ramped up to the target value in alignment with the internal reference.

# 4.5V–42V, 2.5A, High-Efficiency, Synchronous Step-Down DC-DC Converter with Internal Compensation

#### **Thermal-Shutdown Protection**

Thermal-shutdown protection limits total power dissipation in the device. When the junction temperature of the device exceeds +165°C, an on-chip thermal sensor shuts down the device, allowing it to cool. The thermal sensor turns the device on again after the junction temperature cools by 10°C. Soft-start resets during thermal shutdown. Carefully evaluate the total power dissipation (see the <u>Power</u> <u>Dissipation</u> section) to avoid unwanted triggering of the thermal shutdown in normal operation.

#### **Applications Information**

#### Input Capacitor Selection

The input filter capacitor reduces peak currents drawn from the power source and reduces noise and voltage ripple on the input caused by the circuit's switching. The input capacitor RMS current requirement ( $I_{RMS}$ ) is defined by the following equation:

$$I_{RMS} = I_{OUT(MAX)} \times \frac{\sqrt{V_{OUT} \times (V_{IN} - V_{OUT})}}{IN}$$

where,  $I_{OUT(MAX)}$  is the maximum load current. I<sub>RMS</sub> has a maximum value when the input voltage equals twice the output voltage (V<sub>IN</sub> = 2 x V<sub>OUT</sub>), so I<sub>RMS(MAX)</sub> = I<sub>OUT(MAX)</sub>/2.

Choose an input capacitor that exhibits less than +10°C temperature rise at the RMS input current for optimal long-term reliability. Use low-ESR ceramic capacitors with high-ripple-current capability at the input. X7R capacitors are recommended in industrial applications for their temperature stability. Calculate the input capacitance using the following equation:

$$C_{IN} = \frac{I_{OUT(MAX)} \times D \times (1-D)}{\eta \times f_{SW} \times \Delta V_{IN}}$$

where D =  $V_{OUT}/V_{IN}$  is the duty ratio of the controller,  $f_{SW}$  is the switching frequency,  $\Delta V_{IN}$  is the allowable input voltage ripple, and  $\eta$  is the efficiency.

In applications where the source is located some distance from the device input, an electrolytic capacitor should be added in parallel to the ceramic capacitor to provide necessary damping for potential oscillations caused by the inductance of the longer input power path and input ceramic capacitor.

#### **Inductor Selection**

Three key inductor parameters must be specified for operation with the device: inductance value (L), inductor

saturation current ( $I_{SAT}$ ), and DC resistance ( $R_{DCR}$ ). The switching frequency and output voltage determine the inductor value as follows:

$$L = \frac{V_{OUT}}{f_{SW}}$$

where V<sub>OUT</sub>, and f<sub>SW</sub> are nominal values.

Select a low-loss inductor closest to the calculated value with acceptable dimensions and having the lowest possible DC resistance. The saturation current rating ( $I_{SAT}$ ) of the inductor must be high enough to ensure that saturation can occur only above the peak current-limit value of 3.7A.

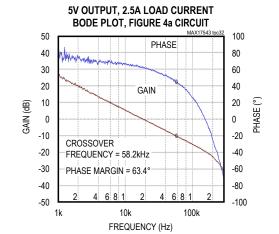

#### **Output Capacitor Selection**

X7R ceramic output capacitors are preferred due to their stability over temperature in industrial applications. The output capacitors are usually sized to support a step load of 50% of the maximum output current in the application, such that output voltage deviation is contained to 3% of nominal output voltage. The minimum required output capacitance can be calculated as follows:

$$C_{OUT} = \frac{5.5}{\left(f_{C} \times V_{OUT}\right)}$$

where  $C_{OUT}$  is in Farad and  $f_C$  is the target closed-loop crossover frequency in Hz. Select  $f_C$  to be 1/9th of  $f_{SW}$  if the switching frequency is less than or equal to 500kHz. If the switching frequency is more than 500kHz, select  $f_C$  to be 55kHz.

Derating of ceramic capacitors with DC-voltage must be considered while selecting the output capacitor. Derating curves are available from all major ceramic capacitor vendors.

#### **Soft-Start Capacitor Selection**

The device implements adjustable soft-start operation to reduce inrush current. A capacitor connected from the SS pin to SGND programs the soft-start time. The selected output capacitance ( $C_{SEL}$ ) and the output voltage ( $V_{OUT}$ ) determine the minimum required soft-start capacitor as follows:

$$C_{SS} \ge 28 \times 10^{-6} \times C_{SEL} \times V_{OUT}$$

The soft-start time  $(t_{SS})$  is related to the capacitor connected at SS  $(C_{SS})$  by the following equation:

$$t_{SS} = \frac{C_{SS}}{5.55 \times 10^{-6}}$$

For example, to program a 1ms soft-start time, a 5.6nF capacitor should be connected from the SS pin to SGND.

# 4.5V–42V, 2.5A, High-Efficiency, Synchronous Step-Down DC-DC Converter with Internal Compensation

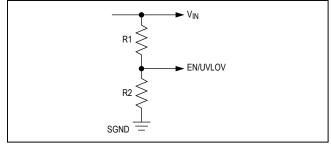

Figure 2. Setting the Input Undervoltage Lockout

# Table 2. C6 Capacitor Value at VariousSwitching Frequencies

| SWITCHING FREQUENCY RANGE (kHz) | C6 (pF) |

|---------------------------------|---------|

| 200 to 300                      | 2.2     |

| 300 to 400                      | 1.2     |

| 400 to 500                      | 0.75    |

#### Setting the Input Undervoltage-Lockout Level

The device offers an adjustable input undervoltage-lockout level. Set the voltage at which the device turns on with a resistive voltage-divider connected from V<sub>IN</sub> to SGND. Connect the center node of the divider to EN/UVLO.

Choose R1 to be  $3.3M\Omega$  and then calculate R2 as follows:

$$R2 = \frac{R1 \times 1.215}{(V_{INU} - 1.215)}$$

where  $V_{INU}$  is the voltage at which the device is required to turn on. Ensure that  $V_{INU}$  is higher than 0.8 x  $V_{OUT}$ .

If the EN/UVLO pin is driven from an external signal source, a series resistance of minimum  $1k\Omega$  is recommended to be placed between the signal source output and the EN/UVLO pin, to reduce voltage ringing on the line.

#### **Loop Compensation**

The device is internally loop-compensated. However, if the switching frequency is less than 500kHz, connect a 0402 capacitor C6 between the CF pin and the FB pin. Use Table 2 to select the value of C6.

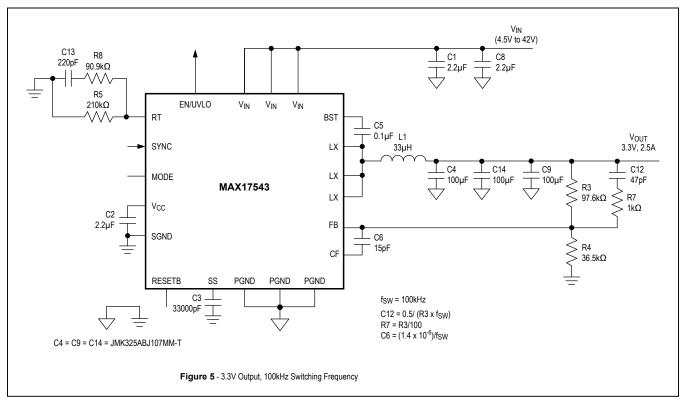

If the switching frequency is less than 200kHz, connect an additional R-C network in parallel to the top resistor of the feedback divider (R3). See Figure 5 to calculate the values of the components R7, C12, and C6.

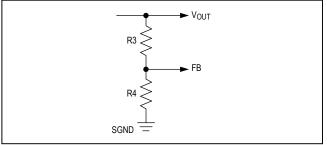

Figure 3. Setting the Output Voltage

#### Adjusting Output Voltage

Set the output voltage with a resistive voltage-divider connected from the positive terminal of the output capacitor ( $V_{OUT}$ ) to SGND (see Figure 3). Connect the center node of the divider to the FB pin. Use the following procedure to choose the resistive voltage-divider values:

Calculate resistor R3 from the output to the FB pin as follows:

$$R3 = \frac{216 \text{ x } 10^3}{(f_C \text{ x } C_{OUT})}$$

where R3 is in k $\Omega$ , crossover frequency  $f_C$  is in kHz, and the output capacitor (C<sub>OUT</sub>) is in  $\mu$ F. Choose  $f_C$  to be 1/9th of the switching frequency ( $f_{SW}$ ) if the switching frequency is less than or equal to 500kHz. If the switching frequency is more than 500kHz, select  $f_C$  to be 55kHz.

Calculate resistor R4 from the FB pin to SGND as follows:

$$R4 = \frac{R3 \times 0.9}{(V_{OUT} - 0.9)}$$

#### **Power Dissipation**

At a particular operating condition, the power losses that lead to temperature rise of the part are estimated as follows:

$$P_{LOSS} = (P_{OUT} \times (\frac{1}{\eta} - 1)) - (I_{OUT}^2 \times R_{DCR})$$

$$P_{OUT} = V_{OUT} \times I_{OUT}$$

where  $P_{OUT}$  is the total output power,  $\eta$  is the efficiency of the converter, and  $R_{DCR}$  is the DC resistances of the inductor. (See the <u>Typical Operating Characteristics</u> for more information on efficiency at typical operating conditions.)

For a multilayer board, the thermal performance metrics for the package are given below:

$$\theta_{JA} = 33^{\circ}C/W$$

$\theta_{JC} = 2^{\circ}C/W$

# 4.5V–42V, 2.5A, High-Efficiency, Synchronous Step-Down DC-DC Converter with Internal Compensation

The junction temperature of the device can be estimated at any given maximum ambient temperature ( $T_{A\_MAX}$ ) from the equation below:

$$T_{J\_MAX} = T_{A\_MAX} + \left(\theta_{JA} \times P_{LOSS}\right)$$

If the application has a thermal management system that ensures that the exposed pad of the device is maintained at a given temperature ( $T_{EP\_MAX}$ ) by using proper heatsinks, then the junction temperature of the device can be estimated at any given maximum ambient temperature from the equation below:

$$T_{J MAX} = T_{EP MAX} + (\theta_{JC} \times P_{LOSS})$$

Junction temperature greater than +125°C degrades operating lifetimes.

#### PCB Layout Guidelines

All connections carrying pulsed currents must be very short and as wide as possible. The inductance of these connections must be kept to an absolute minimum due to the high di/dt of the currents. Since inductance of a current carrying loop is proportional to the area enclosed by the loop, if the loop area is made very small, inductance is reduced. Additionally, small-current loop areas reduce radiated EMI. A ceramic input filter capacitor should be placed close to the V<sub>IN</sub> pins of the IC. This eliminates as much trace inductance effects as possible and gives the IC a cleaner voltage supply. A bypass capacitor for the V<sub>CC</sub> pin also should be placed close to the pin to reduce effects of trace impedance.

When routing the circuitry around the IC, the analog small-signal ground and the power ground for switching currents must be kept separate. They should be connected together at a point where switching activity is at a minimum, typically the return terminal of the  $V_{CC}$  bypass capacitor. This helps keep the analog ground quiet. The ground plane should be kept continuous/unbroken as far as possible. No trace carrying high switching current should be placed directly over any ground plane discontinuity.

PCB layout also affects the thermal performance of the design. A number of thermal vias that connect to a large ground plane should be provided under the exposed pad of the part, for efficient heat dissipation.

For a sample layout that ensures first pass success, refer to the MAX17543 evaluation kit layout available at www.maximintegrated.com.

# 4.5V–42V, 2.5A, High-Efficiency, Synchronous Step-Down DC-DC Converter with Internal Compensation

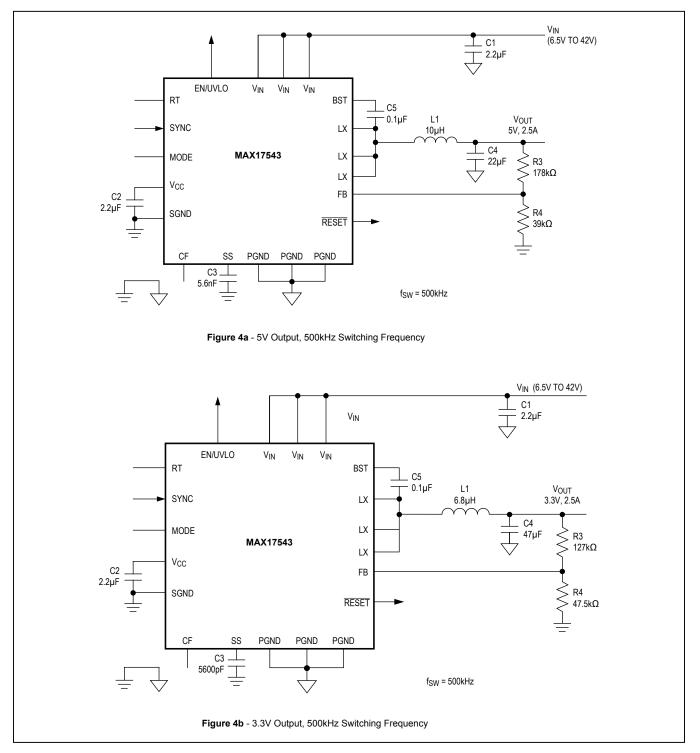

## **Typical Application Circuits**

# 4.5V–42V, 2.5A, High-Efficiency, Synchronous Step-Down DC-DC Converter with Internal Compensation

## **Typical Application Circuits (continued)**

## **Ordering Information**

| PART         | PIN-PACKAGE        |

|--------------|--------------------|

| MAX17543ATP+ | 20 TQFN 4mm x 4 mm |

**Note:** All devices operate over the -40°C to +125°C temperature range, unless otherwise noted.

+Denotes a lead(Pb)-free/RoHS-compliant package. \*EP = Exposed pad.

## **Chip Information**

PROCESS: BICMOS

## **Package Information**

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE    | PACKAGE | OUTLINE        | LAND PATTERN   |

|------------|---------|----------------|----------------|

| TYPE       | CODE    | NO.            | NO.            |

| 20 TQFN-EP | T2044+4 | <u>21-0139</u> | <u>90-0409</u> |

\*EP = Exposed pad.

# 4.5V–42V, 2.5A, High-Efficiency, Synchronous Step-Down DC-DC Converter with Internal Compensation

## **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                               | PAGES<br>CHANGED |

|--------------------|------------------|---------------------------------------------------------------------------|------------------|

| 0                  | 9/14             | Initial release                                                           | —                |

| 1                  | 7/16             | Updated operating and junction temperature values, added new TOC and text | 1–9, 15, 16      |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.