## Low IQ, Wide-Input Range, Active Clamp Current-Mode PWM Controllers

### **General Description**

# Benefits and Features

The MAX17598/MAX17599 low  $I_Q$ , active clamp current-mode PWM controllers contain all the control circuitry required for the design of wide-input isolated/non-isolated forward-converter industrial power supplies. The MAX17598 is well-suited for universal input (rectified 85V AC to 265V AC) or telecom (36V DC to 72V DC) power supplies. The MAX17599 is optimized for low-voltage industrial supplies (4.5V DC to 36V DC).

The devices include an AUX driver that drives an auxiliary MOSFET (clamp switch) that helps implement the active-clamp transformer reset topology for forward converters. Such a reset topology has several advantages including reduced voltage stress on the switches, transformer size reduction due to larger allowable flux swing, and improved efficiency due to elimination of dissipative snubber circuitry. Programmable dead time between the AUX and main driver allows for zero voltage switching (ZVS).

The switching frequency is programmable from 100kHz to 1MHz for the devices with an accuracy of ±8% using an external resistor. This allows optimization of the magnetic and filter components, resulting in compact, cost-effective isolated/nonisolated power supplies. For EMI-sensitive applications, the ICs incorporate a programmable frequency-dithering scheme, enabling low-EMI spread-spectrum operation.

An input undervoltage lockout (EN/UVLO) is provided for programming input-supply start voltage, and to ensure proper operation during brownout conditions. EN/UVLO input is also used to turn on/off the ICs. Input overvoltage (OVI) protection scheme is provided to make sure that the regulator shuts down when input supply exceeds its maximum allowed value.

To control inrush current, the devices incorporate an SS pin to set the soft-start time for the regulators. Power dissipation under fault conditions is minimized by hiccup overcurrent protection (hiccup mode). Soft-stop feature provides safe discharging of the clamp capacitor when the device is turned off, and allows the controller to restart in a well-controlled manner. Additionally, negative current limit is provided in the current-sense circuitry, helping limit clamp switch current under dynamic operating conditions.

SYNC feature is provided to synchronize multiple converters to a common external clock in noise-sensitive applications. Overtemperature fault triggers thermal shutdown for reliable protection of the device. The ICs are available in a 16-pin, TQFN package with 0.5 mm lead spacing.

- Active Clamp, Peak Current-Mode Forward PWM Controller

- ♦ 20µA Startup Current in UVLO

- ◆ 4.5V to 36V Input-Supply Operating Range (MAX17599)

- **♦ Programmable Input Undervoltage Lockout**

- ♦ Programmable Input Overvoltage Protection

- Programmable 100kHz to 1MHz Switching Frequency

- **♦** Switching Frequency Synchronization

- ♦ Programmable Frequency Dithering for Low EMI Spread-Spectrum Operation

- **♦ Programmable Dead Time**

- ♦ Adjustable Soft-Start

- **♦ Programmable Slope Compensation**

- **♦ Fast Cycle-by-Cycle Peak-Current-Limit**

- ♦ 70ns Internal Leading-Edge Current-Sense Blanking

- ♦ Hiccup Mode Output Short-Circuit Protection

- ♦ Soft-Stop for Well-Controlled Clamp Capacitor Discharge

- ♦ Negative Clamp-Switch Current Limit

- ♦ 3mm x 3mm, Lead-Free 16-Pin TQFN

- ♦ -40°C to +125°C Operating Temperature Range

### **Applications**

Telecom and Datacom Power Supplies Isolated Battery Chargers Servers and Embedded Computing Industrial Power Supplies

Ordering Information appears at end of data sheet.

For related parts and recommended products to use with this part, refer to <a href="https://www.maximintegrated.com/MAX17598.related">www.maximintegrated.com/MAX17598.related</a>.

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maximintegrated.com.

## Low IQ, Wide-Input Range, Active Clamp Current-Mode PWM Controllers

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>IN</sub> (MAX17599 only) | 0.3V to +40V               |

|---------------------------------|----------------------------|

| V <sub>DRV</sub> to SGND        |                            |

| (MAX17598 Only)                 | 0.3V to +16V               |

| (MAX17599 Only)                 | 0.3V to +6V                |

| EN/UVLO to SGND                 | 0.3V to $(V_{IN} + 0.3V)$  |

| NDRV, AUXDRV to PGND            | 0.3V to $(V_{DRV} + 0.3V)$ |

| OVI, RT, DITHER, COMP, SS, FB,  |                            |

| SLOPE, DT to SGND               | 0.3V to +6V                |

| CS to SGND                      | 0.8V to +6V                |

| PGND to SGND                    | 0.3V to +0.3V              |

| Maximum Input/Output Current (Continuous)             |                |

|-------------------------------------------------------|----------------|

| V <sub>IN</sub> , V <sub>DRV</sub>                    | 100mA          |

| NDRV (pulsed for less than 100ns)                     | +0.9A/-1.5A    |

| AUXDRV (pulsed for less than 100ns)                   | +0.3A/-0.7A    |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                |

| TQFN (derate 20.8mW/°C above 70°C)                    | 1666mW         |

| Operating Temperature Range                           | 40°C to +125°C |

| Maximum Junction Temperature                          | +150°C         |

| Storage Temperature Range                             | 65°C to +150°C |

| Lead Temperature (soldering, 10s)                     | +300°C         |

| Soldering Temperature (reflow)                        | +260°C         |

|                                                       |                |

### PACKAGE THERMAL CHARACTERISTICS

**TOFN**

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

(Note 1)

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{IN}=12V~(for~MAX17598,~bring~V_{IN}~up~to~21V~for~startup),~V_{CS}=V_{DITHER}=V_{FB}=V_{OVI}=V_{SGND}=V_{PGND}=0V,~V_{EN/UVLO}=+2V,~AUXDRV=NDRV=SS=COMP=SLOPE=unconnected,~R_{RT}=25k\Omega,~R_{DT}=10k\Omega,~C_{VIN}=1\mu\text{F},~C_{VDRV}=1\mu\text{F},~T_{A}=T_{J}=-40^{\circ}\text{C}~to~+125^{\circ}\text{C},~unless~otherwise~noted.}$

| PARAMETER                                           | SYMBOL                      | CON                                      | DITIONS                                                                    | MIN  | TYP  | MAX  | UNITS |

|-----------------------------------------------------|-----------------------------|------------------------------------------|----------------------------------------------------------------------------|------|------|------|-------|

| INPUT SUPPLY (V <sub>IN</sub> )                     |                             |                                          |                                                                            |      |      |      |       |

| V Valtaga Danga                                     | .,                          | MAX17598                                 | MAX17598                                                                   |      |      | 29   | V     |

| V <sub>IN</sub> Voltage Range                       | V <sub>IN</sub>             | MAX17599                                 |                                                                            | 4.5  |      | 36   | V     |

| V Doctotron IIVI O Walsour                          |                             | INI vining                               | MAX17598                                                                   | 18.5 | 20   | 21.5 | V     |

| V <sub>IN</sub> Bootstrap UVLO Wakeup               | V <sub>IN-UVR</sub>         | IN rising                                | MAX17599                                                                   | 3.8  | 4.1  | 4.4  | V     |

| V <sub>IN</sub> Bootstrap UVLO                      |                             | INI falling                              | MAX17598                                                                   | 6.5  | 7    | 7.5  | V     |

| Shutdown Level                                      | V <sub>IN-UVF</sub>         | IN falling                               | MAX17599                                                                   | 3.6  | 3.9  | 4.2  | V     |

| V <sub>IN</sub> Supply Startup Current (under UVLO) | I <sub>IN-</sub><br>STARTUP | V <sub>IN</sub> < UVLO                   | V <sub>IN</sub> < UVLO                                                     |      | 20   | 32   | μΑ    |

| V <sub>IN</sub> Supply Shutdown<br>Current          | I <sub>IN-SH</sub>          | V <sub>EN</sub> = 0V                     | V <sub>EN</sub> = 0V                                                       |      | 20   | 32   | μA    |

| V <sub>IN</sub> Supply Current                      | I <sub>IN-SW</sub>          | Switching, f <sub>SW</sub> =             | 400kHz                                                                     |      | 2    |      | mA    |

| V <sub>IN</sub> Clamp Voltage                       | V <sub>INC</sub>            |                                          | V <sub>EN</sub> = 0V, I <sub>IN</sub> = 2mA sinking<br>(MAX17598) (Note 3) |      | 33   | 36   | V     |

| ENANBLE (EN)                                        |                             |                                          |                                                                            |      |      |      |       |

|                                                     | V <sub>ENR</sub>            | V <sub>EN</sub> rising                   |                                                                            | 1.16 | 1.21 | 1.26 | .,    |

| EN Threshold                                        | V <sub>ENF</sub>            | V <sub>EN</sub> falling                  |                                                                            | 1.1  | 1.15 | 1.20 | V     |

| EN Input Leakage Current                            | I <sub>EN</sub>             | V <sub>EN</sub> = 1.5V, T <sub>A</sub> = | +25°C                                                                      | -100 |      | +100 | nA    |

# Low IQ, Wide-Input Range, Active Clamp Current-Mode PWM Controllers

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN}=12V~(for~MAX17598,~bring~V_{IN}~up~to~21V~for~startup),~V_{CS}=V_{DITHER}=V_{FB}=V_{OVI}=V_{SGND}=V_{PGND}=0V,~V_{EN/UVLO}=+2V,~AUXDRV=NDRV=SS=COMP=SLOPE=unconnected,~R_{RT}=25k\Omega,~R_{DT}=10k\Omega,~C_{VIN}=1\mu\text{F},~C_{VDRV}=1\mu\text{F},~T_{A}=T_{J}=-40^{\circ}\text{C}~to~+125^{\circ}\text{C},~unless~otherwise~noted.}$

| PARAMETER                             | SYMBOL                | CONDITIONS                                                               | MIN                      | TYP  | MAX                      | UNITS |

|---------------------------------------|-----------------------|--------------------------------------------------------------------------|--------------------------|------|--------------------------|-------|

| INTERNAL LDO (V <sub>DRV</sub> )      |                       |                                                                          |                          |      |                          |       |

|                                       |                       | 8V < V <sub>IN</sub> < 15V and 0mA < I <sub>VDRV</sub> < 50mA (MAX17598) | 7.1                      | 7.4  | 7.7                      |       |

| V <sub>DRV</sub> Output Voltage Range | V <sub>VDRV</sub>     | 6V < V <sub>IN</sub> < 15V and 0mA < I <sub>VDRV</sub> < 50mA (MAX17599) | 4.7                      | 4.9  | 5.1                      | V     |

| V <sub>DRV</sub> Current Limit        | I <sub>VDRV-MAX</sub> |                                                                          | 70                       | 100  |                          | mA    |

| V <sub>DRV</sub> Dropout              | V <sub>VDRV-DO</sub>  | $V_{IN} = 4.5V$ , $I_{VDRV} = 20$ mA (MAX17599)                          | 4.2                      |      |                          | V     |

| OVERVOLTAGE PROTECTIO                 | N (OVI)               |                                                                          |                          |      |                          |       |

| OVI Overveltage Threehold             | V <sub>OVIR</sub>     | V <sub>OVI</sub> rising                                                  | 1.16                     | 1.21 | 1.26                     | V     |

| OVI Overvoltage Threshold             | V <sub>OVIF</sub>     | V <sub>OVI</sub> falling                                                 | 1.1                      | 1.15 | 1.2                      | V     |

| OVI Masking Delay                     | t <sub>OVI-MD</sub>   |                                                                          |                          | 2    |                          | μs    |

| OVI Input Leakage Current             | I <sub>OVI</sub>      | $V_{OVI} = 1V, T_A = +25^{\circ}C$                                       | -100                     |      | +100                     | nA    |

| OSCILLATOR (RT)                       |                       |                                                                          |                          |      |                          |       |

| NDRV Switching Frequency<br>Range     | f <sub>SW</sub>       |                                                                          | 100                      |      | 1000                     | kHz   |

| NDRV Switching Frequency<br>Accuracy  |                       |                                                                          | -8                       |      | +8                       | %     |

| Maximum Duty Cycle                    | D <sub>MAX</sub>      | $f_{SW} = 400KHz$ , $R_{DT} = 10k\Omega$                                 | 71                       | 72.5 | 74                       | %     |

| SYNCHRONIZATION (DITHER               | R/SYNC)               |                                                                          |                          |      |                          |       |

| Synchronization Logic-High Input      | V <sub>IH-SYNC</sub>  |                                                                          | 3                        |      |                          | V     |

| Synchronization Pulse Width           |                       |                                                                          |                          | 50   |                          | ns    |

| Synchronization Frequency Range       | f <sub>SYNC</sub>     |                                                                          | 1.1 x<br>f <sub>SW</sub> |      | 1.3 x<br>f <sub>SW</sub> |       |

| DITHERING RAMP GENERAT                | OR (DITHER/           | SYNC)                                                                    |                          |      |                          |       |

| Charging Current                      |                       |                                                                          | 45                       | 50   | 55                       | μΑ    |

| Discharging Current                   |                       |                                                                          | 43                       | 50   | 57                       | μΑ    |

| Ramp-High Trip Point                  |                       |                                                                          |                          | 2    |                          | V     |

| Ramp-Low Trip Point                   |                       |                                                                          |                          | 0.4  |                          | v     |

# Low IQ, Wide-Input Range, Active Clamp Current-Mode PWM Controllers

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN}=12V~(for~MAX17598,~bring~V_{IN}~up~to~21V~for~startup),~V_{CS}=V_{DITHER}=V_{FB}=V_{OVI}=V_{SGND}=V_{PGND}=0V,~V_{EN/UVLO}=+2V,~AUXDRV=NDRV=SS=COMP=SLOPE=unconnected,~R_{RT}=25k\Omega,~R_{DT}=10k\Omega,~C_{VIN}=1\mu\text{F},~C_{VDRV}=1\mu\text{F},~T_{A}=T_{J}=-40^{\circ}\text{C}~to~+125^{\circ}\text{C},~unless~otherwise~noted.}$

| PARAMETER                                          | SYMBOL                | CONDITIO                           | NS                    | MIN  | TYP  | MAX  | UNITS |

|----------------------------------------------------|-----------------------|------------------------------------|-----------------------|------|------|------|-------|

| SOFT-START/SOFT-STOP (S                            | SS)                   |                                    |                       |      |      |      |       |

| Soft-Start Charging Current                        | I <sub>SSCH</sub>     |                                    |                       | 9    | 10   | 11   | μΑ    |

| Soft-Stop Discharging Current                      | ISSDISCH              |                                    |                       | 4.4  | 5    | 5.6  | μA    |

| SS Bias Voltage                                    | V <sub>SS</sub>       |                                    |                       | 1.19 | 1.21 | 1.23 | V     |

| SS Discharge Threshold                             | V <sub>SSDISCH</sub>  | Soft-stop completion               |                       |      | 0.15 |      | V     |

| NDRV DRIVER (NDRV)                                 |                       |                                    |                       |      |      |      |       |

| Pulldown Impedance                                 | R <sub>NDRV-N</sub>   | I <sub>NDRV</sub> (sinking) = 100n | nΑ                    |      | 1.37 | 3    | Ω     |

| Pullup Impedance                                   | R <sub>NDRV-P</sub>   | I <sub>NDRV</sub> (sourcing) = 50r | nΑ                    |      | 4.26 | 8.5  | Ω     |

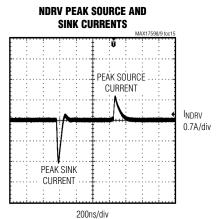

| Peak Sink Current                                  |                       | C <sub>NDRV</sub> = 10nF           |                       |      | 1.5  |      | А     |

| Peak Source Current                                |                       | C <sub>NDRV</sub> = 10nF           |                       |      | 0.9  |      | А     |

| Fall Time                                          | t <sub>NDRV-F</sub>   | C <sub>NDRV</sub> = 1nF            |                       |      | 10   |      | ns    |

| Rise Time                                          | t <sub>NDRV-R</sub>   | C <sub>NDRV</sub> = 1nF            |                       |      | 20   |      | ns    |

| AUXDRV DRIVER (AUXDRV)                             |                       |                                    |                       |      |      |      |       |

| Pulldown Impedance                                 | R <sub>AUXDRV-N</sub> | I <sub>AUXDRV</sub> (sinking) = 10 | 0mA                   |      | 3.35 | 7    | Ω     |

| Pullup Impedance                                   | R <sub>AUXDRV-P</sub> | $I_{AUXDRV}$ (sourcing) = 5        | 50mA                  |      | 9.78 | 19   | Ω     |

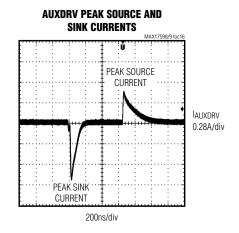

| Peak Sink Current                                  |                       | C <sub>AUXDRV</sub> = 10nF         |                       |      | 0.7  |      | А     |

| Peak Source Current                                |                       | C <sub>AUXDRV</sub> = 10nF         |                       |      | 0.3  |      | А     |

| Fall Time                                          | t <sub>AUXDRV-F</sub> | C <sub>AUXDRV</sub> = 1nF          |                       |      | 16   |      | ns    |

| Rise Time                                          | t <sub>AUXDRV-R</sub> | C <sub>AUXDRV</sub> = 1nF          |                       |      | 32   |      | ns    |

| DEAD TIME (DT)                                     |                       |                                    |                       |      |      |      |       |

|                                                    |                       | NDRV↓ to AUXDRV↓                   | $R_{DT} = 10k\Omega$  |      | 25   |      |       |

| NDRV to AUXDRV Delay                               |                       | NDRV+ 10 AUXDRV+                   | $R_{DT} = 100k\Omega$ |      | 250  |      |       |

| (Dead Time)                                        | t <sub>DT</sub>       | ALIVEDIAL AIDDIA                   | $R_{DT} = 10k\Omega$  |      | 25   |      | ns    |

|                                                    |                       | AUXDRV1 to NDRV1                   | $R_{DT} = 100k\Omega$ |      | 250  |      |       |

| CURRENT-LIMIT COMPARA                              | TOR (CS)              |                                    |                       |      |      |      |       |

| Cycle-by-Cycle Peak-<br>Current-Limit Threshold    | V <sub>CS-PEAK</sub>  |                                    |                       | 290  | 305  | 320  | mV    |

| Cycle-by-Cycle Runaway-<br>Current-Limit Threshold | V <sub>CS-RUN</sub>   |                                    |                       | 340  | 360  | 380  | mV    |

| Cycle-by-Cycle Reverse-<br>Current-Limit Threshold | V <sub>CS-REV</sub>   |                                    |                       | -122 | -102 | -82  | mV    |

# Low IQ, Wide-Input Range, Active Clamp Current-Mode PWM Controllers

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN}=12V \text{ (for MAX17598, bring } V_{IN} \text{ up to 21V for startup)}, V_{CS}=V_{DITHER}=V_{FB}=V_{OVI}=V_{SGND}=V_{PGND}=0V, V_{EN/UVLO}=+2V,$  AUXDRV = NDRV = SS = COMP = SLOPE = unconnected, R<sub>RT</sub> = 25kΩ, R<sub>DT</sub> = 10kΩ, C<sub>VIN</sub> = 1μF, C<sub>VDRV</sub> = 1μF, T<sub>A</sub> = T<sub>J</sub> = -40°C to +125°C, unless otherwise noted. Typical values are at T<sub>A</sub> = T<sub>J</sub> = +25°C.) (Note 2)

| PARAMETER                                                       | SYMBOL                        | CONDITIONS                                                                        | MIN  | TYP    | MAX  | UNITS |

|-----------------------------------------------------------------|-------------------------------|-----------------------------------------------------------------------------------|------|--------|------|-------|

| Current-Sense Leading-Edge<br>Blanking Time                     | <sup>t</sup> CS-BLANK         | From NDRV1 edge                                                                   |      | 70     |      | ns    |

| Current-Sense-Blanking Time for Reverse-Current Limit           | <sup>t</sup> CS-BLANK-<br>Rev | From AUXDRV↓ edge                                                                 |      | 70     |      | ns    |

| Propagation Delay from<br>Comparator Input to NDRV              | t <sub>PDCS</sub>             | From CS rising (10mV overdrive) to NDRV falling (excluding leading-edge blanking) |      | 40     |      | ns    |

| Number of Consecutive<br>Peak-Current-Limit Events to<br>HICCUP | N <sub>HICCUP-P</sub>         |                                                                                   |      | 8      |      | event |

| Number of Runaway Current-<br>Limit Events to HICCUP            | N <sub>-HICCUP-R</sub>        |                                                                                   |      | 1      |      | event |

| Overcurrent Hiccup Timeout                                      |                               |                                                                                   |      | 32,768 |      | cycle |

| Minimum On-Time                                                 | t <sub>ON-MIN</sub>           |                                                                                   | 90   | 130    | 170  | ns    |

| SLOPE COMPENSATION (SL                                          | OPE)                          |                                                                                   |      |        |      |       |

| Slope Bias Current                                              | I <sub>SLOPE</sub>            |                                                                                   | 9    | 10     | 11   | μΑ    |

| Slope Resistor Range                                            | R <sub>SLOPE</sub>            |                                                                                   | 25   |        | 200  | kΩ    |

| Slope Compensation Ramp                                         |                               | $R_{SLOPE} = 100k\Omega$                                                          | 140  | 165    | 190  | mV/μs |

| Default Slope Compensation<br>Ramp                              |                               | V <sub>SLOPE</sub> < 0.2V or 4V < V <sub>SLOPE</sub>                              |      | 50     |      | mV/µs |

| PWM COMPARATOR                                                  |                               |                                                                                   |      |        |      |       |

| Comparator Offset Voltage                                       | V <sub>PWM-OS</sub>           | V <sub>COMP</sub> , when V <sub>CS</sub> = 0V                                     | 1.65 | 1.81   | 2    | V     |

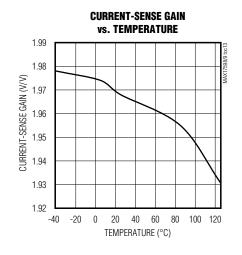

| Current-Sense Gain                                              | A <sub>CS-PWM</sub>           | ΔV <sub>COMP</sub> /ΔV <sub>CS</sub>                                              | 1.75 | 1.97   | 2.15 | V/V   |

| Comparator Propagation Delay                                    | t <sub>PWM</sub>              | Change in V <sub>CS</sub> = 10mV (including internal lead-edge blanking)          |      | 110    |      | ns    |

| ERROR AMPLIFIER                                                 |                               |                                                                                   |      |        |      |       |

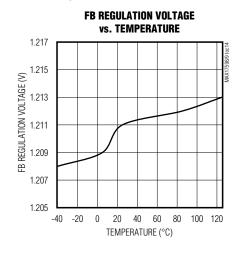

| FB Reference Voltage                                            | V <sub>REF</sub>              | $V_{FB}$ , when $I_{COMP} = 0V$<br>and $V_{COMP} = 1.8V$                          | 1.19 | 1.21   | 1.23 | V     |

| FB Input Bias Current                                           | I <sub>FB</sub>               | $V_{FB} = 1.5V, T_A = +25^{\circ}C$                                               | -100 |        | +100 | nA    |

| Open-Loop Voltage Gain                                          | A <sub>EAMP</sub>             |                                                                                   |      | 90     |      | dB    |

| Transconductance                                                | Gm                            |                                                                                   | 1.5  | 1.8    | 2.1  | mS    |

## Low IQ, Wide-Input Range, Active Clamp Current-Mode PWM Controllers

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN}=12V \text{ (for MAX17598, bring } V_{IN} \text{ up to 21V for startup)}, V_{CS}=V_{DITHER}=V_{FB}=V_{OVI}=V_{SGND}=V_{PGND}=0V, V_{EN/UVLO}=+2V,$  AUXDRV = NDRV = SS = COMP = SLOPE = unconnected, R<sub>RT</sub> = 25kΩ, R<sub>DT</sub> = 10kΩ, C<sub>VIN</sub> = 1μF, C<sub>VDRV</sub> = 1μF, T<sub>A</sub> = T<sub>J</sub> = -40°C to +125°C, unless otherwise noted. Typical values are at T<sub>A</sub> = T<sub>J</sub> = +25°C.) (Note 2)

| PARAMETER                      | SYMBOL | CONDITIONS                            | MIN | TYP | MAX | UNITS |

|--------------------------------|--------|---------------------------------------|-----|-----|-----|-------|

| Transconductance Bandwidth     | BW     | Open-loop (gain = 1), -3dB frequency° |     | 10  |     | MHz   |

| Source Current                 |        | $V_{COMP} = 1.8V, V_{FB} = 1V$        | 80  | 120 | 210 | μΑ    |

| Sink Current                   |        | $V_{COMP} = 1.8V, V_{FB} = 1.75V$     | 80  | 120 | 210 | μΑ    |

| THERMAL SHUTDOWN               |        |                                       |     |     |     |       |

| Thermal Shutdown Threshold     |        | Temperature rising                    |     | 160 |     | °C    |

| Thermal Shutdown<br>Hysteresis |        |                                       |     | 20  |     | °C    |

Note 2: All devices are 100% production tested at +25°C. Limits over temperature are guaranteed by design.

**Note 3:** The MAX17598 is intended for use in universal input power supplies. The internal clamp circuit at IN is used to prevent the bootstrap capacitor from charging to a voltage beyond the absolute maximum rating of the device when EN is low (shutdown mode). Externally limit the maximum current to IN (hence to clamp) to 2mA (max) when EN is low.

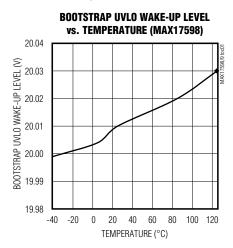

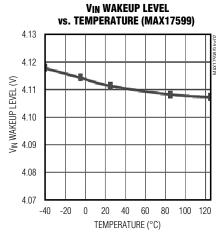

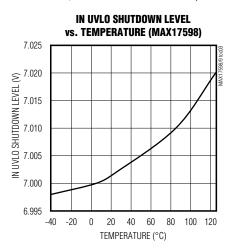

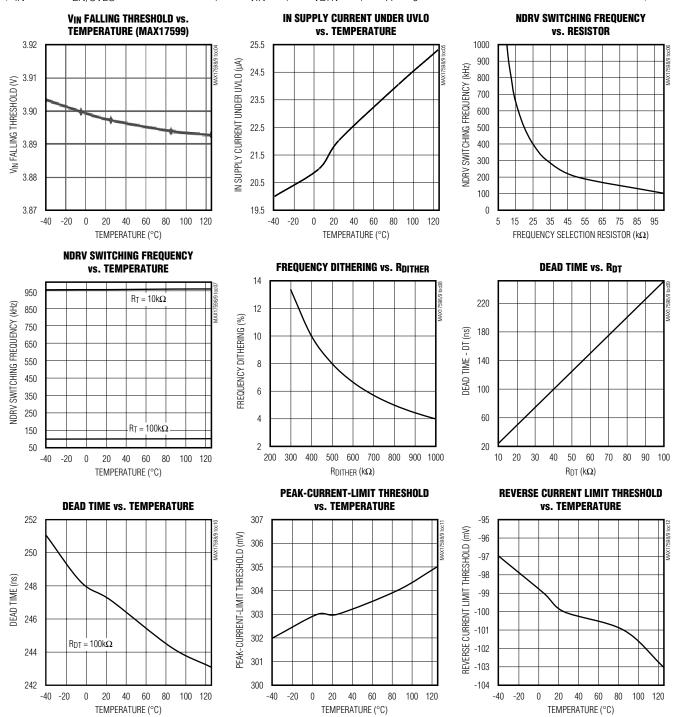

### **Typical Operating Characteristics**

$(V_{IN} = 15V, V_{EN/UVLO} = +2V, COMP = open, C_{VIN} = 1\mu F, C_{VDRV} = 1\mu F, T_A = T_J = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted.)

## Low IQ, Wide-Input Range, Active Clamp Current-Mode PWM Controllers

### **Typical Operating Characteristics (continued)**

$(V_{IN} = 15V, V_{EN/UVLO} = +2V, COMP = open, C_{VIN} = 1\mu F, C_{VDRV} = 1\mu F, T_A = T_J = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted.)

# Low IQ, Wide-Input Range, Active Clamp Current-Mode PWM Controllers

### **Typical Operating Characteristics (continued)**

$(V_{IN} = 15V, V_{EN/UVLO} = +2V, COMP = open, C_{VIN} = 1\mu F, C_{VDRV} = 1\mu F, T_A = T_J = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted.)

# Low IQ, Wide-Input Range, Active Clamp Current-Mode PWM Controllers

**Typical Operating Characteristics (continued)**

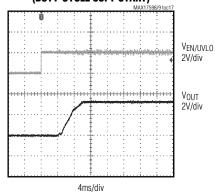

## ENABLE STARTUP WAVEFORM (DUTY-CYCLE SOFT-START)

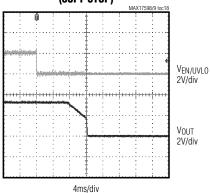

# ENABLE SHUTDOWN WAVEFORM (SOFT-STOP)

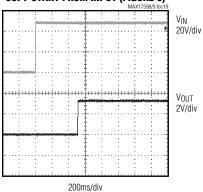

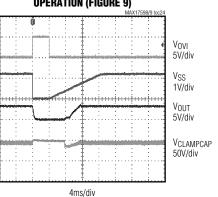

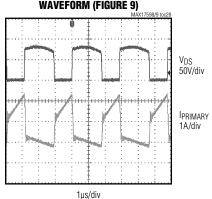

#### **SOFT-START FROM INPUT (FIGURE 9)**

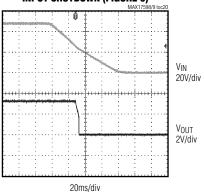

#### **INPUT SHUTDOWN (FIGURE 9)**

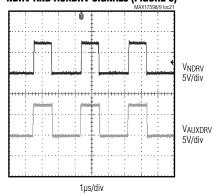

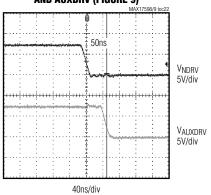

#### NDRV AND AUXDRV SIGNALS (FIGURE 9)

#### DEAD TIME BETWEEN NDRV AND AUXDRV (FIGURE 9)

# Low IQ, Wide-Input Range, Active Clamp Current-Mode PWM Controllers

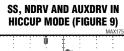

### **Typical Operating Characteristics (continued)**

#### MOMENTARY OVI OPERATION (FIGURE 9)

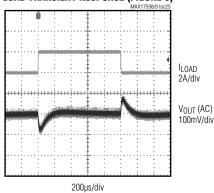

#### **LOAD TRANSIENT RESPONSE (FIGURE 9)**

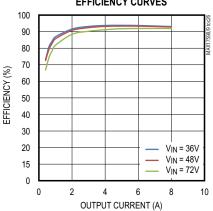

#### **EFFICIENCY CURVES**

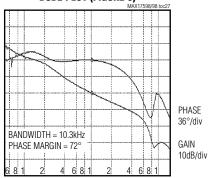

#### **BODE PLOT (FIGURE 9)**

# ACTIVE CLAMP SWITCHING WAVEFORM (FIGURE 9)

# Low IQ, Wide-Input Range, Active Clamp Current-Mode PWM Controllers

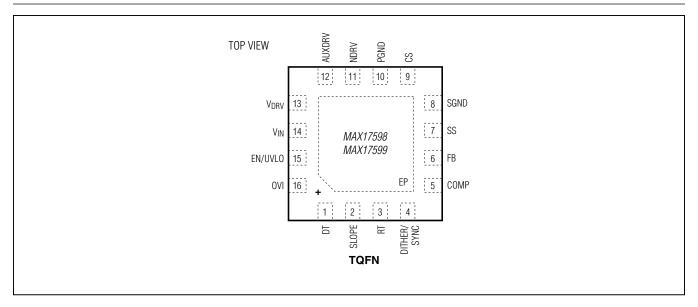

### **Pin Configuration**

## **Pin Description**

| PIN | NAME        | FUNCTION                                                                                                                                                                                                                                                                                                        |

|-----|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | DT          | Dead-Time Programming Resistor Connection. Connect resistor from DT to GND to set the desired dead time between the NDRV and AUXDRV signals. See the <i>Dead Time</i> section to calculate the resistor value for a particular dead time.                                                                       |

| 2   | SLOPE       | Slope Compensation Programming Input. A resistor RSLOPE connected from SLOPE to SGND programs the amount of internal slope compensation. Shorting this pin to SGND sets a default slope compensation of 50mV/µs.                                                                                                |

| 3   | RT          | Switching Frequency Programming Resistor Connection. Connect resistor from RT to SGND to set the PWM switching frequency.                                                                                                                                                                                       |

| 4   | DITHER/SYNC | Frequency Dithering Programming or Synchronization Connection. For spread-spectrum frequency operation, connect a capacitor from DITHER to SGND and a resistor from DITHER to RT. To synchronize the internal oscillator to the externally applied frequency, connect DITHER/SYNC to the synchronization pulse. |

| 5   | COMP        | Transconductance Amplifier Output. Connect the frequency compensation network between COMP and SGND in nonisolated applications and between COMP and FB pins in isolated applications.                                                                                                                          |

| 6   | FB          | Transconductance Error Amplifier Inverting Input                                                                                                                                                                                                                                                                |

| 7   | SS          | Soft-Start/Soft-Stop Capacitor Pin for Forward/Flyback Regulator. Connect a capacitor from SS to SGND to set the soft-start/soft-stop time interval.                                                                                                                                                            |

| 8   | SGND        | Signal Ground. Connect SGND to the signal ground plane.                                                                                                                                                                                                                                                         |

| 9   | CS          | Current-Sense Input. Current-sense connection for average current-sense and cycle-by-cycle current limit. Peak current limit trip voltage is 350mV (typ).                                                                                                                                                       |

| 10  | PGND        | Power Ground. Connect PGND to the power ground plane.                                                                                                                                                                                                                                                           |

## Low IQ, Wide-Input Range, Active Clamp Current-Mode PWM Controllers

### Pin Description (continued)

| PIN | NAME             | FUNCTION                                                                                                                                                          |

|-----|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11  | NDRV             | External Switching NMOS Gate-Driver Output                                                                                                                        |

| 12  | AUXDRV           | PMOS Active-Clamp-Switch Gate-Driver Output. AUXDRV can also be used to drive a pulse transformer for synchronous flyback application.                            |

| 13  | V <sub>DRV</sub> | Linear Regulator Output and Driver Input. Connect a $1\mu F$ bypass capacitor from $V_{DRV}$ to PGND as close as possible to the IC.                              |

| 14  | V <sub>IN</sub>  | Internal $V_{DRV}$ Regulator Input. Connect $V_{IN}$ to the input voltage source. Bypass $V_{IN}$ to PGND with a $0.1\mu F$ minimum ceramic capacitor.            |

| 15  | EN/UVLO          | Enable/Undervoltage Lockout Pin. To externally program the UVLO threshold of the input supply, connect a resistive divider among input supply, EN/UVLO, and SGND. |

| 16  | OVI              | Overvoltage Comparator Input. Connect a resistive divider among the input supply, OVI, and SGND to set the input overvoltage threshold.                           |

| _   | EP               | Exposed Pad                                                                                                                                                       |

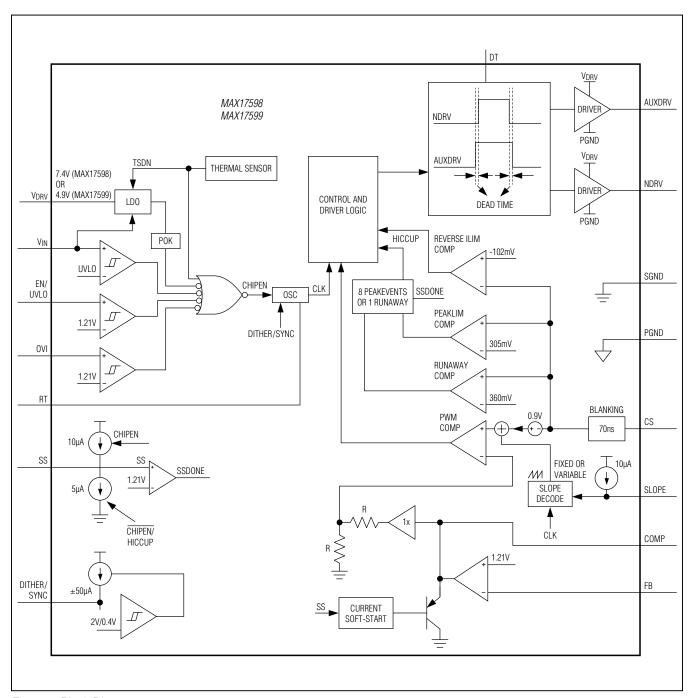

### **Detailed Description**

The MAX17598/MAX17599 low  $I_Q$  active-clamp current-mode PWM controllers contain all the control circuitry required for design of wide-input isolated/nonisolated forward converter industrial power supplies. The MAX17598 has a rising UVLO threshold of 20V with a 13V hysteresis, and is therefore well-suited for universal input (rectified 85V AC to 265V AC) or telecom (36V DC to 72V DC) power supplies. The MAX17599 features a 4.1V rising UVLO with a 200mV hysteresis and is optimized for low-voltage industrial supplies (4.5V DC to 36V DC).

The devices include an AUX driver that drives an auxiliary MOSFET (clamp switch) that helps implement the active-clamp transformer reset topology for forward converters. Such a reset topology has several advantages, including reduced voltage stress on the switches, transformer size reduction due to larger allowable flux swing, and improved efficiency due to elimination of dissipative snubber circuitry. Programmable dead time between the AUX and main driver allows for zero voltage switching (ZVS).

#### Input Voltage Range

The MAX17598 has different rising and falling undervoltage lockout (UVLO) thresholds on the  $V_{\rm IN}$  pin than those of the MAX17599. The thresholds for the MAX17598 are optimized for implementing power-supply startup schemes typically used for off-line AC/DC and telecom DC-DC power supplies that are typically encountered in industrial applications. As such, the MAX17598 has no limitation on the maximum input voltage, as long as the external components are rated suitably, and the maximum operating voltages of the MAX17598 are respected. The MAX17598 can be successfully used in universal input (85V to 265V AC) rectified bus applications, rectified 3-phase DC bus applications, and telecom (36V to 72V DC) applications.

The  $V_{IN}$  pin of the MAX17599 has a maximum operating voltage of 36V. The MAX17599 implements rising and falling thresholds on the  $V_{IN}$  pin that assume power-supply startup schemes, typical of lower voltage DC-DC applications down to an input voltage of 4.5V DC. Thus isolated/non-isolated active-clamp converters with supply-voltage range of 4.5V to 36V can be implemented with the MAX17599. See *Startup Operation* section for more details on power-supply startup schemes for MAX17598/MAX17599.

# Low IQ, Wide-Input Range, Active Clamp Current-Mode PWM Controllers

Figure 1. Block Diagram

# Low IQ, Wide-Input Range, Active Clamp Current-Mode PWM Controllers

#### Linear Regulator (V<sub>DRV</sub>)

The MAX17598/MAX17599 have an internal linear regulator that is powered from the  $V_{IN}$  pin. The output of the linear regulator is connected to the  $V_{DRV}$  pin, and should be decoupled with a 1µF capacitor to ground for stable operation. The  $V_{DRV}$  converter output supplies the MOSFET drivers internal to the MAX17598/MAX17599. The  $V_{DRV}$  voltage is regulated at 7.4V (typ) in the MAX17598, and at 4.9V (typ) in the MAX17599. The maximum operating voltage of the IN pin is 29V for the MAX17598 and 36V for the MAX17599.

#### Maximum Duty Cycle (Dmax)

The MAX17598/MAX17599 operate at a maximum duty cycle of 72.5% (typ). When the SLOPE pin is left OPEN, the ICs have the necessary amount of slope compensation to provide stable, jitter-free current-mode control operation in applications where the operating duty cycle is less than 50%. Slope compensation is necessary for stable operation of current-mode controlled converters at duty cycles greater than 50%, in addition to the loop compensation required for small signal stability. The MAX17598/MAX17599 implement a SLOPE pin for this purpose. See the *Slope Compensation Programming* section for more details.

### **Applications Information**

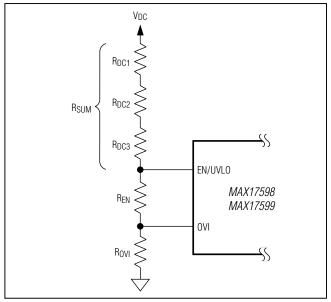

#### Startup Voltage and Input Overvoltage Protection Setting (EN/UVLO, OVI)

The EN/UVLO pin in the MAX17598/MAX17599 serves as an enable/disable input, as well as an accurate programmable undervoltage lockout (UVLO) pin. The MAX17598/MAX17599 do not commence startup operations unless the EN/UVLO pin voltage exceeds 1.21V (typ). The MAX17598/MAX17599 turn off if the EN/UVLO pin voltage falls below 1.15V (typ). A resistor divider from the input DC bus to ground maybe used to divide down and apply a fraction of the input DC voltage to the EN/ UVLO pin as shown in Figure 2. The values of the resistor divider can be selected so that the EN/UVLO pin voltage exceeds the 1.21V (typ) turn on threshold at the desired input DC bus voltage. The same resistor divider can be modified with an additional resistor, R<sub>OVI</sub>, to implement input overvoltage protection, in addition to the EN/UVLO functionality as shown in Figure 2. When the voltage at the OVI pin exceeds 1.21V (typ), the MAX17598/MAX17599 stop switching. Switching resumes with soft-start operation, only if the voltage at the OVI pin falls below 1.15V (typ). The OVI feature is easily disabled by tying the pin to ground. For given values of startup DC input voltage (VSTART) and input overvoltage protection voltage (VOVI), the resistor values for the divider can be calculated as follows, assuming a 24.9k $\Omega$  resistor for ROVI. RSUM represents the series combination of several resistors that might be needed in high-voltage DC bus applications (MAX17598) or a single resistor in low-voltage DC-DC applications (MAX17599).

$$R_{EN} = 24.9 \times \left[ \frac{V_{OVI}}{V_{START}} - 1 \right] k\Omega,$$

where V<sub>START</sub> and V<sub>OVI</sub> are in volts.

$$R_{SUM} = \left[24.9 + R_{EN}\right] \times \left[\frac{V_{START}}{1.21} - 1\right] k\Omega,$$

where  $R_{EN}$  is in  $k\Omega$ .  $R_{SUM}$  might need to be implemented as equal multiple resistors in series ( $R_{DC1}$ ,  $R_{DC2}$ ,  $R_{DC3}$ ) so that voltage across each resistor is limited to its maximum operating voltage.

$$R_{DC1} = R_{DC2} = R_{DC3} = \frac{R_{SUM}}{3} k\Omega.$$

Figure 2. Programming EN/UVLO, OVI

# Low IQ, Wide-Input Range, Active Clamp Current-Mode PWM Controllers

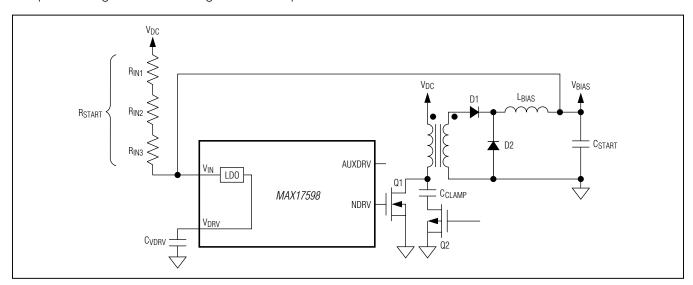

#### **Startup Operation**

The MAX17598 is optimized for implementing activeclamp converters operating either from a rectified AC input or in a 36V DC to 72VDC telecom application. A cost-effective RC startup circuit can be used in such applications. In this startup method (Figure 3), when the input DC voltage is applied, the startup resistor R<sub>START</sub> charges the startup capacitor C<sub>START</sub>, causing the voltage at the V<sub>IN</sub> pin to increase towards the rising VIN UVLO threshold (20V typical). During this time, the MAX17598 draws a low startup current of 20µA (typ) through the startup resistor RSTART. When the voltage at VIN reaches the rising IN UVLO threshold, the MAX17598 commences all internal operations and drives the external MOSFETs connected to NDRV and AUXDRV. In this condition, the MAX17598 draws 2mA (typ) current in from C<sub>START</sub>, in addition to the current required to switch the gates of the external MOSFETs Q1and Q2. Since this current cannot be supported by the current through R<sub>START</sub>, the voltage on C<sub>START</sub> starts to drop. When suitably configured as shown in Figure 3, the converter operates to generate an output voltage (VBIAS) that is bootstrapped to the VIN pin. If the voltage VBIAS exceeds 7V before the voltage on CSTART falls below 7V (typ), then the VIN voltage is sustained by VBIAS, thus allowing the MAX17598 to continue to operate with energy from VBIAS. The large hysteresis (13V typical) of the MAX17598 allows for a small startup capacitor (CSTART). The low startup current (20µA typical) allows the use of a large startup resistor (RSTART), thus reducing power dissipation at higher DC bus voltages. The startup resistor R<sub>START</sub> might need to be implemented as equal, multiple resistors in series (R<sub>IN1</sub>, R<sub>IN2</sub> and R<sub>IN3</sub>) to share the applied high DC voltage in offline applications so that the voltage across each resistor is limited to the maximum continuous operating voltage rating. R<sub>START</sub> and C<sub>START</sub> can be calculated as follows:

$$C_{START} = 0.09 \begin{bmatrix} 7.4 \times C_{VDRV} + 0.04 \times I_{IN} \times C_{SS} \\ + \left(I_{IN} + \frac{Q_{GATE} \times f_{sw}}{10^6}\right) t_{SS} \end{bmatrix} \mu F$$

where  $l_{IN}$  is the supply current drawn at the IN pin in mA,  $Q_{GATE}$  is the sum of the gate charges of the external MOSFETs Q1 and Q2 in nC,  $f_{SW}$  is the switching frequency of the converter in Hz,  $t_{SS}$  is the soft-start time programmed for the converter in ms.  $C_{VDRV}$  is cummulative capacitor used at DRV node in  $\mu\text{F},$  and  $C_{SS}$  is soft-start capacitor in nF. See the <code>Soft-Start</code> section.

$$R_{START} = \frac{\left(V_{START} - 10\right) \times 50}{\left[1 + C_{START}\right]} k\Omega,$$

where  $C_{START}$  is the startup capacitor in  $\mu F$ .

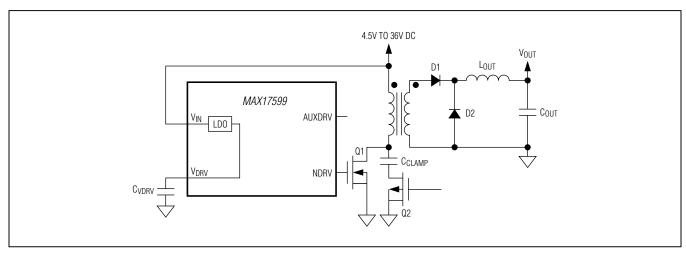

The IN UVLO rising threshold of the MAX17599 is set to 4.1V with a hysteresis of 200mV, and is optimized for low-voltage DC-DC applications in the range of 4.5V DC to 36V DC. The IN pin is rated for a maximum operating input voltage of 36V DC and can directly be connected to the input DC supply.

Figure 3. RC-Based Startup Circuit

## Low IQ, Wide-Input Range, Active Clamp Current-Mode PWM Controllers

Figure 4. Typical Startup Circuit with IN Connected Directly to DC Input

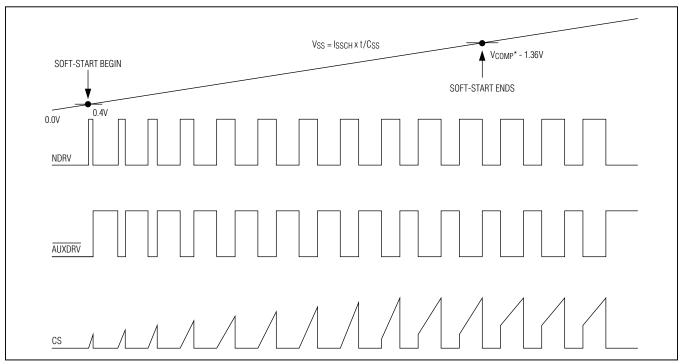

#### Soft-Start and Soft-Stop

In a current-mode isolated active clamp forward converter, the COMP voltage programs the peak current in the primary, and thus the secondary-side inductor current as well. The MAX17598/MAX17599 implement a soft-start scheme that controls the COMP pin of the device at turn on. A useful benefit of this feature is the elimination of need for secondary-side soft-start circuitry in such isolated applications. In the absence of secondary-side soft-start circuitry, the secondary-side error amplifier can cause the output voltage to rapidly reach the regulation value, thus causing inrush current and output voltage overshoot. The MAX17598/MAX17599 avoid this issue by applying a soft-start to the COMP pin. Thus the regulator's primary and secondary currents are ramped up in a well-controlled manner resulting in a current-mode soft-start operation.

Soft-start period of MAX17598/MAX17599 can be programmed by selecting the value of capacitor connected from SS pin to GND. The capacitor  $C_{SS}$  can be calculated as follows:

$$C_{SS} = \frac{10 \times t_{SS}}{V_{COMP} - 1.81} \, nF$$

where  $t_{SS}$  is in ms,  $V_{COMP}$  is steady-state COMP voltage ( $V_{COMP,MAX} = 2.6V$ ).

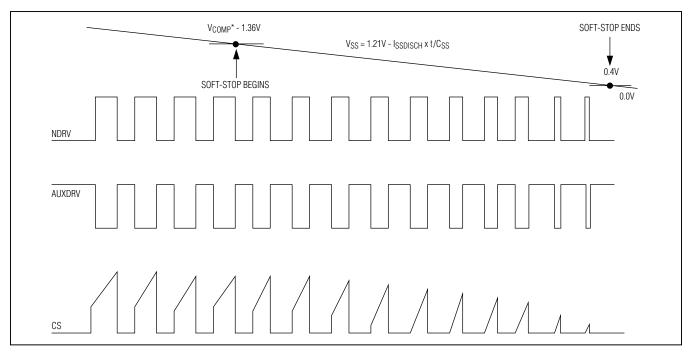

A soft-stop feature ramps down the output voltage when the device is turned off, and provides safe discharging of the clamp capacitor, thus allowing the controller to restart in a well-controlled manner. Additionally, a negative current limit is provided in the current-sense circuitry that helps limit the clamp switch current under dynamic operating conditions, such as momentary input overvoltage charging from a precharged output capacitor. The soft-stop duration is twice that of the programmed soft-start period.

#### **Programming Slope Compensation**

Since the MAX17598/MAX17599 operate at a maximum duty cycle of 72.5% (typ), slope compensation is required to prevent subharmonic instability that occurs naturally in continuous-conduction mode, peak current mode-controlled converters operating at duty cycles greater than 50%. A minimum amount of slope signal is added to the sensed current signal, even for converters operating below 50% duty to provide stable, jitter-free operation. The SLOPE pin allows the user to program the necessary slope compensation by setting the value of the resistor RSLOPE connected from SLOPE pin to ground.

$$R_{SLOPE} = \frac{S_E - 8}{1.55} k\Omega$$

where  $S_E$ , the slope is expressed in mV per microseconds. For the default minimum slope compensation of 50mV/ $\mu$ s (typ), the SLOPE pin should be connected to SGND or left unconnected.

# Low IQ, Wide-Input Range, Active Clamp Current-Mode PWM Controllers

Figure 5. Duty Cycle Soft-Start

Figure 6. Duty Cycle or Current Soft-Stop

$<sup>^{*}</sup>V_{COMP}$  is steady-state COMP voltage.

## Low IQ, Wide-Input Range, Active Clamp Current-Mode PWM Controllers

#### n-Channel MOSFET Gate Driver

The NDRV output drives an external n-channel MOSFET. NDRV can source/sink in excess of 900mA/1500mA peak current. Therefore, select a MOSFET that yields acceptable conduction and switching losses.

#### p-Channel MOSFET Gate Driver

The AUXDRV output drives an external p-channel MOSFET with the aid of a level shifter, as shown in the *Typical Application Circuits*. AUXDRV can source/sink in excess of 300mA/700mA peak current. Therefore, select a MOSFET that yields acceptable conduction and switching losses. The external PMOSFET used must be able to withstand the maximum clamp voltage.

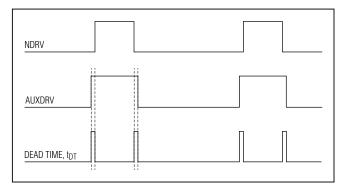

#### **Dead Time**

Dead time between the main and AUX output edges allow ZVS to occur, minimizing switching losses and improving efficiency. The dead time ( $t_{DT}$ ) is applied to both leading and trailing edges of the main and AUX outputs as shown in Figure 7. Connect a resistor between DT and GND to set  $t_{DT}$  to any value between 25ns and 250ns. RDT in  $k\Omega$ , is calculated as:

$$R_{DT} = 0.4 \times t_{DT} k\Omega$$

where t<sub>DT</sub> is in ns.

#### Oscillator/Switching Frequency

The ICs' switching frequency is programmable between 100kHz and 1MHz with a resistor  $R_{RT}$  connected between RT and GND. Use the following formula to determine the appropriate value of  $R_{RT}$  needed to generate the desired output switching frequency ( $f_{SW}$ ):

$$R_{RT} = \frac{1 \times 10^{10}}{f_{SW}}$$

where fsw is the desired switching frequency.

#### Peak-Current-Limit

The current-sense resistor (R<sub>CS</sub>), connected between the source of the n-channel MOSFET and PGND, sets the current limit. The source end of current-sense resistor connects to CS pin of MAX17598/MAX17599. The signal thus obtained is used by the devices, both for current-mode control and peak-current limiting purposes. The current-limit comparator has a voltage trip level (V<sub>CS-PFAK</sub>) of 305mV, and is independent of slope

Figure 7. Dead Time Between AUXDRV and NDRV

compensation applied to stabilize the converter. The following equation is used to calculate the value of R<sub>CS</sub>:

$$R_{CS} = \frac{305 \text{mV}}{1.2 \times I_{PRI PEAK}}$$

where I<sub>PRI\_PEAK</sub> is the peak current in the primary side of the transformer, which also flows through the main n-channel MOSFET. When the voltage produced by this current (through the current-sense resistor) exceeds the current-limit comparator threshold, the MOSFET driver (NDRV) terminates the current on-cycle within 40ns (typ).

The devices implement 70ns of internal leading-edge blanking to ignore leading-edge current spikes encountered in practice due to parasitics. Use a small RC network for additional filtering of the leading-edge spike on the sense waveform when needed. Set the corner frequency of the RC filter network at 5 to 10 times the switching frequency.

For a given peak-current-limit setting, the runaway current limit is typically 20% higher. The peak current-limit-triggered hiccup operation is disabled until the end of soft-start, while the runaway current-limit-triggered hiccup operation is always enabled.

#### **Negative Peak Current Limit**

The MAX17598/MAX17599 protect against excessive negative currents through the clamp switch, primary of the transformer and the clamp capacitor under dynamic operating conditions. The devices limit negative current by monitoring the voltage across  $R_{CS}$ , while the AUXDRV output is low and the p-Channel FET is on. The typical negative-current-limit threshold is set at -102mV (1/3 of the positive-peak-current-limit threshold).

## Low IQ, Wide-Input Range, Active Clamp Current-Mode PWM Controllers

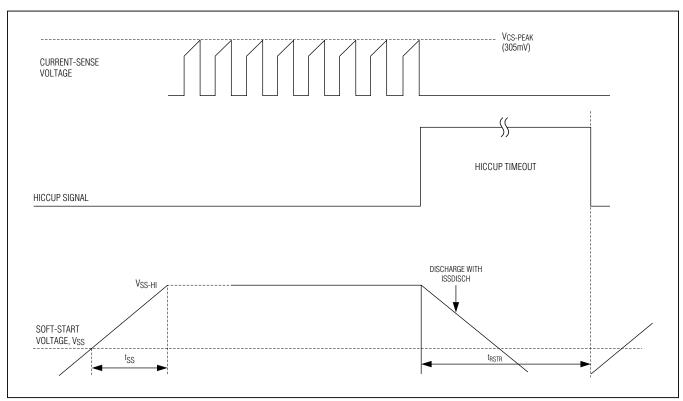

Figure 8. Hiccup-Mode Timing Diagram

# Output Short-Circuit Protection with Hiccup Mode

When the MAX17598/MAX17599 detect eight consecutive peak-current-limit events, both NDRV and AUXDRV driver outputs are turned off (hiccup is followed by softstop) for a restart period, tRSTR. After tRSTR, the device turns on again with a soft-start. The duration of the restart period is 32678 clock cycles, and therefore depends on the switching frequency setting. The device also features a runaway current limit setting at 120% (typ) of the peak current limit. This feature is useful under short-circuit faults in forward converters with synchronous rectifiers that occur during minimum on-time conditions at high input voltages. Under these conditions, the primary peak current tends to build up and staircase beyond the peak current limit setting due to insufficient discharging of the output inductor. One single event of a runaway current limit forces the MAX17598/MAX17599 into hiccup mode operation. Figure 8 shows the behavior of the device prior and during hiccup mode.

#### **Oscillator Synchronization**

The internal oscillator can be synchronized to an external clock by applying the clock to SYNC/DITHER directly. The external clock frequency can be set anywhere between 1.1x to 1.3x the internal clock frequency. Using an external clock increases the maximum duty cycle by a factor equal to f<sub>SYNC</sub>/f<sub>SW</sub>.

# Frequency Dithering for Spread-Spectrum Applications (Low EMI)

The switching frequency of the converter can be dithered in a range of  $\pm 10\%$  by connecting a capacitor from DITHER/SYNC to GND, and a resistor from DITHER to RT as shown in the *Typical Applications Circuit*. This results in lower EMI.

## Low IQ, Wide-Input Range, Active Clamp Current-Mode PWM Controllers

A current source at SYNC/DITHER charges the capacitor  $C_{\rm DITHER}$  to 2V with 50µA. Upon reaching this trip point, it discharges  $C_{\rm DITHER}$  to 0.4V with 50µA. The charging and discharging of the capacitor generates a triangular waveform on SYNC/DITHER with peak levels at 0.4V and 2V.  $C_{\rm DITHER}$  is calculated as:

$$C_{DITHER} = \frac{15.625}{f_{TRI}} nF$$

where fTRI is in kHz.

Typically,  $f_{TRI}$  should be set close to 1kHz. The resistor  $R_{DITHER}$  connected from SYNC/DITHER to RT determines the amount of dither as follows:

$$\text{\%DITHER} = \frac{R_{RT}}{R_{DITHER}}$$

where %DITHER is the amount of dither expressed as a percentage of the switching frequency. Setting  $R_{DITHER}$  to 10 x  $R_{RT}$  generates  $\pm 10\%$  dither.

#### **Layout Recommendations**

All connections carrying pulsed currents must be very short and as wide as possible. The inductance of these connections must be kept to an absolute minimum due to the high di/dt of the currents in high-frequency switching power converters. This implies that the loop areas for forward- and return-pulsed currents in various parts of the circuit should be minimized. Additionally, small current loop areas reduce radiated EMI. Similarly, the heatsink of the MOSFET presents a dV/dt source. Therefore, the surface area of the MOSFET heatsink should be minimized as much as possible.

Ground planes must be kept as intact as possible. The ground plane for the power section of the converter should be kept separate from the analog ground plane, except for a connection at the least-noisy section of the power ground plane, typically the return of the input filter capacitor. The negative terminal of the filter capacitor, the ground return of the power switch, and current-sensing resistor must be close together. PCB layout also affects the thermal performance of the design. A number of thermal vias that connect to a large ground plane should be provided under the exposed pad of the part for efficient heat dissipation. For a sample layout that ensures first pass success, please refer to the MAX17598/MAX17599 Evaluation Kit layouts available at www.maximintegrated.com. For universal AC input designs, follow all applicable safety regulations. Offline power supplies can require UL, VDE, and other similar agency approvals.

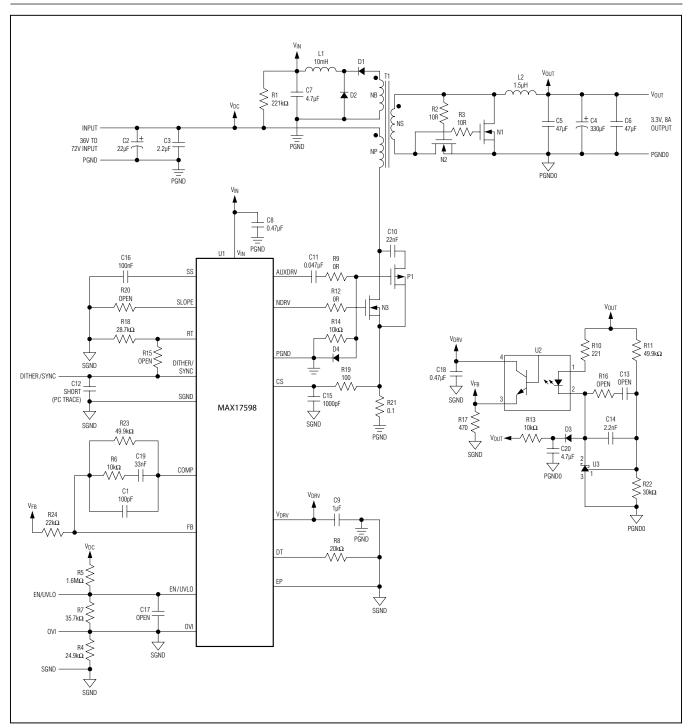

# Low IQ, Wide-Input Range, Active Clamp Current-Mode PWM Controllers

### **Typical Application Circuits**

Figure 9. Typical Application Circuit (Telecom Power Supplies)

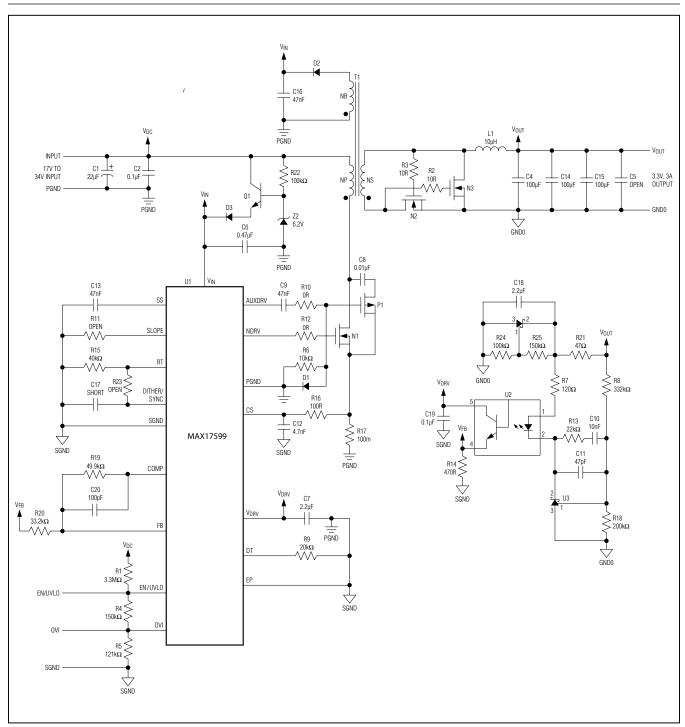

# Low IQ, Wide-Input Range, Active Clamp Current-Mode PWM Controllers

**Typical Application Circuits (continued)**

Figure 10. Typical Application Circuit (Power Supply for Low-Voltage DC-DC Applications)

# Low IQ, Wide-Input Range, Active Clamp Current-Mode PWM Controllers

### **Ordering Information**

| PART                 | TEMP RANGE      | PIN PACKAGE | FUNCTIONALITY                                           | UVLO, IN<br>CLAMP | Dmax |

|----------------------|-----------------|-------------|---------------------------------------------------------|-------------------|------|

| MAX17598ATE+         | -40°C to +125°C | 16 TQFN     | Active-clamp, peak-current-mode, offline PWM controller | 20V, Yes          | 70%  |

| <b>MAX17599</b> ATE+ | -40°C to +125°C | 16 TQFN     | Active-clamp, peak-current-mode, PWM DC-DC controller   | 4V, No            | 70%  |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

## **Package Information**

For the latest package outline information and land patterns (foot-prints), go to <a href="https://www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE | PACKAGE | OUTLINE        | LAND        |

|---------|---------|----------------|-------------|

| TYPE    | CODE    | NO.            | PATTERN NO. |

| 16 TQFN | T1633+4 | <u>21-0136</u> |             |

## Low IQ, Wide-Input Range, Active Clamp Current-Mode PWM Controllers

### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                                                                                                                                           | PAGES<br>CHANGED |

|--------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 0                  | 1/12             | Initial release                                                                                                                                                                                                       | _                |

| 1                  | 3/13             | Updated General Description, Benefits and Features, Absolute Maximum Ratings, Electrical Characteristics, Typical Operating Characteristics, Pin Description, Detailed Description sections, and Figures 1, 3–6, 8–10 | 1–23             |

| 2                  | 4/14             | R2 and R3 components values updated.                                                                                                                                                                                  | 21-22            |

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.