**MAX22213**

Click here to ask an associate for production status of specific part numbers.

# 36V, 3.8A Quad Half H-Bridge Drivers with Integrated Current Sense

#### **General Description**

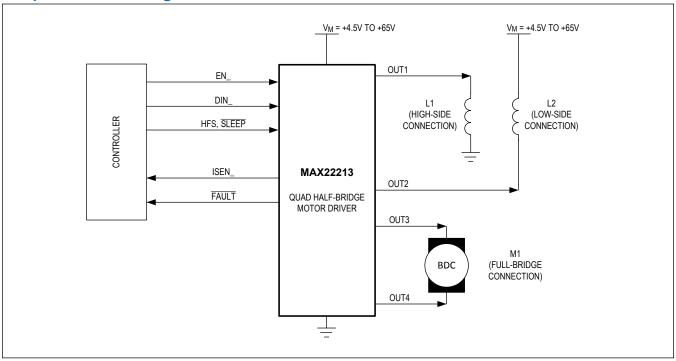

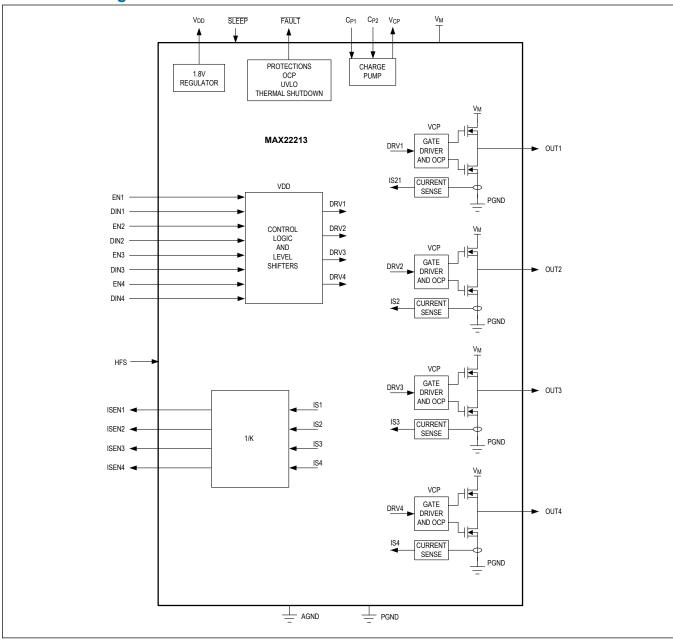

The MAX22213 provides four individually controllable 36V,  $3.8A_{MAX}$  half H-bridge drivers. It can be used to drive four solenoids, two brushed DC motors, one single stepper motor, or a combination of different loads.

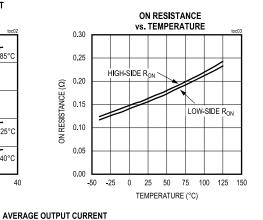

The power FETs have very low impedance resulting in high driving efficiency and low heat generated. The typical total  $R_{ON}$  (high side plus low side) is  $0.25\Omega$  (typ). Each half bridge can be individually PWM controlled by mean of two logic inputs (DIN\_, EN\_).

The MAX22213 integrates non-dissipative current sensing, which eliminates the bulky external power resistors normally required for this function, resulting in dramatic space and power saving compared with mainstream applications based on an external sense resistor. A current proportional to the internally-sensed load current is output to the external current-monitor pins (ISEN\_). By connecting an external resistor to these pins, a voltage proportional to the motor current is generated. The voltage drop across the external resistors can be input into the controller ADC whenever the control algorithm requires the current/torque information.

The maximum output current per half H-bridge is  $I_{MAX} = 3.8A$  and is limited by the overcurrent protection (OCP) circuit. This current can be driven for very short transients and aims to effectively drive small capacitive loads.

The maximum RMS current per H-bridge is  $I_{RMS} = 2A$  assuming a 4-layer PCB at room temperature. Since this current is limited by thermal considerations, the actual maximum RMS current depends on the thermal characteristic of the application (PCB ground planes, heatsinks, forced air ventilation etc.).

In applications in which the requirement of the maximum current is less than 1.5A and high-sensing accuracy is desired, the half full-scale (HFS) logic input pin can be set high to halve the current ratings and double the low-side FET  $R_{ON}$ . This results in better current-monitor accuracy in the bottom end of the current range.

The MAX22213 features OCP, thermal shutdown (TSD), and undervoltage lockout (UVLO). An open-drain, active-low FAULT pin is activated every time a fault condition is detected. During TSD and UVLO events, the driver outputs are three-stated until normal operations are restored.

The MAX22213 is available into a small 5mm x 5mm, 32-pin TQFN and 4.4mm x 9.7mm, 28-pin TSSOP package.

#### **Applications**

- Stepper-Motor Driver

- Brushed DC Motor Driver

- Solenoid Driver

- Latched Valves

#### **Benefits and Features**

- Four Independent Half H-Bridge Drivers

- · 36V Maximum Operating Voltage

- 0.25Ω R<sub>ON</sub> (High Side + Low Side) at T<sub>A</sub> = +25°C

- Fully Independent Half Bridge Control

- Current Ratings per H-Bridge (T<sub>A</sub>= +25°C):

- I<sub>MAX</sub> = 3.8A (Impulsive Current for Driving Capacitive Loads)

- I<sub>RMS</sub> = 2A

- Internal Current Sensing (ICS) Eliminates External Bulky Resistors and Improves Efficiency

- Half Full-Scale (HFS) Pin to Improve Current-Control Accuracy in the Low-Current Range

- Current-Sense Output Monitor

- Fault Indicator Pin (FAULT)

- Protections

- Overcurrent Protection for Each Individual Channel (OCP)

- Undervoltage Lockout (UVLO)

- Thermal Shutdown T<sub>SD</sub> = +165°C

- 5mm x 5mm, 32-Pin TQFN and 4.4mm x 9.7mm, 28-Pin TSSOP Packages

Ordering Information appears at end of data sheet.

19-101603; Rev 1; 2/24

# **Simplified Block Diagram**

### **TABLE OF CONTENTS**

| General Description                          |    |

|----------------------------------------------|----|

| Applications                                 |    |

| Benefits and Features                        |    |

| Simplified Block Diagram                     |    |

| Absolute Maximum Ratings                     | 6  |

| Package Information                          | 6  |

| 32-Pin TQFN—5mm x 5mm                        | 6  |

| 28-Pin TSSOP—4.4mm x 9.7mm                   |    |

| Electrical Characteristics                   |    |

| Typical Operating Characteristics            |    |

| Pin Configurations                           |    |

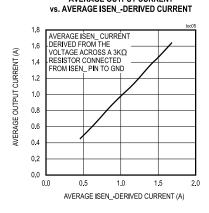

| TQFN Pin Configuration                       |    |

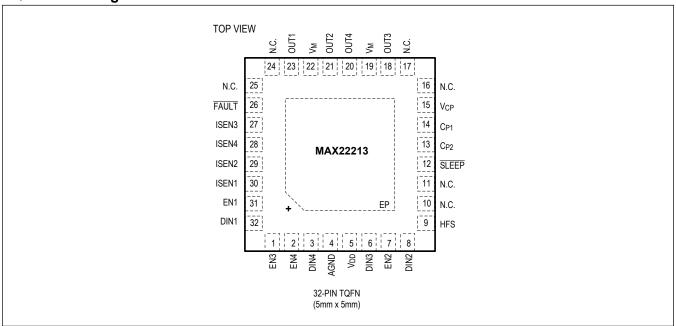

| TSSOP Pin Configuration                      |    |

| Pin Description                              |    |

| Functional Diagrams                          |    |

| Detailed Description                         |    |

| Sleep Mode (SLEEP Pin)                       |    |

| PWM Control                                  |    |

| Current-Sense Output (ISEN_)—Current Monitor |    |

| Half Full Scale (HFS)                        |    |

| Fault Protection                             |    |

| Over Current Protection—(OCP)                |    |

| Thermal-Shutdown Protection                  |    |

| Undervoltage-Lockout Protection              |    |

| Applications Information                     |    |

| Typical Application Circuits                 |    |

| Application Diagram                          |    |

| Ordering Information                         |    |

| Revision History                             | 20 |

|          | LIST OF FIGURES                                                    |

|----------|--------------------------------------------------------------------|

| MAX22213 | 36V, 3.8A Quad Half H-Bridge Drivers with Integrated Current Sense |

Analog Devices | 4 www.analog.com

# MAX22213

# 36V, 3.8A Quad Half H-Bridge Drivers with Integrated Current Sense

| LIST OF TABLES                |  |

|-------------------------------|--|

| Table 1. MAX22213 Truth Table |  |

| Table 2. HFS Truth Table      |  |

#### **Absolute Maximum Ratings**

| V <sub>M</sub> to GND0.3                                    | 3V to +42V [          | DIN_ to GND                    | 0.3V to +6V    |

|-------------------------------------------------------------|-----------------------|--------------------------------|----------------|

| V <sub>DD</sub> to GND0.3V to min (+2.2V, V                 | $V_{M} + 0.3V)$ E     | EN_ to GND                     | 0.3V to +6V    |

| PGND to GND                                                 | V to +0.3V F          | $HF\overline{S}$ to $GND$      | 0.3V to +6V    |

| OUT0.3V to (\)                                              |                       | SLEEP to GND                   |                |

| V <sub>CP</sub> to GND(V <sub>M</sub> - 0.3V) to min (+42V  | $(V, V_M + 6V)$       | Operating Temperature Range    | 40°C to +125°C |

| C <sub>P2</sub> to GND0.3V to min (+42V, V                  | $V_{M} + 0.3V)$       | Junction Temperature           | +160°C         |

| C <sub>P1</sub> to GND (V <sub>M</sub> - 0.3V) to min (+42V |                       | Storage Temperature Range      |                |

| FAULT to GND0                                               |                       | Soldering Temperature (reflow) | +260°C         |

| ISEN_ to GND0.3V to min (+2.2V, V                           | <sub>DD</sub> + 0.3V) |                                |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

#### 32-Pin TQFN—5mm x 5mm

| Package Code                            | T3255-8C       |  |  |

|-----------------------------------------|----------------|--|--|

| Outline Number                          | <u>21-0140</u> |  |  |

| Land Pattern Number                     | 90-0013        |  |  |

| Thermal Resistance, Single-Layer Board: |                |  |  |

| Junction to Ambient (θ <sub>JA</sub> )  | 47°C/W         |  |  |

| Junction to Case (θ <sub>JC</sub> )     | 1.7°C/W        |  |  |

| Thermal Resistance, Four-Layer Board:   |                |  |  |

| Junction to Ambient (θ <sub>JA</sub> )  | 29°C/W         |  |  |

| Junction to Case (θ <sub>JC</sub> )     | 1.7°C/W        |  |  |

#### 28-Pin TSSOP—4.4mm x 9.7mm

| Package Code                           | U28E+5C        |  |  |  |

|----------------------------------------|----------------|--|--|--|

| Outline Number                         | <u>21-0108</u> |  |  |  |

| Land Pattern Number                    | <u>90-0147</u> |  |  |  |

| Thermal Resistance, Four-Layer Board:  |                |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> ) | 24.65°C/W      |  |  |  |

| Junction to Case (θ <sub>JC</sub> )    | 1.52°C/W       |  |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **Electrical Characteristics**

$(V_M$  = +4.5V to +36V, typical values are  $T_A$  = +25°C and  $V_M$  = +24V, limits are 100% tested at  $T_A$  = +25°C. Limits over the operating temperature range and relevant supply-voltage range are guaranteed by design and characterization.)

| PARAMETER                         | SYMBOL          | CONDITIONS        | MIN | TYP | MAX | UNITS |

|-----------------------------------|-----------------|-------------------|-----|-----|-----|-------|

| POWER SUPPLY                      |                 |                   |     |     |     |       |

| Supply-Voltage Range              | V <sub>M</sub>  |                   | 4.5 |     | 36  | V     |

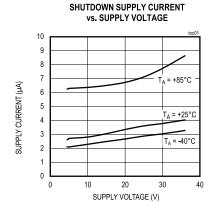

| Sleep-Mode Current<br>Consumption | I <sub>VM</sub> | SLEEP = logic low |     | 4   | 11  | μA    |

### **Electrical Characteristics (continued)**

$(V_M$  = +4.5V to +36V, typical values are  $T_A$  = +25°C and  $V_M$  = +24V, limits are 100% tested at  $T_A$  = +25°C. Limits over the operating temperature range and relevant supply-voltage range are guaranteed by design and characterization.)

| PARAMETER                                          | SYMBOL                 | CONDITIONS                                         | MIN   | TYP                  | MAX   | UNITS |

|----------------------------------------------------|------------------------|----------------------------------------------------|-------|----------------------|-------|-------|

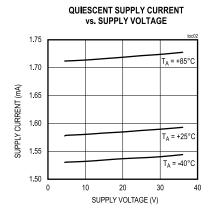

| Quiescent Current<br>Consumption                   | I <sub>VM</sub>        | SLEEP = logic high                                 |       | 2                    | 4     | mA    |

| 1.8V Regulator Output<br>Voltage                   | V <sub>VDD</sub>       | $V_{M}$ = +4.5V, $I_{LOAD}$ = internal consumption | 1.74  | 1.8                  | 1.86  | V     |

| V <sub>DD</sub> Current Limit                      | I <sub>V18(LIM)</sub>  |                                                    | 20    |                      |       | mA    |

| V <sub>DD</sub> UVLO Rising                        | UVLOV18 <sub>R</sub>   | V <sub>DD</sub> rising                             | 1.59  | 1.65                 | 1.69  | V     |

| V <sub>DD</sub> UVLO Falling                       | UVLOV18 <sub>F</sub>   | V <sub>DD</sub> falling                            | 1.535 | 1.58                 | 1.635 | V     |

| Charge-Pump Voltage                                | V <sub>CP</sub>        |                                                    |       | V <sub>M</sub> + 2.7 |       | V     |

| LOGIC LEVEL INPUTS/C                               | UTPUTS                 |                                                    | •     |                      |       | '     |

| Input Voltage<br>Level—High                        | V <sub>IH</sub>        |                                                    | 1.2   |                      |       | V     |

| Input Voltage<br>Level—Low                         | V <sub>IL</sub>        |                                                    |       |                      | 0.65  | V     |

| Input Hysteresis                                   | V <sub>HYS</sub>       |                                                    |       | 110                  |       | mV    |

| Pull-Down Current                                  | I <sub>PD</sub>        | To GND                                             | 16    | 34                   | 50    | μA    |

| Open-Drain Output<br>Logic-Low Voltage             | V <sub>OL</sub>        | I <sub>LOAD</sub> = 5mA                            |       |                      | 0.2   | V     |

| Open-Drain Output<br>Logic-High Leakage<br>Current | Іон                    | V <sub>PIN</sub> = 3.3V                            | -1    |                      | +1    | μΑ    |

| SLEEP Voltage Level<br>High                        | V <sub>IH(SLEEP)</sub> |                                                    | 0.9   |                      |       | V     |

| SLEEP Voltage Level<br>Low                         | V <sub>IL(SLEEP)</sub> |                                                    |       |                      | 0.6   | V     |

| SLEEP Pull-Down Input<br>Resistance                | R <sub>PD(SLEEP)</sub> |                                                    | 0.8   | 1.5                  |       | ΜΩ    |

| <b>OUTPUT SPECIFICATIO</b>                         | NS                     |                                                    |       |                      |       |       |

| Output On-Resistance                               | Pove                   | HFS = logic low                                    |       | 0.125                | 0.22  | Ω     |

| Low-Side                                           | R <sub>ON(LS)</sub>    | HFS = logic high                                   |       | 0.22                 | 0.42  | 1 12  |

| Output On-Resistance<br>High-Side                  | R <sub>ON(HS)</sub>    |                                                    |       | 0.125                | 0.22  | Ω     |

| Output Leakage                                     | I <sub>LEAK</sub>      | Driver off                                         | -5    |                      | +5    | μA    |

| Dead Time                                          | t <sub>DEAD</sub>      |                                                    |       | 100                  |       | ns    |

| Output Slew Rate                                   | SR                     |                                                    |       | 200                  |       | V/µs  |

| PROTECTION CIRCUITS                                | <b>,</b>               | •                                                  | '     |                      |       |       |

| Overcurrent Protection<br>Threshold                | I <sub>OCP</sub>       |                                                    | 3.8   |                      |       | А     |

| Overcurrent Protection Blanking Time               | t <sub>OCP</sub>       |                                                    | 1     | 2.2                  | 3.2   | μs    |

| Autoretry OCP Time                                 | t <sub>RETRY</sub>     |                                                    |       | 3                    |       | ms    |

| UVLO Threshold on V <sub>M</sub>                   | V <sub>UVLO</sub>      | V <sub>M</sub> rising                              | 3.85  | 4                    | 4.15  | V     |

| UVLO Threshold on V <sub>M</sub><br>Hysteresis     | UVLO <sub>HYS</sub>    |                                                    |       | 0.12                 |       | V     |

### **Electrical Characteristics (continued)**

$(V_M = +4.5V \text{ to } +36V, \text{ typical values are } T_A = +25^{\circ}\text{C} \text{ and } V_M = +24V, \text{ limits are } 100\% \text{ tested at } T_A = +25^{\circ}\text{C}.$  Limits over the operating temperature range and relevant supply-voltage range are guaranteed by design and characterization.)

| PARAMETER                                              | SYMBOL              | C                                                         | ONDITIONS                                                                                 | MIN                                                      | TYP  | MAX | UNITS |   |

|--------------------------------------------------------|---------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------|------|-----|-------|---|

| Thermal Protection Threshold Temperature               | TSD                 |                                                           |                                                                                           |                                                          | +165 |     | °C    |   |

| Thermal Protection<br>Temperature Hysteresis           | TSD <sub>HYS</sub>  |                                                           |                                                                                           |                                                          | 20   |     | °C    |   |

| CURRENT-SENSE MONI                                     | TOR                 | •                                                         |                                                                                           |                                                          |      |     |       |   |

| ISEN_ Voltage Range                                    | ISEN                | Voltage range a                                           | t ISEN_ pins                                                                              | 0                                                        |      | 1.1 | V     |   |

| Current-Monitor Scaling                                | K <sub>ISEN</sub>   | current equation                                          | See the I <sub>SEN</sub> output-<br>n in the Current Sense<br>Current monitor section.    |                                                          | 7500 |     | - A/A |   |

| Factor                                                 | MSEN                | current equation                                          | n. See the I <sub>SEN</sub> output-<br>n in the Current Sense<br>Current monitor section. |                                                          | 3840 |     |       |   |

| Current-Monitor<br>Accuracy                            |                     |                                                           | HFS = logic low,<br>I <sub>OUT</sub> = 0.7A to 3A                                         | -5                                                       | 0.4  | +5  |       |   |

|                                                        | DKISEN <sub>1</sub> |                                                           | HFS = logic high,<br>I <sub>OUT</sub> = 0.35A to<br>1.5A                                  | -5                                                       | 0.4  | +5  |       |   |

|                                                        |                     |                                                           | ( <u>Note 1</u> )                                                                         | HFS = logic low,<br>I <sub>OUT</sub> = 0.4A to<br>0.7A   | -10  | 0.6 | +10   | % |

|                                                        |                     |                                                           |                                                                                           | HFS = logic high,<br>I <sub>OUT</sub> = 0.2A to<br>0.35A | -10  | 0.6 | +10   |   |

| Current-Sense Output<br>-3dB Small-Signal<br>Bandwidth | BW                  |                                                           |                                                                                           |                                                          | 400  |     | KHz   |   |

| FUNCTIONAL TIMING                                      |                     |                                                           |                                                                                           |                                                          |      |     |       |   |

| Sleep Time                                             | tSLEEP              | SLEEP = logic 1 to logic 0 for OUT_ to become three-state |                                                                                           |                                                          |      | 150 | μs    |   |

| Wake-Up Time from Sleep                                | tWAKE               | SLEEP = logic 0 to logic 1 to resume normal operation     |                                                                                           |                                                          |      | 3   | ms    |   |

| Enable Time                                            | t <sub>EN</sub>     | Time from EN_ pin rising edge to driver on                |                                                                                           |                                                          |      | 0.4 | μs    |   |

| Disable Time                                           | t <sub>DIS</sub>    | Time from EN_ pin falling edge to driver off              |                                                                                           |                                                          |      | 0.6 | μs    |   |

Note 1: Guaranteed by design, not production tested.

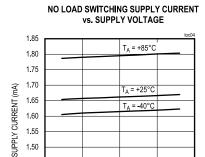

### **Typical Operating Characteristics**

$(V_M = +4.5V \text{ to } +36V; T_A = 25^{\circ}C \text{ unless otherwise noted.})$

1.45

1.40

0

20

SUPPLY VOLTAGE (V)

40

# **Pin Configurations**

#### **TQFN Pin Configuration**

#### **TSSOP Pin Configuration**

# **Pin Description**

| PIN                       |                |                                    |                                                                                                                                                                                                                                                                                             |                      |  |

|---------------------------|----------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|

| TQFN                      | TSSOP          | NAME                               | FUNCTION                                                                                                                                                                                                                                                                                    | TYPE                 |  |

| 26                        | 25             | FAULT                              | Active-Low, Open-Drain, Output Fault Indicator. FAULT goes low to indicate that one or more of the protection mechanisms has been activated. Connect a pull-up resistor from FAULT to the microcontroller supply voltage.                                                                   | Open Drain<br>Output |  |

| 4                         | 7              | AGND                               | Analog Ground. Connect to ground plane.                                                                                                                                                                                                                                                     | GND                  |  |

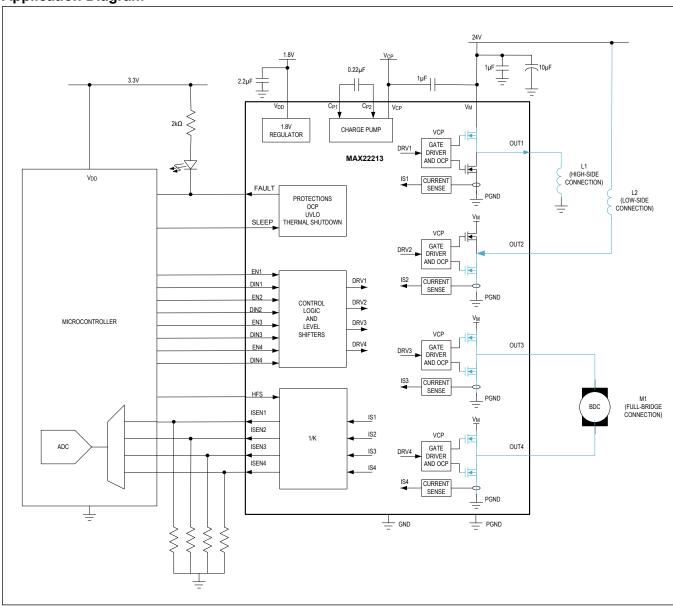

| 19, 22                    | 20, 23         | V <sub>M</sub>                     | Supply Voltage Input. Connect a $V_M$ -rated 1 $\mu$ F (minimum) surface-mounted device capacitor from $V_M$ to GND close to the device, and a 10 $\mu$ F (minimum) electrolytic bypass capacitor from $V_M$ to GND. Higher values can be considered depending on application requirements. | Supply               |  |

| 5                         | 8              | V <sub>DD</sub>                    | 1.8V Linear Regulator Output. Bypass $V_{DD}$ with a 2.2 $\mu$ F capacitor connected close to the device.                                                                                                                                                                                   | Output               |  |

| 23, 21, 18, 20            | 24, 22, 19, 21 | OUT1 to<br>OUT4,<br>respectively   | Driver Outputs                                                                                                                                                                                                                                                                              | Output               |  |

| 30, 29, 27, 28            | 1, 28, 26, 27  | ISEN1 to<br>ISEN4,<br>respectively | Current-Sense Output Monitor. Connect a resistor to GND to monitor the voltage generated with an external ADC (see the Current-Sense Output (ISEN )—Current Monitor section).                                                                                                               | Output               |  |

| 32, 8, 6, 3               | 3, 11, 9, 6    | DIN1 to DIN4, respectively         | /   CM/OS PW/// Inpute                                                                                                                                                                                                                                                                      |                      |  |

| 31, 7, 1, 2               | 2, 10, 4, 5    | EN1 to EN4, respectively           | Enable Pin. Assert high to enable output drivers.                                                                                                                                                                                                                                           | Logic Input          |  |

| 15                        | 18             | V <sub>CP</sub>                    | Charge-Pump Output. Connect a 1 $\mu$ F capacitor between V <sub>CP</sub> and V <sub>M</sub> as close as possible to the device.                                                                                                                                                            | Output               |  |

| 14                        | 17             | C <sub>P1</sub>                    | Charge-Pump Flying Capacitor Pin 1. Connect a 22nF capacitor between CP1 and CP2, as close as possible to the device.                                                                                                                                                                       | Output               |  |

| 13                        | 16             | C <sub>P2</sub>                    | Charge-Pump Flying Capacitor Pin 2. Connect a 22nF capacitor between CP1 and CP2, as close as possible to the device.                                                                                                                                                                       |                      |  |

| 12                        | 15             | SLEEP                              | Active-Low Sleep Pin                                                                                                                                                                                                                                                                        | Logic Input          |  |

| 9                         | 12             | HFS                                | Set Output Current Full Scale. HFS = 0 coefficient is 100%. HFS = 1 coefficient is 50%.                                                                                                                                                                                                     | Logic Input          |  |

| 10, 11, 16,<br>17, 24, 25 | 13, 14         | N.C.                               | No Connection                                                                                                                                                                                                                                                                               |                      |  |

| EP                        | EP             | PGND                               | Power GND. Connect to ground plane. The thermal exposed pad (EP) is also the electrical power GND pin and must be properly connected to GND.                                                                                                                                                | GND                  |  |

# **Functional Diagrams**

#### **Detailed Description**

The MAX22213 provides four individually controllable 36V,  $3.8A_{MAX}$  half H-bridge drivers. It can be used to drive four solenoids, two bushed DC motors, a single stepper motor, or a combination of different loads. The power FETs have very low impedance resulting in high driving efficiency and low heat generation. The typical total  $R_{ON}$  (high side plus low side) is  $0.25\Omega$  (typ). Each half bridge can be PWM controlled by two logic inputs (DIN\_ and EN\_). The MAX22213 integrates non-dissipative current sensing which eliminates the bulky external power-sense resistors to reduce space and save power. The internally sensed current is scaled and output to the external current monitor pins (ISEN\_), which generate a voltage proportional to the load current when a resistor is connected from the ISEN\_ pins to GND. This voltage can be monitored by a microcontroller ADC to get load current and torque information. To improve accuracy for a maximum load current of less than 1.5A, the half full-scale (HFS) logic input can be driven high to halve the maximum current rating and double the low-side FET  $R_{ON}$ . The maximum transient output current for each half bridge is  $R_{MAX} = 3.8A$  and is limited by overcurrent protection (OCP). This current can be tolerated for short intervals and is aimed to drive small capacitive loads. The maximum RMS current per H-Bridge is  $R_{MAX} = 2A$  and is limited by the thermal characteristics of the application such as package and die temperature, PCB ground planes and routing, heatsinks, forced air ventilation, etc.

#### Sleep Mode (SLEEP Pin)

The SLEEP pin can be driven low to place the device into the lowest power-consumption mode possible, with all outputs three-stated, the internal circuits biased off, and the charge pump disabled. A pull-down resistor should be connected between SLEEP and GND to ensure the part is disabled whenever this pin is not actively driven. Driving the SLEEP pin high wakes up the device and returns it to normal mode. twake is 3ms (max).

#### **PWM Control**

When a half-bridge is enabled (EN\_ = logic high), the average output voltage is controlled by the corresponding DIN\_ logic input. PWM techniques can be used to control the output duty cycle and hence to implement motor speed or solenoid current control.

Setting the EN\_ pin at logic low forces the corresponding OUT\_ driver pin to enter a high-impedance mode. The EN\_ input pin should not be used for PWM control.

Each half-bridge (OUT ) is controlled by two logic inputs (DIN , EN ). Table 1 shows the control truth table.

Table 1. MAX22213 Truth Table

| EN_ | IN_ | оит_           | DESCRIPTION                |

|-----|-----|----------------|----------------------------|

| 0   | Х   | High-Impedance | Half H-bridge is disabled. |

| 1   | 0   | Low            | Low-side FET is driven.    |

| 1   | 1   | High           | High-side FET is driven.   |

#### Current-Sense Output (ISEN\_)—Current Monitor

A current proportional to the internally-sensed motor current for each OUT\_ is output to the ISEN\_ pins for each individual half H-bridge. The integrated current sense is unipolar and the current is sensed on the low-side (LS) FET only. Therefore, the current information is meaningful when the LSFET is on and operates in forward mode.

Under this condition, the following ISEN Output Current equation applies:

$$I_{\text{ISEN}}(A) = \frac{I_{\text{OUT}}(A)}{K_{\text{ISEN}}}$$

Where  $K_{ISEN}$  represents the current scaling factor between the output current and its replica at the ISEN\_ pins.  $K_{ISEN}$  is typically 7.5KA/A (with HFS logic low). For example, if the instantaneous output current is 2A, the current sourced at ISEN\_ is 266 $\mu$ A.

When the LS FET is in on in reverse mode or when the HS FET is on, the ISEN current monitor outputs a zero current.

Connecting an external signal resistor,  $R_{ISEN}$ , between ISEN\_ and GND generates a voltage proportional to the motor current. The voltage drop across  $R_{ISEN}$  can be input into the ADC of an external controller in applications in which the motor-control algorithm requires the current/torque information. The  $R_{ISEN}$  value should be chosen so that the peak voltage meets both the ADC full-scale requirement and does not exceed  $V_{ISEN}$  (max). The following equation shows the design formula to calculate  $R_{ISEN}$  once the ADC full-scale voltage ( $V_{FS}$ ) and the maximum operating current ( $I_{MAX}$ ) are known

$$R_{\text{ISEN}}(\Omega) = K_{\text{ISEN}} \times \frac{V_{\text{FS}}(V)}{I_{\text{MAX}}(A)}$$

For example, if the ADC operates up to 1V FS and the maximum operating output current is 2A, then  $R_{ISEN}$  is 7500 x  $1V/2A = 3.75K\Omega$ .

The  $R_{\rm ISEN}$  value also sets the output impedance of the current-sense output circuit (ISEN\_ output impedance). Normally, the input impedance of the ADC is much higher than  $R_{\rm ISEN}$ , enabling a direct connection to the ISEN\_ pin without attenuation. if a low-input-impedance ADC is used, a pre-amplifier (buffer) can be required.

The current-sense-output circuit bandwidth and step response performances (see the Current-Sense Monitor specifications in the <u>Electrical Characteristics</u> section) ensure the current monitor tracks the driver current in motor-drive applications.

#### Half Full Scale (HFS)

The HFS depends on the status of the logic input pin HFS. When HFS is set logic low, the scalar coefficient is 100% and the power FETs'  $R_{ON}$  have a typical value of  $0.25\Omega$  (high side plus low side). When the HFS is set logic high, the scalar coefficient is 50% and the power FETs'  $R_{ON}$  have a typical value higher of  $0.345\Omega$  (high side plus low side). This setting is recommended for applications in which the maximum current does not exceed 1.5A and higher accuracy at low current is desirable.

Table 2 summarizes the HFS settings.

#### **Table 2. HFS Truth Table**

| HFS | MAXIMUM OUTPUT<br>CURRENT (A) | TYPICAL R <sub>ON</sub><br>(HIGH SIDE +<br>LOW SIDE) (Ω) | NOTES                                                                                                                        |

|-----|-------------------------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| 0   | 3                             | 0.25                                                     | Optimized efficiency and extended operating range up to 3.0A <sub>FS</sub> .                                                 |

| 1   | 1.5                           | 0.345                                                    | Reduced operating range up to 1.5A <sub>FS</sub> . Improved current accuracy control at the bottom end of the current range. |

#### **Fault Protection**

#### **Over Current Protection—(OCP)**

OCP protects the device against OUT short circuits to the rails (supply voltage and ground) or excessive load currents.

The OCP threshold is set at 3.8A minimum. If the output current is greater than the OCP threshold for longer than the deglitch time (OCP blanking time), an OCP event is detected, the half H-bridge is set to high-impedance mode and the FAULT output is driven low to indicate to external circuitry that a fault condition has been detected. The half H-bridge is kept in high-impedance mode for 3ms (typ) (treet a specification) before autoretry is initiated when the OUT\_ H-bridge is re-enabled according to its current state as defined by EN\_and DIN\_. If the overcurrent event or short circuit is still present, this cycle repeats. Otherwise, normal operation resumes. The external circuitry monitoring FAULT should take action to avoid prolonged operation under the overcurrent mode as a prolonged OCP autoretry could affect the device reliability.

#### **Thermal-Shutdown Protection**

If the die temperature exceeds  $T_{SD}$  = +165°C (typ), all output pins (OUT1–OUT4) are three-stated and the  $\overline{FAULT}$  pin is driven low. The  $\overline{FAULT}$  pin remains low and the outputs are placed in three-state mode until the die temperature falls by the hysteresis amount of 20°C (typ), after which the  $\overline{FAULT}$  pin is driven high and the outputs are re-enabled.

### MAX22213

# 36V, 3.8A Quad Half H-Bridge Drivers with Integrated Current Sense

#### **Undervoltage-Lockout Protection**

When the  $V_M$  supply voltage is below the UVLO threshold, all OUT\_ outputs are three-stated and the  $\overline{FAULT}$  pin is driven low. The OUT\_ outputs automatically return to their current state (defined by EN\_ and DIN\_) when the  $V_M$  supply voltage exceeds the OVLO threshold (max) and  $\overline{FAULT}$  is driven high.

### **Applications Information**

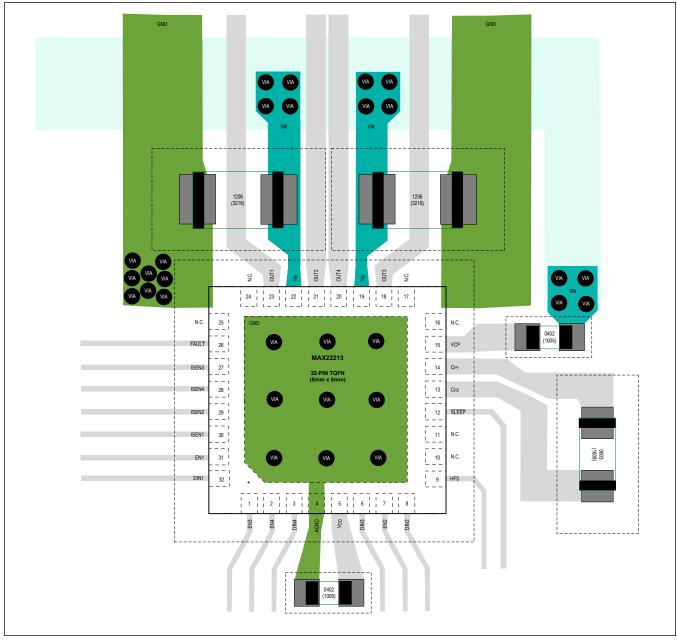

Careful PCB layout is critical to achieve low switching losses and clean, stable operation. Use a multilayer board whenever possible for better noise immunity and power dissipation. Follow these guidelines for good PCB layout:

- 1. Place supply and charge-pump bypass capacitors close to the IC.

- 2. Ensure a good connection from the exposed pad to the GND plane by using vias and ground pours to help to provide an adequate current path and heat dissipation.

- 3. Keep the power traces and load connections short and wide. This practice is essential for high efficiency. Use thick copper PCBs (2oz or 1oz vs. 0.5oz) to enhance full-load efficiency and thermal dissipation.

- 4. Use precision resistors (1% or better) for better accuracy.

Figure 1. MAX22213 Recommended Layout

## **Typical Application Circuits**

#### **Application Diagram**

# **Ordering Information**

| PART NUMBER   | TEMPERATURE RANGE | PIN-PACKAGE  |  |

|---------------|-------------------|--------------|--|

| MAX22213ATJ+  | -40°C to +125°C   | 32 TQFN-EP*  |  |

| MAX22213ATJ+T | -40°C to +125°C   | 32 TQFN-EP*  |  |

| MAX22213AUI+T | -40°C to +125°C   | 28 TSSOP-EP* |  |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

T = Tape and reel.

<sup>\*</sup>EP = Exposed pad.

### **Revision History**

| REVISION<br>NUMBER | REVISION DATE | DESCRIPTION                  | PAGES<br>CHANGED |

|--------------------|---------------|------------------------------|------------------|

| 0                  | 8/23          | Initial release              | _                |

| 1                  | 2/24          | Updated Ordering Information | 19               |