#### **General Description**

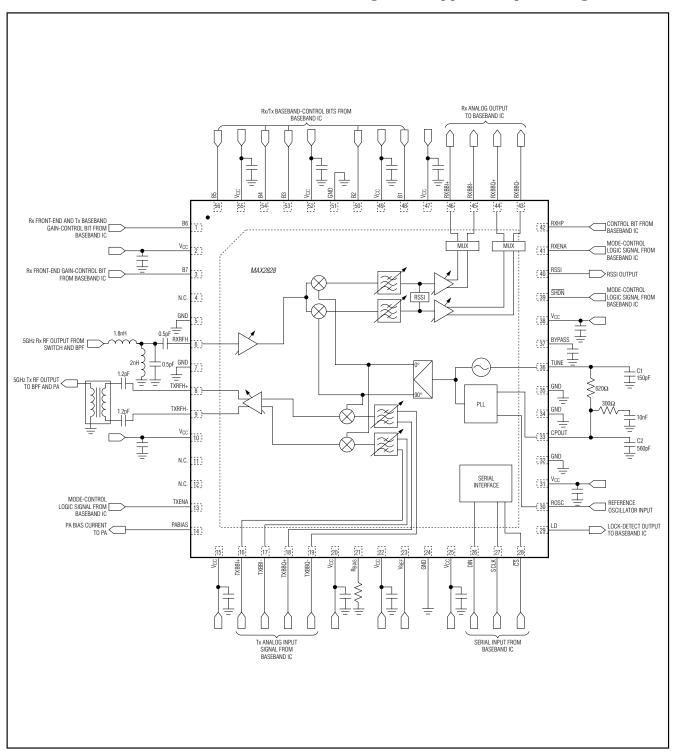

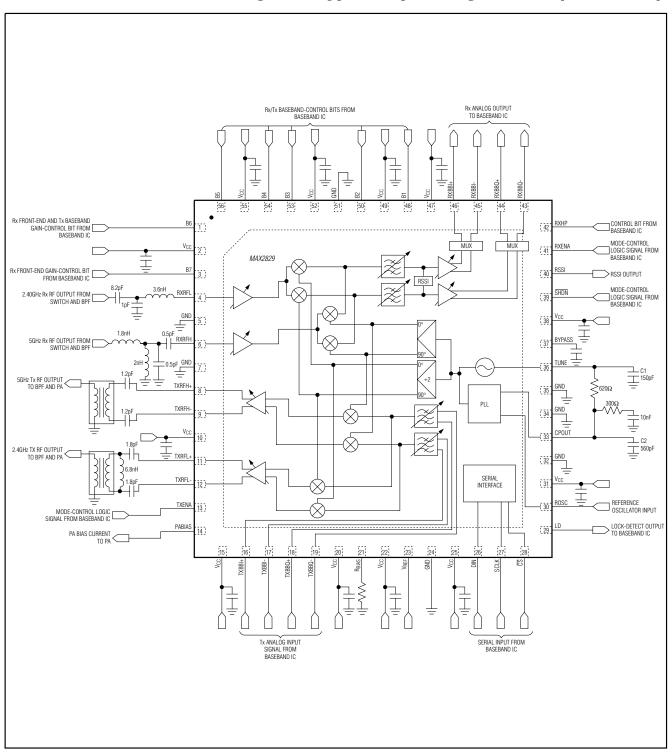

The MAX2828/MAX2829 single-chip, RF transceiver ICs are designed specifically for OFDM 802.11 WLAN applications. The MAX2828 is designed for single-band 802.11a applications covering world-band frequencies of 4.9GHz to 5.875GHz. The MAX2829 is designed for dual-band 802.11a/g applications covering world-bands of 2.4GHz to 2.5GHz and 4.9GHz to 5.875GHz. The ICs include all circuitry required to implement the RF transceiver function, providing a fully integrated receive path, transmit path, VCO, frequency synthesizer, and baseband/control interface. Only the PA, RF switches, RF bandpass filters (BPF), RF baluns, and a small number of passive components are needed to form the complete RF front-end solution.

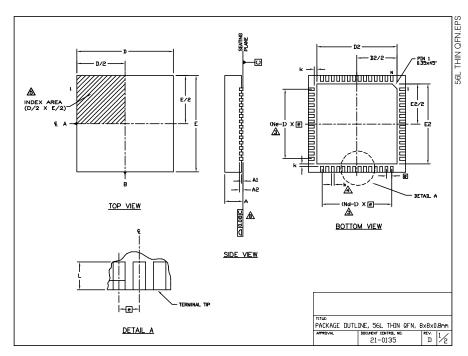

Each IC completely eliminates the need for external SAW filters by implementing on-chip monolithic filters for both the receiver and transmitter. The baseband filtering and the Rx/Tx signal paths are optimized to meet the 802.11a/g IEEE standards and cover the full range of the required data rates (6, 9, 12, 18, 24, 36, 48, and 54Mbps for OFDM; 1, 2, 5.5, and 11Mbps for CCK/DSSS), at receiver sensitivity levels up to 10dB better than 802.11a/g standards. The MAX2828/MAX2829 transceivers are available in the small 56-pin, exposed paddle thin QFN package.

### \_Applications

Single-/Dual-Band 802.11a/b/g Radios 4.9GHz Public Safety Radios 2.4GHz/5GHz MIMO and Smart Antenna Systems

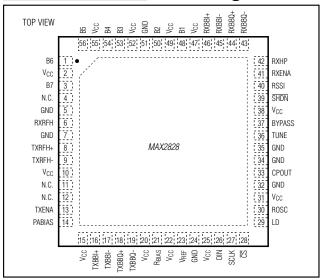

#### **Pin Configurations**

#### Features

- World-Band Operation MAX2828: 4.9GHz to 5.875GHz (802.11a) MAX2829: 2.4GHz to 2.5GHz and 4.9GHz to 5.875GHz (802.11a/b/g)

- ◆ Best-In-Class Transceiver Performance

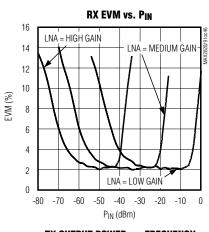

-75dBm Rx Sensitivity at 54Mbps (802.11g)

-46dB (802.11g)/-51dB (802.11a) Tx Sideband Suppression

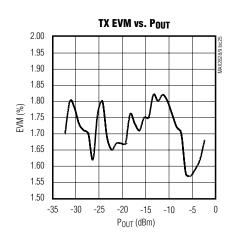

- 1.5% (802.11g) and 2% (802.11a) Tx EVM -100dBc/Hz (802.11g)/-95dBc/Hz (802.11a) LO Phase Noise

Programmable Baseband Lowpass Filters Integrated PLL with 3-Wire Serial Interface 93dB (802.11g)/97dB (802.11a) Receiver Gain-Control Range

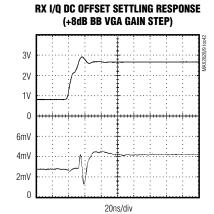

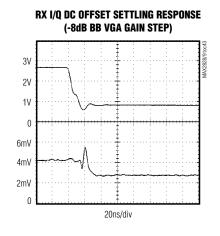

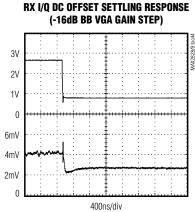

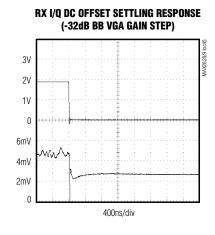

200ns Rx I/Q DC Settling

60dB Dynamic Range Rx RSSI

30dB Tx Power-Control Range

Tx/Rx I/Q Error Detection

I/Q Analog Baseband Interface for Tx and Rx

Digital Mode Selection (Tx. Rx. Standby, a

Digital Mode Selection (Tx, Rx, Standby, and Power Down)

**Supports Both Serial and Parallel Gain Control**

- MIMO and Smart Antenna Compatibility Coherent LO Phase Among Multiple Transceivers

- ♦ Support 40MHz Channel Bandwidth (Turbo Mode)

- ♦ Single +2.7V to +3.6V Supply

- ♦ 1µA Low-Power Shutdown Mode

- ♦ Small 56-Pin TQFN Package (8mm x 8mm)

### **Ordering Information**

| PART        | TEMP RANGE     | PIN-PACKAGE           |

|-------------|----------------|-----------------------|

| MAX2828 ETN | -40°C to +85°C | 56 TQFN-EP* (T5688-2) |

| MAX2829 ETN | -40°C to +85°C | 56 TQFN-EP* (T5688-2) |

<sup>\*</sup>EP = Exposed paddle.

Pin Configurations continued at end of data sheet.

#### **ABSOLUTE MAXIMUM RATINGS**

| VCC, TXRFH_, TXRFL_ to GND                     | 0.3V to +4.2V     |

|------------------------------------------------|-------------------|

| RXRFH, RXRFL, TXBBI_, TXBBQ_, ROSC             | , RXBBI_, RXBBQ_, |

| RSSI, PABIAS, V <sub>REF</sub> , CPOUT, RXENA, | TXENA, SHDN, CS,  |

| SCLK, DIN, B_, RXHP, LD, RBIAS,                |                   |

| BYPASS to GND                                  |                   |

| RXBBI_, RXBBQ_, RSSI, PABIAS, VREF, C          | POUT,             |

| LD Short-Circuit Duration                      | 10s               |

| RF Input Power                                        | +10dBm      |

|-------------------------------------------------------|-------------|

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |             |

| 56-Pin Thin QFN (derate 31.3mW/°C above +70°C)        | 2500mW      |

| Operating Temperature Range40°                        | °C to +85°C |

| Junction Temperature                                  | +150°C      |

| Storage Temperature Range65°C                         | C to +160°C |

| Lead Temperature (soldering, 10s)                     | +300°C      |

|                                                       |             |

CAUTION! ESD SENSITIVE DEVICE

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS

(MAX2828/MAX2829 evaluation kits:  $V_{CC}=2.7V$  to 3.6V, Rx/Tx set to maximum gain,  $R_{BIAS}=11k\Omega$ , no signal at RF inputs, all RF inputs and outputs terminated into  $50\Omega$ , receiver baseband outputs are open, no signal applied to Tx I/Q BB inputs in Tx mode,  $f_{REFOSC}=40MHz$ , registers set to default settings and corresponding test mode,  $T_{A}=-40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $V_{CC}=+2.7V$  and  $T_{A}=+25^{\circ}C$ , unless otherwise noted.) (Note 1)

| PARAMETERS                           |                        | CON                                    | IDITIONS    | 3                                             | MIN  | TYP | MAX  | UNITS |

|--------------------------------------|------------------------|----------------------------------------|-------------|-----------------------------------------------|------|-----|------|-------|

| Supply Voltage                       |                        |                                        |             |                                               | 2.7  |     | 3.6  | V     |

|                                      | Shutdown               | mode, reference                        | e oscillate | or not applied, V <sub>IL</sub> = 0           |      | 1   | 100  | μΑ    |

|                                      |                        | 802.11g MAX                            | ′2820       | $T_A = +25$ °C                                |      | 37  | 47   |       |

|                                      | Standby                | 002.11g WAX                            | .2029       | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |      |     | 51   |       |

|                                      | mode                   | 802.11a                                |             | $T_A = +25^{\circ}C$                          |      | 44  | 51   |       |

|                                      |                        | MAX2828/MA                             | X2829       | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |      |     | 55   |       |

|                                      |                        | 000 11a MAV                            | ′0000       | $T_A = +25^{\circ}C$                          |      | 118 | 151  |       |

|                                      | Du manda               | 802.11g MAX                            | .2029       | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |      |     | 158  |       |

|                                      | Rx mode                | 802.11a                                |             | T <sub>A</sub> = +25°C                        |      | 135 | 180  | Ī     |

|                                      |                        | MAX2828/MA                             | X2829       | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |      |     | 188  |       |

|                                      |                        | 000 11 110                             | (0000       | T <sub>A</sub> = +25°C                        |      | 124 | 164  |       |

|                                      |                        | 802.11g MAX                            |             | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |      |     | 175  |       |

|                                      | Tx mode                | 802.11a<br>MAX2828/MA                  |             | T <sub>A</sub> = +25°C                        |      | 142 | 184  | -     |

|                                      |                        |                                        | X2829       | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |      |     | 197  |       |

| Supply Current                       | Standby                | mode<br>(MIMO) 802.11a                 |             | T <sub>A</sub> = +25°C                        |      | 65  |      | mA    |

|                                      |                        |                                        |             | T <sub>A</sub> = +25°C                        |      | 70  |      |       |

|                                      | Rx mode                | 802.11g MAX2829 T <sub>A</sub> = +25°C |             |                                               | 136  |     | 1    |       |

|                                      | (MIMO)<br>(Note 2)     | 802.11a<br>MAX2828/MA                  | X2829       | T <sub>A</sub> = +25°C                        |      | 154 |      |       |

|                                      | Tx mode                | 802.11g MAX                            | (2829       | T <sub>A</sub> = +25°C                        |      | 139 |      |       |

|                                      | (MIMO)<br>(Note 2)     | 802.11a<br>MAX2828/MA                  | X2829       | T <sub>A</sub> = +25°C                        |      | 157 |      |       |

|                                      | Tx calibrati           | on mode.                               | 802.110     | MAX2829                                       |      | 129 |      | 1     |

|                                      | $T_A = +25^{\circ}$    |                                        | 802.11a     | a MAX2828/MAX2829                             | 147  |     |      | Ī     |

|                                      | RX calibrat            | ion mode.                              | 802.110     | g MAX2829                                     |      | 188 |      |       |

|                                      | $T_A = +25^\circ$      | ,                                      |             | a MAX2828/MAX2829                             |      | 210 |      | 1     |

| Rx I/Q Output Common-Mode<br>Voltage | T <sub>A</sub> = +25°0 | C                                      | 1           |                                               | 0.80 | 0.9 | 1.05 | V     |

#### DC ELECTRICAL CHARACTERISTICS (continued)

(MAX2828/MAX2829 evaluation kits:  $V_{CC}=2.7V$  to 3.6V, Rx/Tx set to maximum gain,  $R_{BIAS}=11k\Omega$ , no signal at RF inputs, all RF inputs and outputs terminated into  $50\Omega$ , receiver baseband outputs are open, no signal applied to Tx I/Q BB inputs in Tx mode,  $f_{REFOSC}=40MHz$ , registers set to default settings and corresponding test mode,  $T_{A}=-40$ °C to +85°C, unless otherwise noted. Typical values are at  $V_{CC}=+2.7V$  and  $T_{A}=+25$ °C, unless otherwise noted.) (Note 1)

| PARAMETERS                                                | CONDITIONS                                         | MIN                   | TYP | MAX | UNITS |

|-----------------------------------------------------------|----------------------------------------------------|-----------------------|-----|-----|-------|

| Rx I/Q Output Common-Mode                                 | $T_A = -40$ °C (relative to +25°C)                 |                       | -25 |     | m\/   |

| Voltage Variation                                         | $T_A = +85^{\circ}C$ (relative to $+25^{\circ}C$ ) |                       | 20  |     | mV    |

| Tx Baseband Input Common-<br>Mode Voltage Operating Range |                                                    | 0.9                   |     | 1.3 | V     |

| Tx Baseband Input Bias Current                            |                                                    |                       |     | 13  | μΑ    |

| Reference Voltage Output                                  | -1mA < I <sub>OUT</sub> < +1mA                     |                       | 1.2 |     | V     |

| Digital Input-Voltage High, VIH                           |                                                    | V <sub>CC</sub> - 0.4 |     |     | V     |

| Digital Input-Voltage Low, VIL                            |                                                    |                       |     | 0.4 | V     |

| Digital Input-Current High, I <sub>IH</sub>               |                                                    | -1                    |     | +1  | μΑ    |

| Digital Input-Current Low, I <sub>IL</sub>                |                                                    | -1                    |     | +1  | μΑ    |

| LD Output-Voltage High, V <sub>OH</sub>                   | Sourcing 100μA                                     | V <sub>CC</sub> - 0.4 |     |     | V     |

| LD Output-Voltage Low, VoL                                | Sinking 100μA                                      |                       |     | 0.4 | V     |

### AC ELECTRICAL CHARACTERISTICS—802.11g Rx Mode (MAX2829)

| PARAMETER                   |                                                                         | CONDITIONS                                                                 | MIN   | TYP   | MAX   | UNITS |

|-----------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------|-------|-------|-------|-------|

| RECEIVER SECTION: LNA RF II | NPUT TO BASEBAND                                                        | I/Q OUTPUTS                                                                |       |       |       |       |

| RF Input Frequency Range    |                                                                         |                                                                            | 2.412 |       | 2.500 | GHz   |

|                             |                                                                         | LNA high-gain mode (B7:B6 = 11)                                            |       | -22   |       |       |

| RF Input Return Loss        | With $50\Omega$ external match                                          | LNA medium-gain mode<br>(B7:B6 = 10)                                       |       | -24   |       | dB    |

|                             |                                                                         | LNA high-gain mode (B7:B6 = 11)                                            | -12   |       |       |       |

| Total Valtage Coin          | Maximum gain,                                                           | T <sub>A</sub> = +25°C                                                     | 87    | 94    |       |       |

|                             | B7:B1 = 1111111                                                         | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C \text{ (Note 1)}$             | 85    |       |       | dB    |

| Total Voltage Gain          | Minimum gain,<br>B7:B1 = 0000000                                        | T <sub>A</sub> = +25°C                                                     |       | 1     | 5.5   |       |

| DE Onio Otomo               | 0 0                                                                     | From high-gain mode (B7:B6 = 11) to medium-gain mode (B7:B6 = 10) (Note 3) |       | -15.5 |       | dB    |

| RF Gain Steps               | From high-gain mode (B7:B6 = 11) to low-gain mode (B7:B6 = 0X) (Note 3) |                                                                            |       | -30.5 |       | uв    |

| Gain Variation Over RF Band | $f_{RF} = 2.412GHz \text{ to } 2.$                                      | 5GHz                                                                       |       |       | 3     | dB    |

| Baseband Gain Range         |                                                                         | ,                                                                          |       | 62    |       | dB    |

### AC ELECTRICAL CHARACTERISTICS—802.11g Rx Mode (MAX2829) (continued)

(MAX2829 evaluation kit:  $V_{CC}$  = +2.7V,  $f_{IN}$  = 2.437GHz; receiver baseband I/Q outputs at 112mV<sub>RMS</sub> (-19dBV),  $f_{REFOSC}$  = 40MHz,  $\overline{SHDN}$  = RXENA =  $\overline{CS}$  = high, RXHP = TXENA = SCLK = DIN = low,  $R_{BIAS}$  = 11k $\Omega$ , registers set to default settings and corresponding test mode,  $T_A$  = +25°C, unless otherwise noted. Unmodulated single-tone RF input signal is used, unless otherwise indicated.) (Tables 1, 2, 3)

| PARAMETER                                       |                                                                     | CONDITIONS                                                                                     | MIN TYP | MAX                                                              | UNITS            |

|-------------------------------------------------|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------|---------|------------------------------------------------------------------|------------------|

|                                                 | Voltage gain ≥ 65dB,                                                | with B7:B6 = 11                                                                                | 3.5     |                                                                  |                  |

| DOD N : 5'                                      | Voltage gain = 50dB,                                                | with B7:B6 = 11                                                                                | 4       |                                                                  | j                |

| DSB Noise Figure                                | Voltage gain = 45dB,                                                | with B7:B6 = 10                                                                                | 16      |                                                                  | dB               |

|                                                 | Voltage gain = 15dB,                                                | with B7:B6 = 0X                                                                                | 36      | 3.5<br>4                                                         |                  |

| Output P-1 <sub>dB</sub>                        | Voltage gain = 90dB,                                                | with B7:B6 = 11                                                                                | 3.2     |                                                                  | V <sub>P-P</sub> |

|                                                 | -35dBm jammers at                                                   | Voltage gain = 60dB,<br>with B7:B6 = 11                                                        | -10     | 1                                                                |                  |

| Out-of-Band Input IP3                           | 40MHz and 78MHz offset; based on IM3                                | Voltage gain = 45dB,<br>with B7:B6 = 10                                                        | -2      |                                                                  | dBm              |

|                                                 | at 2MHz                                                             | Voltage gain = 40dB,<br>with B7:B6 = 0X                                                        | 21      |                                                                  |                  |

|                                                 | Voltage gain = 40dB,                                                | with B7:B6 = 11                                                                                | -29     | 1                                                                |                  |

| In-Band Input P-1 <sub>dB</sub>                 | Voltage gain = 25dB, with B7:B6 = 10                                |                                                                                                | -14     | -                                                                | dBm              |

|                                                 | Voltage gain = 5dB, v                                               | vith B7:B6 = 0X                                                                                | 2       | 3.5 4 16 36 3.2 -10 -2 21 -29 -14 2 -17 -5 14 ±0.5 ±0.1 -4 ±2 ±1 |                  |

| In-Band Input IP3                               | Tones at 7MHz and                                                   | Voltage gain = 40dB,<br>with B7:B6 = 11                                                        | -17     |                                                                  |                  |

|                                                 | 8MHz, IM3 at 6MHz<br>and 9MHz, P <sub>IN</sub> =<br>-40dBm per tone | Voltage gain = 25dB,<br>with B7:B6 = 10                                                        | -5      |                                                                  | dBm              |

|                                                 |                                                                     | Voltage gain = 5dB,<br>with B7:B6 = 0X                                                         | 14      |                                                                  |                  |

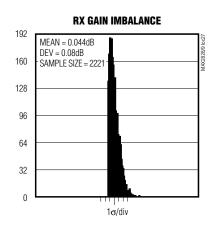

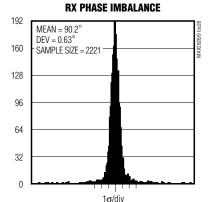

| I/Q Phase Error                                 | B7:B1 = 1101110, 1σ                                                 | variation                                                                                      | ±0.5    | 5                                                                | degrees          |

| I/Q Gain Imbalance                              | B7:B1 = 1101110, 1σ                                                 | variation                                                                                      | ±0.     | 1                                                                | dB               |

| Tx-to-Rx Conversion Gain for Rx I/Q Calibration | B7:B1 = 0010101 (No                                                 | te 4)                                                                                          | -4      |                                                                  | dB               |

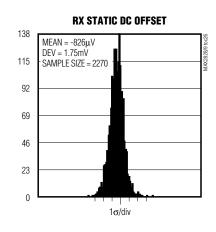

| I/Q Static DC Offset                            | RXHP = 1, B7:B1 = 1                                                 | 101110, 1σ variation                                                                           | ±2      |                                                                  | mV               |

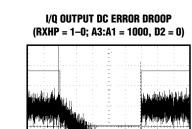

| I/Q DC Droop                                    | After switching RXHP Control/RSSI Register                          | to 0, D2 = 0 (see the RX Definition section)                                                   | ±1      |                                                                  | mV/ms            |

| RF Gain-Change Settling Time                    | o o                                                                 | h gain to medium gain, high gain to<br>gain to low gain; gain settling to<br>state             | 0.4     |                                                                  | μs               |

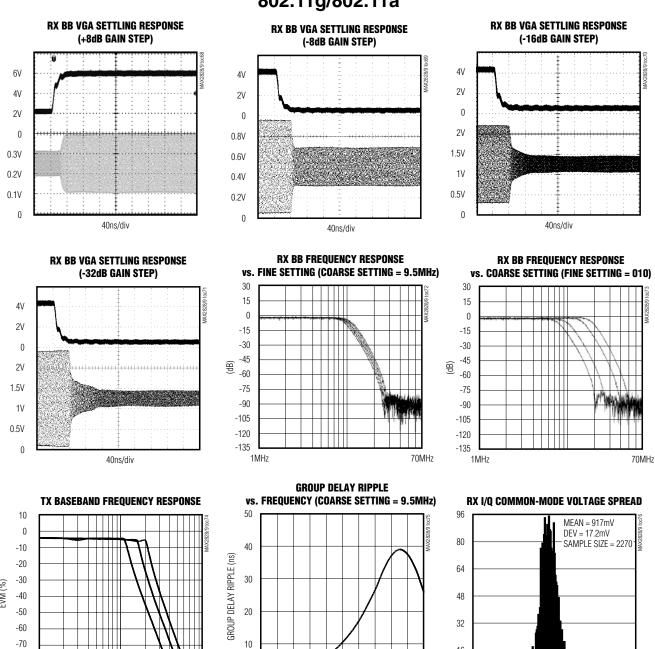

| Baseband VGA Settling Time                      | •                                                                   | ain change from B5:B1 = 10111 to B5:B1 = 00111;<br>ain settling to within ±2dB of steady state |         |                                                                  | μs               |

| Dy I/O Output Load Impodence                    | Minimum differential r                                              | esistance                                                                                      | 10      |                                                                  | kΩ               |

| Rx I/Q Output Load Impedance                    | Maximum differential                                                | capacitance                                                                                    | 8       |                                                                  | рF               |

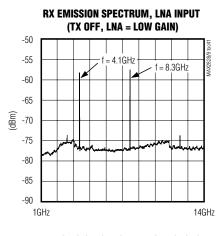

| Spurious Signal Emissions at LNA Input          | RF = 1GHz to 26.5GH                                                 | lz                                                                                             | -67     |                                                                  | dBm              |

### AC ELECTRICAL CHARACTERISTICS—802.11g Rx Mode (MAX2829) (continued)

(MAX2829 evaluation kit:  $V_{CC}$  = +2.7V,  $f_{IN}$  = 2.437GHz; receiver baseband I/Q outputs at 112mV<sub>RMS</sub> (-19dBV),  $f_{REFOSC}$  = 40MHz,  $\overline{SHDN}$  = RXENA =  $\overline{CS}$  = high, RXHP = TXENA = SCLK = DIN = low,  $f_{RBAS}$  = 11k $f_{RBAS}$ , registers set to default settings and corresponding test mode,  $f_{RBAS}$  = +25°C, unless otherwise noted. Unmodulated single-tone RF input signal is used, unless otherwise indicated.) (Tables 1, 2, 3)

| PARAMETER                                |                                                                                           | CONDITIONS                                                                                | MIN  | TYP | MAX   | UNITS   |  |

|------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------|-----|-------|---------|--|

| RECEIVER BASEBAND FILTER                 | S                                                                                         |                                                                                           |      |     | ,     |         |  |

|                                          |                                                                                           | Narrowband mode                                                                           | 7.5  |     |       |         |  |

| Baseband -3dB Corner                     | (See the <i>Lowpass</i>                                                                   | Nominal mode                                                                              |      | 9.5 |       | MHz     |  |

| Frequency                                | Filter Register section)                                                                  | Turbo mode 1                                                                              |      | 14  |       | IVIITIZ |  |

|                                          | ,                                                                                         | Turbo mode 2                                                                              |      | 18  |       |         |  |

| Decelered Filter Deiterking              | fBASEBAND = 15MHz                                                                         |                                                                                           |      | 20  |       |         |  |

| Baseband Filter Rejection (Nominal Mode) | fBASEBAND = 20MHz                                                                         |                                                                                           |      | 39  |       | dB      |  |

| (Normal Wede)                            | fBASEBAND > 40MHz                                                                         | fBASEBAND > 40MHz                                                                         |      |     |       |         |  |

| RSSI                                     |                                                                                           |                                                                                           |      |     |       |         |  |

| RSSI Minimum Output Voltage              | RXHP = 1, low range (D11 = 0, see the <i>Rx Control/RSSI Register Definition</i> section) |                                                                                           |      | 0.5 |       | V       |  |

|                                          | RXHP = 1, high range<br>Register Definition se                                            |                                                                                           | 0.52 |     |       |         |  |

| DCCI Mavirouse Output Valtage            | RXHP = 1, low range (D11 = 0, see the <i>Rx Control/RSSI Register Definition</i> section) |                                                                                           | 2    |     |       | V       |  |

| RSSI Maximum Output Voltage              | RXHP = 1, high range<br>Register Definition se                                            | e (D11 = 1, see the <i>Rx Control/RSSI</i> ction)                                         |      | 2.5 |       | V       |  |

| DCCI Clana                               |                                                                                           | RXHP = 1, low range (D11 = 0, see the <i>Rx Control/RSSI Register Definition</i> section) |      |     |       | m\//dD  |  |

| RSSI Slope                               | RXHP = 1, high range<br>Register Definition se                                            |                                                                                           | 30   |     | mV/dB |         |  |

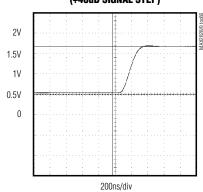

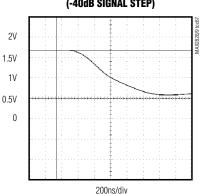

| RSSI Output Settling Time                | To within 3dB of stea                                                                     | dy +40dB signal step                                                                      |      | 0.2 |       |         |  |

| nssi Output settiing Time                | state                                                                                     | -40dB signal step                                                                         |      | 0.7 | ·     | μs      |  |

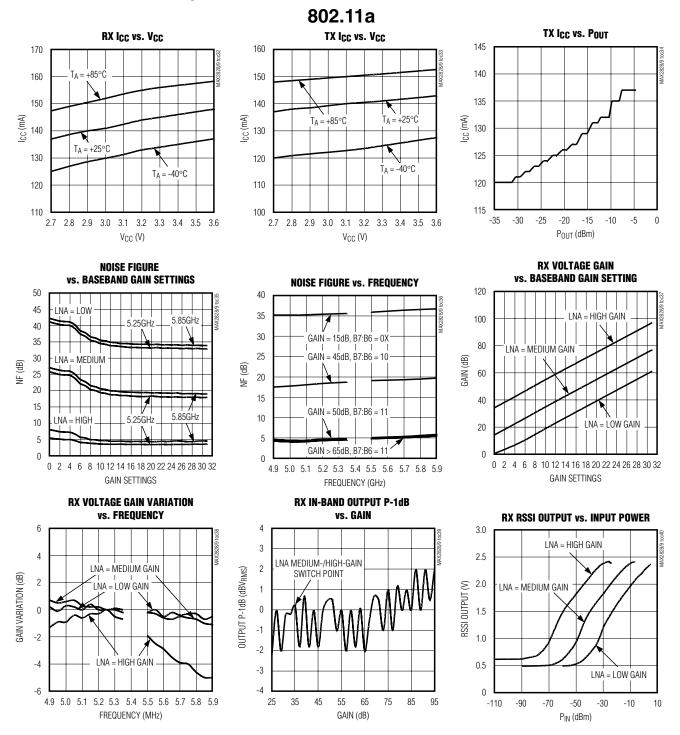

### AC ELECTRICAL CHARACTERISTICS—802.11a Rx Mode (MAX2828/MAX2829)

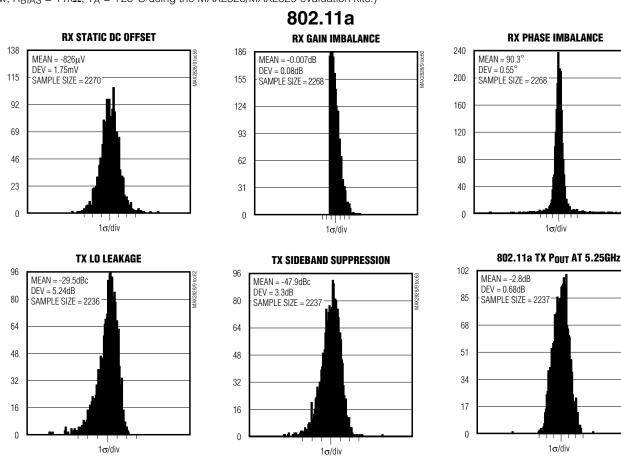

(MAX2828/MAX2829 evaluation kits:  $V_{CC} = +2.7V$ ,  $f_{IN} = 5.25$ GHz; receiver baseband I/Q outputs at 112mV<sub>RMS</sub> (-19dBV),  $f_{REFOSC} = 40$ MHz,  $\overline{SHDN} = RXENA = \overline{CS} = high$ , RXHP = TXENA = SCLK = DIN = low,  $f_{RBAS} = 11$ k $f_{RMS}$ , registers set to default settings and corresponding test mode,  $f_{RMS} = +25$ °C, unless otherwise noted. Unmodulated single-tone RF input signal is used, unless otherwise indicated.) (Tables 1, 2, 3)

| PARAMETER                                                                             |                                             | CONDITIONS                                                              | MIN                                                                                                                          | TYP                                                                                                                                    | MAX   | UNITS            |  |

|---------------------------------------------------------------------------------------|---------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------|------------------|--|

| RECEIVER SECTION: LNA RI                                                              | INPUT TO BASEBAND I                         | Q OUTPUTS                                                               |                                                                                                                              |                                                                                                                                        |       |                  |  |

| DE1 - E D                                                                             | 802.11a low-band mo                         | ode                                                                     | 4.900                                                                                                                        |                                                                                                                                        | 5.350 | 011              |  |

| RF Input Frequency Range                                                              | 802.11a high-band m                         | ode                                                                     | 5.470                                                                                                                        |                                                                                                                                        | 5.875 | GHz              |  |

|                                                                                       |                                             | LNA high-gain mode (B7:B6 = 11)                                         |                                                                                                                              | -15                                                                                                                                    |       |                  |  |

| RF Input Return Loss                                                                  | With $50\Omega$ external match              | LNA medium-gain mode<br>(B7:B6 = 10)                                    |                                                                                                                              | -11                                                                                                                                    |       | dB               |  |

|                                                                                       |                                             | LNA low-gain mode (B7:B6 = 0X)                                          |                                                                                                                              | -7                                                                                                                                     |       |                  |  |

|                                                                                       | Maximum gain,                               | T <sub>A</sub> = +25°C                                                  | 91                                                                                                                           | 0 5.350<br>0 5.875<br>-15<br>-11<br>-7<br>97                                                                                           |       |                  |  |

| Tatal Valta and Oak                                                                   | B7:B1 = 1111111                             | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C (Note 1)}$            | 88                                                                                                                           |                                                                                                                                        |       | -ID              |  |

| Total Voltage Gain                                                                    | Minimum gain,<br>B7:B1 = 0000000            | T <sub>A</sub> = +25°C                                                  |                                                                                                                              | 0                                                                                                                                      | 3     | dB               |  |

| PF 0 : 0:                                                                             | From high-gain mode<br>mode (B7:B6 = 10) (N | (B7:B6 = 11) to medium-gain lote 3)                                     |                                                                                                                              | -19                                                                                                                                    |       | 5                |  |

| 1F Gain Steps                                                                         | 0 0                                         | From high-gain mode (B7:B6 = 11) to low-gain mode (B7:B6 = 0X) (Note 3) |                                                                                                                              | -34.5                                                                                                                                  |       | dB               |  |

| Gain Variation Relative to 5.25GHz                                                    | f <sub>RF</sub> = 4.9GHz                    |                                                                         |                                                                                                                              | -0.3                                                                                                                                   |       |                  |  |

|                                                                                       | $f_{RF} = 5.35GHz$                          | $f_{RF} = 5.35GHz$                                                      |                                                                                                                              |                                                                                                                                        |       | dB               |  |

| 3.23GHZ                                                                               | $f_{RF} = 5.875GHz$                         |                                                                         | 5.470 5.87 = 11) -15  -11  0X) -7  91 97  88  0 3  -19  3 -34.5  -0.3  0.4  -4  62  4.5  4.8  15  36  3.2  -15  0.5  20  -32 |                                                                                                                                        |       |                  |  |

| Baseband Gain Range                                                                   | From maximum basek minimum baseband g       | pand gain (B5:B1 = 11111) to gain (B5:B1 = 00000)                       |                                                                                                                              | 62                                                                                                                                     |       | dB               |  |

|                                                                                       | Voltage gain ≥ 65dB,                        | with B7:B6 = 11                                                         |                                                                                                                              | 4.5                                                                                                                                    |       |                  |  |

| DCD Naina Figura                                                                      | Voltage gain = 50dB,                        | with B7:B6 = 11                                                         | 4.8                                                                                                                          |                                                                                                                                        |       | -10              |  |

| Dob Noise rigure                                                                      | Voltage gain = 45dB,                        | with B7:B6 = 10                                                         | 15                                                                                                                           |                                                                                                                                        |       | dB               |  |

|                                                                                       | Voltage gain = 15dB,                        | with B7:B6 = 0X                                                         |                                                                                                                              | 0 5.350<br>0 5.875<br>-15<br>-11<br>-7<br>97<br>0 3<br>-19<br>-34.5<br>-0.3<br>0.4<br>-4<br>62<br>4.5<br>4.8<br>15<br>36<br>3.2<br>-15 |       |                  |  |

| Output P-1 <sub>dB</sub>                                                              | Voltage gain = 90dB,                        | with B7:B6 = 11                                                         |                                                                                                                              | 3.2                                                                                                                                    |       | V <sub>P-P</sub> |  |

|                                                                                       | -35dBm jammers at                           | Voltage gain = 60dB,<br>with B7:B6 = 11                                 |                                                                                                                              | -15                                                                                                                                    |       |                  |  |

| Out-of-Band Input IP3                                                                 | 40MHz and 78MHz offset; based on IM3        | Voltage gain = 45dB,<br>with B7:B6 = 10                                 |                                                                                                                              | 0.5                                                                                                                                    | (     | dBm              |  |

|                                                                                       | at 2MHz                                     | Voltage gain = 40dB,<br>with B7:B6 = 0X                                 |                                                                                                                              | 20                                                                                                                                     |       |                  |  |

|                                                                                       | Voltage gain = 35dB,                        | with B7:B6 = 11                                                         |                                                                                                                              | -32                                                                                                                                    |       |                  |  |

| In-Band Input P-1 <sub>dB</sub>                                                       | Voltage gain = 20dB,                        | Voltage gain = 20dB, with B7:B6 = 10                                    |                                                                                                                              |                                                                                                                                        |       | dBm              |  |

| Baseband Gain Range  DSB Noise Figure  Dutput P-1 <sub>dB</sub> Dut-of-Band Input IP3 | Voltage gain = 5dB, v                       | Voltage gain = 5dB, with B7:B6 = 0X                                     |                                                                                                                              |                                                                                                                                        | _     |                  |  |

### AC ELECTRICAL CHARACTERISTICS—802.11a Rx Mode (MAX2828/MAX2829) (continued)

(MAX2828/MAX2829 evaluation kits:  $V_{CC}$  = +2.7V,  $f_{IN}$  = 5.25GHz; receiver baseband I/Q outputs at 112mV<sub>RMS</sub> (-19dBV),  $f_{REFOSC}$  = 40MHz,  $\overline{SHDN}$  = RXENA =  $\overline{CS}$  = high, RXHP = TXENA = SCLK = DIN = low,  $R_{BIAS}$  = 11k $\Omega$ , registers set to default settings and corresponding test mode,  $T_A$  = +25°C, unless otherwise noted. Unmodulated single-tone RF input signal is used, unless otherwise indicated.) (Tables 1, 2, 3)

| PARAMETER                                       |                                                  | CONDITIONS                                                                                                                                 | MIN | TYP                                                                           | MAX | UNITS   |  |

|-------------------------------------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------------------------------------------------------------------|-----|---------|--|

|                                                 | Tones at 7MHz and                                | Voltage gain = 35dB,<br>with B7:B6 = 11                                                                                                    |     | -24                                                                           |     |         |  |

| In-Band Input IP3                               | 8MHz, IM3 at 6MHz<br>and 9MHz, P <sub>IN</sub> = | Voltage gain = 20dB,<br>with B7:B6 = 10                                                                                                    |     | -5                                                                            |     | dBm     |  |

|                                                 | -40dBm per tone                                  | Voltage gain = 5dB,<br>with B7:B6 = 0X                                                                                                     |     | 13                                                                            |     |         |  |

| I/Q Phase Error                                 | B7:B1 = 1101110, $1\sigma$                       | variation                                                                                                                                  |     | ±0.4                                                                          |     | degrees |  |

| I/Q Gain Imbalance                              | B7:B1 = 1101110, $1\sigma$                       | variation                                                                                                                                  |     | ±0.1                                                                          |     | dB      |  |

| Tx-to-Rx Conversion Gain for Rx I/Q Calibration | B7:B1 = 0001111 (No                              | ote 4)                                                                                                                                     |     | 0                                                                             |     | dB      |  |

| I/Q Static DC Offset                            | RXHP = 1, B7:B1 = 1                              | 101110, 1σ variation                                                                                                                       |     | ±2<br>±1                                                                      |     |         |  |

| I/Q DC Droop                                    | <u> </u>                                         | After switching RXHP to 0, D2 = 0 (see the Rx Control/RSSI Register Definition section)                                                    |     |                                                                               |     | mV/ms   |  |

| RF Gain-Change Settling Time                    | low gain, or medium (                            | Gain change from high gain to medium gain, high gain to low gain, or medium gain to low gain; gain settling to within ±2dB of steady state |     |                                                                               |     | μs      |  |

| Baseband VGA Settling Time                      |                                                  | thin ±2dB of steady state  ain change from B5:B1 = 10111 to B5:B1 = 00111;  ain settling to within ±2dB of steady state                    |     |                                                                               |     | μs      |  |

| Dy I/O Output I and Improduce                   | Minimum differential r                           | esistance                                                                                                                                  |     | 10                                                                            |     | kΩ      |  |

| Rx I/Q Output Load Impedance                    | Maximum differential                             | capacitance                                                                                                                                |     | 8                                                                             |     | рF      |  |

| Spurious Signal Emissions at LNA input          | RF = 1GHz to 26.5GH                              | Hz                                                                                                                                         |     | -50                                                                           |     | dBm     |  |

| RECEIVER BASEBAND FILTERS                       |                                                  |                                                                                                                                            |     |                                                                               |     |         |  |

|                                                 | (0 11 /                                          | Narrow-band mode                                                                                                                           |     | 7.5                                                                           |     |         |  |

| Baseband -3dB Corner                            | (See the Lowpass Filter Register                 | Nominal mode                                                                                                                               |     | 9.5                                                                           |     | MHz     |  |

| Frequency                                       | Definition section)                              | Turbo mode 1                                                                                                                               |     | 14                                                                            |     | 1011 12 |  |

|                                                 | ,                                                | Turbo mode 2                                                                                                                               |     | ±0.1  0  ±2  ±1  0.4  0.1  10  8  -50  7.5  9.5                               |     |         |  |

| Baseband Filter Rejection                       | fBASEBAND = 15MHz                                |                                                                                                                                            |     |                                                                               | ]   |         |  |

| (Nominal Mode)                                  | fbaseband = 20MHz                                |                                                                                                                                            |     |                                                                               | dB  |         |  |

| · · · · · · · · · · · · · · · · · · ·           | fBASEBAND > 40MHz                                |                                                                                                                                            |     | -5  13  ±0.4  ±0.1  0  ±2  ±1  0.4  0.1  10  8  -50  7.5  9.5  14  18  20  39 |     |         |  |

#### AC ELECTRICAL CHARACTERISTICS—802.11a Rx Mode (MAX2828/MAX2829) (continued)

(MAX2828/MAX2829) evaluation kits:  $V_{CC} = +2.7V$ ,  $f_{IN} = 5.25GHz$ ; receiver baseband I/Q outputs at  $112mV_{RMS}$  (-19dBV),  $f_{REFOSC} = 40MHz$ ,  $\overline{SHDN} = RXENA = \overline{CS} = high$ , RXHP = TXENA = SCLK = DIN = low,  $R_{BIAS} = 11k\Omega$ , registers set to default settings and corresponding test mode,  $T_A = +25^{\circ}C$ , unless otherwise noted. Unmodulated single-tone RF input signal is used, unless otherwise indicated.) (Tables 1, 2, 3)

| PARAMETER                       | COI                                                  | NDITIONS                                                                                  | MIN | TYP  | MAX | UNITS  |

|---------------------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------|-----|------|-----|--------|

| RSSI                            | •                                                    |                                                                                           |     |      |     |        |

| DCCI Mississure Outrout Valtage |                                                      | RXHP = 1, low range (D11 = 0, see the Rx Control/RSSI Register Definition section)        |     |      |     | V      |

| RSSI Minimum Output Voltage     | RXHP = 1, high range (D1 Register Definition section | 1 = 1, see the Rx Control/RSSI                                                            |     | 0.52 |     | V      |

| DSSI Mavimum Output Valtage     |                                                      | RXHP = 1, low range (D11 = 0, see the <i>Rx Control/RSSI Register Definition</i> section) |     | 2    |     | V      |

| RSSI Maximum Output Voltage     | RXHP = 1, high range (D1 Register Definition section | 1 = 1, see the Rx Control/RSSI                                                            |     | 2.5  |     | V      |

| DCCI Clare                      | RXHP = 1, low range (D1 Register Definition section  | 1 = 0, see the Rx Control/RSSI                                                            |     | 22.5 |     | \//aID |

| RSSI Slope                      |                                                      | RXHP = 1, high range (D11 = 1, see the Rx Control/RSSI Register Definition section)       |     | 30   |     | mV/dB  |

| DCCI Output Cattling Time       | To within 3dB of steady                              | +40dB signal step                                                                         |     | 0.2  |     |        |

| RSSI Output Settling Time       | state state -40dB                                    |                                                                                           |     | 0.7  |     | μs     |

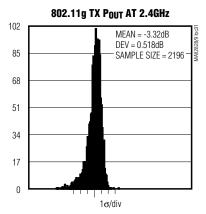

#### AC ELECTRICAL CHARACTERISTICS—802.11g Tx Mode (MAX2829)

$(\text{MAX2829 evaluation kit: } V_{\text{CC}} = +2.7 \text{V, } f_{\text{OUT}} = 2.437 \text{GHz, } f_{\text{REFOSC}} = 40 \text{MHz, } \overline{\text{SHDN}} = \text{TXENA} = \overline{\text{CS}} = \text{high, RXENA} = \text{SCLK} = \text{DIN} = 10 \text{W, } R_{\text{BIAS}} = 11 \text{k}\Omega, 100 \text{mV}_{\text{RMS}} \text{sine and cosine signal (or } 100 \text{mV}_{\text{RMS}}, 54 \text{Mbps IEEE } 802.11 \text{g I/Q signals wherever OFDM is mentioned) applied to baseband I/Q inputs of transmitter, registers set to default settings and corresponding test mode, } T_{\text{A}} = +25 ^{\circ}\text{C}, \text{unless otherwise noted.)} (Table 4)$

| PARAMETER                                              | CONDITIONS                                                |                                                         | MIN   | TYP  | MAX   | UNITS       |  |  |

|--------------------------------------------------------|-----------------------------------------------------------|---------------------------------------------------------|-------|------|-------|-------------|--|--|

| TRANSMIT SECTION: Tx BASEBAND I/Q INPUTS TO RF OUTPUTS |                                                           |                                                         |       |      |       |             |  |  |

| RF Output Frequency Range, fRF                         |                                                           |                                                         | 2.412 |      | 2.500 | GHz         |  |  |

| Output Davier                                          | 54Mbps 802.11g OFDM                                       | 1.5% EVM                                                |       | -2.5 |       | dBm         |  |  |

| Output Power                                           | signal                                                    | signal B6:B1 = 111011                                   |       | -4.5 |       | ubili       |  |  |

| Output Power (CW)                                      | V <sub>IN</sub> = 100mV <sub>RMS</sub> at 1MHz<br>1111111 | N = 100mV <sub>RMS</sub> at 1MHz I/Q CW signal, B6:B1 = |       |      |       | dBm         |  |  |

| Output Power Range                                     | B6:B1 = 111111 to B6:B1                                   | 6:B1 = 111111 to B6:B1 = 000000                         |       |      |       | dB          |  |  |

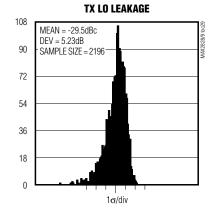

| Carrier Leakage                                        | Without DC offset cancella                                | ation                                                   |       | -27  |       | dBc         |  |  |

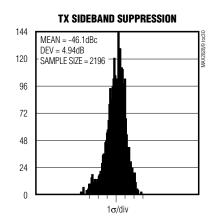

| Unwanted Sideband Suppression                          | Uncalibrated                                              |                                                         |       | -46  |       | dBc         |  |  |

| Tx Output ACP                                          |                                                           | olution bandwidth at 22MHz<br>r (B6:B1 = 111011), OFDM  |       | -69  |       | dBm/<br>MHz |  |  |

| RF Output Return Loss                                  | With external $50\Omega$ match                            |                                                         |       | -14  |       | dB          |  |  |

### AC ELECTRICAL CHARACTERISTICS—802.11g Tx Mode (MAX2829) (continued)

(MAX2829 evaluation kit:  $V_{CC} = +2.7V$ ,  $f_{OUT} = 2.437$ GHz,  $f_{REFOSC} = 40$ MHz,  $\overline{SHDN} = TXENA = \overline{CS} = high$ , RXENA = SCLK = DIN = low,  $R_{BIAS} = 11k\Omega$ ,  $100mV_{RMS}$  sine and cosine signal (or  $100mV_{RMS}$ , 54Mbps IEEE 802.11g I/Q signals wherever OFDM is mentioned) applied to baseband I/Q inputs of transmitter, registers set to default settings and corresponding test mode,  $T_A = +25^{\circ}C$ , unless otherwise noted.) (Table 4)

| PARAMETER                                           |                                                                                       | CON                        | IDITIONS                                                                                                     | MIN     | TYP     | MAX      | UNITS              |

|-----------------------------------------------------|---------------------------------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------|---------|---------|----------|--------------------|

|                                                     |                                                                                       |                            | 2/3 x f <sub>RF</sub>                                                                                        |         | -64     |          |                    |

| RF Spurious Signal Emissions                        | B6:B1 = 111011, OFDM                                                                  |                            | 4/3 x f <sub>RF</sub>                                                                                        |         | -61     |          | dBm/               |

| nr Spurious Signal Emissions                        | signal                                                                                |                            | 5/3 x f <sub>RF</sub>                                                                                        |         | -63     |          | MHz                |

|                                                     |                                                                                       |                            | 8/3 x f <sub>RF</sub>                                                                                        |         | -52     |          |                    |

|                                                     | (See the Lowpass F                                                                    | Filter                     | Nominal mode                                                                                                 |         | 12      |          |                    |

| Baseband -3dB Corner Frequency                      | Register Definition                                                                   |                            | Turbo mode 1                                                                                                 |         | 18      |          | MHz                |

| requency                                            | section)                                                                              |                            | Turbo mode 2                                                                                                 |         | 24      |          |                    |

| Baseband Filter Rejection                           | At 30MHz, in nominal mode (see the <i>Lowpass Filter</i> Register Definition section) |                            |                                                                                                              | 60      |         |          | dB                 |

| Tx Baseband Input Impedance                         | Minimum differential resistance                                                       |                            |                                                                                                              | 60      |         |          | kΩ                 |

| TX baseband input impedance                         | Maximum differentia                                                                   | m differential capacitance |                                                                                                              |         | 0.7     |          | рF                 |

| TRANSMITTER LO LEAKAGE AI CALIBRATION MODE SECTION) |                                                                                       | N USIN                     | IG LO LEAKAGE AND SIDEBA                                                                                     | ND DETE | CTOR (S | EE THE T | x/Rx               |

| Tx BASEBAND I/Q INPUTS TO R                         | RECEIVER OUTPUTS                                                                      | <b>3</b>                   |                                                                                                              |         |         |          | ı                  |

|                                                     | Calibration register,                                                                 |                            | it at 1 x f <sub>TONE</sub> (for LO leakage<br>dBc), f <sub>TONE</sub> = 2MHz,<br>√rms                       |         | -3      |          | dD\/p.io           |

| Lietector Cilitolit                                 | suppre                                                                                |                            | at at 2 x f <sub>TONE</sub> (for sideband<br>ession = -40dBc), f <sub>TONE</sub> =<br>, 100mV <sub>RMS</sub> |         | -13     |          | dBV <sub>RMS</sub> |

| Amplifier Gain Range                                | D12:D11 = 00 to D12:D11 = 11, A3:A0 = 0110                                            |                            |                                                                                                              | 26      |         | dB       |                    |

| Lower -3dB Corner Frequency                         |                                                                                       |                            |                                                                                                              |         | 1       |          | MHz                |

#### AC ELECTRICAL CHARACTERISTICS—802.11a Tx Mode (MAX2828/MAX2829)

(MAX2828/MAX2829) evaluation kits:  $V_{CC} = +2.7V$ ,  $f_{OUT} = 5.25GHz$ ,  $f_{REFOSC} = 40MHz$ ,  $\overline{SHDN} = TXENA = \overline{CS} = high$ , RXENA = SCLK = DIN = low,  $R_{BIAS} = 11k\Omega$ ,  $100mV_{RMS}$  sine and cosine signal (or  $100mV_{RMS}$ , 54Mbps IEEE 802.11a I/Q signals wherever OFDM is mentioned) applied to baseband I/Q inputs of transmitter, registers set to default settings and corresponding test mode,  $T_A = +25^{\circ}C$ , unless otherwise noted.) (Table 4)

| PARAMETER                                           |                                                       | CON                                                                                                       | IDITIONS                                                                                                      | MIN      | TYP     | MAX      | UNITS              |  |

|-----------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|----------|---------|----------|--------------------|--|

| TRANSMIT SECTION: Tx BASEB                          | AND I/Q INPUTS TO F                                   | RF OL                                                                                                     | UTPUTS                                                                                                        | L        |         | <u> </u> |                    |  |

|                                                     | 802.11a low-band mo                                   | ode                                                                                                       |                                                                                                               | 4.900    |         | 5.350    | 01.1               |  |

| RF Output Frequency Range, f <sub>RF</sub>          | 802.11a high-band mode                                |                                                                                                           |                                                                                                               | 5.470    |         | 5.875    | GHz                |  |

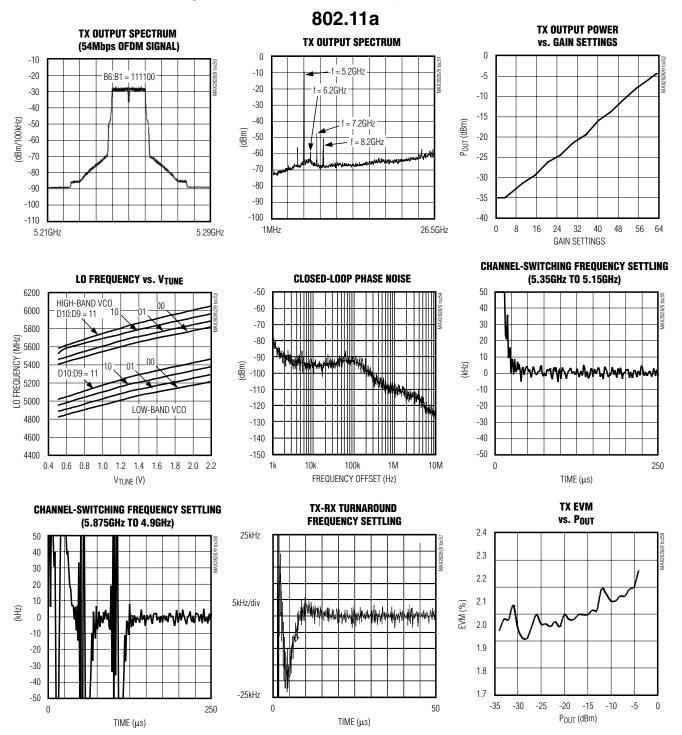

| Output Power                                        | 54Mbps 802.11a OFE                                    | OM                                                                                                        | 2% EVM                                                                                                        |          | -5      |          | dBm                |  |

| Output i owei                                       | signal                                                |                                                                                                           | B6:B1 = 111100                                                                                                |          | -6.5    |          | abiii              |  |

| Output Power (CW)                                   | V <sub>IN</sub> = 100mV <sub>RMS</sub> at 1 1111111   | MHz                                                                                                       | I/Q CW signal, B6:B1 =                                                                                        |          | -4.5    |          | dBm                |  |

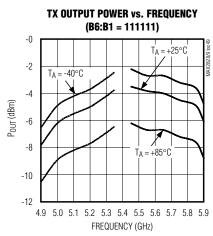

| 0                                                   | $f_{RF} = 4.9GHz$                                     |                                                                                                           |                                                                                                               |          | -6      |          |                    |  |

| Output Power Variation Relative to 5.25GHz          | $f_{RF} = 5.35GHz$                                    |                                                                                                           |                                                                                                               |          | -0.5    |          | dB                 |  |

| to 5.25GHZ                                          | f <sub>RF</sub> = 5.875GHz                            |                                                                                                           |                                                                                                               |          | -1      |          |                    |  |

| Output Power Range                                  | B6:B1 = 111111 to B6                                  | 6:B1                                                                                                      | = 000000                                                                                                      |          | 30      |          | dB                 |  |

| Carrier Leakage                                     | Without DC offset car                                 | ncella                                                                                                    | ition                                                                                                         |          | -27     |          | dBc                |  |

| Unwanted Sideband Suppression                       | Uncalibrated                                          |                                                                                                           |                                                                                                               |          | -51     |          | dBc                |  |

| Tx Output ACP                                       |                                                       | Measured with 1MHz resolution bandwidth at 30MHz offset from channel center (B6:B1 = 111100), OFDM signal |                                                                                                               |          |         | -80      |                    |  |

| RF Output Return Loss                               | With external $50\Omega$ ma                           | atch                                                                                                      |                                                                                                               |          | -16     |          | dB                 |  |

|                                                     |                                                       | 4/5                                                                                                       | x fRF                                                                                                         | -55      |         |          |                    |  |

| DE Caurious Cianal Emissions                        | B6:B1 = 111100,<br>OFDM signal                        | 6/5                                                                                                       | x f <sub>RF</sub>                                                                                             |          | -64     |          | dBm/               |  |

| RF Spurious Signal Emissions                        |                                                       | 7/5                                                                                                       | x fRF                                                                                                         |          | -65     |          | MHz                |  |

|                                                     |                                                       | 8/5                                                                                                       | x f <sub>RF</sub>                                                                                             |          | -49     |          |                    |  |

|                                                     | (see the Lowpass                                      | Nor                                                                                                       | minal mode                                                                                                    |          | 12      |          |                    |  |

| Baseband -3dB Corner<br>Frequency                   | Filter Register                                       | Tur                                                                                                       | bo mode 1                                                                                                     |          | 18      |          | MHz                |  |

| Trequency                                           | Definition section)                                   | Tur                                                                                                       | bo mode 2                                                                                                     |          | 24      |          |                    |  |

| Baseband Filter Rejection                           | At 30MHz, in nominal Register Definition se           |                                                                                                           | le (see the <i>Lowpass Filter</i><br>)                                                                        |          | 60      |          | dB                 |  |

| T. D                                                | Minimum differential r                                | resist                                                                                                    | ance                                                                                                          |          | 60      |          | kΩ                 |  |

| Tx Baseband Input Impedance                         | Maximum differential                                  | сара                                                                                                      | icitance                                                                                                      |          | 0.7     |          | рF                 |  |

| TRANSMITTER LO LEAKAGE AN CALIBRATION MODE SECTION) |                                                       | USIN                                                                                                      | IG LO LEAKAGE AND SIDEBA                                                                                      | ND DETEC | TOR (SE | E THE T  | x/Rx               |  |

| Tx BASEBAND I/Q INPUTS TO R                         | ECEIVER OUTPUTS                                       |                                                                                                           |                                                                                                               |          |         |          |                    |  |

| LO Leakage and Sideband-<br>Detector Output         | Calibration register,<br>D12:D11 = 1, A3:A0<br>= 0110 | leal                                                                                                      | tput at 1 x f <sub>TONE</sub> (for LO<br>kage = -29dBc), f <sub>TONE</sub> =<br>Hz, 100mV <sub>RMS</sub>      | -4.5     |         |          | dBV <sub>RMS</sub> |  |