## 0.9 $\Omega$ , Low-Voltage, Single-Supply Quad SPST **Analog Switches**

### **General Description**

The MAX4751/MAX4752/MAX4753 are low on-resistance. low-voltage, quad, single-pole/single-throw (SPST) analog switches that operate from a single +1.6V to +3.6V supply. These devices have fast switching speeds (ton = 30ns, toff = 25ns), handle rail-to-rail analog signals, and consume less than 1µW of quiescent power. The MAX4753 has break-before-make switching.

When powered from a +3V supply, the MAX4751/ MAX4752/MAX4753 feature low  $0.9\Omega$  (max) on-resistance (R<sub>ON</sub>), with  $0.12\Omega$  (max) R<sub>ON</sub> matching and  $0.1\Omega$ (max) Ron flatness. The digital input is 1.8V CMOS compatible when using a single +3V supply.

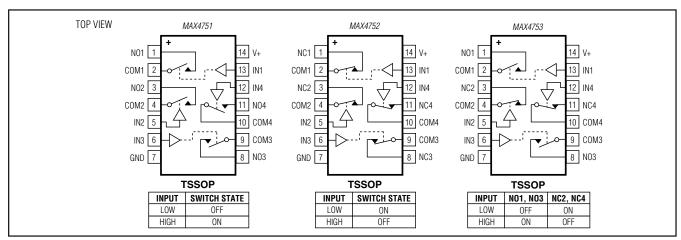

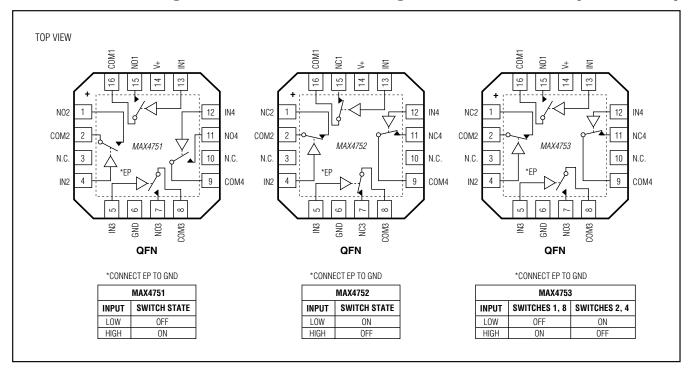

The MAX4751 has four normally open (NO) switches. the MAX4752 has four normally closed (NC) switches. and the MAX4753 has two NO and two NC switches. The MAX4751/MAX4752/MAX4753 are available in 3mm × 3mm, 16-pin QFN and 14-pin TSSOP packages.

### **Applications**

**Power Routing**

Battery-Powered Systems

Audio and Video Signal Routing

Low-Voltage Data-Acquisition Systems

Communications Circuits

**PCMCIA Cards**

Cellular Phones

Modems

Hard Drives

### Features

**♦ Low Ron**

$0.9\Omega$  max (+3V Supply) 2.5 $\Omega$  max (+1.8V Supply)

- ♦ On-Resistance Flatness: 0.1Ω max (+3V)

♦ Ron Matching 0.12Ω max (+3V Supply) 0.25Ω max (+1.8V Supply)

- ◆ +1.6V to +3.6V Single-Supply Operation

- Available in 16-Pin QFN and 3mm × 3mm **Packages**

- ◆ 1.8V CMOS Logic Compatible (+3V Supply)

- High Current-Handling Capacity (100mA Continuous)

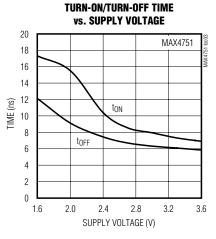

- ♦ Fast Switching: toN = 30ns, toFF = 25ns

### **Ordering Information**

| PART         | TEMP RANGE     | PIN-<br>PACKAGE           | TOP<br>MARK |

|--------------|----------------|---------------------------|-------------|

| MAX4751EUD+T | -40°C to +85°C | 14 TSSOP                  | _           |

| MAX4751EGE+T | -40°C to +85°C | 16 QFN-EP*<br>(3mm × 3mm) | AAC         |

| MAX4752EUD+T | -40°C to +85°C | 14 TSSOP                  | _           |

| MAX4752EGE+T | -40°C to +85°C | 16 QFN-EP*<br>(3mm × 3mm) | AAD         |

| MAX4753EUD+T | -40°C to +85°C | 14 TSSOP                  | _           |

| MAX4753EGE+T | -40°C to +85°C | 16 QFN-EP*<br>(3mm × 3mm) | AAE         |

<sup>\*</sup>EP = Exposed pad.

## Pin Configurations/Functional Diagrams/Truth Tables

Pin Configurations/Functional Diagrams/Truth Tables continued at end of data sheet.

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

T = Tape and reel.

## 0.9 $\Omega$ , Low-Voltage, Single-Supply Quad SPST Analog Switches

#### **ABSOLUTE MAXIMUM RATINGS**

| (Voltages referenced to GND.)                  |             |

|------------------------------------------------|-------------|

| V+, INC                                        | 0.3V to +4V |

| COM_, NO_, NC_ (Note 1)0.3V to (               |             |

| Continuous Current (COM_, NO_, NC_)            | ±100mA      |

| Peak Current COM_, NO_, NC_                    |             |

| (pulsed at 1ms 10% duty cycle)                 | ±200mA      |

| Continuous Power Dissipation ( $T_A = +70$ °C) |             |

| TSSOP (derate 9.1W/°C above +70°C)             | 727mW       |

| QFN (derate 16.9W/°C above +70°C)              | 1349mW      |

| Operating Temperature Range       | 40°C to +85°C  |

|-----------------------------------|----------------|

| Junction Temperature              | +150°C         |

| Storage Temperature Range         | 65°C to +150°C |

| Lead Temperature (soldering, 10s) | +300°C         |

| Soldering Temperature (reflow)    | +260°C         |

|                                   |                |

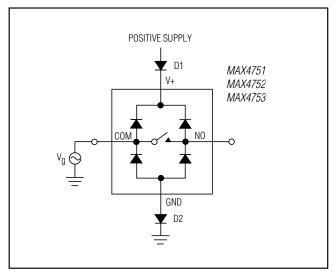

Note 1: Signals on COM\_, NO\_, or NC\_ exceeding V+ or GND are clamped by internal diodes. Limit forward diode current to maximum current rating.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS—Single +3V Supply**

$(V+=+2.7V \text{ to } +3.6V, V_{IH\_}=+1.4V, V_{IL\_}=+0.5V, T_A=T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$  Typical values are at  $V+=+3.0V, T_A=+25^{\circ}C.$ ) (Notes 2, 3)

| PARAMETER                      | SYMBOL                                                         | CONDITIONS                                                                        | TA                                   | MIN  | TYP   | MAX  | UNITS |

|--------------------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------|--------------------------------------|------|-------|------|-------|

| ANALOG SWITCH                  | •                                                              |                                                                                   |                                      |      |       |      |       |

| Analog Signal Range            | V <sub>COM</sub> _,<br>V <sub>NO</sub> _,<br>V <sub>NC</sub> _ |                                                                                   |                                      | 0    |       | V+   | V     |

| O D : (N + 4)                  | -                                                              | V+ = 2.7V,                                                                        | +25°C                                |      | 0.6   | 0.9  |       |

| On-Resistance (Note 4)         | Ron                                                            | I <sub>COM</sub> _ = 100mA,<br>V <sub>NO</sub> _ or V <sub>NC</sub> _ = 1.5V      | T <sub>MIN</sub> to T <sub>MAX</sub> |      |       | 1    | Ω     |

| On-Resistance Match Between    | ADou                                                           | V+ = 2.7V,                                                                        | +25°C                                |      | 0.03  | 0.12 | Ω     |

| Channels (Notes 4, 5)          | ΔRon                                                           | I <sub>COM</sub> = 100mA,<br>V <sub>NO</sub> or V <sub>NC</sub> = 1.5V            | T <sub>MIN</sub> to T <sub>MAX</sub> |      |       | 0.15 |       |

| On-Resistance Flatness         | RFLAT(ON)                                                      | V+ = 2.7V,<br>ICOM_ = 100mA,<br>VNO_ or VNC_ = 1V, 1.5V, 2V                       | +25°C                                |      | 0.04  | 0.1  | Ω     |

| (Note 6)                       |                                                                |                                                                                   | T <sub>MIN</sub> to T <sub>MAX</sub> |      |       | 0.12 |       |

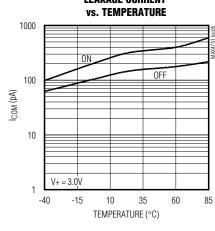

| NO_ or NC_ Off-Leakage Current | INO_(OFF),<br>INC_(OFF)                                        | V+ = 3.6V,                                                                        | +25°C                                | -2.5 | 0.002 | +2.5 | nA    |

| (Note 7)                       |                                                                | V <sub>COM</sub> = 0.3V, 3.6V,<br>V <sub>NO</sub> or V <sub>NC</sub> = 3.6V, 0.3V | T <sub>MIN</sub> to T <sub>MAX</sub> | -5   |       | +5   |       |

| COM_ Off-Leakage Current       | ICOM_(OFF)                                                     | V+ = 3.6V, V <sub>COM</sub> _ = 0.3V,                                             | +25°C                                | -2.5 | 0.002 | +2.5 | nA    |

| (Note 7)                       |                                                                | 3.6V, $V_{NO}$ or $V_{NC}$ = 3.6V, 0.3V                                           | T <sub>MIN</sub> to T <sub>MAX</sub> | -5   |       | +5   |       |

| COM_ On-Leakage Current        |                                                                | V+ = 3.6V, V <sub>COM</sub> _ = 0.3V,                                             | +25°C                                | -2.5 | 0.002 | +2.5 | nA    |

| (Note 7)                       | ICOM_(ON)                                                      | $3.6V$ , $V_{NO}$ or $V_{NC}$ = 0.3V, $3.6V$ , or unconnected                     | T <sub>MIN</sub> to T <sub>MAX</sub> | -5   |       | +5   |       |

# 0.9 $\Omega$ , Low-Voltage, Single-Supply Quad SPST Analog Switches

## **ELECTRICAL CHARACTERISTICS—Single +3V Supply (continued)**

$(V+=+2.7V \text{ to } +3.6V, V_{IH\_}=+1.4V, V_{IL\_}=+0.5V, T_A=T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$  Typical values are at  $V+=+3.0V, T_A=+25^{\circ}C.)$  (Notes 2, 3)

| PARAMETER                     | SYMBOL                | CONDI                                                                           | TIONS                  | TA                                   | MIN  | TYP    | MAX  | UNITS |  |

|-------------------------------|-----------------------|---------------------------------------------------------------------------------|------------------------|--------------------------------------|------|--------|------|-------|--|

| SWITCH DYNAMIC CHARACT        | ERISTICS              |                                                                                 |                        |                                      |      |        |      | •     |  |

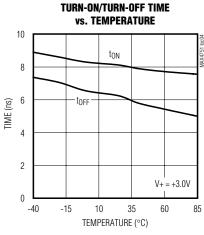

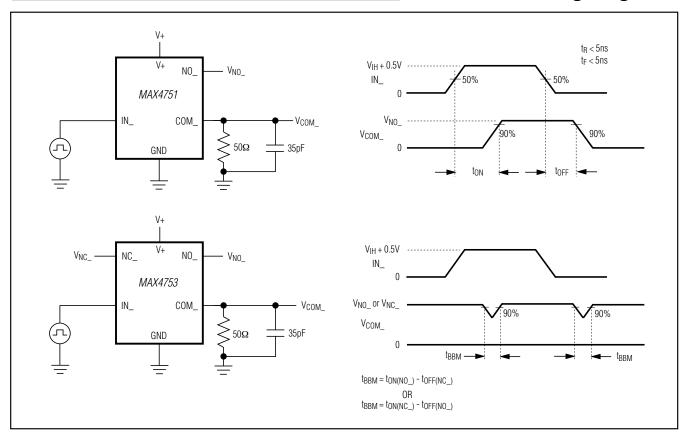

| Turn-On Time                  | ton                   | $V_{NO}$ or $V_{NC}$ = 1.5V,<br>$R_L$ = 50 $\Omega$ , $C_L$ = 35pF,             |                        | +25°C                                |      | 6      | 30   | ns    |  |

| Turr-On Time                  | tON                   | Figure 1                                                                        | _ = 00pi ,             | T <sub>MIN</sub> to T <sub>MAX</sub> |      |        | 30   | 113   |  |

| Turn-Off Time                 | torr                  | $V_{NO}$ or $V_{NC}$<br>$R_L = 50\Omega$ , $C_L$                                |                        | +25°C                                |      | 10     | 25   | ns    |  |

| Turri-Oil Time                | tOFF                  | Figure 1                                                                        | _ = σσρε,              | T <sub>MIN</sub> to T <sub>MAX</sub> |      |        | 25   |       |  |

| Break-Before-Make (Note 8)    | toni                  | $V_{NO}$ and $V_{N}$<br>$R_{L} = 50\Omega$ , $C_{L}$                            |                        | +25°C                                |      | 7      |      | 200   |  |

| (MAX4753 Only)                | tBBM                  | Figure 1                                                                        | _ = δόρε,              | T <sub>MIN</sub> to T <sub>MAX</sub> | 2    |        |      | ns    |  |

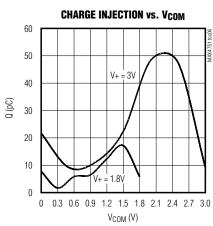

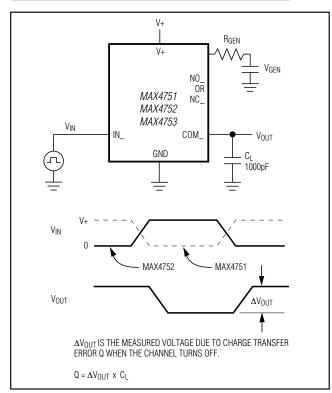

| Charge Injection              | Q                     | V <sub>GEN</sub> = 0, R <sub>GEN</sub> = 0,<br>C <sub>L</sub> = 1.0nF, Figure 2 |                        | +25°C                                |      | 21     |      | рС    |  |

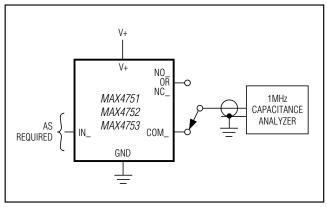

| NO_ or NC_<br>Off-Capacitance | Coff                  | f = 1MHz, Figure 3                                                              |                        | +25°C                                |      | 31     |      | рF    |  |

| COM_ Off-Capacitance          | CCOM_(OFF)            | f = 1MHz, Figure 3                                                              |                        | +25°C                                |      | 30     |      | рF    |  |

| COM_ On-Capacitance           | C <sub>COM</sub> (ON) | f = 1MHz, Fig                                                                   | jure 3                 | +25°C                                |      | 75     |      | рF    |  |

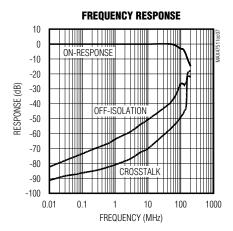

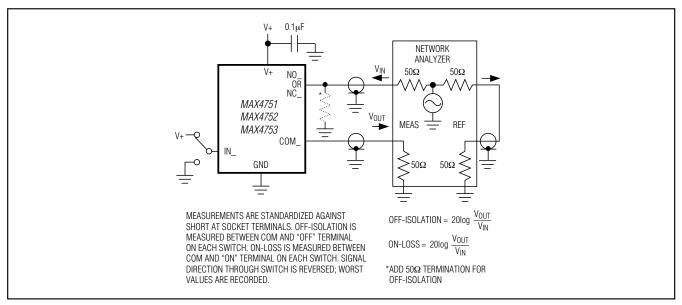

| Off-Isolation (Note 9)        | V <sub>ISO</sub>      |                                                                                 |                        | +25°C                                |      | -51    |      | dB    |  |

| OII-ISOIdtioi (Note 9)        | VISO                  |                                                                                 |                        | +25°C                                | -65  |        |      | QD.   |  |

| Crosstalk                     |                       | $R_L = 50\Omega$ ,<br>$C_L = 5pF$ ,                                             | f = 10MHz              | +25°C                                |      | -70    |      | dB    |  |

| Olossiaik                     |                       | Figure 4                                                                        | f = 1MHz               | +25°C                                |      | -80    |      | QD.   |  |

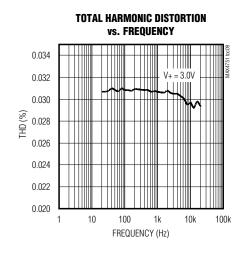

| Total Harmonic Distortion     | THD                   | f = 20Hz to $20kHz$ ,<br>$V_{COM} = 2V_{P-P}$ , $R_L = 32\Omega$                |                        | +25°C                                |      | 0.031  |      | %     |  |

| DIGITAL I/O                   |                       |                                                                                 |                        |                                      |      |        |      |       |  |

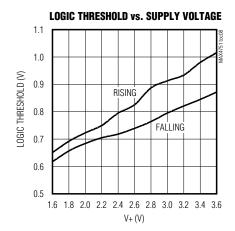

| Input Logic High              | V <sub>IH</sub> _     |                                                                                 |                        | T <sub>MIN</sub> to T <sub>MAX</sub> | 1.4  |        |      | V     |  |

| Input Logic Low               | V <sub>I</sub> L_     |                                                                                 |                        | T <sub>MIN</sub> to T <sub>MAX</sub> |      |        | 0.5  | V     |  |

| Input Leakage Current         | I <sub>IN</sub> _     | V <sub>IN</sub> _ = 0 or V+                                                     |                        | T <sub>MIN</sub> to T <sub>MAX</sub> | -1   | 0.0005 | +1   | μΑ    |  |

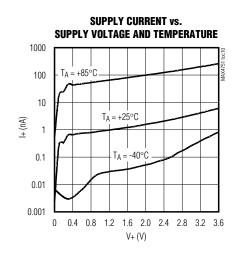

| POWER SUPPLY                  |                       |                                                                                 |                        |                                      |      |        |      |       |  |

| Power-Supply Range            | V+                    |                                                                                 |                        |                                      | +1.6 |        | +3.6 | V     |  |

| Positive Supply Current       | l+                    | $V+ = 3.6V, V_{I}$                                                              | $N_{-} = 0$ or $V_{+}$ |                                      |      |        | 1    | μΑ    |  |

# 0.9 $\Omega$ , Low-Voltage, Single-Supply Quad SPST Analog Switches

### **ELECTRICAL CHARACTERISTICS—Single +1.8V Supply**

$(V+=+1.8V, V_{IH}=+1V, V_{IL}=+0.4V, T_A=T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$  Typical values are at  $T_A=+25^{\circ}\text{C.}$ ) (Notes 2, 3)

| PARAMETER                   | SYMBOL                                                     | CONDITIONS                                                                          | TA                                   | MIN  | TYP    | MAX  | UNITS |

|-----------------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------|------|--------|------|-------|

| ANALOG SWITCH               |                                                            | •                                                                                   |                                      |      |        |      |       |

| Analog Signal Range         | V <sub>COM_</sub> ,<br>V <sub>NO_</sub> , V <sub>NC_</sub> |                                                                                     |                                      | 0    |        | V+   | V     |

| On Desistance (Nets 4)      |                                                            | V+ = 1.8V,                                                                          | +25°C                                |      | 1.4    | 2.5  | 0     |

| On-Resistance (Note 4)      | R <sub>ON</sub>                                            | I <sub>COM</sub> = 10mA,<br>V <sub>NO</sub> or V <sub>NC</sub> = 0.9V               | T <sub>MIN</sub> to T <sub>MAX</sub> |      |        | 3    | Ω     |

| On-Resistance Match Between | A.D.                                                       | V+ = 1.8V,                                                                          | +25°C                                |      | 0.05   | 0.25 |       |

| Channels (Notes 4, 5)       | ΔR <sub>ON</sub>                                           | ICOM_ = 10mA,<br>V <sub>NO_</sub> or V <sub>NC_</sub> = 0.9V                        | T <sub>MIN</sub> to T <sub>MAX</sub> |      |        | 0.25 | Ω     |

| SWITCH DYNAMIC CHARACTE     | RISTICS                                                    |                                                                                     |                                      |      |        |      |       |

| T 0 T                       | ton                                                        | $V_{NO\_}$ or $V_{NC\_}$ = 1.0V,<br>$R_L$ = 50 $\Omega$ , $C_L$ = 35pF,<br>Figure 1 | +25°C                                |      | 25     | 35   | ns    |

| Turn-On Time                |                                                            |                                                                                     | T <sub>MIN</sub> to T <sub>MAX</sub> |      |        | 35   |       |

| T 0"T                       |                                                            | $V_{NO\_}$ or $V_{NC\_}$ = 1.0V,<br>$R_L$ = 50 $\Omega$ , $C_L$ = 35pF,<br>Figure 1 | +25°C                                |      | 20     | 25   |       |

| Turn-Off Time               | toff                                                       |                                                                                     | T <sub>MIN</sub> to T <sub>MAX</sub> |      |        | 30   | ns    |

| Charge Injection            | Q                                                          | V <sub>GEN</sub> = 0, R <sub>GEN</sub> = 0,<br>C <sub>L</sub> = 1.0nF, Figure 2     | +25°C                                |      | 8      |      | рС    |

| DIGITAL I/O                 |                                                            |                                                                                     |                                      |      |        |      |       |

| Input Logic High            | V <sub>IH</sub> _                                          |                                                                                     | T <sub>MIN</sub> to T <sub>MAX</sub> | 1.0  |        |      | V     |

| Input Logic Low             | V <sub>IL</sub> _                                          |                                                                                     | T <sub>MIN</sub> to T <sub>MAX</sub> |      |        | 0.4  | V     |

| Input Leakage Current       | I <sub>IN</sub> _                                          | V <sub>IN</sub> _ = 0 or V+                                                         | T <sub>MIN</sub> to T <sub>MAX</sub> | -1   | 0.0005 | +1   | μΑ    |

| POWER SUPPLY                |                                                            |                                                                                     |                                      | _    |        |      |       |

| Power-Supply Range          | V+                                                         |                                                                                     |                                      | +1.6 |        | +3.6 | V     |

| Positive Supply Current     | l+                                                         | V <sub>IN</sub> _ = 0 or V+                                                         |                                      |      |        | 1    | μΑ    |

- Note 2: The algebraic convention is used in this data sheet; the most negative value is shown in the minimum column.

- Note 3: Parts are tested at +85°C and guaranteed by design and correlation over the full temperature range.

- Note 4: R<sub>ON</sub> and  $\Delta$ R<sub>ON</sub> matching specifications for QFN-packaged parts are guaranteed by design.

- **Note 5:**  $\Delta R_{ON} = R_{ON(MAX)} R_{ON(MIN)}$

- **Note 6:** Flatness is defined as the difference between the maximum and minimum value of on-resistance as measured over the specified analog signal ranges.

- Note 7: Leakage parameters are 100% tested at the maximum-rated hot operating temperature and guaranteed by correlation at  $T_A = +25$ °C.

- Note 8: Guaranteed by design, not production tested.

- Note 9: Off-Isolation =  $20\log_{10}[V_{COM} / (V_{NC} \text{ or } V_{NO})]$ ,  $V_{COM} = \text{ output, } V_{NC} \text{ or } V_{NO} = \text{ input to off switch.}$

# 0.9 $\Omega$ , Low-Voltage, Single-Supply Quad SPST Analog Switches

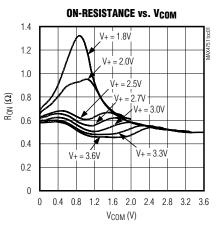

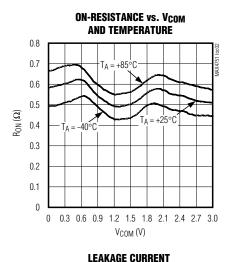

### **Typical Operating Characteristics**

$(V+ = +3V \text{ and } T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

# 0.9 $\Omega$ , Low-Voltage, Single-Supply Quad SPST Analog Switches

## Typical Operating Characteristics (continued)

$(V+ = +3V \text{ and } T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

## Pin Description

|                 |                 | PII             | N               |                 |                 |                           |                                            |

|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|---------------------------|--------------------------------------------|

| MAX4            | MAX4751         |                 | 752             | MAX4753         |                 | NAME                      | FUNCTION                                   |

| TSSOP           | QFN-EP          | TSSOP           | QFN-EP          | TSSOP           | QFN-EP          |                           |                                            |

| 1, 3,<br>8, 11  | 15, 1,<br>7, 11 | _               | _               | _               | _               | NO1, NO2,<br>NO3, NO4     | Switch Normally Open Terminals             |

| _               | _               | 1, 3,<br>8, 11  | 15, 1,<br>7, 11 | _               | _               | NC1, NC2,<br>NC3, NC4     | Switch Normally Closed Terminals           |

| _               | _               | _               | _               | 3, 11           | 1, 11           | NC2, NC4                  | Switch Normally Closed Terminals           |

| _               | _               | _               | _               | 1, 8            | 15, 7           | NO1, NO3                  | Switch Normally Open Terminals             |

| 2, 4,<br>9, 10  | 16, 2,<br>8, 9  | 2, 4,<br>9, 10  | 16, 2,<br>8, 9  | 2, 4,<br>9, 10  | 16, 2,<br>8, 9  | COM1, COM2,<br>COM3, COM4 | Switch Common Terminals                    |

| 7               | 6               | 7               | 6               | 7               | 6               | GND                       | Ground                                     |

| 13, 5,<br>6, 12 | 13, 4,<br>5, 12 | 13, 5,<br>6, 12 | 13, 4,<br>5, 12 | 13, 5,<br>6, 12 | 13, 4,<br>5, 12 | IN1, IN2,<br>IN3, IN4     | Logic Control Inputs                       |

| 14              | 14              | 14              | 14              | 14              | 14              | V+                        | Positive Supply Voltage                    |

| _               | 3, 10           | _               | 3, 10           | _               | 3, 10           | N.C.                      | No Connection. Not internally connected.   |

| _               | _               | _               | _               | _               | _               | EP                        | Exposed Pad (QFN Only). Connect EP to GND. |

# 0.9 $\Omega$ , Low-Voltage, Single-Supply Quad SPST Analog Switches

## Test Circuits/Timing Diagrams

Figure 1. Switching Times

# 0.9 $\Omega$ , Low-Voltage, Single-Supply Quad SPST Analog Switches

## Test Circuits/Timing Diagrams (continued)

Figure 3. NO\_, NC\_, and COM\_ Capacitance

Figure 4. Off-Isolation, On-Loss, and Crosstalk

Figure 2. Charge Injection

## 0.9 $\Omega$ , Low-Voltage, Single-Supply Quad SPST Analog Switches

### **Detailed Description**

The MAX4751/MAX4752/MAX4753 are low  $0.9\Omega$  max (at V+ = 3V) on-resistance, low-voltage quad analog switches that operate from a +1.6V to +3.6V single supply. CMOS construction allows switching analog signals that are within the supply voltage range (GND to V+).

When powered from a +3V supply, the  $0.9\Omega$  (max) R<sub>ON</sub> allows high continuous currents to be switched in a variety of applications.

### **Applications Information**

Proper power-supply sequencing is recommended for all CMOS devices. Do not exceed the absolute maximum ratings because stresses beyond the listed ratings can cause permanent damage to the devices. Always sequence V+ on first, followed by NO\_, NC\_, or COM\_. If power-supply sequencing is not possible, add two small-signal diodes (D1, D2) in series with the supply pins for overvoltage protection (Figure 5). Adding these diodes reduces the analog signal by one diode drop below V+ and one diode drop above GND, but does not affect the low switch resistance and low leakage characteristics of the device. Device operation is unchanged, and the difference between V+ and GND should not exceed 4V.

Power-supply bypassing is needed to improve noise margin and to prevent switching noise propagation from the V+ supply to other components. A 0.1 $\mu$ F capacitor, connected from V+ to GND, is adequate for most applications.

#### **Logic Inputs**

The MAX4751/MAX4752/MAX4753 logic inputs can be driven up to +3.6V regardless of the supply voltage. For example, with a +1.8V supply, IN\_ may be driven low to GND and high to +3.6V. Driving IN\_ rail-to-rail minimizes power consumption.

#### **Analog Signal Levels**

Analog signals that range over the entire supply voltage (V+ to GND) can be passed with very little change in on-

Figure 5. Overvoltage Protection Using Two External Blocking Diodes

resistance (see the *Typical Operating Characteristics*). The switches are bidirectional, so the NO\_, NC\_, and COM\_ pins can be used as either inputs or outputs.

#### Layout

High-speed switches require proper layout and design procedures for optimum performance. Reduce stray inductance and capacitance by keeping traces short and wide. Ensure that bypass capacitors are as close to the device as possible. Use large ground planes where possible.

#### \_Chip Information

**TRANSISTOR COUNT: 228**

PROCESS: CMOS

# 0.9 $\Omega$ , Low-Voltage, Single-Supply Quad SPST Analog Switches

## Pin Configurations/Functional Diagrams/Truth Tables (continued)

## Package Information

For the latest package outline information and land patterns (footprints), go to <a href="https://www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE TYPE | PACKAGE CODE | OUTLINE NO.    | LAND PATTERN NO. |

|--------------|--------------|----------------|------------------|

| 14 TSSOP     | U14+1        | <u>21-0066</u> | <u>90-0113</u>   |

| 16 QFN       | G1633+2      | <u>21-0102</u> | <u>90-0215</u>   |

# 0.9 $\Omega$ , Low-Voltage, Single-Supply Quad SPST Analog Switches

### **Revision History**

| REVISION | REVISION | DESCRIPTION                     | PAGES          |

|----------|----------|---------------------------------|----------------|

| NUMBER   | DATE     |                                 | CHANGED        |

| 2        | 1/13     | Corrected packaging information | 1, 2, 6, 10–13 |

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.