#### **General Description**

The MAX5058/MAX5059 enable secondary-side synchronous rectification in isolated power supplies using widely available power MOSFETs. These devices facilitate the commutation of the secondary-side MOSFETs by providing a clean gate-drive signal that is synchronized to the power MOSFET switching in the primary side of the isolation transformer. The MAX5058/MAX5059 complement the MAX5051 and MAX5042/MAX5043 primaryside PWM ICs and enable the design of high-efficiency synchronously rectified isolated power supplies. Simultaneous conduction of the primary side and the freewheeling synchronous rectifier MOSFET is avoided by having a look-ahead signal (before the primary-side MOSFETs turn ON), thus eliminating large current spikes resulting from a shorted transformer secondary.

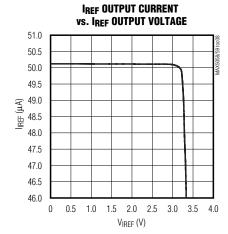

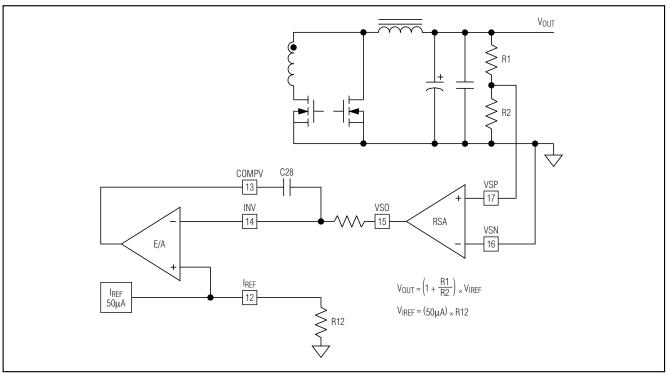

An on-board error amplifier with a versatile current reference output enables virtually unlimited possibilities in reference-voltage generation. Reference voltage for the error amplifier is generated by connecting an appropriate resistor to this output.

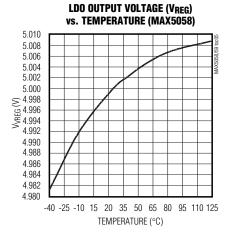

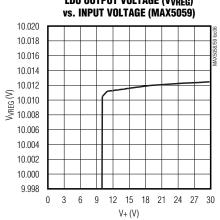

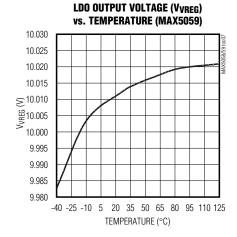

Low on-resistance margining MOSFETs integrated onchip allow for implementation of a margining circuit without the use of external switches. The MAX5058 provides a 5V LDO output for logic-level MOSFETs while the MAX5059 provides a 10V LDO output for conventional 10V MOSFETs.

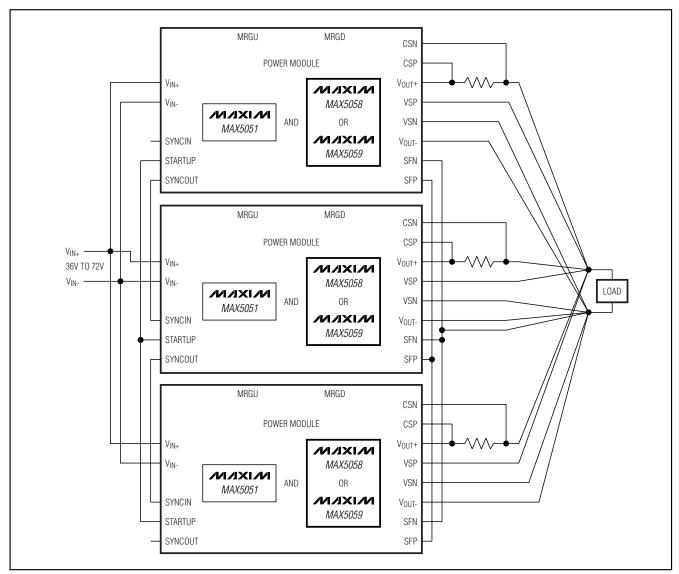

The MAX5058/MAX5059 are designed to enable paralleling of multiple power supplies for accurate current sharing using a simple 2-wire, differential, current-share bus. Parallelability enables expansion of the power capabilities and simplifies thermal management in highoutput-current applications. When used in conjunction with the MAX5051, the primaries can also be synchronized and operated 180 degrees out of phase.

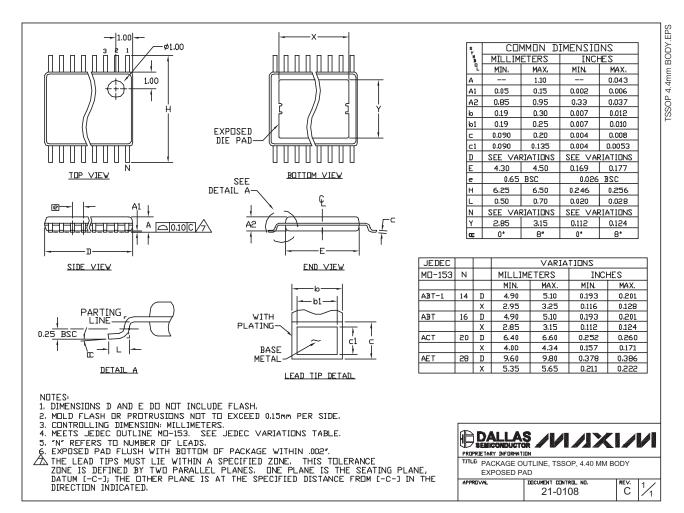

The MAX5058/MAX5059 are available in a 28-pin thermally enhanced TSSOP package and operate over a wide -40°C to +125°C temperature range.

Warning: The MAX5058/MAX5059 are designed to work in circuits that contain high voltages. Exercise caution.

### **Applications**

Isolated Telecom Power Supplies Isolated Networking Power Supplies ±48V Power-Supply Modules **Industrial Power Supplies** ±48V/±12V Server Power Supplies

#### Features

- ♦ Clean Drive Waveforms for Synchronous **MOSFETs**

- ♦ Utilization of a Look-Ahead Signal from the **Primary for Proper Turn-On/Turn-Off Times**

- **♦** Synchronous Rectifier Drivers Capable of Sourcing and Sinking Up to 2A Peak Current

- ♦ Internal Gate-Voltage Regulator for 5V (MAX5058) or 10V (MAX5059) Gate-Drive Voltage

- **♦ Internal Error Amplifier**

- ◆ Accurate Differential Current-Share/Force Circuit Allows Paralleling of Several Power Supplies for **High Output Current**

- ◆ Internal Remote Voltage-Sense Amplifier

- ♦ Flexible Reference-Voltage Generation

- ♦ Output Voltage Regulation Down to 0.5V

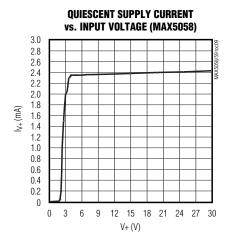

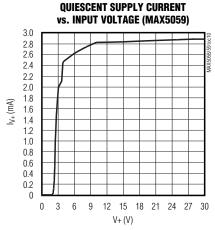

- ♦ Low Quiescent Current Consumption of 2.5mA

- ♦ Integrated Digital Output Margining Circuit Saves **External Parts and Board Space**

- ♦ 30ns Propagation Delay Time from Pulse Input to Output

- **♦** Automatic Detection of Discontinuous Current Conduction and Turn-Off of the Freewheeling **MOSFET**

- ♦ High Efficiency at Low Output Currents and **Reverse-Current Protection**

- ♦ Open-Drain Overtemperature Warning Flag

- **♦ 28-Pin Thermally Enhanced TSSOP Package**

### **Ordering Information**

| PART       | TEMP RANGE      | TEMP RANGE PIN-<br>PACKAGE |    |

|------------|-----------------|----------------------------|----|

| MAX5058AUI | -40°C to +125°C | 28 TSSOP-EP*               | 5  |

| MAX5058EUI | -40°C to +85°C  | 28 TSSOP-EP*               | 5  |

| MAX5059AUI | -40°C to +125°C | 28 TSSOP-EP*               | 10 |

| MAX5059EUI | -40°C to +85°C  | 28 TSSOP-EP*               | 10 |

<sup>\*</sup>EP = Exposed paddle.

Pin Configuration appears at end of data sheet.

MIXIM

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| QREC, QSYNC Continuous Current                 | 50mA     |

|------------------------------------------------|----------|

| QREC, QSYNC Current < 500ns                    | 5A       |

| Continuous Power Dissipation ( $T_A = +70$ °C) |          |

| 28-Pin TSSOP (derate 23.8mW/°C above +70°C)    | 1905mW   |

| Junction Temperature                           | +150°C   |

| Operating Temperature Ranges                   |          |

| MAX5058EUI, MAX5059EUI40°C                     | to +85°C |

| MAX5058AUI, MAX5059AUI40°C t                   | o +125°C |

| Storage Temperature Range65°C t                | o +150°C |

| Lead Temperature (soldering, 10s)              | +300°C   |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V+=+12V, GND=PGND=0, VDR=V_{REG}, C_{QSYNC}=C_{QREC}=0, ZCP=ZCN=BUFIN=CSP=CSN=SFN=VSN=GND, V_{IREF}=V_{VSP}=1.785V, C_{VREG}=2.2\mu F, C_{VP}=1\mu F, C_{COMPS}=0.1\mu F, C_{SFP}=68n F, T_A=T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A=+25^{\circ}C$ .)

| PARAMETER                                | SYMBOL               | CONDITIONS                                          |                                        | MIN  | TYP  | MAX  | UNITS |

|------------------------------------------|----------------------|-----------------------------------------------------|----------------------------------------|------|------|------|-------|

| POWER SUPPLY                             | •                    |                                                     |                                        |      |      |      | •     |

|                                          | .,                   | MAX5058                                             |                                        | 4.5  |      | 28.0 |       |

| Supply Voltage Range                     | V+                   | MAX5059                                             |                                        | 9.3  |      | 28.0 | V     |

| Quiescent Supply Current                 | IQ                   |                                                     |                                        |      | 2.5  | 5    | mA    |

| Cuitabina Cunalu Cumant                  | 1=                   | face OFOR In at DUFIN                               | MAX5058                                |      | 4.5  |      | A     |

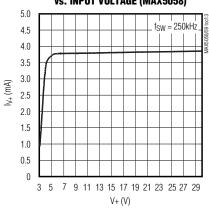

| Switching Supply Current                 | ISW                  | fsw = 250kHz at BUFIN                               | MAX5059                                |      | 6    |      | mA    |

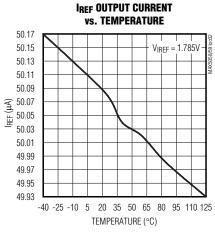

| I <sub>REF</sub> : REFERENCE CURRENT O   | UTPUT                |                                                     |                                        |      |      |      |       |

| Reference Current                        | IIREF                | V <sub>IREF</sub> = 1.785V                          |                                        | 49.2 | 50   | 51.1 | μΑ    |

| Reference Current Variation              | $\Delta I_{ m IREF}$ | V <sub>IREF</sub> = 0.5V to 2.5V                    |                                        | -0.1 |      | +0.1 | %/V   |

| Reference Voltage Compliance<br>Range    |                      | Guaranteed by reference current variation test      |                                        | 0.5  |      | 2.5  | V     |

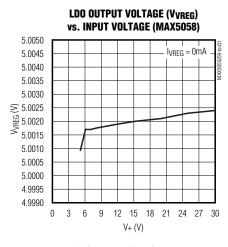

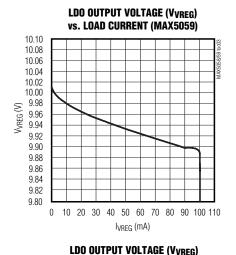

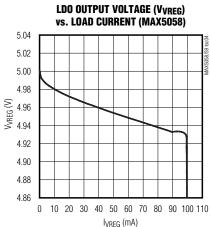

| V <sub>REG</sub> : LOW-DROPOUT REGULA    | TOR                  |                                                     |                                        |      |      |      | •     |

| Pagulator Quitaut                        | Vvreg                | Ivreg = 0 to 30mA MAX5058 MAX5059                   | MAX5058                                | 4.75 | 5    | 5.25 | V     |

| Regulator Output                         |                      |                                                     | 9.4                                    | 10   | 10.6 |      |       |

| Line Regulation                          |                      | MAX5058, V+ = 6V to 28V<br>MAX5059, V+ = 11V to 28V |                                        |      |      | 25   | mV    |

| Line negulation                          |                      |                                                     |                                        |      |      | 25   | IIIV  |

| Dranaut                                  | \/                   | MAX5058                                             | V+ = 4.5V,<br>$I_{VREG} = 30mA$        |      | 200  | 350  | mV    |

| Dropout                                  | VDROP                | MAX5059                                             | V+ = 9.3V,<br>I <sub>VREG</sub> = 30mA |      | 200  | 350  | IIIV  |

| VP: INTERNAL REGULATOR                   | •                    |                                                     | •                                      |      |      |      | •     |

| Regulator Output Setpoint                | VvP                  | $I_{VP} = 0$ to 5mA                                 |                                        | 3.8  |      | 4.3  | V     |

| ZC: ZERO-CURRENT COMPARA                 | TOR                  | •                                                   |                                        |      |      |      |       |

| Zero-Current Comparator<br>Threshold     | Vzcth                | T <sub>A</sub> = +25°C                              |                                        | +3.5 | +5   | +6.5 | mV    |

| Zero-Current Comparator Input<br>Current | Izc                  |                                                     |                                        | -2.5 |      | +2.5 | μΑ    |

2 \_\_\_\_\_\_*NIXIM*

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V+=+12V, GND=PGND=0, VDR=V_{REG}, C_{QSYNC}=C_{QREC}=0, ZCP=ZCN=BUFIN=CSP=CSN=SFN=VSN=GND, V_{IREF}=V_{VSP}=1.785V, C_{VREG}=2.2\mu F, C_{VP}=1\mu F, C_{COMPS}=0.1\mu F, C_{SFP}=68nF, T_A=T_{MIN} \ to \ T_{MAX}, unless otherwise noted. Typical values are at T_A=+25°C.)$

| Zero-Current Comparator Input Range   Vzc   Tom Verdrive, from when Vzcp - Vzcn is greater fran VzcTH to when QSYNC goes low   SynC goes lo  | PARAMETER                         | SYMBOL              | CONDITIONS                |            | MIN  | TYP | MAX  | UNITS |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------------|---------------------------|------------|------|-----|------|-------|

| tzc   greater than VzCTH to when QSYNC goes   65   ms   ms   ms   ms   ms   ms   ms   m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ·                                 | V <sub>ZC</sub>     |                           |            | -0.1 |     | +1.5 | V     |

| BUFIN to Output Propagation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | '                                 | tzc                 | greater than Vzcth to whe |            |      | 65  |      | ns    |

| Delay   BUFIN Input Current   BUFIN   Falling   BUFIN Input Current   BUFIN Input Capacitance   CBUFIN   Possible In Input Capacitance   CBUFIN   Possible In Input-Logic Logic High   VHBUFIN   Possible In Input-Logic Low   VLBUFIN   Possible Input-Logic Low   Possible Input-Logic Logic Low   Possible Input-Logic Logic Logic Low   Possible Input-Logic Logic Logi  | <b>BUFIN: SYNCHRONIZING PULSE</b> | INPUT               |                           |            |      |     |      |       |

| BUFIN Input Capacitance   CBUFIN   PFBUFIN Input-Logic High   VHBUFIN   PUFIN   PUF  | , , ,                             | t <sub>pd</sub>     | •                         | g or QSYNC |      | 40  |      | ns    |

| BUFIN Input-Logic High   VHBUFIN   DUFIN     | BUFIN Input Current               | IBUFIN              |                           |            | -1   |     | +1   | μΑ    |

| Margin Input-Logic Low   Veburin   | BUFIN Input Capacitance           | CBUFIN              |                           |            |      | 10  |      | рF    |

| MARGINNG INPUTS   RMGD Resistance   RRMGD   Sinking 10mA   6.5   11   Ω                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | BUFIN Input-Logic High            | VHBUFIN             |                           |            | 2.4  |     |      | V     |

| RMGD Resistance   RRMGD   Sinking 10mA   6.5   11   Ω                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | BUFIN Input-Logic Low             | V <sub>LBUFIN</sub> |                           |            |      |     | 0.8  | V     |

| RMGU Resistance   RRMGU   Sinking 10mA   S.5   11   Ω                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | MARGINING INPUTS                  |                     |                           |            |      |     |      |       |

| MRGD Input-Logic High   VHMRGD   2.4   V   MRGD   MRGD Input-Logic Low   VLMRGD   2.4   V   MRGU Input-Logic High   VHMRGU   2.4   V   MRGU Input-Logic Low   VLMRGU   2.4   V   MRGU Input-Logic Low   VLMRGU   40   & 0.8   V   MRGU, MRGD Input Resistance   RMRGD, RMRGD   RMRG  | RMGD Resistance                   | R <sub>RMGD</sub>   | Sinking 10mA              |            |      | 6.5 | 11   | Ω     |

| MRGD Input-Logic Low   VLMRGD   2.4   V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | RMGU Resistance                   | R <sub>RMGU</sub>   | Sinking 10mA              |            |      | 6.5 | 11   | Ω     |

| MRGU Input-Logic High         VHMRGU         2.4         V           MRGU Input-Logic Low         VLMRGU         0.8         V           MRGU, MRGD Input Resistance         RMRGD, RMRGD RMRGD         40         kΩ           RMGU, RMGD Leakage Current         IRMGD, RMRGD Input Resistance         Input Resistance         IRMGD, RMRGD Input Resistance         IRMGD, RM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | MRGD Input-Logic High             | VHMRGD              |                           |            | 2.4  |     |      | V     |

| MRGU Input-Logic Low         VLMRGU MRGD Input Resistance         VLMRGU MRGD Input Resistance         RMRGD MRGD MRGD MRGD MRGD MRGD MRGD MRGD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | MRGD Input-Logic Low              | V <sub>LMRGD</sub>  |                           |            |      |     | 0.8  | V     |

| MRGU, MRGD Input Resistance   RMRGD, RMRGU   RMGU, RMGD Leakage Current   IRMGU, RMGD Leakage Current   IRMGU, RMGD Leakage Current   IRMGU, RMGD   IRMGD    | MRGU Input-Logic High             | VHMRGU              |                           |            | 2.4  |     |      | V     |

| RMGU, RMGD Leakage Current   IRMGU, IRMGD   IRMGU, IRMGD Leakage Current   IRMGU, IRMGD   IR | MRGU Input-Logic Low              | V <sub>LMRGU</sub>  |                           |            |      |     | 0.8  | V     |

| DRIVER OUTPUTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | MRGU, MRGD Input Resistance       | _                   |                           |            | 40   |     |      | kΩ    |

| QREC, QSYNC Peak Source Current         IQREC_SO, IQSYNC_SO         2         A           QREC, QSYNC Output-Voltage High         VQREC_H, VQSYNC_H         Measured with respect to VVDR, sourcing 50mA         MAX5058         75         150         mV           QREC, QSYNC Low-to-High Delay Time         TPDLH         CQREC = CQSYNC = 0         30         ns           QREC, QSYNC Peak Sink Current Low         IQREC_SI, IQSYNC_SI         2         A           QREC, QSYNC Output-Voltage Low         VQREC_L, VQSYNC_L         Sinking 50mA         MAX5058         50         100           QREC, QSYNC High-to-Low         TRDHI         CQREC = CQSYNC = 0         40         DS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | RMGU, RMGD Leakage Current        |                     |                           |            | -100 |     | +100 | nA    |

| Current         IQSYNC_SO         Measured with respect to VVDR, sourcing 50mA         MAX5058         75         150         mV           QREC, QSYNC Low-to-High Delay Time         TPDLH         CQREC = CQSYNC = 0 CQREC = CQSYNC = 5nF         30         ns           QREC, QSYNC Peak Sink Current Low         IQREC_SI, IQSYNC_SI         VQREC_L, VQSYNC Output-Voltage         YQREC_L, VQSYNC_L         Sinking 50mA         MAX5058         50         100         mV           QREC, QSYNC High-to-Low         TPDLH         CQREC = CQSYNC = 0         MAX5059         50         100         mV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | DRIVER OUTPUTS                    | •                   |                           |            |      |     |      | •     |

| Max   Max  |                                   |                     |                           |            |      | 2   |      | А     |

| High                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | OREC: OSYNC Output-Voltage        | VODEC H             | Measured with respect to  | MAX5058    |      | 75  | 150  |       |

| Delay Time         TPDLH         CQREC = CQSYNC = 5nF         70         ns           QREC, QSYNC Peak Sink Current         IQREC_SI, IQSYNC_SI         2         A           QREC, QSYNC Output-Voltage Low         VQREC_L, VQSYNC_L         Sinking 50mA         MAX5058         50         100         mV           QREC, QSYNC High-to-Low         CQREC = CQSYNC = 0         40         ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                   |                     | ·                         | MAX5059    |      | 75  | 150  | mV    |

| QREC, QSYNC Peak Sink Current         IQREC_SI, IQSYNC_SI         2         A           QREC, QSYNC Output-Voltage Low         VQREC_L, VQSYNC_L         Sinking 50mA         MAX5058         50         100         mV           QREC, QSYNC High-to-Low         CQREC = CQSYNC = 0         40         ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | QREC, QSYNC Low-to-High           | <b>4</b>            | CQREC = CQSYNC = 0        |            |      | 30  |      | ne    |

| QREC, QSYNC Output-Voltage         VQREC_L, VQSYNC_L         Sinking 50mA         MAX5058         50         100         mV           QREC, QSYNC High-to-Low         CQREC = CQSYNC = 0         40         ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Delay Time                        | IPDLH               | CQREC = CQSYNC = 5nF      |            |      | 70  |      | 115   |

| Low         VQSYNC_L         Sinking 50mA         MAX5059         50         100           QREC, QSYNC High-to-Low         CQREC = CQSYNC = 0         40         ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | QREC, QSYNC Peak Sink Current     |                     |                           |            |      | 2   |      | А     |

| Low         VQSYNC_L         SINKING SUMA         MAX5059         50         100           QREC, QSYNC High-to-Low         CQREC = CQSYNC = 0         40         ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ,                                 | VQREC_L,            | Oighig at Force A         | MAX5058    |      | 50  | 100  | mc\/  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                   |                     | SITIKING SUMA             | MAX5059    |      | 50  | 100  | LIJA  |

| Polov Time Public O O F F I I I I I I I I I I I I I I I I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | QREC, QSYNC High-to-Low           |                     | CQREC = CQSYNC = 0        |            |      | 40  |      | no.   |

| Delay Time   CQREC = CQSYNC = 5NF /0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Delay Time                        |                     | CQREC = CQSYNC = 5nF      |            |      | 70  |      | 115   |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V+=+12V, GND=PGND=0, VDR=V_{REG}, C_{QSYNC}=C_{QREC}=0, ZCP=ZCN=BUFIN=CSP=CSN=SFN=VSN=GND, V_{IREF}=V_{VSP}=1.785V, C_{VREG}=2.2\mu F, C_{VP}=1\mu F, C_{COMPS}=0.1\mu F, C_{SFP}=68nF, T_A=T_{MIN} \ to \ T_{MAX}, \ unless otherwise noted. Typical values are at T_A=+25°C.)$

| PARAMETER                             | SYMBOL           | CONDITIONS                                                            | MIN    | TYP | MAX    | UNITS |

|---------------------------------------|------------------|-----------------------------------------------------------------------|--------|-----|--------|-------|

| ERROR AMPLIFIER                       |                  |                                                                       |        |     |        |       |

| Inverting Input Current               | I <sub>INV</sub> |                                                                       | -50    |     | +50    | nA    |

| Error-Amplifier Input Range           | VINV             |                                                                       | 0      |     | 2.5    | V     |

| Error-Amplifier Input Offset          | Vos              | ICOMPV = 100µA to 5mA                                                 | -5     |     | +5     | mV    |

| Error-Amplifier Output-Voltage<br>Low | VCOMPV           | ICOMPV = 5mA                                                          |        |     | 200    | mV    |

| Error-Amplifier Unity-Gain BW         | GBW              | $R_{COMP} = 220\Omega$ , $I_{COMP} = 5mA$                             |        | 1.3 |        | MHz   |

| Error-Amplifier Voltage Gain          | Avol             | $R_{COMPV} = 220\Omega$ , $I_{COMP} = 5mA$                            |        | 80  |        | dB    |

| Error-Amplifier PSRR                  | PSRR             |                                                                       |        | 60  |        | dB    |

| COMPV Output Resistance to Ground     |                  | (Note 1)                                                              |        | 1   |        | МΩ    |

| REMOTE-SENSE AMPLIFIER (F             | RSA)             | 1                                                                     |        |     |        |       |

| VSN Input Current                     | Ivsn             |                                                                       | -100   |     | +100   | μΑ    |

| VSP Input Current                     | Ivsp             |                                                                       | -20    |     | +100   | μΑ    |

| Input Common-Mode Range               |                  |                                                                       | -0.3   |     | +3.8   | V     |

| Input Offset Voltage                  | Vosrsa           | $I_{VSO} = -0.5 \text{mA} \text{ to } +0.5 \text{mA}$                 |        | -4  |        | mV    |

| Output Impedance                      |                  |                                                                       |        | 8   |        | Ω     |

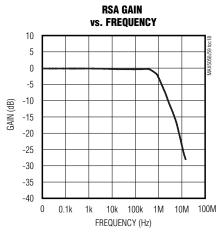

| Amplifier -3dB Frequency              |                  | $I_{VSO} = -0.5$ mA to $+0.5$ mA                                      |        | 1   |        | MHz   |

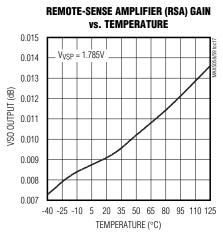

| Remote-Sense Amplifier Gain           | G <sub>RS</sub>  | $I_{VSO} = -0.5$ mA to $+0.5$ mA                                      | 0.9925 | 1   | 1.0075 | V/V   |

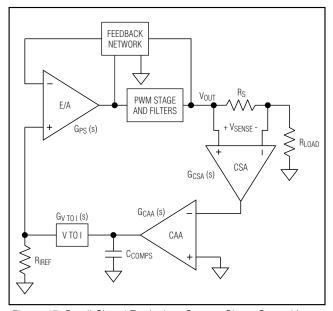

| CURRENT-SENSE AMPLIFIER               | (CSA)            |                                                                       |        |     |        |       |

| CSN Input Current                     | ICSN             | -0.3V ≤ V <sub>CSN</sub> ≤ +3.8V,<br>-0.3V ≤ V <sub>CSP</sub> ≤ +3.8V | -150   |     | +150   | μΑ    |

| CSP Input Current                     | ICSP             | -0.3V ≤ V <sub>CSP</sub> ≤ +3.8V                                      | -40    |     | +150   | μΑ    |

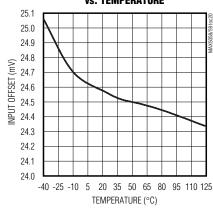

| Input Offset Voltage                  |                  | I <sub>CSO</sub> = -500μA to +500μA (Note 2)                          | +20    | +25 | +30    | mV    |

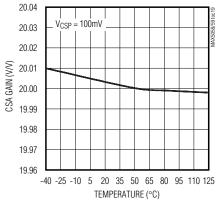

| Current-Sense Amplifier Gain          | GCSA             | I <sub>CSO</sub> = -500μA to +500μA                                   | 19.8   | 20  | 20.2   | V/V   |

| Input Differential-Mode Range         |                  |                                                                       |        |     | 100    | mV    |

| Input Common-Mode Range               |                  |                                                                       | -0.3   |     | +3.8   | V     |

| Output-Voltage Level Shift            | V <sub>LS</sub>  | (Note 2)                                                              | 0.415  |     | 0.570  | V     |

| Output Voltage Range                  | VCSO(MIN)        | ICSO = -500μA to +500μA                                               | 0.1    |     | 3.0    | V     |

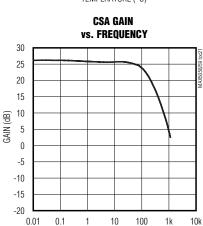

| Amplifier -3dB Frequency              | f-3dB            | I <sub>CSO</sub> = -500μA to +500μA                                   |        | 50  |        | kHz   |

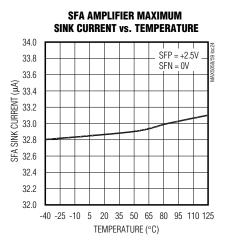

| SHARE-FORCE AMPLIFIER (SF             | A)               |                                                                       |        |     |        |       |

| Sink Current                          |                  |                                                                       |        |     | 60     | μΑ    |

| Source Current                        |                  |                                                                       | 500    |     |        | μΑ    |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V+=+12V, GND=PGND=0, VDR=V_{REG}, C_{QSYNC}=C_{QREC}=0, ZCP=ZCN=BUFIN=CSP=CSN=SFN=VSN=GND, V_{IREF}=V_{VSP}=1.785V, C_{VREG}=2.2\mu F, C_{VP}=1\mu F, C_{COMPS}=0.1\mu F, C_{SFP}=68nF, T_{A}=T_{MIN} \ to \ T_{MAX}, unless otherwise noted. Typical values are at T_{A}=+25^{\circ}C.)$

| PARAMETER                               | SYMBOL    | CONDITIONS             | MIN  | TYP  | MAX  | UNITS |

|-----------------------------------------|-----------|------------------------|------|------|------|-------|

| CURRENT-ADJUST AMPLIFIER (              | (CAA)     |                        | •    |      |      |       |

| Transconductance                        |           |                        |      | 500  |      | μA/V  |

| Common-Mode Input Voltage<br>Range      |           |                        | 0.45 |      | 2.55 | ٧     |

| Output Voltage Range                    |           |                        | 0.85 |      | 2.75 | V     |

| Offset Voltage                          |           | $T_A = +25^{\circ}C$   | 20   | 42   | 65   | mV    |

| Open-Loop Gain                          |           |                        |      | 72   |      | dB    |

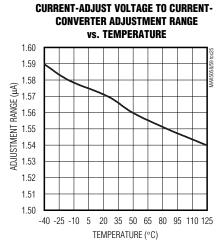

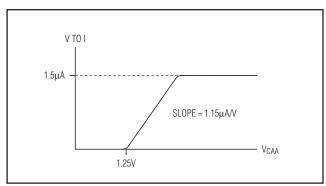

| <b>CURRENT-ADJUST VOLTAGE-T</b>         | O-CURRENT | CONVERTER              |      |      |      |       |

| Input Voltage Range                     |           |                        | 0.75 |      | 2.75 | V     |

| Input Voltage Offset                    |           |                        |      | 1.25 |      | V     |

| Output Voltage Range                    |           |                        | 0.5  |      | 2.5  | V     |

| Transconductance                        |           |                        |      | 1.15 |      | μA/V  |

| Maximum Current Adjustment Value        |           |                        | 1.38 | 1.5  | 1.66 | μΑ    |

| THERMAL SHUTDOWN                        |           |                        |      |      |      |       |

| Thermal Warning Flag Level              |           | When TSF pulls low     |      | +125 |      | °C    |

| Thermal Warning Flag Hysteresis         |           |                        |      | 15   |      | °C    |

| Internal Thermal-Shutdown Level         |           |                        |      | +160 |      | °C    |

| Internal Thermal-Shutdown<br>Hysteresis |           |                        |      | 15   |      | °C    |

| TSF Maximum Output Voltage              |           | I <sub>TSF</sub> = 5mA |      |      | 120  | mV    |

| TSF Output Leakage Current              |           |                        |      |      | 0.1  | μΑ    |

Note 1: Output resistance to ground used for unity-gain stability.

Note 2:  $V_{CSO} = G_{CSA}(V_{CSP} - V_{CSN}) + V_{LS}$ .

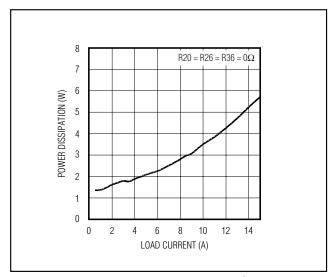

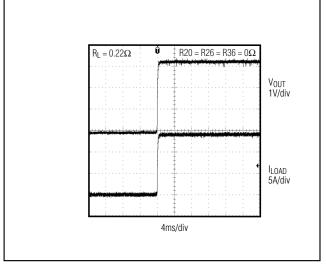

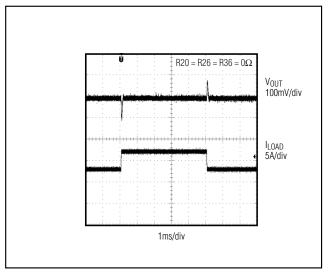

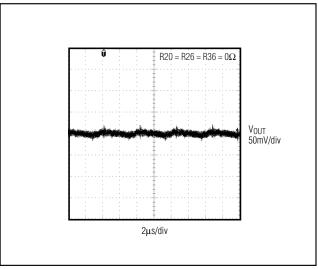

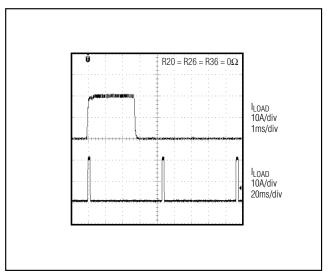

#### **Typical Operating Characteristics**

$(V+=+12V, GND=PGND=0, VDR=V_{REG}, C_{QSYNC}=C_{QREC}=0, ZCP=ZCN=BUFIN=CSP=CSN=SFN=VSN=GND, V_{IREF}=V_{VSP}=1.785V, V_{COMPS}=0.5V, C_{VREG}=2.2\mu F, C_{VP}=1\mu F, C_{COMPS}=0.1\mu F, C_{SFP}=68n F, T_{A}=+25^{\circ}C, unless otherwise noted.)$

### **Typical Operating Characteristics (continued)**

$(V+=+12V, GND=PGND=0, VDR=V_{REG}, C_{QSYNC}=C_{QREC}=0, ZCP=ZCN=BUFIN=CSP=CSN=SFN=VSN=GND, V_{IREF}=V_{VSP}=1.785V, V_{COMPS}=0.5V, C_{VREG}=2.2\mu F, C_{VP}=1\mu F, C_{COMPS}=0.1\mu F, C_{SFP}=68nF, T_{A}=+25^{\circ}C, unless otherwise noted.)$

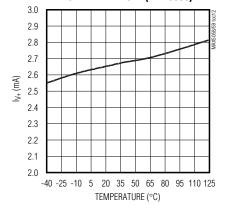

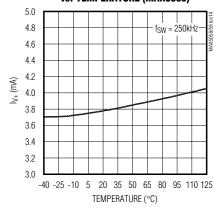

# QUIESCENT SUPPLY CURRENT vs. TEMPERATURE (MAX5059)

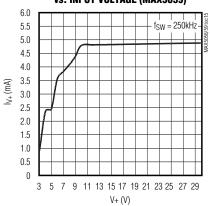

# SWITCHING SUPPLY CURRENT vs. INPUT VOLTAGE (MAX5058)

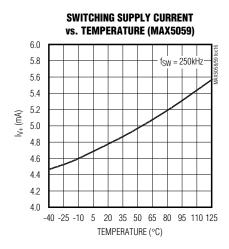

# SWITCHING SUPPLY CURRENT vs. TEMPERATURE (MAX5058)

# SWITCHING SUPPLY CURRENT vs. INPUT VOLTAGE (MAX5059)

### Typical Operating Characteristics (continued)

$(V+=+12V, GND=PGND=0, VDR=V_{REG}, C_{QSYNC}=C_{QREC}=0, ZCP=ZCN=BUFIN=CSP=CSN=SFN=VSN=GND, V_{IREF}=V_{VSP}=1.785V, V_{COMPS}=0.5V, C_{VREG}=2.2\mu F, C_{VP}=1\mu F, C_{COMPS}=0.1\mu F, C_{SFP}=68nF, T_{A}=+25^{\circ}C, unless otherwise noted.)$

# CURRENT-SENSE AMPLIFIER (CSA) GAIN vs. TEMPERATURE

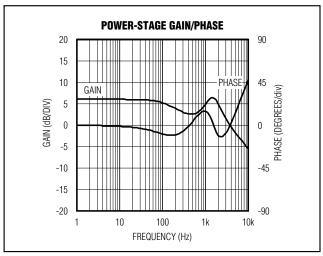

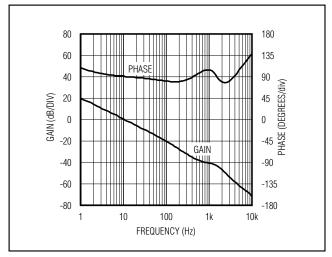

FREQUENCY (Hz)

# CSA INPUT OFFSET vs. TEMPERATURE

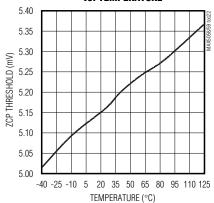

# ZERO-CURRENT COMPARATOR THRESHOLD vs. TEMPERATURE

MIXIM

### **Typical Operating Characteristics (continued)**

$(V+=+12V, \ GND=PGND=0, \ VDR=V_{REG}, \ C_{QSYNC}=C_{QREC}=0, \ ZCP=ZCN=BUFIN=CSP=CSN=SFN=VSN=GND, \ V_{IREF}=V_{VSP}=1.785V, \ V_{COMPS}=0.5V, \ C_{VREG}=2.2\mu F, \ C_{VP}=1\mu F, \ C_{COMPS}=0.1\mu F, \ C_{SFP}=68nF, \ T_{A}=+25^{\circ}C, \ unless \ otherwise \ noted.)$

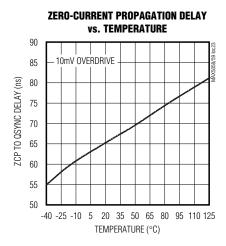

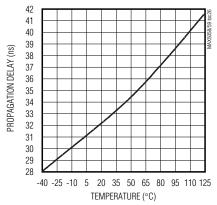

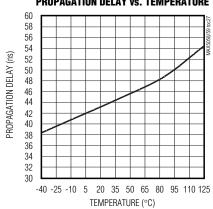

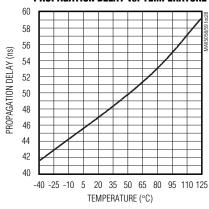

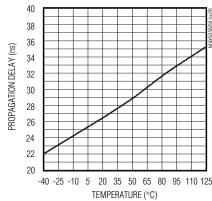

# BUFIN TO QSYNC LOW-TO-HIGH PROPAGATION DELAY vs. TEMPERATURE

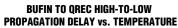

# BUFIN TO QSYNC HIGH-TO-LOW PROPAGATION DELAY vs. TEMPERATURE

### **Pin Description**

| PIN | NAME             | FUNCTION                                                                                                                                                                                                                                              |

|-----|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | ZCP              | Zero-Inductor Current-Sense Comparator Input. The source voltage of the freewheeling FET (N4 in the <i>Typical Application Circuit</i> ) is sensed. The gate drive is terminated when this voltage becomes positive during a primary power-OFF cycle. |

| 2   | ZCN              | Zero-Inductor Current-Sense Comparator Negative Input                                                                                                                                                                                                 |

| 3   | GND              | Ground Connection                                                                                                                                                                                                                                     |

| 4   | SFN              | Negative Input of the Share-Force Amplifier. Connect the SFN inputs together from all the power-supply secondaries, then connect to the load return terminal (isolated GND). Connect to GND when current sharing is not used.                         |

| 5   | SFP              | Positive Input of the Share-Force Amplifier. Connect the SFP pins together from all the power-supply secondaries. Leave this pin unconnected when current sharing is not used.                                                                        |

| 6   | COMPS            | Compensation Output of the Load-Share Transconductance Amplifier                                                                                                                                                                                      |

| 7   | TSF              | Thermal Warning Flag Output                                                                                                                                                                                                                           |

| 8   | MRGU             | Margin-Up Logic Input. When toggled high, the power-supply output voltage is set to the high margin.                                                                                                                                                  |

| 9   | MRGD             | Margin-Down Logic Input. When toggled high, the power-supply output voltage is set to the low margin.                                                                                                                                                 |

| 10  | RMGD             | Resistor Connection for Margin-Down                                                                                                                                                                                                                   |

| 11  | RMGU             | Resistor Connection for Margin-Up                                                                                                                                                                                                                     |

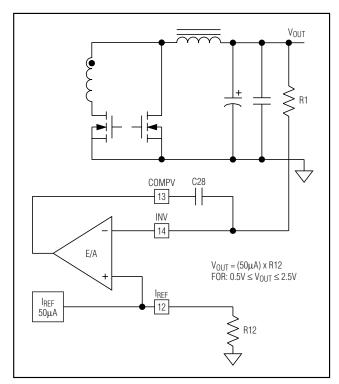

| 12  | I <sub>REF</sub> | Reference Current Output. A resistor from this current source output to GND sets the reference voltage used by the error amplifier.                                                                                                                   |

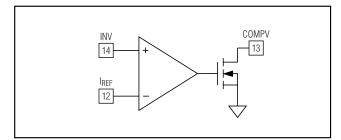

| 13  | COMPV            | Compensation Connection for the Error Amplifier. The feedback optocoupler LED is also connected to this point. This open-drain output is capable of sinking at least 5mA.                                                                             |

| 14  | INV              | Inverting Input of the Error Amplifier. A voltage-divider connected to this input scales the power-supply output voltage for regulation.                                                                                                              |

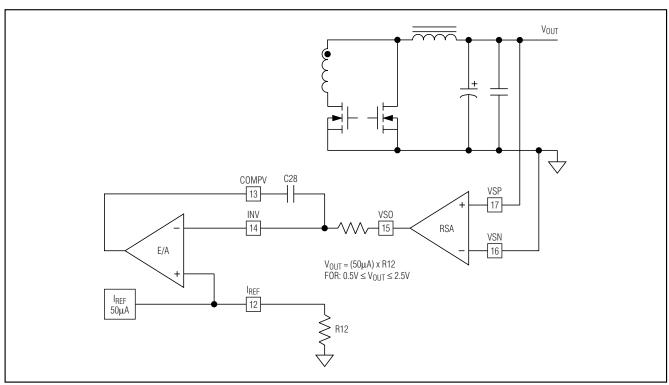

| 15  | VSO              | Output of the Remote-Sense Amplifier                                                                                                                                                                                                                  |

| 16  | VSN              | Negative Input of the Remote-Sense Amplifier. Connect this to the negative terminal of the load.                                                                                                                                                      |

| 17  | VSP              | Positive Input of the Remote-Sense Amplifier. Connect this to the positive terminal of the load.                                                                                                                                                      |

| 18  | CSO              | Output of the Current-Sense Amplifier. It can be used to monitor the output current.                                                                                                                                                                  |

| 19  | CSN              | Connect this input to the negative terminal of the output current-sense resistor. Connect to GND when not used.                                                                                                                                       |

| 20  | CSP              | Connect this input to the positive terminal of the output current-sense resistor. Connect to GND when not used.                                                                                                                                       |

| 21  | VP               | Compensation Pin for Internal +4V Preregulator. A minimum $1\mu F$ low-ESR capacitor must be connected to this pin for bypassing.                                                                                                                     |

| 22  | V+               | Supply Connection for the IC and Input to the Internal 5V (MAX5058) or 10V (MAX5059) Regulator. Maximum voltage on this input is 28V.                                                                                                                 |

| 23  | V <sub>REG</sub> | Regulated +5V (MAX5058) or +10V(MAX5059) Output Used by the Internal Circuitry and the Output Drivers. A minimum 1µF capacitor must be connected to this pin for bypassing.                                                                           |

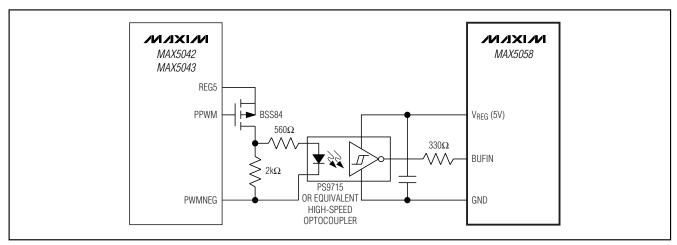

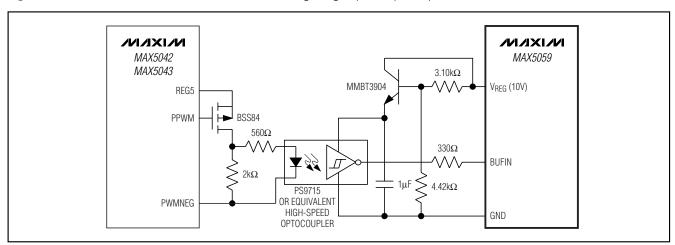

| 24  | BUFIN            | Input for the Synchronizing Pulse. This pulse is provided by the primary-side power IC.                                                                                                                                                               |

| 25  | VDR              | Supply Connection for the Output Drivers. Can be connected to V <sub>REG</sub> for 5V (MAX5058) or 10V (MAX5059) operation.                                                                                                                           |

| 26  | QREC             | Driver Output for the Rectifying MOSFET                                                                                                                                                                                                               |

| 27  | PGND             | Power-Ground Connection. Return ground connection for the gate-driver pulse currents.                                                                                                                                                                 |

| 28  | QSYNC            | Driver Output for the Recirculating MOSFET                                                                                                                                                                                                            |

| _   | EP               | Exposed Pad. This is the exposed pad on the underside of the IC. Connect the exposed paddle to GND and to a large copper ground plane to aid in heat dissipation.                                                                                     |

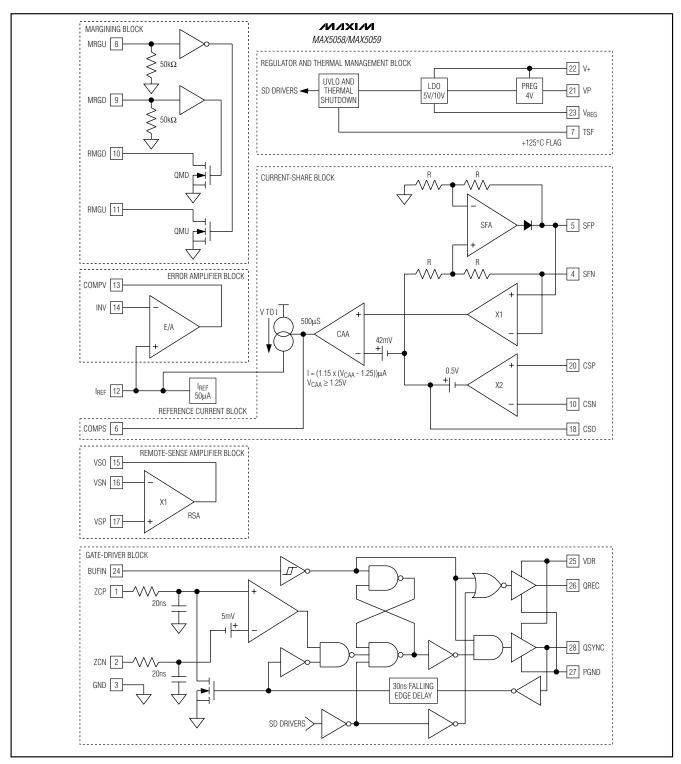

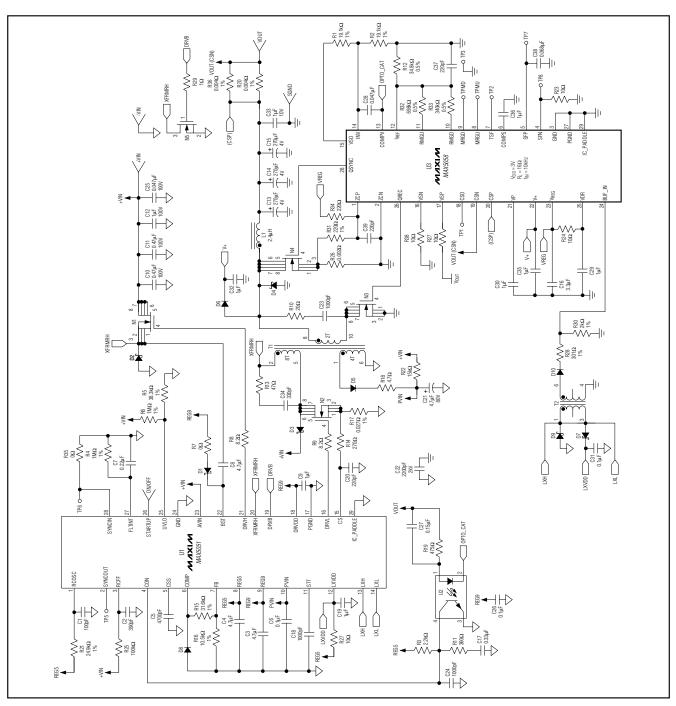

Figure 1. MAX5058/MAX5059 Functional Diagram

#### **Detailed Description**

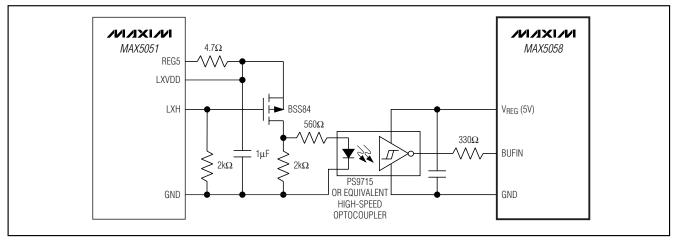

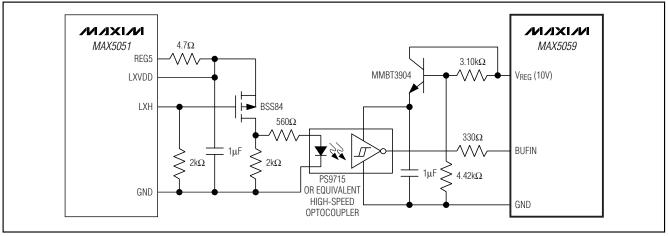

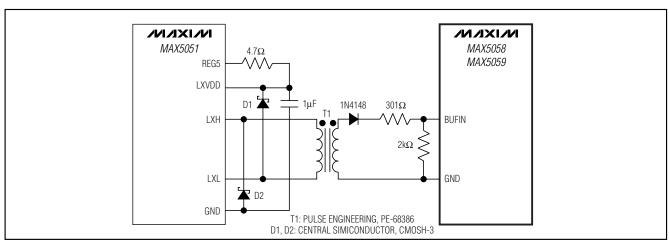

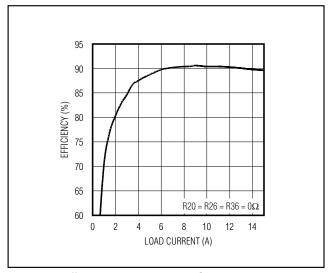

The MAX5058/MAX5059 enable the design of high-efficiency, isolated power supplies using synchronous rectification on the secondary side. These devices commutate the secondary-side MOSFETs by providing a clean gate-drive signal that is synchronized to the power MOSFET switching in the primary side of the isolation transformer. Once fully enhanced, the secondary-side MOSFETs have very low on-resistance, producing a voltage drop much lower than Schottky diodes, resulting in much higher efficiencies. Simultaneous conduction of the synchronous rectifier MOSFETs is avoided by having a look-ahead signal before the primary MOSFETs turn on. This eliminates large current spikes from a shorted transformer secondary.

The MAX5058 has a 5V internal gate-drive voltage regulator that can be used with logic-level MOSFETs. The MAX5059 has a 10V internal gate-drive voltage regulator that can be used with high-gate-voltage MOSFETs.

In addition to the gate drivers, there are blocks that make the MAX5058/MAX5059 complete secondary-side solutions. These blocks are as follows:

- Regulator and thermal-management block

- Buffer input and gate-driver block

- Reference-current block

- Error-amplifier block

- Margining block

- Remote-sense amplifier block

- Current-share block

#### **Regulators and Thermal Management**

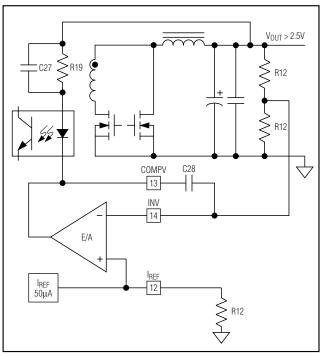

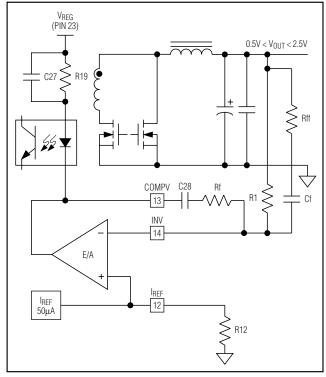

The linear regulators in the MAX5058/MAX5059 provide power for the internal circuitry, as well as power for running the external synchronous MOSFETs. Design is simplified by deriving the power from the secondary winding before the output-filter inductor. The peak voltage at the secondary is at least twice the output voltage, yielding more than 7V peak even for output voltages down to 3.3V. Use a diode and a capacitor to rectify and filter the voltage before applying it to V+ (see D6 and C32 in the Typical Application Circuit). The input for the regulator is V+ and the output is VREG. Connect VDR to VREG to provide the supply for the gate driver's QREC and QSYNC. For logic-level MOSFETs, use the MAX5058. For conventional MOSFETs that require 10V to be fully enhanced, use the MAX5059. The V+ input voltage range is from +4.5V to +28V. Supply enough current to this input to satisfy the guiescent supply current of the MAX5058/MAX5059, as well as the current for the MOSFET drivers. Estimate the total required supply current by using the following formula:

$$I_{V+} = I_{SW} + f_{SW} \times (Q_{N3} + Q_{N4})$$