### **General Description**

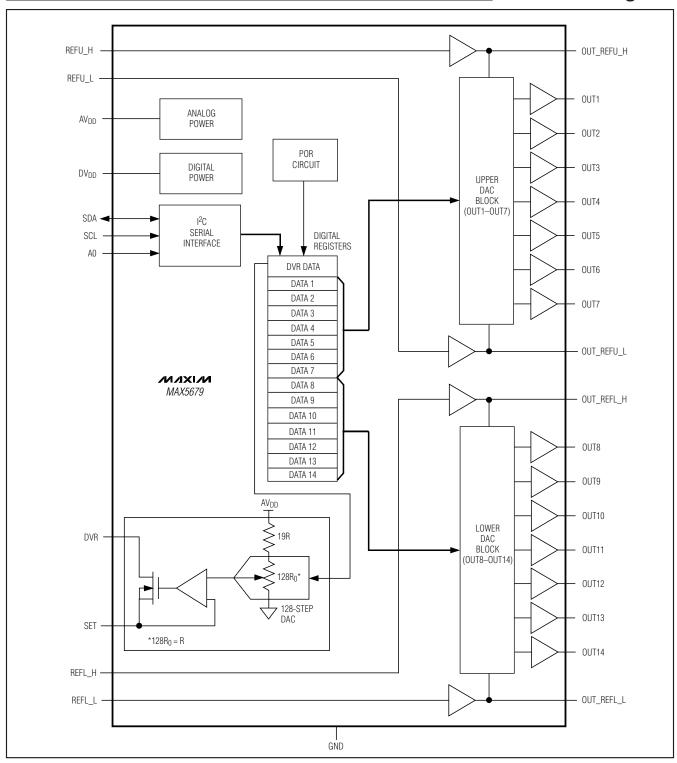

The MAX5679 digitally programmable LCD gamma reference generator provides 18 buffered channels for biasing LCD column drivers. The device provides 14 outputs of 8-bit programmable gamma reference voltage derived from four externally applied reference voltages, and four buffered outputs of the same externally applied reference voltages. An I<sup>2</sup>C serial interface programs the 14 upper and lower range gamma buffer outputs independently.

The MAX5679 features a digitally programmable voltage reference (DVR) with 7-bit adjustable current sink to set the LCD common backplane (VCOM) voltage. The MAX5679 includes a power-on reset (POR) function that configures all 14 programmable gamma outputs to predetermined levels upon initial power-up.

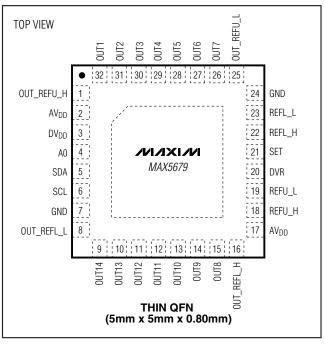

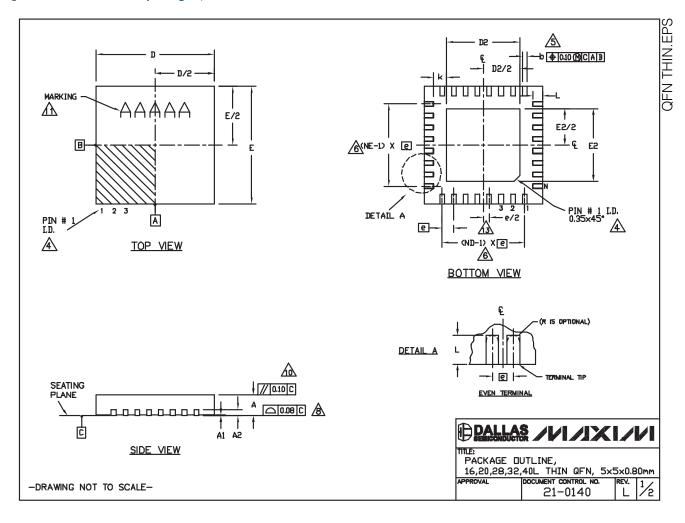

The MAX5679 is available in a 5mm x 5mm, 32-pin TQFN package and is specified over the -40°C to +85°C extended temperature range.

### **Applications**

TFT-LCD Panels for Flat Screen TVs TFT-LCD Panels for Desktop Monitors

## Pin Configuration

### **Features**

- ♦ 7-Bit Adjustable VCOM Calibrator (DVR)

- 14 Programmable Gamma Outputs for LCD Column Driver ICs

8-Bit DAC Resolution for Upper and Lower **Range Outputs**

Maximum Output Swing of (AVDD - 0.2V) (OUT1-OUT7)

Minimum Output Swing of (GND + 0.2V) (OUT8-OUT14)

- **♦** Four Independent Reference Inputs

- **♦ Four Independent Buffered Reference Outputs**

- ♦ 9V to 16.5V Analog Supply

- ♦ 2V to 5.5V Digital Supply

- ♦ 400kHz I<sup>2</sup>C-Compatible Serial Interface

- Pin-Selectable I<sup>2</sup>C Address Bit Allows Two Slave IDs

- ◆ Backward Compatible with the MAX5678

### **Ordering Information**

| PART TEMP RANGE |                | PIN-<br>PACKAGE            | PKG<br>CODE |

|-----------------|----------------|----------------------------|-------------|

| MAX5679ETJ+     | -40°C to +85°C | 32 TQFN-EP*<br>(5mm x 5mm) | T3255+4     |

<sup>+</sup>Denotes a lead-free package.

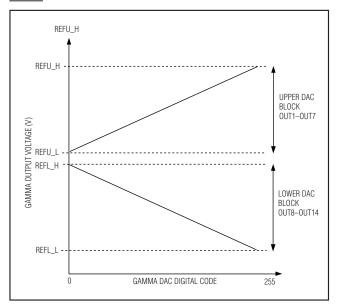

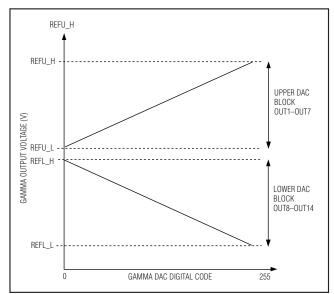

### **Gamma DAC Transfer Function**

Functional Diagram appears at end of data sheet.

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

<sup>\*</sup>EP = Exposed pad.

### **ABSOLUTE MAXIMUM RATINGS**

| AVDD to GND0.3V to +22V DVDD to GND0.3V to +6.0V SET to GND0.3V to +6.0V DVR to GND0.3V to (AVDD + 0.3V) OUT_REF, OUT_ to GND0.3V to (AVDD + 0.3V) REF to GND0.3V to (AVDD + 0.3V) SCL, SDA, A0 to GND0.3V to (DVDD + 0.3V) Maximum Current Into Any Input±50mA Operating Temperature Range40°C to +85°C |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operating Temperature Range40°C to +85°C                                                                                                                                                                                                                                                                 |

| Storage Temperature Range65                                                                         | 5°C to +150°C |

|-----------------------------------------------------------------------------------------------------|---------------|

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )                                               |               |

| 32-Pin TQFN (derate 21mW/°C above +70°C)                                                            | 1700mW        |

| Lead temperature (soldering, 10s)                                                                   | +300°C        |

| Junction Temperature                                                                                | +150°C        |

| ESD Protection                                                                                      |               |

| SCL, SDA to GND, DV <sub>DD</sub> (Human Body Model)<br>All Other Pins (Human Body Model, JESD22-A1 |               |

|                                                                                                     |               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(AV_{DD} = 9V \text{ to } 16.5V, DV_{DD} = 2V \text{ to } 5.5V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}\text{C.})$  (Note 1)

| PARAMETER                      | SYMBOL | CONDITIONS                                                       | MIN                             | TYP   | MAX                             | UNITS   |

|--------------------------------|--------|------------------------------------------------------------------|---------------------------------|-------|---------------------------------|---------|

| GAMMA OUTPUTS                  |        |                                                                  |                                 |       |                                 |         |

| DAC Resolution                 |        |                                                                  | 8                               |       |                                 | Bits    |

| Differential Nonlinearity      |        |                                                                  |                                 | ±0.05 | ±1                              | LSB     |

| Integral Nonlinearity          |        |                                                                  |                                 |       | ±2                              | LSB     |

|                                |        | OUT1                                                             |                                 | 246D  |                                 |         |

|                                |        | OUT2                                                             |                                 | 148D  |                                 |         |

|                                |        | OUT3                                                             |                                 | 118D  |                                 |         |

|                                |        | OUT4                                                             |                                 | 87D   |                                 |         |

|                                |        | OUT5                                                             |                                 | 67D   |                                 |         |

|                                |        | OUT6                                                             |                                 | 55D   |                                 |         |

| Power-On Reset (POR)           |        | OUT7                                                             |                                 | 7D    |                                 | Decimal |

| Gamma Codes                    |        | OUT8                                                             |                                 | 7D    |                                 | Decimai |

|                                |        | OUT9                                                             |                                 | 55D   |                                 |         |

|                                |        | OUT10 67D                                                        |                                 |       |                                 |         |

|                                |        | OUT11 87D                                                        |                                 |       |                                 |         |

|                                |        | OUT12                                                            |                                 | 118D  |                                 |         |

|                                |        | OUT13                                                            |                                 | 148D  |                                 |         |

|                                |        | OUT14                                                            |                                 | 246D  |                                 |         |

| Absolute Accuracy              |        | (Note 2)                                                         |                                 | ±13   | ±70                             | mV      |

| Channel-to-Channel<br>Matching |        | (Note 2)                                                         |                                 | ±18   | ±70                             | mV      |

|                                |        | OUTREFU_H, I <sub>OUT</sub> = I10mAl                             | 1/2 x AV <sub>DD</sub><br>- 0.5 |       | AV <sub>DD</sub> - 0.2          |         |

| Gamma Output Voltage           |        | OUT1-OUT7, OUTREFU_L,<br>IOUT = I20mAl                           | 1/2 x AV <sub>DD</sub><br>+ 0.5 |       | AV <sub>DD</sub> - 0.5          |         |

| Range (Note 3)                 |        | OUTREFL_L, I <sub>OUT</sub> = I10mAl                             | GND + 0.2                       |       | 1/2 x AV <sub>DD</sub><br>+ 0.5 | V       |

|                                |        | OUTREFL_H, OUT8-OUT14,<br>I <sub>OUT</sub> = I <sub>2</sub> 0mAl | GND + 0.5                       |       | 1/2 x AV <sub>DD</sub><br>+ 0.5 |         |

2 \_\_\_\_\_\_ *NIXIN*

### **ELECTRICAL CHARACTERISTICS (continued)**

$(AV_{DD} = 9V \text{ to } 16.5V, DV_{DD} = 2V \text{ to } 5.5V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $T_A = +25^{\circ}\text{C}$ .) (Note 1)

| PARAMETER                          | SYMBOL            | CONDITIONS                                                                         | MIN T                           | ΥP  | MAX                          | UNITS            |  |

|------------------------------------|-------------------|------------------------------------------------------------------------------------|---------------------------------|-----|------------------------------|------------------|--|

| Stability                          |                   | $R_S = 0\Omega$ , no sustained oscillations                                        | 200                             |     |                              | рF               |  |

| Ol D-t-                            | CD                | OUT1-OUT14, REFU_L, REFL_H, no load                                                |                                 | 15  |                              | \// <sub>1</sub> |  |

| Slew Rate                          | SR                | REFU_H, REFL_L, no load                                                            |                                 | 10  |                              | V/µs             |  |

|                                    |                   | OUTREFU_H, I <sub>OUT</sub> = ±10mA,<br>V <sub>OUT</sub> = AV <sub>DD</sub> - 0.2V | :                               | ±5  |                              |                  |  |

|                                    | .,                | OUT1-OUT7, OUTREFU_L,<br>IOUT = ±20mA, V <sub>OUT</sub> = AV <sub>DD</sub> - 0.5V  | :                               | ±5  |                              | ]                |  |

| Load Regulation                    | VREG              | OUT7-OUT14, OUTREFL_H,<br>IOUT = ±20mA, V <sub>OUT</sub> = GND + 0.5V              | :                               | ±5  |                              | mV               |  |

|                                    |                   | OUTREFL_L, I <sub>OUT</sub> = ±10mA,<br>V <sub>OUT</sub> = GND + 0.2V              | -                               | ±5  |                              |                  |  |

|                                    |                   | OUT1-OUT14, V <sub>OUT</sub> = AV <sub>DD</sub> /2                                 | ±:                              | 200 |                              |                  |  |

| Output Short-Circuit<br>Current    |                   | OUTREFU_L, OUTREFL_H, OUTREFL_L, VOUT_ = AVDD/2                                    | ±200                            |     |                              | mA               |  |

| Current                            |                   | OUTREFU_H sourcing                                                                 | 2                               | 200 |                              |                  |  |

|                                    |                   | OUTREFU_H sinking                                                                  | 20                              |     |                              |                  |  |

| Gamma Output Load                  | RL                | Referenced to nominal DC output voltage                                            | 10                              | 000 |                              | Ω                |  |

| Gamma Output Load                  |                   | Referenced to nominal DC output voltage                                            | 2                               | 200 |                              | рF               |  |

| Capacitance                        |                   | $R_S = 5\Omega$ (Note 4)                                                           |                                 | 1   |                              | μF               |  |

| REFU_H, REFU_L, REF                | L_H, REFL_I       | <u>L</u>                                                                           |                                 |     |                              |                  |  |

| Input Voltage Range                |                   | REFU_H, REFU_L                                                                     | AV <sub>DD</sub> /2<br>+ 0.5    |     | $AV_{DD}$                    | V                |  |

| input voitage hange                |                   | REFL_H, REFL_L                                                                     | GND AV <sub>DD</sub> /2 + 0.5   |     | AV <sub>DD</sub> /2<br>+ 0.5 | V                |  |

| Input Resistance                   | R <sub>IN</sub>   | Measured from V <sub>REF</sub> _ to GND                                            | 3                               | 3.3 |                              | МΩ               |  |

| Input Current                      | I <sub>IN</sub>   | Measured from V <sub>REF</sub> to GND with V <sub>REF</sub> = +16.5V               |                                 | 5   |                              | μА               |  |

| Reference Feedthrough<br>Bandwidth | BW <sub>REF</sub> | From any REF input to any reference or gamma output                                |                                 | 40  |                              | kHz              |  |

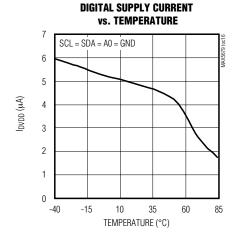

| VCOM CALIBRATOR (D                 | VR)               |                                                                                    |                                 |     |                              |                  |  |

| Power-On Reset<br>VCOM Code        |                   |                                                                                    |                                 |     | 64                           | Decimal          |  |

| Adjustment Steps                   |                   | (Note 5)                                                                           |                                 |     | 125                          | Steps            |  |

| SET Current                        |                   | (Note 6)                                                                           | 20 250                          |     | μΑ                           |                  |  |

| SET External                       |                   | To GND, AV <sub>DD</sub> = 16.5V                                                   | ), AV <sub>DD</sub> = 16.5V 3.3 |     |                              | kΩ               |  |

| Resistance (Note 6)                |                   | To GND, AV <sub>DD</sub> = 9V                                                      | -                               | 1.8 |                              | K77              |  |

| SET Maximum External Capacitance   |                   |                                                                                    | 30                              |     |                              | pF               |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(AV_{DD} = 9V \text{ to } 16.5V, DV_{DD} = 2V \text{ to } 5.5V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.}$  Typical values are at  $T_A = +25^{\circ}C.$ ) (Note 1)

| PARAMETER                                    | SYMBOL             | CONDITIONS                                            | MIN                    | TYP                        | MAX       | UNITS |

|----------------------------------------------|--------------------|-------------------------------------------------------|------------------------|----------------------------|-----------|-------|

| SET Differential<br>Nonlinearity             |                    |                                                       |                        |                            | ±0.5      | LSB   |

| SET Zero-Scale Error                         |                    |                                                       |                        | ±2                         | ±21       | mV    |

| V <sub>SET</sub> /AV <sub>DD</sub> Ratio     |                    | DAC at full scale                                     |                        | 0.05                       |           | V/V   |

| V <sub>SET</sub> /AV <sub>DD</sub> Ratio POR |                    | At power-up                                           |                        | 0.0254                     |           | V/V   |

| DVR Compliance Range                         |                    | DVR compliance measured at midscale                   | V <sub>SET</sub> + 0.5 |                            | $AV_{DD}$ | V     |

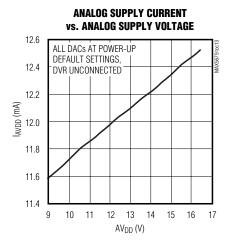

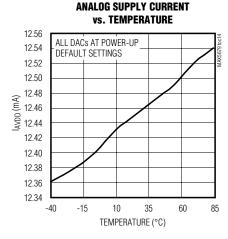

| POWER SUPPLY                                 |                    |                                                       |                        |                            |           |       |

| Analog Supply Voltage                        | $AV_{DD}$          | (Note 7)                                              | 9.0                    |                            | 16.5      | V     |

| AV <sub>DD</sub> High-Voltage<br>Stress      |                    | (Note 7)                                              |                        |                            | 20        | V     |

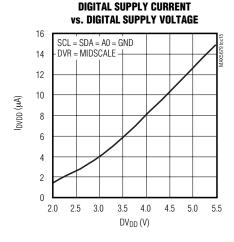

| Digital Supply Voltage                       | DV <sub>DD</sub>   |                                                       | 2.0                    | 3.3                        | 5.5       | V     |

| Analog Supply Current                        | Is                 |                                                       |                        | 12.5                       | 18        | mA    |

| Digital Supply Current                       | I <sub>SD</sub>    |                                                       |                        | 0.01                       | 1         | mA    |

| DIGITAL INPUTS (A0, S                        | DA, SCL)           |                                                       |                        |                            |           |       |

| Input-Logic High<br>Voltage                  | VIH                |                                                       |                        | 0.7 x<br>DV <sub>DD</sub>  |           | V     |

| Input-Logic Low<br>Voltage                   | VIL                |                                                       |                        | 0.3 x<br>DV <sub>DD</sub>  |           | V     |

| Input Leakage Current                        | I <sub>IN</sub>    | V <sub>IN</sub> = 0 or DV <sub>DD</sub>               |                        | ±0.1                       | ±1        | μA    |

| Input Hysteresis                             | V <sub>H</sub> YST |                                                       |                        | 0.05 x<br>DV <sub>DD</sub> |           | V     |

| Input Capacitance                            | CIN                |                                                       |                        | 6                          |           | pF    |

| SDA Output-Logic<br>Low Voltage              | Vol                | ISINK = 3mA                                           |                        |                            | 0.4       | V     |

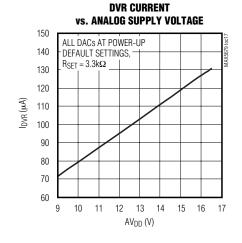

| SERIAL-INTERFACE TII                         | VING               |                                                       | •                      |                            |           |       |

| Serial-Clock Frequency                       | fscl               |                                                       |                        |                            | 400       | kHz   |

| Bus Free Time                                | tBUF               | Between STOP and START                                | 1.3                    |                            |           | μs    |

| REPEATED START<br>Hold Time                  | tHD:STA            | After this period, the first clock pulse is generated | 0.6                    |                            |           | μs    |

| SCL Pulse-Width Low                          | tLOW               |                                                       | 1.3                    |                            |           | μs    |

| SCL Pulse-Width High                         | tHIGH              |                                                       | 0.6                    |                            |           | μs    |

| REPEATED START<br>Setup Time                 | tsu:sta            |                                                       | 0.6                    |                            |           | μs    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(AV_{DD} = 9V \text{ to } 16.5V, DV_{DD} = 2V \text{ to } 5.5V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}\text{C.})$  (Note 1)

| PARAMETER                       | SYMBOL          | CONDITIONS                        | MIN           | TYP | MAX | UNITS |

|---------------------------------|-----------------|-----------------------------------|---------------|-----|-----|-------|

| Data Hold Time                  | thd;dat         |                                   | 0             |     | 900 | ns    |

| Data Setup Time                 | tsu;dat         |                                   | 100           |     |     | ns    |

| SDA/SCL Receiving<br>Rise Time  | t <sub>r</sub>  |                                   | 20 +<br>Cb/10 |     | 300 | ns    |

| SDA/SCL Receiving<br>Fall Time  | tf              |                                   | 20 +<br>Cb/10 |     | 300 | ns    |

| SDA Transmitting<br>Fall Time   | tf              |                                   | 20 +<br>Cb/10 |     | 250 | ns    |

| STOP Setup Time                 | tsu;sto         |                                   | 0.6           |     |     | μs    |

| Ruo Consoitanos                 | C.              | $DV_{DD} = 2V \text{ to } 2.7V$   | 10            |     | 100 | n F   |

| Bus Capacitance                 | C <sub>b</sub>  | $DV_{DD} = 2.7V \text{ to } 5.5V$ | 10            |     | 400 | pF    |

| Suppressed Spike<br>Pulse Width | t <sub>sp</sub> |                                   |               | 50  |     | ns    |

- Note 1: Specifications at T<sub>A</sub> = +85°C are guaranteed by production testing. Specifications at T<sub>A</sub> = -40°C and T<sub>A</sub> = +25°C are guaranteed by design and characterization.

- Note 2: Error from the ideal output defined by the transfer function in the Gamma DAC Transfer Functions section.

- Note 3: Due to power dissipation limits, not all outputs can source/sink IOUT (max) simultaneously.

- Note 4: Rs is a series resistor between the amplifier output and CL. The amplifier should be stable under this condition.

- Note 5: The lower three codes, 0–2, are hardwired to give the same value as code two. This eliminates a zero-current condition in the DVR output.

- Note 6: Keep the minimum current into DVR > 10μA, and maximum current into DVR < 250μA over all codes.

- Note 7: AVDD > 20V is a stress test. Functionality and spec compliance not guaranteed above 16.5V.

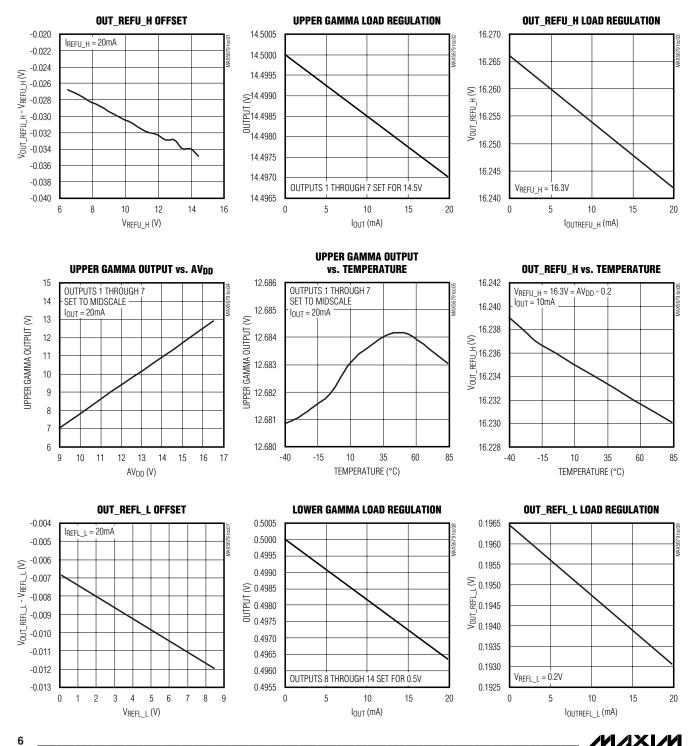

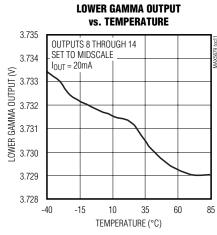

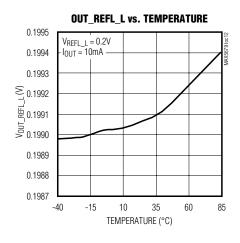

### Typical Operating Characteristics

(AV<sub>DD</sub> = +16.5V, DV<sub>DD</sub> = +3.3V, performance of the *Typical Operating Circuit*, T<sub>A</sub> = +25°C, unless otherwise noted.)

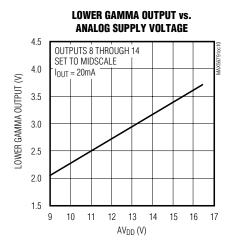

### \_Typical Operating Characteristics (continued)

(AV<sub>DD</sub> = +16.5V, DV<sub>DD</sub> = +3.3V, performance of the *Typical Operating Circuit*, T<sub>A</sub> = +25°C, unless otherwise noted.)

## **Pin Description**

| PIN   | NAME             | FUNCTION                                                                                                                                          |  |  |  |  |

|-------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1     | OUT_REFU_H       | Analog Output. Upper gamma reference high output.                                                                                                 |  |  |  |  |

| 2, 17 | AV <sub>DD</sub> | Analog Power Supply                                                                                                                               |  |  |  |  |

| 3     | DV <sub>DD</sub> | Digital Power Supply                                                                                                                              |  |  |  |  |

| 4     | A0               | Address Bit 0                                                                                                                                     |  |  |  |  |

| 5     | SDA              | Serial-Data Input                                                                                                                                 |  |  |  |  |

| 6     | SCL              | Serial-Clock Input                                                                                                                                |  |  |  |  |

| 7, 24 | GND              | Ground                                                                                                                                            |  |  |  |  |

| 8     | OUT_REFL_L       | Lower Gamma Reference Low Output                                                                                                                  |  |  |  |  |

| 9     | OUT14            | Gamma Reference 14 Output                                                                                                                         |  |  |  |  |

| 10    | OUT13            | Gamma Reference 13 Output                                                                                                                         |  |  |  |  |

| 11    | OUT12            | Gamma Reference 12 Output                                                                                                                         |  |  |  |  |

| 12    | OUT11            | Gamma Reference 11 Output                                                                                                                         |  |  |  |  |

| 13    | OUT10            | Gamma Reference 10 Output                                                                                                                         |  |  |  |  |

| 14    | OUT9             | Gamma Reference 9 Output                                                                                                                          |  |  |  |  |

| 15    | OUT8             | Gamma Reference 8 Output                                                                                                                          |  |  |  |  |

| 16    | OUT_REFL_H       | Lower Gamma Reference High Output                                                                                                                 |  |  |  |  |

| 18    | REFU_H           | Upper Reference High Input                                                                                                                        |  |  |  |  |

| 19    | REFU_L           | Upper Reference Low Input                                                                                                                         |  |  |  |  |

| 20    | DVR              | Sink Current Output                                                                                                                               |  |  |  |  |

| 21    | SET              | Sink Current Set                                                                                                                                  |  |  |  |  |

| 22    | REFL_H           | Lower Reference High Input                                                                                                                        |  |  |  |  |

| 23    | REFL_L           | Lower Reference Low Input                                                                                                                         |  |  |  |  |

| 25    | OUT_REFU_L       | Upper Gamma Reference Low Output                                                                                                                  |  |  |  |  |

| 26    | OUT7             | Gamma Reference 7 Output                                                                                                                          |  |  |  |  |

| 27    | OUT6             | Gamma Reference 6 Output                                                                                                                          |  |  |  |  |

| 28    | OUT5             | Gamma Reference 5 Output                                                                                                                          |  |  |  |  |

| 29    | OUT4             | Gamma Reference 4 Output                                                                                                                          |  |  |  |  |

| 30    | OUT3             | Gamma Reference 3 Output                                                                                                                          |  |  |  |  |

| 31    | OUT2             | Gamma Reference 2 Output                                                                                                                          |  |  |  |  |

| 32    | OUT1             | Gamma Reference 1 Output                                                                                                                          |  |  |  |  |

| _     | EP               | Exposed Pad. Internally connected to GND. Connect to large ground plane for maximum thermal dissipation. Do not use as primary ground connection. |  |  |  |  |

\_\_\_\_\_\_*NIXI/N*

### **Detailed Description**

The MAX5679 provides 18 buffered outputs for biasing LCD column drivers. Fourteen outputs are 8-bit programmable voltages derived from four externally applied reference voltages, and four are buffered outputs of the externally applied reference voltages. Additionally, the MAX5679 features a DVR, using a 7-bit adjustable current sink to set the VCOM voltage.

The MAX5679 includes a POR function that configures all programmable outputs to predetermined levels upon initial power-up. See the *Power-On Reset* section for more information.

An I<sup>2</sup>C serial interface programs the internal DACs to set the 14 upper/lower range gamma buffer outputs and DVR's sink current.

#### I<sup>2</sup>C Serial Interface

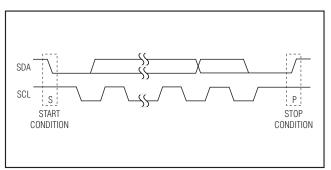

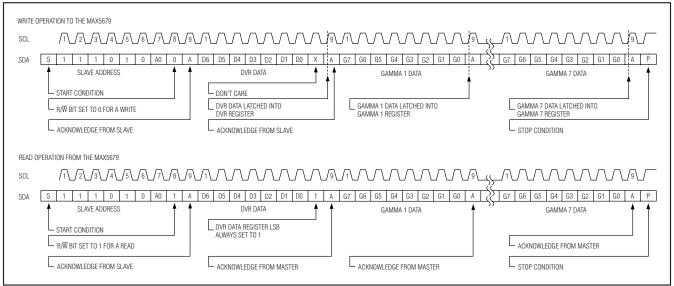

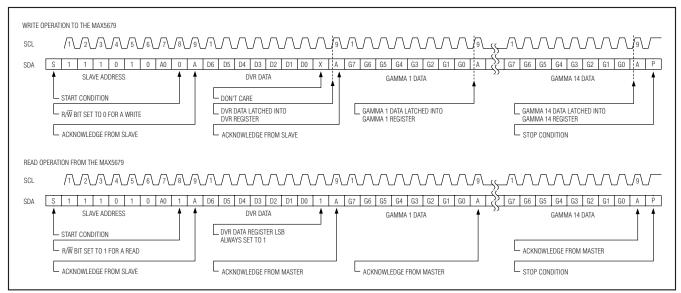

The MAX5679 operates as an I<sup>2</sup>C slave device that sends and receives data through an I<sup>2</sup>C-compatible 2-wire interface. The interface uses a serial-data line (SDA) and a serial-clock line (SCL) to achieve bidirectional communication between master(s) and slave(s). A master (typically a microcontroller) initiates all data transfers to and from the MAX5679 and generates the SCL clock that synchronizes the data transfer (Figure 1). A slave issues an acknowledge bit after it recognizes its address and again after each data byte is read and recognized.

SDA operates as both an input and an open-drain output. Install a pullup resistor, Rp, between SDA and DVDD. The value of Rp depends on the DVDD supply voltage and bus capacitance. SCL operates only as an input. Install a pullup resistor, RpC, on SCL if there are multiple masters on the 2-wire interface, or if the master

Figure 1. I<sup>2</sup>C 2-Wire Serial-Interface Timing Details

in a single-master system has an open-drain SCL output. Each communication with the MAX5679 contains a START (S) condition sent by a master, the 7-bit MAX5679 slave address plus a read/write (R/W) bit, an acknowledge bit, a series of data bytes each followed by an acknowledge bit, and finally a STOP (P) condition. Figure 2 shows how each communication is framed by START and STOP conditions.

#### START and STOP Conditions

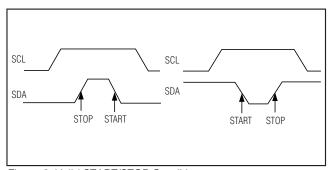

Both SCL and SDA remain high when the interface is not busy. A master signals the beginning of a transmission with a START condition by transitioning SDA from high to low while SCL is high. When the master has finished communicating with the slave, it issues a STOP condition by transitioning SDA from low to high while SCL is high. The bus is then free for another transmission (Figure 1).

### Early STOP Conditions

The MAX5679 recognizes a STOP condition at any point in a transmission even when the STOP condition occurs in the same SCL high pulse as the START condition (Figure 3).

Figure 2. START and STOP Conditions

#### REPEATED START (Sr) Conditions

A REPEATED START (Sr) condition on the bus is when a START condition occurs without a prior STOP condition. An Sr condition terminates any previous operation on the bus, and should be followed by the slave address, which starts a new session. Usually Sr is issued after the acknowledge bit. Issuing Sr in between acknowledge bits prevents completion of the ongoing byte transmission.

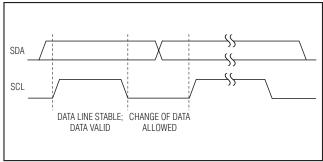

#### Bit Transfer

One data bit is transferred during each clock pulse. The data on SDA must remain stable while SCL is high (Figure 4).

Figure 3. Valid START/STOP Conditions

Figure 4. Bit Transfer

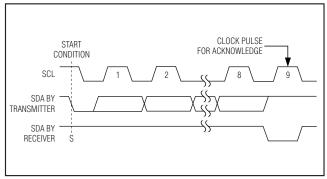

#### Acknowledge

The acknowledge bit is a clocked 9th bit that the recipient uses to signal the receipt of its address and each byte of data (Figure 5). Each byte transferred thus effectively requires nine clock pulses. The master generates the 9th clock pulse, and the recipient pulls down SDA during the acknowledge clock pulse, ensuring the SDA line is stable low during the high period of the clock pulse. When the master is transmitting to the MAX5679, the device generates the acknowledge bit because the MAX5679 is the recipient. When the MAX5679 is transmitting to the master, the master generates the acknowledge bit because the master is the recipient. If the master fails to provide an acknowledge bit during a read from the MAX5679, the MAX5679 interface ceases to provide data and waits for a new START condition and a valid address. Not acknowledging by the master is a legitimate way to terminate reading from the MAX5679; no STOP condition is necessary afterwards.

Figure 5. Acknowledge

### I<sup>2</sup>C Compatibility

The MAX5679 is fully compatible with existing I<sup>2</sup>C systems. The interface supports both standard (100kHz) and fast (400kHz) data-transfer modes. The MAX5679 does not respond to a general call address.

#### Slave Address

The MAX5679 has a 7-bit long slave address (Table 1). The 8th bit following the 7-bit slave address is the R/W bit. The R/W bit is low for a write command or high for a read command.

Bits B7 through B2 of the MAX5679 slave address are set to 111010. Address input, A0, controls the slave address bit, B1. Connect A0 to DV<sub>DD</sub> or GND. The MAX5679 provides two possible slave addresses (Table 1). An interface can control two MAX5679 devices independently.

The address input A0 can be driven dynamically. Ensure that the bit value is stable in the address sequence. The MAX5679 interface compares each address value bit-by-bit to allow the interface to power down in the event of a bus cycle that does not address the MAX5679.

#### Write Data Format

Send a START condition followed by the 7-bit slave address of the device with the R/W bit reset to 0 and one or more data bytes to initiate a write command. The MAX5679 supports two timing modes referred to as

### **Table 1. Slave Address**

| В7 | В6 | B5 | B4 | В3 | B2 | B1 | В0  |

|----|----|----|----|----|----|----|-----|

| 1  | 1  | 1  | 0  | 1  | 0  | Α0 | R/W |

mode 1 and mode 2. See Figures 6a and 6b. In mode 1, the data received by the MAX5679 consists of 9 bytes defined as follows: slave address, DVR data, and gamma 1 data though gamma 7 data. The DVR data is stored in the DVR DAC register, while the gamma data is stored in the gamma DAC registers as defined in Table 2a. A STOP condition after gamma 7 data is received determines the mode to be mode 1 (MAX5678 compatible mode).

If no STOP condition is detected after gamma 7 data and additional data are received, the mode is determined to be mode 2. In mode 2, additional data is sent in the form of gamma 8 data through gamma 14 data. After the gamma 14 data is received a STOP condition should be asserted by the master. The data received after gamma 7 data (i.e. gamma 8 data through gamma 14 data) is stored in the gamma DAC registers according to Table 2b.

Figure 6a, Mode 1 (MAX5678 Compatible Mode)

Figure 6b. Mode 2

Table 2a. Mode 1 (MAX5678 Compatible Mode)

| •                  | ,          |                  |                              |

|--------------------|------------|------------------|------------------------------|

| GAMMA<br>DATA BYTE | _          | PERATION<br>STER | READ OPERATION REGISTER READ |

| 1                  | Register 1 | Register 14      | Register 1                   |

| 2                  | Register 2 | Register 13      | Register 2                   |

| 3                  | Register 3 | Register 12      | Register 3                   |

| 4                  | Register 4 | Register 11      | Register 4                   |

| 5                  | Register 5 | Register 10      | Register 5                   |

| 6                  | Register 6 | Register 9       | Register 6                   |

| 7                  | Register 7 | Register 8       | Register 7                   |

#### Read Data Format

Send a START condition followed by the 7-bit slave address of the device with the R/W bit set to 1 to initiate a read command to the MAX5679. The MAX5679 then sequentially outputs 8 bytes of data if operating in mode 1 or 15 bytes if in mode 2 that correspond to the values stored in its internal registers. The first data byte represents the contents of the DVR register. The following 7 or 14 bytes of data represent the gamma DAC settings.

### **DVR Register**

The DVR register stores the 1st data byte transmitted to the MAX5679 following a START condition and the device slave address when a write operation is performed (Figures 6a and 6b). The DVR register sets the code for the DVR DAC and controls the operation of the SET and DVR outputs. The DVR DAC is a 7-bit DAC with the least significant bit (LSB) of this register as a don't-care bit (Table 3). When performing a read from the MAX5679, the DVR register data is the first byte to be output by the device following a START condition and the slave address. A read from the DVR register always returns an LSB value of 1.

### Gamma Register

The MAX5679 includes a total of 14 gamma registers that store the digital codes for the gamma DACs, which control outputs OUT1-OUT14. When writing to the MAX5679, the first data byte transmitted after the DVR data is stored in the first gamma register and subsequent bytes of data are stored in the remaining gamma registers until either seven or all 14 have been written, depending on the mode (Tables 2a and 2b). Each gamma register controls an upper and a lower DAC output. The upper and lower DACs share the same digital code in mode 1. See the *Gamma DAC Transfer*

Table 2b. Mode 2

| GAMMA<br>REGISTER<br>BYTE | WRITE OPERATION<br>REGISTER DATA<br>STORED | READ OPERATION<br>REGISTER DATA<br>READ |  |  |

|---------------------------|--------------------------------------------|-----------------------------------------|--|--|

| 1                         | Data 1                                     | Data 1                                  |  |  |

| 2                         | Data 2                                     | Data 2                                  |  |  |

| 3                         | Data 3                                     | Data 3                                  |  |  |

| 4                         | Data 4                                     | Data 4                                  |  |  |

| 5                         | Data 5                                     | Data 5                                  |  |  |

| 6                         | Data 6                                     | Data 6                                  |  |  |

| 7                         | Data 7                                     | Data 7                                  |  |  |

| 8                         | Data 8                                     | Data 8                                  |  |  |

| 9                         | Data 9                                     | Data 9                                  |  |  |

| 10                        | Data 10                                    | Data 10                                 |  |  |

| 11                        | Data 11                                    | Data 11                                 |  |  |

| 12                        | Data 12                                    | Data 12                                 |  |  |

| 13                        | Data 13                                    | Data 13                                 |  |  |

| 14                        | Data 14                                    | Data 14                                 |  |  |

Functions section. When a read from the MAX5679 is performed, the contents of the gamma registers are output sequentially after the DVR register data (Figures 6a and 6b). If the MAX5679 is operating in mode 1, issue a stop condition after receiving the 7th gamma byte. If the device is operating in mode 2, issue a stop condition after receiving the 14th gamma byte.

#### Register Update

The registers of the MAX5679 are updated on the rising edge of SCL during the acknowledge bit. All bus cycles require each 8-bit byte to be followed by an acknowledge bit. If a write sequence is aborted before its respective acknowledge bit, the data values are not updated and the MAX5679 waits for a new START condition and a valid slave address. For the MAX5679, a write operation from the master may contain additional data beyond what is required to program all the internal registers. In this situation, the MAX5679 ignores any data beyond the 15th data byte (DVR plus 14 gamma bytes). The MAX5679 also accepts write commands with fewer than 8 bytes. In this case, the number of reqisters that are updated corresponds to the number of bytes sent. If there are more registers than bytes sent, the remaining registers contain their previous values. If multiple write operations are performed by the master, each operation is performed on the MAX5679 data registers as requested.

#### Power-On Reset

On power-up, all internal registers of the MAX5679 (DVR register and 14 gamma registers) are initiated to a preset series of values (Table 3). Use the I<sup>2</sup>C interface to overwrite these values at any point after initial power-up.

### Applications Information

### **Digital Variable Reference (DVR)**

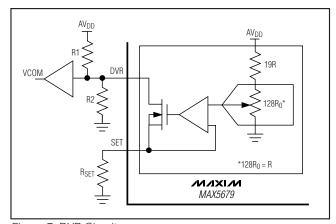

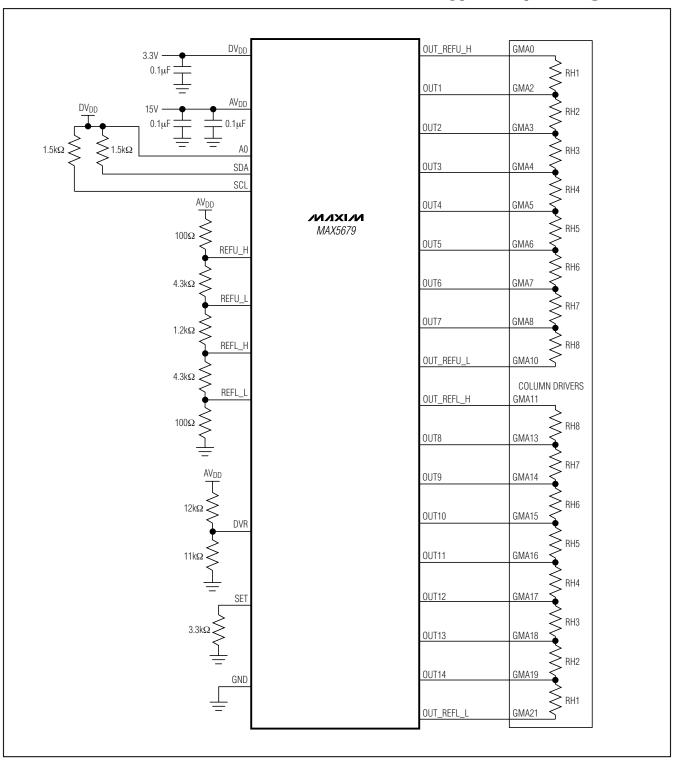

DVR sinks a programmable current set by an internal 7-bit DAC from an external resistive voltage-divider. The DAC is ratiometric relative to AV<sub>DD</sub> and monotonic over all operating conditions. The combination of the resistive voltage-divider (R1 and R2), the external SET resistor (RSET), and the AV<sub>DD</sub> supply determine the maximum and minimum values of the DVR output (Figure 7).

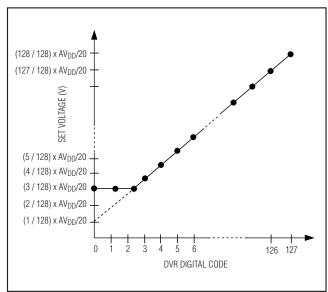

### **DVR DAC Transfer Function and Offset**

An I<sup>2</sup>C interface controls the DVR 7-bit DAC through the DVR register. The DVR DAC determines the voltage at SET as well as the current that DVR can sink. Figure 7 shows the transfer function of the DVR DAC. Calculate the voltage at SET with the following sequation:

$$V_{SET} = \left\{ \frac{DVR\_Code + 1}{128} \right\} \times \left( \frac{AV_{DD}}{20} \right)$$

where DVR\_Code is any integer from 0 to 127. The DVR DAC provides two codes of offset by making the first three DVR codes correspond to the same SET voltage (Figure 8). DVR codes 0, 1, and 2 yield the same output voltage as if DVR code 2 is written to the DVR DAC. The previous equation is valid for codes 2 to 127. For DVR codes 0 to 2, calculate SET voltage with the following equation:

$$V_{SET} = \left\{ \frac{3}{128} \right\} \times \left( \frac{AV_{DD}}{20} \right)$$

Figure 7. DVR Circuit

### Table 3. Power-On Reset Values

| DEGISTED | OUTDUT  | POWER-ON RESET VALUE |    |    |    |    |    |    |    |               |

|----------|---------|----------------------|----|----|----|----|----|----|----|---------------|

| REGISTER | OUTPUT  | B7                   | В6 | B5 | B4 | В3 | B2 | B1 | В0 | DECIMAL VALUE |

| DVR      | SET/DVR | 1                    | 0  | 0  | 0  | 0  | 0  | 0  | Х  | 64            |

| Gamma 1  | OUT1    | 1                    | 1  | 1  | 1  | 0  | 1  | 1  | 0  | 246           |

| Gamma 2  | OUT2    | 1                    | 0  | 0  | 1  | 0  | 1  | 0  | 0  | 148           |

| Gamma 3  | OUT3    | 0                    | 1  | 1  | 1  | 0  | 1  | 1  | 0  | 118           |

| Gamma 4  | OUT4    | 0                    | 1  | 0  | 1  | 0  | 1  | 1  | 1  | 87            |

| Gamma 5  | OUT5    | 0                    | 1  | 0  | 0  | 0  | 0  | 1  | 1  | 67            |

| Gamma 6  | OUT6    | 0                    | 0  | 1  | 1  | 0  | 1  | 1  | 1  | 55            |

| Gamma 7  | OUT7    | 0                    | 0  | 0  | 0  | 0  | 1  | 1  | 1  | 7             |

| Gamma 8  | OUT8    | 0                    | 0  | 0  | 0  | 0  | 1  | 1  | 1  | 7             |

| Gamma 9  | OUT9    | 0                    | 0  | 1  | 1  | 0  | 1  | 1  | 1  | 55            |

| Gamma 10 | OUT10   | 0                    | 1  | 0  | 0  | 0  | 0  | 1  | 1  | 67            |

| Gamma 11 | OUT11   | 0                    | 1  | 0  | 1  | 0  | 1  | 1  | 1  | 87            |

| Gamma 12 | OUT12   | 0                    | 1  | 1  | 1  | 0  | 1  | 1  | 0  | 118           |

| Gamma 13 | OUT13   | 1                    | 0  | 0  | 1  | 0  | 1  | 0  | 0  | 148           |

| Gamma 14 | OUT14   | 1                    | 1  | 1  | 1  | 0  | 1  | 1  | 0  | 246           |

X = Don't care.

14 \_\_\_\_\_\_\_/VIXI/VI

### **Setting the DVR Adjustment Range (RSET)**

An external resistive divider (R1 and R2) in conjuction with RSET, set DVR's adjustment range (Figure 7). The value of RSET controls the range of currents (IDVR) that DVR can sink. Large RSET values decrease LSB size and decrease DVR's adjustment range. Calculate R1, R2, and RSET using the following procedure:

- Choose the maximum DVR output level (V<sub>MAX</sub>), the minimum DVR output level (V<sub>MIN</sub>), and the AV<sub>DD</sub> supply voltage (AV<sub>DD</sub>).

- 2) Calculate the R1/R2 ratio:

$$\frac{R1}{R2} = \left\{ \frac{AV_{DD}}{V_{MAX}} \right\} - 1$$

3) Calculate the R1/RSET ratio:

$$\frac{R1}{R_{SET}} = \left\{ \frac{20 \times \left(V_{MAX} - V_{MIN}\right)}{V_{MAX}} \right\}$$

4) Choose a RSET of approximately the value shown in the *Electrical Characteristics* table and calculate the values for R1 and R2.

Figure 8. DVR DAC Transfer Function

5) DVR's LSB size is:

$$LSB = \left\{ \frac{V_{MAX} - V_{MIN}}{128} \right\}$$

After selecting the values of R1 and R2, calculate the DVR voltage and IDVR with the following equations:

$$\begin{split} V_{DVR} \;\; = \; \left(\frac{R2}{R1 + \, R2}\right) \times \left(1 - \left(\frac{DVR\_Code \, + \, 1}{128}\right) \times \left(\frac{R1}{20 \, \times \, R_{SET}}\right)\right) \times \; AV_{DD} \\ I_{DVR} \;\; = \; \left\{\frac{V_{SET}}{R_{SET}}\right\} \end{split}$$

#### **Gamma DAC Transfer Functions**

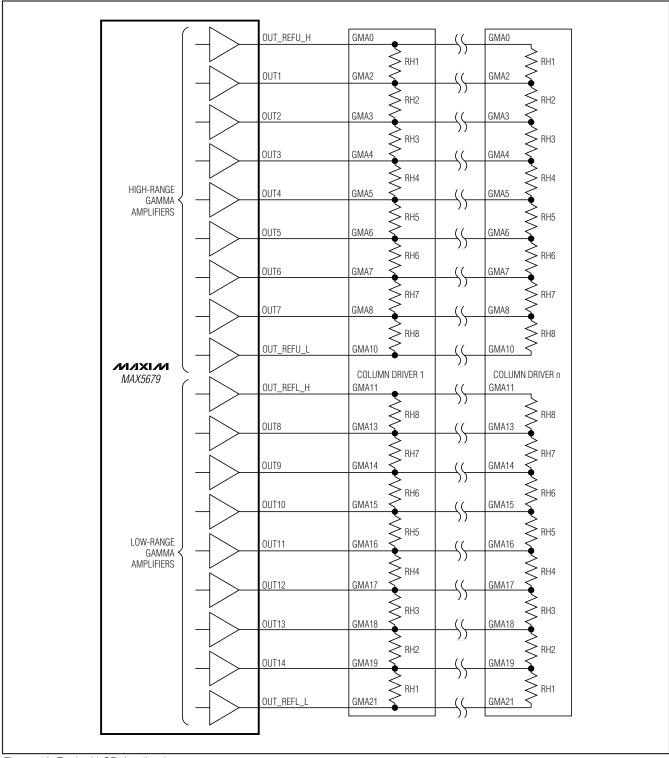

The MAX5679 contains two sets of gamma DAC blocks; an upper gamma DAC block and a lower gamma DAC block (see the *Functional Diagram*). Each DAC block comprises seven independent identical DACs that control seven independent outputs and each DAC block uses a seperate pair of reference inputs that determine its transfer function.

Figure 9. Gamma DAC Transfer Function

Figure 10. Typical LCD Application

16 \_\_\_\_\_\_\_/N/XI/M

### **Upper Block DAC Transfer Function**

The transfer function (see Figure 9) of each of the DACs in the upper DAC block (OUT1-OUT7) is:

$$V_{OUT-} = V_{REFU-L} + \left\{ \frac{DAC\_Code}{256} \right\} \times \left( V_{REFU\_H} - V_{REFU\_L} \right)$$

#### where:

V<sub>OUT</sub> is the output voltage of the respective upper DAC (OUT1-OUT7).

The DAC code is the decimal equivalent of the code written to the gamma register that controls the respective output (see Table 2),  $0 \le DAC\_Code \le 255$ .

VREFU\_H is the high reference for the upper DACs.

V<sub>REFU</sub> L is the low reference for the upper DACs.

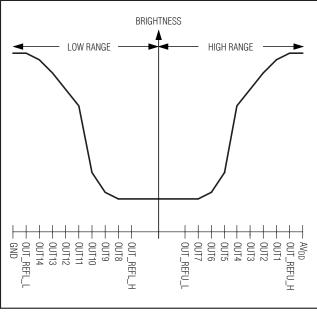

See Figure 10 for a typical LCD application and Figure 11 for a typical LCD gamma curve.

Figure 11. Typical LCD Gamma Curve

#### Lower Block DAC Transfer Function

The transfer function (see Figure 9) of each of the DACs in the lower DAC block (OUT8–OUT14) is:

$$V_{OUT\_} = V_{REFL\_H} - \left\{ \frac{DAC\_Code}{256} \right\} \times \left( V_{REFL\_H} - V_{REFL\_L} \right)$$

#### where:

V<sub>OUT</sub> is the output voltage of the respective lower DAC (OUT8-OUT14).

The DAC code is the decimal equivalent of the code written to the gamma register that controls the respective output (see Table 2),  $0 \le DAC$  code  $\le 255$ .

VREFL\_H is the high reference for the lower DACs.

VREFL L is the low reference for the lower DACs.

See Figure 10 for a typical LCD application and Figure 11 for a typical LCD gamma curve.

### **Layout Information**

Place the resistor-divider close to the DVR output. Place  $R_{SET}$  close to SET. Use bypass capacitors on DVDD and AVDD. Keep all bypass capacitors close to the IC with short connections to the inputs.

\_\_\_\_\_Chip Information

PROCESS: BICMOS

## Typical Operating Circuit

## Functional Diagram

/M/XI/M \_\_\_\_\_

### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

\_ /N/IXI/N

### **Package Information (continued)**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to www.maxim-ic.com/packages.)

| COMMON DIMENSIONS |           |      |      |           |      |      |           |      |      |           |      |      |           |      |      |

|-------------------|-----------|------|------|-----------|------|------|-----------|------|------|-----------|------|------|-----------|------|------|

| PKG.              | 16L 5×5   |      |      | 20L 5×5   |      |      | 28L 5×5   |      |      | 32L 5x5   |      |      | 40L 5×5   |      |      |

| SYMBOL            | MIN.      | NDM. | MAX. | MIN.      | NOM. | MAX. | MIN.      | NDM. | MAX. | MIN.      | NDM. | MAX. | MIN.      | NDM. | MAX. |

| Α                 | 0.70      | 0.75 | 0.80 | 0.70      | 0.75 | 0.80 | 0.70      | 0.75 | 0.80 | 0.70      | 0.75 | 0.80 | 0.70      | 0.75 | 0.80 |

| A1                | 0         | 9.02 | 0.05 | 0         | 0.02 | 0.05 | 0         | 0.02 | 0.05 | 0         | 0.02 | 0.05 | 0         | 0.02 | 0.05 |

| A2                | 0.20 REF. |      |      |

| b                 | 0.25      | 0.30 | 0.35 | 0.25      | 0.30 | 0.35 | 0.20      | 0.25 | 0.30 | 0.20      | 0.25 | 0.30 | 0.15      | 0.20 | 0.25 |

| D                 | 4.90      | 5.00 | 5.10 | 4.90      | 5.00 | 5.10 | 4.90      | 5.00 | 5.10 | 4.90      | 5.00 | 5.10 | 4.90      | 5.00 | 5.10 |

| Ε                 | 4.90      | 5.00 | 5.10 | 4.90      | 5.00 | 5.10 | 4.90      | 5.00 | 5.10 | 4.90      | 5,00 | 5.10 | 4.90      | 5.00 | 5.10 |

| e                 | 0.80 BSC. |      |      | 0.65 BSC. |      |      | 0.50 BSC. |      |      | 0.50 BSC. |      |      | 0.40 BSC. |      |      |

| k                 | 0.25      | -    | -    | 0.25      | -    | _    | 0.25      | _    | -    | 0.25      | ı    | ı    | 0.25      | _    | -    |

| L                 | 0.30      | 0.40 | 0.50 | 0.45      | 0.55 | 0.65 | 0.45      | 0.55 | 0.65 | 0.30      | 0.40 | 0.50 | 0.30      | 0.40 | 0.50 |

| N                 | 16        |      |      | 20        |      |      | 28        |      |      | 32        |      |      | 40        |      |      |

| ND                | 4         |      |      | 5         |      |      | 7         |      | 8    |           |      | 10   |           |      |      |

| NE                | 4         |      |      | 5         |      |      | 7         |      | 8    |           |      | 10   |           |      |      |

| JEDEC             | WHHB      |      |      | WHHC      |      |      | WHHD-1    |      |      | VHHD-2    |      |      |           |      |      |

- DIMENSIONING & TOLERANCING CONFORM TO ASME Y14.5M-1994.

- ALL DIMENSIONS ARE IN MILLIMETERS. ANGLES ARE IN DEGREES.

- N IS THE TOTAL NUMBER OF TERMINALS.

- 1 THE TERMINAL #1 IDENTIFIER AND TERMINAL NUMBERING CONVENTION SHALL CONFORM TO JESD 95-1 SPP-012. DETAILS OF TERMINAL #1 IDENTIFIER ARE OPTIONAL, BUT MUST BE LOCATED WITHIN THE ZONE INDICATED. THE TERMINAL #1 IDENTIFIER MAY BE EITHER A MOLD OR MARKED FEATURE.

- △ DIMENSION № APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.25 mm AND 0.30 mm FROM TERMINAL TIP.

- AND AND NE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E SIDE RESPECTIVELY.

- DEPOPULATION IS POSSIBLE IN A SYMMETRICAL FASHION.

- COPLANARITY APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS.

- DRAWING CONFORMS TO JEDEC MO220, EXCEPT EXPOSED PAD DIMENSION FOR

- T2855-3, T2855-6, T4055-1 AND T4055-2.

- △OL WARPAGE SHALL NOT EXCEED 0.10 mm.

- 11. MARKING IS FOR PACKAGE DRIENTATION REFERENCE ONLY.

- NUMBER OF LEADS SHOWN ARE FOR REFERENCE ONLY.

- ∠3 LEAD CENTERLINES TO BE AT TRUE POSITION AS DEFINED BY BASIC DIMENSION 'e', ±0.05.

- 14. ALL DIMENSIONS APPLY TO BOTH LEADED AND PHFREE PARTS.

-DRAWING NOT TO SCALE-

| EXPOSED PAD VARIATIONS |           |      |      |      |      |      |  |  |  |

|------------------------|-----------|------|------|------|------|------|--|--|--|

| PKG.                   |           | D2   |      | E2   |      |      |  |  |  |

| CODES                  | MIN.      | NOM. | MAX. | MIN. | NDM. | MAX. |  |  |  |

| T1655-2                | 3.00      | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |  |

| T1655-3                | 3.00      | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |  |

| T1655N-1               | 3.00      | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |  |

| T2055-3                | 3.00 3.10 |      | 3.20 | 3.00 | 3.10 | 3.20 |  |  |  |

| T2055-4                | 3.00      | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |  |

| T2055-5                | 3.15      | 3.25 | 3.35 | 3.15 | 3.25 | 3.35 |  |  |  |

| T2055MN-5              | 3.15      | 3.25 | 3.35 | 3.15 | 3.25 | 3.35 |  |  |  |

| T2855-3                | 3.15      | 3.25 | 3.35 | 3.15 | 3.25 | 3.35 |  |  |  |

| T2955-4                | 2.60      | 2.70 | 2.80 | 2.60 | 2.70 | 2.80 |  |  |  |

| T2855-5                | 2.60      | 2.70 | 2.80 | 2.60 | 2.70 | 2.80 |  |  |  |

| T2955-6                | 3.15      | 3.25 | 3.35 | 3.15 | 3.25 | 3.35 |  |  |  |

| T2855-7                | 2.60      | 2.70 | 2.80 | 2.60 | 2.70 | 2.80 |  |  |  |

| T2955-8                | 3.15      | 3.25 | 3.35 | 3.15 | 3.25 | 3.35 |  |  |  |

| T2855N-1               | 3.15      | 3.25 | 3.35 | 3.15 | 3.25 | 3.35 |  |  |  |

| T3255-3                | 3.00      | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |  |

| T3255-4                | 3.00      | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |  |

| T3255M-4               | 3.00      | 3.10 | 3.20 | 3.00 | 3.10 | 3.20 |  |  |  |

| T3255-5                | 3.00      | 3.10 | 3,20 | 3.00 | 3.10 | 3.20 |  |  |  |

| T3255N-1               | 3.00      | 3.10 | 3.20 | 3.00 | 3.10 | 3,20 |  |  |  |

| T4055-1                | 3.40      | 3.50 | 3.60 | 3.40 | 3.50 | 3.60 |  |  |  |

| T4055-2                | 3,40      | 3,50 | 3.60 | 3,40 | 3.50 | 3,60 |  |  |  |

| T4055MN-1              | 3.40      | 3.50 | 3.60 | 3.40 | 3.50 | 3.60 |  |  |  |

PACKAGE DUTLINE,

16,20,28,32,40L THIN QFN, 5x5x0.80mm

DOCUMENT CONTROL NO.

21-0140

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 \_\_\_

© 2008 Maxim Integrated Products

is a registered trademark of Maxim Integrated Products, Inc.