Features

## **Quad Network Power Controller** for Power-Over-LAN

## **General Description**

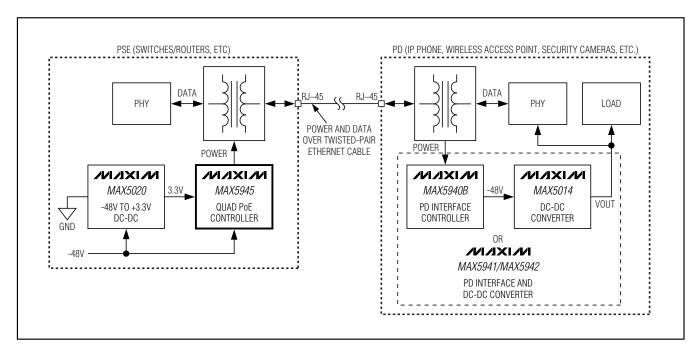

The MAX5945 quad network power controller is designed for use in IEEE 802.3af-compliant power-sourcing equipment (PSE). The device provides power devices (PD) discovery, classification, current-limit, and both DC and AC load disconnect detections. The MAX5945 can be used in either endpoint PSE (LAN switches/routers) or midspan PSE (power injector) applications. The MAX5945 is pin and function compatible with LTC4259A.

The MAX5945 can operate autonomously or be controlled by software through an I2C\*-compatible interface. Separate input and output data lines (SDAIN and SDAOUT) allow usage with optocouplers. The MAX5945 is a slave device. Its four address inputs allow 16 unique MAX5945 addresses. A separate INT output and four independent shutdown inputs (SHD\_) allow fast response from a fault to port shutdown. A RESET input allows hardware reset of the device. A special watchdog feature allows the hardware to gracefully take over control if the software crashes. A cadence timing feature allows the MAX5945 to be used in midspan systems.

The MAX5945 is fully software configurable and programmable. A class-overcurrent detection function enables system power management to detect if a PD draws more current than the allowable amount for its class. Other features are input under/overvoltage lockout, overtemperature protection, output-voltage slew-rate limit during startup, power-good, and fault status. The MAX5945's programmability includes gate-charging current, currentlimit threshold, startup timeout, overcurrent timeout, autorestart duty cycle, PD disconnect AC detection threshold, and PD disconnect detection timeout.

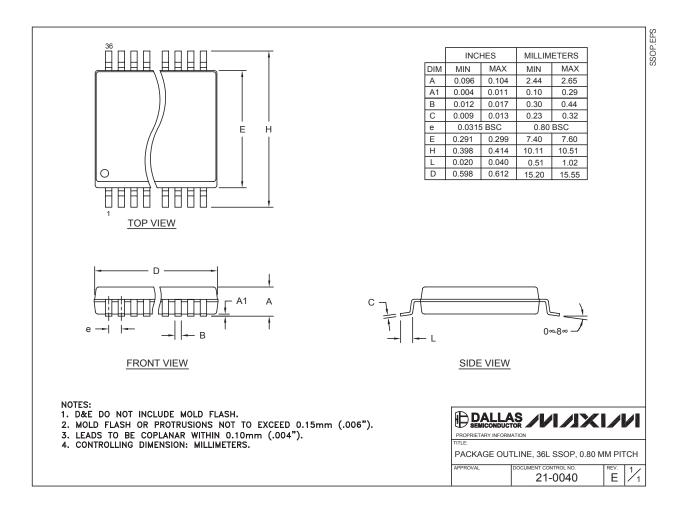

The MAX5945 is available in a 36-pin SSOP package and is rated for both extended (-40°C to +85°C) and commercial (0°C to +70°C) temperature ranges.

## **Applications**

Power-Sourcing Equipment (PSE) Power-Over-LAN/Power-Over-Ethernet Switches/Routers Midspan Power Injectors

\*Purchase of I<sup>2</sup>C components from Maxim Integrated Products, Inc. or one of its sublicensed Associated Companies, conveys a license under the Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I2C Standard Specification as defined by Philips.

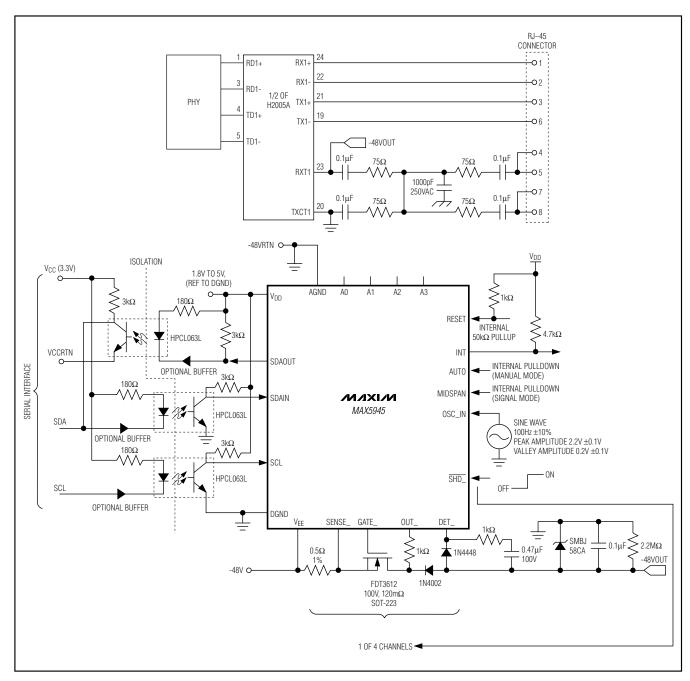

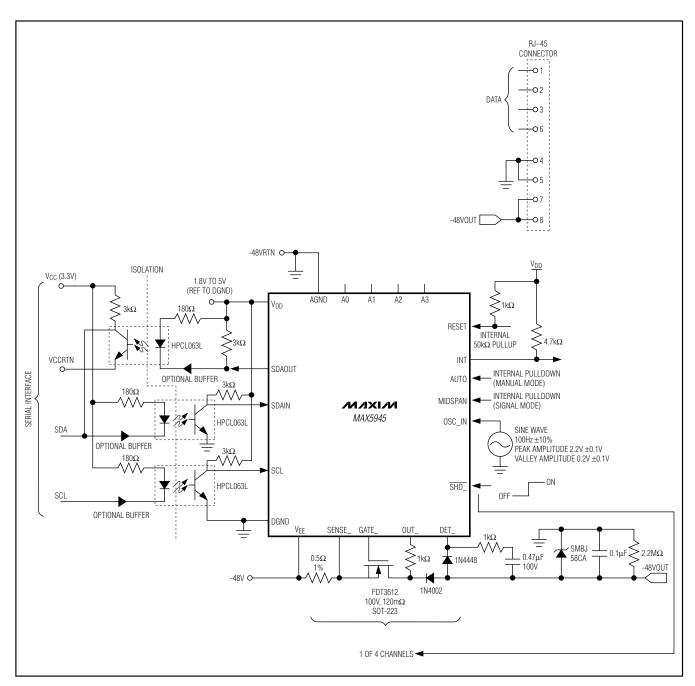

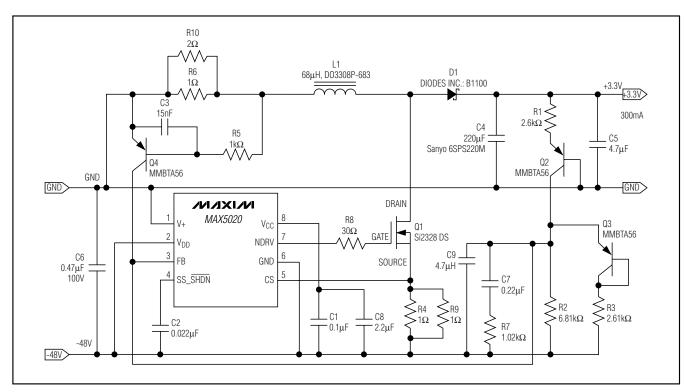

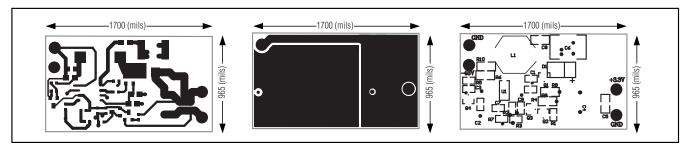

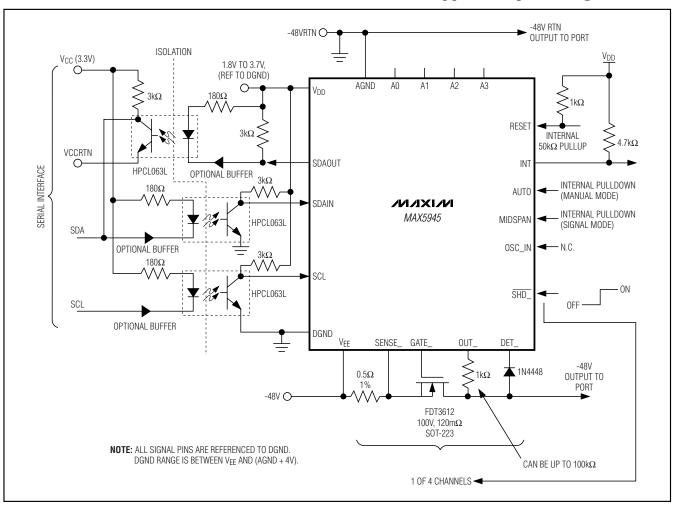

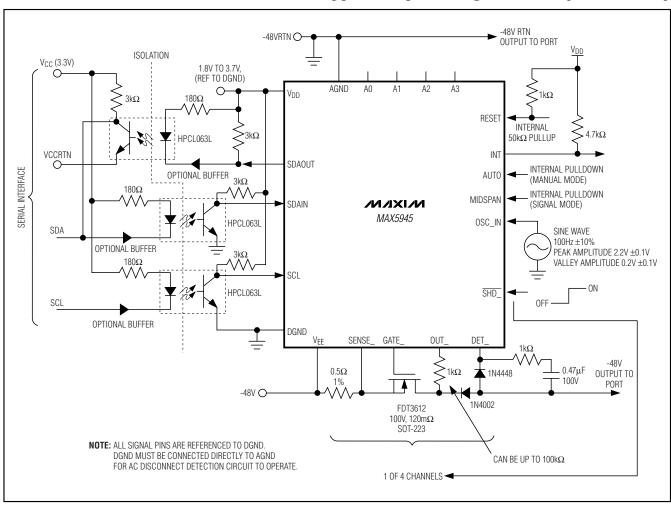

Typical Operating Circuits appear at end of data sheet.

#### ♦ IEEE 802.3af Compliant

- ♦ Pin and Function Compatible with LTC4259A

- ♦ Controls Four Independent, -48V-Powered **Ethernet Ports in Either Endpoint or Midspan PSE Applications**

- ♦ Wide Digital Power Input, VDIG, Common-Mode Range: VEE to (AGND + 7.7V)

- ♦ PD Violation of Class Current Protection

- ◆ PD Detection and Classification

- ♦ Provides Both DC and AC Load Removal **Detections**

- ♦ I<sup>2</sup>C-Compatible, 3-Wire Serial Interface

- **♦** Fully Programmable and Configurable Operation Through I<sup>2</sup>C Interface

- **♦ Current Foldback and Duty-Cycle-Controlled/Programmable Current Limit**

- ♦ Short-Circuit Protection with Fast Gate Pulldown

- **♦ Direct Fast Shutdown Control Capability**

- ♦ Programmable Direct Interrupt Output

- ♦ Watchdog Mode Enable Hardware Graceful **Takeover**

## **Ordering Information**

| PART         | TEMP RANGE     | PIN-PACKAGE |

|--------------|----------------|-------------|

| MAX5945CAX** | 0°C to +70°C   | 36 SSOP     |

| MAX5945EAX   | -40°C to +85°C | 36 SSOP     |

<sup>\*\*</sup>Future product—contact factory for availability.

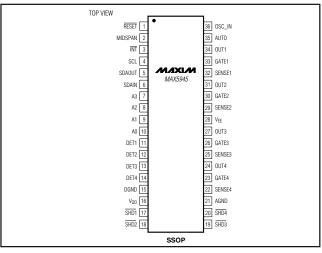

## Pin Configuration

### **ABSOLUTE MAXIMUM RATINGS**

| (Voltages referenced to $V_{EE}$ , unless otherwise AGND, DGND, DET_, $V_{DD}$ , RESET, A3, A2, A1 | 1, A0, <del>ŚHD</del> _, |

|----------------------------------------------------------------------------------------------------|--------------------------|

| OSC_IN, SCL, SDAIN, OUT_ and AUTO                                                                  | 0.3V to +80V             |

| GATE_ (internally clamped, Note 1)                                                                 | 0.3V to +11.4V           |

| SENSE                                                                                              | 0.3V to +24V             |

| V <sub>DD</sub> , RESET, A3, A2, A1, A0, SHD_, OSC_IN,                                             | SCL, SDAIN and           |

| AUTO to DGND                                                                                       | 0.3V to +7V              |

| INT and SDAOUT to DGND                                                                             | 0.3V to +12V             |

| Maximum Current into INT, SDAOUT, DET                                                              | 80mA                     |

| Maximum Power Dissipation          |                   |

|------------------------------------|-------------------|

| 36-Pin SSOP (derate 11.4mW/°C      | above +70°C)941mW |

| Operating Temperature Ranges:      |                   |

| MAX5945EAX                         | 40°C to +85°C     |

| MAX5945CAX                         | 0°C to +70°C      |

| Storage Temperature Range          | 65°C to +150°C    |

| Junction Temperature               | +150°C            |

| Lead Temperature (soldering, 10s). | +300°C            |

|                                    |                   |

Note 1: GATE\_ is internally clamped to 11.4V above VEE. Driving GATE\_ higher than 11.4V above VEE may damage the device.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

(AGND = +32V to +60V,  $V_{EE}$  = 0V,  $V_{DD}$  to DGND = +3.3V, all voltages are referenced to  $V_{EE}$ , unless otherwise noted. Typical values are at AGND = +48V, DGND = +48V,  $V_{DD}$  = (DGND + 3.3V),  $V_{A}$  = +25°C. Currents are positive when entering the pin and negative otherwise.)

| PARAMETER                     | SYMBOL              | CONDI                                                                                          | TIONS                                                                                                                                                                                        | MIN   | TYP | MAX  | UNITS |  |

|-------------------------------|---------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|------|-------|--|

| POWER SUPPLIES                |                     |                                                                                                |                                                                                                                                                                                              |       |     |      |       |  |

|                               | Vagnd               | VAGND - VEE                                                                                    |                                                                                                                                                                                              | 32    |     | 60   |       |  |

| On a vating Valtage Dange     | V <sub>DGND</sub>   |                                                                                                |                                                                                                                                                                                              | 0     |     | 60   | V     |  |

| Operating Voltage Range       | V                   | $V_{DD}$ to $V_{DGND}$ , $V_{DGND} = 0$                                                        | Vagnd                                                                                                                                                                                        | 1.71  |     | 5.50 | V     |  |

|                               | V <sub>DD</sub>     | $V_{DD}$ to $V_{DGND}$ , $V_{DGND} = 0$                                                        | VEE                                                                                                                                                                                          | 3.0   |     | 5.5  |       |  |

| Supply Currents               | lee                 | all logic inputs open, SCL INT and SDAOUT open; n                                              | DUT_ = V <sub>EE</sub> , SENSE_ = V <sub>EE</sub> , DET_ = AGND, all logic inputs open, SCL = SDAIN = V <sub>DD</sub> , NT and SDAOUT open; measured at AGND n power mode after GATE_ pullup |       |     |      | mA    |  |

|                               | IDIG                | All logic inputs high, meas                                                                    |                                                                                                                                                                                              | 2.7   | 5.6 | 1    |       |  |

| GATE DRIVER AND CLAMPING      | G                   |                                                                                                |                                                                                                                                                                                              |       |     |      |       |  |

| GATE_ Pullup Current          | I <sub>PU</sub>     | Power mode, gate drive of                                                                      | n, V <sub>GATE</sub> = V <sub>EE</sub> (Note 2)                                                                                                                                              | -40   | -50 | -60  | μΑ    |  |

| Weak GATE_ Pulldown Current   | I <sub>PDW</sub>    | SHD_ = DGND, VGATE_ =                                                                          | V <sub>EE</sub> + 5V                                                                                                                                                                         | 30    | 40  | 50   | μΑ    |  |

| Maximum Pulldown Current      | I <sub>PDS</sub>    | VSENSE = 1V, VGATE_ = VEE + 2V                                                                 |                                                                                                                                                                                              |       | 100 |      | mA    |  |

| External Gate Drive           | Vgs                 | VGATE - VEE , power mode                                                                       | V <sub>GATE</sub> - V <sub>EE</sub> , power mode, gate drive on                                                                                                                              |       | 10  | 11   | V     |  |

| CURRENT LIMIT                 |                     |                                                                                                |                                                                                                                                                                                              |       |     |      |       |  |

| Current-Limit Clamp Voltage   | V <sub>SU_LIM</sub> | Maximum V <sub>SENSE_</sub> allowe V <sub>OUT_</sub> = V <sub>EE</sub> (Note 3)                | Maximum V <sub>SENSE</sub> allowed during current limit, V <sub>OUT</sub> = V <sub>EE</sub> (Note 3)                                                                                         |       | 212 | 220  | mV    |  |

| Overcurrent Threshold After   |                     | Overcurrent VSENSE_<br>threshold allowed for                                                   | Default, class 0, class 3, class 4                                                                                                                                                           | 178.5 |     | 196  |       |  |

| Startup                       | VFLT_LIM            | t ≤ tFAULT after startup;                                                                      | Class 1                                                                                                                                                                                      | 49    |     | 61   | mV    |  |

|                               |                     | V <sub>OUT</sub> = V <sub>EE</sub>                                                             | Class 2                                                                                                                                                                                      | 90    |     | 104  | 1     |  |

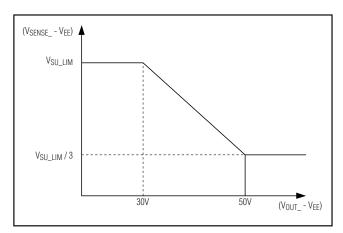

| Foldback Initial OUT_ Voltage | VFLBK_ST            |                                                                                                | V <sub>OUT</sub> - V <sub>EE</sub> , above which the current-limit trip voltage starts folding back                                                                                          |       | 30  |      | V     |  |

| Foldback Final OUT_ Voltage   | VFLBK_END           | V <sub>OUT</sub> - V <sub>EE</sub> , above which voltage reaches V <sub>TH</sub> <sub>FB</sub> | n the current-limit trip                                                                                                                                                                     |       | 50  |      | V     |  |

## **ELECTRICAL CHARACTERISTICS (continued)**

(AGND = +32V to +60V,  $V_{EE}$  = 0V,  $V_{DD}$  to DGND = +3.3V, all voltages are referenced to  $V_{EE}$ , unless otherwise noted. Typical values are at AGND = +48V, DGND = +48V,  $V_{DD}$  = (DGND + 3.3V),  $T_{A}$  = +25°C. Currents are positive when entering the pin and negative otherwise.)

| PARAMETER                                          | SYMBOL              | CONDITIONS                                                                                                      | MIN  | TYP  | MAX  | UNITS |

|----------------------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| Minimum Foldback Current-<br>Limit Threshold       | V <sub>TH_FB</sub>  | V <sub>OUT_</sub> = V <sub>AGND</sub>                                                                           |      | 64   |      | mV    |

| SENSE_ Input Bias Current                          |                     | V <sub>SENSE</sub> _ = V <sub>EE</sub>                                                                          |      |      | -2   | μΑ    |

| SUPPLY MONITORS                                    |                     |                                                                                                                 |      |      |      |       |

| VEE Undervoltage Lockout                           | VEEUVLO             | VAGND - VEE, (VAGND - VEE) increasing                                                                           | 27   | 28.5 | 30   | V     |

| VEE Undervoltage-Lockout<br>Hysteresis             | VEEUVLOH            |                                                                                                                 |      | 3    |      | V     |

| VEE Overvoltage                                    | V <sub>EE</sub> _OV | (VAGND - VEE) > VEE_OV, VAGND increasing                                                                        | 61   | 62.5 | 64   | V     |

| VEE Overvoltage Hysteresis                         | Vovh                |                                                                                                                 |      | 1    |      | V     |

| V <sub>EE</sub> Undervoltage                       | V <sub>EE_UV</sub>  | (VAGND - VEE) < VEE_UV, VAGND decreasing                                                                        | 39   | 40   | 41   | V     |

| V <sub>DD</sub> Overvoltage                        | V <sub>DD_OV</sub>  | (V <sub>DD</sub> - V <sub>DGND</sub> ) > V <sub>DD_OV</sub> , V <sub>DD</sub> increasing                        | 3.57 | 3.71 | 3.90 | V     |

| V <sub>DD</sub> Undervoltage                       | V <sub>DD_UV</sub>  | (V <sub>DD</sub> - V <sub>DGND</sub> ) < V <sub>DD_UV</sub> , V <sub>DD</sub> decreasing                        | 2.55 | 2.82 | 2.97 | V     |

| V <sub>DD</sub> Undervoltage Lockout               | V <sub>DDUVLO</sub> | Device operates when (V <sub>DD</sub> - V <sub>DGND</sub> ) > V <sub>DDUVLO</sub> , V <sub>DD</sub> increasing  |      |      | 1.7  | V     |

| V <sub>DD</sub> Undervoltage-Lockout<br>Hysteresis | V <sub>DDHYS</sub>  |                                                                                                                 |      | 120  |      | mV    |

| Thermal-Shutdown Threshold                         | T <sub>SHD</sub>    | Ports shut down and device resets if its junction temperature exceeds this limit, temperature increasing        |      | +150 |      | °C    |

| Thermal-Shutdown Hysteresis                        | TSHDH               |                                                                                                                 |      | 20   |      | °C    |

| OUTPUT MONITOR                                     |                     |                                                                                                                 |      |      |      |       |

| OUT_ Input Current                                 | IBOUT               | V <sub>OUT</sub> = V <sub>AGND</sub> , all modes                                                                |      |      | 2    | μΑ    |

| Idle Pullup Current at OUT_                        | I <sub>DIS</sub>    | OUT_ discharge current, detection and classification off, port shutdown, VOUT_ = VAGND - 2.8V                   | 200  |      | 260  | μА    |

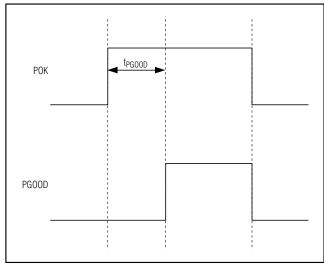

| PGOOD High Threshold                               | PGTH                | V <sub>OUT_</sub> - V <sub>EE</sub> , OUT_ decreasing                                                           | 1.8  | 2.0  | 2.2  | V     |

| PGOOD Hysteresis                                   | PGHYS               |                                                                                                                 |      | 220  |      | mV    |

| PGOOD Low-to-High Glitch<br>Filter                 | tpgood              | Minimum time PGOOD has to be high to set bit in register 10h                                                    | 2    |      | 4    | ms    |

| LOAD DISCONNECT                                    |                     |                                                                                                                 |      |      |      |       |

| DC Load Disconnect<br>Threshold                    | V <sub>DCTH</sub>   | Minimum V <sub>SENSE</sub> allowed before disconnect (DC disconnect active), V <sub>OUT</sub> = V <sub>EE</sub> | 3    | 4    | 5    | mV    |

|                                                    | •                   |                                                                                                                 |      |      |      | •     |

## **ELECTRICAL CHARACTERISTICS (continued)**

(AGND = +32V to +60V,  $V_{EE} = 0V$ ,  $V_{DD}$  to DGND = +3.3V, all voltages are referenced to  $V_{EE}$ , unless otherwise noted. Typical values are at AGND = +48V, DGND = +48V,  $V_{DD} = (DGND + 3.3V)$ ,  $T_A = +25^{\circ}C$ . Currents are positive when entering the pin and negative otherwise.)

| PARAMETER                                 | SYMBOL              | COND                                                                               | ITIONS                  | MIN  | TYP  | MAX  | UNITS  |

|-------------------------------------------|---------------------|------------------------------------------------------------------------------------|-------------------------|------|------|------|--------|

| AC Load Disconnect<br>Threshold (Note 4)  | I <sub>ACTH</sub>   | Current into DET_, ACD_<br>OSC_IN = 2.2V                                           | _EN_ bit = high,        | 300  | 325  | 350  | μA     |

| Oscillator Buffer Gain                    | Aosc                | V <sub>DET_</sub> / V <sub>OSC_IN</sub> , ACD_E<br>C <sub>DET</sub> = 400nF        | :N_ bit = high,         | 2.92 | 2.98 | 3.04 | V/V    |

| OSC_IN Fail Threshold (Note 5)            | Vosc_fail           | Port will not power on if \ACD_EN_ bit = high                                      | Vosc_in < Vosc_fail and | 1.8  | 1.9  | 2.1  | V      |

| OSC_IN Input Resistance                   | Zosc                | OSC_IN input impedance active                                                      | e when all the ACD_EN_  | 100  |      |      | kΩ     |

| OSC_IN Input Capacitance                  | Cosc_in             |                                                                                    |                         |      | 5    |      | рF     |

| Load Disconnect Timer                     | tDISC               | Time from V <sub>SENSE</sub> < V <sub>DC</sub> < I <sub>ACTH</sub> to gate shutdow |                         | 300  |      | 400  | ms     |

| DETECTION                                 | •                   |                                                                                    |                         |      |      |      |        |

| Detection Probe Voltage (First Phase)     | V <sub>DPH1</sub>   | V <sub>AGND</sub> - V <sub>DET</sub> during th                                     | e first detection phase | 3.8  | 4    | 4.2  | \<br>\ |

| Detection Probe Voltage<br>(Second Phase) | V <sub>DPH2</sub>   | V <sub>AGND</sub> - V <sub>DET</sub> during the phase                              | e second detection      | 9.0  | 9.3  | 9.6  | V      |

| Current-Limit Protection                  | IDLIM               | V <sub>DET</sub> = V <sub>AGND</sub> , during of current through DET_              | 1.5                     | 1.75 | 2.0  | mA   |        |

| Short-Circuit Threshold                   | V <sub>DCP</sub>    | If VAGND - VOUT < VDCP of phase a short circuit to All                             |                         | 1.62 |      | V    |        |

| Open-Circuit Threshold                    | I <sub>D_OPEN</sub> | First point measurement open condition                                             |                         | 12.5 |      | μΑ   |        |

| Resistor Detection Window                 | RDOK                | (Note 7)                                                                           |                         | 18.6 |      | 26.5 | kΩ     |

| Resistor Rejection Window                 | RDBAD               | Detection rejects lower v                                                          | alues //                |      |      | 16   | kΩ     |

| Tresistor rejection window                | LIDBAD              | Detection rejects higher                                                           | values                  | 30   |      |      | N22    |

| CLASSIFICATION                            |                     |                                                                                    |                         |      |      |      |        |

| Classification Probe Voltage              | V <sub>CL</sub>     | VAGND - VDET_ during cl                                                            | assification            | 16   |      | 20   | V      |

| Current-Limit Protection                  | ICILIM              | V <sub>DET</sub> = V <sub>AGND</sub> , during of measure current through           |                         | 50   |      | 75   | mA     |

|                                           |                     |                                                                                    | Class 0, class 1        | 5.5  | 6.5  | 7.5  |        |

| 01:                                       |                     | Classification current                                                             | Class 1, class 2        | 13.5 | 14.5 | 15.5 |        |

| Classification Current Thresholds         | ICL                 | thresholds between                                                                 | Class 2, class 3        | 21.5 | 23   | 24.5 | mA     |

| 50110100                                  |                     | classes                                                                            | Class 3, class 4        | 31   | 33   | 35   |        |

|                                           |                     |                                                                                    | >Class 4                | 45   | 48   | 51   |        |

| DIGITAL INPUTS/OUTPUTS (                  | REFERRED t          | o DGND)                                                                            |                         |      |      |      | _      |

| Digital Input Low                         | V <sub>I</sub> L    |                                                                                    |                         |      |      | 0.9  | V      |

| Digital Input High                        | VIH                 |                                                                                    |                         | 2.4  |      |      | V      |

\_\_\_\_\_\_NIXI/N

## **ELECTRICAL CHARACTERISTICS (continued)**

(AGND = +32V to +60V,  $V_{EE}$  = 0V,  $V_{DD}$  to DGND = +3.3V, all voltages are referenced to  $V_{EE}$ , unless otherwise noted. Typical values are at AGND = +48V, DGND = +48V,  $V_{DD}$  = (DGND + 3.3V),  $T_{A}$  = +25°C. Currents are positive when entering the pin and negative otherwise.)

| PARAMETER                                          | SYMBOL                | CONDIT                                                                | TIONS                                                                                                             | MIN | TYP                        | MAX | UNITS |  |

|----------------------------------------------------|-----------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----|----------------------------|-----|-------|--|

| Internal Input Pullup/Pulldown<br>Resistor         | R <sub>DIN</sub>      | Pullup (pulldown) resistor default level                              | to V <sub>DD</sub> (DGND) to set                                                                                  | 25  | 50                         | 75  | kΩ    |  |

| Open-Drain Output Low<br>Voltage                   | VoL                   | ISINK = 15mA                                                          | I <sub>SINK</sub> = 15mA                                                                                          |     |                            |     | V     |  |

| Open-Drain Leakage                                 | loL                   | Open-drain high impedan                                               | Open-drain high impedance, V <sub>O</sub> = 3.3V                                                                  |     |                            |     | μΑ    |  |

| TIMING                                             |                       |                                                                       |                                                                                                                   |     |                            |     |       |  |

| Startup Time                                       | tstart                |                                                                       | Fime during which a current limit set by V <sub>SU_LIM</sub> s allowed, starts when the GATE_s turned on (Note 8) |     | 60                         | 70  | ms    |  |

| Fault Time                                         | tfault                | Maximum allowed time for condition set by V <sub>FLT_LIM</sub>        |                                                                                                                   | 50  | 60                         | 70  | ms    |  |

| Port Turn-Off Time                                 | toff                  | Minimum delay between a does not apply in the case                    |                                                                                                                   | 0.5 | 0.75                       | 1.0 | ms    |  |

| Detection Time                                     | tDET                  | Maximum time allowed be is completed                                  | Maximum time allowed before detection is completed                                                                |     |                            |     | ms    |  |

| Midspan Mode Detection<br>Delay                    | tDMID                 |                                                                       |                                                                                                                   |     |                            |     | S     |  |

| Classification Time                                | tCLASS                | Time allowed for classifica                                           | Time allowed for classification                                                                                   |     |                            |     | ms    |  |

| VEEUVLO Turn-On Delay                              | t <sub>DLY</sub>      | _                                                                     | Time V <sub>AGND</sub> must be above the V <sub>EEUVLO</sub> thresholds before the device operates                |     |                            |     | ms    |  |

|                                                    |                       |                                                                       | RSTR bits = 00                                                                                                    |     | 16 x<br>t <sub>FAULT</sub> |     |       |  |

| Restart Timer                                      | t <sub>RESTART</sub>  | Time a port has to wait before turning on after an overcurrent fault, | RSTR bits = 01                                                                                                    |     | 32 x<br>tfault             |     | ms    |  |

|                                                    |                       | RSTR_EN bit = high                                                    | RSTR bits = 10                                                                                                    |     | 64 x<br>tfault             |     |       |  |

|                                                    |                       |                                                                       | RSTR bits = 11                                                                                                    |     | 0                          |     |       |  |

| Watchdog Clock Period                              | twD                   | Rate of decrement of the v                                            | watchdog timer                                                                                                    |     | 164                        |     | ms    |  |

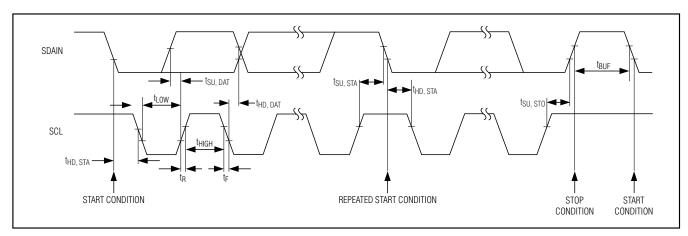

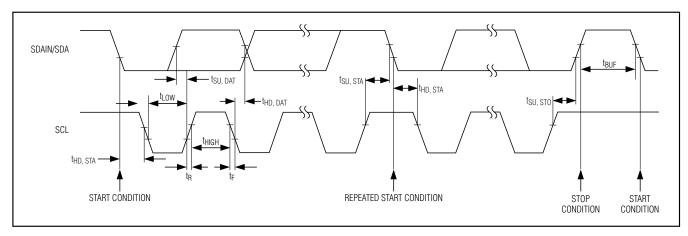

| TIMING CHARACTERISTICS for                         | or 2-WIRE F           | AST MODE (Figures 5 and                                               | 6)                                                                                                                |     |                            |     |       |  |

| Serial Clock Frequency                             | fscl                  | (Note 9)                                                              |                                                                                                                   |     |                            | 400 | kHz   |  |

| Bus Free Time Between a STOP and a START Condition | t <sub>BUF</sub>      | (Note 9)                                                              |                                                                                                                   | 1.2 |                            |     | μs    |  |

| Hold Time for Start Condition                      | t <sub>HD</sub> , STA | (Note 9)                                                              |                                                                                                                   | 0.6 |                            |     | μs    |  |

| Low Period of the SCL Clock                        | tLOW                  | (Note 9)                                                              |                                                                                                                   | 1.2 |                            |     | μs    |  |

| High Period of the SCL Clock                       | tHIGH                 | (Note 9)                                                              |                                                                                                                   | 0.6 |                            |     | μs    |  |

## **ELECTRICAL CHARACTERISTICS (continued)**

(AGND = +32V to +60V,  $V_{EE}$  = 0V,  $V_{DD}$  to DGND = +3.3V, all voltages are referenced to  $V_{EE}$ , unless otherwise noted. Typical values are at AGND = +48V, DGND = +48V,  $V_{DD}$  = (DGND + 3.3V),  $V_{DD}$  = +25°C. Currents are positive when entering the pin and negative otherwise.)

| PARAMETER                                        | SYMBOL   | CONDITIONS | MIN       | TYP | MAX | UNITS |

|--------------------------------------------------|----------|------------|-----------|-----|-----|-------|

| Setup Time for a Repeated START Condition (Sr)   | tsu, sta | (Note 9)   | 0.6       |     |     | μs    |

| Data Hold Time                                   | thd, dat | (Note 9)   | 0         |     | 150 | ns    |

| Data Setup Time                                  | tsu, dat | (Note 9)   | 100       |     |     | ns    |

| Rise Time of Both SDA and SCL Signals, Receiving | tR       | (Note 9)   | 20 + 0.10 | Св  | 300 | ns    |

| Fall Time of SDA Transmitting                    | tF       | (Note 9)   | 20 + 0.10 | Св  | 300 | ns    |

| Setup Time for STOP Condition                    | tsu, sto | (Note 9)   | 0.6       |     |     | μs    |

| Capacitive Load for Each Bus<br>Line             | Св       | (Note 9)   |           |     | 400 | рF    |

| Pulse Width of Spike<br>Suppressed               | tsp      | (Note 9)   |           |     | 50  | ns    |

- **Note 2:** Default values. The charge/discharge currents are programmable through the serial interface (see the *Register Map and Description* section).

- **Note 3:** Default values. The current-limit thresholds are programmed through the I<sup>2</sup>C-compatible serial interface (see the *Register Map and Description* section).

- Note 4: This is the default value. Threshold can be programmed through serial interface R23h[2:0].

- **Note 5:** AC disconnect works only if  $V_{DD} V_{DGND} \ge 3V$ .

- Note 6: tDISC can also be programmed through the serial interface (R29h) (see the Register Map and Description section).

- Note 7: R<sub>D</sub> = (V<sub>OUT\_2</sub> V<sub>OUT\_1</sub>) / (I<sub>DET\_2</sub> I<sub>DET\_1</sub>). V<sub>OUT\_1</sub>, V<sub>OUT\_2</sub>, I<sub>DET\_2</sub> and I<sub>DET\_1</sub> represent the voltage at OUT\_ and the current at DET\_ during phase 1 and 2 of the detection.

- **Note 8:** Default values. The startup and fault times can also be programmed through the I<sup>2</sup>C serial interface (see the *Register Map and Description* section).

- Note 9: Guaranteed by design. Not subject to production testing.

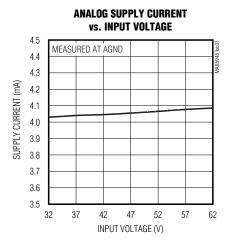

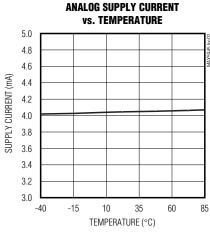

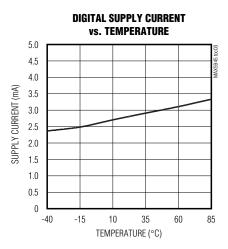

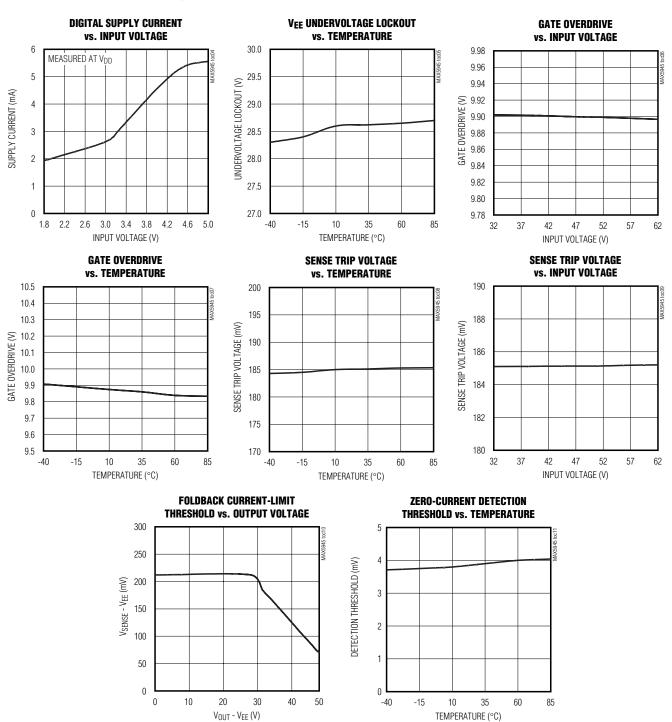

## Typical Operating Characteristics

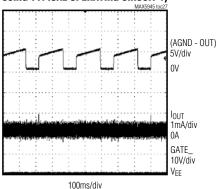

$(V_{EE} = -48V, V_{DD} = +3.3V, AUTO = AGND = DGND = 0V, \overline{RESET} = \overline{SHD}_{-} = unconnected, R_{SENSE} = 0.5\Omega$ , all registers = default setting,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

6 \_\_\_\_\_\_ /N/XI/N

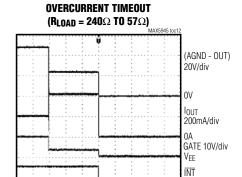

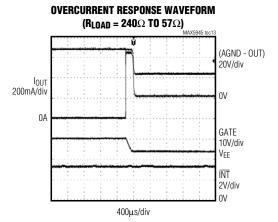

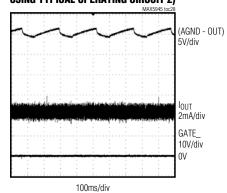

## Typical Operating Characteristics (continued)

$(V_{EE} = -48V, V_{DD} = +3.3V, AUTO = AGND = DGND = 0V, \overline{RESET} = \overline{SHD}_{-} = unconnected, R_{SENSE} = 0.5\Omega$ , all registers = default setting,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

MIXIM

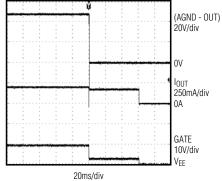

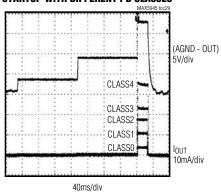

## Typical Operating Characteristics (continued)

$(V_{EE} = -48V, V_{DD} = +3.3V, AUTO = AGND = DGND = 0V, \overline{RESET} = \overline{SHD}_{-} = unconnected, R_{SENSE} = 0.5\Omega$ , all registers = default setting,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

2V/div

0V

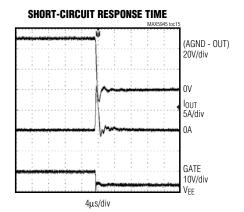

## SHORT-CIRCUIT RESPONSE TIME MAXX5945

20ms/div

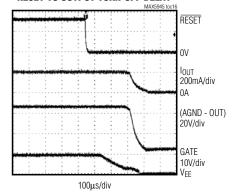

#### **RESET** TO OUTPUT TURN-OFF DELAY

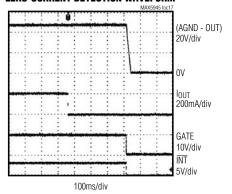

### ZERO-CURRENT DETECTION WAVEFORM

## Typical Operating Characteristics (continued)

$(V_{EE} = -48V, V_{DD} = +3.3V, AUTO = AGND = DGND = 0V, \overline{RESET} = \overline{SHD}_{-} = unconnected, R_{SENSE} = 0.5\Omega$ , all registers = default setting,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

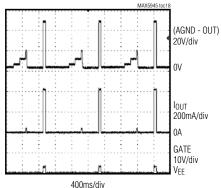

#### **OVERCURRENT RESTART DELAY**

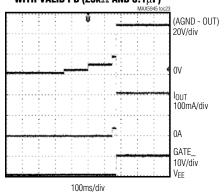

## STARTUP WITH VALID PD

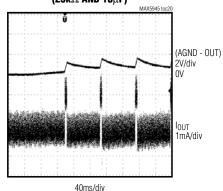

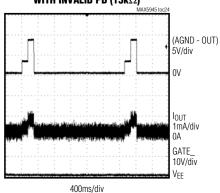

## DETECTION WITH INVALID PD (25k $\Omega$ and 10 $\mu$ F)

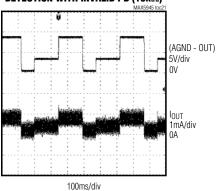

DETECTION WITH INVALID PD (15k $\Omega$ )

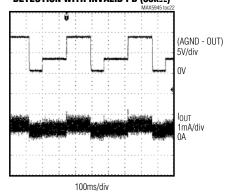

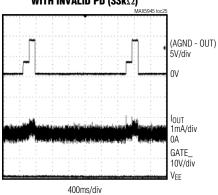

### DETECTION WITH INVALID PD (33k $\Omega$ )

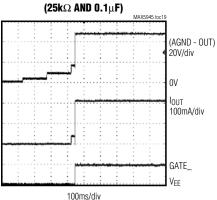

## STARTUP IN MIDSPAN MODE WITH VALID PD (25k $\Omega$ and 0.1 $\mu$ F)

## Typical Operating Characteristics (continued)

(VEE = -48V, VDD = +3.3V, AUTO = AGND = DGND = 0V,  $\overline{\text{RESET}} = \overline{\text{SHD}}$  = unconnected,  $R_{\text{SENSE}} = 0.5\Omega$ , all registers = default setting,  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted.)

## DETECTION WITH MIDSPAN MODE WITH INVALID PD (15 $k\Omega$ )

## DETECTION WITH MIDSPAN MODE WITH INVALID PD (33k $\Omega$ )

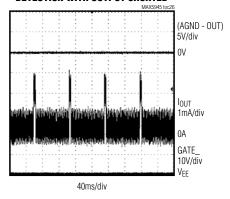

#### **DETECTION WITH OUTPUT SHORTED**

DETECTION WITH INVALID PD (OPEN CIRCUIT, USING TYPICAL OPERATING CIRCUIT 1)

## DETECTION WITH INVALID PD (OPEN CIRCUIT, USING TYPICAL OPERATING CIRCUIT 2)

### STARTUP WITH DIFFERENT PD CLASSES

10 \_\_\_\_\_\_/N/X//M

## **Pin Description**

| PIN               | NAME                              | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                 | RESET                             | Hardware Reset. Pull $\overline{\text{RESET}}$ low for at least 300µs to reset the device. All internal registers reset to their default value. The address (A0–A3), and AUTO and MIDSPAN input logic levels latch on during low-to-high transition of $\overline{\text{RESET}}$ . Internally pulled up to $V_{DD}$ with $50k\Omega$ resistor.                                                                                                                |

| 2                 | MIDSPAN                           | MIDSPAN Mode Input. An internal $50k\Omega$ pulldown resistor to DGND sets the default mode to endpoint PSE operation (power-over-signal pairs). Pull MIDSPAN TO $V_{DIG}$ to set MIDSPAN operation. The MIDSPAN value latches after the IC is powered up or reset (see the <i>PD Detection</i> section).                                                                                                                                                     |

| 3                 | ĪNT                               | Open-Drain Interrupt Output. INT goes low whenever a fault condition exists. Reset the fault condition using software or by pulling RESET low (see the <i>Interrupt</i> section of the <i>Detailed Description</i> for more information about interrupt management).                                                                                                                                                                                          |

| 4                 | SCL                               | Serial Interface Clock Line                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5                 | SDAOUT                            | Serial Output Data Line. Connect the data line optocoupler input to SDAOUT (see the <i>Typical Application Circuit</i> ). Connect SDAOUT to SDAIN if using a 2-wire I <sup>2</sup> C-compatible system.                                                                                                                                                                                                                                                       |

| 6                 | SDAIN                             | Serial Interface Input Data Line. Connect the data line optocoupler output SDAIN (see the <i>Typical Application Circuit</i> ). Connect SDAIN to SDAOUT if using a 2-wire wire I <sup>2</sup> C-compatible system.                                                                                                                                                                                                                                            |

| 7–10              | A3, A2, A1, A0                    | Address Bits. A3, A2, A1, and A0 form the lower part of the device's address. Address inputs default high with an internal $50k\Omega$ pullup resistor to $V_{DD}$ . The address values latch when $V_{DD}$ or $V_{EE}$ ramps up and exceeds its UVLO threshold or after a reset. The 3 MSB bits of the address are set to 010.                                                                                                                               |

| 11–14             | DET1, DET2,<br>DET3, DET4         | Detection and Classification Voltage Outputs. Use DET1 to set the detection and classification probe voltages on port 1. Use DET1 for the AC voltage sensing of port 1 when using the AC disconnect scheme (see the <i>Typical Application Circuit</i> ).                                                                                                                                                                                                     |

| 15                | DGND                              | Connect to Digital Ground                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 16                | $V_{\mathrm{DD}}$                 | Positive Digital Supply. Connect to digital supply (referenced to DGND).                                                                                                                                                                                                                                                                                                                                                                                      |

| 17–20             | SHD1, SHD2,<br>SHD3, SHD4         | Port Shutdown Inputs. Pull $\overline{SHD}$ low to turn off the external FET on port Internally pulled up to $V_{DD}$ with a $50k\Omega$ resistor.                                                                                                                                                                                                                                                                                                            |

| 21                | AGND                              | Analog Ground. Connect to the high-side analog supply.                                                                                                                                                                                                                                                                                                                                                                                                        |

| 22, 25,<br>29, 32 | SENSE4, SENSE3,<br>SENSE2, SENSE1 | MOSFET Source Current-Sense Negative Inputs. Connect to the source of the power MOSFET and connect a current-sense resistor between SENSE_ and V <sub>EE</sub> (see the <i>Typical Application Circuit</i> ).                                                                                                                                                                                                                                                 |

| 23, 26,<br>30, 33 | GATE4, GATE3,<br>GATE2, GATE1     | Port_ MOSFET Gate Drivers. Connect GATE_ to the gate of the external FET (see the <i>Typical Application Circuit</i> ).                                                                                                                                                                                                                                                                                                                                       |

| 24, 27,<br>31, 34 | OUT4, OUT3,<br>OUT2, OUT1         | MOSFET Drain-Output Voltage Senses. Connect OUT_ to the power MOSFET drain through a resistor (100 $\Omega$ to 100k $\Omega$ ). The low leakage at OUT_ limits the drop across the resistor to less than 100mV (see the <i>Typical Application Circuit</i> ).                                                                                                                                                                                                 |

| 28                | VEE                               | Low-Side Analog Supply Input. Connect the low-side analog supply to VEE (-48V). Bypass with a 1µF capacitor between AGND and VEE.                                                                                                                                                                                                                                                                                                                             |

| 35                | AUTO                              | AUTO or SHUTDOWN Mode Input. Force high to enter AUTO mode after a reset or power-up. Drive low to put the MAX5945 into SHUTDOWN mode. In SHUTDOWN mode, software controls the operational modes of the MAX5945. A $50k\Omega$ internal pulldown resistor defaults AUTO low. AUTO latches when $V_{DD}$ or $V_{EE}$ ramps up and exceeds its UVLO threshold or when the device resets. Software commands can take the MAX5945 out of AUTO while AUTO is high. |

| 36                | OSC_IN                            | Oscillator Input. AC-disconnect detection function uses OSC_IN. Connect a 100Hz ±10%, 2VP-P ±5%, +1.2V offset sine wave to OSC_IN. If the oscillator positive peak falls below the OSC_FAIL threshold of 2V, the ports that have the AC function enabled shut down and are not allowed to power up. When not using the AC-disconnect detection function, leave OSC_IN unconnected.                                                                            |

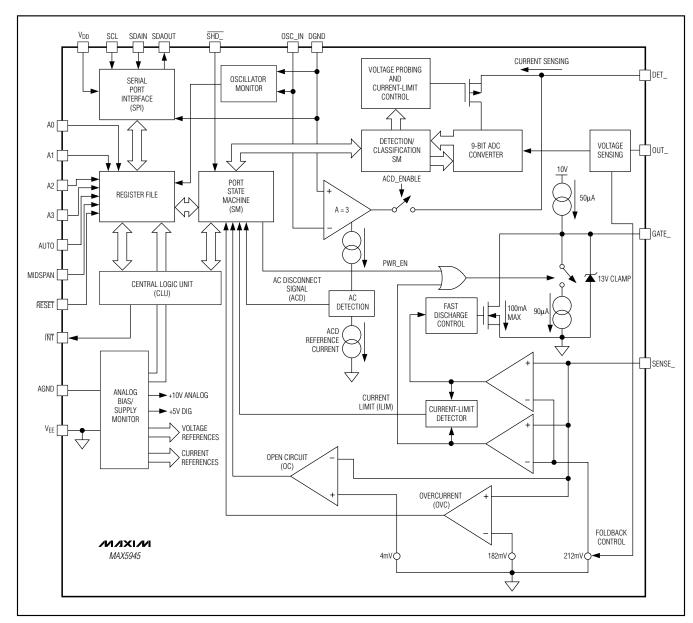

Figure 1. MAX5945 Functional Diagram

## Detailed Description

The MAX5945 four-port network power controller controls -32V to -60V negative supply rail systems. Use the MAX5945, which is compliant with the IEEE 802.3af standard for PSE in power-over-LAN applications. The MAX5945 provides PD discovery, classification, current limit, both DC and AC load disconnect detections, and other necessary functions for an IEEE 802.3af-compli-

ant PSE. The MAX5945 can be used in either endpoint PSE (LAN switch/router) or midspan PSE (power injector) applications.

The MAX5945 is fully software-configurable and programmable with more than 25 internal registers. The device features an I<sup>2</sup>C-compatible, 3-wire serial interface and a class-overcurrent detection. The class-overcurrent detection function enables system power man-

agement where it detects a PD that draws more current than the allowable amount for its class. The MAX5945's extensive programmability enhances system flexibility and allows for uses in other applications.

The MAX5945 has four different operating modes: auto mode, semi-auto mode, manual mode, and shutdown mode (see the *Operation Modes* section). A special watchdog feature allows the hardware to gracefully take over control if the software/firmware crashes. A cadence timing feature allows the MAX5945 to be used in midspan systems.

The MAX5945 provides input undervoltage lockout, input undervoltage detection, input overvoltage lockout, overtemperature protection, output-voltage slew-rate limit during startup, power-good status, and fault status. The MAX5945's programmability includes gate-charging current, current-limit threshold, startup timeout, overcurrent timeout, autorestart duty cycle, PD disconnect AC detection threshold and PD disconnect detection timeout.

The MAX5945 communicates with the system microcontroller through an  $I^2C$ -compatible interface. The MAX5945 features separate input and output data lines (SDAIN and SDAOUT) for use with optocoupler isolation. The MAX5945 is a slave device. Its four address inputs allow 16 unique MAX5945 addresses. A separate  $\overline{INT}$  output and four independent shutdown inputs ( $\overline{SHD}$ ) allow fast interrupt signals between the MAX5945 and the microcontroller. A  $\overline{RESET}$  input allows hardware reset of the device.

#### Reset

Reset is a condition the MAX5945 enters after any of the following conditions:

- After power-up (VEE and VDD rise above their UVLO thresholds).

- Hardware reset. The RESET input is driven low and up high again any time after power-up.

- Software reset. Writing a 1 into R1Ah[4] any time after power-up.

- Thermal shutdown.

During a reset, the MAX5945 resets its register map to the reset state as shown in Table 30 and latches in the state of AUTO (pin 35) and MIDSPAN (pin 2). During normal operation, changes at the AUTO and MIDSPAN inputs are ignored. While the condition that caused the reset persists (i.e., high temperature, RESET input low, or UVLO conditions) the MAX5945 will not acknowledge any addressing from the serial interface.

#### Port Reset (R1Ah[3:0])

Set high anytime during normal operation to turn off power and clear the events and status registers of the corresponding port. Port reset only resets the events and status registers.

#### **Operation Modes**

The MAX5945 contains four independent but identical state machines to provide reliable and real-time control of the four network ports. Each state machine has four different operating modes: auto, semi-auto, manual, and shutdown. Auto mode allows the device to operate automatically without any software supervision. Semiauto mode, upon request, continuously detects and classifies a device connected to a port but does not power up that port until instructed by software. Manual mode allows total software control of the device and is useful in system diagnostic. Shutdown mode terminates all activities and securely turns off power to the ports. Switching between AUTO, SEMI, or MANUAL mode does not take effect until the part finishes its current task. When the port is set into SHUTDOWN mode, all the port operations are immediately stopped and the port remains idle until SHUTDOWN is exited.

#### Automatic (AUTO) Mode

Enter automatic (AUTO) mode by forcing the AUTO input high prior to a reset, or by setting R12h[P\_ M1,P\_M0] to [1,1] during normal operation (see Tables 15 and 15a). In AUTO mode, the MAX5945 performs detection, classification, and powers up the port automatically once a valid PD is detected at the port. If a valid PD is not detected at the port, the MAX5945 repeats the detection routine continuously until a valid PD is detected.

Going into AUTO mode, the DET\_EN and CLASS\_EN bits are set to high and stay high unless changed by software. Using software to set DET\_EN and/or CLASS\_EN low causes the MAX5945 to skip detection and/or classification. As a protection, disabling the detection routine in AUTO mode will not allow the corresponding port to power up, unless the DET\_BYP (R23H[4]) is set to 1.

The AUTO status is latched into the register only during a reset. Any changes to the AUTO input after reset is ignored.

#### Semi-Automatic (SEMI) Mode

Enter semi-automatic (SEMI) mode by setting R12h[P\_M1,P\_M0] to [1,0] during normal operation (see Tables 15 and 15a). In SEMI mode, the MAX5945, upon request, performs detection and/or classification repeatedly but does not power up the port(s), regardless of the status of the port connection.

Setting R19h[PWR\_ON\_] (Table 21) high immediately terminates detection/classification routines and turns on power to the port(s).

R14h[DET\_EN\_, CLASS\_EN\_] default to low in SEMI mode. Use software to set R14h[DET\_EN\_, CLASS\_EN\_] to high to start the detection and/or classification routines. R14h[DET\_EN\_, CLASS\_EN\_] are reset every time the software commands a power-off of the port (either through reset or PWR\_OFF). In any other case, the status of the bits is left unchanged (including when the state machine turns off the power because a load disconnect or a fault condition is encountered).

#### MANUAL Mode

Enter MANUAL mode by setting R12h[P\_M1,P\_M0] to [0,1] during normal operation (see Tables 15 and 15a). MANUAL mode allows the software to dictate any sequence of operation. Write a 1 to both R14h[DET\_EN\_] and R14h[CLASS\_EN\_] start detection and classification operations, respectively, and in that priority order. After execution, the command is cleared from the register(s). PWR\_ON\_ has highest priority. Setting PWR\_ON\_ high at any time causes the device to immediately enter the powered mode. Setting DET\_EN and CLASS\_EN high at the same time causes detection to be performed first. Once in the powered state, the device ignores DET\_EN\_ or CLASS\_EN\_ commands.

When switching to MANUAL mode from another mode, DET\_EN\_, CLASS\_EN\_ default to low. These bits become pushbutton rather than configuration bits (i.e., writing ones to these bits while in MANUAL mode commands the device to execute one cycle of detection and/or classification. The bits are reset back to zeros at the end of the execution). Putting the MAX5945 into shutdown mode immediately turns off power and halts all operations to the corresponding port. The event and status bits of the affected port(s) are also cleared. In SHUTDOWN mode, the DET\_EN\_, CLASS\_EN\_, and PWR\_ON\_ commands are ignored.

In SHUTDOWN mode, the serial interface operates normally.

#### Watchdog

R1Dh, R1Eh, and R1Fh registers control watchdog operation. The watchdog function, when enabled, allows the MAX5945 to gracefully take over control or securely shut down the power to the ports in case of software/firmware crashes. Contact the factory for more details.

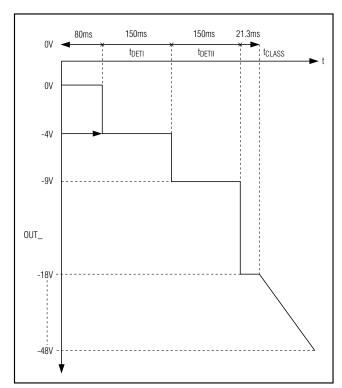

#### **PD Detection**

When PD detection is activated, the MAX5945 probes the output for a valid PD. After each detection cycle, the device sets the DET\_END\_ bit R04h/05h[3:0] high and reports the detection results in the status registers R0Ch[2:0], R0Dh[2:0], R0Eh[2:0], and R0Fh[2:0]. The DET\_END\_ bit is reset to low when read through R05h or after a port reset. Both DET\_END\_ bit status registers are cleared after the port powers down.

A valid PD has a  $25k\Omega$  discovery signature characteristic as specified in the IEEE 802.3af standard. Table 1 shows the IEEE 802.3af specification for a PSE detecting a valid PD signature (see the *Typical Application Circuit* and Figure 2). The MAX5945 can probe and categorize different types of devices connected to the port such as a valid PD, an open circuit, a low resistive load, a high resistive load, a high capacitive load, a positive DC supply, or a negative DC supply.

During detection, the MAX5945 turns off the external MOSFET and forces two probe voltages through the DET\_ input. The current through the DET\_ input is measured as well as the voltage at OUT\_. A two-point slope measurement is used as specified by the IEEE 802.3af standard to verify the device connected to the port. The MAX5945 implements appropriate settling times and a 100ms digital integration to reject 50Hz/60Hz power-line noise coupling.

An external diode, in series with the DET\_ input, restricts PD detection to the 1st quadrant as specified by the IEEE 802.3af standard. To prevent damage to non-PD devices and to protect itself from an output short circuit, the MAX5945 limits the current into DET\_ to less than 2mA maximum during PD detection.

In midspan mode, the MAX5945 waits 2.2s before attempting another detection cycle after every failed detection. The first detection, however, happens immediately after issuing the detection command.

## Power Device Classification (PD Classification)

During the PD classification mode, the MAX5945 forces a probe voltage (-18V) at DET\_ and measures the current into DET\_. The measured current determines the class of the PD.

After each classification cycle, the device sets the CL\_END\_ bit (R04h/05h[7:4]) high and reports the classification results in the status registers R0Ch[6:4], R0Dh[6:4], R0Eh[6:4], and R0Fh[6:4]. The CL\_END\_ bit is reset to low when read through register R05h or after a port reset. Both Class\_END\_ bit status registers are cleared after the port powers down.

## Table 1. PSE PI Detection Modes Electrical Requirement (Table 33-2 of the IEEE 802.3af Standard)

| PARAMETER                                 | SYMBOL              | MIN  | MAX  | UNITS | ADDITIONAL INFORMATION                                |

|-------------------------------------------|---------------------|------|------|-------|-------------------------------------------------------|

| Open-Circuit Voltage                      | Voc                 | _    | 30   | V     | In detection mode only                                |

| Short-Circuit Current                     | Isc                 | 1    | 5    | mA    | In detection mode only                                |

| Valid Test Voltage                        | V <sub>V</sub> ALID | 2.8  | 10   | V     |                                                       |

| Voltage Difference Between<br>Test Points | ΔV <sub>TEST</sub>  | 1    | _    | V     |                                                       |

| Time Between Any Two Test<br>Points       | t <sub>BP</sub>     | 2    | _    | ms    | This timing implies a 500Hz maximum probing frequency |

| Slew Rate                                 | V <sub>SLEW</sub>   | _    | 0.1  | V/µs  |                                                       |

| Accept Signature Resistance               | R <sub>GOOD</sub>   | 19   | 26.5 | kΩ    |                                                       |

| Reject Signature Resistance               | R <sub>BAD</sub>    | < 15 | > 33 | kΩ    |                                                       |

| Open-Circuit Resistance                   | Ropen               | 500  | _    | kΩ    |                                                       |

| Accept Signature<br>Capacitance           | CGOOD               | l    | 150  | nF    |                                                       |

| Reject Signature<br>Capacitance           | C <sub>BAD</sub>    | 10   | _    | μF    |                                                       |

| Signature Offset Voltage<br>Tolerance     | Vos                 | 0    | 2.0  | V     |                                                       |

| Signature Offset Current<br>Tolerance     | los                 | 0    | 12   | μA    |                                                       |

## Table 2. PSE Classification of a PD (Table 33-4 of the IEEE 802.3af Standard)

| MEASURED ICLASS (mA) | CLASSIFICATION          |

|----------------------|-------------------------|

| 0 to 5               | Class 0                 |

| > 5 and < 8          | May be Class 0 and 1    |

| 8 to 13              | Class 1                 |

| > 13 and < 16        | May be Class 0, 1, or 2 |

| 16 to 21             | Class 2                 |

| > 21 and < 25        | May be Class 0, 2, or 3 |

| 25 to 31             | Class 3                 |

| > 31 and <35         | May be Class 0, 3, or 4 |

| 35 to 45             | Class 4                 |

| > 45 and < 51        | May be Class 0 or 4     |

Table 2 shows the IEEE 802.3af requirement for a PSE classifying a PD at the power interface (PI).

#### **Powered State**

When the part enters PWR MODE, the  $t_{START}$  and  $t_{DISC}$  timers are reset. Before turning on the power, the part

checks if any other port is not turning on and if the tfault timer is zero. Another check is performed if the ACD\_EN bit is set, in this case OSC\_FAIL bit must be low (oscillator is okay) for the port to be powered.

If these conditions are met then the part enters startup where it turns on power to the port. An internal signal, POK\_, is asserted high when  $V_{OUT}$  is within 2V from VEE. PGOOD\_ status bits are set high if POK\_ stays high longer than  $t_{PGOOD}$ . PGOOD immediately resets when POK goes low.

The PWR\_CHG bit sets when a port powers up or down. PWR\_EN sets when a port powers up and resets when a port shuts down. The port shutdown timer lasts 0.5ms and prevents other ports from turning off during that period, except in the case of emergency shutdowns (RESET = L, RESET\_IC = H, VEEUVLO, VDDUVLO, and TSHD).

The MAX5945 always checks the status of all ports before turning off. A priority logic system determines the order to prevent the simultaneous turn-on or turn-off of the ports. The port with the lesser ordinal number gets priority over the others (i.e., port 1 turns on first, port 2 second, port 3 third and port 4 fourth). Setting PWR\_OFF\_ high turns off power to the corresponding port.

Figure 2. Detection, Classification, and Power-Up Port Sequence

Figure 3. PGOOD Timing

#### **Overcurrent Protection**

A sense resistor (Rs), connected between SENSE\_ and VEE, monitors the load current. Under all circumstances, the voltage across Rs never exceeds the threshold Vsu Lim. If SENSE\_ exceeds Vsu Lim, an internal current-limiting circuit regulates the GATE voltage, limiting the current to I I M = VSU I M / Rs. During transient conditions, if the SENSE\_ voltage exceeds VSU LIM. a fast pulldown circuit activates to quickly recover from the current overshoot. During startup, if the current-limit condition persists, when the startup timer, tSTART, times out, the port shuts off and the STRT\_FLT\_ bit is set. In normal powered state, the MAX5945 checks for overcurrent conditions as determined by VFLT LIM = ~88% of VSU LIM. The tFAULT counter sets the maximum allowed continuous overcurrent period. The trault counter increases when VSENSE exceeds VFLT LIM and decreases at a slower pace when VSENSE drops below VFLT LIM. A slower decrement for the tFAULT counter allows for detecting repeated short-duration overcurrents. When the counter reaches the tFAULT limit, the MAX5945 powers off the port and asserts the IMAX\_FLT\_ bit. For a continuous overstress, a fault latches exactly after a period of tfault. VSU LIM, is programmable using R27h[4-7]. tFAULT is programmable using R16h[2-3] and R28[4-7].

After power-off due to an overcurrent fault, and if the RSTR\_EN bit is set, the tFAULT timer is not immediately reset but starts decrementing at the same slower pace. The MAX5945 allows the port to be powered on only when the tFAULT counter is at zero. This feature sets an automatic duty-cycle protection to the external MOSFET to avoid overheating. The duty cycle is programmable using R16h[6-7].

The MAX5945 continuously flags when the current exceeds the maximum current allowed for the class as indicated in the CLASS status register. When class overcurrent occurs, the MAX5945 sets the IVC bit in register R09h.

#### Foldback Current

During startup and normal operation, an internal circuit senses the voltage at OUT\_ and reduces the current-limit value when (VOUT\_ - VEE) > 30V. The foldback function helps to reduce the power dissipation on the FET. The current limit eventually reduces to 1/3 of  $I_{LIM}$  when (VOUT\_ - VEE) > 50V (see Figure 4).

Figure 4. Foldback Current Characteristics

#### **MOSFET Gate Driver**

Connect the gate of the external n-channel MOSFET to GATE\_. An internal 50µA current source pulls GATE\_ to (VEE + 10V) to turn on the MOSFET. An internal 40µA current source pulls down GATE\_ to VEE to turn off the MOSFET.

The pullup and pulldown current controls the maximum slew rate at the output during turn-on or turn-off. The pullup current (gate-charging current) is programmable using R23h[5-7]. Use the following equation to set the maximum slew rate:

$$\frac{\Delta V_{OUT}}{\Delta t} = \frac{I_{GATE}}{C_{GD}}$$

where C<sub>GD</sub> is the total capacitance between GATE and DRAIN of the external FET. Current limit and the capacitive load at the drain control the slew rate during start-up. During current-limit regulation, the MAX5945 manipulates the GATE\_ voltage to control the voltage at SENSE\_. A fast pulldown activates if SENSE\_ overshoots the limit threshold. The fast pulldown current increases with the amount of overshoot. The maximum fast pulldown current is 100mA.

During turn-off, when the GATE voltage reaches a value lower than 1.2V, a strong pulldown switch is activated to keep the FET securely off.

#### **Digital Logic**

V<sub>DD</sub> supplies power for the internal logic circuitry. V<sub>DD</sub> ranges from +1.71V to +3.7V and determines the logic thresholds for the CMOS connections (SDAIN, SDAOUT, SCL, AUTO, SHD\_, A\_). This voltage range enables the MAX5945 to interface with a nonisolated low-voltage microcontroller. The MAX5945 checks the

digital supply for compatibility with the internal logic. The MAX5945 also features a VDD undervoltage lockout (VDDUVLO) of +1.35V. A VDDUVLO condition keeps the MAX5945 in reset and the ports shut off. Bit 0 in the supply event register shows the status of VDDUVLO (Table 11) after VDD has recovered. All logic inputs and outputs reference to DGND. DGND and AGND are completely isolated internally to the MAX5945. In a completely isolated system, the digital signal can be referenced indifferently to VAGND or VEE or at voltages even higher than AGND (up to 60V). VDD - VDGND must be greater than 3.0V when VDGND  $\leq$  (VEE + 3.0V)

When using the AC disconnect detection feature, AGND must be connected directly to DGND and  $V_{DD}$  must be greater than +3V. In this configuration, connect DGND to AGND at a single point in the system as close to MAX5945 as possible.

#### **Hardware Shutdown**

SHD\_ shuts down the respective ports without using the serial interface. Hardware shutdown offers an emergency turn-off feature that allows a fast disconnect of the power supply from the port. Pull SHD\_ low to remove power.

#### Interrupt

The MAX5945 contains an open-drain logic output (INT) that goes low when an interrupt condition exists. R00h and R01h (Tables 5 and 6) contain the definitions of the interrupt registers. The mask register R01h determines events that trigger an interrupt. As a response to an interrupt, the controller reads the status of the event register to determine the cause of the interrupt and takes subsequent actions. Each interrupt event register also contains a clear-on-read (CoR) register. Reading through the CoR register address clears the interrupt. INT remains low when reading the interrupt through the read-only addresses. For example, to clear a startup fault on port 4 read address 09h (see Table 10). Use the global pushbutton bit on register 1Ah (bit 7, Table 22) to clear interrupts, or use a software or hardware reset.

#### **Undervoltage and Overvoltage Protection**

The MAX5945 contains several undervoltage and overvoltage protection features. Table 11 in the *Register Map and Description* section shows a detailed list of the undervoltage and overvoltage protection features. An internal VEE undervoltage lockout (VEEUVLO) circuit keeps the MOSFET off and the MAX5945 in reset until VAGND - VEE exceeds 29V for more than 3ms. An internal VEE overvoltage (VEE\_OV) circuit shuts down the ports when (VAGND - VEE) exceeds 60V. The digital supply also contains an undervoltage lockout (VDDUVLO).

The MAX5945 also features three other undervoltage and overvoltage interrupts: VEE undervoltage interrupt (VEEUV), VDD undervoltage interrupt (VDDUV), and VDD overvoltage interrupt (VDDOV). A fault latches into the supply events register (Table 11) but the MAX5945 does not shut down the ports with a VEEUV, VDDUV, or VDDOV.

#### **DC** Disconnect Monitoring

Setting R13h[DCD\_EN\_] bits high enable DC load monitoring during a normal powered state. If SENSE\_ falls below the DC load disconnect threshold, VDCTH, for more than tDISC, the device turns off power and asserts the LD\_DISC\_ bit of the corresponding port. tDISC is programmable using R16h[0-1] and R27h[0-3].

#### **AC Disconnect Monitoring**

The MAX5945 features AC load disconnect monitoring. Connect an external sine wave to OSC\_IN. The oscillator requirements are:

- Frequency x  $V_{P-P} = 200V_{P-P} \times Hz \pm 15\%$

- Positive peak voltage > +2V

- Frequency > 60Hz

- A 100Hz ±10%, 2Vp-p ±5%, with +1.2V offset (Vpeak = +2.2V, typ) is recommended.

The MAX5945 buffers and amplifies 3x the external oscillator signal and sends the signal to DET\_, where the sine wave is AC coupled to the output. The MAX5945 senses the presence of the load by monitoring the amplitude of the AC current returned to DET\_ (see the *Functional Diagram*).

Setting R13h[ACD\_EN\_] bits high enable AC load disconnect monitoring during the normal powered state. If the AC current peak at the DET\_ pin falls below IACTH for more than tDISC, the device turns off power and asserts the LD\_DISC\_ bit of the corresponding port. IACTH is programmable using R23h[0-3].

An internal comparator checks for a proper amplitude of the oscillator input. If the positive peak of the input sinusoid falls below a safety value of 2V, OSC\_FAIL sets and the port shuts down. Power cannot be applied to the ports when ACD\_EN is set high and OSC\_FAIL is set high. Leave OSC\_IN unconnected or connect it to DGND when not using AC disconnect detection.

When using the AC disconnect detection feature, connect AGND directly to DNGD as close as possible to the IC. The MAX5945 also requires a V<sub>DD</sub> of greater than +3V for this function. See the *Typical Application Circuit* with AC disconnect for other external component requirements.

#### Table 3. MAX5945 Address

| 0 1 0 | АЗ | A2 | A1 | A0 | R/W |

|-------|----|----|----|----|-----|

|-------|----|----|----|----|-----|

#### Thermal Shutdown

If the MAX5945 die temperature reaches +150°C, an overtemperature fault generates and the MAX5945 shuts down and the MOSFETs turn off. The die temperature of the MAX5945 must cool down below +130°C to remove the overtemperature fault condition. After a thermal shutdown, the part is reset.

#### **Address Inputs**

A3, A2, A1, and A0 represent the four LSBs of the chip address, the complete 7-bit chip address (see Table 3).

The four LSBs latch on the low-to-high transition of RESET or after a power-supply start (either on V<sub>DD</sub> or V<sub>EE</sub>). Address inputs default high through an internal  $50k\Omega$  pullup resistor to V<sub>DD</sub>. The MAX5945 also responds to the call through a global address 60h (see the *Global Addressing and Alert Response Protocol* section).

### I<sup>2</sup>C-Compatible Serial Interface

The MAX5945 operates as a slave that sends and receives data through an I<sup>2</sup>C-compatible, 2-wire or 3-wire interface. The interface uses a serial data input line (SDAIN), a serial data output line (SDAOUT), and a serial clock line (SCL) to achieve bidirectional communication between master(s) and slave(s). A master (typically a microcontroller) initiates all data transfers to and from the MAX5945, and generates the SCL clock that synchronizes the data transfer. In most applications, connect the SDAIN and the SDAOUT lines together to form the serial data line (SDA).

Using the separate input and output data lines allows optocoupling with the controller bus when an isolated supply powers the microcontroller.

The MAX5945 SDAIN line operates as an input. The MAX5945 SDAOUT operates as an open-drain output. A pullup resistor, typically 4.7k $\Omega$ , is required on SDAOUT. The MAX5945 SCL line operates only as an input. A pullup resistor, typically 4.7k $\Omega$ , is required on SCL if there are multiple masters, or if the master in a single-master system has an open-drain SCL output.

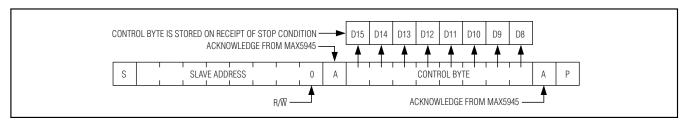

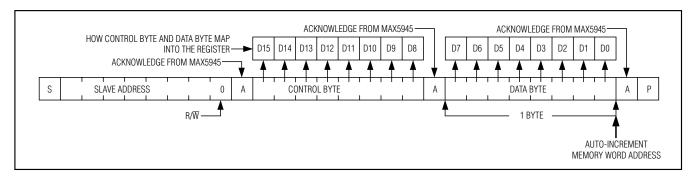

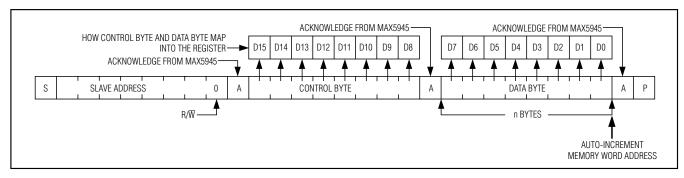

#### Serial Addressing

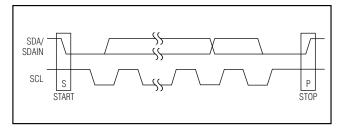

Each transmission consists of a START condition (Figure 7) sent by a master, followed by the MAX5945 7-bit slave address plus R/W bit, a register address byte, one or more data bytes, and finally a STOP condition.

Figure 5. 2-Wire Serial Interface Timing Details

Figure 6. 3-Wire Serial Interface Timing Details

Figure 7. Start and Stop Conditions

##

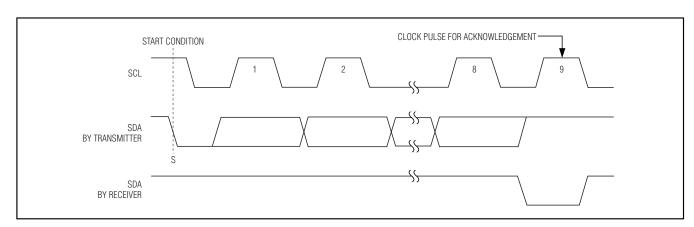

Figure 8. Bit Transfer

#### Start and Stop Conditions

Both SCL and SDA remain high when the interface is not busy. A master signals the beginning of a transmission with a START (S) condition by transitioning SDA from high to low while SCL is high. When the master fin-

ishes communicating with the slave, the master issues a STOP (P) condition by transitioning SDA from low to high while SCL is high. The stop condition frees the bus for another transmission.

Figure 9. Acknowledge

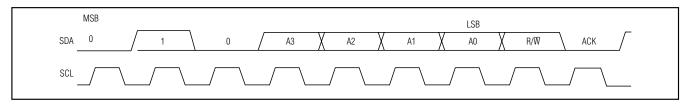

Figure 10. Slave Address

#### Bit Transfer

Each clock pulse transfers one data bit (Figure 8). The data on SDA must remain stable while SCL is high.

### Acknowledge

The acknowledge bit is a clocked 9th bit (Figure 9), which the recipient uses as a handshake receipt of each byte of data. Thus each byte effectively transferred requires 9 bits. The master generates the 9th clock pulse, and the recipient pulls down SDA (or the SDAOUT in the 3-wire interface) during the acknowledge clock pulse, so the SDA line is stable low during the high period of the clock pulse. When the master transmits to the MAX5945, the MAX5945 generates the acknowledge bit. When the MAX5945 transmits to the master, the master generates the acknowledge bit.

### Slave Address

The MAX5945 has a 7-bit long slave address (Figure 10). The bit following the 7-bit slave address (bit eight) is the R/W bit, which is low for a write command and high for a read command.

010 always represent the first three bits (MSBs) of the MAX5945 slave address. Slave address bits A3, A2, A1, and A0 represent the states of the MAX5945's A3, A2, A1, and A0 inputs, allowing up to sixteen MAX5945 devices to share the bus. The states of the A3, A2, A1,

and A0 latch in upon the reset of the MAX5945 into register R11h. The MAX5945 monitors the bus continuously, waiting for a START condition followed by the MAX5945's slave address. When the MAX5945 recognizes its slave address, it acknowledges and is then ready for continued communication.

#### Global Addressing and Alert Response Protocol