# Nano Power Buck-Boost with Input Voltage Monitor

### **General Description**

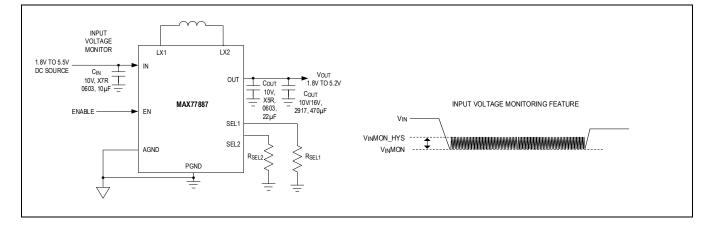

The MAX77887 is a high-efficiency nano power buckboost converter with an input voltage monitoring feature, ensuring that the battery voltage does not drop below the pre-set threshold levels to protect the battery.

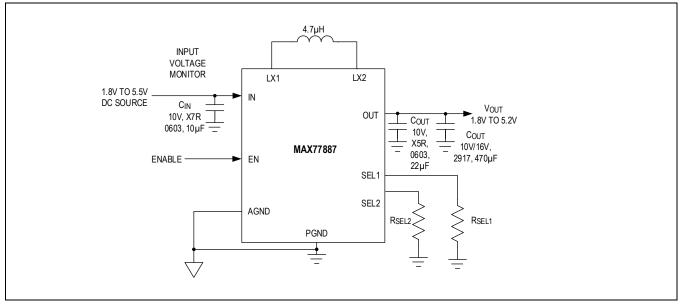

The converter operates on an input supply between 1.8V and 5.5V. Output voltage between 1.8V and 5.2V is configured through a resistor connected to the hardware control pin,  $R_{SEL1}$ . It can operate in CCM, Skip, and Low Power Mode to ensure maximum efficiency over a wide range of load currents.

MAX77887 offers two unique hardware control pins R<sub>SEL1</sub> and R<sub>SEL2</sub>. The resistor connected at SEL1 (R<sub>SEL1</sub>) selects the predefined output voltage from 1.8V to 5.2V as OUT. The resistor connected at SEL2 (R<sub>SEL2</sub>) allows the configuration of two different Switching Current Limit (I<sub>LIM</sub>) levels and 16 Input Voltage Monitoring Threshold levels.

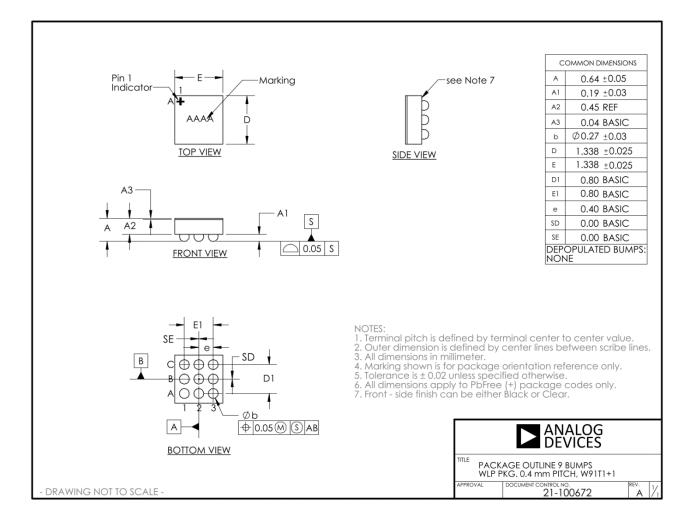

The MAX77887 is available in 1.36mm x 1.36mm, 9bump, 0.4mm pitch, wafer-level package (WLP).

### **Applications**

- LPWAN SoC Companion Power Solution

- IoT and Wearable Applications

- Asset Trackers

- Smart Meters

#### **Benefits and Features**

- 1.8V to 5.5V Input Voltage

- Output Voltage from 1.8V to 5.2V

- Peak Efficiency of 92.5% (5.5V<sub>IN</sub>, 3.8V<sub>OUT</sub>)

- 430nA Typical Quiescent Current

- 10nA Shutdown Current

- R<sub>SEL</sub> Configurations

- Output Voltage

- 400mA/200mA Switching Current Limit

- 16 Input Voltage Monitoring Threshold Levels

- Protection Features

- Input Undervoltage Lockout (UVLO)

- Switching Current Limit

- Thermal Shutdown (THS)

- 1.36mm x 1.36mm, 9-Bump, 0.4mm Pitch, WLP

Ordering Information appears at end of data sheet.

# 1-Cell Buck-Boost Converter with Input Voltage Protection Application Circuit

# Nano Power Buck-Boost with Input Voltage Monitor

### **Absolute Maximum Ratings**

| IN, OUT, LX1, LX2 to GND               | 0.3V to +6.0V                     |

|----------------------------------------|-----------------------------------|

| EN, SEL1, SEL2 to GND                  | 0.3V to V <sub>IN</sub> + 0.3V    |

| Continuous Power Dissipation for WLP F | Package at T <sub>A</sub> = +70°C |

| (derate 11.91mW/°C above +70°C) (Not   | te 1)952.56mW                     |

| Maximum Junction Temperature   | +150°C          |

|--------------------------------|-----------------|

| Storage Temperature Range      | -65°C to +150°C |

| Soldering Temperature (reflow) | +260°C          |

Note 1: Package thermal measurement is based on the JESD-51 series.

Note 2: Thermal parameters are based on FR-4, 4-layer board.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Package Information**

| Package Code                                       | W91T1+1          |  |  |

|----------------------------------------------------|------------------|--|--|

| Outline Number                                     | <u>21-100672</u> |  |  |

| Land Pattern Number Refer to Application Note 1891 |                  |  |  |

| Thermal Resistance, Four Layer Board:              |                  |  |  |

| Junction-to-Ambient (θ <sub>JA</sub> )             | 83.98°C/W        |  |  |

For the latest package outline information and land patterns (footprints), go to <u>www.analog.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a fourlayer board. For detailed information on package thermal considerations, refer to <u>www.analog.com/thermal-tutorial</u>.

# Nano Power Buck-Boost with Input Voltage Monitor

# Nano Power Buck-Boost with Input Voltage Monitor

# **Electrical Characteristics**

(Typical values are at  $T_J \approx T_A = +25^{\circ}$ C,  $V_{IN} = +3.6$ V,  $V_{OUT} = +3.3$ V, unless otherwise specified. Limits are 100% tested at  $T_J = +25^{\circ}$ C. Limits over the operating temperature range ( $T_J = -40^{\circ}$ C to  $+125^{\circ}$ C) and relevant supply voltage range are guaranteed by design and characterization unless otherwise noted.)

| PARAMETER                               | SYMBOL                                    | CONDITIONS                                                                                                                |                                                   | MIN  | TYP  | MAX  | UNITS |

|-----------------------------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|------|------|------|-------|

| INPUT SUPPLY                            |                                           |                                                                                                                           |                                                   |      |      |      |       |

| Operating Voltage<br>Range              | VIN                                       |                                                                                                                           |                                                   | 1.8  |      | 5.5  | V     |

| Input Undervoltage<br>Lockout           | VUVLO_rising                              |                                                                                                                           |                                                   | 1.7  | 1.75 | 1.8  | V     |

| UVLO Hysteresis                         | VUVLO_Hys                                 | VUVLO_rising - VUV                                                                                                        | /LO_falling                                       |      | 60   |      | mV    |

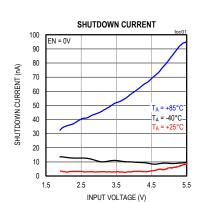

| Shutdown Supply<br>Current              | ISHDN                                     | EN = LOW, TJ = +2                                                                                                         | 5°C                                               |      | 10   | 100  | nA    |

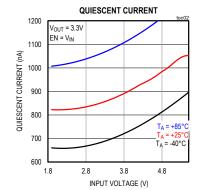

| Input Quiescent Current                 | lQ                                        | EN = HIGH, no swite                                                                                                       | ching, Tյ = +25°C                                 |      | 430  | 930  | nA    |

| OUTPUT VOLTAGE                          |                                           |                                                                                                                           |                                                   |      |      |      |       |

| Output Voltage Range                    | Vout                                      |                                                                                                                           |                                                   | 1.8  |      | 5.2  | V     |

| Output Voltage                          | VOUT AGO                                  | In CCM mode, T <sub>J</sub> =                                                                                             | -40°C to +125°C                                   | -2   |      | +2   | 0/    |

| Accuracy                                | VOUT_ACC                                  | LPM and Skip mode                                                                                                         | at TJ = 25°C                                      | -1.0 |      | +4.0 | %     |

| EN LOGIC LEVEL                          |                                           |                                                                                                                           |                                                   |      |      |      |       |

| Input LOW Level                         | VIL                                       |                                                                                                                           |                                                   |      |      | 0.4  | V     |

| Input HIGH Level                        | VIH                                       |                                                                                                                           |                                                   |      |      |      | V     |

| THERMAL PROTECTION                      | N                                         | ·                                                                                                                         |                                                   |      |      |      | -     |

| Thermal Shutdown<br>Threshold           | TSHDN                                     | T <sub>J</sub> rising                                                                                                     |                                                   |      | 165  |      | °C    |

| Thermal shutdown<br>Hysteresis          | T <sub>HYS</sub>                          | TSHDN_R-TSHDN_F                                                                                                           |                                                   |      | 20   |      | °C    |

| BUCK-BOOST REGULA                       | TOR                                       |                                                                                                                           |                                                   |      |      |      |       |

| High-Side Switching                     | LIM                                       | V <sub>IN</sub> = 1.8V to 5.5V,                                                                                           | 66.5kΩ ≤ $R_{SEL2}$                               | 340  | 400  | 460  |       |

| Current Limit                           | 'L IIVI                                   | L = 4.7µH                                                                                                                 | R <sub>SEL2</sub> ≤ 56.2kΩ                        | 160  | 200  | 240  | mA    |

| Low-Side Switch On<br>Resistance        | R <sub>DSON_LOW</sub>                     | I <sub>LX</sub> = +180mA                                                                                                  |                                                   |      | 250  |      | mΩ    |

| High-Side Switch On<br>Resistance       | R <sub>DSON_HIGH</sub>                    | I <sub>LX</sub> = -180mA                                                                                                  |                                                   |      | 250  |      | mΩ    |

| Turn-On Delay Time                      | <sup>t</sup> DLY_EN                       | Delay from rising edge of EN signal to<br>start of output voltage ramp                                                    |                                                   |      | 1.6  | 2.7  | ms    |

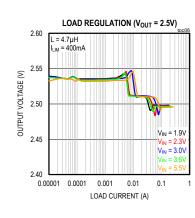

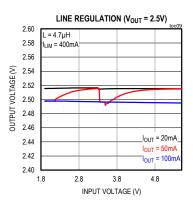

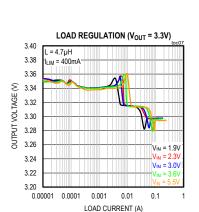

| Line Regulation                         | $\Delta V / \Delta V_{INx}$               | V <sub>IN</sub> = 1.8V to 5.5V, I <sub>OUT</sub> = 0A, 50mA                                                               |                                                   | -1.1 |      | +1.1 | %     |

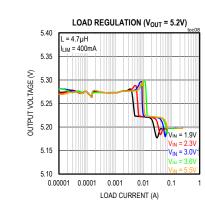

| Load Regulation                         | ΔV ILLIM = 400mA, VII<br>IOUT = 10mA to 7 | I <sub>OUT</sub> = 10mA to 200mA (CCM mode),<br>I <sub>LIM</sub> = 400mA, V <sub>IN</sub> = 3.6V, V <sub>OUT</sub> = 3.3V |                                                   |      | 0.7  |      | %     |

|                                         |                                           | IOUT = 10mA to 75r<br>ILIM = 200mA, VIN =                                                                                 | nA (CCM mode),<br>= 3.6V, V <sub>OUT</sub> = 3.3V |      | 0.8  |      | 70    |

| Minimum Effective<br>Output Capacitance | C <sub>EFF</sub> (Min)                    |                                                                                                                           |                                                   |      | 100  |      | μF    |

# Nano Power Buck-Boost with Input Voltage Monitor

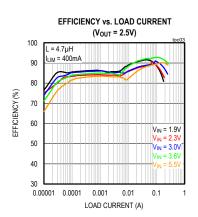

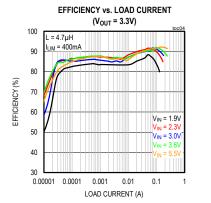

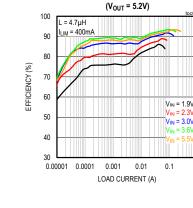

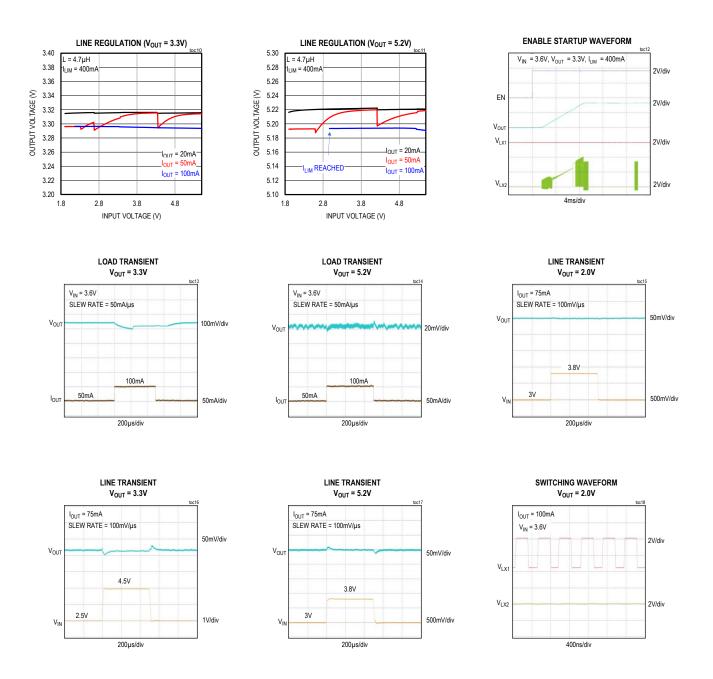

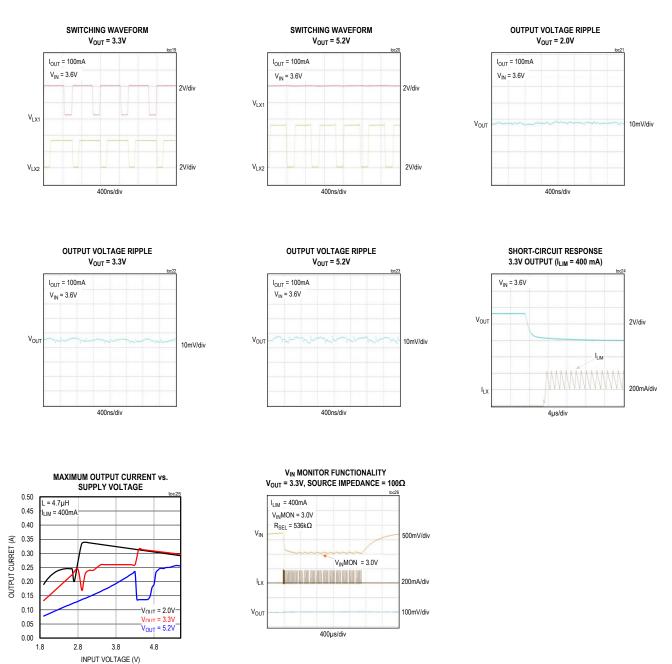

### **Typical Operating Characteristics**

$(V_{IN} = 3.6V, V_{OUT} = 3.3V, L = 4.7\mu$ H (Murata DFE201610E-4R7M = P2), C<sub>OUT</sub> = 22µF Ceramic + 100µF Electrolytic, I<sub>LIM</sub> = 400mA, V<sub>IN</sub>MON = 1.8V, T<sub>A</sub> = +25°C, unless otherwise noted.)

EFFICIENCY vs. LOAD CURRENT

1

# Nano Power Buck-Boost with Input Voltage Monitor

$(V_{IN} = 3.6V, V_{OUT} = 3.3V, L = 4.7\mu$ H (Murata DFE201610E-4R7M = P2), C<sub>OUT</sub> = 22µF Ceramic + 100µF Electrolytic, I<sub>LIM</sub> = 400mA, V<sub>IN</sub>MON = 1.8V, T<sub>A</sub> = +25°C, unless otherwise noted.)

# Nano Power Buck-Boost with Input Voltage Monitor

$(V_{IN} = 3.6V, V_{OUT} = 3.3V, L = 4.7\mu$ H (Murata DFE201610E-4R7M = P2), C<sub>OUT</sub> = 22µF Ceramic + 100µF Electrolytic, I<sub>LIM</sub> = 400mA, V<sub>IN</sub>MON = 1.8V, T<sub>A</sub> = +25°C, unless otherwise noted.)

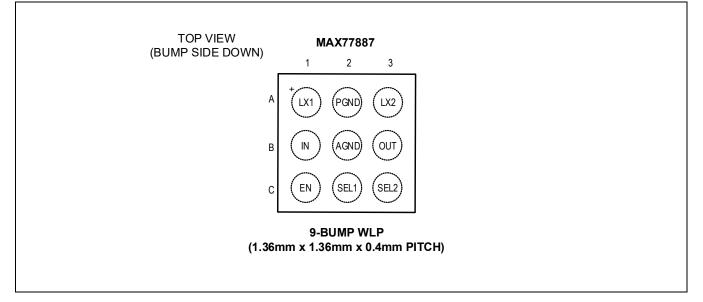

# **Pin Configuration**

# **Pin Descriptions**

| PIN | NAME | FUNCTION                                                                                                                      | Туре             |

|-----|------|-------------------------------------------------------------------------------------------------------------------------------|------------------|

| A1  | LX1  | Switching Node 1 of Buck-Boost Converter                                                                                      | Power            |

| A2  | PGND | Buck-Boost Converter Power Ground                                                                                             | Power<br>Ground  |

| A3  | LX2  | Switching Node 2 of Buck-Boost Converter                                                                                      | Power            |

| B1  | IN   | Buck-Boost Converter Input. Bypass with a 10V 10µF ceramic capacitor to GND pin.                                              | Power<br>Input   |

| B2  | AGND | Buck-Boost Converter Analog Ground                                                                                            | Analog<br>Ground |

| В3  | OUT  | Buck-Boost Converter Output. Bypass with a 10V 22µF ceramic capacitor to GND pin.                                             | Power<br>Output  |

| C1  | EN   | Buck-Boost Enable Input                                                                                                       | Digital<br>Input |

| C2  | SEL1 | Configuration Selection. Connect a resistor between SEL1 and PGND. See <u>Table 1</u> for resistor values and configurations. | Analog<br>Input  |

| C3  | SEL2 | Configuration Selection. Connect a resistor between SEL2 and PGND. See <u>Table 2</u> for resistor values and configurations. | Analog<br>Input  |

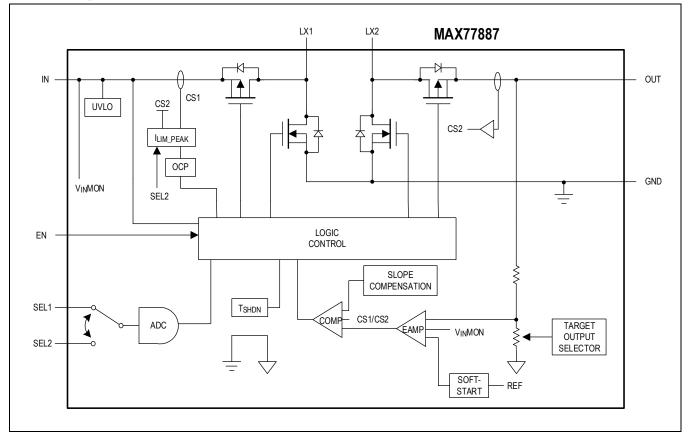

### **Block Diagram**

## **Detailed Description**

The MAX77887 is a nano power buck-boost with ultra-low quiescent current (430nA, typ) and high efficiency with an input range of 1.8V to 5.5V. The IC offers the Input Voltage Monitor feature which can protect the battery voltage from dropping below the preset threshold level in pulse load conditions. The IC is ideal for either primary battery-powered applications or double alkaline battery-powered applications that require long standby/idling time with short working time, such as asset tracking devices, or wearables. The IC operates in Low Power Mode (LPM), Skip Mode, or CCM Mode depending on operating conditions to achieve optimized efficiency performance.

The resistor between the SEL1 pin and GND ( $R_{SEL1}$ ) can be used to select the output voltage level within a range of 1.8V to 5.2V. The resistor between the SEL2 pin and GND ( $R_{SEL2}$ ) is used to set the following:

- Switching Current Limit (I<sub>LIM</sub>)

- Input Voltage Monitor Threshold levels (V<sub>MINMON</sub>)

See the <u>SEL Pin Configuration</u> section for more details.

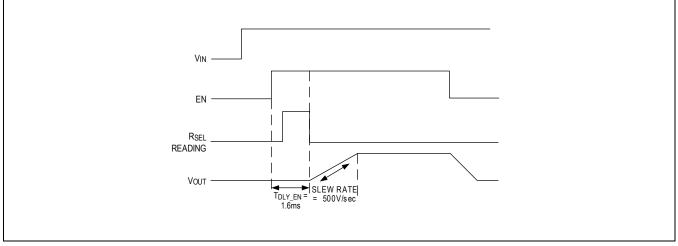

#### Start-Up

The start-up behavior is depicted in <u>Figure 1</u>. When EN goes logic HIGH and  $V_{IN} > V_{UVLO_R}$ , the IC starts up by turning on the bias circuits, after which the resistance value at the two SEL pins is read sequentially. The IC typically takes 1.6ms (T<sub>DLY EN</sub>, start-up delay time) after the rising edge of the EN signal to start the soft-start process.

During soft-start, the slew rate is maintained at 0.5V/ms. The soft-start procedure is completed when the output reaches the target regulation voltage.

If the output is pre-biased to the target voltage level, the device skips the soft-start procedure and directly enters normal regulation.

Figure 1. Start-Up Behavior

#### **Buck-Boost Control Scheme**

The buck-boost converter operates using adaptive on-time current-mode control. The buck-boost utilizes an H-bridge topology to regulate the output voltage using a single inductor and output capacitor.

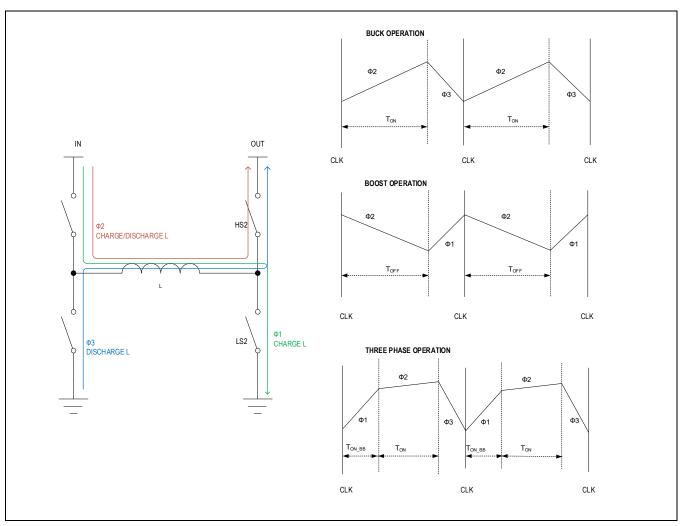

The H-bridge topology has three switching phases. See *Figure 2* for details.

- Φ1 switch period (Phase 1: HS1 = ON, LS2 = ON) stores energy in the inductor. Inductor current ramps up at a rate proportional to the input voltage divided by inductance: V<sub>IN</sub>/L.

- Φ2 switch period (Phase 2: HS1 = ON, HS2 = ON) ramps inductor current up or down depending on the differential voltage across the inductor: (V<sub>IN</sub> - V<sub>OUT</sub>)/L.

- Φ3 switch period (Phase 3: LS1 = ON, HS2 = ON) ramps inductor current down at a rate proportional to the output voltage divided by inductance: (-V<sub>OUT</sub>/L).

Boost operation (V<sub>IN</sub> < V<sub>OUT</sub>) utilizes  $\Phi$ 2 and  $\Phi$ 1 within one cycle during the preconfigured off time. See the representation of the inductor current waveform for boost mode operation in <u>Figure 2</u>.

Buck operation (V<sub>IN</sub> > V<sub>OUT</sub>) utilizes  $\Phi$ 2 and  $\Phi$ 3 within one cycle during the preconfigured on time. See the representation of the inductor current waveform for buck mode operation in *Figure 2*.

Three-phase operation (V<sub>IN</sub> close to V<sub>OUT</sub>) utilizes  $\Phi$ 1 for a pre-configured buck-boost on time,  $\Phi$ 2 is triggered for preconfigured on time, and then  $\Phi$ 3 is triggered till the current reaches zero. See the representation of the inductor current waveform for the three-phase mode operation in *Figure* 2.

# Nano Power Buck-Boost with Input Voltage Monitor

Figure 2. Buck-Boost H-Bridge Topology

#### Low Power Mode

The IC automatically enters Low Power Mode (LPM) when the load current is very low to achieve high efficiency at light loads. In this mode, the error amplifier and other internal blocks are deactivated to lower  $I_Q$  consumption. A low-power voltage comparator is used to monitor the output voltage in LPM.

When the load current reduces and the switching frequency falls to  $F_{MIN}$  (133kHz, typ), the part switches at  $F_{MIN}$  till the output voltage reaches above 2% of the target output voltage. After the output voltage crosses this level, the part is in Low Power Mode. In Low Power Mode, the IC generates an on-time of predetermined length when the output voltage reaches 2% above the target output voltage. When the load is increased, the IC must switch at a higher frequency to service the load and when the switching frequency reaches  $F_{MIN}$ , the part switches at  $F_{MIN}$  till the output falls to the target voltage. When the output hits the target voltage, the part enters Skip Mode.

#### SKIP Mode and CCM Mode

When the load is high enough and the switching frequency is higher than the  $F_{MIN}$  (133kHz, typ), the part exits Low Power Mode and enters Skip Mode. In the Skip Mode of operation, an on-time of predetermined length is triggered when the output voltage reaches the target value. During the Skip Mode of operation, the negative inductor current is prevented by turning off the FETs after the inductor current crosses 0A.

At higher output load currents when the inductor current does not have zero crossing, the part enters CCM (Continuous Conduction Mode) where the part operates using adaptive on-time control. The IC regulates to target voltage during the CCM mode of operation.

#### **Thermal Shutdown**

When the junction temperature exceeds  $T_{SHDN_R}$  (165°C, typ), thermal protection of the MAX77887 is triggered causing the buck-boost converter output to be disabled until the junction temperature drops below thermal protection falling threshold level  $T_{SHDN_F}$  (145°C, typ). The part automatically starts up again when the junction temperature drops below the thermal protection falling threshold.

#### Undervoltage Lockout

When V<sub>IN</sub> falls below V<sub>UVLO\_F</sub> (1.69V, typ), the buck-boost regulator is disabled, and all registers are reset. The IC is reenabled only when V<sub>IN</sub> rises above V<sub>UVLO\_R</sub> (1.75V, typ).

#### **Switching Current Limit**

The MAX77887 provides cycle by cycle-by-cycle switching current limit to protect the IC and the system. The IC senses the peak switching current of the high side switches during on time. When the peak current reaches the Switching Current Limit ( $I_{LIM}$ ), the switches for the charging phase are turned off and the switches used to discharge the inductor current are turned on until the peak current reaches the valley current limit. This procedure continues until the peak switching current no longer hits the  $I_{LIM}$  threshold. The IC supports two different Switching Current Limits 400mA (higher limit) and 200mA (lower limit) which can be configured using  $R_{SEL2}$ . For more information see the <u>SEL Pin Configuration</u> section.

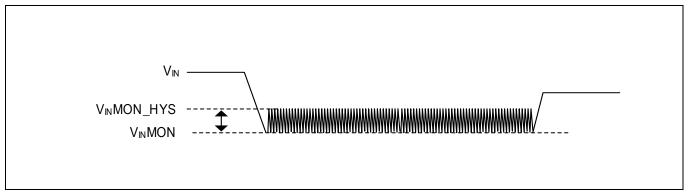

#### **Input Voltage Monitor**

The MAX77887 provides an input voltage monitor feature which ensures battery voltage does not drop below the preset threshold – Input Voltage Monitor Threshold level (V<sub>IN</sub>MON) to protect the battery. When the MAX77887 detects the input recovers to the V<sub>IN</sub>MON\_HYS level, the IC starts switching again. This procedure continues until the IC does not detect V<sub>IN</sub> dropping to the V<sub>IN</sub>MON level. If V<sub>IN</sub> does not drop to the V<sub>IN</sub>MON level any further, the IC resumes its normal switching pattern.

Figure 3. VINMON Feature

#### **SEL Pin Configurations**

MAX77887 has two hardware configuration pins (SEL1 and SEL2) to configure the features of the part. A resistor tied between SEL1 and ground ( $R_{SEL1}$ ) is used to select the output voltage level (OUT). A resistor tied between SEL2 and ground ( $R_{SEL2}$ ) is used to select the Switching Current Limit and Input Voltage Monitor Threshold levels.

### Table 1. RSEL1 Selection Table

| R <sub>SEL1</sub> (kΩ) | OUT (V) | R <sub>SEL1</sub> (kΩ) | OUT (V) |

|------------------------|---------|------------------------|---------|

| Short                  | 3.3     | 66.5                   | 3.4     |

| 4.99                   | 1.8     | 80.6                   | 3.6     |

| 5.90                   | 1.9     | 95.3                   | 3.7     |

| 7.15                   | 2.0     | 113                    | 3.8     |

| 8.45                   | 2.1     | 133                    | 3.9     |

| 10.0                   | 2.2     | 162                    | 4.0     |

| 11.8                   | 2.3     | 191                    | 4.1     |

| 14.0                   | 2.4     | 226                    | 4.2     |

| 16.9                   | 2.5     | 267                    | 4.3     |

| 20.0                   | 2.6     | 324                    | 4.4     |

| 23.7                   | 2.7     | 383                    | 4.5     |

| 28.0                   | 2.8     | 453                    | 4.6     |

| 34.0                   | 2.9     | 536                    | 4.7     |

| 40.2                   | 3.0     | 634                    | 5.0     |

| 47.5                   | 3.1     | 768                    | 5.1     |

| 56.2                   | 3.2     | 909/OPEN               | 5.2     |

# Table 2. RSEL2 Selection Table

| R <sub>SEL2</sub> (kΩ) | V <sub>IN</sub> MON (V) | I <sub>LIM</sub> (mA) | R <sub>SEL2</sub> (kΩ) | V <sub>IN</sub> MON (V) | I <sub>LIM</sub> (mA) |

|------------------------|-------------------------|-----------------------|------------------------|-------------------------|-----------------------|

| Short                  | 1.8                     | 200                   | 66.5                   | 1.8                     | 400                   |

| 4.99                   | 1.9                     | 200                   | 80.6                   | 1.9                     | 400                   |

| 5.90                   | 2.0                     | 200                   | 95.3                   | 2.0                     | 400                   |

| 7.15                   | 2.1                     | 200                   | 113                    | 2.1                     | 400                   |

| 8.45                   | 2.2                     | 200                   | 133                    | 2.2                     | 400                   |

| 10.0                   | 2.3                     | 200                   | 162                    | 2.3                     | 400                   |

| 11.8                   | 2.4                     | 200                   | 191                    | 2.4                     | 400                   |

| 14.0                   | 2.5                     | 200                   | 226                    | 2.5                     | 400                   |

| 16.9                   | 2.6                     | 200                   | 267                    | 2.6                     | 400                   |

| 20.0                   | 2.7                     | 200                   | 324                    | 2.7                     | 400                   |

| 23.7                   | 2.8                     | 200                   | 383                    | 2.8                     | 400                   |

| 28.0                   | 2.9                     | 200                   | 453                    | 2.9                     | 400                   |

| 34.0                   | 3.0                     | 200                   | 536                    | 3.0                     | 400                   |

| 40.2                   | 3.1                     | 200                   | 634                    | 3.1                     | 400                   |

| 47.5                   | 3.2                     | 200                   | 768                    | 3.2                     | 400                   |

| 56.2                   | 3.4                     | 200                   | 909/OPEN               | 3.4                     | 400                   |

# Nano Power Buck-Boost with Input Voltage Monitor

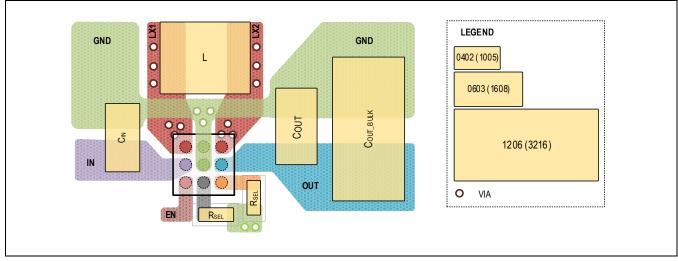

#### PCB Layout Guidelines

Careful circuit board layout is critical to achieve low switching power losses and clean, stable operation. <u>Figure 4</u> shows an example PCB layout.

When designing the PCB, use the following guidelines:

- The input capacitor should be placed immediately next to the IN pin of the device. Since the device operates at a high switching frequency, this placement is critical for the effective decoupling of high-frequency noise from the IN pin.

- 2) Prioritize the low-impedance ground plane of the PCB directly underneath the IC, C<sub>OUT</sub>, C<sub>IN</sub>, and the inductor. Cutting this ground plane risks interrupting the switching current loops.

- 3) AGND must carefully connect to PGND. Connect AGND to the low-impedance ground plane on the PCB (the same net as PGND) away from any critical loops.

4) Keep the power traces and load connections short and wide. This practice is essential for high efficiency.

Figure 4. Example Layout

# **Typical Application Circuit**

# **Ordering Information**

| PART NUMBER    | PIN-PACKAGE |  |

|----------------|-------------|--|

| MAX77887AEWL+T | 9 WLP       |  |

+Denotes a lead(Pb)-free/RoHS-compliant package.

T = Tape and reel.

# Nano Power Buck-Boost with Input Voltage Monitor

# **Revision History**

| VISION<br>IMBER | REVISION<br>DATE | DESCRIPTION              |  |

|-----------------|------------------|--------------------------|--|

| 0               | 3/24             | Release for Market Intro |  |

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.