19-3217; Rev 0; 3/08 EVALUATION KIT AVAILABLE 16-Bit RISC Microcontroller-Based

## **16-Bit RISC Microcontroller-Based** Smart Data-Acquisition Systems

## **General Description**

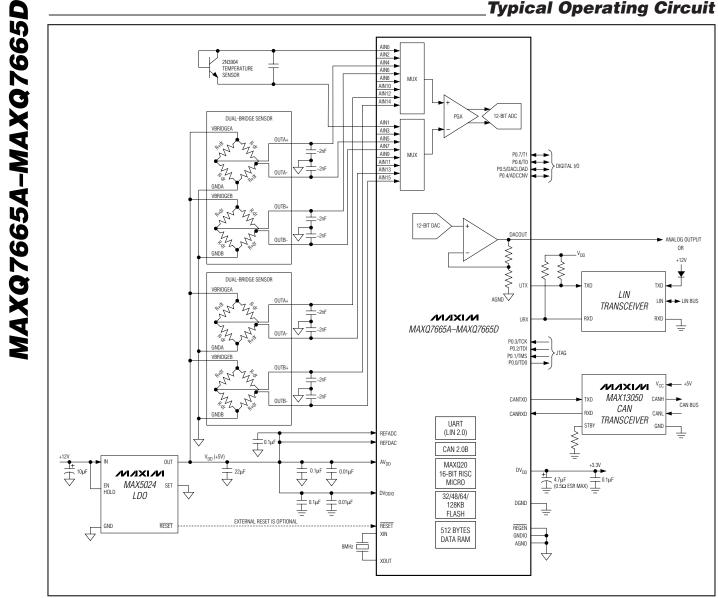

The MAXQ7665A–MAXQ7665D smart systems-on-a-chip (SoC) are data-acquisition systems based on a microcontroller ( $\mu$ C). As members of the MAXQ<sup>®</sup> family of 16bit, reduced instruction set computing (RISC)  $\mu$ Cs, the MAXQ7665A–MAXQ7665D are ideal for low-cost, lowpower, embedded applications such as automotive, industrial controls, and building automation. The flexible, modular architecture design used in these  $\mu$ Cs allows development of targeted products for specific applications with minimal effort.

www.[

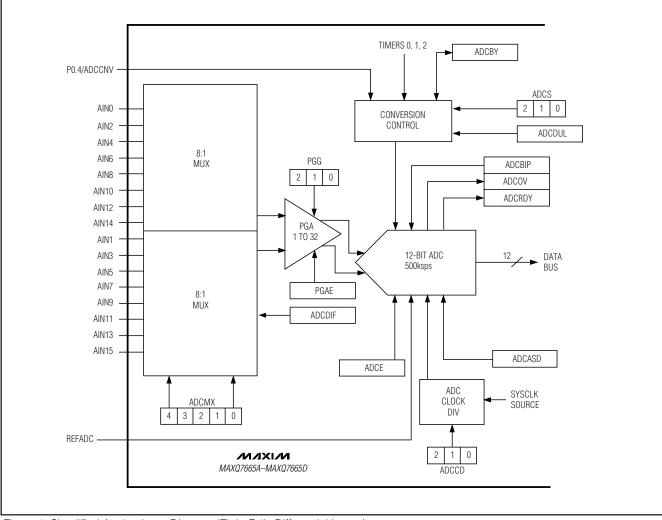

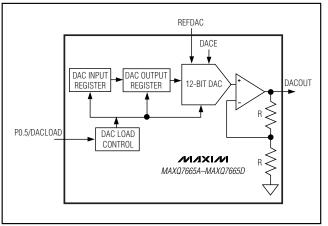

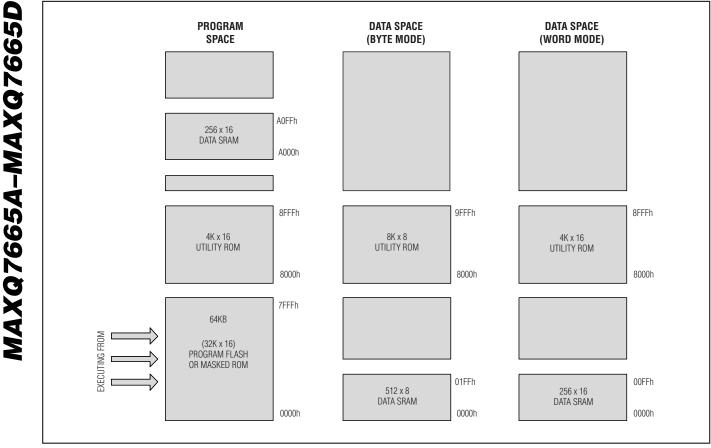

The MAXQ7665A-MAXQ7665D incorporate a high-performance 16-bit RISC core, a 12-bit 500ksps SAR ADC with a programmable gain amplifier (PGA), and a full CAN 2.0B controller supporting transfer rates up to 1Mbps. These devices include a 12-bit DAC with a buffered voltage output and on-chip oscillator circuitry to operate from an external high frequency (8MHz) crystal. There is also a built-in internal RC oscillator as an alternative to using an external crystal. The MAXQ7665A-MAXQ7665D contain an internal temperature sensor to measure die temperature and a remote temperature-sensor driver. The analog functions and digital I/O are powered from a +5V supply, while the internal digital core is powered from +3.3V, which can be supplied by an on-chip linear regulator. These devices also include a dual power-supply supervisor with reset and a JTAG interface for in-system programming and debugging. The 16-bit RISC µC includes up to 128KB (64K x 16) of flash memory and 512 bytes (256 x 16) of RAM.

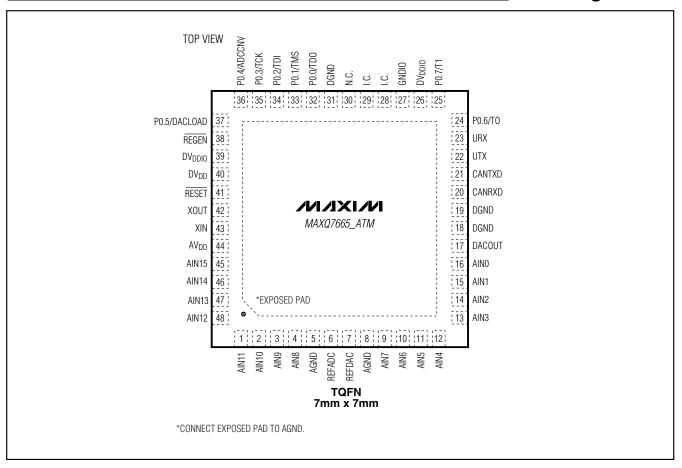

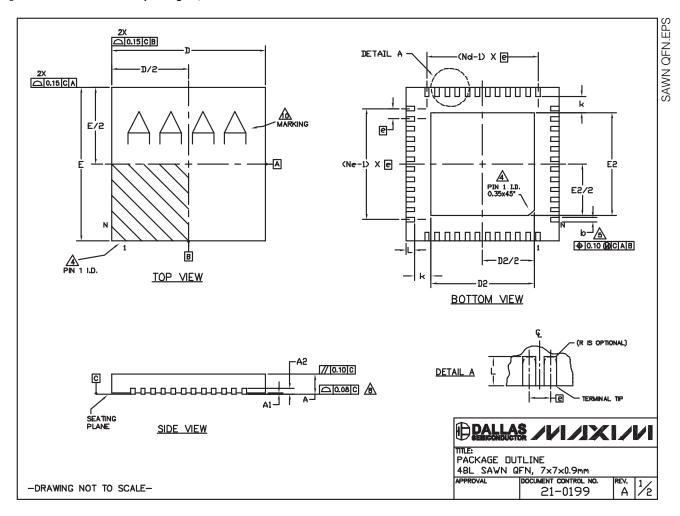

The MAXQ7665A–MAXQ7665D are available in a 7mm x 7mm 48-pin TQFN package and are specified to operate from -40°C to +125°C.

Automotive Steering Sensors CAN- and LIN-Based Automotive Sensors Industrial Control

# Features

**Applications**

High-Performance, Low-Power, 16-Bit RISC Core DC-to-8MHz Operation, Approaching 1MIPS per MHz Low Power (< 3mA/MIPS, DVDD = +3.3V) 16-Bit Instruction Word, 16-Bit Data Bus 33 Instructions (Most Require Only One Clock Cycle) 16-Level Hardware Stack

MAXQ is a registered trademark of Maxim Integrated Products, Inc. DeviceNet is a trademark of Open DeviceNet Vendor Association, Inc.

Three Independent Data Pointers with Automatic Increment/Decrement

- Program and Data Memory

Up to 128KB (64K x 16) Internal Flash

512 Bytes (256 x 16) Internal RAM

- Smart Analog Peripherals

Low-Power, Eight Differential-Channel, 12-Bit, 500ksps ADC

Programmable-Gain Amplifier, Software-Selectable Gain: 1V/V, 2V/V, 4V/V, 8V/V, 16V/V, 32V/V

12-Bit DAC with Buffered Voltage Output External References for ADC and DAC Internal (Die) and External Diode Temperature Sensing

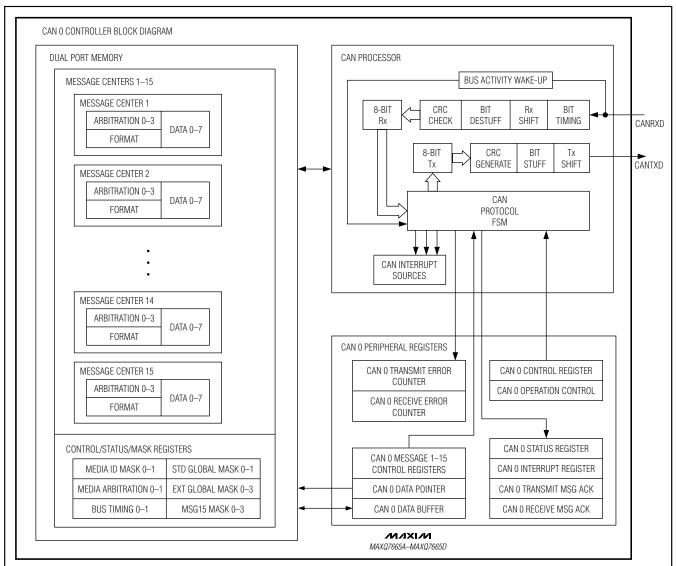

- Timer/Digital I/O Peripherals Full CAN 2.0B Controller

# 15 Message Centers (256-Byte Dual Port Memory) Programmable Bit Rates from 10kbps to 1Mbps Standard 11-Bit or Extended 29-Bit Identification Modes Two Data Masks and Associated IDs for DeviceNET™, SDS and Other Higher Layer CAN Protocols External Transmit Disable for Autobaud SIESTA Low-Power Mode Wake-Up on CANRXD Edge Transition UART (LIN) with User-Programmable Baud Rate

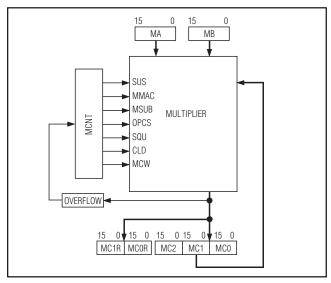

- 16 x 16 Hardware Multiplier with 48-Bit Accumulator, Single Clock Cycle Operation

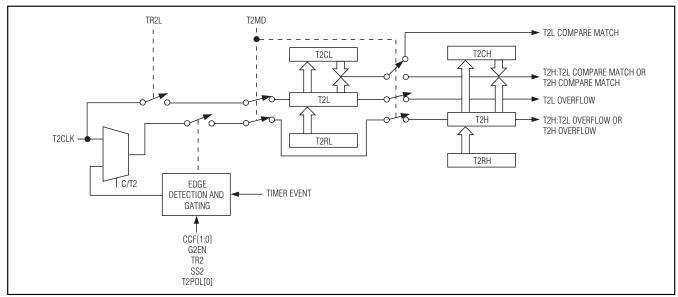

- Three 16-Bit (or Six 8-Bit) Programmable Timer/Counter/PWM

- Eight General-Purpose, Digital I/O Pins, with External Interrupt Capability

- All Interrupts Can Be Used as a Wake-Up

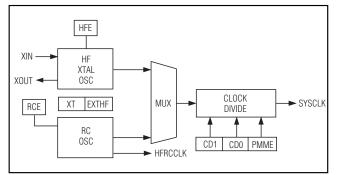

- Crystal/Clock Module Internal Oscillator for Use with External Crystal On-Chip RC Oscillator Eliminates External Crystal External Clock-Source Operation

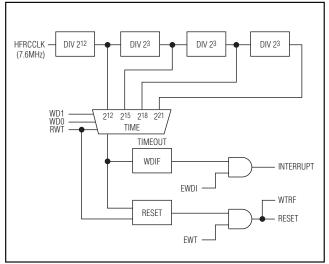

- Programmable Watchdog Timer

- Power-Management Module

Power-On Reset (POR)

Power-Supply Supervisor/Brownout Detection for Digital

I/O and Digital Core Supplies

- On-Chip +3.3V, 50mA Linear Regulator

- JTAG Interface

Extensive Debug and Emulation Support

In-System Test Capability

Flash-Memory-Program Download

Software Bootstrap Loader for Flash Programming

Ultra-Low-Power Consumption

- Low-Power, Divide-by-256 PMM Mode Stop Mode

Ordering Information/Selector Guide and Pin Configuration appear at end of data sheet.

**Note:** Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device may be simultaneously available through various sales channels. For information about device errata, go to: <u>www.maxim-ic.com/errata</u>.

## M /X / M

Maxim Integrated Products 1

For pricing delivery, and ordering information please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com. www.DataSheet4U.com

## **ABSOLUTE MAXIMUM RATINGS**

| I | DV <sub>DD</sub> to DGND, AGND, or GNDIO0.3V to +4V<br>DGND to GNDIO or AGND0.3V to +0.3V | Continuous Current into Any Pin±50mA<br>Continuous Power Dissipation ( $T_{A} = +70^{\circ}$ C) |

|---|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

|   |                                                                                           |                                                                                                 |

|   | DV <sub>DDIO</sub> to DGND, AGND, or GNDIO0.3V to +6V                                     | 48-Pin TQFN (derate 40mW/°C above +70°C)                                                        |

|   | AV <sub>DD</sub> to DGND, AGND, or GNDIO0.3V to +6V                                       | Operating Temperature Range40°C to +125°C                                                       |

|   | Digital Inputs/Outputs to DGND, AGND, or GNDIO                                            | Junction Temperature+150°C                                                                      |

|   | -0.3V to (DV <sub>DDIO</sub> + 0.3V)                                                      | Storage Temperature Range65°C to +150°C                                                         |

|   | Analog Inputs/Outputs to DGND, AGND, or GNDIO                                             | Lead Temperature (soldering, 10s)+300°C                                                         |

|   | -0.3V to (AV <sub>DD</sub> + 0.3V)                                                        |                                                                                                 |

|   | RESET, XIN, XOUT to DGND, AGND, or GNDIO                                                  |                                                                                                 |

|   |                                                                                           |                                                                                                 |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS**

-0.3V to (DV<sub>DD</sub> + 0.3V)

$(AV_{DD} = DV_{DDIO} = +5.0V, DV_{DD} = +3.3V, f_{SYSCLK} = 8MHz, V_{REFDAC} = V_{REFADC} = +5V, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                                                         | SYMBOL           | CONDITIONS                                                                                                    | MIN  | TYP  | MAX  | UNITS |

|-------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| POWER REQUIRMENTS                                                 |                  | •                                                                                                             | •    |      |      |       |

|                                                                   |                  | Safe mode (RC/2 = 3.8MHz)                                                                                     | 2.7  | 3.3  | 3.6  |       |

| Quarte Malta da Davada                                            | DV <sub>DD</sub> | Normal mode                                                                                                   | 3.0  | 3.3  | 3.6  | V     |

| Supply Voltage Range                                              | AV <sub>DD</sub> |                                                                                                               | 4.75 | 5.0  | 5.25 | V     |

|                                                                   | DVDDIO           |                                                                                                               | 4.75 | 5.0  | 5.25 |       |

|                                                                   | 1                | Shutdown (Note 2)                                                                                             |      | 0.1  | 10   | μA    |

| AV <sub>DD</sub> Supply Current                                   | Iavdd            | All analog functions enabled                                                                                  |      | 6.7  | 8    | mA    |

|                                                                   |                  | ADC enabled, f <sub>ADC</sub> = 1ksps, f <sub>SYSCLK</sub> = 8MHz                                             |      | 4.2  |      |       |

|                                                                   |                  | ADC enabled, f <sub>ADC</sub> = 500ksps, f <sub>SYSCLK</sub> = 8MHz                                           |      | 1890 |      |       |

| Analog Module Subfunction                                         |                  | DAC enabled (zero scale)                                                                                      |      | 305  |      | μA    |

| Incremental Supply Current                                        |                  | Internal temperature sensor enabled                                                                           |      | 502  |      |       |

|                                                                   |                  | Additional current when one or more of the ADC, DAC, and/or temperature sensor is enabled (only counted once) |      | 128  |      |       |

|                                                                   |                  | PGA enabled                                                                                                   |      | 4.5  |      | mA    |

|                                                                   |                  | CPU in stop mode, all peripherals disabled                                                                    |      | 3    | 20   | μA    |

|                                                                   |                  | Medium-speed mode (Note 3)                                                                                    |      |      | 5    |       |

| DV <sub>DD</sub> Supply Current                                   | IDVDD            | High-speed mode (Note 4)                                                                                      |      |      | 28   | 100 Å |

|                                                                   |                  | Low-speed mode (Note 5)                                                                                       |      |      | 2    | mA    |

|                                                                   |                  | Flash erase or write mode                                                                                     |      | 35   | 50   |       |

|                                                                   |                  | DV <sub>DD</sub> supervisor and brownout monitor                                                              |      | 2    |      |       |

| DV <sub>DD</sub> Module Subfunction<br>Incremental Supply Current |                  | HF crystal oscillator                                                                                         | 150  |      | μA   |       |

| incremental oupply our ont                                        |                  | Internal RC oscillator                                                                                        |      | 200  |      |       |

| DV <sub>DDIO</sub> Supply Current                                 | IDVDDIO          | All digital I/Os static at GND or $DV_{DDIO}$                                                                 |      |      | 10   | μA    |

|                                                                   | טועעעי           | (Note 6)                                                                                                      |      |      | 1000 | μΛ    |

## **ELECTRICAL CHARACTERISTICS (continued)**

| PARAMETER                               | SYMBOL | CONDITIONS                                                               | MIN  | TYP  | MAX  | UNITS   |

|-----------------------------------------|--------|--------------------------------------------------------------------------|------|------|------|---------|

| MEMORY SECTION                          | •      | •                                                                        |      |      |      |         |

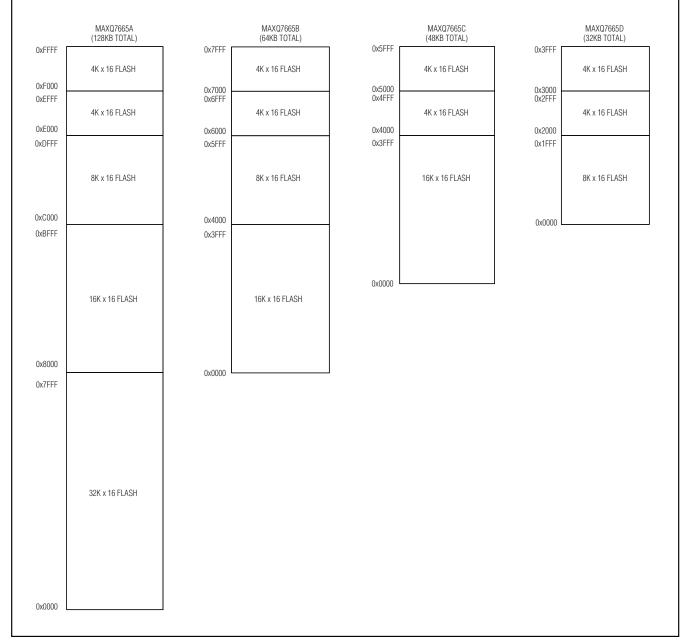

|                                         |        | MAXQ7665A                                                                |      | 128  |      |         |

|                                         |        | MAXQ7665B                                                                |      | 64   |      | KD      |

| Flash Memory Size                       |        | MAXQ7665C                                                                |      | 48   |      | KB      |

|                                         |        | MAXQ7665D                                                                |      | 32   |      | 1       |

|                                         |        | DV <sub>DD</sub> = +3V, at +25°C                                         |      | 1    |      | MCycles |

| Flash Erase/Write Endurance             |        | DV <sub>DD</sub> = +3V, at +85°C                                         |      | 100  |      | kCycles |

|                                         |        | DV <sub>DD</sub> = +3V, at +125°C                                        |      | 100  |      | kCycles |

| Flash Erase Timing                      |        | One sector                                                               |      | 0.7  | 15   | S       |

|                                         |        | Single word                                                              |      | 11   | 360  | μs      |

| Flash Program Timing                    |        | Entire flash                                                             |      | 1.5  | 4.5  | S       |

|                                         |        | $T_A = +125^{\circ}C$ , single write                                     | 20   |      |      |         |

| Flash Data Retention Time               |        | First 100,000 cycles at +25°C, then retention tested at $T_A$ = +125°C   | 10   |      |      | Years   |

| RAM Memory Size                         |        |                                                                          |      | 512  |      | Bytes   |

| Utility ROM Size                        |        |                                                                          |      | 4096 |      | Words   |

| ANALOG SENSE PATH                       | •      | •                                                                        |      |      |      | •       |

| Resolution                              | NADC   | No missing codes                                                         | 12   |      |      | Bits    |

|                                         |        | Gain = 1, bipolar mode, V <sub>IN</sub> = ±2500mV,<br>500ksps            |      | ±0.5 | ±4.0 |         |

|                                         |        | Gain = 8, unipolar mode, V <sub>IN</sub> = +400mV,<br>142ksps            |      | ±2.0 |      |         |

| Integral Nonlinearity                   | INLADC | Gain = 16, bipolar mode, V <sub>IN</sub> = ±156mV,<br>142ksps            |      | ±2.0 | ±4.0 | - LSB   |

|                                         |        | Gain = 32, bipolar mode, V <sub>IN</sub> = ±50mV,<br>142ksps             |      | ±2.0 |      |         |

|                                         |        | Gain = 1, bipolar, V <sub>IN</sub> = ±2500mV, 500ksps                    |      |      | ±1.0 |         |

| Differential Nonlinearity               | DNLADC | Gain = 16, bipolar, V <sub>IN</sub> = ±156mV, 142ksps                    |      |      | ±1.0 | LSB     |

|                                         |        | All other gain settings                                                  |      | ±0.6 |      |         |

| Offset Error                            |        | Input referred                                                           |      | ±2.5 | ±5   | mV      |

| Offset-Error Temperature<br>Coefficient |        |                                                                          |      | ±8   |      | µV/°C   |

| Zero-Code Error                         |        | Bipolar, differential measurement of error for ideal ADC output of 0x000 |      | ±2.5 |      | mV      |

| Gain Error                              |        | Exclude offset and reference error                                       | -1.0 |      | +1.0 | %       |

| Gain-Error Temperature<br>Coefficient   |        |                                                                          |      | ±8.5 |      | ppm/°C  |

| Signal-to-Noise Plus Distortion         | SINAD  | PGA gain = 1V/V                                                          |      | -71  |      | dB      |

| Total Harmonic Distortion               | THD    | PGA gain = 1V/V                                                          |      | -85  |      | dB      |

## **ELECTRICAL CHARACTERISTICS (continued)**

| PARAMETER                       | SYMBOL              | CONDITIO                               | ONS                            | MIN                         | TYP MAX                     | UNITS |  |

|---------------------------------|---------------------|----------------------------------------|--------------------------------|-----------------------------|-----------------------------|-------|--|

| Spurious-Free Dynamic Range     | SFDR                | PGA gain = 1V/V                        |                                |                             | -91                         | dB    |  |

| Conversion Clock Frequency      | <b>f</b> ADCCLK     | fsysclk = 8MHz                         |                                | 0.5                         | 8.0                         | MHz   |  |

|                                 |                     | PGA gain = 1V/V, R <sub>SOUR</sub>     | $CE \le 1k\Omega$              |                             | 500                         |       |  |

| Sample Rate                     | <sup>f</sup> SAMPLE | Any PGA gain setting > 1 $5k\Omega$    | V/V, R <sub>SOURCE</sub> ≤     |                             | 142                         | ksps  |  |

| Conversion Time                 | tCONV               | t <sub>ACQ</sub> plus 13 ADCCLK cy     | cles at 8MHz                   |                             | t <sub>ACQ</sub> +<br>1.625 | μs    |  |

| Channel/Gain Select Plus        |                     | PGA gain = 1V/V, R <sub>SOUR</sub>     | CE ≤ 1kΩ                       |                             | 2                           |       |  |

| Conversion Time                 |                     | Any PGA gain setting, Rs               | SOURCE $\leq 5 \text{k}\Omega$ |                             | 7                           | μs    |  |

|                                 |                     | PGA gain = 1V/V, R <sub>SOUR</sub>     | CE ≤ 1kΩ                       |                             | 375                         | ns    |  |

| Track-and-Hold Acquisition Time | tacq                | Any PGA gain setting > 1 $5k\Omega$    | V/V, R <sub>SOURCE</sub> ≤     |                             | 5                           | μs    |  |

| Turn-On Time                    | <b>t</b> RECOV      |                                        |                                |                             | 5                           | μs    |  |

| Aperture Delay                  |                     |                                        |                                |                             | 30                          | ns    |  |

| Aperture Jitter                 |                     |                                        |                                |                             | 50                          | psp₋p |  |

|                                 |                     |                                        | PGA gain = 1                   | 0                           | AV <sub>DD</sub>            |       |  |

|                                 |                     |                                        | PGA gain = 2                   | 0                           | 1.6                         |       |  |

|                                 |                     |                                        | PGA gain = 4                   | 0                           | 0.8                         |       |  |

|                                 |                     | Unipolar mode<br>Bipolar mode, AIN+ to | PGA gain = 8                   | 0                           | 0.4                         |       |  |

|                                 |                     |                                        | PGA gain = 16                  | 0                           | 0.2                         |       |  |

|                                 |                     |                                        | PGA gain = 32                  | 0                           | 0.1                         |       |  |

|                                 |                     |                                        | PGA gain = 1                   | -VREFADC<br>/2              | +VREFADC<br>/2              |       |  |

| Input-Voltage Range             |                     |                                        | PGA gain = 2                   | -VREFADC<br>/4              | +VREFADC<br>/4              | V     |  |

|                                 |                     |                                        | PGA gain = 4                   | -V <sub>REFADC</sub><br>/8  | +V <sub>REFADC</sub><br>/8  |       |  |

|                                 |                     | AIN-                                   | PGA gain = 8                   | -VREFADC<br>/16             | +V <sub>REFADC</sub><br>/16 |       |  |

|                                 |                     |                                        | PGA gain = 16                  | -VREFADC<br>/32             | +V <sub>REFADC</sub><br>/32 |       |  |

|                                 |                     |                                        | PGA gain = 32                  | -V <sub>REFADC</sub><br>/64 | +V <sub>REFADC</sub><br>/64 |       |  |

| Absolute Input-Voltage Range    |                     |                                        |                                | AGND                        | AV <sub>DD</sub>            | V     |  |

| Input Leakage Current           |                     | AIN15-AIN0                             |                                |                             | ±20                         | nA    |  |

|                                 |                     |                                        | PGA gain = 1                   |                             | 180                         |       |  |

|                                 |                     |                                        | PGA gain = 2                   | 140                         |                             | ]     |  |

|                                 |                     |                                        | PGA gain = 4                   | 1                           | 120                         | 1     |  |

| Small-Signal Bandwidth (-3dB)   |                     | $V_{IN} \times gain = 100 m V_{P-P}$   | PGA gain = 8                   | 1                           | 100                         | MHz   |  |

|                                 |                     |                                        | PGA gain = 16                  | 82                          |                             | 1     |  |

|                                 |                     |                                        | PGA gain = 32                  |                             | 80                          | 1     |  |

## **ELECTRICAL CHARACTERISTICS (continued)**

| PARAMETER                               | SYMBOL                  | CONDITIO                                                        | ONS                          | MIN | ТҮР  | MAX     | UNITS            |

|-----------------------------------------|-------------------------|-----------------------------------------------------------------|------------------------------|-----|------|---------|------------------|

|                                         |                         |                                                                 | PGA gain = 1                 |     | 180  |         |                  |

|                                         |                         |                                                                 | PGA gain = 2                 |     | 140  |         | ]                |

| Large Cignel Dep dwidth ( 2dD)          |                         |                                                                 | PGA gain = 4                 |     | 120  |         | - kHz            |

| Large-Signal Bandwidth (-3dB)           |                         | $V_{IN} \times gain = 3.2 V_{P-P}$                              | PGA gain = 8                 |     | 100  |         |                  |

|                                         |                         |                                                                 | PGA gain = 16                |     | 82   |         |                  |

|                                         |                         |                                                                 | PGA gain = 32                |     | 80   |         |                  |

|                                         |                         |                                                                 | PGA gain = 1                 |     | 13.6 |         |                  |

|                                         |                         |                                                                 | PGA gain = 2                 |     | 2    |         |                  |

|                                         |                         | Single-ended, any input                                         | PGA gain = 4                 |     | 4    |         | ~F               |

| Input Capacitance                       |                         | of AIN0 to AIN15                                                | PGA gain = 8                 |     | 8    |         | pF               |

|                                         |                         |                                                                 | PGA gain = 16                |     | 16   |         |                  |

|                                         |                         |                                                                 | PGA gain = 32                |     | 32   |         |                  |

| Crosstalk Between Channels              | V <sub>CT</sub>         | AIN15–AIN0, $V_{IN} = 1V_{P-P}$<br>= 5k $\Omega$                | , 10kHz, R <sub>SOURCE</sub> |     | -80  |         | dB               |

| Input Common-Mode Rejection<br>Ratio    | CMRR                    | AIN15–AIN0 (bipolar, differential),<br>$V_{CM} = 100mV$ to 4.5V |                              | -70 | -90  |         | dB               |

| Power-Supply Rejection Ratio            | PSRR                    | $AV_{DD} = +4.75V \text{ to } +5.25V$                           | V                            | 67  | 75   |         | dB               |

| DAC SECTION (DACOUT, RL = 5             | kΩ and C <sub>L</sub> = | 100pF)                                                          |                              |     |      |         |                  |

| Resolution                              | NDAC                    | Guaranteed monotonic                                            |                              | 12  |      |         | Bits             |

| Differential Nonlinearity               | DNLDAC                  | Code 147h to E68h                                               |                              |     | ±0.4 | ±1      | LSB              |

| Integral Nonlinearity                   | INLDAC                  | Code 147h to E68h                                               |                              |     | ±0.5 | ±4      | LSB              |

| Offset Error                            |                         | Reference to code 040h                                          |                              |     | ±2.5 | ±30     | mV               |

| Offset-Error Temperature<br>Coefficient |                         |                                                                 |                              |     | ±5   |         | µV/∘C            |

| Gain Error                              |                         | Excludes reference error,                                       | , tested at E68h             |     | ±3   | ±20     | LSB              |

| Gain-Error Temperature<br>Coefficient   |                         | Excludes offset and refer calculated from FSR                   | ence drift;                  |     | ±2   |         | ppm of<br>FSR/°C |

| DAC Output Range                        |                         | No load                                                         |                              | 0   |      | VREFDAC | V                |

| -                                       |                         | Terminetien                                                     | DAC enabled                  |     | 0.5  |         | Ω                |

| DC Output Impedance                     | Z <sub>OUT</sub>        | Termination resistance to AGND                                  | Power-down<br>mode           |     | 105  |         | kΩ               |

| Output Slew Rate                        |                         | 400h to C00h code swing                                         | g, rising or falling         |     | 0.6  |         | V/µs             |

| Output Settling Time                    |                         | 147h to E68h code swing<br>LSB (Note 7)                         | , settling to $\pm 0.5$      |     | 8    | 15      | μs               |

|                                         |                         | Short to AGND                                                   |                              |     | -27  |         |                  |

| Output Short-Circuit Current            |                         | Short to AGND<br>Short to AV <sub>DD</sub>                      |                              |     | 46   |         | mA               |

## ELECTRICAL CHARACTERISTICS (continued)

$(AV_{DD} = DV_{DDIO} = +5.0V, DV_{DD} = +3.3V, f_{SYSCLK} = 8MHz, V_{REFDAC} = V_{REFADC} = +5V, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C.$  (Note 1)

| PARAMETER                                                                                        | SYMBOL      | CONDITIONS                                                   |                                                                                                      | MIN  | TYP    | MAX              | UNITS             |  |

|--------------------------------------------------------------------------------------------------|-------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------|--------|------------------|-------------------|--|

| DAC Glitch Impulse                                                                               |             | From 7FFh to 800h                                            |                                                                                                      |      | 12     |                  | nV∙s              |  |

| DAC Power-On Time                                                                                |             | Excluding referen                                            | ice, settling to ±0.5 LSB                                                                            |      | 14     |                  | μs                |  |

| Power-Supply Rejection                                                                           |             | AV <sub>DD</sub> step from +                                 | -4.75V to +5.25V                                                                                     |      | 62     |                  | μV/V              |  |

| Output Noise                                                                                     |             | $C_L = 200 pF$                                               |                                                                                                      |      | 200    |                  | μV <sub>RMS</sub> |  |

| EXTERNAL REFERENCE INPUTS                                                                        |             |                                                              |                                                                                                      |      |        |                  |                   |  |

| REFADC Input-Voltage Range                                                                       |             |                                                              |                                                                                                      | 1.0  | 5.0    | AV <sub>DD</sub> | V                 |  |

| REFDAC Input-Voltage Range                                                                       |             |                                                              |                                                                                                      | 0    | 5.0    | AV <sub>DD</sub> | V                 |  |

| REFDAC Input Impedance                                                                           |             |                                                              |                                                                                                      |      | 200    |                  | kΩ                |  |

| REFADC Leakage Current                                                                           |             | ADC disabled                                                 |                                                                                                      |      | 1      |                  | μA                |  |

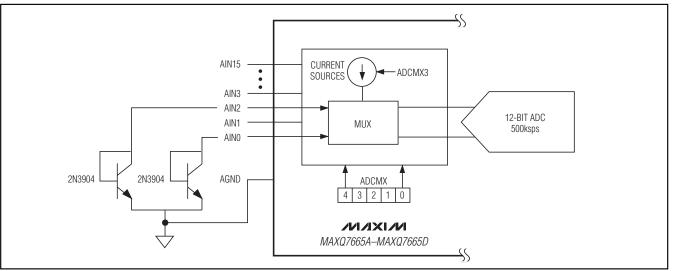

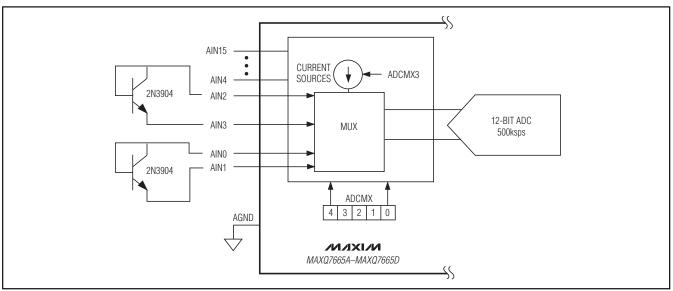

| TEMPERATURE SENSOR (Remo                                                                         | e NPN Tran  | sistor 2N3904)                                               |                                                                                                      |      |        |                  |                   |  |

|                                                                                                  |             |                                                              | T <sub>A</sub> = +25°C                                                                               |      | ±1     |                  |                   |  |

|                                                                                                  |             | Internal diode                                               | $T_A = -30^{\circ}C \text{ to } +85^{\circ}C$                                                        |      | ±2     |                  |                   |  |

| Temperature Error                                                                                |             |                                                              | $T_A = -40^{\circ}C \text{ to } + 125^{\circ}C$                                                      |      | ±5     |                  |                   |  |

|                                                                                                  |             |                                                              | $T_A = +25^{\circ}C,$<br>$T_{BJ} = +25^{\circ}C$                                                     |      | ±2     |                  |                   |  |

|                                                                                                  |             | External diode,<br>differential<br>configuration<br>(Note 8) | $T_A = -30^{\circ}C \text{ to } +85^{\circ}C,$<br>$T_{RJ} = +25^{\circ}C$                            |      | ±3     |                  | °C                |  |

|                                                                                                  |             |                                                              | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C,$<br>$T_{RJ} = +25^{\circ}C$                           |      | ±3     |                  | ]                 |  |

|                                                                                                  |             |                                                              | $T_A = -30^{\circ}C \text{ to } +85^{\circ}C,$<br>$T_{RJ} = -30^{\circ}C \text{ to } +85^{\circ}C$   |      | ±3     |                  |                   |  |

|                                                                                                  |             |                                                              | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C,$<br>$T_{RJ} = -40^{\circ}C \text{ to } +125^{\circ}C$ |      | ±5     |                  |                   |  |

| Internal (Die) or External<br>Temperature Measurement Error<br>vs. V <sub>REFADC</sub> Variation |             |                                                              |                                                                                                      |      | 0.095  |                  | °C/mV             |  |

|                                                                                                  |             | High level                                                   |                                                                                                      |      | 74.7   |                  |                   |  |

| External Diode Source Current                                                                    |             | Low level                                                    |                                                                                                      |      | 4      |                  | μΑ                |  |

| External Diode Drive Current Ratio                                                               |             |                                                              |                                                                                                      |      | 18.7:1 |                  | μΑ/μΑ             |  |

| Conversion Time                                                                                  |             | fADCCLK = fSYSCL<br>internal utility ROM                     | <sub>_K</sub> = 8MHz, no interrupts,<br>V tempConv                                                   |      | 70     |                  | μs                |  |

| Temperature Resolution                                                                           |             | 12-bit ADC                                                   |                                                                                                      |      | 0.125  |                  | °C/LSB            |  |

| +3.3V LINEAR REGULATOR (CDV                                                                      | DD = 4.7µF) | 1                                                            |                                                                                                      |      |        |                  |                   |  |

| DV <sub>DDIO</sub> Input-Voltage Range                                                           |             |                                                              |                                                                                                      | 4.25 | 5.0    | 5.25             | V                 |  |

| DV <sub>DD</sub> Output Voltage                                                                  |             | REGEN = GNDIO                                                | )                                                                                                    | 3.0  | 3.4    | 3.6              | V                 |  |

| DV <sub>DD</sub> Input-Voltage Range                                                             |             | REGEN = DV <sub>DDIC</sub>                                   |                                                                                                      | 3.0  |        | 3.6              | V                 |  |

| No-Load Quiescent Current                                                                        |             |                                                              | de; all digital peripherals                                                                          |      | 15     |                  | μA                |  |

| Output Short-Circuit Current                                                                     |             | Short to DGND                                                |                                                                                                      |      | 110    |                  | mA                |  |

## **ELECTRICAL CHARACTERISTICS (continued)**

| PARAMETER                                                                  | SYMBOL               | CONDIT                                                                                                                        | IONS                     | MIN  | ТҮР   | MAX  | UNITS |

|----------------------------------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------|--------------------------|------|-------|------|-------|

| SUPPLY VOLTAGE SUPERVISOR                                                  | RS AND BRO           | WNOUT DETECTION                                                                                                               |                          | •    |       |      |       |

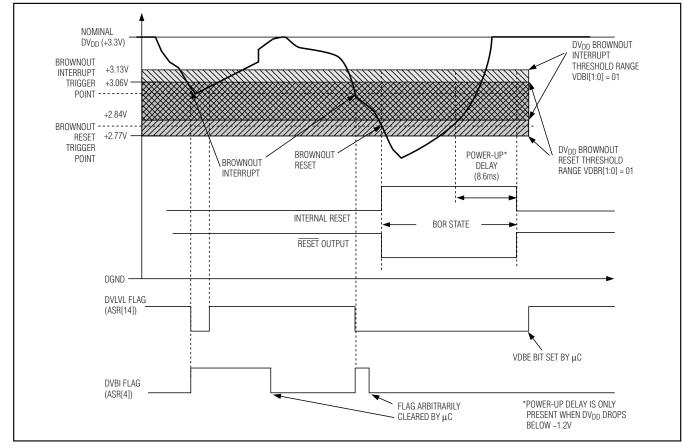

| DV <sub>DD</sub> Voltage-Supervisor Reset<br>Rising Threshold              |                      | Power-on default, DV <sub>DD</sub><br>(Note 9)                                                                                | voltage rising           | 2.70 |       | 2.99 | V     |

|                                                                            |                      | DV <sub>DD</sub> voltage falling, firmware selectable,                                                                        | VDBR = 00b<br>(default)  | 2.70 |       | 2.99 |       |

| DV <sub>DD</sub> Voltage-Supervisor<br>Brownout Reset Falling Threshold    | VVDBR                | measured with CPU                                                                                                             | VDBR = 01b               | 2.77 |       | 3.06 | V     |

|                                                                            |                      | active at 8MHz                                                                                                                | VDBR = 10b               | 2.84 |       | 3.13 |       |

|                                                                            | (Note 10) VDBR = 11b |                                                                                                                               | 2.91                     |      | 3.20  |      |       |

| Software-Selectable DVDD                                                   |                      | DV <sub>DD</sub> voltage falling, firmware selectable,                                                                        | VDBI = 00b<br>(default)  | 2.77 |       | 3.06 |       |

| Voltage-Supervisor Brownout                                                | VVDBI                | measured with CPU                                                                                                             | VDBI = 01b               | 2.84 |       | 3.13 | V     |

| Interrupt Falling Threshold                                                |                      | active at 8MHz                                                                                                                | VDBI = 10b               | 2.91 |       | 3.20 |       |

|                                                                            |                      | (Note 11)                                                                                                                     | VDBI = 11b               | 2.99 |       | 3.27 | 1     |

|                                                                            |                      | DV <sub>DDIO</sub> voltage falling, firmware selectable,                                                                      | VIOBI = 00b<br>(default) | 4.25 |       | 4.74 |       |

| DV <sub>DDIO</sub> Voltage-Supervisor<br>Brownout Interrupt Threshold      | VVIOBI               | measured with CPU                                                                                                             | VIOBI = 01b              | 4.30 |       | 4.79 | V     |

|                                                                            |                      | active at 8MHz                                                                                                                | VIOBI = 10b              | 4.35 |       | 4.84 |       |

|                                                                            |                      | (Note 12)                                                                                                                     | VIOBI = 11b              | 4.40 |       | 4.89 |       |

| Voltage-Supervisor Hysteresis                                              |                      | DV <sub>DD</sub> , DV <sub>DDIO</sub>                                                                                         | •                        |      | 1     |      | %     |

| DV <sub>DD</sub> Brownout-Interrupt to<br>Brownout Reset Falling Threshold |                      | Voltage difference betw<br>V <sub>VDBR</sub> , time allowing so<br>before reset asserted, V<br>VDBR = 10b                     | ftware clean-up          | 155  |       |      | mV    |

|                                                                            |                      | DV <sub>DD</sub>                                                                                                              |                          | 1.0  |       | 3.6  |       |

| Voltage Monitor Range                                                      |                      | DVDDIO                                                                                                                        |                          | 0    |       | 5.25 | V     |

| DV <sub>DD</sub> Ramp-Up Rate                                              |                      | DV <sub>DD</sub> must rise faster th<br>between +2.7V and +3.0                                                                |                          | 35   |       |      | mV/ms |

| RESET Hold Time                                                            |                      | After DV <sub>DD</sub> rises above trip threshold                                                                             | the $V_{VDBR}$ voltage   |      | 16    |      | ms    |

| CAN INTERFACE                                                              |                      |                                                                                                                               |                          |      |       |      |       |

| CAN Baud Rate                                                              |                      | CANCLK = 8MHz                                                                                                                 |                          |      |       | 1    | Mbps  |

| CANCLK Mean Frequency Error                                                |                      | 50ppm external crystal e                                                                                                      | error, 8MHz crystal      |      | 60    |      | ppm   |

| CANCLK Total Frequency Error                                               |                      | 50ppm external crystal error, 8MHz crystal,<br>clock divided and measured over 500µs<br>interval, mean plus peak cycle jitter |                          |      | < 0.5 |      | %     |

| HIGH-FREQUENCY CRYSTAL OS                                                  | CILLATOR             |                                                                                                                               |                          |      |       |      |       |

| Cleak Fragueney                                                            |                      | Using external crystal                                                                                                        |                          | 1.00 |       | 8.12 |       |

| Clock Frequency                                                            |                      | External clock source                                                                                                         |                          |      |       | 8.12 | MHz   |

| Crystal Oscillator Startup Time                                            |                      | 8MHz crystal                                                                                                                  |                          |      | 10    |      | ms    |

| External Clock Input Duty Cycle                                            |                      | Ratio high-to-low or low-                                                                                                     | to-high                  | 45   |       | 55   | %     |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(AV_{DD} = DV_{DDIO} = +5.0V, DV_{DD} = +3.3V, f_{SYSCLK} = 8MHz, V_{REFDAC} = V_{REFADC} = +5V, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C.$ ) (Note 1)

| PARAMETER                        | SYMBOL      | CONDITIONS                                        | MIN                         | ΤΥΡ   | MAX                         | UNITS |

|----------------------------------|-------------|---------------------------------------------------|-----------------------------|-------|-----------------------------|-------|

| Crystal Oscillator Stability     |             | Excluding crystal                                 |                             | 3     |                             | ppm/V |

|                                  |             | HFIC = 00b (default)                              |                             | 7     |                             |       |

| VIN Input Lond Conseitance       |             | HFIC = 01b                                        |                             | 18    |                             |       |

| XIN Input Load Capacitance       |             | HFIC = 10b                                        |                             | 27    |                             | pF    |

|                                  |             | HFIC = 11b                                        |                             | 34    |                             |       |

|                                  |             | HFOC = 00b (default)                              |                             | 6     |                             |       |

| XOUT Output Load Capacitance     |             | HFOC = 01b                                        |                             | 17    |                             | рF    |

| XOOT Output Load Capacitance     |             | HFOC = 10b                                        |                             | 27    |                             | ρr    |

|                                  |             | HFOC = 11b                                        |                             | 34    |                             |       |

| XIN Input Low Voltage            |             | Driven with external clock source                 |                             |       | 0.3 x<br>DV <sub>DD</sub>   | V     |

| XIN Input High Voltage           |             | Driven with external clock source                 | 0.7 x<br>DV <sub>DD</sub>   |       |                             | V     |

| INTERNAL RC OSCILLATOR           |             |                                                   |                             |       |                             | •     |

| Oscillator Frequency             |             |                                                   | 7.0                         | 7.6   | 8.0                         | MHz   |

| Oscillator Startup Time          |             |                                                   |                             | 10    |                             | μs    |

| Oscillator Jitter                |             |                                                   |                             | 2.7   |                             | ns    |

| UART (LIN) INTERFACE (UTX, UF    | RX)         |                                                   |                             |       |                             |       |

| UART Baud Rate                   |             |                                                   | 0                           |       | 2                           | Mbps  |

| Minimum LIN Mode Operation       |             |                                                   |                             |       | 1                           | kbps  |

| Maximum LIN Mode Operation       |             |                                                   | 20                          |       |                             | kbps  |

|                                  |             | Crystal clock source                              | -0.5                        |       | +0.5                        |       |

| UART Baud Rates Error            |             | Using internal RC oscillator before autobaud      | -14.0                       |       | +14.0                       | %     |

|                                  |             | Using internal RC oscillator after autobaud       | -0.5                        |       | +0.5                        |       |

| RESET (RESET)                    |             |                                                   |                             |       |                             |       |

| RESET Internal Pullup Resistance |             | Pullup to DV <sub>DD</sub>                        |                             | 305   |                             | kΩ    |

| RESET Output Voltage             |             | High, RESET deasserted, no load                   | 0.9 x<br>DV <sub>DD</sub>   |       |                             | V     |

|                                  |             | Low, RESET asserted, no load                      |                             |       | 0.4                         |       |

| RESET Input High Voltage         |             |                                                   | 0.7 x<br>DV <sub>DD</sub>   |       |                             | V     |

| RESET Input Low Voltage          |             |                                                   |                             |       | 0.3 x<br>DV <sub>DD</sub>   | V     |

| DIGITAL INPUTS (P0, CANRXD       | , URX, REGE | EN)                                               | •                           |       |                             |       |

| Input Low Voltage                |             |                                                   |                             |       | 0.3 x<br>DV <sub>DDIO</sub> | V     |

| Input High Voltage               |             |                                                   | 0.7 x<br>DV <sub>DDIO</sub> |       |                             | V     |

| Input Hysteresis                 |             |                                                   |                             | 500   |                             | mV    |

| Input Leakage Current            |             | $V_{IN} = GNDIO$ or $DV_{DDIO}$ , pullup disabled | -1                          | ±0.01 | +1                          | μA    |

www.DataSheet4U.com

## **ELECTRICAL CHARACTERISTICS (continued)**

$(AV_{DD} = DV_{DDIO} = +5.0V, DV_{DD} = +3.3V, f_{SYSCLK} = 8MHz, V_{REFDAC} = V_{REFADC} = +5V, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C.$ ) (Note 1)

| PARAMETER                    | SYMBOL     | CONDITIONS                             | MIN                         | ΤΥΡ   | MAX | UNITS |

|------------------------------|------------|----------------------------------------|-----------------------------|-------|-----|-------|

| Input Pullup Resistance      |            | Pullup to DV <sub>DDIO</sub>           |                             | 400   |     | kΩ    |

| Input Capacitance            |            | $V_{IN} = GNDIO \text{ or } DV_{DDIO}$ |                             | 15    |     | рF    |

| DIGITAL OUTPUTS (P0, CAN     | ITXD, UTX) |                                        |                             |       |     |       |

| Output Low Voltage           |            | I <sub>SINK</sub> = 1.6mA              |                             |       | 0.4 | V     |

| Output High Voltage          |            | ISOURCE = 1.6mA                        | DV <sub>DDIO</sub><br>- 0.5 |       |     | V     |

| Output Leakage Current       |            | I/O pins, three-state                  | -1                          | ±0.01 | +1  | μA    |

| Output Capacitance           |            | I/O pins, three-state                  |                             | 15    |     | рF    |

| Output Short Circuit Current |            | Short to $DV_{DDIO} = +5.25V$          |                             | 29    |     | m ^   |

| Output Short-Circuit Current |            | Short to GNDIO                         |                             | 28    |     | - mA  |

**Note 1:** All devices are 100% production tested at  $T_A = +25^{\circ}C$ .

Note 2: All analog functions disabled and all digital inputs connected to supply or ground.

Note 3: Medium-speed mode: CPU and one timer running at 1MHz from an external crystal oscillator, all other peripherals disabled, all digital I/Os static at DV<sub>DDIO</sub> or GNDIO.

**Note 4:** High-speed mode: CPU and three timers running at 8MHz from an external crystal oscillator, CAN enabled and communicating at 500kbps, all other peripherals disabled, all digital I/Os static at DV<sub>DDIO</sub> or GNDIO.

Note 5: Low-speed mode: CPU and one timer running from an external crystal oscillator in PMM mode, all other peripherals disabled, all digital I/Os static at DV<sub>DDIO</sub> or GNDIO.

Note 6: CAN transmitting at 500kbps, one timer output at 500kHz, all active I/Os are loaded with 20pF capacitor, all remaining digital I/Os are at DV<sub>DDIO</sub> or GNDIO.

Note 7: Guaranteed by design and characterization.

Note 8: Based on diode ideality factor of 1.008.

Note 9: DV<sub>DD</sub> must rise above V<sub>VDBR</sub> for RESET to become deasserted. Caution: Operation is not guaranteed for DV<sub>DD</sub> below +2.7V (utility ROM) or +3.0V (flash).

Note 10: RESET is asserted if DV<sub>DD</sub> falls below V<sub>VDBR</sub>. Caution: Operation is not guaranteed for DV<sub>DD</sub> below +2.7V (utility ROM) or +3.0V (flash).

Note 11: An interrupt is generated if DV<sub>DD</sub> falls below V<sub>VDBI</sub>. Caution: Operation is not guaranteed for DV<sub>DD</sub> below +2.7V (utility ROM) or +3.0V (flash).

Note 12: An interrupt is generated if DV<sub>DDIO</sub> falls below V<sub>VIOBI</sub>. Caution: Operation is not guaranteed if DV<sub>DDIO</sub> or AV<sub>DD</sub> is below 4.75V, except for the DV<sub>DDIO</sub> brownout monitor and +3.3V linear regulator, that still operate down to 0V and +4.25V, respectively.

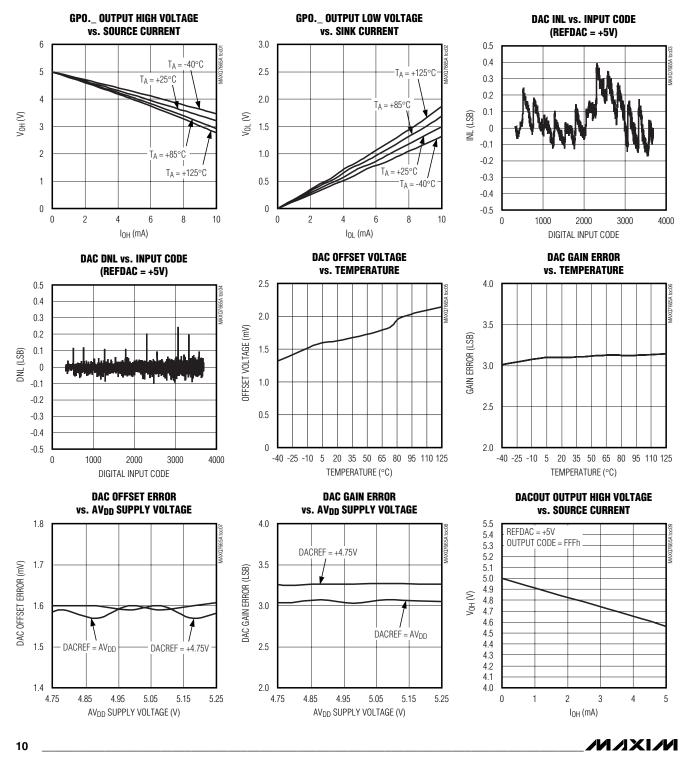

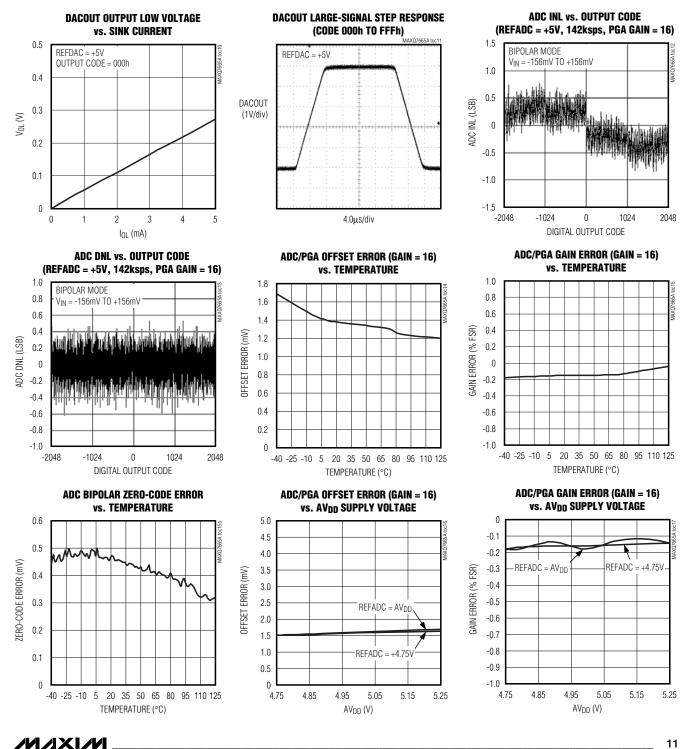

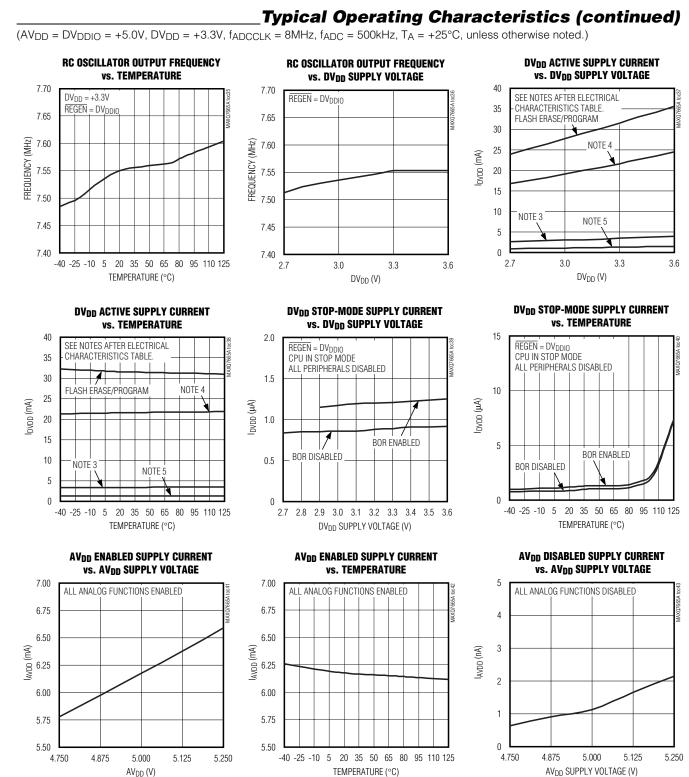

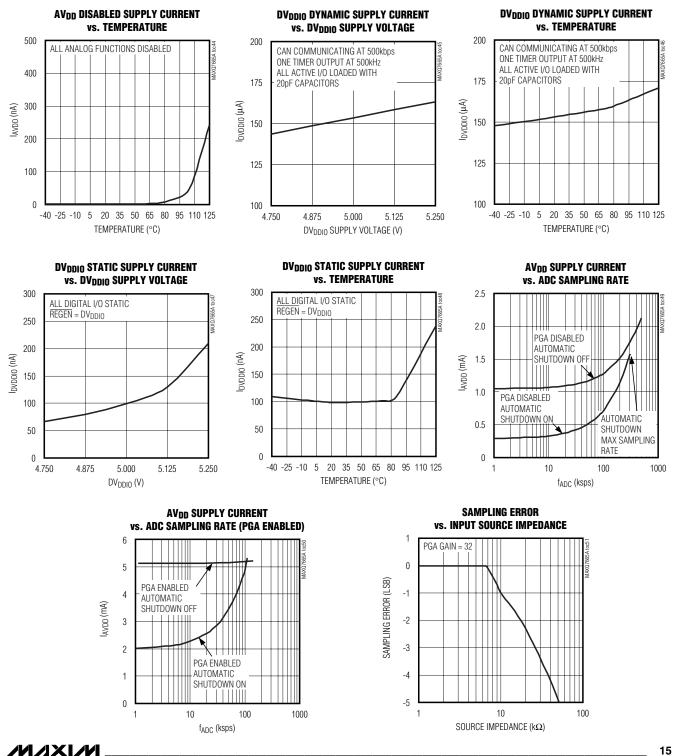

(AV<sub>DD</sub> = DV<sub>DDIO</sub> = +5.0V, DV<sub>DD</sub> = +3.3V, f<sub>ADCCLK</sub> = 8MHz, f<sub>ADC</sub> = 500kHz, T<sub>A</sub> = +25°C, unless otherwise noted.)

MAXQ7665A-MAXQ7665D

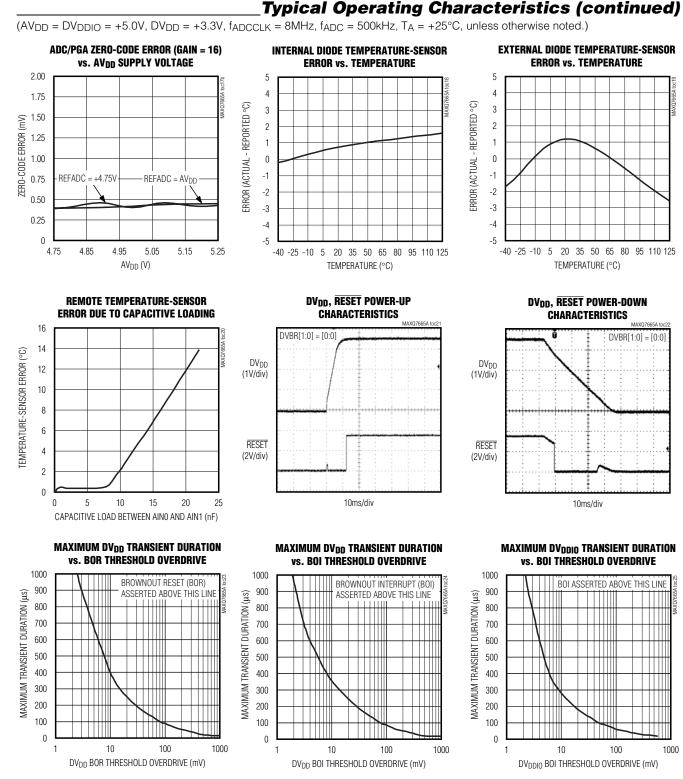

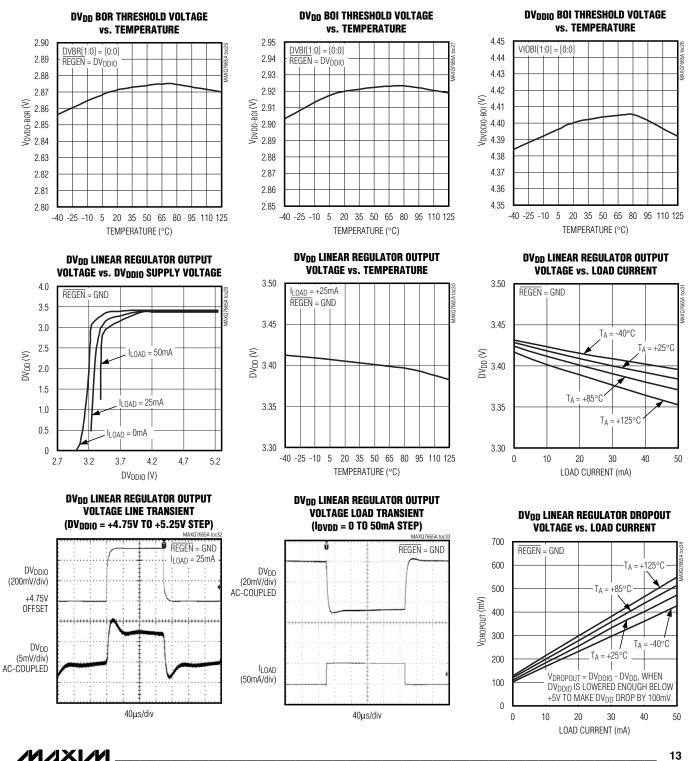

## **Typical Operating Characteristics (continued)**

(AVDD = DVDDIO = +5.0V, DVDD = +3.3V, fADCCLK = 8MHz, fADC = 500kHz, TA = +25°C, unless otherwise noted.)

/N/IXI/N

(AVDD = DVDDIO = +5.0V, DVDD = +3.3V, fADCCLK = 8MHz, fADC = 500kHz, TA = +25°C, unless otherwise noted.)

MAXQ7665A-MAXQ7665D

M \X | M

(AV<sub>DD</sub> = DV<sub>DDIO</sub> = +5.0V, DV<sub>DD</sub> = +3.3V, f<sub>ADCCLK</sub> = 8MHz, f<sub>ADC</sub> = 500kHz, T<sub>A</sub> = +25°C, unless otherwise noted.)

## **Pin Description**

| PIN        | NAME               | FUNCTION                                                                                                                                                                                                                                                |

|------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | AIN11              | Analog Input Channel 11. AIN11 is multiplexed to the PGA as a differential input with AIN10.                                                                                                                                                            |

| 2          | AIN10              | Analog Input Channel 10. AIN10 is multiplexed to the PGA as a differential input with AIN11.                                                                                                                                                            |

| 3          | AIN9               | Analog Input Channel 9. AIN9 is multiplexed to the PGA as a differential input with AIN8.                                                                                                                                                               |

| 4          | AIN8               | Analog Input Channel 8. AIN8 is multiplexed to the PGA as a differential input with AIN9.                                                                                                                                                               |

| 5, 8       | AGND               | Analog Ground                                                                                                                                                                                                                                           |

| 6          | REFADC             | ADC External Reference Input. Connect an external reference voltage between 1V and AV <sub>DD</sub> to REFADC.                                                                                                                                          |

| 7          | REFDAC             | DAC External Reference Input. Connect an external reference voltage between 0V and AV_DD to REFDAC.                                                                                                                                                     |

| 9          | AIN7               | Analog Input Channel 7. AIN7 is multiplexed to the PGA as a differential input with AIN6.                                                                                                                                                               |

| 10         | AIN6               | Analog Input Channel 6. AIN6 is multiplexed to the PGA as a differential input with AIN7.                                                                                                                                                               |

| 11         | AIN5               | Analog Input Channel 5. AIN5 is multiplexed to the PGA as a differential input with AIN4.                                                                                                                                                               |

| 12         | AIN4               | Analog Input Channel 4. AIN4 is multiplexed to the PGA as a differential input with AIN5.                                                                                                                                                               |

| 13         | AIN3               | Analog Input Channel 3. AIN3 is multiplexed to the PGA as a differential input with AIN2.<br>AIN3–AIN0 have remote temperature sensor capability.                                                                                                       |

| 14         | AIN2               | Analog Input Channel 2. AIN2 is multiplexed to the PGA as a differential input with AIN3.<br>AIN3–AIN0 have remote temperature sensor capability.                                                                                                       |

| 15         | AIN1               | Analog Input Channel 1. AIN1 is multiplexed to the PGA as a differential input with AIN0.<br>AIN3–AIN0 have remote temperature sensor capability.                                                                                                       |

| 16         | AINO               | Analog Input Channel 0. AIN0 is multiplexed to the PGA as a differential input with AIN1.<br>AIN3–AIN0 have remote temperature sensor capability.                                                                                                       |

| 17         | DACOUT             | DAC Buffer Output. DACOUT is the DAC voltage buffer output.                                                                                                                                                                                             |

| 18, 19, 31 | DGND               | Digital Ground for the Digital Core and Flash                                                                                                                                                                                                           |

| 20         | CANRXD             | CAN Bus Receiver Input. Control area network receiver input.                                                                                                                                                                                            |

| 21         | CANTXD             | CAN Bus Transmitter Output. Control area network transmitter output.                                                                                                                                                                                    |

| 22         | UTX                | UART Transmitter Output                                                                                                                                                                                                                                 |

| 23         | URX                | UART Receiver Input                                                                                                                                                                                                                                     |

| 24         | P0.6/T0            | Port 0 Bit 6/Timer 0. P0.6 is a general-purpose digital I/O with interrupt/wake-up input capability T0 is a primary timer/PWM input or output.                                                                                                          |

| 25         | P0.7/T1            | Port 0 Bit 7/Timer 1. P0.7 is a general-purpose digital I/O with interrupt/wake-up input capability T1 is a primary timer/PWM input or output.                                                                                                          |

| 26, 39     | DV <sub>DDIO</sub> | Digital I/O Supply Voltage. Supplies all digital I/O except for XIN, XOUT, and RESET. Bypass $DV_{DDIO}$ to GNDIO with a 0.1µF capacitor placed as close as possible to the device. $DV_{DDIO}$ is also connected to the input of the linear regulator. |

| 27         | GNDIO              | Digital I/O Ground                                                                                                                                                                                                                                      |

| 28, 29     | I.C.               | Internal Connection. Connect I.C. to GNDIO or DV <sub>DDIO</sub> .                                                                                                                                                                                      |

| 30         | N.C.               | No Connection. No internal connection. Leave N.C. unconnected.                                                                                                                                                                                          |

| 32         | P0.0/TDO           | Port 0 Data 0/JTAG Serial Test Data Output. P0.0 is a general-purpose digital I/O with interrupt/wake-up capability. TDO is the JTAG serial test, data output.                                                                                          |

## Pin Description (continued)

| PIN | NAME             | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 33  | P0.1/TMS         | Port 0 Data 1/JTAG Test Mode Select. P0.1 is a general-purpose digital I/O with interrupt/wake-<br>up capability. TMS is the JTAG test mode, select input.                                                                                                                                                                                                                                                                                                                                                                                                        |

| 34  | P0.2/TDI         | Port 0 Data 2/JTAG Serial Test Data Input. P0.2 is a general-purpose digital I/O with interrupt/wake-up capability. TDI is the JTAG serial test, data input.                                                                                                                                                                                                                                                                                                                                                                                                      |

| 35  | P0.3/TCK         | Port 0 Data 3/JTAG Serial Test Clock Input. P0.3 is a general-purpose digital I/O with interrupt/wake-up capability. TCK is the JTAG serial test, clock input.                                                                                                                                                                                                                                                                                                                                                                                                    |

| 36  | P0.4/ADCCNV      | Port 0 Data 4/ADC Start Conversion Control. P0.4 is a general-purpose digital I/O. ADCCNV is firmware configurable for a rising or falling edge start/convert to trigger ADC conversions.                                                                                                                                                                                                                                                                                                                                                                         |

| 37  | P0.5/DACLOAD     | Port 0 Data 5/DAC Data Register Load/Update Input. P0.5 is a general-purpose digital I/O with interrupt/wake-up capability. DACLOAD is firmware configurable for a rising or falling edge to update the DACOUT register.                                                                                                                                                                                                                                                                                                                                          |

| 38  | REGEN            | Active-Low Linear Regulator Enable Input. Connect $\overline{\text{REGEN}}$ to GNDIO to enable the linear regulator. Connect to $\text{DV}_{\text{DDIO}}$ to disable the linear regulator.                                                                                                                                                                                                                                                                                                                                                                        |

| 40  | DV <sub>DD</sub> | Digital Supply Voltage. DV <sub>DD</sub> supplies the internal digital core and flash memory. DV <sub>DD</sub> is internally connected to the output of the internal 3.3V linear regulator. Disable the internal regulator to connect DV <sub>DD</sub> to an external supply. When using the on-chip linear regulator, bypass DV <sub>DD</sub> to DGND with a 4.7 $\mu$ F ±20% capacitor with a maximum ESR of 0.5 $\Omega$ . In addition, bypass DV <sub>DD</sub> with a 0.1 $\mu$ F capacitor. Place both bypass capacitors as close as possible to the device. |

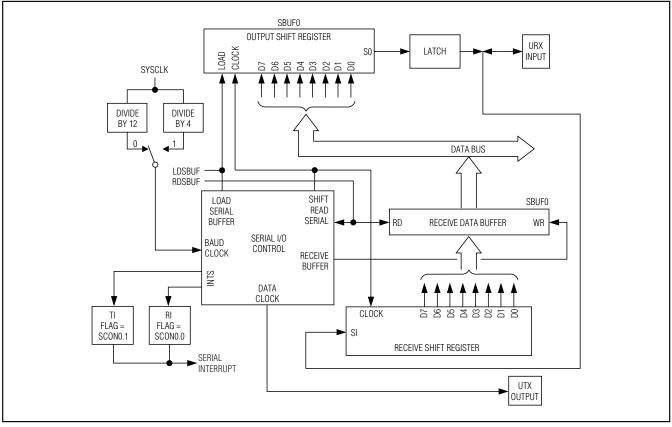

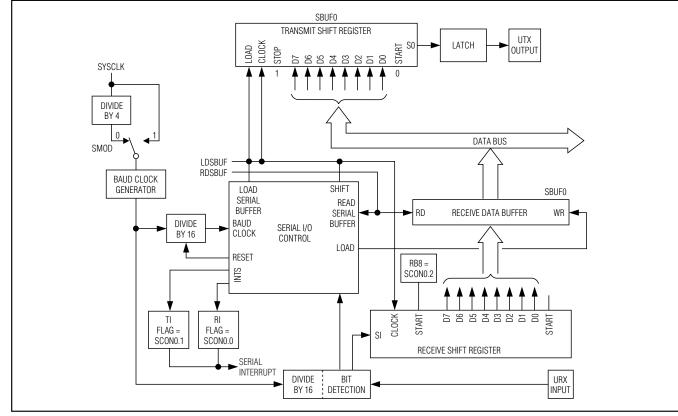

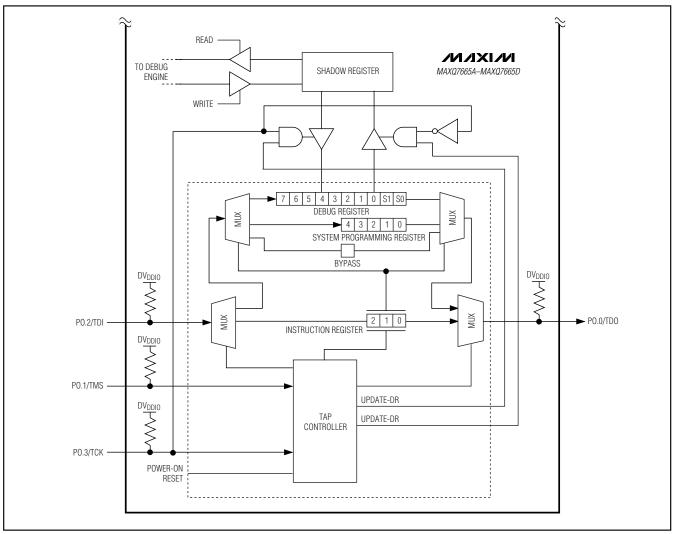

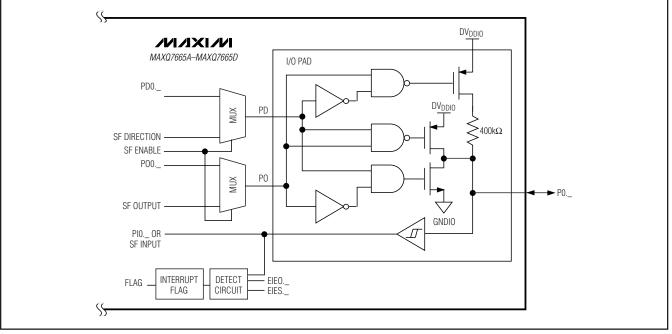

| 41  | RESET            | Reset Input and Output. Active-low open-drain input/output with internal $360k\Omega$ pullup to DV <sub>DD</sub> . Drive low to reset the $\mu$ C. RESET is low during power-up reset and during DV <sub>DD</sub> brownout conditions.                                                                                                                                                                                                                                                                                                                            |