# 16 BIT ERROR CHECKING & CORRECTION

# MB1426

April, 1986 Edition 1.0

## DESCRIPTION

The MB1426 Error Checking and Correction (ECC) device is designed to enhance memory reliability in 16-bit systems. Using a modified Hamming Single-Error-Correction/Double-Error-Detection (SEC/DED) code, the ECC can find and correct all single-bit errors and detect all double-bit errors. The MB1426 is a TTL device fabricated in low-power Schottky and is housed in a 64-pin Pin-Grid-Array (PGA) package.

#### FEATURES

- Detects and corrects all single-bit errors

- Detects all double-bit errors

- On-chip latches for memory-read, check-bit, and syndrome data

- Separate busses for CPU and memory data

- Direct read/write by ECC-through mode

- Low power Schottky TTL for high performance

- Single +5V supply

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit.

## **PIN ASSIGNMENTS**

|               |          |             |                |                |                | _              | _              | _              |                |

|---------------|----------|-------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| 0<br>28       | 0<br>27  | 0<br>26     | 0<br>25        | 0<br>24        | <b>0</b><br>23 | <b>0</b><br>22 | 0<br>21        | <b>0</b><br>20 | <b>O</b><br>19 |

| 29            | 0<br>58  | <b>6</b> 57 | <b>2</b> 6     | <b>9</b><br>55 | <b>0</b><br>54 | <b>9</b><br>53 | <b>0</b><br>52 | <b>0</b><br>51 | <b>0</b><br>18 |

| 30<br>30      | 0<br>59  |             |                |                |                |                |                | <b>0</b><br>50 | 0<br>17        |

| 31            | 60       |             |                |                |                |                |                | <b>0</b><br>49 | 0<br>16        |

| 0<br>32       | 61<br>61 |             |                |                |                |                |                | <b>0</b><br>48 | <b>0</b><br>15 |

| 0<br>33       | 62<br>62 |             |                |                |                |                |                | 0<br>47        | <b>O</b><br>14 |

| 0<br>34       | 63       |             |                |                |                |                |                | <b>0</b><br>46 | 0<br>13        |

| 0<br>35       | 0<br>64  | 0           | NDE            | x              |                |                |                | <b>0</b><br>45 | 0<br>12        |

| 0<br>36       | 0<br>37  | 0<br>38     | <b>0</b><br>39 | <b>0</b><br>40 | 0<br>41        | 0<br>42        | <b>0</b><br>43 | 0<br>44        | 0<br>11        |

| <b>0</b><br>1 | 2        | 0<br>3      | <b>0</b><br>4  | <b>0</b><br>5  | <b>0</b><br>6  | 9<br>7         | 0<br>8         | °              | <b>O</b><br>10 |

| No. | I/O | Name  | No. | I/O | Name  | No. | I/O | Name  | No. | I/O | Name |

|-----|-----|-------|-----|-----|-------|-----|-----|-------|-----|-----|------|

| 01  | В   | CD08  | 17  | В   | CB1   | 33  | I   | PWC0  | 49  | В   | CB4  |

| 02  | 1   | PWC1  | 18  | В   | CB2   | 34  | В   | CD14  | 50  | В   | CB5  |

| 03  | В   | CD07  | 19  | В   | MD01  | 35  | В   | CD12  | 51  | В   | MD00 |

| 04  | В   | CD05  | 20  | В   | MD03  | 36  | В   | CD10  | 52  | В   | MD02 |

| 05  | В   | CD04  | 21  | В   | MD04  | 37  | В   | CD09  | 53  | В   | MD05 |

| 06  | В   | CD03  | 22  | В   | MD06  | 38  | 1   | ECCTH | 54  |     | GND  |

| 07  | В   | CD01  | 23  | В   | MD07  | 39  | В   | CD06  | 55  | В   | MD09 |

| 08  | 0   | ERR   | 24  | В   | MD08  | 40  |     | GND   | 56  | В   | MD11 |

| 09  | 0   | MERR  | 25  | В   | MD10  | 41  | В   | CD02  | 57  | В   | MD13 |

| 10  | Т   | STCB0 | 26  | В   | MD12  | 42  | В   | CD00  | 58  | В   | MD15 |

| 11  | Т   | STCB1 | 27  | В   | MD14  | 43  | I   | ERREN | 59  | I   | RCLK |

| 12  | Т   | STCB2 | 28  | 1   | BSCNT | 44  | Ι   | EN    | 60  | 0   | PERR |

| 13  | Т   | STCB3 | 29  | В   | P1    | 45  | I   | SLE   | 61  |     | VCC  |

| 14  | Т   | STCB4 | 30  | 0   | PERR1 | 46  | I   | RST   | 62  | В   | CD15 |

| 15  | т   | STCB5 | 31  | В   | P0    | 47  |     | VCC   | 63  | В   | CD13 |

| 16  | В   | CB0   | 32  | 0   | PERR0 | 48  | В   | CB3   | 64  | В   | CD11 |

B: Bidirectional pin

I: Input pin

O: Output pin

3

## **PIN DESCRIPTIONS**

----

| Pin No. | Designator                               | Function                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |  |  |

|---------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|

| 33      | PWC0                                     | Partial Write Control/Read Write Control:                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |  |  |

| 2       | PWC1                                     | These pins are used to control read write and they are also used to control the partial write.                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |  |  |  |

|         |                                          | If both $\overline{PWC0}$ and $\overline{PWC1}$ = "H" the read operation is selected.                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |  |  |

|         |                                          | If both $\overline{PWC0}$ and $\overline{PWC1}$ = "L" the word write operation is selected.                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |  |  |

|         |                                          | In the partial write mode, if $\overrightarrow{PWC0}$ = "L" and $\overrightarrow{PWC1}$ = "H", the lower byte (MD0 to MD7) is written CPU data and the upper byte (MD8 to MD15) is written memory data which is latched during previous read operation. On the other hand, if $\overrightarrow{PWC0}$ = "H" and $\overrightarrow{PWC1}$ = "L" the lower byte is written memory data and the upper byte is written CPU data. |  |  |  |  |  |  |  |  |  |  |  |

| 59      | RCLK                                     | Read Data Latch Clock:                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |  |

|         |                                          | This pin is used to strobe the read data from memory and latch into the internal read data latch.<br>The rising edge of RCLK strobes read data from MD00/MD15 and check bits from CB0/CB5.                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |  |  |  |

|         |                                          | In the read cycle, data is strobed on the rising of RCLK.                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |  |  |

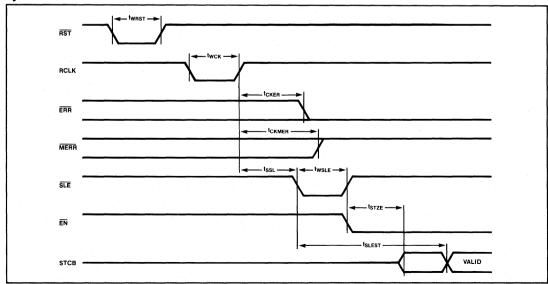

| 45      | SLE                                      | Syndrome Latch Enable:                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |  |

|         | )                                        | This pin is used to latch syndrome bits into the internal syndrome latch. The falling edge of $\overline{SLE}$ strobes and latches the syndrome bits until $\overline{RST}$ = "L".                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |  |  |

| 46      | RST                                      | Syndrome Latch Reset:                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |  |  |

|         |                                          | This pin is used to reset syndrome latch. If $\overrightarrow{RST}$ = "L", the syndrome latch is reset and the latch is enabled to accept next string of syndrome bits.                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |

| 43      | ERREN                                    | Error Enable:                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |  |  |

|         | 4                                        | This pin is used to enable ERR and MERR outputs.                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |  |

|         |                                          | If ERREN = "L", ERR and MERR are set "H" and disabled.                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |  |

| 44      | ĒN                                       | Syndrome Output Enable:                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |

|         |                                          | This pin is used to enable syndrome outputs (STCB0 and STCB5).                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |  |  |  |

|         |                                          | If EN = "L", STCB0/STCB5 are enabled. If EN = "H", STCB0/STCB5 are disabled and in the high-<br>impedance state.                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |  |

| 38      | ECCTH                                    | ECC Through:                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |  |  |

|         |                                          | This pin is used to enable the ECC-through mode.                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |  |

|         |                                          | If ECCTH = "L", ECC-through mode is enabled and the read or write cycle is executed without regard to the ECC function.                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |

|         |                                          | When ECC is utilized, the ECCTH pin must be "H".                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |  |  |

| 28      | BSCNT                                    | Bus Control:                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |  |  |

|         |                                          | This pin is used to control the operating mode of data pins CD00/CD15 and MD00/MD15, also to disable PERR0, PERR1 and PERR.                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |  |  |

|         | n an | If BSCNT = "L" all data pins are in the input mode and PERR0, PERR1 and PERR are disabled (set "H").                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |  |  |  |

|         |                                          | If $\overrightarrow{\text{BSCNT}}$ = "H", the operating mode of these data pins is controlled by the states of $\overrightarrow{\text{PWC0}}$ , and $\overrightarrow{\text{PWC1}}$ , and $\overrightarrow{\text{PERR0}}$ , $\overrightarrow{\text{PERR1}}$ and $\overrightarrow{\text{PERR}}$ are enabled corresponding the the state of $\overrightarrow{\text{PWC0}}$ and $\overrightarrow{\text{PWC1}}$ .                |  |  |  |  |  |  |  |  |  |  |  |

| 42      | CD00                                     | CPU Data:                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |  |  |

| 7       | CD01                                     | These pins have a common I/O capability and are connected to the CPU data bus.                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |  |  |  |

| 41<br>6 | CD02<br>CD03                             | In the write cycle, these pins are in the input mode, that is, the CPU data is input to these pins an                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |  |  |

3-41

| Pin No.  | Designator   | Function                                                                                                                                                                |

|----------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5        | CD04         | output to memory through MD00/MD15.                                                                                                                                     |

| 4        | CD05         | In a read cycle, these pins are in the output mode, that is, memory data from MD00/MD15 is                                                                              |

| 39       | CD06         | output to the CPU via these pins.                                                                                                                                       |

| 3        | CD07         |                                                                                                                                                                         |

| 1        | CD07         |                                                                                                                                                                         |

|          |              |                                                                                                                                                                         |

| 37       | CD09         |                                                                                                                                                                         |

| 36       | CD10         |                                                                                                                                                                         |

| 64       | CD11         |                                                                                                                                                                         |

| 35       | CD12         |                                                                                                                                                                         |

| 63       | CD13         |                                                                                                                                                                         |

| 34       | CD14         |                                                                                                                                                                         |

| 62       | CD15         |                                                                                                                                                                         |

| 51       | MD00         | Memory Data:                                                                                                                                                            |

| 19       | MD01         | These pins have a common I/O capability and they are connected to the memory data bus.                                                                                  |

| 52       | MD02         |                                                                                                                                                                         |

| 20       | MD03         | In a write cycle, these pins are in the output mode, that is, CPU data from CD00/CD15 is output to                                                                      |

| 21       | MD04         | memory through these pins.                                                                                                                                              |

| 53       | MD05         | In a read cycle, these pins are in the input mode, that is, memory data is input to these pins and                                                                      |

| 22       | MD06         | output through CD00/CD15.                                                                                                                                               |

| 23       | MD07         |                                                                                                                                                                         |

| 24       | MD08         |                                                                                                                                                                         |

| 55       | MD09         |                                                                                                                                                                         |

| 25       | MD10         |                                                                                                                                                                         |

| 56       | MD10<br>MD11 |                                                                                                                                                                         |

| 16       | MD12         |                                                                                                                                                                         |

| 57       | MD12<br>MD13 |                                                                                                                                                                         |

| 27       | MD13<br>MD14 |                                                                                                                                                                         |

| 27<br>58 | MD14<br>MD15 |                                                                                                                                                                         |

|          | MD15         |                                                                                                                                                                         |

| 31       | P0           | Parity Bit:                                                                                                                                                             |

| 29       | P1           | These pins have a common I/O capability and P0 and P1 correspond, respectively, to the lower byte and the upper byte. The parity bit from the CPU should be odd parity. |

| 16       | CB0          | Check Bit:                                                                                                                                                              |

| 17       | CB1          | These pins have a common I/O capability and are connected to the check bit memory I/O line.                                                                             |

| 18       | CB2          |                                                                                                                                                                         |

| 48       | CB3          | In a write cycle, check bit data is generated by the check bit generator using CPU data; the                                                                            |

| 49       | CB4          | check-bit pattern is output to check bit memory, that is, during a write cycle, these pins operate ir                                                                   |

| 50       | CB5          | the output mode.                                                                                                                                                        |

|          |              | In a read cycle, the check-bit pattern from memory is input to these pins, that is, during a read cycle, these pins operate in the input mode.                          |

| 10       | STCB0        | Syndrome-Through Check Bit:                                                                                                                                             |

| 11       | STCB1        |                                                                                                                                                                         |

| 12       | STCB2        | These pins output the syndrome bits when read or partial write is selected. These outputs are                                                                           |

| 13       | STCB3        | used to analyze an error bit in the data word (CD00/CD15) and in the check bits (CB0/CB5).                                                                              |

| 14       | STCB4        | In the ECC-through mode, these pins output the check bits from memory.                                                                                                  |

| 15       | STCB5        |                                                                                                                                                                         |

| 8        | ERR          | Error:                                                                                                                                                                  |

| -        |              |                                                                                                                                                                         |

|          |              | This pin outputs the error flag when any single- or multiple-bit error is detected.                                                                                     |

## **PIN DESCRIPTIONS** (continued)

3

#### PIN DESCRIPTIONS (continued)

| Pin No.  | Designator    | Function                                                                                                                                                                                                               |

|----------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9        | MERR          | Multiple Error:                                                                                                                                                                                                        |

|          |               | This pin outputs the multiple error flag when a multiple-bit error is detected.                                                                                                                                        |

| 32       | PERR0         | Parity Error:                                                                                                                                                                                                          |

| 30<br>60 | PERR1<br>PERR | These pins output a parity error flag when parity error occurs on CPU data. If PERR0 = "L", a parity error on CD00/CD07 and P0 occurs. If PERR1 = "L", a parity error on CD8/CD15 and P1 occurs. PERR = PERR0 · PERR1. |

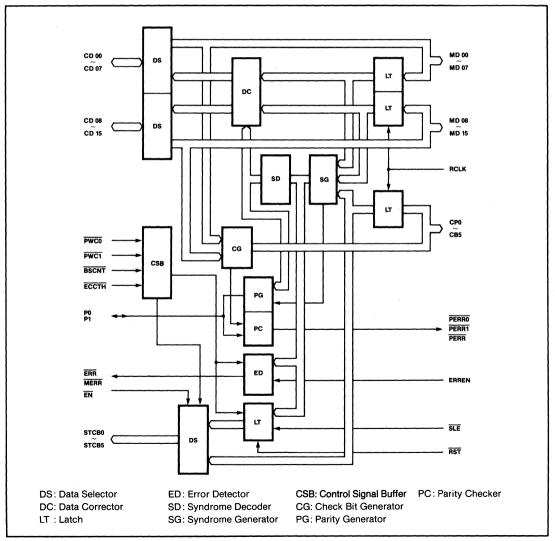

## **BLOCK DIAGRAM**

#### ANALYSIS OF BLOCK DIAGRAM

DS (Data Selector): Selects memory-read or memory-write data.

**DC (Data Corrector):** Corrects a single-bit error by using syndrome decoder.

LT (Latches): Latches memory-read, check-bit, and syndrome data.

**ED (Error Detector):** Detects single-bit or double-bit errors of memory-read data (MD00/MD15 and CB0/CB5). Single-bit or double-bit errors are determined, respectively, by the states of ERR and MERR.

**SG (Syndrome Generator):** Generates a syndrome-bit pattern to check memory-read data.

**SD** (Syndrome Decoder): Decodes syndrome-bit pattern of Syndrome Generator. When a single-bit error is detected, locates error bit and inverts the parity bit.

CSB (Control Signal Buffer): Buffers all control signals.

CG (Check Bit Generator): Generates check bit for checking memory-write data.

PG (Parity Generator): Generates odd parity bit for bus data.

PC (Parity Checker): Checks odd parity bit for bus data.

SDS (Syndrome Data Selector): Selects syndrome data or memory-check bit.

#### FUNCTIONAL DESCRIPTION

The error-detecting and error-correcting capabilities of the MB1426 ECC provides the user with a high order of confidence in memory reliability. Using a modified Hamming SEC/DED code, the ECC is able to detect and correct all single-bit errors and to detect all double-bit errors, even those containing consecutive strings of 0s and 1s. The detect/correct cycle for single-bit errors occurs without interrupting the CPU. Error flags notify the user when an error is detected.

The MB1426 has on-chip latches for memory-read, check-bit, and syndrome data; latching of the memory data allows the user to execute a partial (byte) write. To further enhance transmission reliability, a parity generator and checker is available to the user. A brief description of the read, write, and partial-write capabilities are described in subsequent paragraphs; for a detailed analysis of operating principles, refer to the Functional Truth Tables.

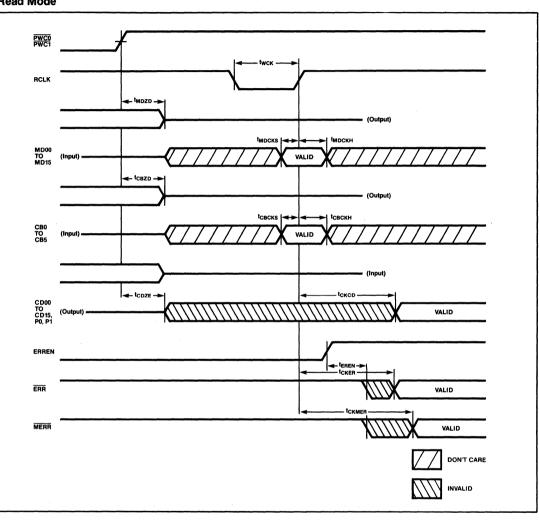

#### **Read Cycle**

The read cycle is executed by setting BSCNT, PWC0, and PWC1 to the High state. The data and check bits from memory are read out and latched on the rising edge of RCLK; the latched data is sent to the syndrome generator and data corrector. The syndrome bit pattern is generated and decoded by the syndrome decoder; the decoded results are then sent to the data corrector.

If a single-bit error is detected, the  $\overline{ERR}$  flag is raised and the error is corrected by the data corrector; the corrected data is output to CD00/CD15. When a single-bit error is detected and  $\overline{SLE}$  is driven Low, the falling edge triggers the syndrome latches; this latched data is output to STCB0/STCB5 when  $\overline{EN}$  is driven Low. Because data is held in the syndrome latches until  $\overline{RST}$  is driven Low, " $\overline{RST}$  = L" should be executed before the syndrome data is used to identify the error-bit location.

If multiple-bit errors or a bit string (0s or 1s) error is detected, both ERR and MERR flags are raised and the latched memory data is output to CD00/CD15. For these cases, the data correction cycle is not executed.

In the read cycle, odd parity bits for bytes MD00/MD07 and MD08/MD15, respectively, are output to P0 and P1.

#### Write Cycle

Write capabilities of the MB1426 include both word write and partial (byte) write; either operation can be selected by setting PWC0 and PWC1 to the proper states—see Truth Tables that follow. If the CPU is capable of parity coding, the parity bits of P0 and P1 are utilized and, in both the word and paritial-byte write modes, the parity bits are checked.

The word write mode is executed by setting both PWC0 and PWC1 to the Low state. In the word-write mode, CPU data from CD00/CD15 is transferred to the check-bit generator and to MD00/MD15. Data appearing at MD00/MD15 is output and written into memory. The check-bit generator uses the CPU data to generate the check bits and these are output to CB0/CB5. The CPU and check-bit data are written into memory during the same write cycle.

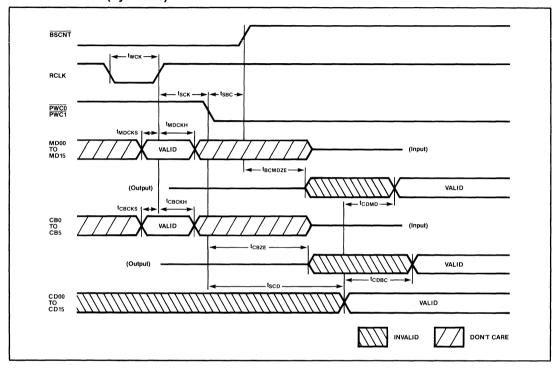

The partial write mode is executed by setting either  $\overline{PWC0}$  or  $\overline{PWC1}$  to the Low state. If  $\overline{PWC0}$  is Low and  $\overline{PWC1}$  is High, the partial write is performed on byte CD00/CD07; in reverse states, byte CD08/CD15 is affected. Before a partial write is executed, the memory and check-bit data must be latched by setting  $\overline{BBSCNT}$  to the Low state; this action puts CD00/CD15, MD00/MD15, P0, and P1 in the input mode and avoids data output to the CPU and memory.

The 8-bits of CPU data to be written to memory and the data to be read from memory are sent to the check-bit generator and to MD00/MD15; the data on MD00/MD15 is written into memory. Check bits are generated from 8-bits of CPU data and 8-bits of memory data and the check bits are then output to CB0/CB5. The partial write operation can be summarized as follows:

- Set BBSCNT Low and latch the 16-bit memory data and 6 check bits by executing a read cycle.

- Set either PWC0 or PWC1 Low and execute a write cycle.

(In this case, BSCNT should be High to change MD00/ MD15 from the input to the output mode.)

- Check bits are generated by 8 bits of CPU data and 8 bits of memory data.

## FUNCTIONAL TRUTH TABLES

## CPU Bus/Memory Bus Control

| BSCNT | PWC0 | PWC1 | CD00 to<br>CD07, P0 | CD08 to<br>CD15, P1 | MD00 to MD07        | MD08 to MD15        | Function      |

|-------|------|------|---------------------|---------------------|---------------------|---------------------|---------------|

|       | н    | н    | Output              | Output              | Input               | Input               | Read          |

| н     | L    | н    | Input               | Input               | Output <sup>1</sup> | Output <sup>2</sup> | Partial Write |

|       | н    | L    | Input               | Input               | Output <sup>2</sup> | Output <sup>1</sup> | Farilar Write |

|       | L    | L    | Input               | Input               | Output              | Output              | Write         |

| L     | х    | х    | Input               | Input               | Input               | Input               | No function   |

Notes:

1. The CPU data is written into memory.

2. Memory data from previous read cycle is written into memory.

## Syndrome Output Control

| ECCTH | PWC0 | PWC1 | EN | CB0 to CB5 | STCB0 to STCB5 | Function      |  |  |

|-------|------|------|----|------------|----------------|---------------|--|--|

|       | н    | н    |    | Input      | Syndrome       | Read          |  |  |

| н     | L    | н    |    | Output     | Quadranas      | Dentiel Maine |  |  |

|       | н    | L L  | L  | Output     | Syndrome       | Partial Write |  |  |

|       | L    | L    |    | Output     |                | Write         |  |  |

| L     | х    | х    |    | Input      | Check Bit      | ECC-Through   |  |  |

| X     | х    | х    | н  |            | High-Z         |               |  |  |

## Hamming Code

|                 | CPU Data |   |   |   |   |   |   |   |   |   |    |      |    | -  |    |    |          |

|-----------------|----------|---|---|---|---|---|---|---|---|---|----|------|----|----|----|----|----------|

| Check Bit       | 0        | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | . 11 | 12 | 13 | 14 | 15 | Function |

| CB0             |          | х |   | x |   | х |   | Х |   | X |    | X    | ÷  | Х  |    | Х  | Odd      |

| CB1             |          |   | х | x |   |   | х | х |   |   | x  | x    |    |    | x  | Х  | Odd      |

| CB2             |          |   |   |   | х | х | х | x | х | x | x  |      | х  |    |    | X  | Even     |

| CB3             | x        | х | х | x | х | X | х | x | х |   |    |      |    |    |    |    | Odd      |

| CB4             | x        | х | х |   | х |   |   | x |   |   |    |      | х  | х  | x  | х  | Even     |

| C <sub>B5</sub> | x        |   |   |   |   |   |   |   | x | x | х  | х    | x  | х  | x  | х  | Odd      |

3

## FUNCTIONAL TRUTH TABLES (continued) Check Bit Generation

CB0 = CD01 + CD03 + CD05 + CD07 + CD09 + CD11 + CD13 + CD15

CB1 = CD02 + CD03 + CD06 + CD07 + CD10 + CD11 + CD14 + CD15

CB2 = CD04 + CD05 + CD06 + CD07 + CD08 + CD09 + CD10 + CD12 + CD15

CB3 = CD00 + CD01 + CD02 + CD03 + CD04 + CD05 + CD06 + CD07 + CD08

CB4 = CD00 + CD01 + CD02 + CD04 + CD07 + CD12 + CD13 + CD14 + CD15

CB5 = CD00 + CD08 + CD09 + CD10 + CD11 + CD12 + CD13 + CD14 + CD15

#### Syndrome Decode

|          |                                     | Error Bit |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |       |

|----------|-------------------------------------|-----------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|-------|

| Syndrome | Memory Bus Data (MD) Check Bit (CB) |           |    |    |    |    |    |    |    |    | No |    |    |    |    |    |   |   |   |   |   |   |       |

| (STCB)   | 00                                  | 01        | 02 | 03 | 04 | 05 | 06 | 07 | 08 | 09 | 10 | 11 | 12 | 13 | 14 | 15 | 0 | 1 | 2 | 3 | 4 | 5 | Error |

| 0        | 0                                   | 1         | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 1 | 0 | 0 | 0 | 0 | 0 | 0     |

| 1        | 0                                   | 0         | 1  | 1  | 0  | 0  | 1  | 1  | 0  | 0  | 1  | 1  | 0  | 0  | 1  | 1  | 0 | 1 | 0 | 0 | 0 | 0 | 0     |

| 2        | 0                                   | 0         | 0  | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 1  | 0  | 0  | 1  | 0 | 0 | 1 | 0 | 0 | 0 | 0     |

| 3        | 1                                   | 1         | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 1 | 0 | 0 | 0     |

| 4        | 1                                   | 1         | 1  | 0  | 1  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 1  | 1  | 1  | 1  | 0 | 0 | 0 | 0 | 1 | 0 | 0     |

| 5        | 1                                   | 0         | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 0 | 0 | 0 | 0 | 0 | 1 | 0     |

#### **Error Detection and Correction**

| ERR | MERR | Message            | Detect | Correct |

|-----|------|--------------------|--------|---------|

| н   | н    | No Error           |        | -       |

| L   | н    | Single Bit Error   | Yes    | Yes     |

| L   | L    | Multiple Bit Error | Yes    | No      |

#### **Error Flag Control**

| ERREN | ECCTH | PWC0 | PWC1 | ERR<br>MERR |  |  |

|-------|-------|------|------|-------------|--|--|

| 0     | x     | х    | x    |             |  |  |

| х     | 0     | x    | x    | disable     |  |  |

| 1     | 1     | 0    | 0    |             |  |  |

|       |       | 0    | 1    |             |  |  |

| 1     | 1     | 1    | 0    | enable      |  |  |

|       |       | 1    | 1    |             |  |  |

#### Parity Error Flag Control

| BSCNT | PWC0 | PWC1 | PERR0  | PERR1  | PERR   |

|-------|------|------|--------|--------|--------|

|       | Н    | Н    | Н      | н      | н      |

| н     | L    | н    | enable | н      |        |

| П     | Н    | L    | н      | anakia | enable |

|       | L    | L    | enable | enable |        |

| L     | x    | x    | н      | н      | н      |

H: Disable state

## **ABSOLUTE MAXIMUM RATINGS**

| Parameter             | Symbol           | Rating      | Unit |  |

|-----------------------|------------------|-------------|------|--|

| Power Supply Voltage  | V <sub>CC</sub>  | 7.0         | v    |  |

| Input Voltage         | Vi               | -0.5 to 5.5 | v    |  |

| Output Voltage        | Vo               | -0.5 to 5.5 | v    |  |

| Operating Temperature | T <sub>OP</sub>  | -25 to 85   | °C   |  |

| Storage Temperature   | T <sub>STG</sub> | -55 to 125  | °C   |  |

#### Note:

Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to the conditions as detailed in the operational specifications of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **DC CHARACTERISTICS**

(Recommended Operating Conditions unless otherwise noted.)

|                                 |                                 |                  | Value |     |      |      |                                                    |  |

|---------------------------------|---------------------------------|------------------|-------|-----|------|------|----------------------------------------------------|--|

| Parameter                       |                                 | Symbol           | Min   | Тур | Max  | Unit | Conditions                                         |  |

| Supply Current                  | Supply Current                  |                  |       | 240 | 400  | mA   | V <sub>CC</sub> = 5.5V                             |  |

| hand have Quarter               | Except for PWC0,<br>PWC1, ECCTH | -200             |       |     |      |      |                                                    |  |

| Input Low Current               | PWC0, PWC1,<br>ECCTH            | կլ               |       |     | -400 | μA   | V <sub>CC</sub> = 5.5V, V <sub>IN</sub> = 0.5V     |  |

|                                 |                                 | Чнт              |       |     | 20   |      | V <sub>CC</sub> = 5.5V, V <sub>IN</sub> = 2.4V     |  |

| Input High Current              |                                 | I <sub>IH2</sub> |       |     | 100  | μA   | V <sub>CC</sub> = 5.5V, V <sub>IN</sub> = 5.5V     |  |

| Input Clamp Voltage             |                                 | V <sub>IC</sub>  |       |     | -1.5 | v    | V <sub>CC</sub> = 4.5V, I <sub>I</sub> = -18mA     |  |

| Output Low Voltage              |                                 | V <sub>OL</sub>  |       |     | 0.5  | v    | V <sub>CC</sub> = 4.5V, I <sub>OL</sub> = 10mA     |  |

| Output High Voltage             |                                 | V <sub>OH</sub>  | 2.4   |     |      | v    | V <sub>CC</sub> = 4.5V, I <sub>OH</sub> = -3.3mA   |  |

| Output Leakage Current (High-Z) |                                 | l <sub>oz</sub>  | -100  |     | 100  | μA   | V <sub>CC</sub> = 5.5V, V <sub>I</sub> = 0.5V/2.4V |  |

| Output Short Circuit Current    |                                 | los              |       | -60 |      | mA   | $V_{\rm CC}$ = 5.5V, $V_{\rm O}$ = 0V              |  |

| Input Low Voltage               | Input Low Voltage               |                  |       |     | 0.8  | V    |                                                    |  |

| Input High Voltage              |                                 | VIH              | 2.0   |     |      | v    |                                                    |  |

## **RECOMMENDED OPERATING CONDITIONS**

|                     |                 | Value |     |      |      |

|---------------------|-----------------|-------|-----|------|------|

| Parameter           | Symbol          | Min   | Тур | Max  | Unit |

| Supply Voltage      | V <sub>CC</sub> | 4.5   | 5.0 | 5.5  | ν    |

| Output High Current | I <sub>ОН</sub> |       |     | -3.3 | mA   |

| Output Low Current  | I <sub>OL</sub> |       |     | 10   | mA   |

| Ambient Temperature | T <sub>A</sub>  | 0     |     | 70   | °C   |

## AC CHARACTERISTICS (continued)

(Recommended operating conditions and AC test conditions unless otherwise noted.)

|                                            |                                 | Value   |    |     |      |

|--------------------------------------------|---------------------------------|---------|----|-----|------|

| Parameter                                  | Symbol                          | Min Typ |    | Max | Unit |

| Delay Time from RCLK to CD, P0, P1         | t <sub>CKCD</sub>               |         | 35 | 57  | ns   |

| Delay Time from RCLK to ERR                | t <sub>CKER</sub>               |         | 22 | 37  | ns   |

| Delay Time from RCLK to MERR               | t <sub>CKMER</sub>              |         | 25 | 42  | ns   |

| Delay Time from ERREN to ERR, MERR         | t <sub>EREN</sub>               |         | 11 | 21  | ns   |

| MD Set Up Time referenced to RCLK          | t <sub>MDCKS</sub>              | 15      |    |     | ns   |

| MD Hold Time referenced to RCLK            | t <sub>MDCKH</sub>              | 10      |    |     | ns   |

| CB Set Up Time referenced to RCLK          | t <sub>CBCKS</sub>              | 15      |    |     | ns   |

| CB Hold Time referenced to RCLK            | t <sub>свскн</sub>              | 10      |    |     | ns   |

| Disable Time of MD from PWC0/PWC1          | t <sub>MDZD</sub>               |         | 15 | 26  | ns   |

| Disable Time of CB from PWC0/PWC1          | t <sub>CBZD</sub>               |         | 15 | 26  | ns   |

| Enable Time of CD, P0, P1 from PWC0/PWC1   | t <sub>CDZE</sub>               |         | 22 | 36  | ns   |

| Delay Time from CD to MD                   | t <sub>CDMD</sub>               |         | 16 | 27  | ns   |

| Delay Time from CD to CB                   | t <sub>CDCB</sub>               |         | 21 | 34  | ns   |

| Delay Time from CD to PERR0/PERR1          | t <sub>CDPEN</sub>              |         | 22 | 35  | ns   |

| Delay Time from CD to PERR                 | t <sub>CDPER</sub>              |         | 23 | 38  | ns   |

| Delay Time from P0/P1 to PERR0/PERR1       | t <sub>PPEN</sub>               |         | 12 | 22  | ns   |

| Delay Time from P0/P1 to PERR              | t <sub>PPER</sub>               |         | 14 | 26  | ns   |

| Enable Time of MD from PWC0/PWC1           | t <sub>MDZE</sub>               |         | 20 | 32  | ns   |

| Enable Time of CD from PWC0/PWC1           | t <sub>CBZE</sub>               |         | 20 | 32  | ns   |

| Disable Time of CD, P0, P1 from PWC0/PWC1  | t <sub>CDZD</sub>               |         | 15 | 26  | ns   |

| Delay Time from PWC0/PWC1 to PERR0, PERR1  | t <sub>PWPEN</sub>              |         | 10 | 18  | ns   |

| Delay Time from PWC0/PWC1 to PERR          | t <sub>PWPER</sub>              |         | 12 | 22  | ns   |

| Enable Time of MD from BSCNT               | t <sub>BCMDZE</sub>             |         | 20 | 35  | ns   |

| Delay Time from SLE to STCB                | t <sub>SLEST</sub> 1            |         | 23 | 37  | ns   |

| Enable Time of STCB from EN                | t <sub>STZE</sub> 1             |         | 15 | 24  | ns   |

| RCLK Set Up Time referenced to SLE         | t <sub>SSL</sub> 1              | 44      |    |     | ns   |

| Delay Time from MD to CD                   | t <sub>MDCDTH<sup>2</sup></sub> |         | 21 | 34  | ns   |

| Delay Time from MD to P0, P1               | t <sub>MDPTH</sub> <sup>2</sup> |         | 28 | 48  | ns   |

| Delay Time from CB to STCB                 | t <sub>CBSTTH</sub> 2           |         | 18 | 30  | ns   |

| RCLK Set Up Time referenced to PWC0, PWC1  | t <sub>CKS</sub> <sup>3</sup>   | 57      |    |     | ns   |

| PWC0, PWC1 Set Up Time referenced to BSCNT | t <sub>SBC</sub> <sup>3</sup>   | 10      |    |     | ns   |

| Delay Time from PWC0/PWC1 to CD            | t <sub>SCD</sub> 3              |         | 15 | 26  | ns   |

3

#### AC CHARACTERISTICS (continued)

(Recommended operating conditions and AC test conditions unless otherwise noted.)

|                  |        | Value |     |     |      |

|------------------|--------|-------|-----|-----|------|

| Parameter        | Symbol | Min   | Тур | Max | Unit |

| RCLK Pulse Width | twck   | 20    |     |     | ns   |

| RST Pulse Width  | twrst  | 20    |     |     | ns   |

| SLE Pulse Width  | WSLE   | 20    |     |     | ns   |

#### Notes:

1. Syndrome Latch

2. ECC-Through Mode 3. Partial Write Mode

#### 3. Partial Write Mode

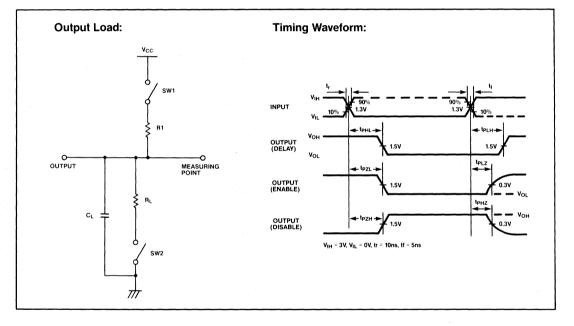

#### AC TEST CONDITONS

| Parameter    | Symbol                               | RL(Ω) | R1(Ω)     | CL(pF) | SW1       | SW2      |

|--------------|--------------------------------------|-------|-----------|--------|-----------|----------|

| Delay Time   | t <sub>PLH</sub><br>t <sub>PHL</sub> | 1.0K  | · · · · · | 50     | Off       | On       |

| Enable Time  | t <sub>PLZ</sub><br>t <sub>PHZ</sub> | 1.0K  | 0.5K      | 5      | On<br>Off | On<br>On |

| Disable Time | t <sub>PZL</sub><br>t <sub>PZH</sub> | 1.0K  | 0.5K      | 50     | On<br>Off | On<br>On |

TIMING DIAGRAMS Read Mode

3

## TIMING DIAGRAMS (continued) Write Mode (Word Write)

#### TIMING DIAGRAMS (continued) Partial Write Mode (Byte Write)

## Syndrome Latch

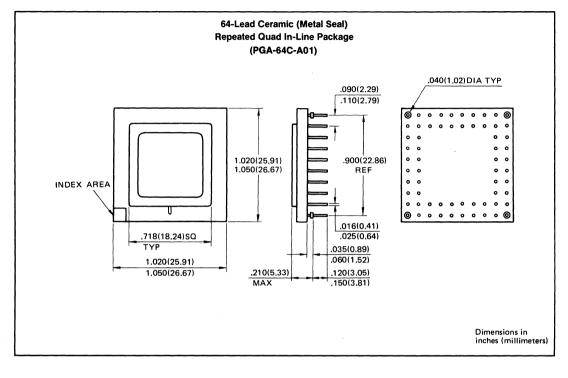

#### PACKAGE DIMENSIONS

3