The MB15A03 is a Phase Locked Loop (PLL) frequency synthesizer LSI operating at up to 1.1 GHz. It incorporates a dual-modulus prescaler allowing either a 64/65 or a 128/129 frequency division to be selected.

The MB15A03 has a built-in power save function, achieving low power consumption.

The MB15A03 design is ideal for analog mobile telecommunications equipment.

## ■ FEATURES

- Operation at high speed: Up to 1.1 GHz

- Operation at low voltage: 2.7 to 3.6 V

- Low current consumption: Typical 6.5 mA (Vcc = 3 V)

- Built-in power saving function: Typical 100  $\mu$ A (Vcc = 3V)

- Dual-modulus prescaler divide ratio: 64/65 or 128/129

- · Reference divider

- Binary 14-bit reference counter (divide ratio of 6 to 16,383)

- Comparative dividers

- Binary 7-bit swallow counter (divide ratio of 0 to 127)

- Binary 11-bit programmable counter (divide ratio of 5 to 2,047)

- Internal phase comparator with phase conversion features

- Internal digital lock detection circuit for PLL lock/unlock detection

- Operating temperature range: –40 to +85°C

### ■ PACKAGES

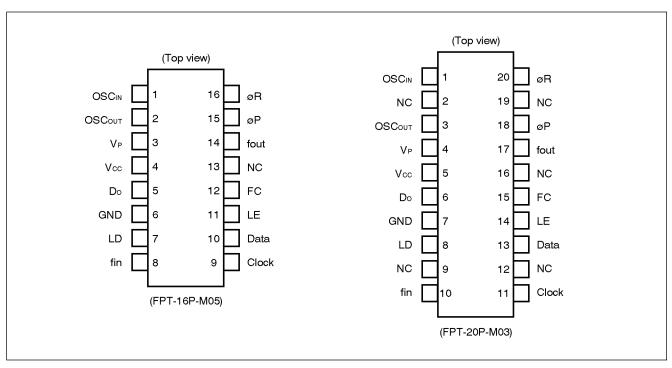

# **■ PIN ASSIGNMENTS**

# **■ PIN DESCRIPTIONS**

| Pin No. |                     |        |     |                                                                                                                                                                                                                                                                                       |

|---------|---------------------|--------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SSOP-16 | SSOP-20             | Symbol | I/O | Function                                                                                                                                                                                                                                                                              |

| 1       | 1                   | OSCIN  | ı   | Crystal oscillator connection pin serving as a reference divider input pin (oscillator circuit input pin).                                                                                                                                                                            |

| 2       | 3                   | ОSСоит | 0   | Crystal oscillator connection pin (oscillator circuit output pin).                                                                                                                                                                                                                    |

| 3       | 4                   | VP     | _   | Power supply pin for charge pump output.                                                                                                                                                                                                                                              |

| 4       | 5                   | Vcc    | _   | Power supply pin.                                                                                                                                                                                                                                                                     |

| 5       | 6                   | Do     | 0   | Internal charge pump output pin. The phase characteristic is inverted according to the FC pin setting.                                                                                                                                                                                |

| 6       | 7                   | GND    | _   | GND pin                                                                                                                                                                                                                                                                               |

| 7       | 8                   | LD     | 0   | Lock detector output pin.<br>When locked: LD = "H"; when unlocked: LD = "L".                                                                                                                                                                                                          |

| 8       | 10                  | fin    | I   | Prescaler input pin. The pin must be AC-coupled for input.                                                                                                                                                                                                                            |

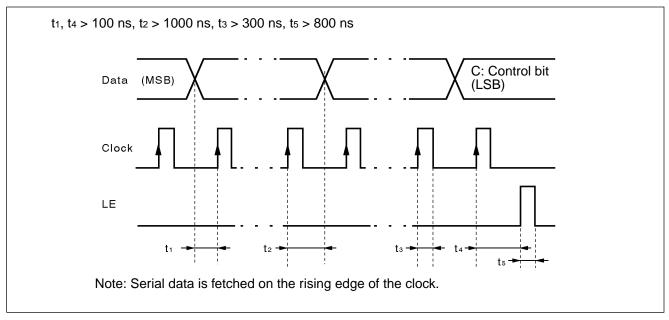

| 9       | 11                  | Clock  | I   | Clock input pin for 19-bit shift registers. The shift register reads data at the rise of the clock pulse.                                                                                                                                                                             |

| 10      | 13                  | Data   | I   | Binary-coded serial data input pin. The last bit in the data is a control bit. Control bit = "H": Sends data to the 16-bit latch. "L": Sends data to the 18-bit latch.                                                                                                                |

| 11      | 14                  | LE     | I   | Load enable signal input pin. When LE = "H", the pin sends the contents of the shift register to the latch according to the control bit.                                                                                                                                              |

| 12      | 15                  | FC     | I   | Phase comparator phase switching pin. When FC = "L", the pin inverts the characteristics of the charge pump and the phase comparator. The pin also switches the fout pin (test pin) output between fr and fp.                                                                         |

| 14      | 17                  | fout   | 0   | Phase comparator input monitor pin. The pin outputs the reference divider output (fr) or programmable divider output (fp) signal according to the FC pin input level. FC = "H": Equivalent to fr output FC = "L": Equivalent to fp output This pin is an N-channel open-drain output. |

| 15      | 18                  | øΡ     | 0   | Phase comparator output pin for external charge pump. The phase characteristic is inverted according to the FC pin setting. This pin is an N-channel open-drain output.                                                                                                               |

| 16      | 20                  | øR     | 0   | Phase comparator output pin for external charge pump. The phase characteristic is inverted according to the FC pin setting. This pin is a CMOS output.                                                                                                                                |

| 13      | 2, 9, 12,<br>16, 19 | N.C.   | _   | No connection                                                                                                                                                                                                                                                                         |

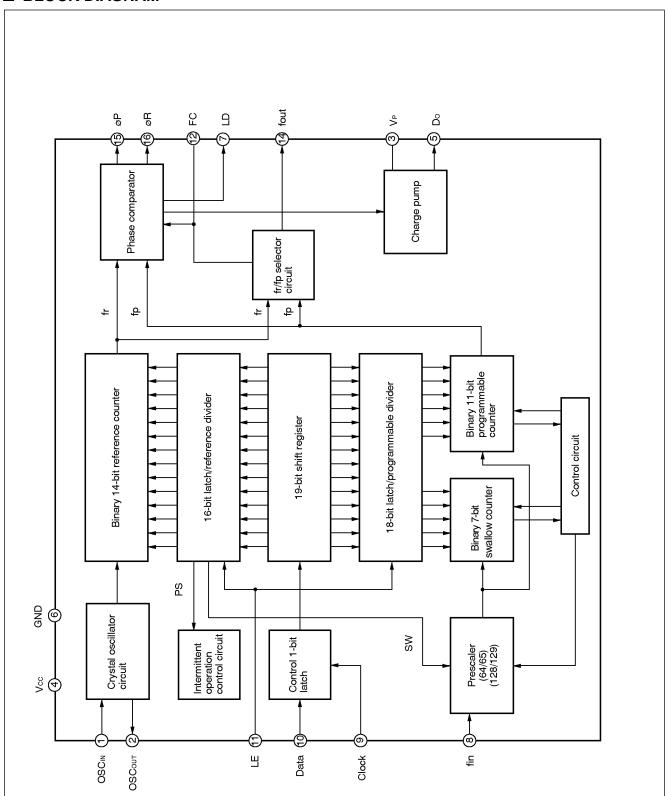

# **■ BLOCK DIAGRAM**

#### ■ ABSOLUTE MAXIMUM RATINGS

| Parameter            | Symbol | Rat         | Unit      |       |

|----------------------|--------|-------------|-----------|-------|

| Farameter            | Symbol | Min.        | Max.      | Offic |

| Power supply voltage | Vcc    | -0.5        | 5.0       | V     |

| Power supply voltage | VP     | Vcc         | 5.5       | V     |

| Output voltage       | Vo     | -0.5        | Vcc + 0.5 | V     |

| Output current       | lo     | -10         | 10        | mA    |

| Open-drain voltage   | Voop   | -0.5        | 6.0       | V     |

| Storage temperature  | Tstg   | <b>-</b> 55 | +125      | °C    |

Note: Permanent device damage may occur if the above **Absolute Maximum Ratings** are exceeded. Functional operation should be restricted to the conditions detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### ■ RECOMMENDED OPERATING CONDITIONS

| Parameter             | Symbol |      | Unit |      |       |  |

|-----------------------|--------|------|------|------|-------|--|

| Farameter             | Symbol | Min. | Тур. | Max. | Offic |  |

| Dower cumply veltage  | Vcc    | 2.7  | 3.0  | 3.6  | V     |  |

| Power supply voltage  | VP     | Vcc  | _    | 5.0  | V     |  |

| Input voltage         | Vin    | GND  | _    | Vcc  | V     |  |

| Operating temperature | Та     | -40  | _    | +85  | °C    |  |

#### HANDLING PRECAUTIONS

Although the MB15A03 contains an antistatic element to prevent electrostatic breakdown and the circuitry has been improved in electrostatic protection, observe the following precautions when handling the device:

- Store or carry this device in a conductive case.

- As this is a static-sensitive device, take proper anti-ESD precautions. Ensure that personnel and equipment are properly grounded. Cover workbenches with grounded conductive mats.

- Always turn the power supply off before inserting or removing the device from its socket.

- Protect leads with a conductive sheet when handling or transporting PC boads with devices.

## **■ ELECTRICAL CHARACTERISTICS**

$(Vcc = 2.7 V to 3.6 V, Ta = -40^{\circ}C to +85^{\circ}C)$

| Parame                        | tor          | Symbol             | Condition     | VCC = 2.7 V | Value |         | Unit             |  |

|-------------------------------|--------------|--------------------|---------------|-------------|-------|---------|------------------|--|

| r dramotor                    |              | Symbol             | Condition     | Min.        | Тур.  | Max.    | 0                |  |

| Power supply current          | *1           | Icc                | _             | _           | 6.5   | _       | mA               |  |

| Power saving current          |              | <b>I</b> PS        | _             | _           | 100   | _       | μΑ               |  |

| Operating frequency           | fin*2        | fin                | _             | 300         | _     | 1100    | MHz              |  |

| Operating frequency           | OSCIN        | fosc               | _             | _           | 12    | 20      | MHz              |  |

| Input sensitivity             | fin          | Pfin               | 50 Ω system   | -10         | _     | 6       | dBm              |  |

| input sensitivity             | OSCIN        | Vosc               | _             | 0.5         | _     | _       | V <sub>P-P</sub> |  |

| High-level input voltage      | Data, Clock, | Vıн                | _             | 0.7 × Vcc   | _     | _       | V                |  |

| Low-level input voltage       | LE, FC       | VıL                | _             | _           | _     | 0.3×Vcc | V                |  |

| High-level input current      | Clock, Data  | Іін                | _             | _           | _     | 1.0     | μΑ               |  |

| Low-level input current       | Clock, Data  | <b>I</b> IL*3      | _             | -1.0        | _     | _       | μΑ               |  |

| Input current                 | OSCIN        | losc*3             | _             | _           | ±50   | _       | μΑ               |  |

| High-level output voltage     | Excluding Do | Vон*4              | _             | 2.1         | _     | _       | V                |  |

| Low-level output voltage      | and OSCout   | Vo <sub>L</sub> *5 | _             | _           | _     | 0.4     | V                |  |

| High impedance cutoff current | Do, fout, øP | OFF*6              | _             | _           | _     | 1.1     | μΑ               |  |

| Output currrent               | Excluding Do | <b>І</b> он*3      | Vcc = 3.0 V   | -1.0        | _     | _       | mA               |  |

| Output cument                 | and OSCout   | Іоь                | 7 VCC = 3.0 V | _           |       | 1.0     | mA               |  |

<sup>\*1:</sup> Assuming the PLL lock conditions: fin = 1.1 GHz, fosc = 12 MHz, Vcc = 3.0 V

<sup>\*2:</sup> The fin pin must be AC-coupled. The minimum operating frequency assumes coupling at 1000 pF.

<sup>\*3:</sup> A minus sign (–) indicates the direction of the signal flowing from the IC.

<sup>\*4:</sup> Assuming Vcc = 3.0 V and IoH = -1 mA

<sup>\*5:</sup> Assuming Vcc = 3.0 V and IoL = 1 mA

<sup>\*6:</sup> Vcc = 3.6 V, Vp = Vcc to 5.0 V, Voop = GND to 6.0 V

#### **■ FUNCTIONAL DESCRIPTIONS**

#### 1. Pulse Swallow Function

For the pulse swallow function, select the respective setting values using the following equation:

$$f_{VCO} = [(P \times N) + A] \times f_{OSC} \div R$$

fvco : Output frequency of external VCO P : Divide ratio of prescaler (64 or 128)

N : Divide ratio of 11-bit programmable counter (5 to 2047)

A : Divide ratio of 7-bit swallow counter (0 to 127, where A < N)

fosc : Reference oscillation frequency (OSC<sub>IN</sub> input frequency)

R : Divide ratio of 14-bit programmable reference counter (6 to 16383)

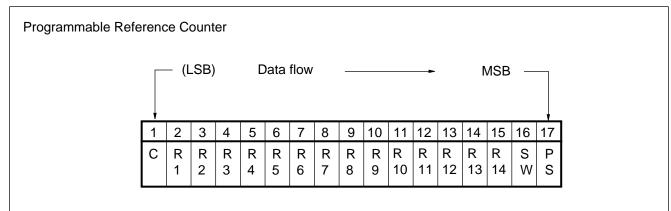

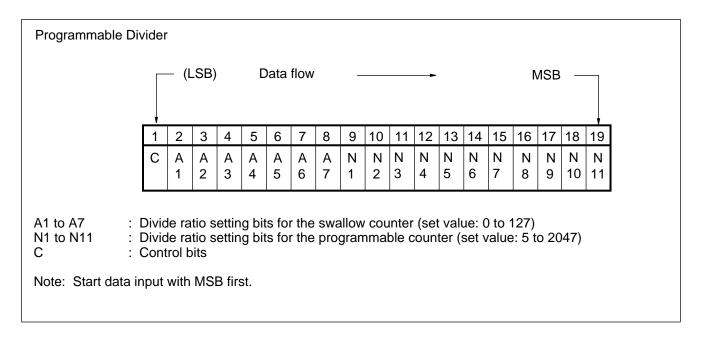

#### 2. Serial Data Input Method

Serial data is processed using three input pins (Data, Clock, and LE) to control the 16-bit reference divider and the 18-bit programmable divider separately.

Binary serial data is entered through the Data pin.

Serial data is transferred to the internal shift register in sequence on the rising edge of each clock. When the load enable signal is high, the input data is transferred to the latch according to the control bit.

Control bit = "H"  $\rightarrow$  Transfer to the 16-bit latch Control bit = "L"  $\rightarrow$  Transfer to the 18-bit latch

#### (1) Serial Data Format

R1 to R4 : Divide ratio setting bits for the programmable reference counter (6 to 16,383)

SW : Divide ratio setting bits for the prescaler

PS : Power saving control bit

C : Control bits

Note: Start data input with MSB first.

#### (2) Data Settings

• Binary 14-bit reference counter (R1 to R14)

| Divide ratio | R<br>14 | R<br>13 | R<br>12 | R<br>11 | R<br>10 | R<br>9 | R<br>8 | R<br>7 | R<br>6 | R<br>5 | R<br>4 | R<br>3 | R<br>2 | R<br>1 |

|--------------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| 6            | 0       | 0       | 0       | 0       | 0       | 0      | 0      | 0      | 0      | 0      | 0      | 1      | 1      | 0      |

| 7<br>•       | 0       | 0       | 0       | 0       | 0       | 0      | 0      | 0      | 0      | 0      | 0      | 1      | 1      | 1      |

| 16383        | 1       | 1       | 1       | 1       | 1       | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 1      |

Note: A divide ratio less than 6 is prohibited.

• Binary 11-bit programmable counter (N1 to N11)

| Divide ratio | N  | N  | N | N | N | N | N | N | N | N | N |

|--------------|----|----|---|---|---|---|---|---|---|---|---|

|              | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 |

| 5            | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 |

| 6            | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

| 2047         | •  | •  | • | • | • | • | • | • | • | • | • |

|              | •  | •  | • | • | • | • | • | • | • | • | • |

|              | 1  | 1  | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

Note: A divide ratio less than 5 is prohibited.

# • Binary 7-bit swallow counter (A1 to A7)

| Divide ratio       | A<br>7 | A<br>6 | A<br>5 | A<br>4 | A<br>3 | A<br>2 | <b>A</b> 1 |

|--------------------|--------|--------|--------|--------|--------|--------|------------|

| 0                  | 0      | 0      | 0      | 0      | 0      | 0      | 0          |

| 1<br>•<br>•<br>127 | 0 •    | 0 •    | 0 •    | 0 •    | 0 •    | 0 •    | 1 •        |

#### • Prescaler (SW)

| Divide ratio | SW |

|--------------|----|

| 64/65        | 1  |

| 128/129      | 0  |

#### • Power saving (intermittent operation) control (PS)

| Mode              | PS |

|-------------------|----|

| Normal mode       | 1  |

| Power saving mode | 0  |

Note: Be sure to reset the PS bit to 0 immediately after turning the power on.

Users can operate internal circuits only when required and halt them when not required. This process reduces the overall circuit power consumption (intermittent operation).

However, letting the LSI simply start operating the halted circuit results in excessive error signal output from the phase comparator unlocking the PLL. This is because the reference frequency (fr) and comparative frequency (fp) inputs to the phase comparator have an undefined phase relationship even when the two frequencies are the same.

To solve this problem, the MB15A03 provides intermittent operation control to suppress variation in the locked frequency by forcibly aligning the phases when the circuit returns from the halted state.

#### (3) Serial Data Input Timing

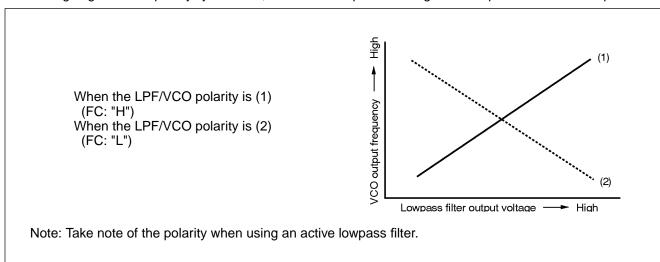

#### 3. Relationships between FC Pin Inputs and Phase Characteristics

The FC pin is the phase switching pin for the phase comparator. Controlling the FC pin input allows the characteristics of the internal charge pump output (Do) and external charge pump outputs (ØR and ØP) to be selected. Also, the phase comparator input monitor pin (fout) is controlled through the FC pin.

The following table shows the relationship between FC pin inputs and Do, ØR, ØP, and fout:

| Phase comparator input |    | FC: | "H" |      | FC: "L" |    |    |      |  |

|------------------------|----|-----|-----|------|---------|----|----|------|--|

| Phase comparator input | Do | øR  | øΡ  | fout | Do      | øR | øΡ | fout |  |

| fp < fr                | Н  | L   | L   |      | L       | Н  | Z  |      |  |

| fr < fp                | L  | Н   | Z   | fr   | Н       | L  | L  | fp   |  |

| fp = fr                | Z  | L   | Z   |      | Z       | L  | Z  |      |  |

#### Z: High impedance

When designing a PLL frequency synthesizer, control the FC pin according to the lowpass filter and VCO polarities.

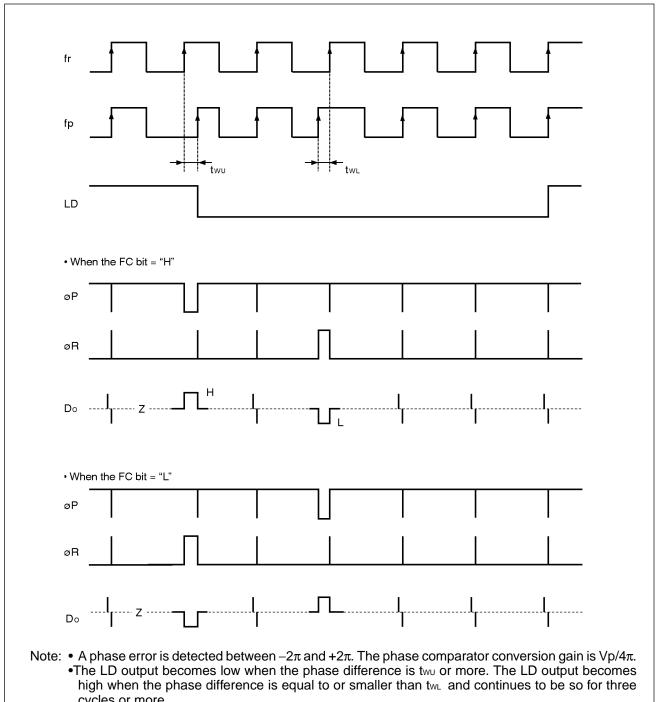

#### **■ PHASE COMPARATOR OUTPUT WAVEFORMS**

- cycles or more.

- •two and two depend on the OCSIN input frequency as follows:  $twu \ge 8/fosc [s] \dots$  When fosc = 12.8 MHz,  $twu \ge 625$  ns  $t_{WL} \le 16/f_{OSC}$  [s] ..... When  $f_{OSC} = 12.8$  MHz,  $t_{WL} \le 1250$  ns

# **■ TYPICAL CHARACTERISTIC CURVES**

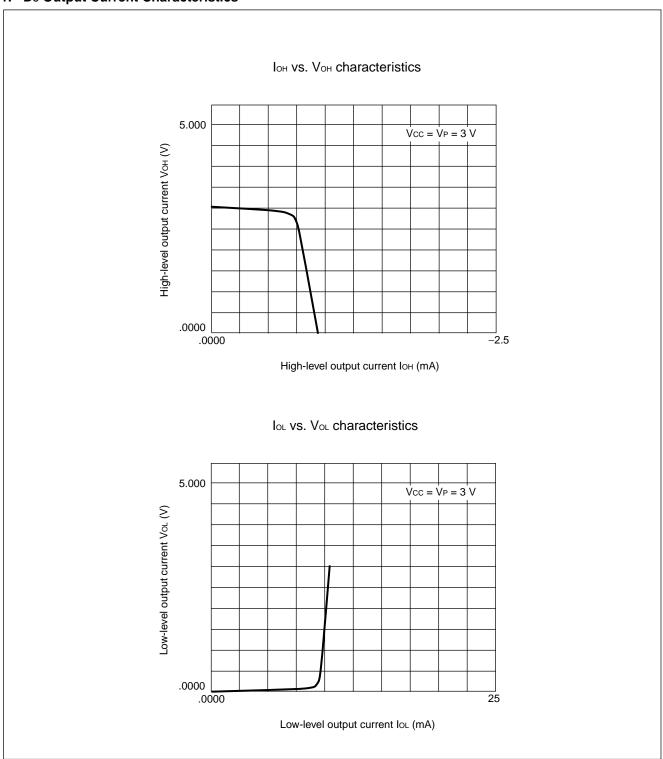

## 1. Do Output Current Characteristics

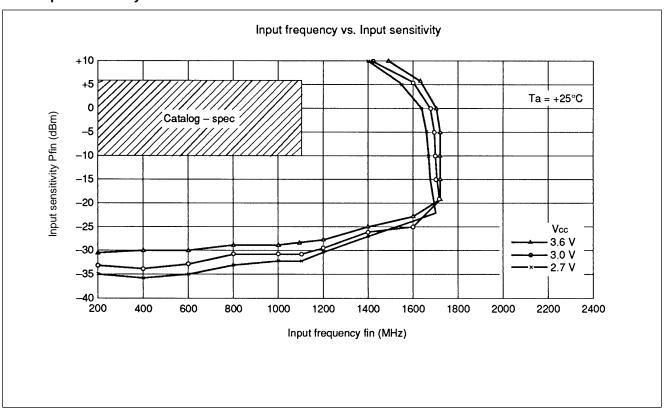

# 2. fin Input Sensitivity Characteristics

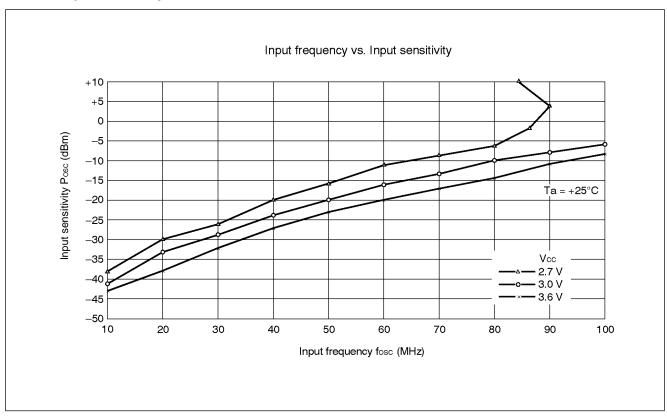

## 3. OSCIN Input Sensitivity Characteristics

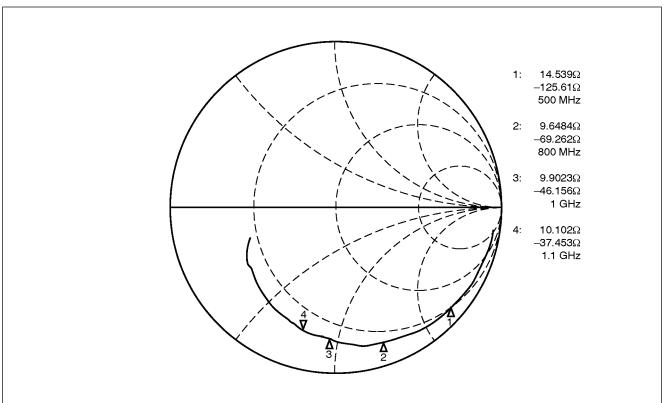

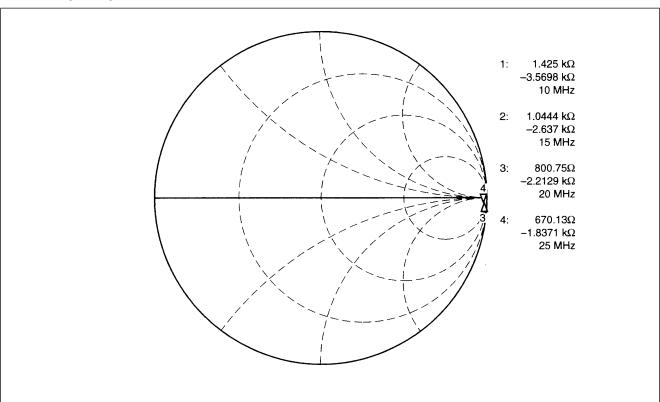

# 4. fin Input Impedance Characteristics

## 5. OSC<sub>IN</sub> Input Impedance Characteristics

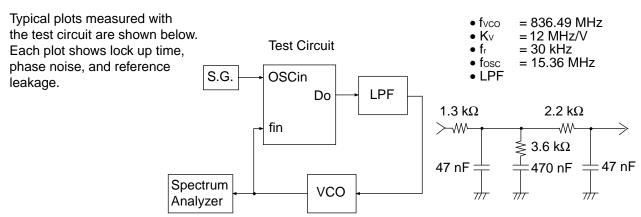

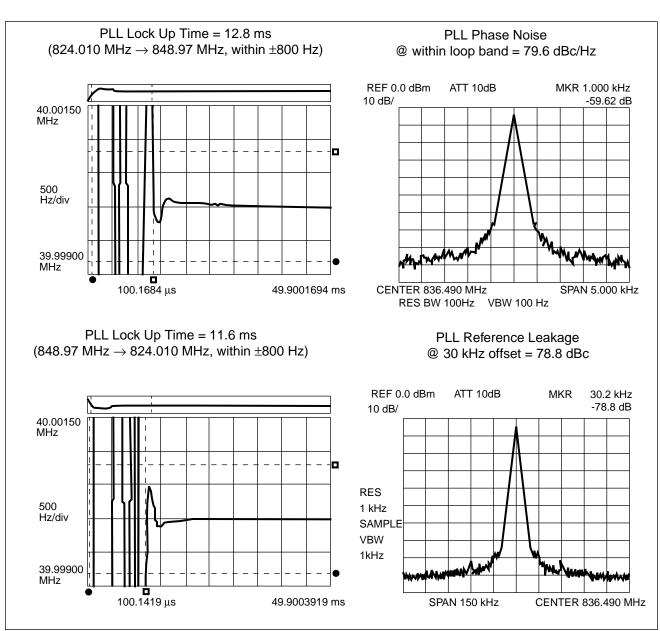

#### **■ REFERENCE INFORMATION**

# ■ TEST CIRCUIT EXAMPLE (fin/OSC<sub>IN</sub> Input Sensitivity Measurement)

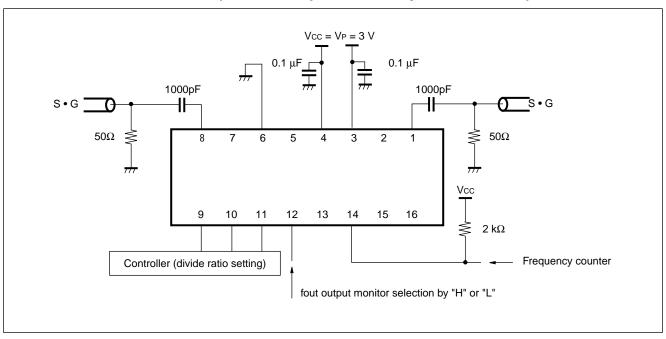

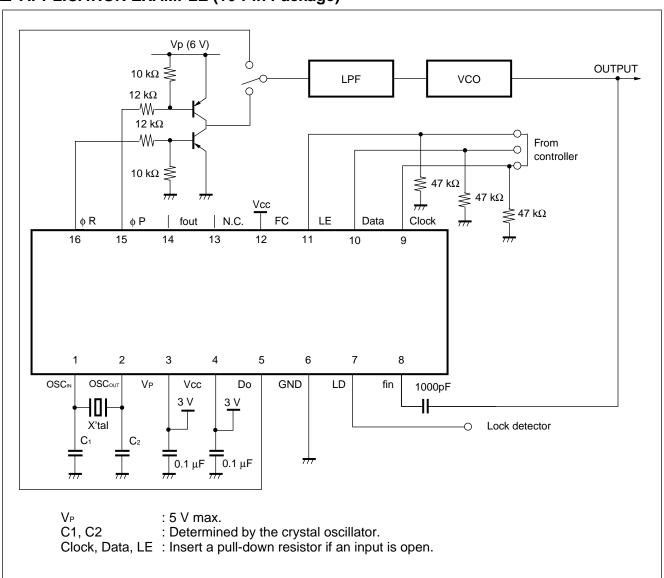

# ■ APPLICATION EXAMPLE (16-Pin Package)

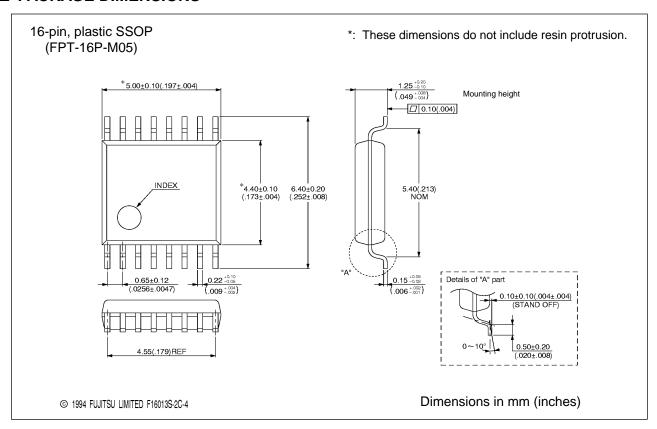

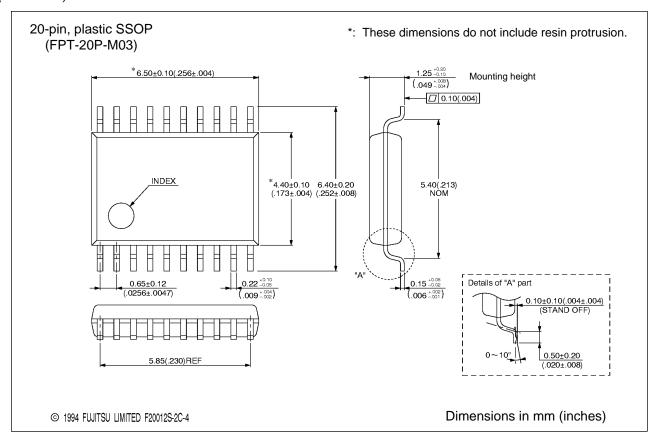

# **■** ORDERING INFORMATION

| Part number | Package                               | Remarks |

|-------------|---------------------------------------|---------|

| MB15A03PFV1 | 16-pin, plastic SSOP<br>(FPT-16P-M05) |         |

| MB15A03PFV2 | 20-pin, plastic SSOP<br>(FPT-20P-M03) |         |

#### **■ PACKAGE DIMENSIONS**

(Continued)

(Continued)

All Rights Reserved.

Circuit diagrams using Fujitsu products are included to illustrate typical semiconductor applications. Information sufficient for construction purposes may not be shown.

The information contained in this document has been carefully checked and is believed to be reliable. However, Fujitsu Microelectronics, Inc. assumes no responsibility for inaccuracies.

The information contained in this document does not convey any license under the copyrights, patent rights, or trademarks claimed and owned by Fujitsu Limited, its subsidiaries, or Fujitsu Microelectronics, Inc.

Fujitsu Microelectronics, Inc. reserves the right to change products or specifications without notice.

No part of the publication may be copied or reproduced in any form or by any means, or transferred to any third party without prior written consent of Fujitsu Microelectronics, Inc.

MB15A03

Visit our web site for the latest information:

# http://www.fujitsumicro.com

### **Customer Response Center:**

For semiconductor products, flat panel displays, and PC cards in the U.S., Canada, and Mexico, please contact the Fujitsu Microelectronics Customer Response Center (CRC). The CRC provides a single point of contact for resolving customer issues and answering technical questions.

**Web:** Click on Tech Support in the FMI home page, then submit our form.

**Tel:** Telephone: 1-800-866-8608 Monday through Friday, 7 to 5 PST.

Outside U.S., Canada, and Mexico, call: 010-1-408-922-9000 and ask for the Customer Response Center. (*Note: Country code may vary.*)

**Fax:** (408) 922-9179

**E-Mail:** fmicrc@fmi.fujitsu.com

CP-TC-DS-20293-7/96