# ETHERNET ENCODER / DECODER

# **MB 502A**

October 1983 Edition 2.0

#### ETHERNET ENCODER/DECODER

The Fujitsu MB 502A is an Ethernet\* Encoder/Decoder designed to meet all the requirements of the Ethernet Blue Book specification and fabricated with high-speed ECL and Schottky TTL technology.

The encoder converts serial binary data into complementary Manchester code. The decoder converts Manchester code into binary data and synchronous clock signals. The decoding method is a digital phase locked loop with dual bandwidth which allows both fast lock-on and a small amount of jitter. Typical acquisition is eight bits or better. A key feature of the decoder design is its capability to recover distorted input signals. The MB 502A is packaged in a 24-pin ceramic standard DIP.

#### **FEATURES**

- Full Ethernet compatibility

- Manchester encode and decode

- Level conversion: transceiver level to/from TTL level

- Carrier detection

- Large distortion recovery: ±20 ns

- Dual bandwidth phase locked loop: allows fast acquisition

- Loopback "CONFIDENCE" test feature

- Built-in clock generator

- Small external parts count: all passive external components

- High-speed ECL and Schottky TTL technology

- Single power supply: +5V

- Low power dissipation: 750mW typ.

- 24-pin standard Dual In-line Ceramic Package

<sup>\*</sup>Ethernet is a trade mark of Xerox Corp. U.S.A.

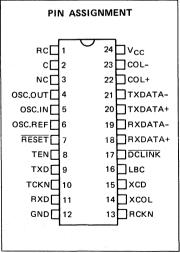

## PIN ASSIGNMENT TABLE

| Group               | Pin Number  | Symbol                          | Pin Name                                                | I/O   | Level               | Function                                                         |

|---------------------|-------------|---------------------------------|---------------------------------------------------------|-------|---------------------|------------------------------------------------------------------|

| Power               | 12          | GND                             | Power                                                   | ı     |                     | Ground                                                           |

| Group               | 24          | V <sub>cc</sub>                 | supply                                                  | ı     |                     | +5V DC power supply                                              |

|                     | 18<br>19    | RXDATA+<br>RXDATA-              | Receive<br>data pair                                    | -     | ECL<br>differential | Interfacing to receive pair of the transceiver cable.            |

| Cable<br>Group      | 20<br>21    | TXDATA+<br>TXDATA-              | Transmit<br>data pair                                   | 0     | ECL<br>differential | Interfacing to transmit pair of the transceiver cable.           |

|                     | 22<br>23    | COL+<br>COL-                    | Collision<br>presence pair                              | l     | ECL<br>differential | Interfacing to collision presence pair of the transceiver cable. |

|                     | 8           | TEN                             | Transmit<br>encode enable                               | ı     | TTL                 | Input for encoding and TXDATA± enable.                           |

|                     | 9           | TXD                             | Transmit<br>serial data                                 | ı     | TTL                 | Input for transmit data to be encoded onto the Ethernet coax.    |

|                     | . 10        | TCKN                            | Transmit<br>data clock                                  | 0     | TTL                 | Stable 10MHz clock output for transmit bit stream.               |

| EDLC                | 11          | RXD                             | Receive<br>serial data                                  | 0     | TTL                 | Output of received and decoded bit stream.                       |

| Group               | 13          | RCKN                            | Receive<br>data clock                                   | 0     | TTL                 | Clock output to strobe RXD.                                      |

|                     | 14          | XCOL                            | Collision presence                                      | 0     | TTL                 | Duplication of the collision presence pair (COL±).               |

|                     | 15          | XCD                             | Receive<br>carrier detect                               | 0     | TTL                 | Carrier detect function of the decoder.                          |

|                     | 16          | LBC                             | Loopback<br>command                                     | ı     | TTL                 | Input to command the MB502A to operate in loopback mode.         |

| Oscillator<br>Group | 4<br>5<br>6 | OSC. OUT<br>OSC. IN<br>OSC. REF | Oscillator<br>pins                                      | 0 - 0 | ECL                 | Pins for direct connection of discrete oscillator components.    |

|                     | 1<br>2      | RC<br>C                         | Capacitor<br>pins                                       | _     | ECL<br>-            | Pins for direct connection of a capacitor.                       |

|                     | 3           | NC                              | Non-connection<br>(PLL test)                            | 0     | ECL                 | Output pin for PLL testing purpose only.                         |

| Others              | 7           | RESET                           | FF test                                                 | ı     | TTL                 | Input pin to initialize flip-flops for testing purpose only.     |

|                     | 17          | DCLINK                          | DC/AC<br>coupling<br>select for<br>transceiver<br>pairs | 1     | TTL                 | Input to select DC/AC coupling of transceiver cable pairs.       |

## **FUNCTIONAL DESCRIPTION**

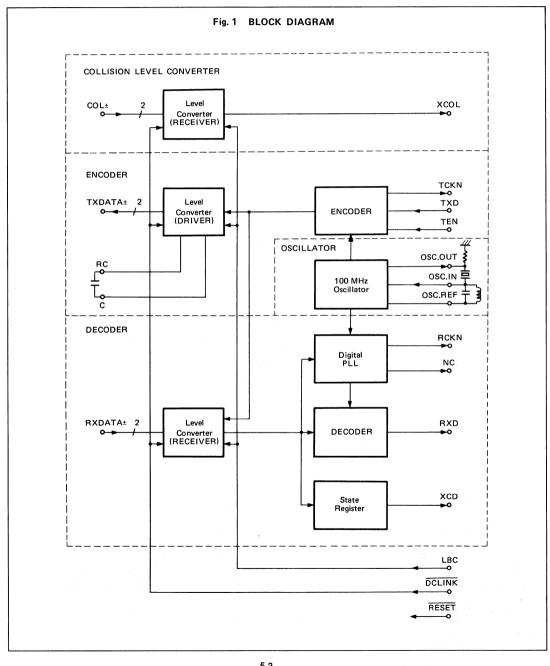

The MB 502A has five major functions; encode, decode, collision, master clock generation and loopback.

#### **ENCODE**

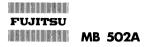

The encoder section of the MB 502A is a simple circuit which performs an appropriate exclusive-OR between the transmit clock and transmit data using latches to reduce the skew of TXDATA± outputs. The encoder sends the transmit clock (TCKN) to the Data Link controller. Then an encode enable signal (TEN) and data (TXD) are returned from the Data Link controller.

#### **DECODE**

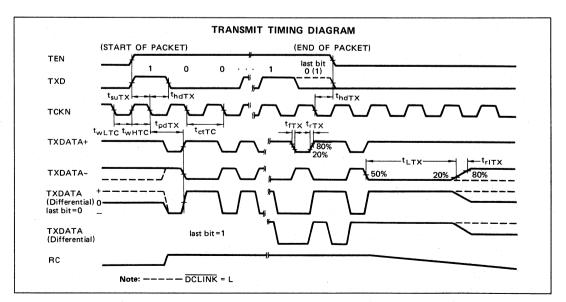

The decoder performs three functions. First, it decodes data using the differential receive inputs (RXDATA+ and RXDATA-) of the transceiver cable. Next is the carrier detect function. The carrier is derived from the receive inputs and passed to the Data Link controller from the XCD output. The last function is the stripping of the first several bits (eight bits maximum) of the packet. This is not a part of the Ethernet Physical Layer specification. The receive clock (RCKN) is actually inhibited for 6 or 7 clock cycles to allow the PLL (phase locked loop) to gain acquisition. This function was designed into the Encoder/Decoder because the EDLC (Ethernet Data Link Controller, MB 8795B) is a byte oriented device, and the function is more appropriately

#### SIGNAL PIN DESCRIPTION

#### CABLE GROUP

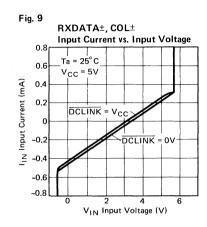

RXDATA± (receive serial data pair, inputs)

These are the inputs to the decoder. They receive Manchester coded signals which the transceiver encounters on the Ethernet coax.

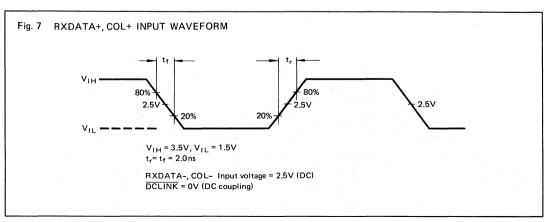

The input circuit is a differential receiver and can receive voltages of 0 to  $V_{CC}$ . The differential receiver has two operation modes; DC coupled operation and AC coupled operation, which are selected by  $\overline{\text{DCLINK}}$  input.

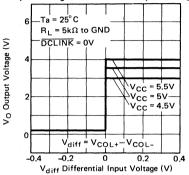

In DC coupled operation (DCLINK is low), the differential threshold is typically 0V. The differential input voltage of more than 0.2V is regarded as high level and the differential input voltage of less than -0.2V is regarded as low level.

In AC coupled operation (DCLINK is high), the differential threshold is typically -0.2V. A differential input voltage of more than -0.05V is regarded as high level and a differential input voltage of less than -0.4V is regarded as low level.

The receiver circuit is designed to supply a high level to the decoder when RXDATA+ and RXDATA- are not receiving data but are just short-circuited through a transformer coil or left unconnected. However, when RXDATA± are receiving data, the differential threshold is typically 0V to minimize receiving distortion.

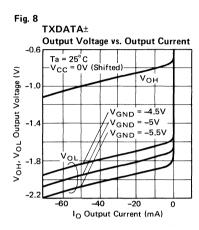

#### TXDATA± (transmit data pair, outputs)

These are the outputs of the encoder. They transmit Manchester coded signals to the transceiver.

The driver output circuit is an emitter-follower and

provided in the Encoder/Decoder which is bit oriented.

The decoder PLL has excellent distortion handling capability. It is designed to recover ± 20ns exercised.

#### COLLISION

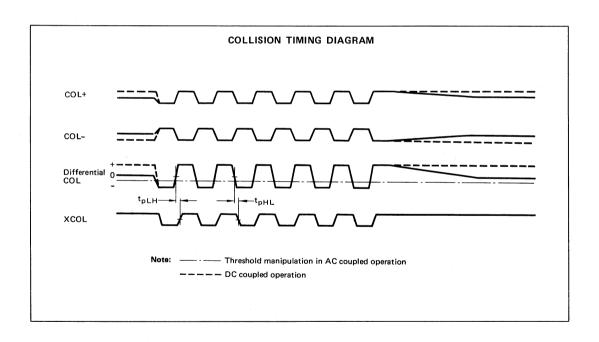

The collision detect inputs (COL+ and COL-) are simply converted to a TTL level signal (XCOL). The latching and timing functions for this signal are provided in the EDLC (MB 8795B).

#### MASTER CLOCK GENERATION

The oscillator generates and supplies a 100MHz master clock signal to the encoder and decoder.

Discrete oscillator components such as a crystal may be directly connected to the provided oscillator pins.

The oscillation frequency must be 100MHz with a tolerance of less than  $\pm 0.01\%$  to meet the Ethernet specification because one tenth of the oscillation frequency is the transmit bit rate.

## LOOPBACK

A loopback input is provided to allow all encoding and decoding functions to be exercised without using the transceiver cable. During loopback operation, the encoded data is routed internally to the decoder, the transmit outputs are idle, and the receive and collision inputs are ignored.

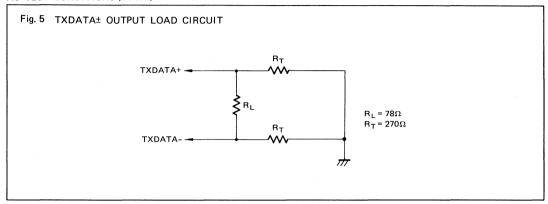

requires a pull-down resistor (270 $\Omega$  typ.). It can drive a transceiver cable differential impedance of 78 $\Omega$ .

The differential transmitter outputs (TXDATA+ and TXDATA-) also have the ability to emulate a transformer drive. This is actually implemented to reduce the current involved in a transformer termination of the transmit outputs in the transceiver which has a DC resistance of zero ohms. After the encoding function stops, the transmitter outputs gradually return to a OV differential between the two output wires. The returning time is determined by an external capacitor connected between the RC and C pins.

## COL± (collision presence pair, inputs)

This pair of signals indicates the presence of a collision generated by the transceiver.

The input circuit is a differential receiver and can receive voltages of 0V to  $V_{\rm CC}$ . The differential receiver has two operation modes; DC coupled operation and AC coupled operation, which are selected by  $\overline{\rm DCLINK}$

In DC coupled operation (DCLINK is low), the differential threshold is typically 0V. A differential input voltage of more than 0.2V is regarded as high level and a differential input voltage of less than -0.2V is regarded as low level.

In AC coupled operation (DCLINK is high), the differential threshold is typically -0.2V. A differential input voltage of more than -0.05V is regarded as high

level and a differential input voltage of less than -0.4V is regarded as low level.

The receiver circuit is designed to supply a high level to the level converter when COL+ and COL- are not receiving data but are just short-circuited through a transformer coil or left unconnected.

Unlike RXDATA±, the differential threshold is set to -0.2V even when COL± are receiving data.

#### **EDLC GROUP**

## TEN (transmit encode enable, input)

This is an input to the on-chip Manchester encoder and enables TXDATA pair. Input high enables TXDATA pair; input low makes TXDATA pair idle (high).

## TXD (transmit serial data, input)

This is an input to the on-chip Manchester encoder and provides data to be encoded.

Serial binary data must be supplied to this input synchronously with the falling edge of TCKN (transmit data clock).

This input is enabled when TEN (transmit encode enable) is high.

#### TCKN (transmit data clock, output)

10MHz clock output for the transmit serial binary data. This is stable one-tenth of the master clock frequency. See TXD (transmit serial data) description.

## RXD (receive serial data, output)

This is an output of the on-chip Manchester decoder and provides decoded data from Ethernet coax to a Data Link controller.

This output is synchronous with the falling edge of RCKN (receive data clock).

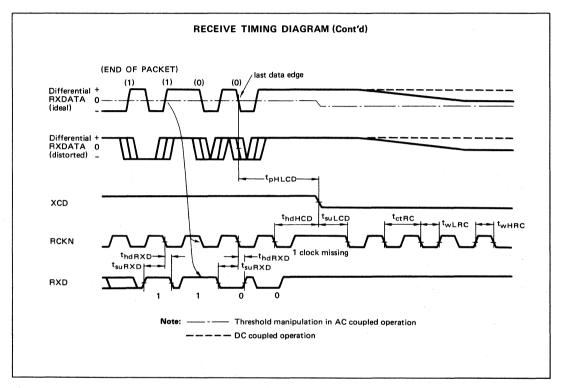

#### RCKN (receive data clock, output)

Clock output to strobe RXD (receive serial data). See RXD (receive serial data) description.

At the beginning of a packet, RCKN is inhibited for 6 or 7 clock cycles to allow the PLL to gain acquisition. And at the end of a packet, RCKN is inhibited for 1 clock cycle.

During idle state, this output generates a 10MHz clock signal.

#### XCOL (collision presence, output)

This is a TTL duplication of the collision presence pair (COL $^\pm$ ). The transceiver connected to Ethernet coax supplies a high level or differential voltage of 0V to COL  $^\pm$  when collision is not seen on the coax. It supplies a 10MHz square wave signal to COL  $^\pm$  when collision is detected. Accordingly, XCOL outputs high level when collision is not seen and outputs a 10MHz square wave signal during collision presence.

## XCD (receive carrier detect, output)

This output provides carrier detect function of the Manchester decoder. This signal is used by a Data Link controller receiver as a data acquisition enable signal and by a Data Link controller transmitter as transmition permission information.

Output is low when the Ethernet coax is idle.

#### LBC (loopback command, input)

High level input to this pin dictates loopback mode operation. During the loopback mode operation,

XCOL output is high level,

TXDATA+ output is high level, RXDATA± inputs are ignored

and the data supplied to TXD (transmit serial data) when TEN (transmit encode enable) is high is encoded, supplied to the Manchester decoder through the internal route and output from RXD (receive serial data), RCKN (receive data clock) and XCD (receive carrier detect).

#### OSCILLATOR GROUP

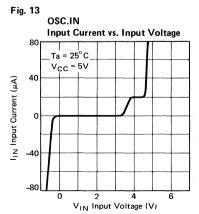

## OSC.OUT, OSC.IN AND OSC.REF (oscillator pins)

A 100MHz crystal is to be placed between OSC.IN and OSC.OUT.

An LC tank circuit is to be placed between OSC.IN and OSC.REF to assure start-up in the proper harmonic of the crystal.

OSC.OUT is an emitter-follower output and requires a pull-down resistor (330 $\Omega$  typ.). A phase adjusting capacitor is to be placed in parallel with the pull-down resistor to make the delay through the oscillator close to 10ns to increase the efficiency of the crystal.

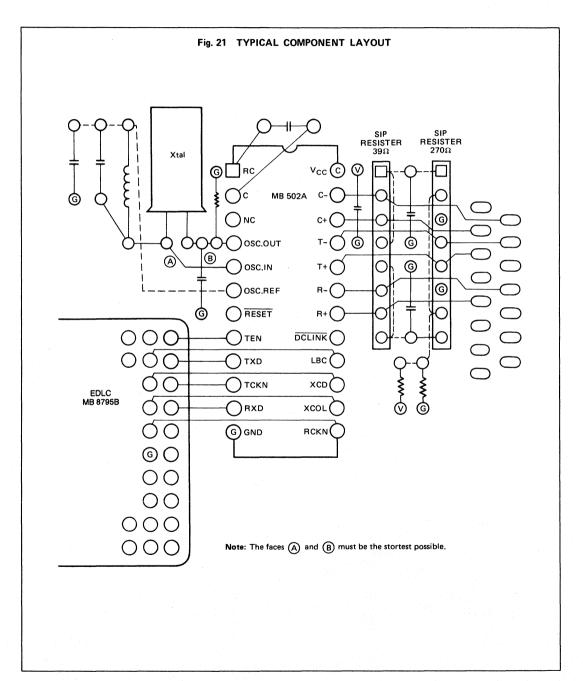

As a design recommendation, connection wires should be as short as possible.

#### **OTHERS**

## RC and C (capacitor pins)

A capacitor placed between these pins provides the timing for the transformer emulation of the transmit pair.

In AC coupled operation (DCLINK is high), after data transmission, TXDATA-goes high with rise time determined by the time-constant of the internal resistor and the connected capacitor. When a 470pF capacitor is connected, the rise time of TXDATA- is typically 0.8µs (20% to 80%).

Because pin C is connected to  $V_{CC}$  on chip, DC voltage must never be supplied to this pin.

## DCLINK (DC/AC coupling select for transceiver pair)

This input is to select DC/AC coupling of transceiver cable pairs. Low level selects DC coupling. High level selects AC coupling and makes both TXDATA+ and TXDATA- high during idle state to prevent the transformer from saturation.

See CABLE GROUP description.

This pin must be stuck at high or low level. It may be connected directly to  $V_{\rm CC}$  or ground.

## RESET (FF testing purpose only)

This input pin is to initialize flip-flops for testing purposes only and must be connected to  $V_{CC}$  or stuck at high level in a normal operation.

## NC (non-connection)

This output pin is for testing purposes only and must be left open in a normal operation.

# **ABSOLUTE MAXIMUM RATINGS\***

| Rating                    | Symbol            | Value                                                        | Unit |

|---------------------------|-------------------|--------------------------------------------------------------|------|

| Supply Voltage            | V <sub>cc</sub>   | -0.3 to 7.0                                                  | V    |

| TTL Level Input Voltage   | V <sub>ITTL</sub> | -0.3 to 7.0                                                  | V    |

| Receiver Input Voltage    | V <sub>IR</sub>   | -0.3 to V <sub>CC</sub> + 0.3                                | V    |

| Driver Output Voltage     | V <sub>ODV</sub>  | V <sub>CC</sub> (max)                                        | V    |

| Driver Output Current     | Гору              | -40.0 to 0                                                   | mA   |

| Oscillator Input Voltage  | V <sub>iosc</sub> | V <sub>CC</sub> -4 to V <sub>CC</sub> ,<br>and more than-0.3 | V    |

| Oscillator Output Current | loosc             | -20.0 to 0                                                   | mA   |

| Operating Temperature     | T <sub>OP</sub>   | -25 to 100                                                   | °C   |

| Storage Temperature       | T <sub>STG</sub>  | -65 to 125                                                   | °c   |

<sup>\*</sup> Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to the conditions as destailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **RECOMMENDED OPERATING CONDITIONS**

|                 | Parameter                              | Symbol            | Value                             | Operating Temperature |

|-----------------|----------------------------------------|-------------------|-----------------------------------|-----------------------|

| Supply Voltag   | Supply Voltage                         |                   | 5.0V ± 5%                         | -                     |

| TTL High Lev    | TTL High Level Output Current          |                   | -0.4 mA to 0 mA                   |                       |

| TTL Low Leve    | el Output Current                      | l <sub>oL</sub>   | 0 mA to 8 mA                      |                       |

| Receiver Input  | Voltage                                | V <sub>IR</sub>   | 0V to V <sub>CC</sub>             |                       |

| Driver Termin   | ator                                   | R <sub>LD</sub>   | 270Ω                              | 0°C to +70°C          |

| Differential Lo | pad                                    | R <sub>DLD</sub>  | 78Ω                               | 0 6 10 +70 6          |

| Oscillator Terr | minator                                | R <sub>LOSC</sub> | $330\Omega$ and $33$ pF parallel* |                       |

| Crystal for Os  | cillator                               | f <sub>XTAL</sub> | 100 MHz ± 0.01%**                 |                       |

| Capacitor plac  | Capacitor placed between C and RC pins |                   | 470pF                             |                       |

| LC Tank         | Inductance                             | Losc              | 0.15 μΗ                           |                       |

| Constant        | Capacitance                            | Cosc              | 33pF*                             |                       |

<sup>\*</sup> The values of the oscillator capacitors may have to be tuned for a particular components layout. Both capacitors should be adjusted for maximum voltage at OSC.IN.

\*\* 5th overtone series resonant.

However, once the correct values are determined for that layout, any more tuning will not be necessary for each board.

# DC CHARACTERISTICS

(Recommended operating conditions unless otherwise noted.)

| _                                       | 0                |                                                      |                     | Value |      |      |      |

|-----------------------------------------|------------------|------------------------------------------------------|---------------------|-------|------|------|------|

| Parameter                               | Symbol           | Condition                                            | V <sub>cc</sub> (V) | min.  | typ. | max. | Unit |

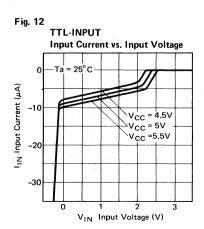

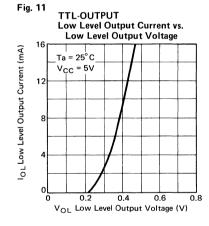

| High Level Input Voltage                | V <sub>IH</sub>  |                                                      |                     | 2.0   |      |      | ٧    |

| Low Level Input Voltage                 | VIL              |                                                      |                     |       |      | 0.8  | ٧    |

| Input Clamp Voltage <sup>*1</sup>       | V <sub>IC</sub>  | I <sub>IL</sub> = -18mA                              | 4.75                | -1.5  |      |      | ٧    |

| High Level Output Voltage *2            | V <sub>oh</sub>  | I <sub>OH</sub> = -0.4mA                             | 4.75                | 2.7   |      |      | V    |

| Low Level Output Voltage *2             | V <sub>OL</sub>  | I <sub>OL</sub> = 8mA                                | 4.75                |       |      | 0.5  | ٧    |

| High Level Input Current                | I <sub>tH</sub>  | V <sub>IH</sub> = 2.7V                               | 5.25                |       |      | 20   | μΑ   |

| Low Level Input Current                 | l <sub>IL</sub>  | V <sub>IL</sub> = 0.4V                               | 5.25                | -100  |      |      | μΑ   |

| Output Short Current                    | Ios              | V <sub>O</sub> = 0V                                  | 5.25                | -100  |      | -20  | mA   |

| High Level Differential Input Voltage   | V <sub>IHD</sub> | V <sub>IR+</sub> - V <sub>IR</sub> -<br>DCLINK = 0V  |                     | 0.2   |      |      | ٧    |

| Low Level Differential Input Voltage    | V <sub>ILD</sub> | V <sub>IR+</sub> – V <sub>IR</sub> –<br>DCLINK = 0V  |                     |       |      | -0.2 | ٧    |

| High Level Differential Input Voltage   | V <sub>IHD</sub> | V <sub>IR+</sub> - V <sub>IR-</sub><br>DCLINK = 4.5V |                     | -0.05 |      |      | ٧    |

| Low Level Differential Input Voltage    | VILD             | V <sub>IR+</sub> - V <sub>IR-</sub><br>DCLINK = 4.5V |                     |       |      | -0.4 | ٧    |

| High Level Differential Input Voltage   | V <sub>IHD</sub> | V <sub>IR+</sub> V <sub>IR-</sub><br>DCLINK = 4.5V   |                     | 0.2   |      |      | ٧    |

| Low Level Differential Input Voltage *5 | VILD             | V <sub>IR+</sub> - V <sub>IR-</sub><br>DCLINK = 4.5V |                     |       |      | -0.2 | ٧    |

| High Level Input Current                | I <sub>IHR</sub> | V <sub>IR</sub> = 5.25V<br>DCLINK = 0V               | 5.25                |       |      | 0.7  | mA   |

| Low Level Input Current                 | IILR             | V <sub>IR</sub> = 0V<br>DCLINK = 0V                  | 5.25                | -1.5  |      |      | mΑ   |

Note: 1: Applicable to TTL input pins. (TEN, TXD, LBC, DCLINK and RESET)

2: Applicable to TTL output pins. (TCKN, RXD, RCKN, XCOL and XCD)

3: Applicable to COL± and RXDATA±.

4: Applicable to RXDATA± while XCD output is low (idle state) and COL±.

5: Applicable to RXDATA± while XCD output is high.

(Recommended operating conditions unless otherwise noted.)

| _                                            |                   |                                         |                     | Value |      |       |      |

|----------------------------------------------|-------------------|-----------------------------------------|---------------------|-------|------|-------|------|

| Parameter                                    | Symbol            | Condition                               | V <sub>cc</sub> (V) | min.  | typ. | max.  | Unit |

| High Level Output Voltage *1                 | V <sub>OHTX</sub> |                                         | 5.0                 |       | 4.1  |       | ٧    |

| Low Level Output Voltage *1                  | V <sub>OLTX</sub> |                                         | 5.0                 |       | 3.3  |       | ٧    |

| High Level Differential Output<br>Voltage *1 | V <sub>OHD</sub>  | $\frac{V_{O^+} - V_{O^-}}{DCLINK} = 0V$ |                     | 0.55  |      | 1.0   | V    |

| Low Level Differential Output<br>Voltage *1  | V <sub>OLD</sub>  | $\frac{V_{O^+} - V_{O^-}}{DCLINK} = 0V$ |                     | -1.0  |      | -0.55 | v    |

| Oscillator Reference Voltage *2              | V <sub>BB</sub>   |                                         | 5.0                 |       | 3.7  |       | ٧    |

| High Level Input Current*3                   | I <sub>IHO</sub>  | V <sub>IH</sub> = 4.1V                  | 5.0                 |       |      | 150   | μΑ   |

| High Level Output Voltage*4                  | V <sub>оно</sub>  | OSC.IN is open                          | 5.0                 |       | 4.15 |       | ٧    |

| Low Level Output Voltage *4                  | V <sub>OLO</sub>  | V <sub>IOSC</sub> = 4.1V                | 5.0                 |       | 3.3  |       | V    |

| RC Internal Resistor                         | R <sub>RC</sub>   | V <sub>RC</sub> = 0.5V                  | 0.5                 | 25    | 50   | 100   | kΩ   |

| Power Supply Current                         | Icc               | All signal pins are open.               | 5.25                |       |      | 220   | mA   |

Note: 1: Applicable to TXDATA±.

These pins are connected to ground through 270 $\Omega$  resistor. And 78 $\Omega$  resistor is placed between these pins.

2: Applicable to OSC.REF.

3: Applicable to OSC.IN.

4: Applicable to OSC.OUT.

This pin is connected to ground through a 330 $\Omega$  resistor.

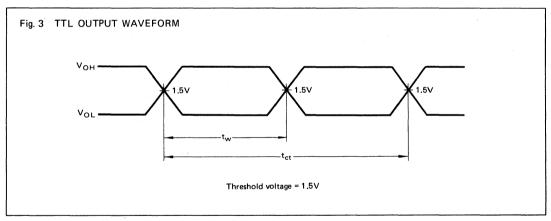

# **AC CHARACTERISTICS**

## TRANSMIT TIMING

(Recommended operating conditions unless otherwise noted. V<sub>CC</sub>=5.0V)

| D                           | Symbol            | 0 - 1:::                                                         |            | Value |        | -      | l lmia |  |

|-----------------------------|-------------------|------------------------------------------------------------------|------------|-------|--------|--------|--------|--|

| Parameter                   | Symbol            | Condition                                                        | Fig.       | min.  | typ.   | max.   | Unit   |  |

| TCKN Cycle Time             | t <sub>ctTC</sub> |                                                                  | 2,3        | 99.99 | 100.00 | 100.01 | ns     |  |

| TCKN Low Time               | t <sub>wLTC</sub> |                                                                  | 2,3        | 40    | 50     |        | ns     |  |

| TCKN High Time              | t <sub>wHTC</sub> |                                                                  | 2,3        | 40    | 50     |        | ns     |  |

| TXDATA± Encode Time         | t <sub>pdTX</sub> |                                                                  | 2,3<br>5,6 |       | 95     |        | ns     |  |

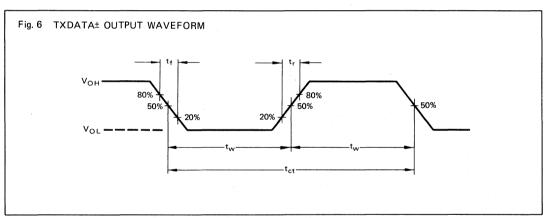

| TXDATA± Output Rise Time    | t <sub>rTX</sub>  |                                                                  | 5,6        |       | 2.0    |        | ns     |  |

| TADATA± Output Fall Time    | t <sub>fTX</sub>  |                                                                  | 5,6        |       | 2.0    |        | ns     |  |

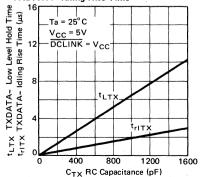

| TXDATA- Low Level Hold Time | t <sub>LTX</sub>  | C <sub>TX</sub> = 470pF<br>DCLINK = V <sub>CC</sub>              | 5,6        |       | 3      |        | μs     |  |

| TXDATA- Idling Rise Time    | t <sub>rITX</sub> | $C_{TX} = 470pF$ $(20\% \sim 80\%)$ $\overline{DCLINK} = V_{CC}$ | 5,6        |       | 0.8    |        | μs     |  |

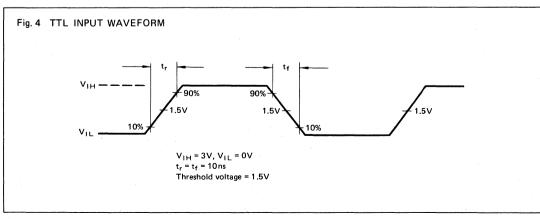

| TXD, TEN Setup Time         | t <sub>suTX</sub> |                                                                  | 4          | 20    |        |        | ns     |  |

| TXD, TEN Hold Time          | t <sub>hdTX</sub> |                                                                  | 4          | 0     |        |        | ns     |  |

## **RECEIVE TIMING**

(Recommended operating conditions unless otherwise noted. V<sub>CC</sub>=5.0V)

| Parameter               | Symbol              | Condition |         | Value |        |        | Linit |

|-------------------------|---------------------|-----------|---------|-------|--------|--------|-------|

| Parameter               |                     |           | Fig.    | min.  | typ.   | max.   | Unit  |

| RCKN Cycle Time in Idle | t <sub>ctRC</sub>   |           | 2,3     | 99.99 | 100.00 | 100.01 | ns    |

| RCKN Low Time           | t <sub>wLRC</sub>   |           | 2,3     | 35    | 50     |        | ns    |

| RCKN High Time          | t <sub>wHRC</sub>   |           | 2,3     | 35    | 50     |        | ns    |

| RCKN Delay Time         | t <sub>pHLRC</sub>  |           | 2, 3, 7 |       | 120    |        | ns    |

| XCD ON Delay Time       | t <sub>pLHCD</sub>  |           | 2, 3, 7 |       | 80     | 110    | ns    |

| XCD OFF Delay Time      | t <sub>pHLCD</sub>  |           | 2, 3, 7 |       | 230    |        | ns    |

| XCD Low Hold Time       | t <sub>hdLCD</sub>  |           | 2,3     | 0     | 10     |        | ns    |

| XCD High Hold Time      | t <sub>hd</sub> HCD |           | 2,3     |       | 120    |        | ns    |

| XCD Low Setup Time      | t <sub>suLCD</sub>  |           | 2, 3    |       | 80     |        | ns    |

| RXD Setup Time          | t <sub>suRXD</sub>  |           | 2, 3    | 20    | 60     |        | ns    |

| RXD Hold Time           | t <sub>hdRXD</sub>  |           | 2, 3    | 10    | 20     |        | ns    |

## LOOPBACK TIMING

(Recommended operating conditions unless otherwise noted. V<sub>CC</sub>=5.0V)

| Parameter                      | Complete            | Condition |         | Value |      |      | Unit |

|--------------------------------|---------------------|-----------|---------|-------|------|------|------|

| Farameter                      | Symbol              | Condition | Fig.    | min.  | typ. | max. | Oill |

| LBC Receiving Data Purge Time  | t <sub>pgLBC</sub>  |           | 2, 3, 4 |       | 230  |      | ns   |

| LBC Receiving Data Accept Time | t <sub>acLBC</sub>  |           | 2, 3, 4 |       | 80   |      | ns   |

| DATA Through Time              | t <sub>pHLTRU</sub> |           | 2, 3, 4 |       | 280  |      | ns   |

| TEN Wait Time                  | t <sub>wtEN</sub>   |           | 2, 3, 4 | 0     |      |      | ns   |

In Loopback mode operation, COL± and RXDATA± inputs are ignored, TXDATA+ and XCOL are high level and XCD, RCKN and RXD functions are in the same manner as a normal receive operation.

## **COLLISION TIMING**

(Recommended operating conditions unless otherwise noted, V<sub>CC</sub>=5.0V)

| Parameter                             | Symbol           | Condition   | Condition |      | Value |      |      |  |

|---------------------------------------|------------------|-------------|-----------|------|-------|------|------|--|

| r at attleter                         | Symbol           | Condition   | Fig.      | min. | typ.  | max. | Unit |  |

| COL to XCOL<br>Propagation Delay Time | t <sub>pLH</sub> | DCLINK = 0V | 2,3,7     | -    | 9     | 30   | ns   |  |

| COL to XCOL<br>Propagation Delay Time | t <sub>pHL</sub> | DCLINK = 0V | 2,3,7     |      | 11    | 30   | ns   |  |

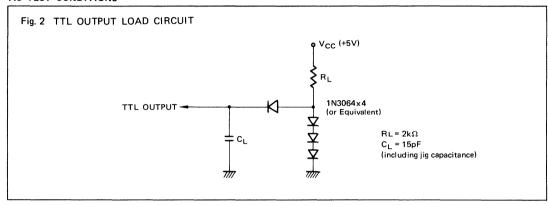

## AC TEST CONDITIONS

5

## AC TEST CONDITIONS (Cont'd)

# J

# TYPICAL CHARACTERISTICS CURVES

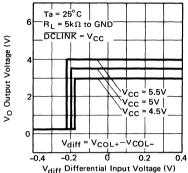

Fig. 14

COL± to XCOL TRANSFER (Receiver Threshold)

Output Voltage vs. Differential Input Voltage

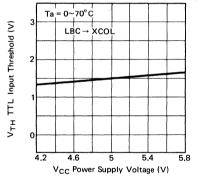

Fig. 16

TTL-INPUT THRESHOLD

TTL Input Threshold vs. Power Supply Voltage

Fig. 18

TXDATA- LOW LEVEL HOLD TIME

TXDATA- Low Level Hold Time

TXDATA- Idling Rise Time

vs. RC Capacitance

Fig. 15

COL± to XCOL TRANSFER (Receiver Threshold)

Output Voltage vs. Differential Input Voltage

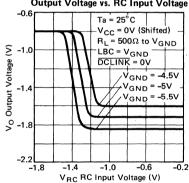

Fig. 17

RC to TXDATA- TRANSFER

Output Voltage vs. RC Input Voltage

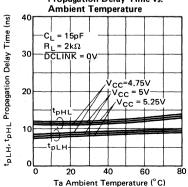

Fig. 19

COL± to XCOL PROPAGATION DELAY TIME

Propagation Delay Time vs.

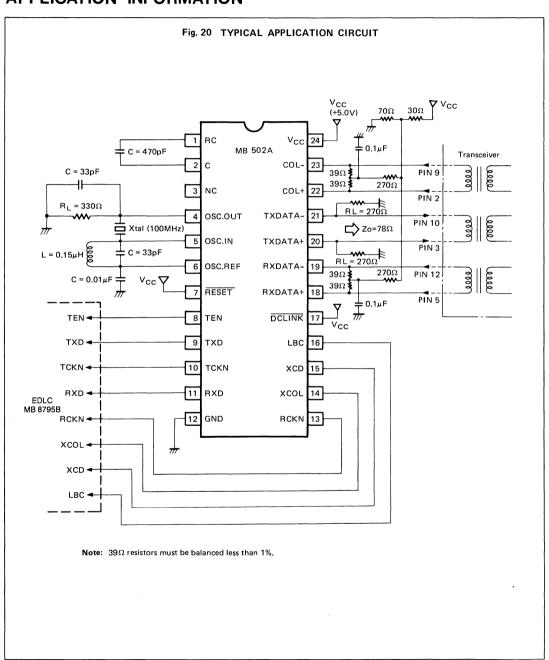

# **APPLICATION INFORMATION**

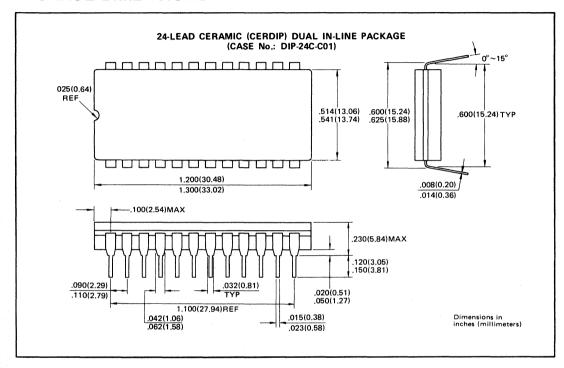

# PACKAGE DIMENSIONS