# MEMORY Consumer FCRAM<sup>TM</sup> cmos

## 256M Bit (4 bank x 1M word x 64 bit)

Consumer Applications Specific Memory for SiP

## MB81EDS256445

#### **■ DESCRIPTION**

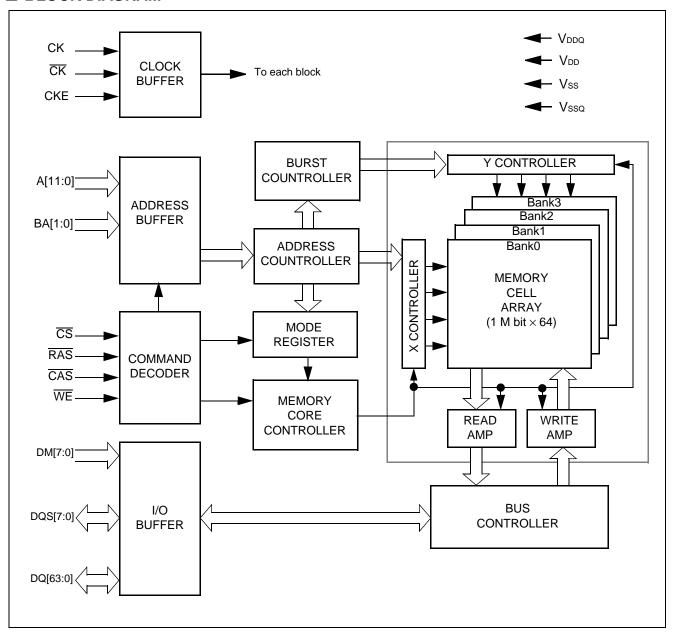

The Fujitsu MB81EDS256445 is a CMOS Fast Cycle Random Access Memory (FCRAM\*) with Low Power Double Data Rate (LPDDR) SDRAM Interface containing 268,435,456 storages accessible in a 64-bit format. MB81EDS256445 is suited for consumer application requiring high data band width with low power consumption.

\*: FCRAM is a trademark of Fujitsu Microelectronics Limited, Japan

#### ■ FEATURES

- 1 M word × 64 bit × 4 banks organization

- DDR Burst Read/Write Access Capability

- -tck = 4.6 ns Min / 216 MHz Max (Tj ≤ + 105  $^{\circ}$ C)

- $-t_{CK} = 5 \text{ ns Min} / 200 \text{ MHz Max } (Tj \le + 125 °C)$

- Low Voltage Power Supply:  $V_{DD} = V_{DDQ} + 1.7 \text{ V to } + 1.95 \text{ V}$

- Junction Temperature:  $T_J = -10 \, ^{\circ}\text{C}$  to  $+ 125 \, ^{\circ}\text{C}$

- 1.8 V-CMOS compatible inputs

- Burst Length: 2, 4, 8, 16

- CAS latency: 2, 3, 4

- Clock Stop capability during idle periods

- Auto Precharge option for each burst access

- Configurable Driver Strength and Pre Driver Strength

- Auto Refresh and Self Refresh Modes

- Deep Power Down Mode

- Low Power Consumption

- -IDD4R =300 mA Max @ 3.46 GByte/s

- -IDD4W =330 mA Max @ 3.46 GByte/s

- 4 K refresh cycles / 4 ms (Tj  $\leq$  +125 °C)

#### **■ PIN DESCRIPTIONS**

| Symbol          | Туре   | Fun                     | ection |           |

|-----------------|--------|-------------------------|--------|-----------|

| CK, CK          | Input  | Clock                   |        |           |

| CKE             | Input  | Clock Enable            |        |           |

| CS              | Input  | Chip Select             |        |           |

| RAS             | Input  | Row Address Strobe      |        |           |

| CAS             | Input  | Column Address Strobe   |        |           |

| WE              | Input  | Write Enable            |        |           |

| BA[1:0]         | Input  | Bank Address Inputs     |        |           |

| A[11:0]         | loput  | Address Inputs          | Row    | A0 to A11 |

| A[11.0]         | Input  | Address inputs          | Column | A0 to A7  |

| AP(A10)         | Input  | Auto Precharge Enable   | ·      | ·         |

| DM[7:0] *1      | Input  | Input Data Mask Enable  |        |           |

| DQ[63:0] *1, *2 | I/O    | Data Bus Input / Output |        |           |

| DQS[7:0] *2     | I/O    | Data Strobe             |        |           |

| Vddq, Vdd       | Supply | Power Supply            |        |           |

| Vssq, Vss       | Supply | Ground                  |        |           |

<sup>\*1 :</sup> DM0, DM1, DM2, DM3, DM4, DM5, DM6 and DM7 correspond to DQ[7:0], DQ[15:8], DQ[23:16], DQ[31:24], DQ[39:32], DQ[47:40], DQ[55:48] and DQ[63:56].

<sup>\*2 :</sup> DQS0, DQS1, DQS2, DQS3, DQS4, DQS5, DQS6 and DQS7 correspond to DQ[7:0], DQ[15:8], DQ[23:16], DQ[31:24], DQ[39:32], DQ[47:40], DQ[55:48] and DQ[63:56].

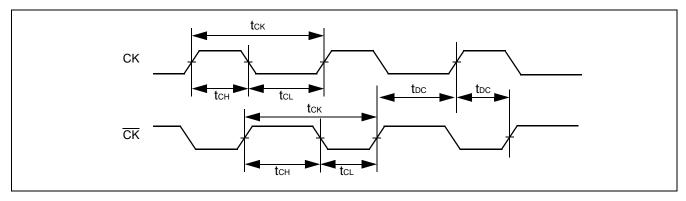

#### 1. Clock Inputs (CK and $\overline{CK}$ )

CK and  $\overline{\text{CK}}$  are differential clock inputs. All address and control input signals are sampled on the rising edge of CK. And the rising edge of  $\overline{\text{CK}}$  increment device internal address counter and drive even and odd data input/out respectively.

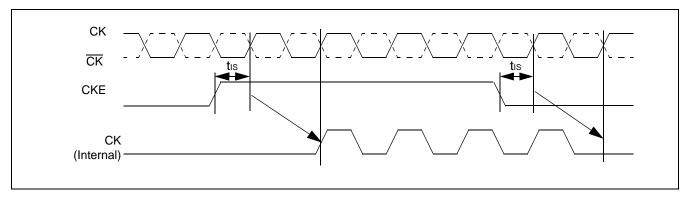

#### 2. Clock Enable (CKE)

CKE is a high active clock enable signal. When CKE = Low is latched at the rising edge of CK, the next CK rising edge will be invalid. CKE controls power down mode and self refresh mode.

#### 3. Chip Select (CS)

$\overline{\text{CS}}$  enables all commands inputs,  $\overline{\text{RAS}}$ ,  $\overline{\text{CAS}}$ , and  $\overline{\text{WE}}$ , and address inputs.  $\overline{\text{CS}}$  = High disable command input but internal operation such as burst cycle will not be suspended.

#### 4. Command Inputs (RAS, CAS and WE)

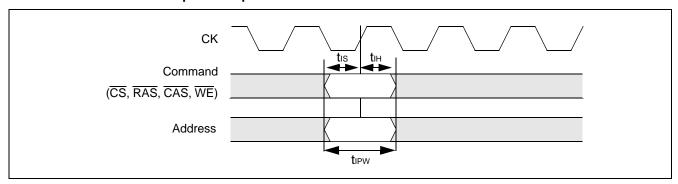

The combination of RAS, CAS, and WE input in conjunction with CS at a rising edge of the CK define the command for device operation. Refer to the "■COMMAND TRUTH TABLE".

#### 5. Bank Address Inputs (BA0, BA1)

BA0 and BA1 define to which bank an ACTIVE, READ, WRITE or PRECHARGE command is being applied.

#### 6. Address Inputs (A0 to A11)

Address input selects an arbitrary location of a total of 1,048,576 words of each memory cell matrix. Total twenty address input signals are required to decode such a matrix. Row Address (RA) is input from A0 to A11 and Column Address (CA) is input from A0 to A7. Row addresses are latched with ACTIVE (ACT or MACT) commands, and Column addresses and Auto Precharge (AP) bit are latched with Read (READ or READA) or Write command (WRIT or WRITA).

#### • Command and address inputs setup and hold time

#### 7. Input Data Mask (DM0 to DM7)

DM is an input mask signal for write data. Input data is masked when DM is sampled High on the both edges of DQS along with input data. DM0, DM1, DM2, DM3, DM4, DM5, DM6 and DM7 correspond to DQ[7:0], DQ[15:8], DQ[23:16], DQ[31:24], DQ[39:32], DQ[47:40], DQ[55:48] and DQ[63:56] respectively. Refer to the "DQ/DQS/DM Correspondence Table".

#### 8. Data Bus Input / Output (DQ0 to DQ63)

DQ is data bus input / output signal.

#### 9. Data Strobe (DQS0 to DQS7)

DQS is edge aligned with output read data and center aligned with input write data. DQS0, DQS1, DQS2, DQS3, DQS4, DQS5, DQS6 and DQS7 correspond to DQ[7:0], DQ[15:8], DQ[23:16], DQ[31:24], DQ[39:32], DQ[47:40], DQ[55:48] and DQ[63:56] respectively. Refer to the "DQ/DQS/DM Correspondence Table".

#### • DQ/DQS/DM Correspondence Table

| DQ        | DQS  | DM  |

|-----------|------|-----|

| DQ[7:0]   | DQS0 | DM0 |

| DQ[15:8]  | DQS1 | DM1 |

| DQ[23:16] | DQS2 | DM2 |

| DQ[31:24] | DQS3 | DM3 |

| DQ[39:32] | DQS4 | DM4 |

| DQ[47:40] | DQS5 | DM5 |

| DQ[55:48] | DQS6 | DM6 |

| DQ[63:56] | DQS7 | DM7 |

#### **■ BLOCK DIAGRAM**

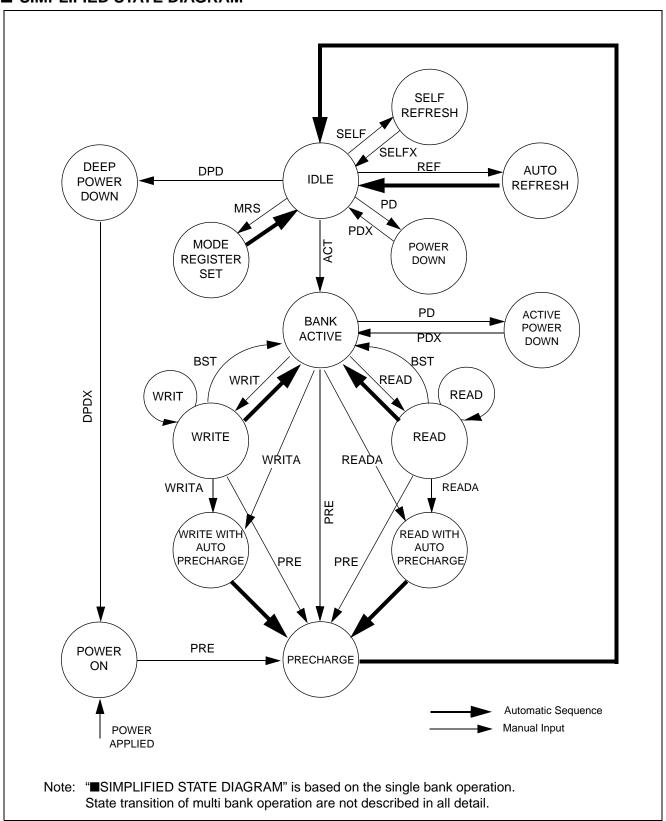

#### **■ SIMPLIFIED STATE DIAGRAM**

#### **■ FUNCTIONAL DESCRIPTION**

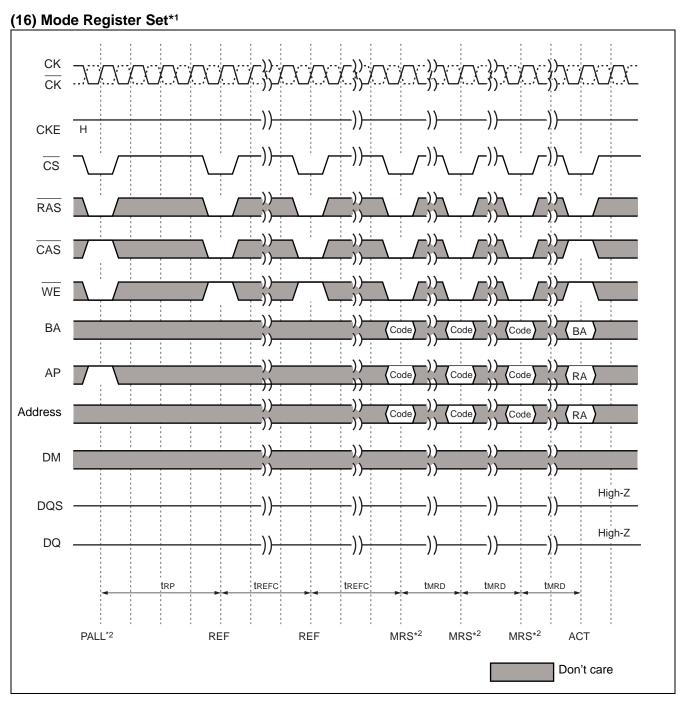

#### 1. Power Up Initialization

This device internal condition after power-up will be undefined. The following Power up initialization sequence must be performed to start proper device operation.

- 1. Apply power (VDD should be applied before or in parallel with VDDQ) and start clock. Attempt to maintain either NOP or DESL command at the input.

- 2. Maintain stable power, stable clock, and NOP or DESL condition for a minimum of 300  $\mu$ s.

- 3. Precharge all banks by PRECHARGE (PRE) or PRECHARGE ALL (PALL) command.

- 4. Assert minimum of 2 AUTO REFRESH (REF) commands.

- 5. Program the Mode Register by MODE REGISTER SET (MRS) command.

- 6. Program the Extended Mode Register by MODE REGISTER SET (MRS) command.

In addition, CKE must be High to ensure that output is High-Z state. The Mode Register and Extended Mode Register can be set before 2 Auto-refresh commands (REF).

#### 2. Mode Register

The Mode Register is used to configure the type of device function among optional features. This device has 2 Mode Registers, Mode Register and Extended Mode Register. Mode Registers can be programmed by MODE REGISER SET (MRS) command. Refer to the "Mode Register Table" in

"

FUNCTIONAL DESCRIPTION".

#### **Mode Register Table**

#### **Mode Register** BA<sub>1</sub> $\mathsf{B}\mathsf{A}_0$ A<sub>11</sub> **A**<sub>10</sub> $A_9$ A<sub>8</sub> $A_7$ $A_6$ $A_5$ $A_4$ Аз $A_2$ $A_1$ $A_0$ **ADDRESS** Mode Register 0 0 0 0 CL 0 BL 0 0 $A_4$ **CAS Latency** $A_1$ Αo **Burst Length** $A_6$ $A_5$ $A_2$ 0 0 0 Reserved 0 0 0 Reserved 1 Reserved 0 0 0 0 1 2 0 1 0 0 0 4 1 0 3 0 8 1 1 1 1 1 0 0 4 1 0 0 16 1 0 1 Reserved 1 0 1 Reserved 1 1 0 Reserved 1 1 0 Reserved 1 1 Reserved 1 1 Reserved 1 1 **Extended Mode Register** BΑ<sub>1</sub> BA<sub>0</sub> $A_9$ $A_8$ **A**7 $A_6$ $A_5$ $A_4$ $A_2$ $A_1$ $A_0$ Аз **ADDRESS** Extended Mode 0 1 0 0 0 0 0 **PDS** DS 0 0 0 0 0 Register $A_6$ Pre Driver Strength $A_5$ **Driver Strength** Fast Normal 0 0 Slow Weak 1 1

#### 3. Burst Length (BL)

Burst Length (BL) is the number of word to be read or write as the result of a single READ or WRITE command. It can be set on 2, 4, 8, 16 words boundary through Mode Register. The burst type is sequential that is incremental decoding scheme within a boundary address to be determined by burst length. Device internal address counter assigns +1 to the previous address until reaching the end of boundary address and then wrap round to least significant address (=0).

| Burst  | Start | ing Colu              | ımn Ad     | dress | Burst Address Sequence          |

|--------|-------|-----------------------|------------|-------|---------------------------------|

| Length | Аз    | <b>A</b> <sub>2</sub> | <b>A</b> 1 | Ao    | (Hexadecimal)                   |

| 2      | Х     | Х                     | Х          | 0     | 0 - 1                           |

| 2      | Х     | Х                     | Х          | 1     | 1 - 0                           |

|        | Х     | Х                     | 0          | 0     | 0 - 1 - 2 - 3                   |

| 4      | Х     | Х                     | 0          | 1     | 1 - 2 - 3 - 0                   |

| 4      | Х     | Х                     | 1          | 0     | 2 - 3 - 0 - 1                   |

|        | Х     | Х                     | 1          | 1     | 3 - 0 - 1 - 2                   |

|        | Х     | 0                     | 0          | 0     | 0 - 1 - 2 - 3 - 4 - 5 - 6 - 7   |

|        | Х     | 0                     | 0          | 1     | 1 - 2 - 3 - 4 - 5 - 6 - 7 - 0   |

|        | Х     | 0                     | 1          | 0     | 2 - 3 - 4 - 5 - 6 - 7 - 0 - 1   |

| 8      | Х     | 0                     | 1          | 1     | 3 - 4 - 5 - 6 - 7 - 0 - 1 - 2   |

| 0      | Х     | 1                     | 0          | 0     | 4 - 5 - 6 - 7 - 0 - 1 - 2 - 3   |

|        | Х     | 1                     | 0          | 1     | 5 - 6 - 7 - 0 - 1 - 2 - 3 - 4   |

|        | Х     | 1                     | 1          | 0     | 6 - 7 - 0 - 1 - 2 - 3 - 4 - 5   |

|        | Х     | 1                     | 1          | 1     | 7 - 0 - 1 - 2 - 3 - 4 - 5 - 6   |

|        | 0     | 0                     | 0          | 0     | 0-1-2-3-4-5-6-7-8-9-A-B-C-D-E-F |

|        | 0     | 0                     | 0          | 1     | 1-2-3-4-5-6-7-8-9-A-B-C-D-E-F-0 |

|        | 0     | 0                     | 1          | 0     | 2-3-4-5-6-7-8-9-A-B-C-D-E-F-0-1 |

|        | 0     | 0                     | 1          | 1     | 3-4-5-6-7-8-9-A-B-C-D-E-F-0-1-2 |

|        | 0     | 1                     | 0          | 0     | 4-5-6-7-8-9-A-B-C-D-E-F-0-1-2-3 |

|        | 0     | 1                     | 0          | 1     | 5-6-7-8-9-A-B-C-D-E-F-0-1-2-3-4 |

|        | 0     | 1                     | 1          | 0     | 6-7-8-9-A-B-C-D-E-F-0-1-2-3-4-5 |

| 16     | 0     | 1                     | 1          | 1     | 7-8-9-A-B-C-D-E-F-0-1-2-3-4-5-6 |

| 10     | 1     | 0                     | 0          | 0     | 8-9-A-B-C-D-E-F-0-1-2-3-4-5-6-7 |

|        | 1     | 0                     | 0          | 1     | 9-A-B-C-D-E-F-0-1-2-3-4-5-6-7-8 |

|        | 1     | 0                     | 1          | 0     | A-B-C-D-E-F-0-1-2-3-4-5-6-7-8-9 |

|        | 1     | 0                     | 1          | 1     | B-C-D-E-F-0-1-2-3-4-5-6-7-8-9-A |

|        | 1     | 1                     | 0          | 0     | C-D-E-F-0-1-2-3-4-5-6-7-8-9-A-B |

|        | 1     | 1                     | 0          | 1     | D-E-F-0-1-2-3-4-5-6-7-8-9-A-B-C |

|        | 1     | 1                     | 1          | 0     | E-F-0-1-2-3-4-5-6-7-8-9-A-B-C-D |

|        | 1     | 1                     | 1          | 1     | F-0-1-2-3-4-5-6-7-8-9-A-B-C-D-E |

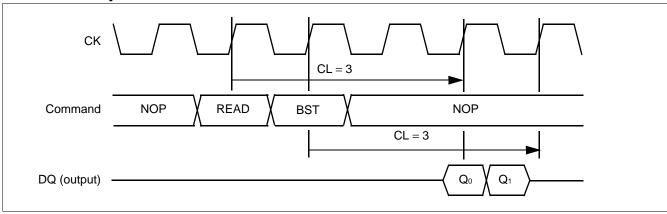

#### 4. CAS Latency (CL)

CAS Latency (CL) is the delay between READ command being registered and first read data becoming available during read operation. First read data will be valid after (CL-1)  $\times$  tck + tac from the CK rising edge where Read command being latched.

#### 5. Driver Strength (DS)

Driver Strength (DS) is to adjust the driver strength of data output.

#### 6. Pre Driver Strength (PDS)

Pre Driver Strength (PDS) is to adjust the transition time of the data output without changing the output driver impedance.

#### **■ COMMAND TRUTH TABLE**

#### 1) Basic Command Truth Table

| Command                          | Symbol | cs | RAS | CAS | WE | ВА | A10<br>(AP) | A[9:0],<br>A11 |

|----------------------------------|--------|----|-----|-----|----|----|-------------|----------------|

| DESELECT*1                       | DESL   | Н  | Х   | Х   | Χ  | Х  | Х           | Х              |

| NO OPERATION *1                  | NOP    | L  | Н   | Н   | Н  | Х  | Х           | Х              |

| BURST TERMINATE *2, *3           | BST    | L  | Н   | Н   | L  | Х  | Χ           | Х              |

| READ *3, *4                      | READ   | L  | Н   | L   | Н  | V  | L           | CA             |

| READ with Auto-precharge *3, *4  | READA  | L  | Н   | L   | Н  | V  | Н           | CA             |

| WRITE *3, *4                     | WRIT   | L  | Н   | L   | L  | V  | L           | CA             |

| WRITE with Auto-precharge *3, *4 | WRITA  | L  | Н   | L   | L  | V  | Н           | CA             |

| BANK ACTIVE *4, *5               | ACT    | L  | L   | Н   | Н  | V  |             | RA             |

| PRECHARGE SINGLE BANK *5, *6     | PRE    | L  | L   | Н   | L  | V  | L           | Х              |

| PRECHARGE ALL BANKS *5, *6       | PALL   | L  | L   | Н   | L  | Х  | Н           | Х              |

| AUTO REFRESH *6                  | REF    | L  | L   | L   | Н  | Х  | Х           | Х              |

| MODE REGISTER SET *7             | MRS    | L  | L   | L   | L  | V  | V           | V              |

Note: V = Valid, L = V<sub>IL</sub>, H = V<sub>IH</sub>, X can be either V<sub>IL</sub> or V<sub>IH</sub>, RA = Row Address, CA = Column Address All commands are assumed to be valid state transitions and latched on the rising edge of CK. CKE assume to be kept High.

<sup>\*1:</sup> NOP and DESL commands have the same functionality. Unless specifically noted, NOP will represent both NOP and DESL command in later description.

<sup>\*2:</sup> When the current state is IDLE and CKE=L, BST command will represent DPD command. Refer to the "■CKE COMMAND TRUTH TABLE".

<sup>\*3:</sup> BST command can be applied to READ or WRIT. READA and WRITA must not be terminated by BST command.

<sup>\*4:</sup> READ, READA, WRIT and WRITA commands can be issued after the corresponding bank has been activated. Refer to the "■SIMPLIFIED STATE DIAGRAM".

<sup>\*5:</sup> ACT command can be issued after corresponding bank has been precharged by PRE or PALL command. Refer to the "■ SIMPLIFIED STATE DIAGRAM".

<sup>\*6:</sup> REF command can be issued after all banks have been precharged by PRE or PALL command. Refer to the "■SIMPLIFIED STATE DIAGRAM".

<sup>\*7:</sup> MRS command can be issued after all banks have been precharged and all DQ are in High-Z. Mode Register and Extended Mode Register are selected through BA input. Mode Register and Extended Mode Register must be set by MRS command after power up.

#### 2) CKE Command Truth Table

| Command                  | Symbol | CI  | <b>KE</b> | CS | RAS | CAS | WE  | ВА | A[11:0] |

|--------------------------|--------|-----|-----------|----|-----|-----|-----|----|---------|

| Command                  | Symbol | n-1 | n         | CS | KAS | CAS | VVL | ВА | A[11.0] |

| SELF REFRESH ENTRY*1     | SELF   | Н   | L         | L  | L   | L   | Н   | Х  | х       |

| SELF REFRESH EXIT *2     | SELEV  | L   | Н         | L  | Н   | Н   | Н   | Х  | Х       |

| SELF REFRESH EXIT        | SELFX  | _   | п         | Н  | Х   | Х   | Х   | Х  | Х       |

| DOWED DOWN ENTRY **      | DD     | Н   |           | L  | Н   | Н   | Н   | Х  | Х       |

| POWER DOWN ENTRY *1      | PD     | "   | L         | Н  | Х   | Х   | Х   | Х  | Х       |

| POWER DOWN EXIT          | PDX    | L   | Н         | L  | Н   | Н   | Н   | Х  | Х       |

| POWER DOWN EXIT          | FDX    | _   | 11        | Н  | Х   | Х   | Х   | Х  | Х       |

| DEEP POWER DOWN ENTRY *1 | DPD    | Н   | L         | L  | Н   | Н   | L   | х  | Х       |

| DEEP POWER DOWN EXIT     | DPDX   | L   | Н         | L  | Н   | Н   | Н   | Х  | Х       |

| DEEP POWER DOWN EXIT     | שרטא   | _ L | п         | Н  | Х   | Х   | Х   | Х  | Х       |

Note: V = Valid,  $L = V_{IL}$ ,  $H = V_{IH}$ , X can be either  $V_{IL}$  or  $V_{IH}$

<sup>\*1:</sup> SELF and DPD commands can be issued after all banks have been precharged and all DQ are in High-Z.

<sup>\*2:</sup> CKE should be held High more than treet period after SELFX.

#### 3) Single Bank Operation

| Current State | CS | RAS | CAS | WE | Address    | Command    | Function                               |

|---------------|----|-----|-----|----|------------|------------|----------------------------------------|

| IDLE          | Н  |     |     | Х  | DESL       |            |                                        |

|               | L  | Н   | Н   | Н  | Х          | NOP        | NOP                                    |

|               | L  | Н   | Н   | L  | Х          | BST        | _                                      |

|               | L  | Н   | L   | Н  | BA, CA, AP | READ/READA | Illegal *1                             |

|               | L  | Н   | L   | L  | BA, CA, AP | WRIT/WRITA | - illegal                              |

|               | L  | L   | Н   | Н  | BA, RA     | ACT        | Bank Active                            |

|               | L  | L   | Н   | L  | BA, AP     | PRE/PALL   | NOP *2                                 |

|               | L  | L   | L   | Η  | X          | REF        | Auto Refresh *3                        |

|               | L  | L   | L   | L  | MODE       | MRS        | Mode Register Set *3, *4               |

| BANK ACTIVE   | Н  | Х   | Х   | Χ  | X          | DESL       |                                        |

|               | L  | Н   | Н   | Η  | X          | NOP        | NOP                                    |

|               | L  | Н   | Н   | L  | Х          | BST        | _                                      |

|               | L  | Н   | L   | Н  | BA, CA, AP | READ/READA | Start Read; Determine AP               |

|               | L  | Н   | L   | L  | BA, CA, AP | WRIT/WRITA | Start Write; Determine AP              |

|               | L  | L   | Н   | Н  | BA, RA     | ACT        | Illegal *1                             |

|               | L  | L   | Н   | L  | BA, AP     | PRE/PALL   | Precharge; Determine<br>Precharge Type |

|               | L  | L   | L   | Ι  | Х          | REF        | Illogol                                |

|               | L  | L   | L   | L  | MODE       | MRS        | - Illegal                              |

| Current State | CS | RAS | CAS | WE | Address    | Command    | Function                                                 |

|---------------|----|-----|-----|----|------------|------------|----------------------------------------------------------|

| READ          | Н  | Х   | Χ   | Χ  | Х          | DESL       | NOP                                                      |

|               | L  | Н   | Н   | Н  | Х          | NOP        | TNOP                                                     |

|               | L  | Н   | Н   | L  | Х          | BST        | Burst Terminate → BANK ACTIVE                            |

|               | L  | Н   | L   | H  | BA, CA, AP | READ/READA | Interrupt burst read by new burst read; Determine AP     |

|               | L  | Н   | L   | L  | BA, CA, AP | WRIT/WRITA | Illegal                                                  |

|               | L  | L   | Н   | Τ  | BA, RA     | ACT        | Illegal *1                                               |

|               | L  | L   | Н   | L  | BA, AP     | PRE/PALL   | Terminate burst read by precharge → IDLE                 |

|               | L  | L   | L   | Η  | Х          | REF        | Illegal                                                  |

|               | L  | L   | L   | L  | MODE       | MRS        | Tillegal                                                 |

| WRITE         | Ι  | X   | Χ   | Χ  | X          | DESL       | NOP                                                      |

|               | Ш  | Н   | Н   | Η  | X          | NOP        | 1101                                                     |

|               | L  | Н   | Н   | L  | Х          | BST        | Burst terminate → BANK ACTIVE                            |

|               | L  | Н   | L   | Н  | BA, CA, AP | READ/READA | Interrupt burst write by new burst read; Determine AP *5 |

|               | L  | Н   | L   | L  | BA, CA, AP | WRIT/WRITA | Interrupt burst write by new burst write; Determine AP   |

|               | L  | L   | Н   | Н  | BA, RA     | ACT        | Illegal *1                                               |

|               | L  | L   | Н   | L  | BA, AP     | PRE/PALL   | Tillegal                                                 |

|               | L  | L   | L   | Н  | Х          | REF        | Illegal                                                  |

|               | L  | L   | L   | L  | MODE       | MRS        | lliogai                                                  |

| Current State       | CS | RAS | CAS | WE | Address    | Command    | Function   |

|---------------------|----|-----|-----|----|------------|------------|------------|

| READ WITH           | Н  | Х   | Х   | Χ  | Х          | DESL       | NOP        |

| AUTO<br>PRECHARGE   | L  | Н   | Н   | Н  | X          | NOP        | NOF        |

|                     | L  | Н   | Н   | L  | X          | BST        | Illegal    |

|                     | L  | Н   | L   | Н  | BA, CA, AP | READ/READA |            |

|                     | L  | Н   | L   | L  | BA, CA, AP | WRIT/WRITA | Illegal *1 |

|                     | L  | L   | Н   | Н  | BA, RA     | ACT        | illegal    |

|                     | L  | L   | Н   | L  | BA, AP     | PRE/PALL   |            |

|                     | L  | L   | L   | Н  | X          | REF        | Illegal    |

|                     | L  | L   | L   | L  | MODE       | MRS        | illegai    |

| WRITE WITH          | Н  | Х   | Χ   | Χ  | Х          | DESL       | NOP        |

| AUTO PRE-<br>CHARGE | L  | Н   | Н   | Η  | X          | NOP        | NOF        |

|                     | L  | Н   | Н   | Г  | X          | BST        | Illegal    |

|                     | L  | Н   | L   | Н  | BA, CA, AP | READ/READA |            |

|                     | L  | Н   | L   | L  | BA, CA, AP | WRIT/WRITA | Illegal *1 |

|                     | L  | L   | Н   | Н  | BA, RA     | ACT        | illegal    |

|                     | L  | L   | Н   | L  | BA, AP     | PRE/PALL   |            |

|                     | L  | L   | L   | Η  | Х          | REF        | Illegal    |

|                     | L  | L   | L   | L  | MODE       | MRS        | illegai    |

| Current State | CS | RAS | CAS | WE | Address    | Command    | Function                  |

|---------------|----|-----|-----|----|------------|------------|---------------------------|

| Write         | Н  | Х   | Χ   | Χ  | Х          | DESL       |                           |

| Recovering    | L  | Н   | Н   | Η  | Х          | NOP        | NOP                       |

|               | L  | Н   | Н   | L  | Х          | BST        |                           |

|               | L  | Н   | L   | Н  | BA, CA, AP | READ/READA | Illegal                   |

|               | L  | Н   | L   | L  | BA, CA, AP | WRIT/WRITA | Start Write; Determine AP |

|               | L  | L   | Н   | Н  | BA, RA     | ACT        | Illegal *1                |

|               | L  | L   | Н   | L  | BA, AP     | PRE/PALL   | - Illegal                 |

|               | L  | L   | L   | Н  | Х          | REF        | Illegal                   |

|               | L  | L   | L   | L  | MODE       | MRS        | - Illegal                 |

| Precharging   | Н  | Х   | Х   | Х  | Х          | DESL       | NOP                       |

|               | L  | Н   | Н   | Н  | Х          | NOP        | TNOP                      |

|               | L  | Н   | Н   | L  | X          | BST        | Illegal                   |

|               | L  | Н   | L   | Н  | BA, CA, AP | READ/READA |                           |

|               | L  | Н   | L   | L  | BA, CA, AP | WRIT/WRITA | Illegal *1                |

|               | L  | L   | Н   | Н  | BA, RA     | ACT        |                           |

|               | L  | L   | Н   | L  | BA, AP     | PRE/PALL   | NOP *2                    |

|               | L  | L   | L   | Н  | Х          | REF        | Illegal                   |

|               | L  | L   | L   | L  | MODE       | MRS        | Tilleyai                  |

#### (Continued)

| Current State            | CS  | RAS | CAS | WE | Address    | Command                       | Function   |

|--------------------------|-----|-----|-----|----|------------|-------------------------------|------------|

| Bank                     | Н   | Х   | Х   | Х  | X          | DESL                          | NOP        |

| Activating               | L   | Н   | Н   | Н  | Х          | NOP                           | NOP        |

|                          | L   | Н   | Н   | L  | Х          | BST                           |            |

|                          | L   | Н   | L   | Н  | BA, CA, AP | READ/READA                    |            |

|                          | L   | Н   | L   | L  | BA, CA, AP | WRIT/WRITA                    | Illegal *2 |

|                          | L   | L   | Н   | Н  | BA, RA     | ACT                           |            |

|                          | L   | L   | Н   | L  | BA, AP     | PRE/PALL                      |            |

|                          | L   | L   | L   | Н  | Х          | REF/SELF                      | Illegal    |

|                          | L   | L   | L   | L  | MODE       | MRS                           | illegai    |

| Refreshing/              | Н   | Х   | Х   | Χ  | X          | DESL                          | NOP        |

| Mode Register<br>Setting | L   | Н   | Н   | Н  | Х          | NOP                           | NOP        |

| g                        | L   | Н   | Н   | L  | Х          | BST                           |            |

|                          | L   | Н   | L   | Х  | Х          | READ/READA/<br>WRIT/WRITA     | Illegal    |

|                          | L L |     | Х   | Х  | Х          | ACT/PRE/PALL/<br>REF/SELF/MRS |            |

RA = Row Address

CA = Column Address

BA = Bank Address

CA = Column Address AP = Auto Precharge

Note: Assuming CKE = H during the previous clock cycle and the current clock cycle. After illegal commands are asserted, following command and stored data should not be guaranteed.

\*1: Illegal to bank in the specified state. Command entry may be legal depending on the state of bank selected by BA.

\*2: NOP to bank in precharging or in idle state. Bank in active state may be precharged depending on BA.

\*3: Illegal if any bank is not idle.

\*4: MRS command should be issued on condition that all DQ are in High-Z.

\*5: Requires appropriate DM masking.

#### **■ BANK OPERATION COMMAND TABLE**

Minimum clock latency or delay time for single bank operation

|             |               |                                             | 2nd Command (same bank)           |                   |                           |             |             |                                  |                                  |                                  |                                        |                                            |  |  |  |  |

|-------------|---------------|---------------------------------------------|-----------------------------------|-------------------|---------------------------|-------------|-------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------------|--------------------------------------------|--|--|--|--|

|             |               | MRS                                         | АСТ                               | READ              | READA                     | WRIT        | WRITA       | BST                              | PRE                              | PALL                             | REF                                    | SELF                                       |  |  |  |  |

|             | MRS           | tmrd                                        | tmrd                              | _                 | _                         | _           | _           | <b>t</b> MRD                     | tmrd                             | tmrd                             | tmrd                                   | tmrd                                       |  |  |  |  |

|             | ACT           | 1                                           | 1                                 | trcd              | t <sub>RCD</sub>          | trco        | *5<br>trcd  | _                                | tras                             | tras                             | 1                                      | 1                                          |  |  |  |  |

|             | READ          | 1                                           | 1                                 | 1                 | 1                         | BL/2<br>+CL | BL/2<br>+CL | 1                                | <sup>•3</sup><br>1               | *3<br>1                          | 1                                      | 1                                          |  |  |  |  |

|             | READA         | *1, *2<br>BL/2<br>+ t <sub>RP</sub>         | BL/2<br>+ t <sub>RP</sub>         | _                 |                           | _           |             | BL/2<br>+ t <sub>RP</sub>        | BL/2<br>+ t <sub>RP</sub>        | BL/2<br>+ t <sub>RP</sub>        | BL/2<br>+ t <sub>RP</sub>              | *1, *2<br>BL/2<br>+ t <sub>RP</sub>        |  |  |  |  |

| p           | WRIT          |                                             |                                   | *6<br>2<br>+ twrr | *6<br>2<br>+ <b>t</b> wtr | 1           | 1           | 1                                | BL/2<br>+ 1<br>+ twr             | BL/2<br>+ 1<br>+ twr             |                                        | _                                          |  |  |  |  |

| 1st Command | WRITA         | *1, *2<br>BL/2<br>+ 1<br>+ t <sub>DAL</sub> | BL/2<br>+ 1<br>+ t <sub>DAL</sub> | 1                 | _                         | _           | _           | BL/2<br>+1<br>+ t <sub>DAL</sub> | BL/2<br>+1<br>+ t <sub>DAL</sub> | BL/2<br>+1<br>+ t <sub>DAL</sub> | *1<br>BL/2<br>+1<br>+ t <sub>DAL</sub> | *1, *2<br>BL/2<br>+1<br>+ t <sub>DAL</sub> |  |  |  |  |

| st Co       | READ -<br>BST | 1                                           | 1                                 | 1                 | 1                         | CL          | CL          | . 1                              | *3<br>1                          | *3<br>1                          | 1                                      | -                                          |  |  |  |  |

| _           | WRIT -<br>BST |                                             | _                                 | 1<br>+ twrr       | 1<br>+ twrr               | 1           | 1           | '                                | *3<br>1<br>+ twr                 | *3<br>1<br>+ twr                 |                                        |                                            |  |  |  |  |

|             | PRE           | *1, *2<br><b>t</b> RP                       | ṫRP                               | _                 | _                         | _           | _           | <b>t</b> RP                      | 1                                | 1                                | *1<br><b>t</b> RP                      | *1, *2<br><b>t</b> RP                      |  |  |  |  |

|             | PALL          | *2<br><b>t</b> RP                           | <b>t</b> RP                       | _                 | _                         | _           | _           | <b>t</b> RP                      | 1                                | 1                                | <b>t</b> RP                            | *2<br><b>t</b> RP                          |  |  |  |  |

|             | REF           | trefc                                       | trefc                             |                   | _                         | _           | _           | trefc                            | trefc                            | trefc                            | trefc                                  | trefc                                      |  |  |  |  |

| " ,         | SELFX         | trefc                                       | trefc                             | _                 | _                         | _           | _           | trefc                            | trefc                            | trefc                            | trefc                                  | trefc                                      |  |  |  |  |

<sup>&</sup>quot; - ": illegal

<sup>\*1:</sup> Assume all banks are in IDLE state.

<sup>\*2:</sup> Assume output is in High-Z state.

<sup>\*3:</sup> Assume tras (Min.) is satisfied.

<sup>\*4:</sup> ACT to READA interval must be longer than tRAS - BL/2.

<sup>\*5:</sup> ACT to WRITA interval must be longer than tras - (1 + BL/2 + twr).

<sup>\*6:</sup> Assume appropriate DM masking.

Minimum clock latency or delay time for multi bank operation

| 1411111     | mum clock     | laterity C                          | or delay    | unie ioi                  |                           | nd Com      |             | her ban                          | k)    |                           |                                         |                                         |

|-------------|---------------|-------------------------------------|-------------|---------------------------|---------------------------|-------------|-------------|----------------------------------|-------|---------------------------|-----------------------------------------|-----------------------------------------|

|             |               | MRS                                 | ACT         | READ                      | READA                     | WRIT        | WRITA       | BST                              | PRE   | PALL                      | REF                                     | SELF                                    |

|             | MRS           | <b>t</b> mrd                        | tmrd        | _                         | _                         | _           | _           | <b>t</b> mrd                     | tmrd  | tmrd                      | tmrd                                    | tmrd                                    |

|             | ACT           | _                                   | trrd        | 1                         | 1                         | 1           | 1           | 1                                | 1     | tras                      | _                                       | _                                       |

|             | READ          | _                                   | *1, *3<br>1 | 1                         | 1                         | BL/2<br>+CL | BL/2<br>+CL | 1                                | 1     | 1                         | _                                       | _                                       |

|             | READA         | *1, *2<br>BL/2<br>+ t <sub>RP</sub> | *1, *3<br>1 | BL/2                      | BL/2                      | BL/2<br>+CL | BL/2<br>+CL | BL/2<br>+ t <sub>RP</sub>        | 1     | BL/2<br>+ t <sub>RP</sub> | *1<br>BL/2<br>+ t <sub>RP</sub>         | BL/2<br>+ t <sub>RP</sub>               |

| р           | WRIT          | _                                   | *1, *3<br>1 | *5<br>2<br>+ <b>t</b> wTR | *5<br>2<br>+ <b>t</b> wtr | 1           | 1           | 1                                | 1     | BL/2<br>+ 1<br>+ twr      | _                                       | _                                       |

| 1st Command | WRITA         | + 1<br>+ 1<br>+ tdal                | *1, *3<br>1 | BL/2<br>+ 1<br>+ twrr     | BL/2<br>+ 1<br>+ twrr     | BL/2        | BL/2        | BL/2<br>+1<br>+ t <sub>DAL</sub> | 1     | BL/2<br>+ 1<br>+ tdal     | *1<br>BL/2<br>+ 1<br>+ t <sub>DAL</sub> | *1<br>BL/2<br>+ 1<br>+ t <sub>DAL</sub> |

| st Co       | READ -<br>BST | _                                   | *1, *3<br>1 | 1                         | 1                         | CL          | CL          | 1                                | 1     | <sup>-4</sup><br>1        | _                                       | _                                       |

| 1           | WRIT -<br>BST | _                                   | 1           | 1<br>+ twr                | 1<br>+ twrr               | 1           | 1           | '                                | 1     | 1<br>+ twr                | -                                       | -                                       |

|             | PRE           | *1, *2<br><b>t</b> RP               | *1, *3<br>1 | 1                         | 1                         | 1           | 1           | 1                                | 1     | 1                         | *1<br><b>t</b> RP                       | *1, *2<br><b>t</b> RP                   |

|             | PALL          | *1<br><b>t</b> RP                   | trp         | _                         | _                         | _           | _           | trp                              | 1     | 1                         | trp                                     | trp                                     |

|             | REF           | trefc                               | trefc       | _                         | _                         | _           | _           | trefc                            | trefc | trefc                     | trefc                                   | trefc                                   |

|             | SELFX         | trefc                               | trefc       | _                         | _                         | _           | _           | trefc                            | trefc | trefc                     | trefc                                   | trefc                                   |

<sup>&</sup>quot; - ": illegal

<sup>\*1:</sup> Assume other bank is in IDLE state.

<sup>\*2:</sup> Assume output is in High-Z state.

<sup>\*3:</sup> Assume trrd is satisfied.

<sup>\*4:</sup> Assume tras is satisfied.

<sup>\*5:</sup> Assume appropriate DM masking.

#### **■ COMMAND DESCRIPTION**

#### 1. DESELECT (DESL)

When  $\overline{\text{CS}}$  is High at the CK rising edge, all input signals are neglected. Internal operation such as burst cycle is held.

#### 2. NO OPERATION (NOP)

NOP disables address and data input and internal operation such as burst cycle is held.

#### 3. BANK ACTIVE (ACT)

ACT activates the bank selected by BA and latch the row address through A0 to A11.

#### 4. READ (READ)

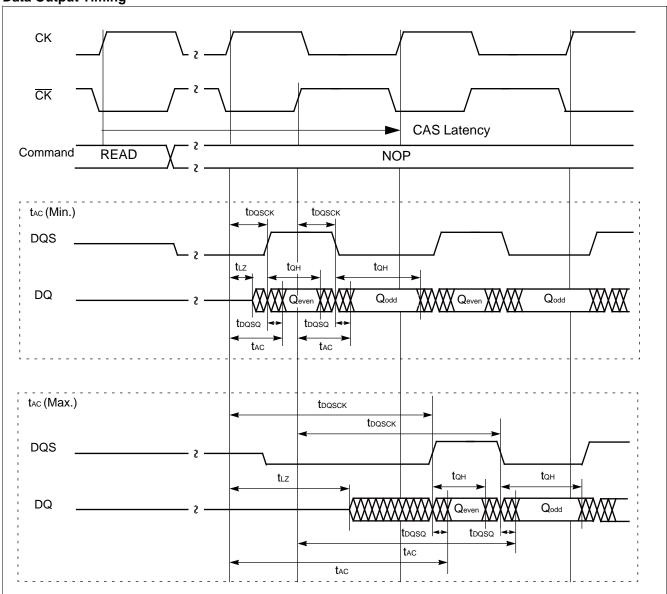

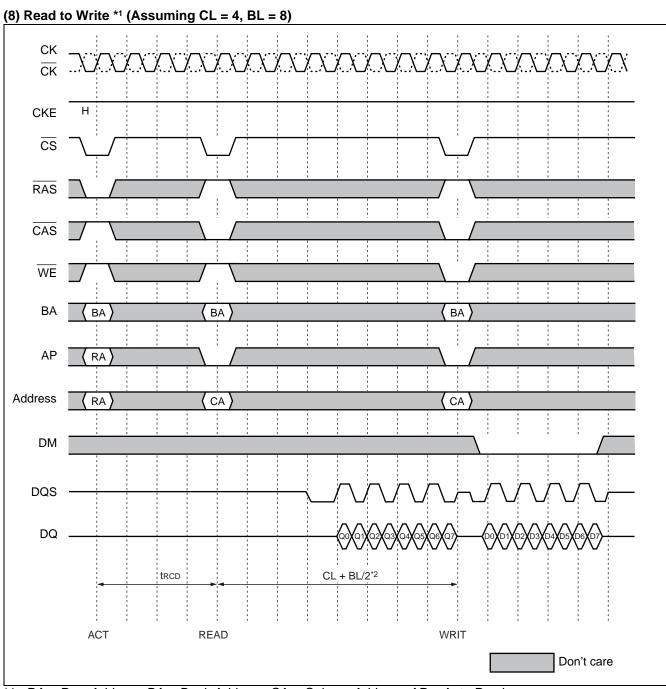

READ initiates burst read operation to an activated row address. Address inputs of A[7:0] determine starting column address and A10 determines whether Auto Precharge is used or not. Initially DQS output Low level then start toggling together with data output with respect to CL and BL. The read data output is edge-aligned with first rising edge of DQS and successive read data output are edge-aligned to the successive edge of DQS. The CK drives the rising edge of DQS and Even data, and the  $\overline{CK}$  drives the falling edge of DQS and Odd data.

#### **Data Output Timing**

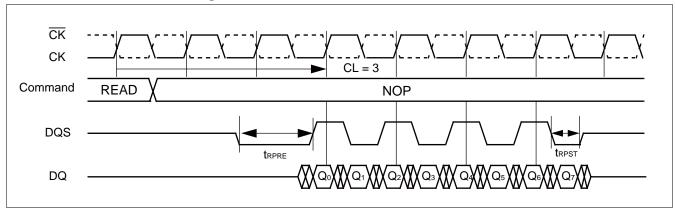

#### Read Preamble and Postamble @CL = 3

#### 5. READ with Auto Precharge (READA)

READA commands can be issued by READ command with AP (A10) = H. Auto precharge is a feature which precharge the activated bank after the completion of burst read operation. The  $t_{RAS}$  is defined from between ACTIVE (ACT) command to the internal precharge which starts after BL/2 from READA command. READ with Auto precharge operation should not be interrupted by subsequent READ, READA, WRITE, WRITEA commands. Next ACTIVE (ACT) command can be issued after BL/2 +  $t_{RP}$  after READA command.

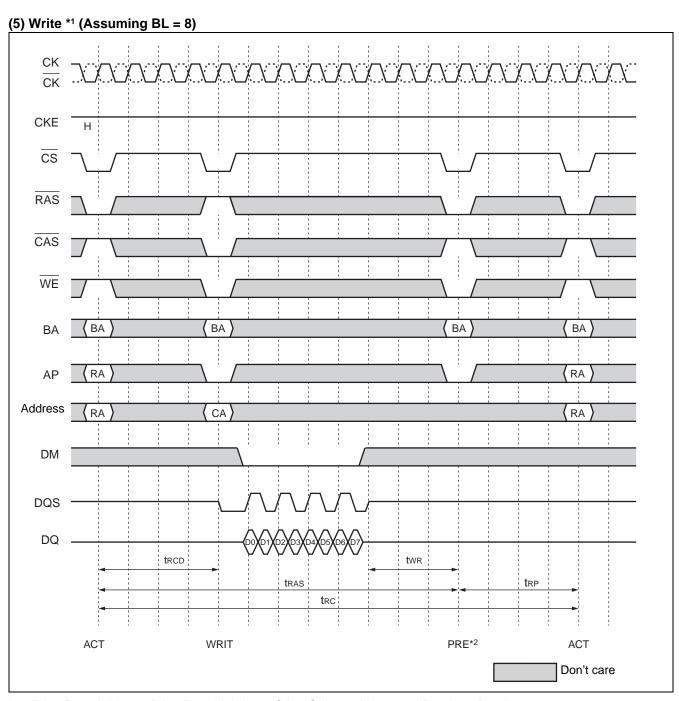

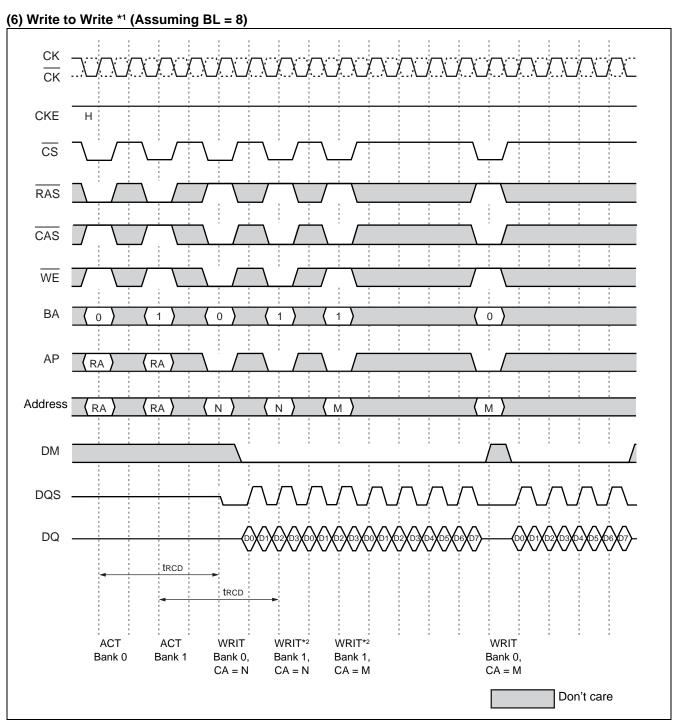

#### 6. WRITE (WRIT)

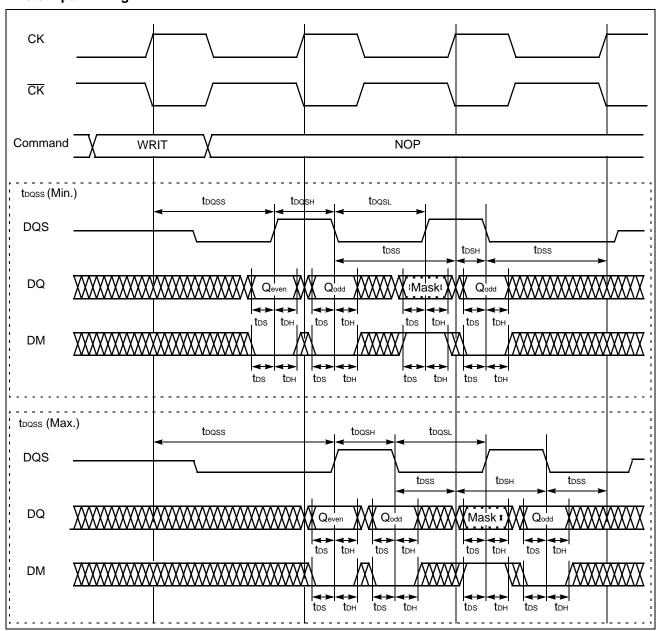

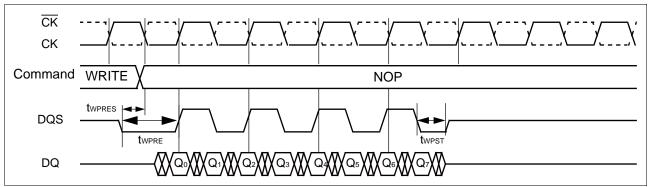

WRIT initiates burst write operation to an active row address. Address inputs of A[7:0] determine starting column address and AP(A10) determines whether Auto Precharge is used or not. DQS input must be provided in order to latch the input data. DQS must be brought to Low to satisfy the specified time duration of the Write Preamble Setup Time to CK (twpres). Input data window must be guaranteed with specified minimum setup and hold time against edge of DQS input (tds, tdh). The input data appearing on DQ is written into memory cell array subject to the DM input logic level appearing coincident with the input data. If a given signal on DM is registered Low, the corresponding data will be written into the cell array. And if a given signal on DM is registered High, the corresponding data will be masked and write will not be executed to that byte. After data input with respect to BL is completed, DQS must be kept low for the specified minimum value of Write Postamble Time (twpst).

#### **Data Input Timing**

#### Write Preamble and Postamble

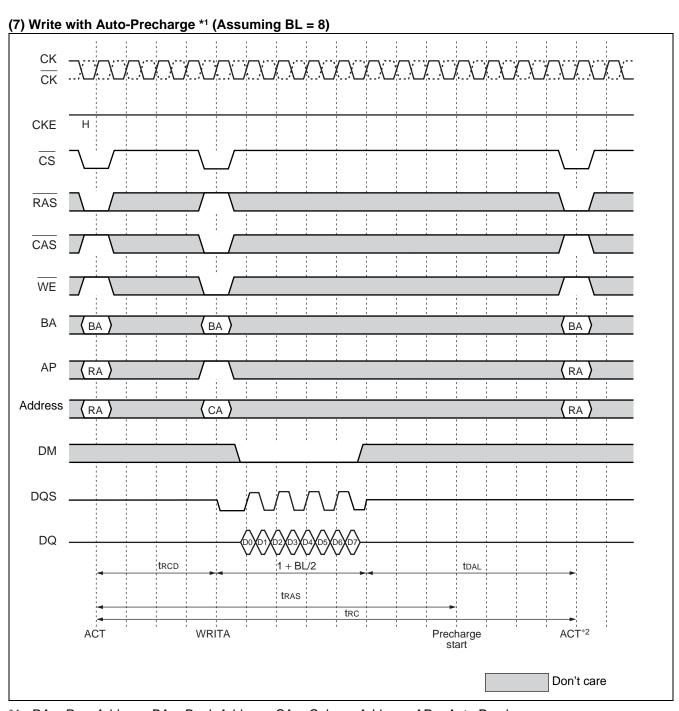

#### 7. WRITE with Auto Precharge (WRITA)

WRITA commands can be issued by WRIT command with AP (A10) = H. Auto precharge is a feature which precharge the activated bank after the completion of burst write operation. The  $t_{RAS}$  is defined from between ACTIVE (ACT) command to the internal precharge which starts after 1+ BL/2 +  $t_{WR}$  from WRITA command. WRIT with Auto precharge operation should not be interrupted by subsequent READ, READA, WRIT, WRITA commands. Next ACTIVE (ACT) command can be issued after 1+ BL/2 +  $t_{DAL}$  after WRITA command.

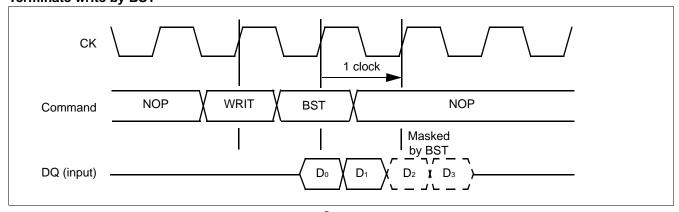

#### 8. BURST TERMINATE (BST)

BST terminates the burst read or write operation. When a burst read is terminated by BST command, the data output will be in High-Z after CAS latency from the BST command. When a burst write is terminated by BST command, the data input after 1 clock from BST command will be masked.

#### Terminate read by BST @CL=3

#### Terminate write by BST

#### 9. PRECHARGE SINGLE BANK (PRE)

PRECHARGE SINGLE BANK (PRE) command starts precharge operation for a bank selected by BA. A selected bank will be in IDLE state after specified time duration of transfer precharged. If AP(A10) = L, a bank to be selected by BA is precharged.

#### 10. PRECHARGE ALL BANK (PALL)

PRECHARGE ALL BANKS (PALL) command starts precharge operation for all banks. All banks will be in IDLE state after specified time duration of tree from PALL command. A10 determines whether one or all banks are precharged. If AP(A10) = H, all banks are precharged and BA input is a "don't care".

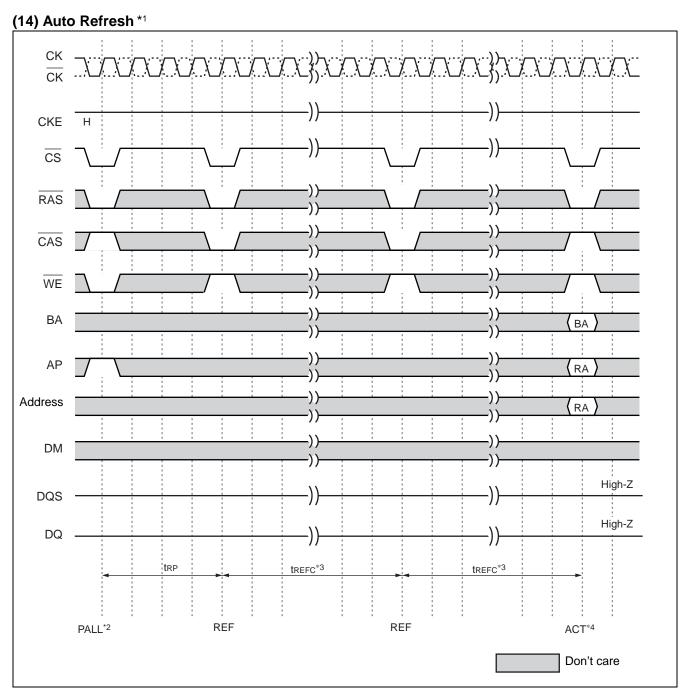

#### 11. AUTO REFRESH (REF)

AUTO REFRESH (REF) command starts internal refresh operation which uses the internal refresh address counter. All banks must be precharged prior to the Auto-refresh command. Data retention capability depends on the Junction Temperature (Tj). Total 4,096 AUTO REFRESH (REF) commands must be asserted within the following refresh period of tree.

| Tj Max ( °C) | tref (ms) |

|--------------|-----------|

| + 105        | 16        |

| + 125        | 4         |

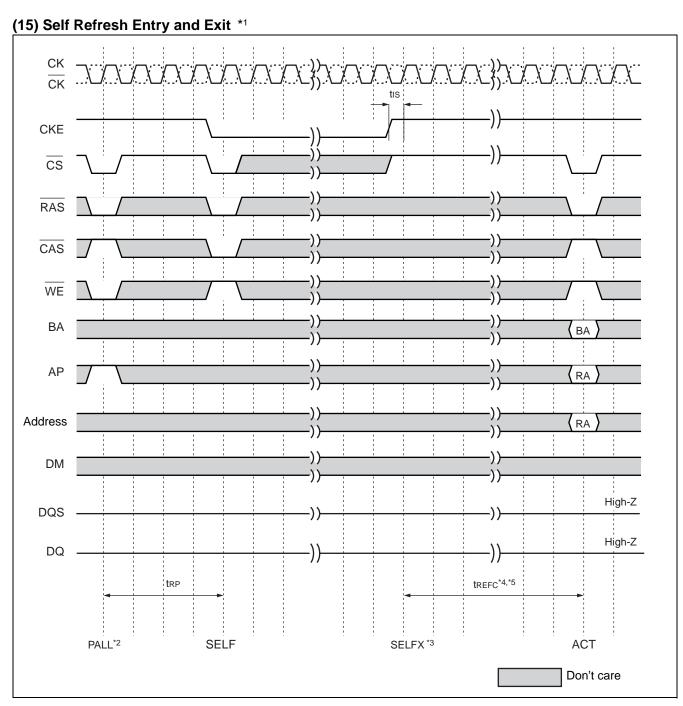

#### 12. SELF-REFRESH ENTRY (SELF)

SELF REFRESH ENTRY (SELF) commands can be issued by AUTO REFRESH (REF) command in conjunction with CKE = Low after last read data has been appeared on DQ. During Self Refresh mode, stored data can be retained without external clocking and all inputs except for CKE will be "don't care". Self refresh mode can be used when Tj is less than +85°C. Auto Refresh must be issued to retain data when Tj is greater than +85°C.

#### 13. SELF-REFRESH EXIT (SELFX)

To exit self-refresh mode, apply minimum tis after CKE brought High, and then the NO OPERATION command (NOP) or the DESELECT command (DESL) should be asserted within one tree period. CKE should be held High within one tree period after tis. Refer to the "(15) Self Refresh Entry and Exit" in "TIMING DIAGRAMS" for the detail. It is recommended to assert an Auto-refresh command just after the tree period to avoid the violation of refresh period.

#### 14. MODE REGISTER SET (MRS)

MODE REGISTER SET (MRS) commands to program the mode registers. Once a mode register is programmed, the contents of the register will be held until re-programmed by another MRS command. MRS command should only be issued on conditions that all DQs are in High-Z and all banks are in IDLE state. The contents of the mode registers is undefined after the power-up and Deep Power Down Exit. Therefore MRS must be issued to set each content of mode registers after initialization. Refer to the "Power Up Initialization" in "■FUNCTIONAL DESCRIPTION".

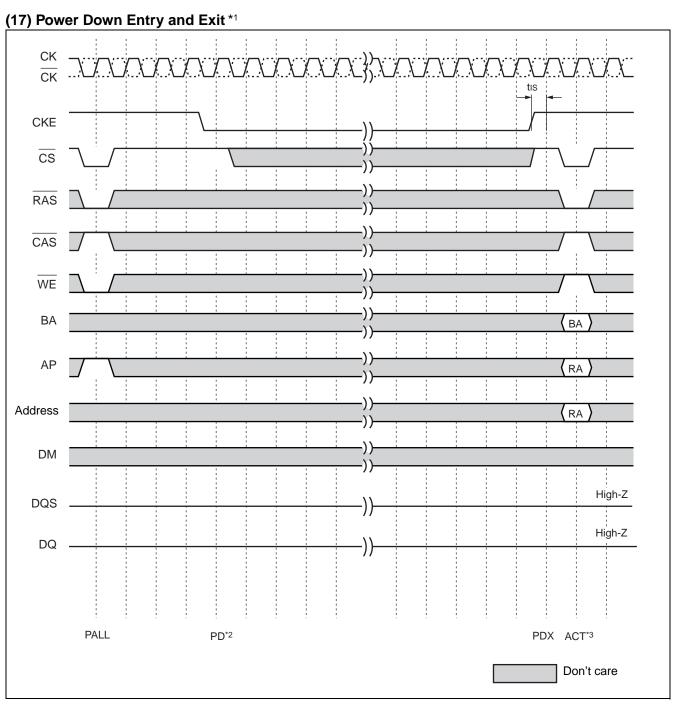

#### 15. POWER DOWN ENTRY (PD)

POWER DOWN ENTRY (PD) commands to drive the device in Power Down mode and maintains low power state as long as CKE is kept Low. During Power Down state, all inputs signals are "don't care" except for CKE. Power Down mode must be entered on condition that all DQs are in High-Z.

#### 16. POWER DOWN EXIT (PDX)

POWER DOWN EXIT (PDX) commands to resume the device from Power Down mode. Any commands can be detected 1 clock after PDX commands.

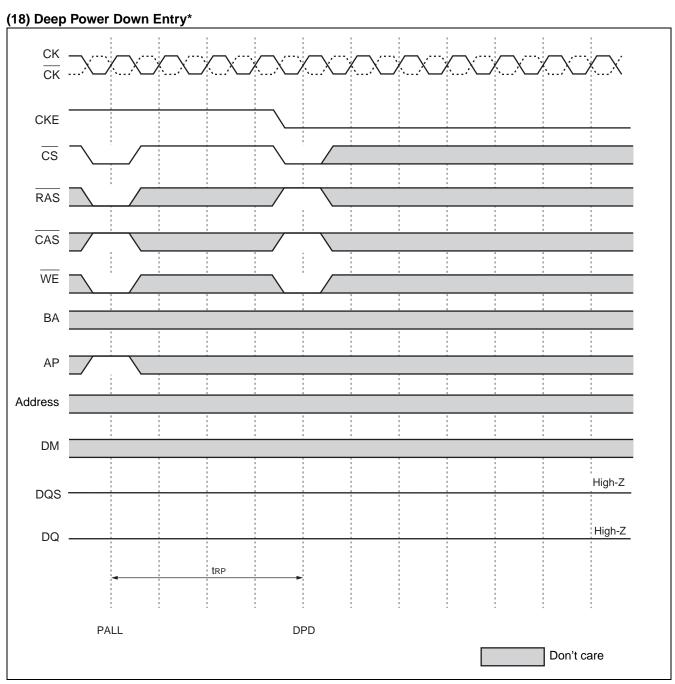

#### 17. DEEP POWER DOWN ENTRY (DPD)

DEEP POWER DOWN ENTRY (DPD) commands to drive the device in Deep Power Down mode which is the lowest power consumption but all stored data and the contents of mode registers will be lost. During Deep Power Down state, all inputs signals except for CKE are "don't care" and all DQs and DQS will be in High-Z. Deep Power Down mode must be entered on conditions that all DQs are in High-Z and all banks are in IDLE state.

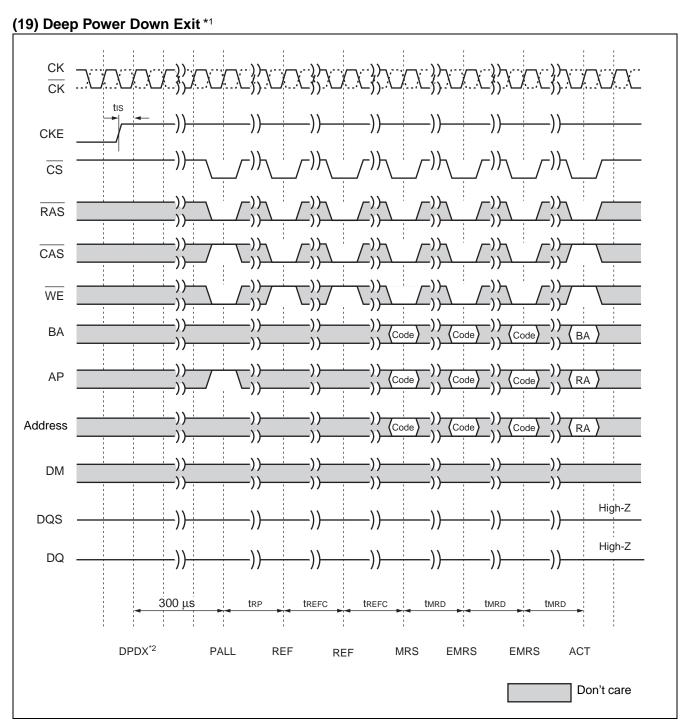

#### 18. DEEP POWER DOWN EXIT (DPDX)

DEEP POWER DOWN EXIT (DPDX) commands to resume the device from Deep Power Down mode. Power up initialization procedure must be performed after DPDX commands. Refer to the "Power Up Initialization" in "■ FUNCTIONAL DESCRIPTION".

#### ■ ABSOLUTE MAXIMUM RATINGS

| Parameter                              | Symbol    | Rating       | Unit |

|----------------------------------------|-----------|--------------|------|

| Supply Voltage Relative to Vss         | VDD,VDDQ  | -0.5 to +2.3 | V    |

| Input / Output Voltage Relative to Vss | VIN, VOUT | -0.5 to +2.3 | V    |

| Short Circuit Output Current           | Іоит      | ±50          | mA   |

| Power Dissipation                      | PD        | 1.0          | W    |

| Storage Temperature                    | Тѕтс      | -55 to +125  | °C   |

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

#### ■ RECOMMENDED OPERATING CONDITIONS

| Parameter               | Symbol    | Min.                 | Тур. | Max.                   | Unit |

|-------------------------|-----------|----------------------|------|------------------------|------|

| Cupply Voltage*1        | Vdd, Vddq | 1.7                  | 1.8  | 1.95                   | V    |

| Supply Voltage*1        | Vss, Vssq | 0                    | 0    | 0                      | V    |

| DC Input High Voltage*2 | VIH (DC)  | $V_{DDQ} \times 0.7$ | _    | VDDQ + 0.3             | V    |

| AC Input High Voltage*2 | VIH (AC)  | $V_{DDQ} \times 0.8$ |      | VDDQ + 0.3             | V    |

| DC Input Low Voltage*3  | VIL (DC)  | -0.3                 |      | VDDQ × 0.3             | V    |

| AC Input Low Voltage*3  | VIL (AC)  | -0.3                 |      | V <sub>DDQ</sub> × 0.2 | V    |

| Junction Temperature    | Tj        | -10                  | _    | +125                   | °C   |

<sup>\*1:</sup> V<sub>DDQ</sub> must be less than or equal to V<sub>DD</sub>.

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

> Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure. No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their representatives beforehand.

#### **■ CAPACITANCE**

$(T_a = + 25 \, {}^{\circ}C. f = 1 \, MHz)$

|                                  |                  |      |      | (    | <b>O</b> , |

|----------------------------------|------------------|------|------|------|------------|

| Parameter                        | Symbol           | Min. | Тур. | Max. | Unit       |

| Input Capacitance, Except for DM | C <sub>IN1</sub> | 3    | _    | 5    | pF         |

| Input Capacitance for DM         | C <sub>IN2</sub> | 5    | _    | 7    | pF         |

| I/O Capacitance                  | C <sub>I/O</sub> | 5    | _    | 7    | pF         |

<sup>\*2:</sup> Maximum DC voltage on input or I/O pins is VDDQ + 0.3 V. During voltage transitions, inputs may positive overshoot to V<sub>DDQ</sub> + 1.0V for periods of up to 3 ns.

<sup>\*3:</sup> Minimum DC voltage on input or I/O pins is -0.3 V. During voltage transitions, inputs may negative overshoot to Vssq - 1.0V for periods of up to 3 ns.

#### **■ ELECTRICAL CHARACTERISTICS**

#### 1. DC Characteristics

(Under recommended operating conditions unless otherwise noted)

| Doromotor                                         | Parameter Symbol Condition |                                                                                                                                                                                |                             |                        | Value |      |  |

|---------------------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------------------------|-------|------|--|

| Parameter                                         | Symbol                     | Condition                                                                                                                                                                      |                             | Min.                   | Max.  | Unit |  |

| Output High Voltage                               | V <sub>OH(DC)</sub>        | Iон = -0.1 mA                                                                                                                                                                  |                             | V <sub>DDQ</sub> - 0.2 | 1     | V    |  |

| Output Low Voltage                                | V <sub>OL(DC)</sub>        | loL = 0.1 mA                                                                                                                                                                   |                             |                        | 0.2   | V    |  |

| Input Leakage<br>Current                          | lu                         | $0 \text{ V} \le \text{ V}_{\text{IN}} \le \text{ V}_{\text{DDQ}},$<br>All other pins not under test = $0 \text{ V}$                                                           |                             | - 5                    | 5     | μА   |  |

| Output Leakage<br>Current                         | ILO                        | 0 V ≤ V <sub>IN</sub> ≤ V <sub>DDQ</sub> , Data out disabled                                                                                                                   |                             | - 5                    | 5     | μА   |  |

| Operating One Bank<br>Active-Precharge<br>Current | I <sub>DD0</sub>           | trc = trc min, tcк = tcк min, CKE = Viн, addresses inputs are SWITCHING; data bus inputs are STABLE                                                                            | CS = V <sub>IH</sub>        | _                      | 65    | mA   |  |

| Precharge Standby Current                         | I <sub>DD2P</sub>          | All banks idle, CKE = V <sub>IL</sub> ,  CS = V <sub>IH</sub> , tck = tck min, address and control inputs are                                                                  | Tj ≤ + 105 °C               | _                      | 3     | mA   |  |

|                                                   | IDDZF                      | SWITCHING;<br>data bus inputs are STABLE                                                                                                                                       | Tj ≤ + 125 °C               | _                      | 5     |      |  |

|                                                   | I <sub>DD2N</sub>          | All banks idle, CKE = V <sub>IH</sub> ,<br>CS = V <sub>IH</sub> , tc <sub>K</sub> = tc <sub>K</sub> min,<br>address and control inputs are SWITC<br>data bus inputs are STABLE | CHING;                      | _                      | 15    | mA   |  |

| Operating Burst Read                              | I <sub>DD4R</sub>          | One bank active, BL = 4,<br>tcκ = tcκ min,<br>Output pin open, Gapless data,                                                                                                   | Tj ≤ + 105 °C               | _                      | 300   | mA   |  |

| Current                                           | IDD4R                      | address inputs are SWITCHING; 50% data change each burst transfer                                                                                                              | Tj ≤ + 125 °C               | _                      | 280   | IIIA |  |

| Operating Burst Write                             |                            | One bank active, BL = 4,<br>tcκ = tcκ min, Gapless data,                                                                                                                       | Tj ≤ + 105 °C               | _                      | 330   | A    |  |

| Current                                           | IDD4W                      | address inputs are SWITCHING; 50% data change each burst transfer                                                                                                              | Tj ≤ + 125 °C               | _                      | 305   | - mA |  |

| Auto Refresh Current                              | I <sub>DD5</sub>           | trc = trrc min, tcк = tcк min, CKE = VIH, address and control inputs are SWITC data bus inputs are STABLE                                                                      | ntrol inputs are SWITCHING; |                        | 120   | mA   |  |

#### (Continued)

| Doromotor Sum              | Symbol           | Condition                                                                                                                     | Val  | I Incia |      |

|----------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------|------|---------|------|

| Parameter Symbol           |                  | Condition                                                                                                                     | Min. | Max.    | Unit |

| Self Refresh Current       | I <sub>DD6</sub> | CKE = V <sub>IL</sub> , $\overline{CS}$ = V <sub>IL</sub> , address and control inputs are STABLE; data bus inputs are STABLE | _    | 4       | mA   |

| Deep Power Down<br>Current | I <sub>DD8</sub> | address and control inputs are STABLE;<br>data bus inputs are STABLE                                                          | _    | 20      | μА   |

Notes: • All voltages are referenced to Vss.

- After power on, initialization following power-up timing is required. DC characteristics are guaranteed after the initialization.

- IDD depends on the output termination or load condition, clock cycle rate, signal clocking rate. The specified values are obtained with the output open condition.

#### 2. AC Characteristics

(Under recommended operating conditions unless otherwise noted)\*1,\*2

| Parameter (Under recommen                                  |           |               | •              | <del>'</del>          | Value |               |  |

|------------------------------------------------------------|-----------|---------------|----------------|-----------------------|-------|---------------|--|

|                                                            |           |               | Symbol         | Min.                  | Max.  | Unit          |  |

| DQ Output Access Time from CK/CK (tck = tck min)*3, *4, *7 |           |               | <b>t</b> AC    | 2                     | 6     | ns            |  |

| DQS Output Access Time from C                              | CK/CK *3, | *4            | <b>t</b> DQSCK | 2                     | 6     | ns            |  |

| Clock High Level Width *3                                  |           |               | <b>t</b> cH    | 2                     | _     | ns            |  |

| Clock Low Level Width *3                                   |           |               | <b>t</b> cL    | 2                     | _     | ns            |  |

| Delay between CK and CK *4                                 |           |               | <b>t</b> DC    | 0.45                  | 0.55  | <b>t</b> cĸ   |  |

|                                                            | CL = 2    |               |                | 15                    |       |               |  |

| Clock Cycle Time                                           | CL = 3    |               | to             | 7.4                   |       | 200           |  |

| Clock Cycle Time                                           | CL = 4    | Tj ≤ + 105 °C | <b>t</b> ck    | 4.6                   | _     | ns            |  |

|                                                            | CL = 4    | Tj ≤ + 125 °C |                | 5                     |       |               |  |

| DO and DM Input Satur Time                                 |           | Tj ≤ + 105 °C | <b>t</b>       | 0.4                   |       | 20            |  |

| DQ and DM Input Setup Time                                 |           | Tj ≤ + 125 °C | <b>t</b> DS    | 0.5                   | _     | ns            |  |

| DO and DM Input Hold Time                                  |           | Tj ≤ + 105 °C | tou            | 0.4                   | _     | ns            |  |

| DQ and DM Input Hold Time                                  |           | Tj ≤ + 125 °C | <b>t</b> DH    | 0.5                   | _     | ns            |  |

| DQ and DM Input Pulse Width                                |           |               | <b>t</b> DIPW  | 0.35                  | _     | <b>t</b> cĸ   |  |

| Address and Control Input Setup                            | Time *3   |               | <b>t</b> ıs    | 0.9                   | _     | ns            |  |

| Address and Control Input Hold Time *3                     |           |               | tıн            | 0.9                   | _     | ns            |  |

| Address and Control Input Pulse                            | Width     |               | <b>t</b> IPW   | 0.6                   | _     | <b>t</b> cĸ   |  |

| DQ Low-Z Time from CK/CK *3, *                             | 5         |               | <b>t</b> LZ    | 0                     | _     | ns            |  |

| DQ High-Z Time from CK/CK *3, *                            | 5, *6     |               | <b>t</b> HZ    | _                     | 6     | ns            |  |

| DQS to DQ Skew*4                                           |           |               | <b>t</b> DQSQ  | _                     | 0.4   | ns            |  |

| DQ Output Hold Time from DQS                               | *3, *4    |               | <b>t</b> QH    | t <sub>DC</sub> - 0.5 | _     | ns            |  |

| WRIT Command to 1st DQS Late                               | ching Tra | nsition       | togss          | 0.75                  | 1.25  | <b>t</b> cĸ   |  |

| DQS Input High Level Width                                 |           |               | <b>t</b> DQSH  | 0.35                  | _     | <b>t</b> cĸ   |  |

| DQS Input Low Level Width                                  |           |               | <b>t</b> DQSL  | 0.35                  | _     | <b>t</b> cĸ   |  |

| DQS Falling Edge to CK Setup T                             | ïme       |               | toss           | 0.2                   | _     | <b>t</b> cĸ   |  |

| DQS Falling Edge Hold Time from CK                         |           |               | <b>t</b> DSH   | 0.2                   | _     | tск           |  |

| MRS Command Period                                         |           |               | <b>t</b> mrd   | 2                     | _     | <b>t</b> cĸ   |  |

| Write Preamble Setup Time                                  |           |               | twpres         | 0                     | _     | ns            |  |

| Write Preamble Time                                        |           |               | twpre          | 0.25                  | _     | <b>t</b> cĸ   |  |

| Write Postamble Time                                       |           |               | twpst          | 0.4                   | 0.6   | <b>t</b> cĸ   |  |

| Read Preamble Time                                         |           | CL = 2        | to             | 0.5                   | 1.1   | <b>t</b>      |  |

| TVEAU FIEAIIINIE TIITE                                     |           | CL = 3, 4     | <b>t</b> rpre  | 0.9                   | 1.1   | <b>- t</b> ск |  |

| Read Postamble Time                                        |           |               | <b>t</b> RPST  | 0.4                   | 0.6   | <b>t</b> cĸ   |  |

#### (Continued)

(Under recommended operating conditions unless otherwise noted)\*1, \*2

| Parameter                             |              | Symbol        | Value                   |      | Unit  |

|---------------------------------------|--------------|---------------|-------------------------|------|-------|

|                                       |              | Syllibol      | Min.                    | Max. | Offic |

| ACT to PRE, PALL Command Period *7    |              | <b>t</b> ras  | 37                      | 8000 | ns    |

| ACT to ACT Command Period (Same Bank  | x) *7        | <b>t</b> RC   | 59.2                    |      | ns    |

| REF to ACT, REF Command Period        |              | trefc         | 100                     | _    | ns    |

| ACT to READ or WRIT Command Period    |              | <b>t</b> RCD  | 20                      | _    | ns    |

| Precharge Period *7                   |              | <b>t</b> RP   | 18                      | _    | ns    |

| ACT to ACT Command Period (Other Bank | )            | <b>t</b> rrd  | 9.2                     | _    | ns    |

| Write Recovery Time                   |              | <b>t</b> wr   | 12                      | _    | ns    |

|                                       | CL = 2       | <b>t</b> dal  | 1 CLK + t <sub>RP</sub> | _    |       |

| Data Input to ACT, REF Command Period | CL = 3       |               | 2 CLK + trp             |      | ns    |

|                                       | CL = 4       |               | 3 CLK + trp             |      |       |

| Internal Write to READ Command Period |              | <b>t</b> wtr  | 9.2                     | _    | ns    |

| Average Refresh Berind *8             | Tj ≤ + 105°C | 1             | _                       | 3.9  | μs    |

| Average Refresh Period *8             | Tj ≤ + 125°C | <b>t</b> refi |                         | 0.97 |       |

| Avorago Pariodio Pofrach Interval     | Tj ≤ + 105°C | tref          | _                       | 16   | ms    |

| Average Periodic Refresh Interval     | Tj ≤ + 125°C |               |                         | 4    |       |

| Transition Time *9                    |              | tτ            |                         | 1    | ns    |

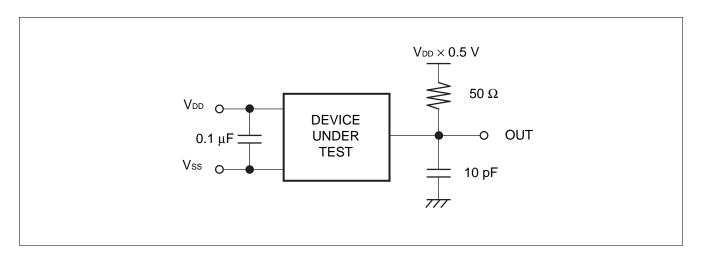

- \* 1: AC characteristics are measured after the Power up initialization procedure.

- \* 2: V<sub>DD</sub> × 0.5 is the reference level for 1.8 V I/O for measuring timing of input/output signals.

- \* 3: If input signal transition time (t<sub>T</sub>) is longer than 1 ns;  $[(t_T/2) 0.5]$  ns should be added to t<sub>AC</sub> (Max), t<sub>DQSCK</sub> (Max) and t<sub>HZ</sub> (max) spec values,  $[(t_T/2) 0.5]$  ns should be subtracted from t<sub>LZ</sub> (Min) and t<sub>QH</sub> (Min) spec values, and (t<sub>T</sub> 1.0) ns should be added to t<sub>CH</sub> (Min), t<sub>CL</sub> (Min), t<sub>IH</sub> (Min), t<sub>IH</sub> (Min), t<sub>DS</sub> (Min) and t<sub>DH</sub> (Min) spec values.

- \* 4: The data valid window is defined as toh tooso. The data valid window depends on toc which is defined between rising edge of CK and rising edge of CK. The data valid window is guaranteed when toc is satisfied.

- \* 5: tac, tbqsck, tlz and thz, are measured under output load circuit shown in " 3. Measurement Condition of AC Characteristics" in " ELECRTRICAL CHARACTERISTICS" and Driver Strength (DS) = Normal, Pre Driver Strength (PDS) = Fast are assumed.

- \* 6: Specified where output buffer is no longer driven.

- \* 7: The sum of actual clock count of tras and trap must be equal or greater than specified minimum trac.

- \* 8: This value is for reference only.

- \* 9: Transition times are measured between VIH (AC) min and VIL (AC) max.

#### 3. Measurement Condition of AC Characteristics

#### **■ TIMING DIAGRAMS**

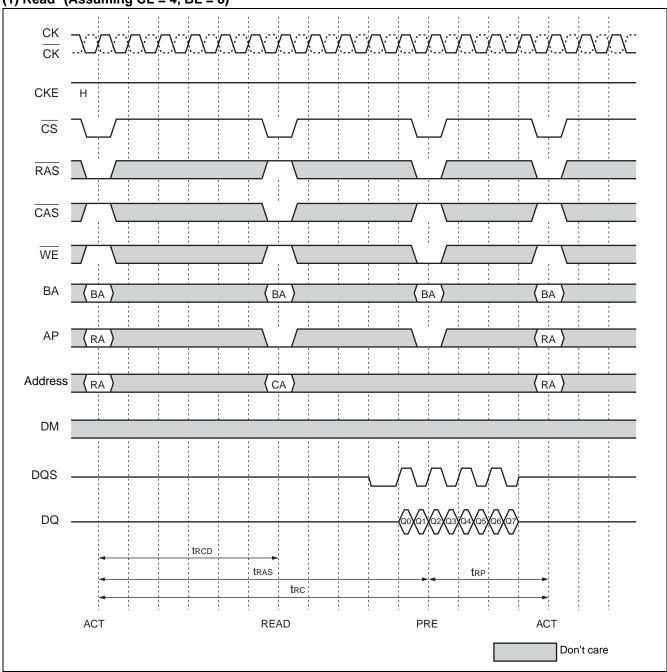

#### (1) Read\* (Assuming CL = 4, BL = 8)

<sup>\*:</sup> RA = Row Address, BA = Bank Address, CA = Column Address, AP = Auto Precharge

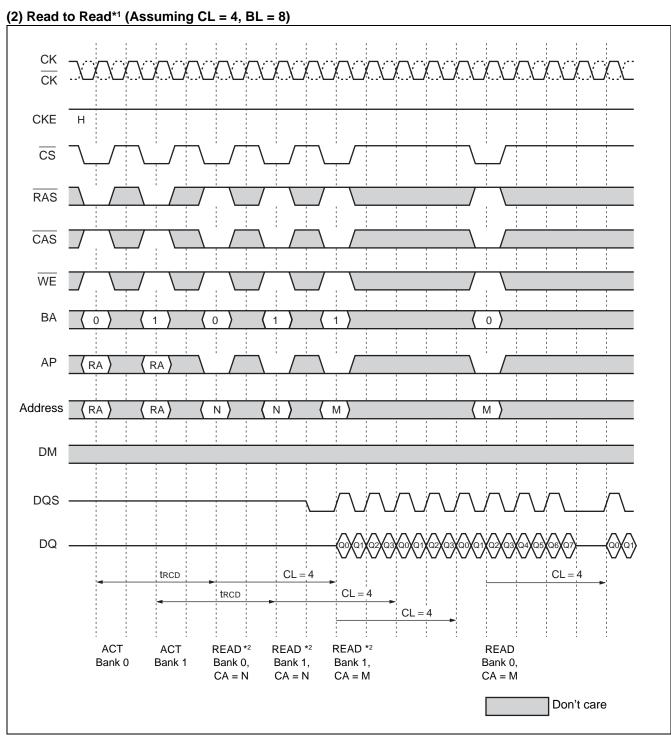

<sup>\*1:</sup> RA = Row Address, BA = Bank Address, CA = Column Address, AP = Auto Precharge

<sup>\*2:</sup> Previous burst read can be interrupted by subsequent burst read.

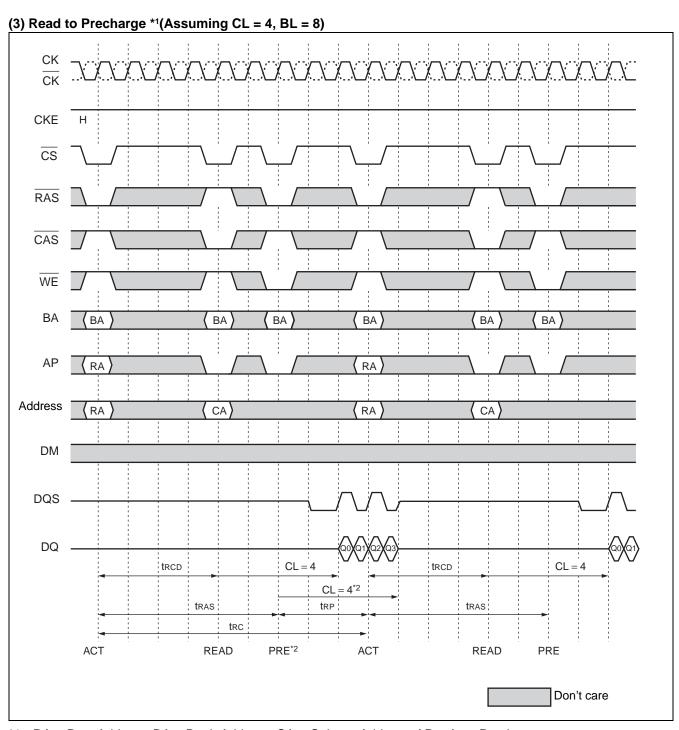

- \*1: RA = Row Address, BA = Bank Address, CA = Column Address, AP = Auto Precharge

- \*2: Burst read operation can be terminated by PRE command. All DQ pins become High-Z after CL from PRE command.

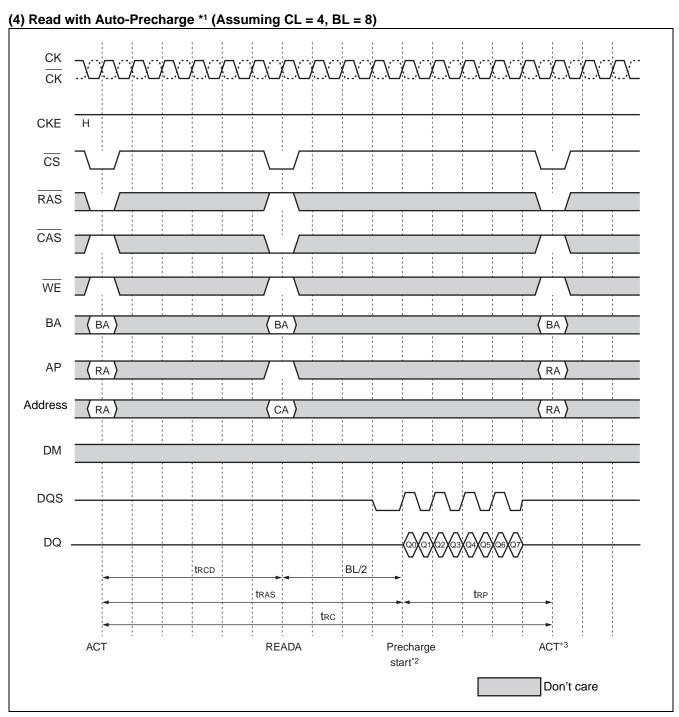

<sup>\*1:</sup> RA = Row Address, BA = Bank Address, CA = Column Address, AP = Auto Precharge

<sup>\*2:</sup> Internal precharge operation starts after BL/2 from READA command. tras must be satisfied.

<sup>\*3:</sup> Next ACT command can be issued after BL/2 + tRP from READA command. tRc must be satisfied.

\*1: RA = Row Address, BA = Bank Address, CA = Column Address, AP = Auto Precharge

<sup>\*2:</sup> Burst write operation should not be terminated by PRE command. PRE can be issued after 1 + BL/2 + twn from WRIT command.

\*1: RA = Row Address, BA = Bank Address, CA = Column Address, AP = Auto Precharge

<sup>\*2:</sup> Previous burst write can be interrupted by subsequent burst write.

\*1 : RA = Row Address, BA = Bank Address, CA = Column Address, AP = Auto Precharge

<sup>\*2 :</sup> Next ACT command can be issued after 1 + BL/2 + tDAL (Min) from WRITA command. tRC must be satisfied.

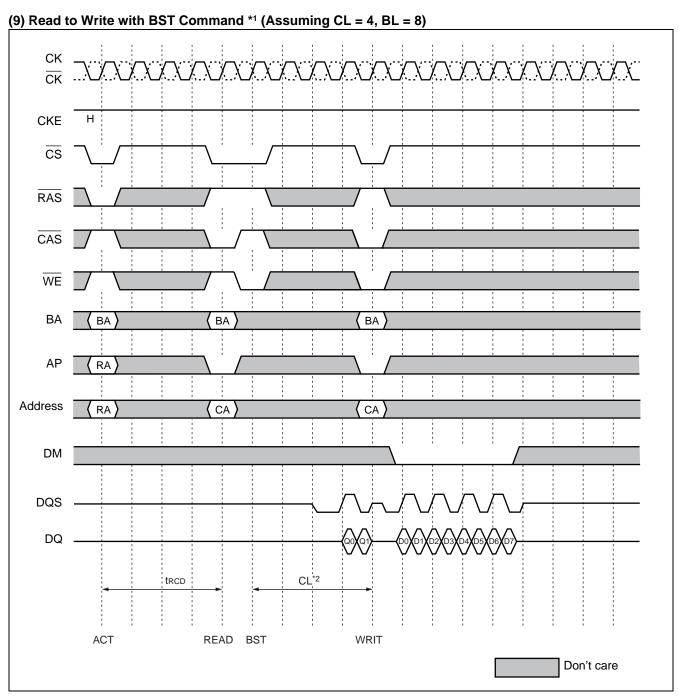

\*1 : RA = Row Address, BA = Bank Address, CA = Column Address, AP = Auto Precharge

<sup>\*2 :</sup> WRIT command can be issued after CL + BL/2 after READ command.

\*1 : RA = Row Address, BA = Bank Address, CA = Column Address, AP = Auto Precharge

<sup>\*2 :</sup> WRIT command can be issued after CL from burst read termination by BST command.

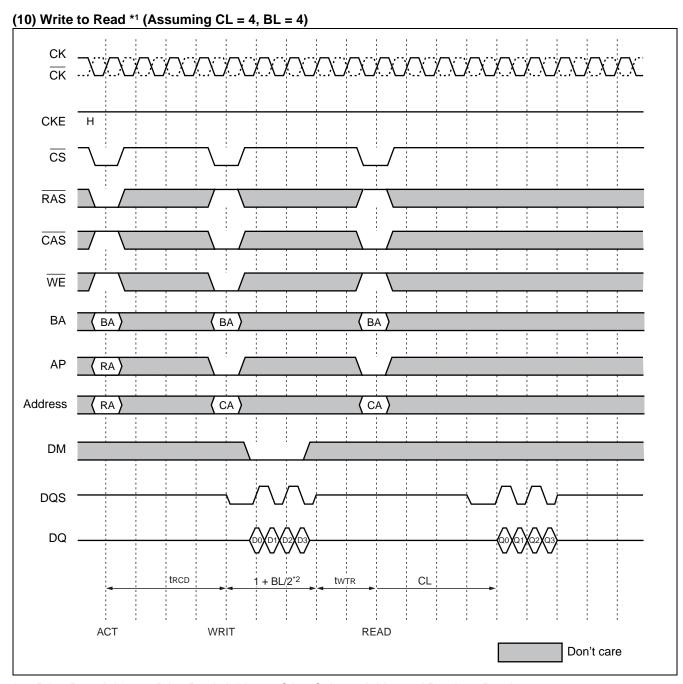

\*1 : RA = Row Address, BA = Bank Address, CA = Column Address, AP = Auto Precharge

<sup>\*2 :</sup> READ command can be issued after 1 + BL/2 + twrn from WRIT command.

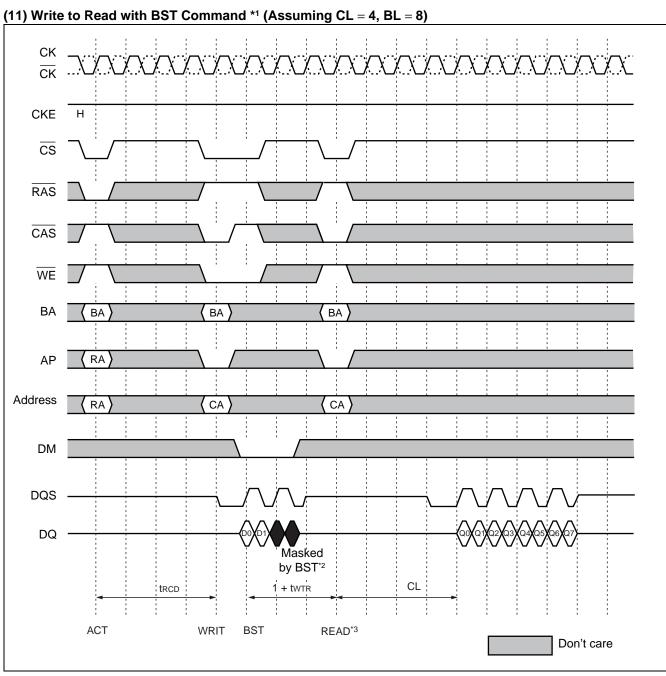

\*1 : RA = Row Address, BA = Bank Address, CA = Column Address, AP = Auto Precharge

<sup>\*2 :</sup> The data input after 1 clock from BST command will be masked.

<sup>\*3 :</sup> READ command can be issued after 1 + twtr from burst write termination by BST command.

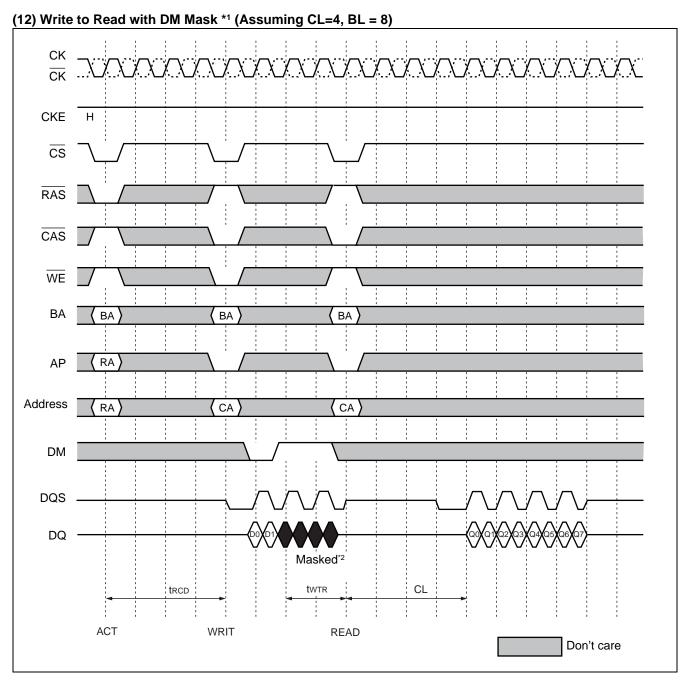

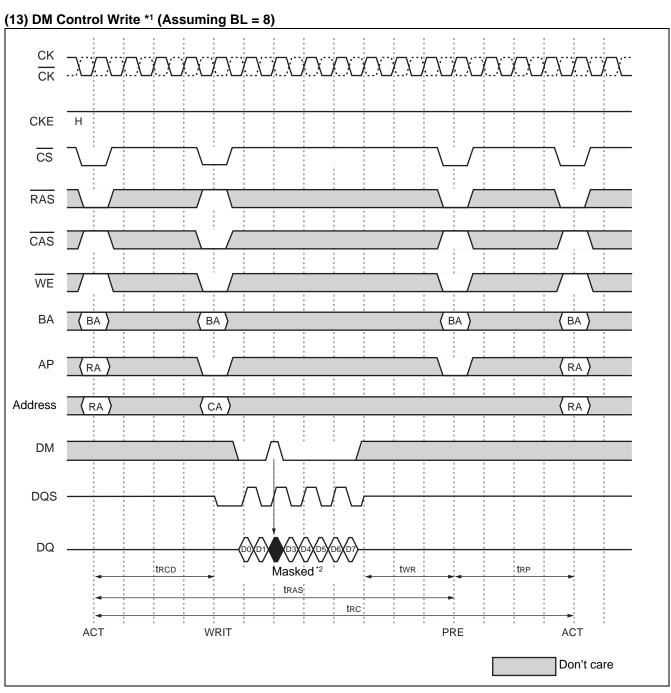

\*1 : RA = Row Address, BA = Bank Address, CA = Column Address, AP = Auto Precharge

<sup>\*2 :</sup> DM must be High during twTR from last pair of input data.

\*1 : RA = Row Address, BA = Bank Address, CA = Column Address, AP = Auto Precharge

<sup>\*2 :</sup> When DM is registered High, the corresponding data will be masked.

- \*1 : RA = Row Address, BA = Bank Address, AP = Auto Precharge

- \*2 : All banks must be precharged prior to the AUTO REFRESH command (REF).

- \*3: Either NOP or DESL command should be asserted during treec period.

- \*4 : ACT or MRS or REF command should be asserted after treet from REF command.

- \*1 : RA = Row Address, BA = Bank Address, AP = Auto Precharge

- \*2 : All banks must be precharged prior to SELF REFRESH ENTRY (SELF) command.

- \*3: SELF REFRESH EXIT (SELFX) command can be latched at the CK rising edge.

- \*4 : Either NOP or DESL command can be used during treer period.

- \*5 : CKE should be held High during treet period after SELFX command.

- \*1 : RA = Row Address, BA = Bank Address, AP = Auto Precharge

- \*2: MODE REGISTER SET (MRS) command must be asserted after all banks have been precharged and all DQ are in High-Z.

<sup>\*1 :</sup> RA = Row Address, BA = Bank Address, AP = Auto Precharge

DS05-11456-1E

49

<sup>\*2 :</sup> PD command can be issued after all DQ are in High-Z.

<sup>\*3 :</sup> ACT command can be issued after 1 clock from POWER DOWN EXIT (PDX) command.

<sup>\*:</sup> DEEP POWER DOWN ENTRY (DPD) Command can be issued after all banks have been precharged and all DQ are in High-Z.

<sup>\*1:</sup> RA = Row Address, BA = Bank Address, AP = Auto Precharge

<sup>\*2:</sup> Power up initialization procedure must be performed after DPDX command.

### **FUJITSU MICROELECTRONICS LIMITED**

Shinjuku Dai-Ichi Seimei Bldg., 7-1, Nishishinjuku 2-chome, Shinjuku-ku, Tokyo 163-0722, Japan

Tel: +81-3-5322-3329 http://jp.fujitsu.com/fml/en/

For further information please contact:

#### **North and South America**

FUJITSU MICROELECTRONICS AMERICA, INC. 1250 E. Arques Avenue, M/S 333

Sunnyvale, CA 94085-5401, U.S.A.

Tel: +1-408-737-5600 Fax: +1-408-737-5999

http://www.fma.fujitsu.com/

### **Europe**

FUJITSU MICROELECTRONICS EUROPE GmbH Pittlerstrasse 47, 63225 Langen, Germany Tel: +49-6103-690-0 Fax: +49-6103-690-122 http://emea.fujitsu.com/microelectronics/

#### Korea

FUJITSU MICROELECTRONICS KOREA LTD. 206 Kosmo Tower Building, 1002 Daechi-Dong, Gangnam-Gu, Seoul 135-280, Republic of Korea Tel: +82-2-3484-7100 Fax: +82-2-3484-7111 http://kr.fujitsu.com/fmk/

#### **Asia Pacific**

FUJITSU MICROELECTRONICS ASIA PTE. LTD. 151 Lorong Chuan, #05-08 New Tech Park 556741 Singapore Tel: +65-6281-0770 Fax: +65-6281-0220 http://www.fmal.fujitsu.com/

FUJITSU MICROELECTRONICS SHANGHAI CO., LTD. Rm. 3102, Bund Center, No.222 Yan An Road (E), Shanghai 200002, China Tel: +86-21-6146-3688 Fax: +86-21-6335-1605

http://cn.fujitsu.com/fmc/

FUJITSU MICROELECTRONICS PACIFIC ASIA LTD. 10/F., World Commerce Centre, 11 Canton Road, Tsimshatsui, Kowloon, Hong Kong

Tel: +852-2377-0226 Fax: +852-2376-3269

http://cn.fujitsu.com/fmc/en/

Specifications are subject to change without notice. For further information please contact each office.

#### All Rights Reserved.

The contents of this document are subject to change without notice.

Customers are advised to consult with sales representatives before ordering.

The information, such as descriptions of function and application circuit examples, in this document are presented solely for the purpose of reference to show examples of operations and uses of FUJITSU MICROELECTRONICS device; FUJITSU MICROELECTRONICS does not warrant proper operation of the device with respect to use based on such information. When you develop equipment incorporating the device based on such information, you must assume any responsibility arising out of such use of the information.

FUJITSU MICROELECTRONICS assumes no liability for any damages whatsoever arising out of the use of the information.

Any information in this document, including descriptions of function and schematic diagrams, shall not be construed as license of the use or exercise of any intellectual property right, such as patent right or copyright, or any other right of FUJITSU MICROELECTRONICS or any third party or does FUJITSU MICROELECTRONICS warrant non-infringement of any third-party's intellectual property right or other right by using such information. FUJITSU MICROELECTRONICS assumes no liability for any infringement of the intellectual property rights or other rights of third parties which would result from the use of information contained herein.

The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite).

Please note that FUJITSU MICROELECTRONICS will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products.

Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

Exportation/release of any products described in this document may require necessary procedures in accordance with the regulations of the Foreign Exchange and Foreign Trade Control Law of Japan and/or US export control laws.

The company names and brand names herein are the trademarks or registered trademarks of their respective owners.

Edited: Sales Promotion Department