Preliminary

# MB86613S IEEE1394 Open HCI Controller Product Specification Provisional

Revision 1.00, July 2, 2001

Fujitsu Limited Fujitsu VLSI Ltd.

#### 1. Introduction

#### **Related Documents**

This specification document was prepared based on the following documents:

- 1) IEEE1394- 1995 High Performance Serial Bus and P1394a draft2.0

- 2) 1394 Open Host Controller Interface (Open HCI) Specification Release1.1

- 3) PCI Local Bus Specification (Revision 2.2)

- 4) PCI Bus Power Management Specification (Version 1.1)

#### 1.1. Overview

MB86613S is Fujitsu's IEEE1394- OHCI (Open Host Controller Interface) Controller LSI that is compliant with IEEE1394- 1995, P1394a and OHCI (revision 1.1, release) standard drafts. This LSI integrates both 1394 PHY and LINK layers including analog PLL, transceiver, and comparator circuits using Fujitsu's advanced full CMOS process for the cost- effective single- chip solution.

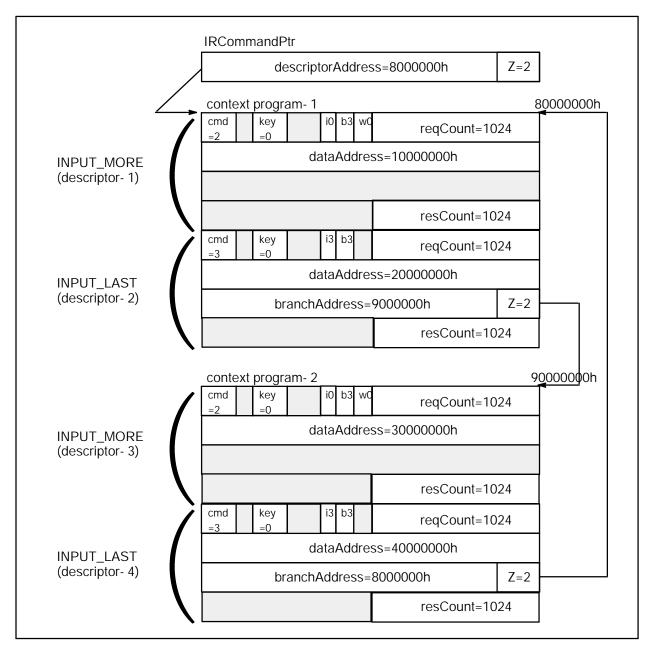

In addition to the 1394 block, the MB86613S contains various DMA engines called ContextProgram Controllers used for OHCI functions and PCI block. ContextProgram block consists of total 13 channels of independent DMA that are each dedicated to asynchronous and isochronous transmit and isochronous- asynchronous common receive operations. On- chip, 5V and 3.3V operable, PCI bus controller is compliant with PCI local bus standard (revision2.2) incorporating one 32- bit DMA controller and power management functions as specified in PCI bus power management specification (version 1.1).

For valuable host side design, this chip also incorporates serial Configuration ROM interface.

The device operates by +5V or +3.3V power supply for the PCI and DMA blocks and +3.3V for the whole 1394 block.

To provide with the cost- effective solution, the LSI is housed in a 100- pin plastic small QFP package.

## 1.2. Features

- 1) 1394 Serial Bus Controller Block:

- Compliant with IEEE1394-1995 and P1394a draft2.0

- Integrates PHY and LINK layers into single- chip.

- 1394 port number : 1 port

- Transfer Data Rate : \$100, \$200, and \$400

- On- chip PLL : 400MHz for PHY and 50MHz for Link core.

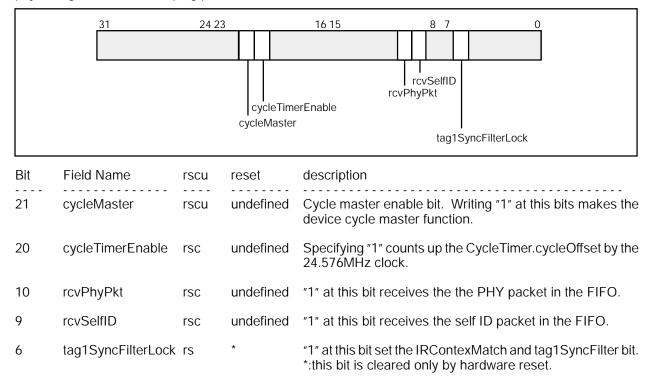

- Cycle- Master Function

- On- chip Bus Management CSRs

- 6- pin cable supported

- On- chip transceiver and comparator

- On- chip another comparator for detecting the cable power

- 2) ContextProgram Controller Block :

- Compliant with Open HCI standard draft (revision 1.1)

- Total 13 independent ContextProgram Controllers:

- a) Asynchronous Transmit DMA : 2 channels for response and request each

- b) Isochronous Transmit DMA : 4 channels

- c) Receive DMA : 7 channels for Asynchronous response and request each, 4 isochronous, and 1 self- ID receive

- On- chip 6KB FIFO :

- a) Asynchronous Transmit- FIFO : 1.5KB

- b) Isochronous Transmit- FIFO : 1.5KB

- c) Asynchronous/Isochronous Receive- FIFO : 3.0KB

- On- chip context program work memory : 128B x 3

- 3) PCI Bus Controller Block :

- Compliant with PCI local bus specification (revision 2.2)

- On- chip 32- bit DMA controller

- On- chip power management (PCI power management standard, revision 1.1, compliant)

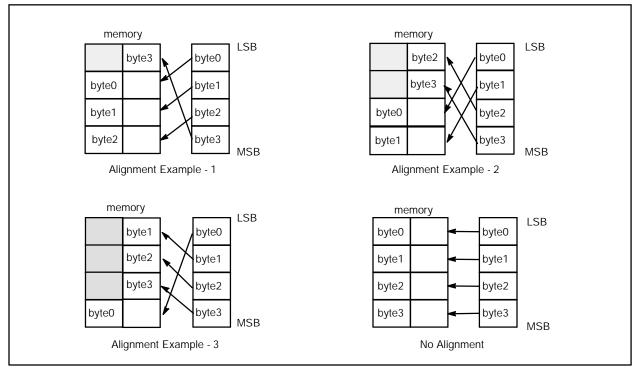

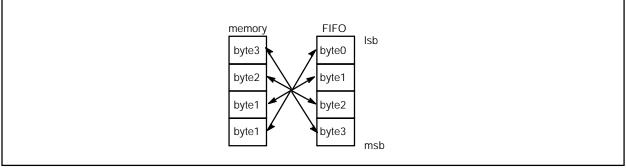

- Alignment function

- Byte swap function

- 33MHz operation

- On- chip serial ROM interface

- On- chip universal type (5V/3.3V) PCI buffer.

- 4) Others:

- -

- 100- pin plastic LQFP package

- Two power supply systems : +5V and +3.3V

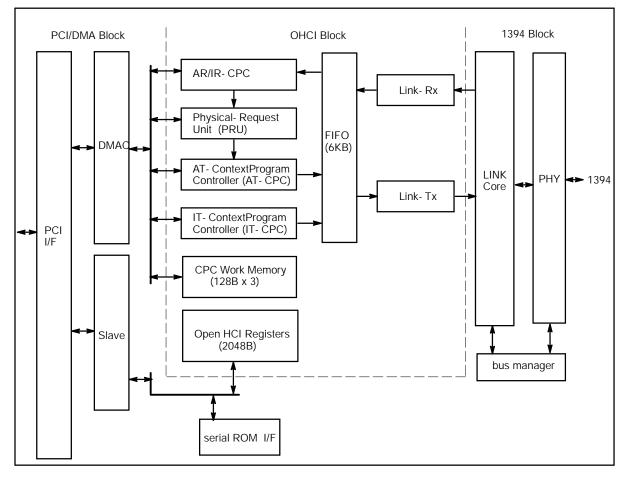

## 1.3. Block Diagram

## 1.4. Block Description

#### 1.5.1. PCI Block

PCI block consists of the following components :

(1) PCI Interface:

32- bit, 33MHz, PCI local bus interface compliant with PCI spec revision 2.2. This is the 5V/3.3V operable local bus interface with host side.

- (2) DMAC DMA bus master which is associated with the PCI interface.

- (3) Slave:

DMA slave mode controller which is used for the register access in response to the DMA bus master request.

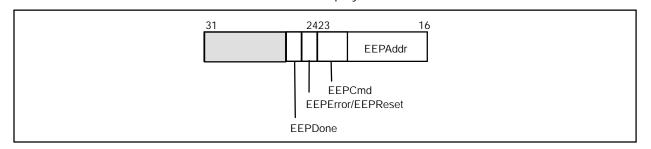

(4) Serial ROM Interface: This interface connects with an EEPROM (PCI Configuration ROM) containing various information such as PCI subsystem ID, and subsystem vendor ID.

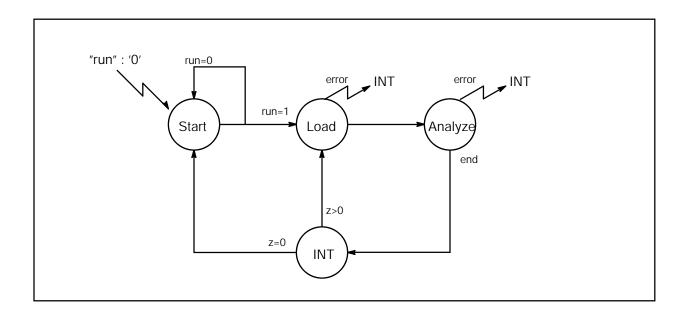

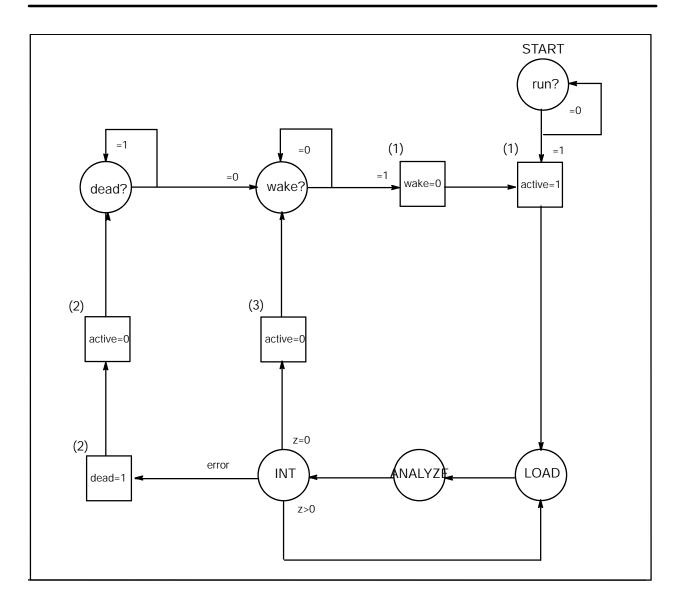

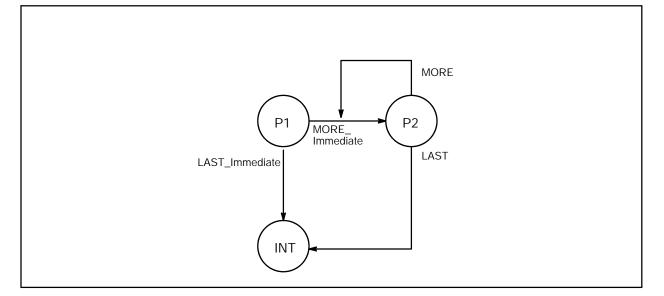

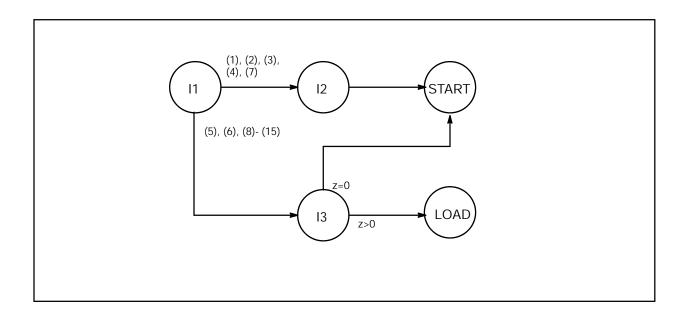

# 1.5.2. OHCI Block

OHCI block includes the powerful DMA engines for ContextProgram Control, work memory, FIFO, and LINK-Tx, - Rx sections:

ContextProgramController (CPC) : This controller is ContextProgram Processor Unit that analyzes the context programs stored in the system memory.

For Receive state, the on- chip R- CPC transfers the OHCI packet stored in the FIFO to the system memory via PCI interface. For Transmit state, the on- chip AT- , and IT- CPC transmit the packet stored in the system memory to the FIFO.

This section also includes a PHY Request Unit (PRU) which works for automatically decoding the physical request packet if received.

## 1.5.3. ContextProgram Work Memory (CP Work)

This block is work RAM area used for storing IT- , AT- , and, Receive- context program to be processed, and also storing header information on received physical request packet. The area is formed by 128B x 3 units of SRAM.

## 1.5.4. Open HCI Registers

This block contains total 2048- byte register set as defined in the Open HCI standard. For the register map, see Section 3 in this document.

## 1.5.5. FIFO

This is a 6Kbytes FIFO memory used for storing the packet received and to be transmitted. The internal area is divided, one for Asynchronous/Isochronous Transmit (AT- FIFO and IT- FIFO) and one for Asynchronous/ Isochronous Receive (R- FIFO).

## 1.5.6. LINK- Rx

This block is on OHCI- 1394 boundary that is placed between the internal FIFO and LINK core. LINK- Rx is responsible for adding the OHCI trailer data to the packet received by 1394 LINK core and storing into the FIFO.

#### 1.5.7. LINK- Tx

Similarly with LINK- Rx, this Link- Transmit section converts the OHCI packet stored in the FIFO by CPC into the 1394 format packet for the LINK core.

#### 1.5.8. LINK Core

This block generates the data CRC, header CRC, and also transmits self ID packets and controls packet transmit and receive.

#### 1.5.9. PHY

This block controls the 1394 serial bus protocol, including data encoding and bus arbitration.

#### 1.5.10. bus manager

This block manages the cycle timer, generates interrupts, and holds the bus management CSRs.

## 2. Pin Functions

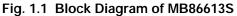

## 2.2. Pin Assignment

Figure 2.1 shows the MB86613S pin assignment.

Fig. 2.1 Pin Assignment

# 2.3. Pin Function

# 2.3.1. PCI Bus Interface

Notes:

I/O denotes input/output pin.O denotes output pin.I denotes input pin.OD denotes open- drain output pin.

| Name of pin | I/O | Function                                                                                                                                                                                                                                           |

|-------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCICLK      | I   | PCI bus clock input pin (Max. 33MHz)                                                                                                                                                                                                               |

| RST#        | I   | System reset input pin.                                                                                                                                                                                                                            |

| AD31 : 0    | I/O | 32- bit PCI Address/Data multiplexed pins.                                                                                                                                                                                                         |

| C/BE3# : 0# | I/O | PCI Bus Command / Byte Enable multiplexed pins.                                                                                                                                                                                                    |

| PAR         | I/O | Even Parity pin for AD31:0 and C/BE3#:0#. This pin state becomes valid after 1 PCICLK.                                                                                                                                                             |

| FRAME#      | I/O | Frame signal pin that indicates the PCI bus is driven by the master.                                                                                                                                                                               |

| IRDY#       | I/O | Data Ready signal pin for bus master device.                                                                                                                                                                                                       |

| TRDY#       | I/O | Data Ready signal pin for target device.                                                                                                                                                                                                           |

| STOP#       | I/O | Stop signal pin for the data transfer from target to master.                                                                                                                                                                                       |

| IDSEL       | I   | Chip select pin to access the configuration register.                                                                                                                                                                                              |

| DEVSEL#     | I/O | Device select pin. While the device is a target, this pin outputs the select signal that indicates the self device is selected. While the device is a master, this pin functions as an input pin to indicate that a device on the bus is selected. |

| REQ#        | 0   | Request signal output pin to the bus arbiter to request for the PCI bus use.                                                                                                                                                                       |

| GNT#        | I   | Grant signal input pin from the bus arbiter to receive the response to the REQ# signal.                                                                                                                                                            |

| PERR#       | I/O | Data Parity Error input/output pin.                                                                                                                                                                                                                |

| SERR#       | OD  | Address Parity Error output pin. (Open- drain type output pin.)                                                                                                                                                                                    |

| INTA#       | OD  | Interrupt output pin. (Open- drain type output pin.)                                                                                                                                                                                               |

|             |     |                                                                                                                                                                                                                                                    |

| PME#        | 0   | PCI power management enable                                                                                                                                                                                                                        |

# 2.3.2. Memory Interface

| Name of pin | I/O | Function                                                          |

|-------------|-----|-------------------------------------------------------------------|

| EEDI        | 0   | Data output pin for EEPROM device.                                |

| EEDO        | I   | Data input pin for EEPROM device.                                 |

|             |     |                                                                   |

|             |     |                                                                   |

|             |     |                                                                   |

| EECS        | 0   | Chip Select pin to select the externally connected EEPROM device. |

| EECLK       | 0   | Clock output pin for EEPROM device.                               |

# 2.3.3. 1394 Interface

| Name of pin | I/O | Function                                                                        |

|-------------|-----|---------------------------------------------------------------------------------|

| TPA         | I/O | TPA positive signals of 1394 cable port.                                        |

| ТРВ         | I/O | TPB positive signals of 1394 cable port.                                        |

| TPA#        | I/O | TPA negative signals of 1394 cable port.                                        |

| TPB#        | I/O | TPB negative signal of 1394 cable port.                                         |

| TPBIAS      | 0   | TP Bias voltage supply pin.                                                     |

| CPS         | I   | Cable Power input pin.                                                          |

| RO          | 0   | Load resistance connection pin (Connect with GND via a $5.1k\Omega$ . resistor) |

# 2.3.4. Others

| Name of pin | I/O | Function                                                                    |

|-------------|-----|-----------------------------------------------------------------------------|

| X1(CLK), X0 | I   | Clock input pin for the on- chip PLL (24.576MHz) or Crystal oscillator pins |

| RF          | 0   | Connect this pin with GND via a 5.1k $\Omega$ . resistor)                   |

| FIL         | 0   | Filter circuit connection pin.                                              |

|             |     |                                                                             |

| TEST        | I   | This pin is used for the test mode. Normally connect this pin with GND.     |

| N.C.        | -   | Non- connection pins. Do not connect with these pins.                       |

| C/BE | Command Type              | Target | Master |

|------|---------------------------|--------|--------|

| 0000 | Interrupt Acknowledge     | NO     | NO     |

| 0001 | Special Cycle             | NO     | NO     |

| 0010 | I/O Read                  | YES    | NO     |

| 0011 | I/O Write                 | YES    | NO     |

| 0100 |                           | -      |        |

| 0101 |                           |        |        |

| 0110 | Memory Read               | YES    | YES    |

| 0111 | Memory Write              | YES    | YES    |

| 1000 |                           |        |        |

| 1001 |                           |        |        |

| 1010 | Configuration Read        | YES    | NO     |

| 1011 | Configuration Write       | YES    | NO     |

| 1100 | Memory Read Multiple      | -      | YES    |

| 1101 | Dual Address Cycle        | NO     | NO     |

| 1110 | Memory Read Line          | -      | YES    |

| 1111 | Memory Write & Invalidate | NO     | YES    |

## Table 2.1 Supported PCI Bus Command

# 2.4. Connection Example with External Components

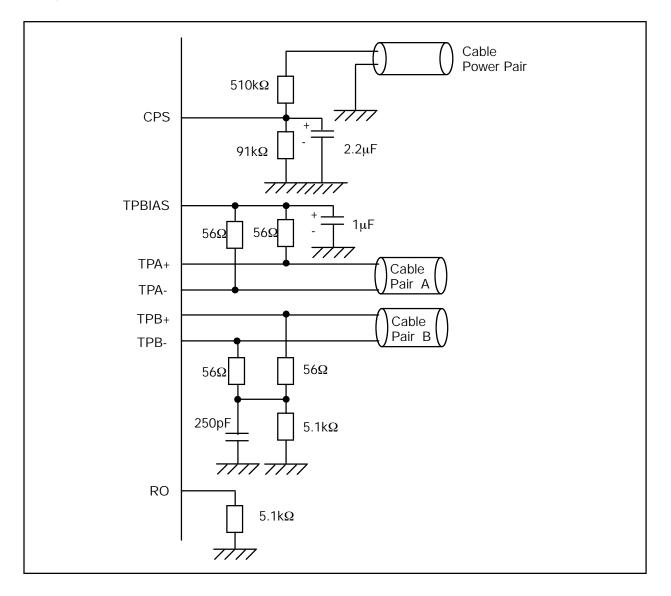

## 2.4.1. 1394 Port

Figure 2.2 shows an example of connection diagram on 1394 port.

CPS pin inputs a cable power divided by a 510k $\Omega$  and a 91k $\Omega$  resistors. Insert an 1µF capacitor between TPBIAS pin and GND and also the TPBIAS pin is to be connected with each TPA pin through a 56 $\Omega$  resistor. TPB and TPB# pins are connected with GND through 56 $\Omega$  resistors also. (a CR circuit composed of a 250pF and 5.1k $\Omega$  is further required between the 56 $\Omega$  resistor and GND.) RO pin is connected with GND through a 5.1k $\Omega$  resistor. TPA and TPB pins at the unused ports should be connected to GND, and TPBIAS pins to Open.

Those resistor and capacitor are reference values and does not guarantee stable operation on your application system.

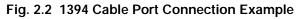

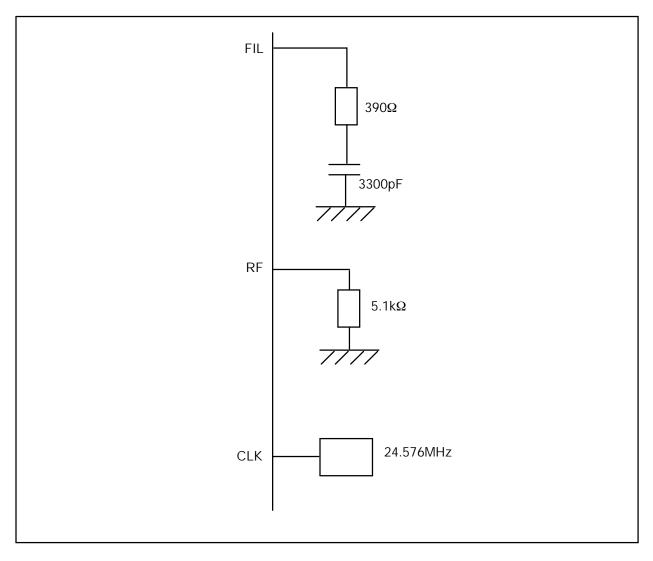

## 2.4.2. Filter Circuit

Figure 2.3 and 2.4 shows an example of connection diagram on PLL filter circuit. A circuit where the  $390\Omega$  and a 3300pF are connected is required between the FIL pin and GND. RF pin is connected with GND through a 5.1K $\Omega$  resister. The CLK pin requires a 24.576MHz of clock module operating at +3.3V. Pin39 must be open when using a external clock module. When using the crystal oscillator, connect it and capacitors as Figure 2.4.

Those resistor and capacitor are reference values and does not guarantee stable operation on your application system.

Fig. 2.3 PLL Filter Connection Example A

Fig. 2.4 PLL Filter Connection Example B

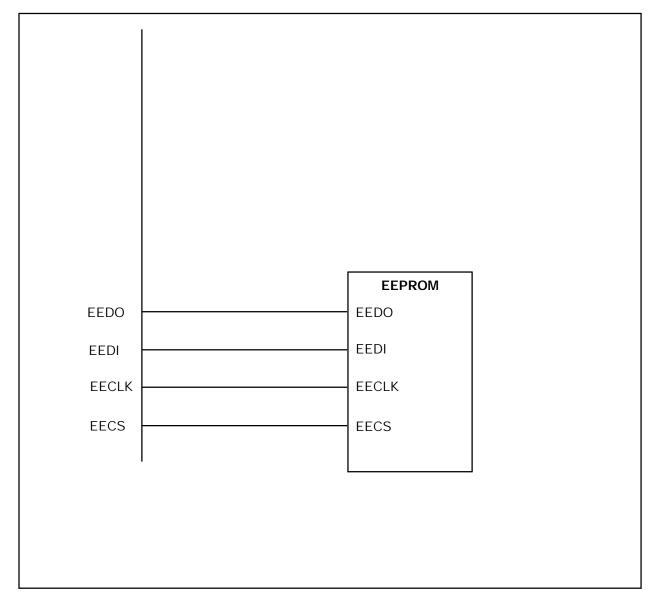

## 2.4.3. Memory Interface

Figure 2.5 shows connection diagram with external memory devices.

- a) EEPROM:

- ..... An external EEPROM is a mandatory device. For the EEPROM address mapping, see section xxx.

Fig. 2.5 Memory Interface Connection Diagram

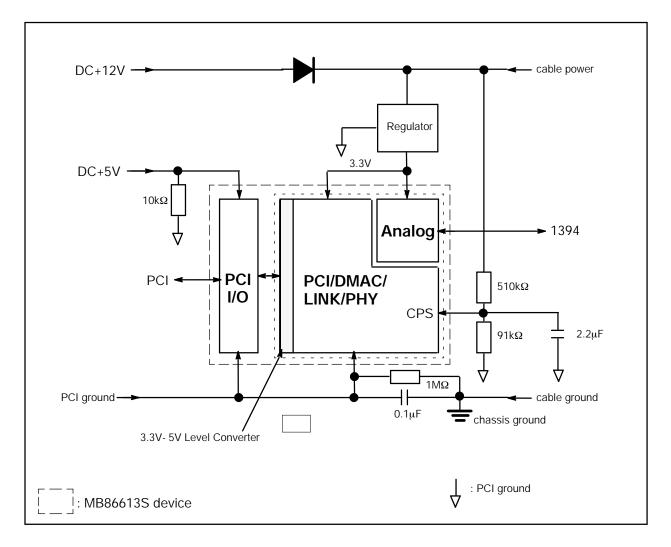

## 2.5. System Configuration Example

Figure 2.6 shows an example of MB86613S system configuration. This example assumes a system where it provides the cable power and also receives the cable power to activate even while the device is powered off. The device power supply voltage (3.3V) should be provided from DC+12V PCI or the cable power regulated. 5VDC is connected with PCI ground through a  $10K\Omega$  register.

Fig. 2.6 System Configuration Example

## 3. PCI Configuration Register

This section describes the on- chip PCI configuration registers.

"r" denotes the register that can be read out.

"w" denotes the register that can be written. "c" denotes the register whose value can be cleared to "0". "u" denotes the register whose value is undefined depending on the MB86613S device status.

| Dev    | ice ID        | Vende          | or ID           | 00h |

|--------|---------------|----------------|-----------------|-----|

| Stat   | us            | Comr           | nand            | 04h |

|        | Class C       | ode            | Revision ID     | 08h |

| BIST   | Header Type   | Latency Timer  | Cache Line Size | 0Ch |

|        | MEM Ba        | se Address     |                 | 10h |

|        |               |                |                 | 14h |

|        |               |                |                 | 18h |

|        |               |                |                 | 1Ch |

|        |               |                |                 | 20h |

|        |               |                |                 | 24h |

|        | CARDBU        | S CIS Pointer  |                 | 28h |

| Sub    | system ID     | Subsyster      | n Vendor ID     | 2Ch |

|        | Expansion RON | I Base Address |                 | 30h |

|        |               |                | Cap_Ptr         | 34h |

|        |               |                |                 | 38h |

| MAXLAT | MINGNT        | Interrupt Pin  | Interrupt Line  | 3Ch |

|        | PCI_HC        | CI Control     |                 | 40h |

## 3.1. Register Description

## 3.1.1. Vendor ID

| Bit | Field Name | rwcu | reset | description                                         |

|-----|------------|------|-------|-----------------------------------------------------|

|     | Vendor ID  |      |       | Indicates the PCI vendor ID. (Vendor ID = "10CF"h.) |

## 3.1.2. Device ID

| Bit   | Field Name | rwcu | reset | description          |

|-------|------------|------|-------|----------------------|

|       |            |      |       |                      |

| 31:16 | Device ID  | r    | 2010h | Device ID = "2010"h. |

## 3.1.3. Command

This register controls the MB86613S functions when generating and responding to the PCI cycle. Writing "0000"h at this register separate the device from PCI interface except for the configuration access.

|     |                   | 15 14 13 |       | 7 6 5 4 3 2 1 0<br>i/o_enable<br>memory_enable<br>master_enable<br>parity_err_enable<br>tepping_enable<br>enable |

|-----|-------------------|----------|-------|------------------------------------------------------------------------------------------------------------------|

| Bit | Field Name        | rwcu     | reset | description                                                                                                      |

| 8   | SERR_enable       | rw       | Ob    | 0 : Does not output SERR#.<br>1 : Outputs SERR# if a parity error is detected.                                   |

| 7   | stepping_enable   | r        | Ob    | Since the device does not support the stepping function, this bit always indicates "0".                          |

| 6   | parity_err_enable | rw       | 0b    | 0 : Does not output PERR#.<br>1 : Outputs PERR# if a parity error is detected.                                   |

| 4   | Invalidate_enable | rw       | Ob    | 0 : Uses memory write command.<br>1 : Uses memory write & invalidate command.                                    |

| 2   | master_enable     | rw       | 0b    | 0 : Prohibits the bus master operation.<br>1 : Allows the bus master operation.                                  |

| 1   | memory_enable     | rw       | 0b    | 0 : 0 : Prohibits the memory access.<br>1 : Allows the memory access.                                            |

| 0   | i/o_enable        | rw       | Ob    | 0 : Prohibits the I/O access.<br>1 : Allows the I/O access.                                                      |

## 3.1.4. Status

This register holds event status on PCI interface. When any of events occurred, please clear the bit corresponding to the event by writing "1" at that bit.

|       |                     | mas   | DEVSEL_tin<br>arget_abort<br>.asserted<br>cted | Capabilities_List                                                                                                                                         |

|-------|---------------------|-------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit   | Field Name          | rwcu  | reset                                          | description                                                                                                                                               |

| 31    | parity_err_detectec | d rcu | Ob                                             | This bit indicates "1" when a parity error occurs.                                                                                                        |

| 30    | SERR_asserted       | rcu   | Ob                                             | This bit indicates "1" when a system error occurs.                                                                                                        |

| 29    | master_abort        | rcu   | Ob                                             | This bit indicates "1" when detecting the master- abort and the transfer stops.                                                                           |

| 28    | target_abort        | rcu   | 0b                                             | This bit indicates "1" when detecting the target- abort and the transfer is stopped.                                                                      |

| 26:25 | DEVSEL_time         | r     | 01b                                            | Read out value from this bit is "01h". The contents of the bits reacts within 2 PCICLK after FRAME# asserted.                                             |

| 24    | PERR_asserted       | rcu   | Ob                                             | This bit indicates "1" when a parity error is detected, that is, when 'Command.parity_enable' bit is set and PERR# signal is output or PERR# is detected. |

| 23    | fast_target         | r     | 1b                                             | This bit indicates "1" because the device supports the high- speed back- to- back transfer.                                                               |

| 20    | Capabilities_List   | r     | 1b                                             | This bit indicates "1" because the device supports the PCI bus power management.                                                                          |

## 3.1.5. Revision ID

| Bit | Field Name | rwcu | reset | description                                             |

|-----|------------|------|-------|---------------------------------------------------------|

|     |            |      |       |                                                         |

| 7:0 | revision   | r    | 00h   | This bit indicates the device revision ID. It is "00h". |

## 3.1.6. Class Code

This register is used for identifying the MB86613S functions and programming interface. Each class code is read only field that displays the functional and programming interface information.

| base_class sub_class prog_if | 31         | 24 23     | 16 15   | 8 |

|------------------------------|------------|-----------|---------|---|

|                              | base_class | sub_class | prog_if |   |

|                              |            |           |         |   |

| Bit | Field Name                         | rwcu        | reset             | description                                                                                                                                                      |

|-----|------------------------------------|-------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |                                    |             |                   |                                                                                                                                                                  |

|     | base_class<br>sub_class<br>prog_if | r<br>r<br>r | 0Ch<br>00h<br>10h | These bits indicate "0Ch" for the serial bus controller.<br>These bits indicate "00h" for the IEEE1394 compliant.<br>These bits indicate "10h" for the Open HCI. |

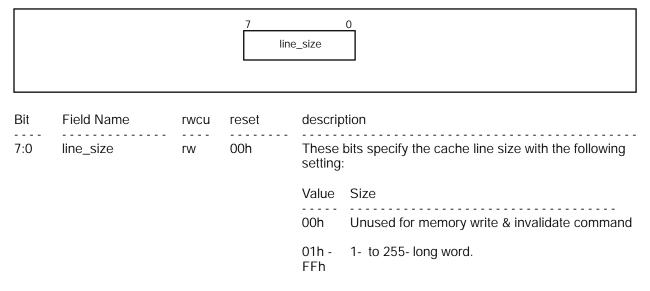

#### 3.1.7. Cache Line Size

This register specifies the cache line size in 32- bit long- word that is guaranteed for the memory write and invalidate command.

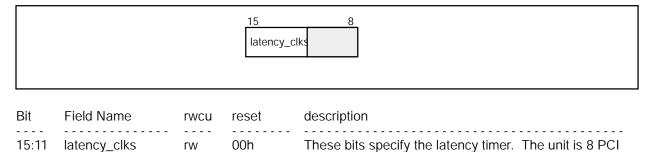

#### 3.1.8. Latency Timer

This register specifies the PCI latency timer value. The latency timer counts the time from the FRAME# asserted until the PCI bus occupied.

clocks.

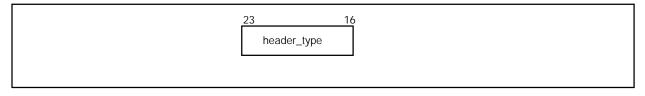

## 3.1.9. Header Type

This register indicates the register configuration at addresses 10h to 3Fh in configuration space and the supported function(s). MB86613S supports the single- function so this register indicates "00h".

#### Preliminary

| Bit | Field Name  | rwcu | reset | description                                                                   |

|-----|-------------|------|-------|-------------------------------------------------------------------------------|

|     | header_type |      | 00h   | These bits indicate the header type. "00h" is read out.<br>(Single- function) |

#### 3.1.10. BIST

This is a BIST control register. But the MB86613S does not support the BIST and so this register indicates "00h".

|       |            |       | 31    | BIST                                   |

|-------|------------|-------|-------|----------------------------------------|

| Bit   | Field Name | rwcu  | reset | description                            |

| 31:24 | BIST       | <br>r | 00h   | "00h" is read out. (No BIST supported) |

#### 3.1.11. MEM Base Address

This register specifies the base address for the Open HCI and debug registers' space used for memory command. When the debug register is enable the base address is defined in 4096- byte boundary. The first 4096- byte space is used for the Open HCI register and the second 2048- byte for the debug register.

|       | 31             | 24 23 | 3        | 1615 876543210                                                                                                                                                           |

|-------|----------------|-------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |                |       | re       | rg_mem_addr                                                                                                                                                              |

|       |                |       |          | mem_space<br>mem_space_type<br>prefetch                                                                                                                                  |

|       |                |       |          |                                                                                                                                                                          |

| Bit   | Field Name     | rwcu  | reset    | description                                                                                                                                                              |

| 31:10 | reg_mem_addr   | rw    | 00_0000h | These bits set the base address for the OHCI and debug<br>registers. (when debug- reg enabled: 4096- byte<br>boundary. when debug- reg disabled: 2048- byte<br>boundary) |

| 11    | reg_mem_addr   | rw    | Ob       | This bit is available only when the debug register is disable 0 is indicated for the debug register enabled.                                                             |

| 10:4  | reg_mem_addr   | r     | 00h      | "00h" is indicated. (Read only field)                                                                                                                                    |

| 3     | prefetch       | r     | Ob       | This bit indicates "0".                                                                                                                                                  |

| 2:1   | mem_space_type | r     | 00b      | These bits indicate "00". (i,e, 32- bit address width)                                                                                                                   |

| 0     | mem_space      | r     | 0b       | This bit indicates "0". (i.e., use the memory address.)                                                                                                                  |

## 3.1.12. CARDBUS CIS Pointer

This register indicates the head address for the EPROM (BIOS ROM) that contains the card bus information. When the device is released from a hardware reset, it automatically loads the required data from the externally connected EEPROM.

| 31         | 24 23 | 3     | 16 15       | 8 7         | 0           |             |

|------------|-------|-------|-------------|-------------|-------------|-------------|

|            |       |       | CIS_pointer |             |             |             |

|            |       |       |             |             |             |             |

|            |       |       |             |             |             |             |

| Field Name | rwcu  | reset | description |             |             |             |

|            |       |       |             | CIS_pointer | CIS_pointer | CIS_pointer |

undefined These bits indicate the CIS pointer.

#### 3.1.13. Subsystem

CIS\_pointer

r

31:0

This register indicates the subsystem and subsystem- vendor ID (product ID) to identify the MB86613S device when it is connected together with another device on the same add- on board. The data are automatically loaded from the external EEPROM when the chip is released from the hardware reset.

|       | 31 24               | 23      | 16 15 8 7 O                                    |           |

|-------|---------------------|---------|------------------------------------------------|-----------|

|       | subsy               | stem_ID | subsystem_vendor_ID                            |           |

|       |                     |         |                                                |           |

| Bit   | Field Name          | rwcu    | reset description                              |           |

| 31:16 | subsystem_ID        | r       | undefined These bits indicate the subsystem II | <br>Э.    |

| 15:0  | subsystem_vender_ID | r       | undefined These bits indicate the subsystem ve | endor ID. |

## 3.1.14. Expansion ROM Base Address

This register specifies the base address for the EPROM (BIOS ROM) device externally connected with the MB86613S device. The data are automatically loaded by the rom\_enable bit from the external EEPROM when the chip is released from the hardware reset.

|       | 31           | 24 23 |       | 16 15<br>rom_mem_addr                    | 8    | 7         |        |               |

|-------|--------------|-------|-------|------------------------------------------|------|-----------|--------|---------------|

|       |              |       |       |                                          |      |           | ror    | <br>m_enable  |

| Bit   | Field Name   | rwcu  | reset | description                              |      |           |        |               |

| 31:16 | rom_mem_addr | rw    | 0000h | These bits specify<br>(64K- byte boundar |      | ase addre | ss for | the BIOS ROM. |

| 15:1  | rom_mem_addr | r     | 0000h | These bits indicate                      | "00C | )0h".     |        |               |

| 0     | rom_enable   | rw    | Ob    | The specified base bit if the Command    |      |           |        |               |

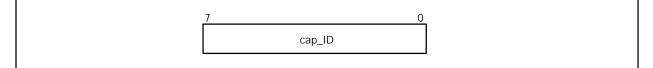

## 3.1.15. CAP\_PTR

This register indicates the address for "Capabilities Linked List" that exists in configuration space.

|     |                      |      | 7<br>capabilit | 0<br>ies_pointer                     |

|-----|----------------------|------|----------------|--------------------------------------|

| Bit | Field Name           | rwcu | reset          | description                          |

| 7:0 | capabilities_pointer | r    | undefined      | These bits indicate the CAP pointer. |

#### 3.1.16. Interrupt Line

This register indicates the interrupt line status.

| 7 0       |

|-----------|

| Intr_line |

|           |

|           |

| Bit | Field Name | rwcu | reset | description |                                                                                                                                                                                               |

|-----|------------|------|-------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | Intr_line  | rw   | 00h   |             | specify the connectivity between the device<br>and and host system interrupt signal with<br>g setting:<br>Connection<br>connects with any of IRQ0- 15.<br>reserve<br>unknown or no connection |

## 3.1.17. Interrupt Pin

This register indicates the interrupt pin usage.

|     |            |      | 15    | 8<br>Intr_pin |  |  |

|-----|------------|------|-------|---------------|--|--|

| Bit | Field Name | rwcu | reset | description   |  |  |

#### 3.1.18. MINGNT

This read- only register indicates burst time required for the device. The time is 1/4 micro seconds unit.

15:8 Intr\_pin r 01h These bits indicate "01h" (use the INTA#.)

|       |            |      | 23    | 16<br>Min_Gnt                    |

|-------|------------|------|-------|----------------------------------|

| Bit   | Field Name | rwcu | reset | description                      |

| 23:16 | Min_Gnt    | r    | 20h   | These bits indicate "20h" (8μs). |

#### 3.1.19. MAXLAT

This read- only register indicates PCI bus access time required for the device. The time is 1/4 micro seconds unit.

|     |            |       | 31    | 24<br>Max_Lat |  |  |

|-----|------------|-------|-------|---------------|--|--|

| Dit | Field Name | nucli | rocot | doscription   |  |  |

| Bit   | Field Name | rwcu | reset | description                       |

|-------|------------|------|-------|-----------------------------------|

|       |            |      |       |                                   |

| 31:24 | Max_Lat    | r    | 50h   | These bits indicate "50h" (20µs). |

## 3.1.20. PCI\_HCI Control

This register specifies the byte- swap control defined in the Open HCI specification.

|     | 31              | 24 23 | 3     | 16 15                              | 8 7 |    | 0                |

|-----|-----------------|-------|-------|------------------------------------|-----|----|------------------|

|     |                 |       |       |                                    |     |    |                  |

|     |                 |       |       |                                    |     | PC | I_Global_Swap    |

| Bit | Field Name      | rwcu  | reset | description                        |     |    |                  |

| 0   | PCI_Global_Swap | rw    | Ob    | Writing 1 at this accessed to/fror |     |    | wap for the data |

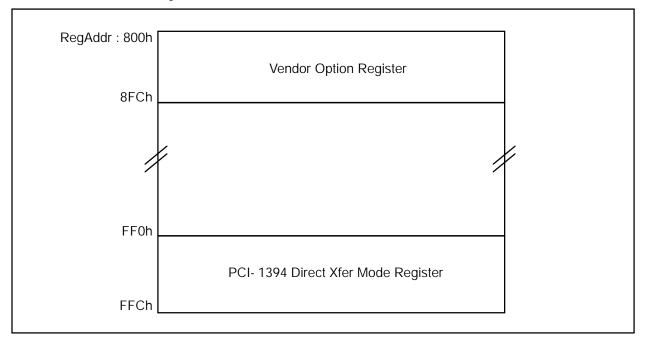

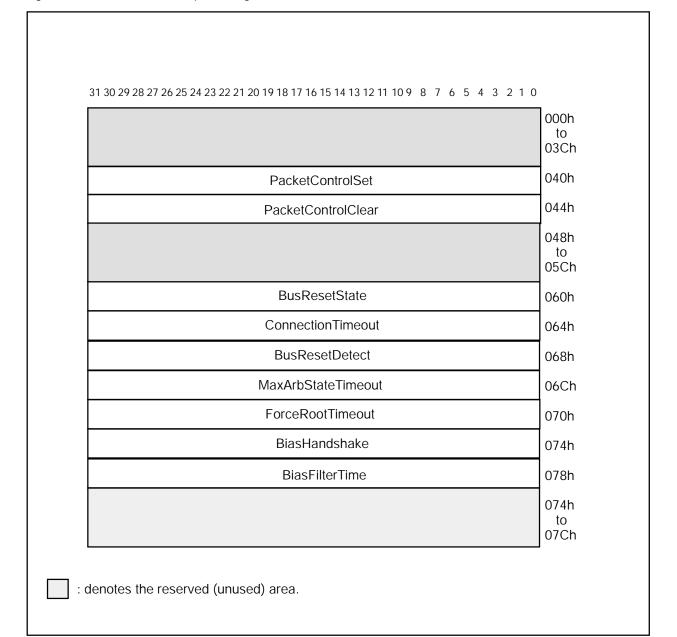

## 3.2. Open HCI Register

The addresses for the following listed Open HCI register set must be specified with the MEM Base Address register in the PCI configuration register.

r denotes the register can be read.

- w denotes the register can be written.

- s denotes the bit can be written (1b)

- c denotes the bit can be cleared (0b)

- u denotes the read value undefined depending on the MB86613S device status.

| 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 | _            |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------|--------------|--|--|--|--|--|--|

| Version                                                                               | 000h         |  |  |  |  |  |  |

| GUID_ROM                                                                              | 004h         |  |  |  |  |  |  |

| ATRetries                                                                             | 008h         |  |  |  |  |  |  |

| CSRData                                                                               | 00Ch         |  |  |  |  |  |  |

| CSRCompare                                                                            | 010h         |  |  |  |  |  |  |

| CSRControl                                                                            | 014h         |  |  |  |  |  |  |

| ConfigROMhdr                                                                          | 018h         |  |  |  |  |  |  |

| BusID                                                                                 | 01Ch         |  |  |  |  |  |  |

| BusOption                                                                             | 020h         |  |  |  |  |  |  |

| GUIDHi                                                                                | 024h         |  |  |  |  |  |  |

| GUIDLo                                                                                | 028h         |  |  |  |  |  |  |

|                                                                                       | 02Ch to 030h |  |  |  |  |  |  |

| ConfigROMMap                                                                          | 034h         |  |  |  |  |  |  |

| PostedWriteAddressLo                                                                  | 038h         |  |  |  |  |  |  |

| PostedWriteAddressHi                                                                  | 03Ch         |  |  |  |  |  |  |

| Vendor ID                                                                             | 040h         |  |  |  |  |  |  |

|                                                                                       | 044h to 04Ch |  |  |  |  |  |  |

| HCControlSet                                                                          | 050h         |  |  |  |  |  |  |

| HCControlClear                                                                        | 054h         |  |  |  |  |  |  |

|                                                                                       | 058h to 060h |  |  |  |  |  |  |

| SelfIDBuffer [Self ID]                                                                | 064h         |  |  |  |  |  |  |

| SelfIDCount [Self ID]                                                                 | 068h         |  |  |  |  |  |  |

|                                                                                       | 06Ch         |  |  |  |  |  |  |

|                                                                                       | J            |  |  |  |  |  |  |

|                                                                                       |              |  |  |  |  |  |  |

| (C : denotes the reserved (unused) area.                                              | ontinued)    |  |  |  |  |  |  |

|                                                                                       |              |  |  |  |  |  |  |

| 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 | 0            |

|-------------------------------------------------------------------------------------|--------------|

| IRMultiChanMaskHiSet                                                                | 070h         |

| IRMultiChanMaskHiClear                                                              | 074h         |

| IRMultiChanMaskLoSet                                                                | 078h         |

| IRMultiChanMaskLoClear                                                              | 07Ch         |

| IntEventSet                                                                         | 080h         |

| IntEventClear                                                                       | 084h         |

| IntMaskSet                                                                          | 088h         |

| IntMaskClear                                                                        | 08Ch         |

| IsoXmitIntEventSet                                                                  | 090h         |

| IsoXmitIntEventClear                                                                | 094h         |

| IsoXmitIntMaskSet                                                                   | 098h         |

| IsoXmitIntMaskClear                                                                 | 09Ch         |

| IsoRecvIntEventSet                                                                  | 0A0h         |

| IsoRecvIntEventClear                                                                | 0A4h         |

| IsoRecvIntMaskSet                                                                   | 0A8h         |

| IsoRecvIntMaskClear                                                                 | 0ACh         |

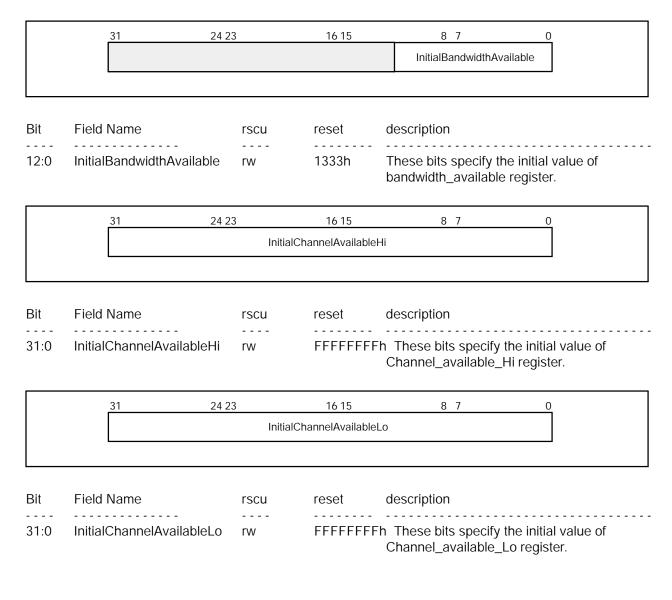

| InitialBandwidthAvailable                                                           | 0B0h         |

| InitialChannelsAvailableHi                                                          | 0B4h         |

| InitialChannelsAvailableLo                                                          | 0B8h         |

|                                                                                     | 0BCh to 0D8h |

| FairnessControl                                                                     | 0DCh         |

| LinkControlSet                                                                      | 0E0h         |

| LinkControlClear                                                                    | 0E4h         |

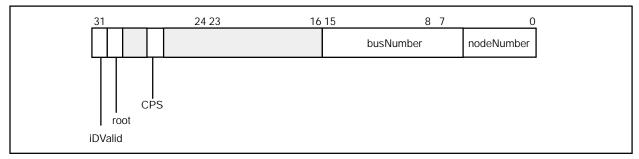

| NodeID                                                                              | 0E8h         |

| PhyControl                                                                          | 0ECh         |

| IsochronousCycleTimer                                                               | 0F0h         |

|                                                                                     | Continued)   |

| : denotes the reserved (unused) area.                                               |              |

FUJITSU

|                                                      | 0F4h<br>to<br>0FCh |

|------------------------------------------------------|--------------------|

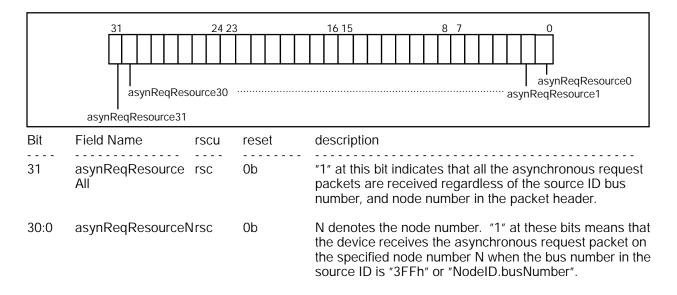

| AsynchronousRequestFilterHiSet                       | 100h               |

| AsynchronousRequestFilterHiClear                     | 104h               |

| AsynchronousRequestFilterLoSet                       | 108h               |

| AsynchronousRequestFilterLoClear                     | 10Ch               |

| PhysicalRequestFilterHiSet                           | 110h               |

| PhysicalRequestFilterHiClear                         | 114h               |

| PhysicalRequestFilterLoSet                           | 118h               |

| PhysicalRequestFilterLoClear                         | 11Ch               |

| PhysicalUpperBound                                   | 120h               |

|                                                      | 124h<br>to<br>17Ch |

| ContextControlSet [Asynchronous request transmit]    | 180h               |

| ContextControlClear [Asynchronous request transmit]  | 184h               |

|                                                      | 188h               |

| CommandPtr [Asynchronous request transmit]           | 18Ch               |

|                                                      | 190h<br>to<br>19Ch |

| ContextControlSet [Asynchronous response transmit]   | 1A0h               |

| ContextControlClear [Asynchronous response transmit] | 1A4h               |

|                                                      | 1A8h               |

| CommandPtr [Asynchronous response transmit]          | 1ACh               |

|                                                      | 1B0h<br>to<br>1BFh |

| ContextControlSet [Asynchronous request receive]     | 1C0h               |

| : denotes the reserved (unused) area.                | (Continued)        |

| ContextControlClear [Asynchronous request receive]   | 1C4h               |

|------------------------------------------------------|--------------------|

|                                                      | 1C8h               |

| CommandPtr [Asynchronous request receive]            | 1CC                |

|                                                      | 1D0r<br>to<br>1DFr |

| ContextControlSet [Asynchronous response receive]    | 1E0ł               |

| ContextControlClear [Asynchronous response receive]  | 1E4h               |

|                                                      | 1E8h               |

| CommandPtr [Asynchronous response receive]           | 1ECI               |

|                                                      | 1F0h<br>to<br>1FCh |

| ContextControlSet [Isochronous transmit- context0]   | 200h               |

| ContextControlClear [Isochronous transmit- context0] | 204h               |

|                                                      | 208h               |

| CommandPtr [Isochronous transmit- context0]          | 20Cł               |

| ContextControlSet [Isochronous transmit- context1]   | 210h               |

| ContextControlClear [Isochronous transmit- context1] | 214h               |

|                                                      | 218h               |

| CommandPtr [Isochronous transmit- context1]          | 21Cł               |

| ContextControlSet [Isochronous transmit- context2]   | 220h               |

| ContextControlClear [Isochronous transmit- context2] | 224h               |

|                                                      | 228h               |

| CommandPtr [Isochronous transmit- context2]          | 22Cł               |

| ContextControlSet [Isochronous transmit- context3]   | 230h               |

| ContextControlClear [Isochronous transmit- context3] | 234h               |

|                                                      | 238h               |

FUJITSU

| 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 |             |

|---------------------------------------------------------------------------------|-------------|

| CommandPtr [Isochronous transmit- context3]                                     | 23Ch        |

|                                                                                 | 240h<br>to  |

|                                                                                 | 3FCh        |

| ContextControlSet [Isochronous receive- context0]                               | 400h        |

| ContextControlClear [Isochronous receive- context0]                             | 404h        |

|                                                                                 | 408h        |

| CommandPtr [Isochronous receive- context0]                                      | 40Ch        |

| ContextMatch [Isochronous receive- context0]                                    | 410h        |

|                                                                                 | 414h<br>to  |

|                                                                                 | 41Ch        |

| ContextControlSet [Isochronous receive- context1]                               | 420h        |

| ContextControlClear [Isochronous receive- context1]                             | 424h        |

|                                                                                 | 428h        |

| CommandPtr [Isochronous receive- context1]                                      | 42Ch        |

| ContextMatch [Isochronous receive- context1]                                    | 430h        |

|                                                                                 | 434h        |

|                                                                                 | to<br>43Ch  |

| ContextControlSet [Isochronous receive- context2]                               | 440h        |

| ContextControlClear [Isochronous receive- context2]                             | 444h        |

|                                                                                 | 448h        |

| CommandPtr [Isochronous receive- context2]                                      | 44Ch        |

| ContextMatch [Isochronous receive- context2]                                    | 450h        |

|                                                                                 | 454h        |

|                                                                                 | to<br>45Ch  |

| ContextControlSet [Isochronous receive- context3]                               | 460h        |

| ContextControlClear [Isochronous receive- context3]                             | 464h        |

|                                                                                 | (Continued) |

| : denotes the reserved (unused) area.                                           |             |

|                                              | 468h               |

|----------------------------------------------|--------------------|

| CommandPtr [Isochronous receive- context3]   | 46Ch               |

| ContextMatch [Isochronous receive- context3] | 470h               |

|                                              | 474h<br>to<br>7FCh |

## 3.2.1. Version

Г

This register indicates the revised edition number of the Open HCI Specification. "01h" is indicated in the version field and "10h" in the revision field. Normally "1b" is indicated in the GUIDE\_ROM bit because the data in the GUIDE ROM are loaded automatically with the Global Unique ID register.

|             | 31                  | 24.2      | 3         | 16  | 15                                                 | 8   | 7              | 0               |

|-------------|---------------------|-----------|-----------|-----|----------------------------------------------------|-----|----------------|-----------------|

|             |                     |           | version   |     |                                                    |     | revision       |                 |

|             |                     | <br>GUID_ | ROM       |     |                                                    |     |                |                 |

| Bit         | Field Name          | rwu       | reset     | des | cription                                           |     |                |                 |

| 24<br>23:16 | GUID_ROM<br>version | r<br>r    | 1b<br>01h | The | is indicated.<br>se bits indicate "(<br>compliant. | 011 | n" which means | the 1394A draft |

| 7:0         | revision            | r         | 10h       | The | se bits indicate "<br>compliant.                   | 001 | n" which means | the 1394A draft |

# 3.2.2. GUID\_ROM

This is a port type register to read out the data that the GUID ROM contains. This register is not supported.

|              | 31                | 24 2    | 3          | 16 15                                     | 8 | 7 0     |

|--------------|-------------------|---------|------------|-------------------------------------------|---|---------|

|              |                   |         | rdData     |                                           |   | miniROM |

|              | addrReset         | rdStart |            |                                           |   |         |

| Bit          | Field Name        | rscu    | reset      | description                               |   |         |

| 31           | addrReset         | r       | Ob         | "0b" is indicated.                        |   |         |

| 25           | rdStart           | r       | 0b         | "0b" is indicated.                        |   |         |

| 23:16<br>7:0 | rdData<br>miniROM | r<br>r  | 00h<br>00h | "00h" is indicated.<br>"00h" is indicated |   |         |

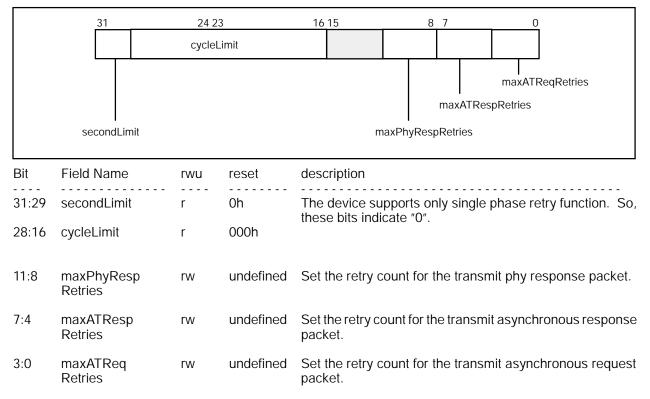

## 3.2.3. ATRetries

This register sets the retry count when transmitting the asynchronous packet or receiving the "ack\_busy\_#" or "ack\_data\_error" acknowledge. The register performs the retries of the count set here when the received acknowledge is "ack\_busy\_#" or "ack\_data\_error". "0" are indicated on the secondLimit and the cycleLimit fields respectively because the MB86613S does not support the dual phase relay.

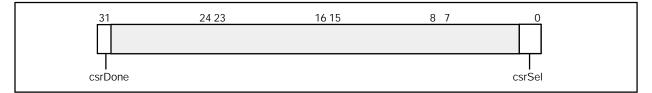

## 3.2.4. Bus Management CSR

This register is used for making the device operate the automatic compare- swap for the on- chip bus management CSR while the MB86613S device is operating as the resource manager. This register is used as follows:

Store the data that you want to set in the bus management CSR in the csrData. Then, store the data to be compared with the bus management CSR in the csrCompare. After that, select any of register for the bus management CSR by csrSel bit. At that time, the csrDone bit is cleared.

With these steps, if the compare- swap is completed, "1" is indicated in the csrDone bit. At that time, the csrData indicate the data previously stored in the bus management CSR which has been selected by the csrSel bit. This means, if the compare- swap is succeeded, the same data are read out from the csrData and csrCompare. In case the different data are read out from these bits, please set the data read out from the csrData in the csrCompare and repeat the same steps as above.

Bus reset loads '3Fh' to bus\_manager\_ID register and the following registers value to other three Bus management CSR registers.

| CSR Address       | csrSel | by Bus reset               | description           |

|-------------------|--------|----------------------------|-----------------------|

| "FFFF_F000_021Ch" | '00b'  | 3Fh                        | bus_manager_ID        |

| "FFFF_F000_0220h" | '01b'  | InitialBandwidthAvailable  | bandwidth_available   |

| "FFFF_F000_0224h" | '10b'  | InitialChannelsAvailableHi | channels_available_hi |

| "FFFF_F000_0228h" | '11b'  | InitialChannelsAbailableLo | channels_available_lo |

| 31      | 24 23 | 16 15   | 87 | 0 |  |

|---------|-------|---------|----|---|--|

|         |       | csrData |    |   |  |

| <u></u> |       |         |    |   |  |

|         |       |         |    |   |  |

| Bit | Field Name | rwu | reset | description                                         |

|-----|------------|-----|-------|-----------------------------------------------------|

|     | csrData    | rwu |       | Store the data to be set in the bus management CSR. |

| Bit | Field Name | rwu | reset     | description                                                |

|-----|------------|-----|-----------|------------------------------------------------------------|

|     | csrCompare | rw  | undefined | Store the data to be compared with the bus management CSR. |

| Bit Field Name rwu reset description            |                                                                                                                                        |

|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| 31 csrDone ru '1b' This bit indica              | ates "1" when the compare is done.                                                                                                     |

| following sett<br>Value E<br>'OOb' k<br>'O1b' k | elect the bus management CSR with the<br>ting:<br>Bus Management CSR<br>bus_manager_ID<br>bandwidth_available<br>channels_available_hi |

## 3.2.5. Config ROM Header

This register stores and indicates the first data of the 1934 configuration ROM (off- set "FFFF\_F000\_0400h"). For the software reset state (HCControl.softReset), the current stored data are indicated.

| info length crc length rom crc value | info_length crc_length rom_crc_value |

|--------------------------------------|--------------------------------------|

| inite_tengui ete_tengui              |                                      |

## Preliminary

| Bit   | Field Name    | rwu | reset | description                                                                         |

|-------|---------------|-----|-------|-------------------------------------------------------------------------------------|

| 31:24 | info_length   | rw  | 00h   | Set the quadlet count of the bus_info_block included in the 1394 configuration ROM. |

| 23:16 | crc_length    | rw  | 00h   | Set the 1394 configuration ROM byte count in quadlet unit.                          |

| 15:0  | rom_crc_value | rw  | 0000h | Set the 1394 configuration ROM CRC.                                                 |

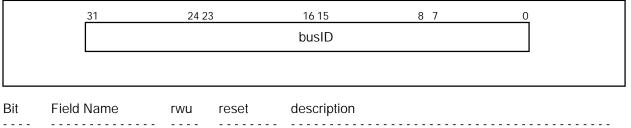

#### 3.2.6. Bus Identification

This register stores and indicates the first data of the bus\_Info\_block field in the 1934 configuration ROM (offset "FFFF\_F000\_0404h").

| DI   | i leiu Name | TVVU | 16361  | description                                                             |

|------|-------------|------|--------|-------------------------------------------------------------------------|

| 31:0 | busID       |      | 3133 _ | These bits indicate "3133_3934h" which means the "1394"d in ASCII code. |

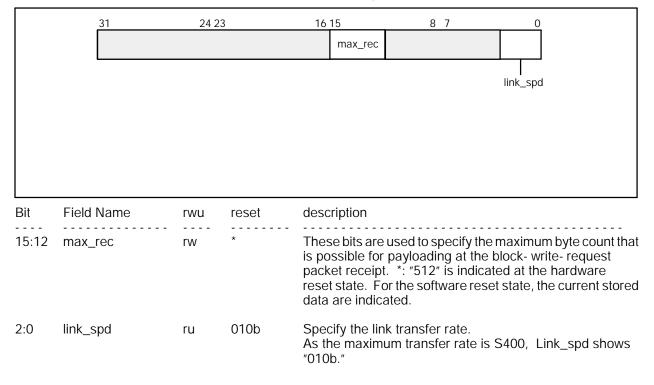

## 3.2.7. Bus Options

This register stores and indicates the second data of the bus\_Info\_block field in the 1934 configuration ROM (off- set "FFFF\_F000\_0404h"). The max\_rec field is available only when the HCControl.linkEnable bit is set. If a packet, which has the transmission speed over the setting, is received, it is invalid.

## 3.2.8. Global Unique ID

This register contains and indicates a part of data in bus\_info\_block of 1394 configuration ROM with FFFF\_F0000\_040C, 0410h offset. The data for vendor ID and chip ID contained in the externally connected EEPROM are loaded into this register after releasing from the hardware reset state. Yet the software reset does not flush the data and the register still holds the previous data.

|      | 31             | 24 23<br>node_vende |           | 16 15<br>dor_ID                 | 8    | 7 (<br>chip_ID_hi  |                |

|------|----------------|---------------------|-----------|---------------------------------|------|--------------------|----------------|

|      |                |                     |           |                                 |      |                    |                |

| Bit  | Field Name     | rwu                 | reset     | description                     |      |                    |                |

| 31:8 | node_vendor_ID | rw                  | undefined | 1394 OHCI vendor I              | D is | s loaded from the  | EEPROM.        |

| 7:0  | chip_ID_hi     | rw                  | undefined | The upper 8- bit code loaded.   | e o  | f chip ID included | d in EEPROM is |

|      | 31             | 24 23               | 3         | 16 15                           | 8    | 7                  |                |

|      |                |                     |           | chip_ID_lo                      |      |                    |                |

|      |                |                     |           |                                 |      |                    |                |

| Bit  | Field Name     | rwu                 | reset     | description                     |      |                    |                |

| 31:0 | chip_ID_lo     | rw                  | undefined | Load the lower 32- b<br>EEPROM. | it c | ode of chip ID in  | cluded in      |

## 3.2.9. Configuration ROM Mapping

This register specifies the base address for the 1394 configuration ROM space. However, since the first 20- byte (offset: FFFF\_F000\_0400- 0410h) in the ROM is built in the MB86613S, the specified value in this register has no meaning. The base address must be set to this register before setting the HCControl.linkEnable bit.

|       | 31            | 24 23 | 3            | 16 15                                | 8 7 | 0                    |

|-------|---------------|-------|--------------|--------------------------------------|-----|----------------------|

|       |               |       | configROMade | dr                                   |     |                      |

|       |               |       |              |                                      |     |                      |

|       |               |       |              |                                      |     |                      |

| Bit   | Field Name    | rwu   | reset        | description                          |     |                      |

| 31:10 | configROMaddr | rw    | undefined    | Specify the base a 1024- byte bounda |     | configuration ROM in |

#### 3.2.10. PostedWriteAddress

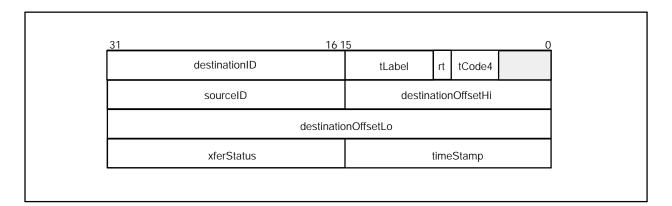

This register is used for storing and indicating the packet source ID and destinationOffset if a host bus error occurs while the payload data for received physical write request packet is storing into a host memory. This register is valid only when the HCControl.postedWriteEnable bit is set.

The structure of register is 4 FIFOs.

When a host bus error occurs, this register stores the packet source ID and destination offset. After that, IntEvent.PostedWriteErr bit is set. Software needs to take the following steps when the IntEvent.PostedWriteErr bit is set:

- 1) Read out the PostedWriteAddress\_Hi register.

- 2) Read out the PostedWriteAddress\_Lo register.

- 3) Clear the IntEvent.PostedWriteErr bit.

If the IntEvent.PostedWriteErr bit is still set, take the above steps repeatedly.

| Bit   | Field Name | rwu | reset     | description                                                                                                          |

|-------|------------|-----|-----------|----------------------------------------------------------------------------------------------------------------------|

| 31:16 | sourceID   | ru  | undefined | Stores the source ID written in the packet that caused<br>an error during the physical write request packet receive. |

| 15:0  | offsetHi   | ru  | undefined | Stores the upper 16- bit of offset_address written in the packet that caused an error during the packet receive.     |

|      | 31         | 24 23 |           | 16 15       | 8 7 | 0                                             |

|------|------------|-------|-----------|-------------|-----|-----------------------------------------------|

|      |            |       |           | offsetLo    |     |                                               |

|      |            |       |           |             |     |                                               |

|      |            |       |           |             |     |                                               |

| Bit  | Field Name | rwu   | reset     | description |     |                                               |

| 31:0 | offsetLo   | ru    | undefined |             |     | _address written in t<br>ng the packet receiv |

## 3.2.11. Vendor ID

This register indicates the vender ID of the 1394 Open HCI acquired from the Registration Authority Committee (RAC). This bits indicate "000000"h because this MB86613S is complied with the OHCI.

|       | 31       |              | 24 23 | }               | 16 15             | 8 7            | 0 |  |

|-------|----------|--------------|-------|-----------------|-------------------|----------------|---|--|

|       |          | vendorUnique |       | vendorCompanyID |                   |                |   |  |

|       |          |              |       |                 |                   |                |   |  |

|       |          |              |       |                 |                   |                |   |  |

| Bit   | Field Na | me           | rwu   | reset           | description       |                |   |  |

| 31:24 | vendorU  | nique        | <br>r | 00h             | These bits indica | ate "00h".     |   |  |

| 23:0  | vendorC  | ompanyID     | r     | 000000h         | These bits indica | ate "000000h". |   |  |

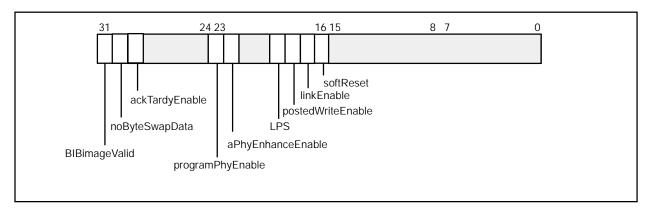

## 3.2.12. HCControl

This register controls the host operation conditions such as byte- swap and link enable.

noByteSwapData and PostedWriteEnable bits must be set when the linkEnable is not set. MB86613S contains PHY and LINK connected together inside of the chip. So, software can not control the performance between PHY and LINK. Therefore, programPhyEnable bit indicates "0" and aPhyEnhanceEnable bit indicates "1". When a "disconnect" is found in the 1394 network, the device automatically clears the linkEnable bit. Do not set linkEnable bit before Configuration ROM mapping register is set. As D1 state of PCI power management doesn't supported, ackTaedyEnable bit is reserved.

# FUJITSU

## Preliminary

| Bit | Field Name        | rscu | reset     | description                                                                                                                                                           |

|-----|-------------------|------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31  | BIBimageValid     | rsc  | Ob        | When this bit is zero, return ack_type_error on block<br>read requests.<br>When this bit is set, enable the mechanism of<br>automatically updating configuration ROM. |

| 30  | noByteSwapData    | rsc  | undefined | Big Endian: specify "1". Little Endian: specify "0".                                                                                                                  |

| 29  | ackTardyEnable    | rsc  | Ob        | reserved                                                                                                                                                              |

| 23  | programPhyEnable  | e r  | Ob        | This bit always indicates "0".                                                                                                                                        |

| 22  | aPhyEnhanceEnbl   | r    | 1b        | This bit always indicates "1".                                                                                                                                        |

| 19  | LPS               | rsc  | 0b        | Specifying "1" at this bit sets the LINK to ON.                                                                                                                       |

| 18  | postedWriteEnable | rsc  | undefined | Specifying "1" at this bit supports the posted write function.                                                                                                        |

| 17  | linkEnable        | rsu  | Ob        | Specifying "1" at this bit makes the LINK enabled.                                                                                                                    |

| 16  | softReset         | rsu  | *         | "1" at this bit performs the software reset. "1" is indicated during the hardware or software reset.                                                                  |

## 3.2.13. Self ID Buffer Pointer

Specify the host memory base address where the received self ID packet is stored.

|     | 31         | 24 23     | 16 15         | 8 7 | 0 |  |

|-----|------------|-----------|---------------|-----|---|--|

|     |            | selfIDBuf | ferPtr        |     |   |  |

|     |            |           |               |     |   |  |

|     |            |           |               |     |   |  |

| Rit | Field Name | rwu rese  | t description |     |   |  |

| Bit | Field Name      | rwu | reset | description                                                                                                    |

|-----|-----------------|-----|-------|----------------------------------------------------------------------------------------------------------------|

|     | selfIDBufferPtr | rw  |       | Specify the base address of the host memory where the received self ID packet is stored. (2048- byte boundary) |

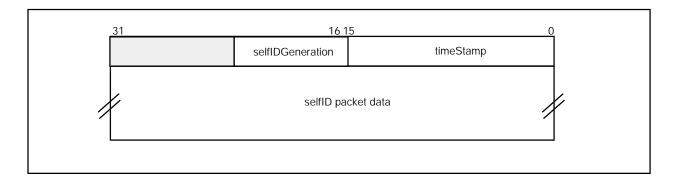

## 3.2.14. Self ID Count

This register indicates the status information with regard to self ID packet at a bus reset. selfIDSize field is cleared by the bus reset.

|       | 31               | 24 2 | 3              | 16 15                      | 8 7                                                  | 0                       |

|-------|------------------|------|----------------|----------------------------|------------------------------------------------------|-------------------------|

|       |                  |      | selfIDGenerati | ion                        | selfIDSize                                           |                         |

|       | selfIDError      |      |                |                            |                                                      |                         |

| Bit   | Field Name       | rwu  | reset          | description                |                                                      |                         |

| 31    | selfIDError      | ru   | undefined      |                            | cates "1" when an error<br>If ID packet is stored in |                         |

| 23:16 | selfIDGeneration | ru   | undefined      | These are s<br>bus reset d | elfID generation counte<br>etected.                  | r that increments every |

| 12:2  | selfIDSize       | ru   | undefined      | These bits quadlet uni     | indicate the size of rece<br>t.                      | ived self ID packet in  |

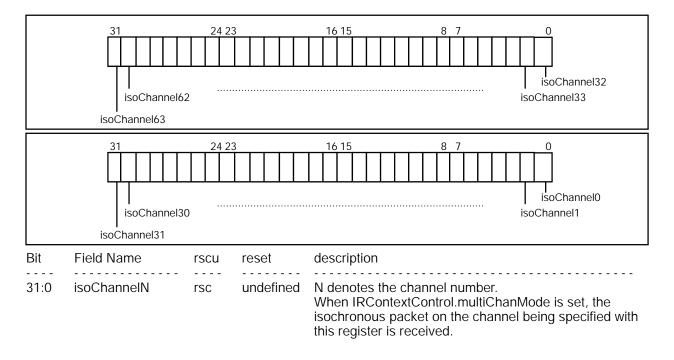

## 3.2.15. IRMultiChanMask

This register is used for setting the channel of packet when isochronous packet with multiple channels is received. This register is valid only when IRContextControl.multiChanMode bit is set. Also, only one channel out of 4 channels of IR- CPC can be used. If multiple channels are set with their IRContextControl.multiChan-Mode bit, The priority is made to channel 0 in order. Using this register requires the IRContextControl.buffer-Fill and isochHeader bits to be set. Also, the IRContextMatch.channelNumber filed is invalid.

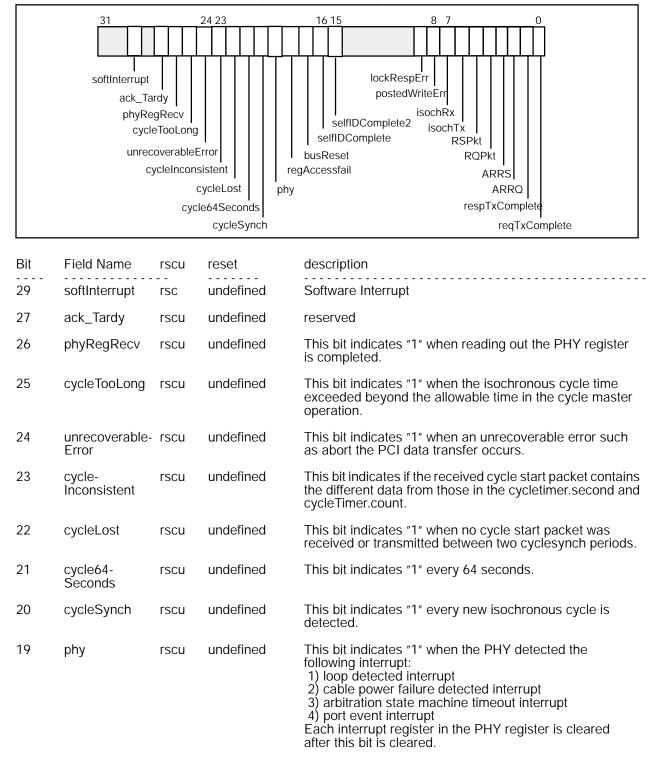

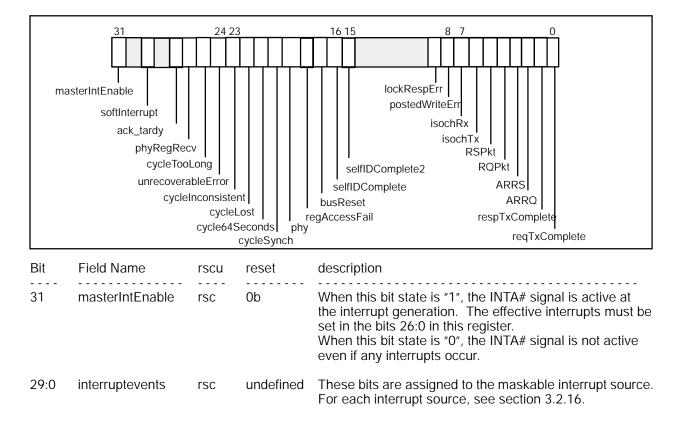

## 3.2.16. IntEvent

This register indicates the interrupt event for transfer error during the packet transfer or between the device and host memory. The read value from the IntEventClear register contains the AND operated value between IntEvent register and IntMask register. The device clears selfIDcomplete bit by setting the IntEvent.busReset bit at the bus reset. Software must not clear the busReset bit until the selfIDComplete bit contains "1".

Also, the interrupt event can be desirably generated by setting the desired bit.

# FUĴĨTSU

| Bit | Field Name            | rscu   | reset     | description                                                                                                                                                                                   |

|-----|-----------------------|--------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18  | regAccessFail         | rscu   | undefined | This bit indicates"1" when OHCI register access failed by SCLK missing from PHY.                                                                                                              |

| 17  | busReset              | rscu   | undefined | This bit indicates "1" when a bus reset is detected.                                                                                                                                          |

| 16  | selfIDComplete        | e rscu | undefined | This bit indicates "1" when self ID packet was completely received.                                                                                                                           |

| 15  | selfIDcomplete        | e2rscu | undefined | This bit indicates"1" when next self ID packet was completely received during selfIDComplete is"1".                                                                                           |

| 9   | lockRespError         | rscu   | undefined | This bit indicates "1" when an acknowledge except<br>"ack_complete" is received after transmitting the lock<br>response packet in response to the received lock request<br>packet.            |

| 8   | posted-<br>WriteError | rscu   | undefined | This bit indicates "1" when a host bus error occurs while<br>the received phy write request packet is stored in the host<br>memory and ack_complete acknowledge has already<br>been reported. |

| 7   | isochRx               | ru     | undefined | This bit indicates "1" when the context program process for the isochronous- receive is done. For details, see section 3.2.19.                                                                |

| 6   | isochTx               | ru     | undefined | This bit indicates "1" when the isochronous packet transmit is done. For details, see section 3.2.18.                                                                                         |

| 5   | RSPkt                 | rscu   | undefined | This bit indicates "1" when the received asynchronous response packet is completely stored in the host memory.                                                                                |

| 4   | RQPkt                 | rscu   | undefined | This bit indicates "1" when the received asynchronous request packet is completely stored in the host memory.                                                                                 |

| 3   | ARRS                  | rscu   | undefined | This bit indicates "1" when the context program process for the asynchronous- receive response is done.                                                                                       |

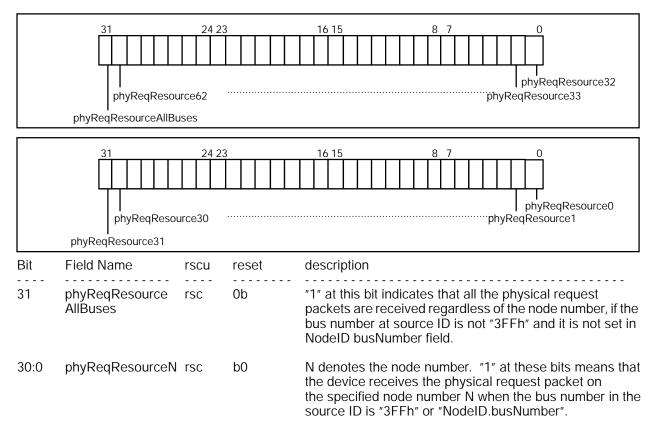

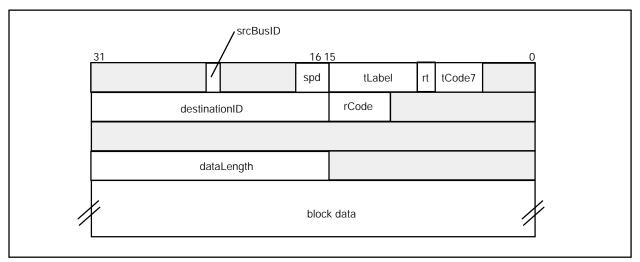

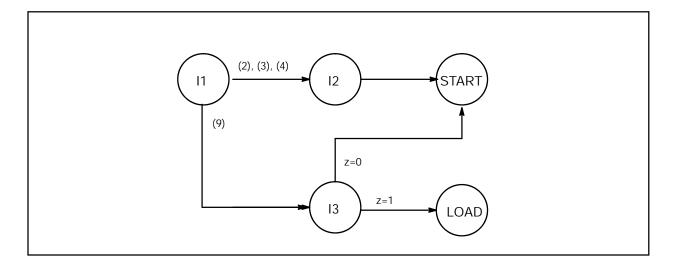

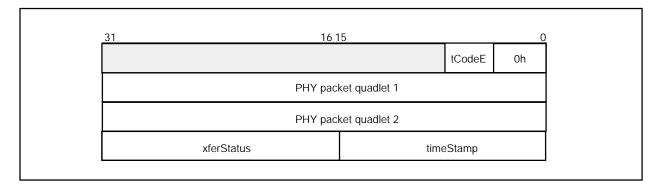

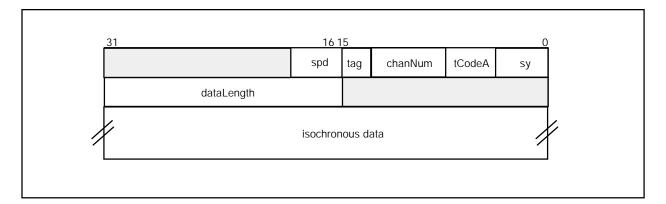

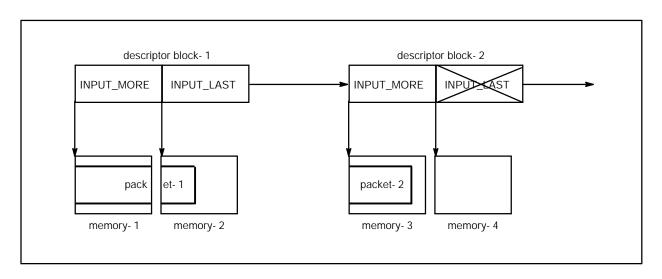

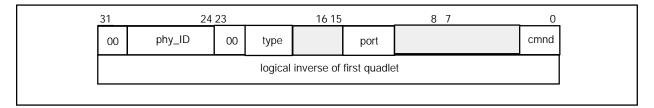

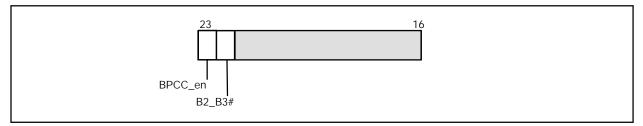

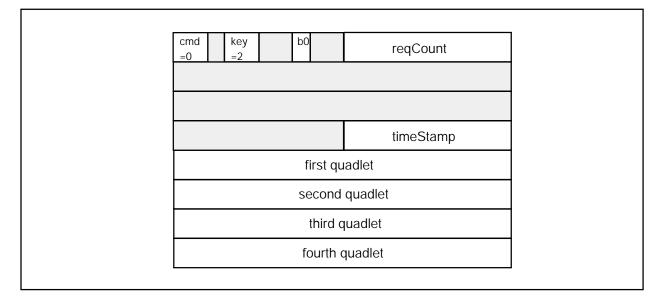

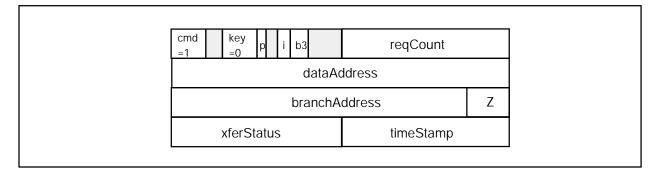

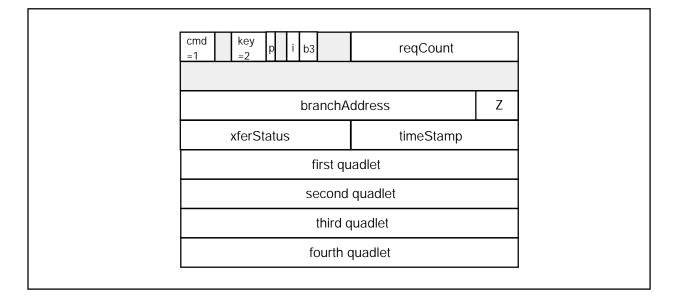

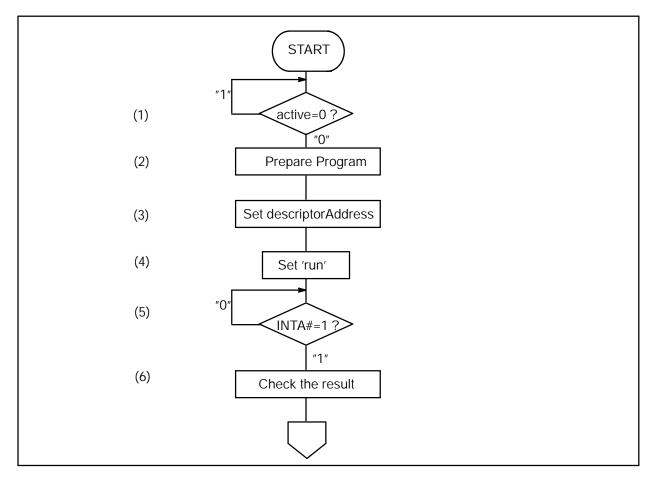

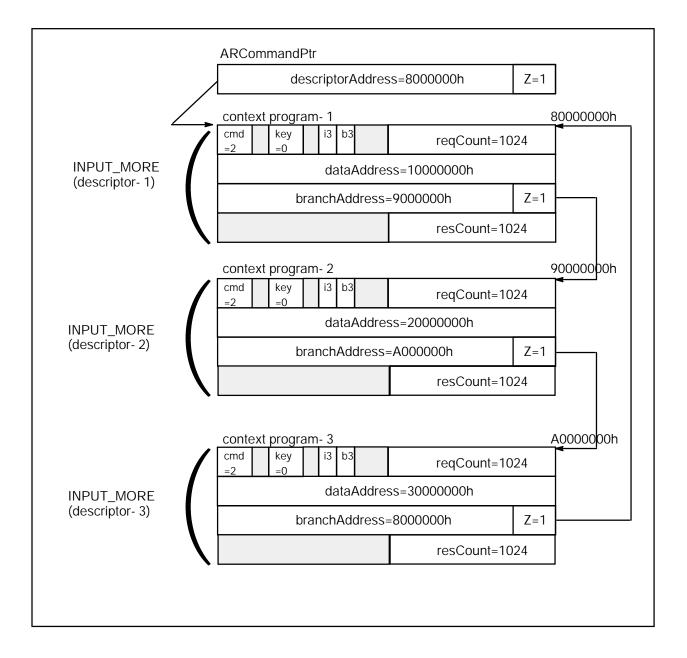

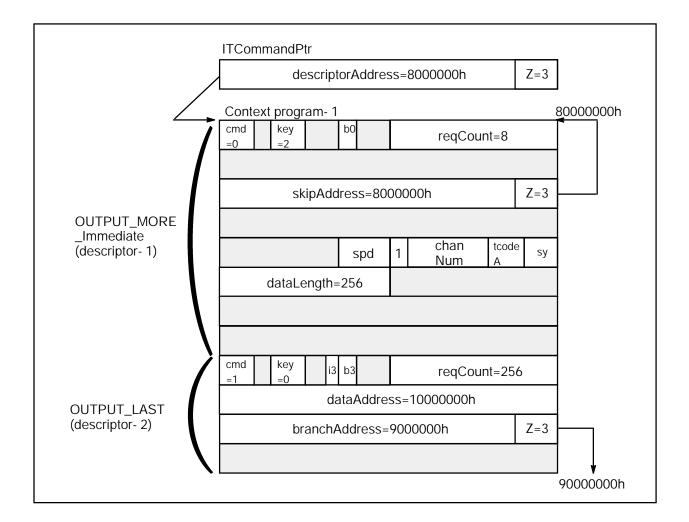

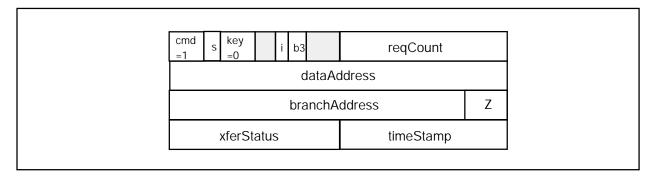

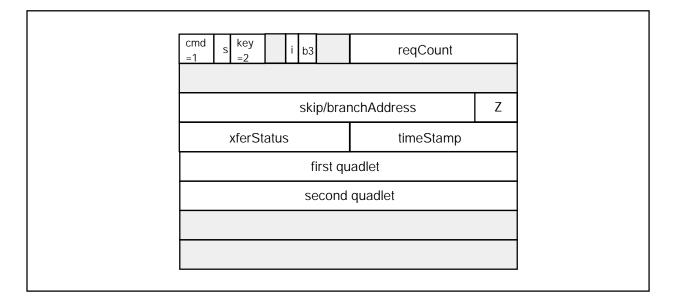

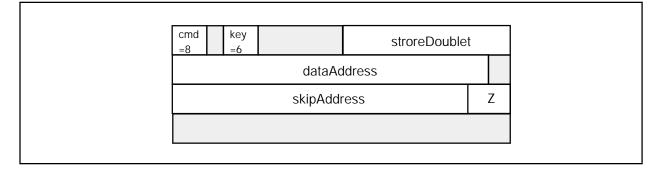

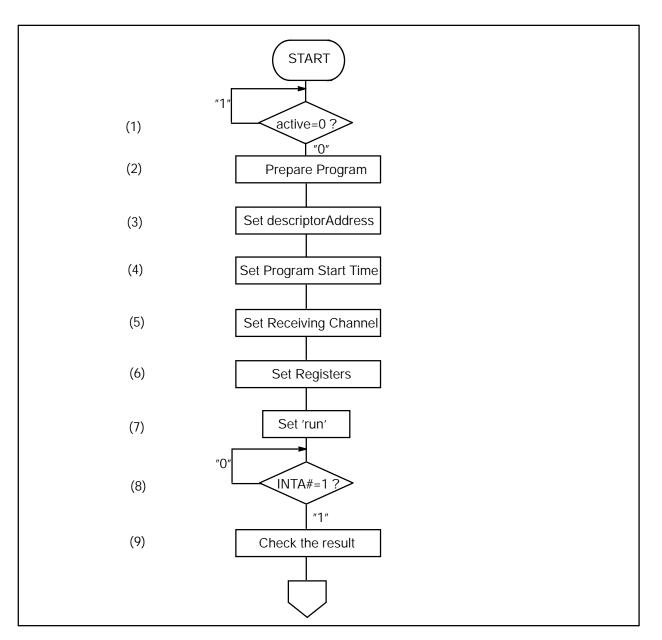

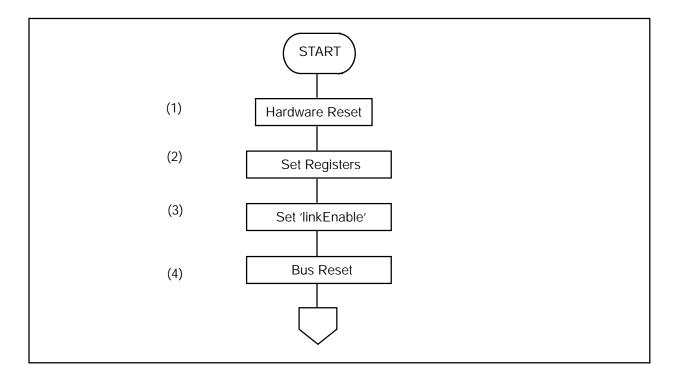

| 2   | ARRQ                  | rscu   | undefined | This bit indicates "1" when the context program process for the asynchronous- receive request is done.                                                                                        |