# Microprocessor SPARClite **CMOS**

# Peripherals for SPARClite

# MB86943B

### **■** DESCRIPTION

The MB86943B is a bus bridge that allows high-speed [data] transfers between the host processor (SPARClite\* Family) and the PCI-bus. This bridge chip enables SPARClite (host CPU) access in program mode (direct master operation) to devices on a PCI bus. Also, the SPARClite host can invoke the built-in DMA function on the bridge chip to allow access to devices on the PCI bus. Access from the PCI side to devices on the SPARClite bus (SL bus) is enabled by using the bridge chip slave operation function. The DMA function can be started up from the SL-bus side. The MB86943B supports Door Bell functions and Mail Box function as well.

\*: SPARClite is a trademark of SPARC International, Inc. in the United States. Fujitsu Microelectronics, Inc. has been granted permission to use the trademark.

### **■ FEATURES**

### **Key hardware features**

- Functions for SL-bus to PCI slave (possible to work in program mode)

- Functions for PCI-bus to SL-bus slave (possible to work in program mode)

- Two-channel DMA functions (between the SL-bus and the PCI-bus)

- Functions to access the SL-bus's external areas (ECS0 through ECS2)

- Interrupt communication functions between the SL-bus and the PCI-bus by use of Door Bell and Mail Box.

(Continued)

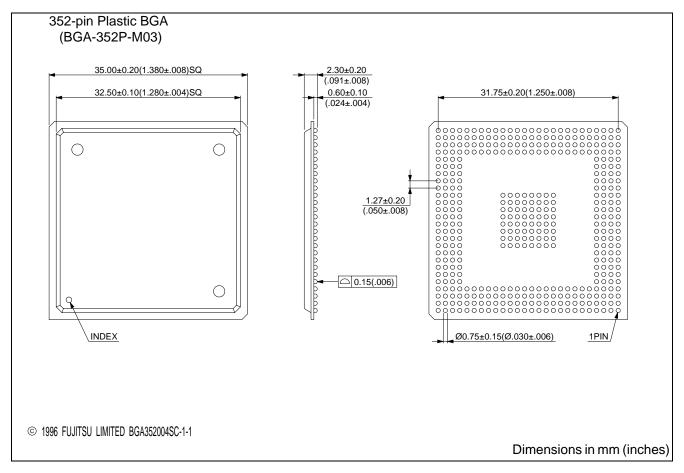

### ■ PACKAGE

### (Continued)

### Bus bridge features

The host SPARClite can access the PCI-bus's target by use of the chip's PCI-bus direct master functions (Direct Master Operation). Also the PCI-bus's other masters can access the SPARClite bus by use of the chip's PCI-bus direct slave functions (Direct Slave Operation). These functions allow individual bus masters to mutually access the PCI-bus area and SL-bus area. With the Direct Master or the Direct Slave in operation, data are transferred via the 128-byte data buffer, so that a high-speed burst transfer can be achieved.

Direct Master Operation

Allows the SL-bus processor to directly access the PCI space.

Allows high-speed burst transfer via the relevant data buffer.

• Direct Slave Operation

Allows the PCI-bus master to directly access the SL-bus space.

Allows high-speed burst transfer via the relevant data buffer.

### Provided with two independent DMA channels

- Carries out 32/64-bit transfer.

- Possible to work DMA control from the SL-bus side.

- Bidirectional DMA functions by use of the bidirectional data buffer having a capacity of 128 bytes.

- High-speed data chain mode by use of the built-in registers.

High Speed Data Chain Mode Using Internal Registers.

Because DMA descriptors are stored in internal registers there is no need to fetch descriptors from external memory, enabling high speed DMA operations in descriptor chain mode.

### Functions to access the SL-bus's external areas

• Pins ECS0 through ECS2 (External Chip Select) allow the access to the SL-bus's external I/Os, the memory via the bridge chip.

### **Door Bell functions**

The functions notify bidirectional interrupts; SL-bus  $\rightarrow$  PCI-bus and PCI-bus  $\rightarrow$  SL-bus.

#### **Mail Box functions**

Provided with eight registers possible to perform PCI write/SL read and eight registers possible to perform SL write/PCI read, so that messages can be communicated from both sides. A means is also provided to interrupt from the writing side to the reading side at same time.

The PCI-bus and the SL-bus can operate asynchronously by use of different clocks.

#### Data bus widths

SL-bus 64/32 bits. PCI-bus 64/32 bits.

### Address bus widths

SL-bus 32 bits (fixed) ADR<1:0> ignored, ASI<3:0> supported.

PCI-bus 64/32 bits.

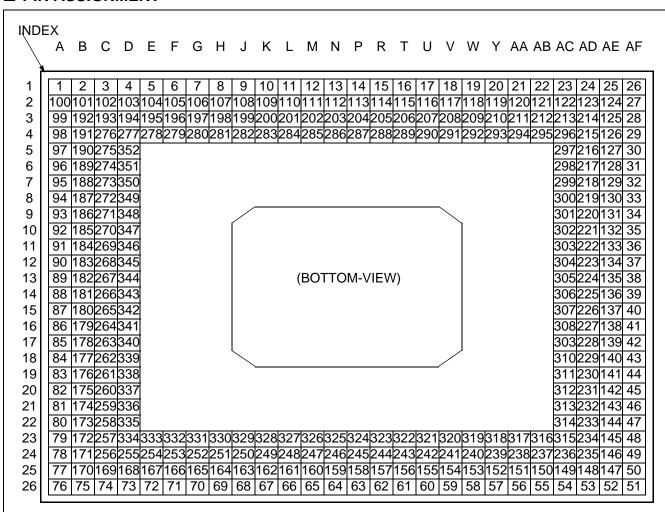

### **■ PIN ASSIGNMENT**

Signals (259 pins); 248 pins of them already used

| V <sub>DD3</sub> (32 pins) | 282,                                 | 301, | 320, | 339,   | 196,    | 108,  | 20,    | 23   |      |     |

|----------------------------|--------------------------------------|------|------|--------|---------|-------|--------|------|------|-----|

| linternal LOGIC,           | 287,                                 | 306, | 325, | 344,   | 299,    | 131,  | 45,    | 48   |      |     |

| Power-supply for I/Os      | 291,                                 | 310, | 329, | 348,   | 54,     | 154,  | 70,    | 73   |      |     |

|                            | 296,                                 | 315, | 334, | 277    | 79,     | 177,  | 270,   | 98   |      |     |

| V <sub>DD5</sub> (21 pins) | 281,                                 | 300, | 319, | 338,   | 194,    | 198,  | 112,   | 15,  | 209, | 212 |

| Power-supply for PCI       | 286,                                 | 305, | 324, | 343,   | 215,    | 272,  | 275    |      |      |     |

| I/Os                       | 292,                                 | 311, | 330, | 349    |         |       |        |      |      |     |

| Vss (38 pins)              | 1,                                   | 26,  | 51,  | 76,    | 195,    | 6,    | 285,   | 288, | 210, | 121 |

| linternal LOGIC,           | 279,                                 | 298, | 317, | 336,   | 216,    | 129,  | 39,    | 312  |      |     |

| GND common to I/Os         | 284,                                 | 303, | 322, | 341,   | 55,     | 64,   | 331,   |      |      |     |

|                            | 289,                                 | 308, | 327, | 346,   | 80,     | 89,   | 186,   | 273, | 190  |     |

|                            | 294,                                 | 313, | 332, | 351    |         |       |        |      |      |     |

| VPDP (1 pin)               | 92                                   |      | Wher | n moui | nted, c | onnec | ted to | Vss  |      |     |

| A feed-through current     | feed-through current prevention cell |      |      |        |         |       |        |      |      |     |

| OVSENS (1 pin)             | 93 When mounted, connected to Vss    |      |      |        |         |       |        |      |      |     |

| A power-sensing cell       |                                      |      |      |        |         |       |        |      |      |     |

|                            |                                      |      |      |        |         |       |        |      |      |     |

|     | G Pin<br>mber | Pin name         | At-              |     | G Pin<br>mber | Pin name         | At-              |     | G Pin<br>mber | Pin              | At-              |

|-----|---------------|------------------|------------------|-----|---------------|------------------|------------------|-----|---------------|------------------|------------------|

| FJ  | JEDEC         |                  | tribute          | FJ  | JEDEC         |                  | tribute          | FJ  | JEDEC         | name             | tribute          |

| 1   | A1            | Vss              | Vss              | 284 | L4            | Vss              | Vss              | 286 | N4            | V <sub>DD5</sub> | V <sub>DD5</sub> |

| 279 | F4            | Vss              | Vss              | 109 | K2            | AD[08]           | PCI I/O          | 19  | W1            | AD[57]           | PCI I/O          |

| 282 | J4            | V <sub>DD3</sub> | V <sub>DD3</sub> | 10  | K1            | AD[10]           | PCI I/O          | 290 | U4            | AD[60]           | PCI I/O          |

| 2   | B1            | AD[19]           | PCI I/O          | 201 | L3            | C/BE[0]#         | PCI I/O          | 117 | V2            | AD[56]           | PCI I/O          |

| 101 | B2            | AD[18]           | PCI I/O          | 110 | L2            | AD[04]           | PCI I/O          | 207 | U3            | AD[62]           | PCI I/O          |

| 103 | D2            | FRAME#           | PCI I/O          | 202 | МЗ            | AD[06]           | PCI I/O          | 20  | Y1            | V <sub>DD3</sub> | V <sub>DD3</sub> |

| 102 | C2            | AD[17]           | PCI I/O          | 11  | L1            | AD[07]           | PCI I/O          | 208 | V3            | AD[58]           | PCI I/O          |

| 3   | C1            | C/BE[2]#         | PCI I/O          | 287 | P4            | V <sub>DD3</sub> | V <sub>DD3</sub> | 21  | AA1           | AD[53]           | PCI I/O          |

| 194 | D3            | V <sub>DD5</sub> | V <sub>DD5</sub> | 12  | M1            | AD[05]           | PCI I/O          | 118 | W2            | AD[54]           | PCI I/O          |

| 195 | E3            | Vss              | Vss              | 285 | M4            | Vss              | Vss              | 210 | Y3            | Vss              | Vss              |

| 278 | E4            | TRDY#            | PCI I/O          | 112 | N2            | V <sub>DD5</sub> | V <sub>DD5</sub> | 209 | W3            | V <sub>DD5</sub> | V <sub>DD5</sub> |

| 4   | D1            | IRDY#            | PCI I/O          | 111 | M2            | AD[00]           | PCI I/O          | 22  | AB1           | AD[51]           | PCI I/O          |

| 104 | E2            | (N.C.)           | N.C.             | 13  | N1            | AD[03]           | PCI I/O          | 119 | Y2            | AD[55]           | PCI I/O          |

| 105 | F2            | STOP#            | PCI I/O          | 203 | N3            | AD[02]           | PCI I/O          | 293 | Y4            | AD[52]           | PCI I/O          |

| 196 | F3            | V <sub>DD3</sub> | V <sub>DD3</sub> | 14  | P1            | AD[01]           | PCI I/O          | 120 | AA2           | AD[49]           | PCI I/O          |

| 5   | E1            | DEVSEL#          | PCI I/O          | 204 | P3            | REQ64#           | PCI I/O          | 211 | AA3           | AD[50]           | PCI I/O          |

| 280 | G4            | AD[15]           | PCI I/O          | 113 | P2            | ACK64#           | PCI I/O          | 23  | AC1           | V <sub>DD3</sub> | V <sub>DD3</sub> |

| 106 | G2            | SERR#            | PCI I/O          | 114 | R2            | C/BE[6]#         | PCI I/O          | 121 | AB2           | Vss              | Vss              |

| 197 | G3            | PAR              | PCI I/O          | 15  | R1            | V <sub>DD5</sub> | V <sub>DD5</sub> | 212 | AB3           | V <sub>DD5</sub> | V <sub>DD5</sub> |

| 198 | НЗ            | V <sub>DD5</sub> | V <sub>DD5</sub> | 288 | R4            | Vss              | Vss              | 24  | AD1           | AD[45]           | PCI I/O          |

| 6   | F1            | Vss              | Vss              | 16  | T1            | C/BE[4]#         | PCI I/O          | 295 | AB4           | AD[48]           | PCI I/O          |

| 107 | H2            | AD[12]           | PCI I/O          | 291 | V4            | V <sub>DD3</sub> | V <sub>DD3</sub> | 213 | AC3           | AD[46]           | PCI I/O          |

| 7   | G1            | PERR#            | PCI I/O          | 115 | T2            | PAR64            | PCI I/O          | 122 | AC2           | AD[47]           | PCI I/O          |

| 199 | J3            | AD[13]           | PCI I/O          | 205 | R3            | C/BE[7]#         | PCI I/O          | 123 | AD2           | AD[42]           | PCI I/O          |

| 108 | J2            | V <sub>DD3</sub> | V <sub>DD3</sub> | 17  | U1            | AD[63]           | PCI I/O          | 25  | AE1           | AD[43]           | PCI I/O          |

| 200 | K3            | AD[11]           | PCI I/O          | 206 | Т3            | C/BE[5]#         | PCI I/O          | 214 | AD3           | AD[44]           | PCI I/O          |

| 8   | H1            | C/BE[1]#         | PCI I/O          | 18  | V1            | AD[59]           | PCI I/O          | 292 | W4            | V <sub>DD5</sub> | V <sub>DD5</sub> |

| 283 | K4            | AD[09]           | PCI I/O          | 116 | U2            | AD[61]           | PCI I/O          | 294 | AA4           | Vss              | Vss              |

| 9   | J1            | AD[14]           | PCI I/O          | 289 | T4            | Vss              | Vss              | 296 | AC4           | V <sub>DD3</sub> | V <sub>DD3</sub> |

| 281 | H4            | V <sub>DD5</sub> | V <sub>DD5</sub> |     | •             |                  |                  |     | •             |                  | •                |

V<sub>DD3</sub> : A 3.3 V power-supply pin (for supplying I/O power and internal power)

V<sub>DD5</sub>: Either a 5 V power-supply pin or 3.3 V power-supply pin (for supplying power to PCI I/Os) N.C.: Use this in an open state.

|     | (G Pin<br>umber | Pin name         | At-              |     | G Pin<br>mber | Pin name         | At-<br>trib- |     | G Pin<br>Imber | Pin name         | At-              |

|-----|-----------------|------------------|------------------|-----|---------------|------------------|--------------|-----|----------------|------------------|------------------|

| FJ  | JEDEC           |                  | tribute          | FJ  | JEDEC         |                  | ute          | FJ  | JEDEC          |                  | tribute          |

| 26  | AF1             | Vss              | Vss              | 303 | AC11          | Vss              | Vss          | 305 | AC13           | V <sub>DD5</sub> | V <sub>DD5</sub> |

| 298 | AC6             | Vss              | Vss              | 132 | AE10          | DACK1#           | 0            | 44  | AF19           | ADR<23>          | I/O*             |

| 301 | AC9             | V <sub>DD3</sub> | V <sub>DD3</sub> | 35  | AF10          | EOP1#            | 0            | 309 | AC17           | ADR<24>          | I/O*             |

| 27  | AF2             | AD[41]           | PCI I/O          | 222 | AD11          | (N.C.)           | N.C.         | 140 | AE18           | ADR<25>          | I/O*             |

| 124 | AE2             | AD[40]           | PCI I/O          | 133 | AE11          | ADR<2>           | I/O*         | 228 | AD17           | ADR<26>          | I/O*             |

| 126 | AE4             | AD[36]           | PCI I/O          | 223 | AD12          | ADR<3>           | I/O*         | 45  | AF20           | V <sub>DD3</sub> | V <sub>DD3</sub> |

| 125 | AE3             | AD[38]           | PCI I/O          | 36  | AF11          | ADR<4>           | I/O*         | 229 | AD18           | ADR<27>          | I/O*             |

| 28  | AF3             | AD[39]           | PCI I/O          | 306 | AC14          | V <sub>DD3</sub> | $V_{DD3}$    | 46  | AF21           | ADR<28>          | I/O*             |

| 215 | AD4             | V <sub>DD5</sub> | V <sub>DD5</sub> | 37  | AF12          | ADR<5>           | I/O*         | 141 | AE19           | ADR<29>          | I/O*             |

| 216 | AD5             | Vss              | Vss              | 304 | AC12          | ADR<6>           | I/O*         | 231 | AD20           | ADR<30>          | I/O*             |

| 297 | AC5             | AD[34]           | PCI I/O          | 135 | AE13          | ADR<7>           | I/O*         | 230 | AD19           | ADR<31>          | I/O*             |

| 29  | AF4             | AD[37]           | PCI I/O          | 134 | AE12          | ADR<8>           | I/O*         | 47  | AF22           | (N.C.)           | N.C.             |

| 127 | AE5             | AD[33]           | PCI I/O          | 38  | AF13          | ADR<9>           | I/O*         | 142 | AE20           | BMREQ#           | I/O*             |

| 128 | AE6             | AD[35]           | PCI I/O          | 224 | AD13          | ADR<10>          | I/O*         | 312 | AC20           | Vss              | Vss              |

| 217 | AD6             | AD[32]           | PCI I/O          | 39  | AF14          | Vss              | Vss          | 143 | AE21           | BMACK#           | I/O*             |

| 30  | AF5             | (N.C.)           | N.C.             | 225 | AD14          | ADR<11>          | I/O*         | 232 | AD21           | ERROR#           | l*               |

| 299 | AC7             | V <sub>DD3</sub> | V <sub>DD3</sub> | 136 | AE14          | ADR<12>          | I/O*         | 48  | AF23           | V <sub>DD3</sub> | V <sub>DD3</sub> |

| 129 | AE7             | Vss              | Vss              | 137 | AE15          | ADR<13>          | I/O*         | 144 | AE22           | RGSL#            | *                |

| 218 | AD7             | EAS#             | 0                | 40  | AF15          | ADR<14>          | I/O*         | 233 | AD22           | BMINH#           | l*               |

| 219 | AD8             | ECS0#            | 0                | 307 | AC15          | ADR<15>          | I/O*         | 49  | AF24           | WINDOWS#         | l*               |

| 31  | AF6             | ECS1#            | 0                | 41  | AF16          | ADR<16>          | I/O*         | 314 | AC22           | ASI<0>           | l*               |

| 130 | AE8             | ECS2#            | 0                | 310 | AC18          | V <sub>DD3</sub> | $V_{DD3}$    | 234 | AD23           | ASI<1>           | <b> </b> *       |

| 32  | AF7             | EBMREQ#          | 0                | 138 | AE16          | ADR<17>          | I/O*         | 145 | AE23           | ASI<2>           | <b> </b> *       |

| 220 | AD9             | EBMACK#          | <b> </b> *       | 226 | AD15          | ADR<18>          | I/O*         | 146 | AE24           | ASI<3>           | l*               |

| 131 | AE9             | V <sub>DD3</sub> | V <sub>DD3</sub> | 42  | AF17          | ADR<19>          | I/O*         | 50  | AF25           | SRSTO#           | t/s O            |

| 221 | AD10            | DRQ0#            | <b> </b> *       | 227 | AD16          | ADR<20>          | I/O*         | 235 | AD24           | SRSTI#           | <b> </b> *       |

| 33  | AF8             | DACK0#           | 0                | 43  | AF18          | ADR<21>          | I/O*         | 311 | AC19           | V <sub>DD5</sub> | V <sub>DD5</sub> |

| 302 | AC10            | EOP0#            | 0                | 139 | AE17          | ADR<22>          | I/O*         | 313 | AC21           | Vss              | Vss              |

| 34  | AF9             | DRQ1#            | *                | 308 | AC16          | Vss              | Vss          | 315 | AC23           | V <sub>DD3</sub> | V <sub>DD3</sub> |

| 300 | AC8             | V <sub>DD5</sub> | V <sub>DD5</sub> |     |               |                  |              |     |                |                  |                  |

<sup>\*:</sup> With a pull-up resistor

V<sub>DD3</sub> : A 3.3 V power-supply pin (for supplying I/O power and internal power)

V<sub>DD5</sub> : Either a 5 V power-supply pin or 3.3 V power-supply pin (for supplying power to PCI I/Os)

N.C. : Use this in an open state.

|     | (G Pin<br>ımber | Pin name         | At-              |     | G Pin<br>mber | Pin              | At-              | PKG Pi | n number | Pin              | At-              |

|-----|-----------------|------------------|------------------|-----|---------------|------------------|------------------|--------|----------|------------------|------------------|

| FJ  | JEDEC           |                  | tribute          | FJ  | JEDEC         | name             | tribute          | FJ     | JEDEC    | name             | tribute          |

| 51  | AF26            | Vss              | Vss              | 322 | T23           | Vss              | Vss              | 324    | P23      | V <sub>DD5</sub> | V <sub>DD5</sub> |

| 317 | AA23            | Vss              | Vss              | 155 | U25           | D<0>             | I/O*             | 69     | H26      | D<22>            | I/O*             |

| 320 | V23             | V <sub>DD3</sub> | V <sub>DD3</sub> | 60  | U26           | D<1>             | I/O*             | 328    | K23      | D<23>            | I/O*             |

| 52  | AE26            | CLKIN            | I                | 243 | T24           | D<2>             | I/O*             | 163    | J25      | DP5              | I/O*             |

| 147 | AE25            | TMS              | <b>I</b> *       | 156 | T25           | D<3>             | I/O*             | 249    | K24      | D<24>            | I/O*             |

| 149 | AC25            | TRST#            | <b>I</b> *       | 244 | R24           | D<4>             | I/O*             | 70     | G26      | V <sub>DD3</sub> | V <sub>DD3</sub> |

| 148 | AD25            | TCK              | <b>I</b> *       | 61  | T26           | D<5>             | I/O*             | 250    | J24      | D<25>            | I/O*             |

| 53  | AD26            | TDO              | 0                | 325 | N23           | V <sub>DD3</sub> | V <sub>DD3</sub> | 71     | F26      | D<26>            | I/O*             |

| 236 | AC24            | TDI              | l*               | 62  | R26           | D<6>             | I/O*             | 164    | H25      | D<27>            | I/O*             |

| 237 | AB24            | BREQ#            | 0                | 323 | R23           | D<7>             | I/O*             | 252    | G24      | D<28>            | I/O*             |

| 316 | AB23            | BGRNT#           | <b>I</b> *       | 158 | P25           | DP7              | I/O*             | 251    | H24      | D<29>            | I/O*             |

| 54  | AC26            | V <sub>DD3</sub> | V <sub>DD3</sub> | 157 | R25           | D<8>             | I/O*             | 72     | E26      | D<30>            | I/O*             |

| 150 | AB25            | BRIN#            | <b> </b> *       | 63  | P26           | D<9>             | I/O*             | 165    | G25      | D<31>            | I/O*             |

| 151 | AA25            | BGOUT#           | 0                | 245 | P24           | D<10>            | I/O*             | 331    | G23      | Vss              | Vss              |

| 238 | AA24            | PBREQ#           | <b>I</b> *       | 64  | N26           | Vss              | Vss              | 166    | F25      | DP4              | I/O*             |

| 55  | AB26            | Vss              | Vss              | 246 | N24           | D<11>            | I/O*             | 253    | F24      | D<32>            | I/O*             |

| 318 | Y23             | BE0#             | I/O*             | 159 | N25           | D<12>            | I/O*             | 73     | D26      | V <sub>DD3</sub> | V <sub>DD3</sub> |

| 152 | Y25             | BE1#             | I/O*             | 160 | M25           | D<13>            | I/O*             | 167    | E25      | D<33>            | I/O*             |

| 239 | Y24             | BE2#             | I/O*             | 65  | M26           | D<14>            | I/O*             | 254    | E24      | D<34>            | I/O*             |

| 240 | W24             | BE3#             | I/O*             | 326 | M23           | D<15>            | I/O*             | 74     | C26      | D<35>            | I/O*             |

| 56  | AA26            | BE4#             | I/O*             | 66  | L26           | DP6              | I/O*             | 333    | E23      | D<36>            | I/O*             |

| 153 | W25             | BE5#             | I/O*             | 329 | J23           | V <sub>DD3</sub> | V <sub>DD3</sub> | 255    | D24      | D<37>            | I/O*             |

| 57  | Y26             | BE6#             | I/O*             | 161 | L25           | D<16>            | I/O*             | 168    | D25      | D<38>            | I/O*             |

| 241 | V24             | BE7#             | I/O*             | 247 | M24           | D<17>            | I/O*             | 169    | C25      | D<39>            | I/O*             |

| 154 | V25             | V <sub>DD3</sub> | V <sub>DD3</sub> | 67  | K26           | D<18>            | I/O*             | 75     | B26      | DP3              | I/O*             |

| 242 | U24             | (N.C.)           | N.C.             | 248 | L24           | D<19>            | I/O*             | 256    | C24      | D<40>            | I/O*             |

| 58  | W26             | RDWR#            | I/O*             | 68  | J26           | D<20>            | I/O*             | 330    | H23      | V <sub>DD5</sub> | V <sub>DD5</sub> |

| 321 | U23             | AS#              | I/O*             | 162 | K25           | D<21>            | I/O*             | 332    | F23      | Vss              | Vss              |

| 59  | V26             | (N.C.)           | N.C.             | 327 | L23           | Vss              | Vss              | 334    | D23      | V <sub>DD3</sub> | V <sub>DD3</sub> |

| 319 | W23             | V <sub>DD5</sub> | V <sub>DD5</sub> |     |               |                  |                  |        |          |                  |                  |

<sup>\*:</sup> With a pull-up resistor

V<sub>DD3</sub> : A 3.3 V power-supply pin (for supplying I/O power and internal power)

V<sub>DD5</sub> : Either a 5 V power-supply pin or 3.3 V power-supply pin (for supplying power to PCI I/Os)

N.C.: Use this in an open state.

|     | (G Pin<br>ımber | Pin name         | At-              |     | G Pin<br>ımber | Pin name         | At-              |     | G Pin<br>ımber | Pin              | At-              |

|-----|-----------------|------------------|------------------|-----|----------------|------------------|------------------|-----|----------------|------------------|------------------|

| FJ  | JEDEC           |                  | tribute          | FJ  | JEDEC          |                  | tribute          | FJ  | JEDEC          | name             | tribute          |

| 76  | A26             | Vss              | Vss              | 341 | D16            | Vss              | Vss              | 343 | D14            | V <sub>DD5</sub> | V <sub>DD5</sub> |

| 336 | D21             | Vss              | Vss              | 178 | B17            | D<62>            | I/O*             | 94  | A8             | REQ#             | PCI O            |

| 339 | D18             | V <sub>DD3</sub> | V <sub>DD3</sub> | 85  | A17            | D<63>            | I/O*             | 347 | D10            | PRST#            | PCII             |

| 77  | A25             | D<41>            | I/O*             | 264 | C16            | DP0              | I/O*             | 186 | В9             | Vss              | Vss              |

| 170 | B25             | D<42>            | I/O*             | 179 | B16            | (N.C.)           | N.C.             | 270 | C10            | V <sub>DD3</sub> | V <sub>DD3</sub> |

| 172 | B23             | D<43>            | I/O*             | 265 | C15            | READY#           | t/s O            | 95  | A7             | AD[29]           | PCI I/O          |

| 171 | B24             | D<44>            | I/O*             | 86  | A16            | READYIN#         | I                | 271 | C9             | GNT#             | PCII             |

| 78  | A24             | D<45>            | I/O*             | 344 | D13            | V <sub>DD3</sub> | V <sub>DD3</sub> | 96  | A6             | AD[27]           | PCI I/O          |

| 257 | C23             | D<46>            | I/O*             | 87  | A15            | RDYOUT#          | I                | 187 | B8             | AD[30]           | PCI I/O          |

| 258 | C22             | D<47>            | I/O*             | 342 | D15            | MEXC#            | t/s O            | 273 | C7             | Vss              | Vss              |

| 335 | D22             | DP2              | I/O*             | 181 | B14            | IRQ#             | 0                | 272 | C8             | V <sub>DD5</sub> | $V_{\text{DD5}}$ |

| 79  | A23             | V <sub>DD3</sub> | V <sub>DD3</sub> | 180 | B15            | (N.C.)           | N.C.             | 97  | A5             | AD[25]           | PCI I/O          |

| 173 | B22             | D<48>            | I/O*             | 88  | A14            | HOST             | <b> </b> *       | 188 | B7             | AD[31]           | PCI I/O          |

| 174 | B21             | D<49>            | I/O*             | 266 | C14            | SLD64            | *                | 350 | D7             | AD[28]           | PCI I/O          |

| 259 | C21             | D<50>            | I/O*             | 89  | A13            | Vss              | Vss              | 189 | В6             | AD[26]           | PCI I/O          |

| 80  | A22             | Vss              | Vss              | 267 | C13            | BST8             | l*               | 274 | C6             | AD[24]           | PCI I/O          |

| 337 | D20             | D<51>            | I/O*             | 182 | B13            | (N.C.)           | N.C.             | 98  | A4             | V <sub>DD3</sub> | V <sub>DD3</sub> |

| 175 | B20             | D<52>            | I/O*             | 183 | B12            | TEST0            | 0                | 190 | B5             | Vss              | Vss              |

| 260 | C20             | D<53>            | I/O*             | 90  | A12            | TEST1            | 0                | 275 | C5             | V <sub>DD5</sub> | V <sub>DD5</sub> |

| 261 | C19             | D<54>            | I/O*             | 345 | D12            | TEST2            | 0                | 99  | А3             | AD[23]           | PCI I/O          |

| 81  | A21             | D<55>            | I/O*             | 91  | A11            | TEST3            | 0                | 352 | D5             | IDSEL            | PCI I            |

| 176 | B19             | DP1              | I/O*             | 348 | D9             | V <sub>DD3</sub> | V <sub>DD3</sub> | 276 | C4             | AD[20]           | PCI I/O          |

| 82  | A20             | D<56>            | I/O*             | 184 | B11            | (N.C.)           | N.C.             | 191 | B4             | C/BE[3]#         | PCI I/O          |

| 262 | C18             | D<57>            | I/O*             | 268 | C12            | (N.C.)           | N.C.             | 192 | В3             | AD[22]           | PCI I/O          |

| 177 | B18             | V <sub>DD3</sub> | V <sub>DD3</sub> | 92  | A10            | VPDP             | VPDP             | 100 | A2             | AD[21]           | PCI I/O          |

| 263 | C17             | D<58>            | I/O*             | 269 | C11            | INTA#            | PCI O            | 193 | C3             | AD[16]           | PCI I/O          |

| 83  | A19             | D<59>            | I/O*             | 93  | A9             | OVSENSE          | OVSNS            | 349 | D8             | V <sub>DD5</sub> | V <sub>DD5</sub> |

| 340 | D17             | D<60>            | I/O*             | 185 | B10            | CLK              | PCII             | 351 | D6             | Vss              | Vss              |

| 84  | A18             | D<61>            | I/O*             | 346 | D11            | Vss              | Vss              | 277 | D4             | V <sub>DD3</sub> | V <sub>DD3</sub> |

| 338 | D19             | V <sub>DD5</sub> | V <sub>DD5</sub> |     |                |                  |                  |     |                |                  |                  |

<sup>\*:</sup> With a pull-up resistor

V<sub>DD3</sub>: A 3.3 V power-supply pin (for supplying I/O power and internal power)

V<sub>DD5</sub>: Either a 5 V power-supply pin or 3.3 V power-supply pin (for supplying power to PCI I/Os)

OVSENSE: A power-sensing pin. Usually fixed to L.

TEST0 to TEST3: TEST pins. Use them in an open state.

N.C.: Use this in an open state. VPDP: A TEST pin. Usually fixed to L.

## **■ PIN DESCRIPTION**

## 1. PCI Bus interface (89 pins))

| Function class      | Pin name   | 1/0          | Number of pins | Description                                                                                                                                                                                                                                                                                                                                |

|---------------------|------------|--------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | CLK        | I            | 1              | A pin for the PCI-bus clock input. The PCI-bus interface operates in synchronization with this clock, up to 33 MHz.                                                                                                                                                                                                                        |

| System              | PRST#      | I            | 1              | A pin for the PCI system reset input.<br>A signal for PCI system reset. This signal, when asserted, initializes everything within the companion chip.                                                                                                                                                                                      |

|                     | AD[31:00]  | t/s I/O      | 32             | Pins for the address data signals. The 32 lower-order bits of PCI-bus address data.                                                                                                                                                                                                                                                        |

| Address<br>data bus | C/BE[3:0]# | t/s I/O      | 4              | Pins for the command byte enable signals for the PCI-bus. In address phase, these pins indicate a PCI-bus command. In data phase, these pins indicate the effective byte lane of AD[31:00].                                                                                                                                                |

|                     | PAR        | t/s I/O      | 1              | A pin for the PCI-bus parity signal. Indicates the even parity of AD[31:00] and C/BE[3:0]#, 36 signals in total.                                                                                                                                                                                                                           |

|                     | FRAME#     | s/t/s<br>I/O | 1              | A pin for the frame signal. This signal indicates that the PCI bus cycle is being executed. This pin outputs the master (initiator) signal on the PCI bus. When the MB86943B is the initiator, this pin is used in output state.                                                                                                           |

|                     | IRDY#      | s/t/s<br>I/O | 1              | A pin for the initiator ready signal. Indicates that the PCI-bus master (initiator) is ready to complete a bus cycle.                                                                                                                                                                                                                      |

| Bus control         | TRDY#      | s/t/s<br>I/O | 1              | A pin for the target ready signal. Indicates that the accessed PCI target (resource) is ready to complete a bus cycle.                                                                                                                                                                                                                     |

|                     | DEVSEL#    | s/t/s<br>I/O | 1              | A pin for the device select signal. Indicates that a PCI target decodes the address on the AD line to respond to a bus cycle.                                                                                                                                                                                                              |

|                     | STOP#      | s/t/s<br>I/O | 1              | A pin for the stop signal. Indicates that the accessed PCI target is waiting for the bus cycle to finish before the PCI-bus master finishes access in whole or in part.                                                                                                                                                                    |

| Bus control         | IDSEL      | ı            | 1              | A pin for the initialize device select signal input. The signal line AD[31:11] is used as the IDSEL signal line for each PCI resource. For this purpose, AD[31:11] are all used as an input pin for any resource. The signal lines AD[31:11] are driven by the PCI-bus master so as to select a specific PCI resource configuration space. |

| Arbitration control | REQ#       | t/s O        | 1              | A pin for the request signal output. A signal that conveys that the companion chip requests the PCI-bus right. With the PRST# signal asserted, this pin is put to a tristate when involved in a point-to-point signal.                                                                                                                     |

### (Continued)

| Function class            | Pin name   | I/O          | Number of pins | Description                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------|------------|--------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Arbitration control       | GNT#       | _            | 1              | A pin for the grant signal input. A signal that notifies that the companion chip gained the PCI-bus from the PCI central arbiter in response to the request for the PCI-bus right made by the companion chip. This is a point-to-point signal.                                                                                                                                                                    |

| Error notifi-             | PERR#      | s/t/s<br>I/O | 1              | A pin for the parity error signal. Indicates, in PCI-bus data phase, that a parity error occurred in data transferred on the signal lines - AD, C/BE#, PAR, and PAR64. When data are input to the companion chip, this pin is used for output. When data are output from the companion chip, this pin is used for input.                                                                                          |

| cation                    | SERR#      | o/d          | 1              | A pin for the system error signal. Indicates, in PCI-bus address phase, that a parity error occurred in an address transferred on the signal lines - AD, C/BE#, PAR, and PAR64. When an error occurs that the companion chip can detect, the error can be notified as an SERR# by means of making suitable settings in the PCI SERR# Enable Register.                                                             |

| Interrupt<br>notification | INTA#      | o/d          | 1              | A pin for the interrupt output. A pin that notifies the PCI-bus of an interrupt. When an error occurs that the companion chip can detect, the error can be notified as an INTA# by means of making suitable settings in the PCI-bus Interrupt Enable Register.                                                                                                                                                    |

|                           | AD[63:32]  | t/s I/O      | 32             | Pins for the 64-bit expanded address data signals. The 32 higher-order bits of PCI-bus address data.                                                                                                                                                                                                                                                                                                              |

|                           | C/BE[7:4]# | t/s I/O      | 4              | Pins for the 64-bit expansion command byte enable signals. Pins for command byte enable signals for the PCI-bus. These pins are meaningless in address phase. In data phase, these pins indicate the effective byte lane of AD[63:32].                                                                                                                                                                            |

|                           | PAR64      | t/s I/O      | 1              | A pin for the 64-bit expansion PCI-bus parity signal. Indicates the even parity of AD[63:32] and C/BE[7:4]# 36 signals in total.                                                                                                                                                                                                                                                                                  |

| PCI 64-bit<br>expansion   | REQ64#     | s/t/s<br>I/O | 1              | A pin for the 64-bit data access request signal. Indicates that the PCI-bus master can execute a 64-bit data bus cycle.  When a high-level signal is input to the SLD64 pin with the SPAR-Clite bus being in 64-bit data operation and when the companion chip operates as the PCI bus master, the REQ64# signal is asserted concurrently with the FRAME# signal, and the 64-bit data cycles are always required. |

|                           | ACK64#     | s/t/s<br>I/O | 1              | A pin for the 64-bit data access enable signal. Indicates that the accessed PCI target can execute a 64-bit data bus cycle.                                                                                                                                                                                                                                                                                       |

Note: t/s : Used as a tri-state output driver

s/t/s : Used as a sustained tri-state output driver o/d : Used as an open drain output driver

pull up : Built-in pull-up resistance

## 2. SPARClite bus interface pins (138 pins)

| Function class    | Pin name | 1/0          | Number of pins | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------|----------|--------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System clock      | CLKIN    | I            | 1              | A pin for SPARClite bus clock input. The SPARClite bus interface operates in synchronization with this clock, up to 50 MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Reset             | SRSTI#   | l<br>pull up | 1              | A pin for reset input from the SPARClite-bus. When the "L" level is input to this pin, the following operation is activated.  (1) Clearing of the SL-bus Init Done bit of the SL-bus Configuration Register.  (2) Clearing of the registers other than those related to the PCI Configuration.  (3) Assertion of the SRSTO# signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                   |          | t/s O        | 1              | A pin for the reset output to the SPARClite-bus. This pin is asserted in one of the instances given below.  (1) When the PRST# signal is input.  (2) When the SRSTI# signal is input.  (3) When "1" is set in the Software Reset bit of the Reset Register, which is related to the PCI Configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Bus<br>definition | HOST     | l<br>pull up | 1              | A pin for the PCI-bus host definition. A pin that decides whether or not the SPARClite should generate PCI configuration cycles as the host CPU of the PCI-bus. This pin is an input pin fixed either to the "L" level or to the "H" level. When the "H" level is being input to this pin: The SPARClite becomes the host CPU of the PCI-bus, and the companion chip is defined as a host bridge. In this instance, use of the SL-bus configuration related PCI Configuration Address Register and the PCI Configuration Address Register allows generation of configuration cycles into the PCI-bus. When the "L" level is being input to this pin: The PCI Configuration Address Register and the PCI Configuration Data Register, which are related to the SL-bus Configuration, are ignored when written and become indeterminate registers when read, so that configuration cycles cannot be generated into the PCI-bus. |

|                   | SLD64    | l<br>pull up | 1              | A pin for the SPARClite data bus width definition. A pin that decides the data bus width in the SPARClite-bus cycles in which the companion chip intervenes. This pin is an input pin fixed either to the "L" level or to the "H" level. When the "H" level is being input to this pin: The SPARClite-bus is defined as a 64-bit data width - D<63:0>, BE0# to BE7#, and PARITY0 to PARITY7 are regarded as valid. When the "L" level is being input to this pin: The SPARClite-bus is defined as a 32-bit data width - D<31:0>, BE4# to BE7#, and PARITY4 to PARITY7 are regarded as valid. D<63:32>, BE0# to BE3#, and PARITY0 to PARITY3 assume the state of high input impedance.                                                                                                                                                                                                                                         |

| Function class                 | Pin name | I/O         | Number of pins | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------------|----------|-------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bus<br>definition              | BST8     | l<br>pul up | 1              | A pin for the SPARClite-bus burst transfer length definition. A pin that decides a burst transfer length in the SPARClite-bus cycles in which the companion chip intervenes. This pin is an input pin fixed either to the "L" level or to the "H" level. When the "H" level is being input to this pin: The SPARClite-bus, when subjected to a burst transfer, is defined as an 8-burst transfer. When the "L" level is being input to this pin: The SPARClite bus, when subjected to a burst transfer, is defined as a 4-burst transfer. |

| Interrupt<br>notifica-<br>tion | IRQ#     | 0           | 1              | A pin for the interrupt signal to the SPARClite. When a cause of interrupt specified by the SL-bus Interrupt Enable Register occurs, this pin is switched to the "L" level to notify the interrupt.                                                                                                                                                                                                                                                                                                                                       |

| Function class | Pin name  | I/O            | Number of pins | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------|-----------|----------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address        | ADR<31:2> | I/O<br>pull up | 30             | Pins for the address signal.  When the companion chip has the bus right:  This pin outputs an address signal. This pin is effective over a bus cycle period, and the output value during an idle cycle is not guaranteed.  The value sequentially changes under a burst transfer.  ADR<5:3> under burst transfer with a 64-bit bus width in operation changes as given below.  [For 4-burst transfer]  (1) 000→001→010→011  (2) 100→101→110→111  [For 8-burst transfer]  000→001→010→011→100→101→110→111  ADR<4:2> under a burst transfer with a 32-bit bus width in operation changes as given below.  [For 4-burst transfer]  (1) 000→001→010→011  (2) 100→101→110→111  [For 8-burst transfer]  000→001→010→011→100→101→110→111  When the companion chip doesn't have the bus right:  This pin becomes an address input pin to be used to request the direct master access involved in internal registers.  When SLD64 = "1" (a 64-bit data width specified)  ADR<31:3> is regarded as a valid address in carrying out a single transfer. When a 4-burst transfer is in operation, the 2 lowerorder bits ADR<4:3> need to be 00, and when an 8-burst transfer is in operation, the 3 lower-order bits ADR<5:3> need to be 000.  In other instances, a burst response called forth by the BMACK# signal is not made, but a single transfer is carried out. When SLD64 = "0" (a 32-bit data width specified)  ADR<31:2> is regarded as a valid address in carrying out a single transfer. When a 4-burst transfer is carried out. When SLD64 = "0" (a 32-bit data width specified)  ADR<31:2> is regarded as a valid address in carrying out a single transfer. When a 4-burst transfer is in operation, the lower order 2 bits of address ADR<3:2> need to be 00, and when an 8-burst transfer is in operation, the lower order 2 bits of address ADR<3:2> need to be 00, and when an 8-burst transfer is in operation, the lower order 3 bits of address ADR<4:2> need to be 000. In other instances, a burst response called forth by the BMACK# signal is not made, but a single transfer is carried out. |

| Function class               | Pin name              | I/O            | Number of pins | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------|-----------------------|----------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data bus                     | D<63:0>               | I/O<br>pull up | 64             | Pins for the data signal.  When the companion chip has the bus right: These pin form a bidirectional data bus. If data is of double-word type, the data needs to be aligned to an address of a multiple of 8, if data is of single-word type, the data needs to be aligned to a multiple of 4.  D<31:0> is used in 32-bit burst mode.  When the companion chip doesn't have the bus right: These pins form a data bus used to access internal registers, the external ECS space, and the PCI space from the SPARClite.  Access by use of 64-bit bus width and access by use of 32-bit bus width are supported. Reading from the SPARClite is effected in conformity with a data size requested. In writing, valid bytes are specified by use of BE0# to BE7# for a 64-bit bus width, and by use of BE4# to BE7# for a 32-bit bus width.  Specifying discontinuous BE#s is forbidden. |

| Data bus<br>informa-<br>tion | BE0# to<br>BE7#       | I/O<br>pull up | 8              | Pins for the byte enable signal.  When SLD64 = "1" (a 64-bit data width specified) The valid bytes enabled for D<63:0> are BE0# to BE7#.  When SLD64 = "0" (a 32-bit data width specified) The valid byte enabled for D<31:0> are BE4# to BE7#.  When the companion chip has the bus right: These pins output "L"s to valid bytes both in write and read. These signals are effective over a bus cycle.  When the companion chip doesn't have the bus right: These pins are for a signal for specifying the valid byte data. In reading, any data of 64-bit width or 32-bit width are regarded as valid. In writing, data corresponding to active BEx#s are written. Discontinuous BEx#s are forbidden.                                                                                                                                                                              |

|                              | PARITY0 to<br>PARITY7 | I/O<br>pull up | 8              | Pins for the parity signals. These are data parity signals. When SLD64 = "1" (a 64-bit data width specified) The parity bits for D<63:0> are PARITY0 to PARITY7. When SLD64 = "0" (a 32-bit data width specified) The parity bits for D<31:0> are PARITY4 to PARITY7. When the companion chip has the bus right: When reading as viewed from the companion chip, these pins work as parity input; when writing, these pins work as parity output. When the companion chip doesn't have the bus right and accessed via the companion chip: When reading as viewed from the SPARClite, these pins work as parity output; when writing, these pins work as parity input.                                                                                                                                                                                                                |

| Function class              | Pin name | I/O          | Number of pins | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------------------|----------|--------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                             | ASI<3:0> | l<br>pull up | 4              | Pins for the address space identification input signal. When the companion chip has the bus right: These signals are meaningless. When the companion chip doesn't have the bus right: These pins are input pins for the address space identification signals output from the SPARClite. These pins pass input signals used for the SPARClite to intervene in the companion chip and to identify an address space. These pins are sampled at the cycle immediately subsequent to the cycle in which AS# is asserted. |

| Address<br>informa-<br>tion | WINDOWS# | l<br>pull up | 1              | A pin for the windows input signal. When the companion chip has the bus right: This signal is meaningless. When the companion chip doesn't have the bus right: Some types of SPARClite CPUs do not support every bit of ADR<31:0>. Thus, in using one of SPARClites of such type, in- putting the "L" level to this pin allows ADR<31:28> and ASI<3:0> not to be subjected to decoding. This pin is sampled at the cycle immediately subsequent to the cycle in which AS# is asserted.                              |

|                             | RGSL#    | l<br>pull up | 1              | A pin for the register select input signal. When the companion chip has the bus right: This signal is meaningless. When the companion chip doesn't have the bus right: The "L" level signal input to this pin when the SPARClite accesses internal registers of the companion chip. This pin needs to be asserted during the relevant access cycle.                                                                                                                                                                 |

| Function class | Pin name | I/O            | Number of pins | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------|----------|----------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | AS#      | I/O<br>pull up | 1              | A pin for the address strobe signal.  When the companion chip has the bus right: An address strobe is output only when "1" is set in the SDRAM Mode bit of the SL-bus Configuration Register. An "L" is asserted for one clock cycle in the first cycle of the bus cycle.  When the companion chip doesn't have the bus right: The address strobe is fed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Cycle          | RDWR#    | I/O<br>pull up | 1              | A pin for the read/write signal.  When the companion chip has the bus right: This is a read/write signal. An "L" is output if the current cycle is a write cycle; the "H" is output over the period of a read cycle. The output level is kept up from the beginning to the end of the bus cycle.  When the companion chip doesn't have the bus right: This signal specifies the read/write when the SPARClite accesses internal registers, the PCI space, and the ECS space. This pin is sampled at the cycle immediately subsequent to the cycle in which AS# is asserted. And if it is "H", then read operation is carried out; if it is "L", then write operation is carried out.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| control        | BMREQ#   | I/O<br>pull up | 1              | A pin for the burst transfer enable signal.  When the companion chip has the bus right: A signal for a request for burst transfer toward the SPARClite. Either a direct slave or DMA access occurs only when "1" is set in the SDRAM Mode bit of the SL-bus Configuration Register. If the condition to carry out burst transfer is being satisfied, then make this signal "L" to request burst transfer. At the same time, the EBMREQ# signal is asserted, too. The EBMREQ# signal is deasserted at the same time with the first ready cycle.  When the companion chip doesn't have the bus right: A signal for a request for burst transfer from the SPARClite. The level of this signal is determined at the cycle immediately subsequent to the cycle in which AS# is asserted. If it is "L" and if the timing permits burst transfer, then the burst transfer is performed in response to the BMACK#; if the timing doesn't permit burst transfer, then a BMACK# response is not made, and only a single transfer is carried out.  In accessing an internal register or the ECS space from the SPARClite, the burst transfer is not responded even if a request for burst transfer is asserted. |

| Function class   | Pin name | I/O              | Number of pins | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------|----------|------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | BMACK#   | I/O<br>pull up   | 1              | A pin for the burst transfer response signal.  When the companion chip has the bus right: This signal is acknowledgment input from the SPARClite in burst mode. If the "L" level is input at the same cycle as READY# with burst transfer requested (with the "L" output to BMREQ#), the burst transfer mode is assumed.  (This operation is feasible in both schemes - either the "L" is input in the same cycle as READY# or the "L" was input at a prior cycle and is kept until reaching the cycle of READY#.)  When the companion chip doesn't have the bus right: In an instance in which the SPARClite decodes an address space accessed via the companion chip, this terminal outputs acknowledgment in burst mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Cycle<br>control | BMINH#   | l<br>pull up     | 1              | A pin for the burst transfer inhibit input signal. When the companion chip has the bus right: This signal is meaningless. When the companion chip doesn't have the bus right: An input pin for a signal to disable a burst transfer request. With the "L" input to this pin, the burst response with the BMACK# output is not performed even though a burst transfer is requested from the SPARClite. The level of this signal is determined at the cycle immediately subsequent to the cycle in which AS# is asserted; if it is "L", the BMACK# output is maintained at the "H" level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                  | READY#   | t/s O<br>pull up | 1              | A pin for the ready signal output.  When the companion chip has the bus right:  If the companion chip has the bus right:  This signal is output if a time-out occurs in the built-in ready timer. To make the ready timer effective, a longer time period needs to be set in the ready timer than the amount of wait given to the wait generator in each ECS space and than the setting in the external watchdog timer.  When the companion chip doesn't have the bus right:  In reading the internal register or the PCI space from the SPAR-Clite, the "L" is output when data is made ready on the data bus. In writing to the internal register or to the PCI space, the "L" is output when data is taken into the companion chip.  In accessing the ECS space from the SPARClite, a ready output signal internally generated comes out of this pin. This pin outputs a ready signal generated by the built-in wait generator. Also, it outputs this signal when a time-out occurs in the built-in ready timer. For this reason, to make the ready timer effective, a longer time period needs to be set in the ready timer than the amount of wait given to the wait generator and than the setting in the external watchdog timer. |