# CMOS ETHERNET ENCODER/DECODER

DATA SHEET APRIL1993

## **FEATURES**

- 10 Mbit/sec Manchester encoder/decoder

- Compatible with IEEE 802.3 10BASE2, 10BASE5 and 10BASE-T specifications

- Receiver clock recovery with dual phase locked loop for high stability

- Decodes Manchester data with up to ±20 ns of jitter.

- · Loopback capability for diagnostics

- TTL compatible host interface

- Interfaces directly to the AUI (transceiver) cable

- High speed CMOS technology with a single 5 V supply

- · Low power consumption, typically 16 mA

- Power Down Mode: I<sub>CC</sub> = 5 mA typ

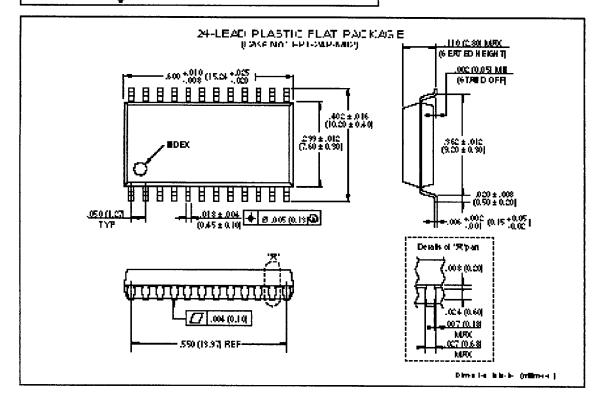

- Available in 24-pin plastic DIP and SOP packages

## **GENERAL DESCRIPTION**

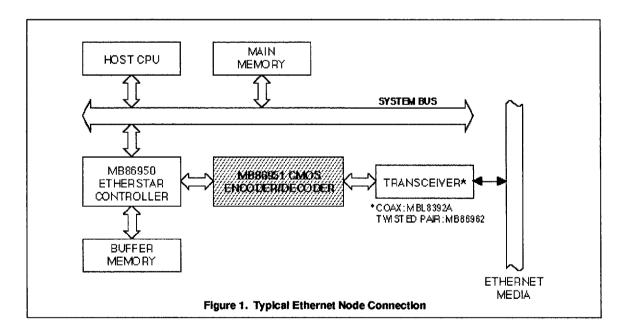

The MB86951 is a 10 Mbit/sec Manchester encoder/decoder that is designed to meet the requirements for Ethernet local area networks. This device, when used with companion chips such as Fujitsu's MB86950 EtherStar<sup>TM</sup> Controller and either the MBL8392A Coaxial Transceiver or the MB86962 Twisted Pair Transceiver (see Figure 1), forms a complete chip set that meets the requirements of the ISO/ANSI/IEEE 8802-3 international standard for Ethernet, Thin Net, and 10BASE-T networks.

The encoder/decoder interfaces with the network controller on the system side and with the transceiver on the network side. It contains a receiver with phase locked loop, a driver, a collision signaling detector, and an oscillator.

During transmit operation, the MB86951 receives NRZ (non-return-to-zero) data from the controller and converts the serial binary data stream into a Manchester encoded stream which is transmitted out on a balanced differential pair to the transceiver. During receive

operation it converts Manchester encoded data on a balanced differential pair from the transceiver into NRZ data and forwards it to the controller, together with a 10 MHz synchronous receive data clock. A phase locked loop is used for clock recovery to allow a worst case jitter of ±20 ns.

The MB86951 is fabricated using Fujitsu's high speed, low power, CMOS technology and is supplied in 24-pin plastic DIP and small outline (SOP) packages.

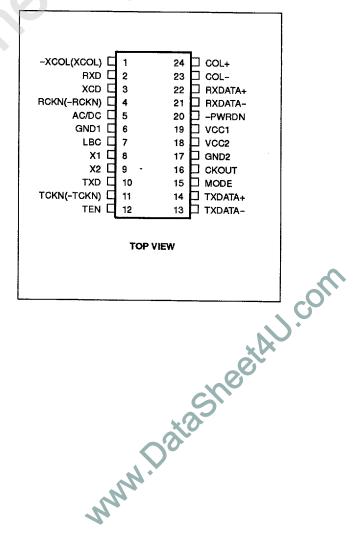

## PIN CONFIGURATION

**3749756 0010882 675**

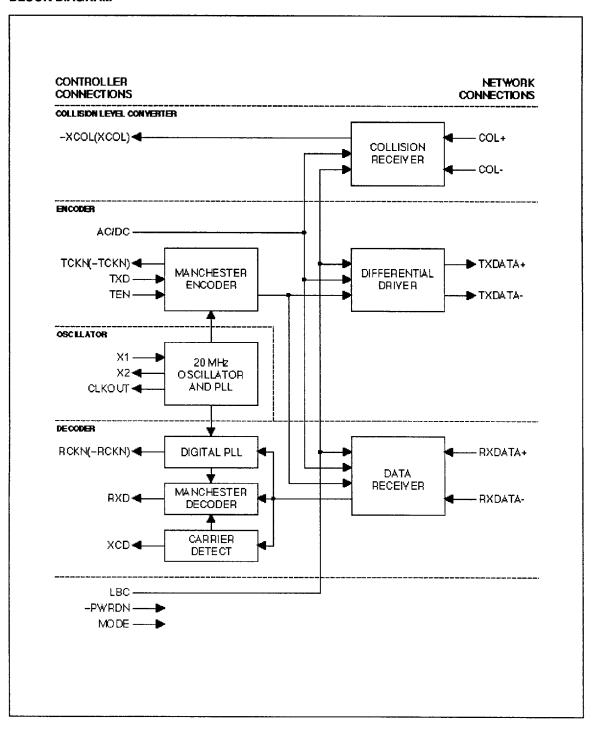

## **BLOCK DIAGRAM**

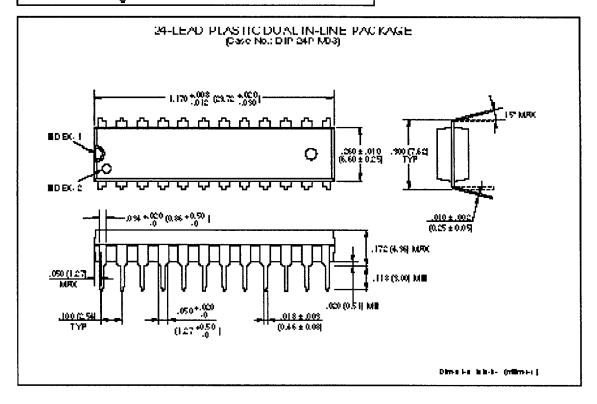

#### **ORDERING CODE**

| PACKAGE STYLE                | PACKAGE CODE | $V_{CC} = +5 \text{ V} \pm 5\%, T_A = 0 \text{ to } +70^{\circ}\text{C}$ |

|------------------------------|--------------|--------------------------------------------------------------------------|

| 24-Pin Plastic Dual In-line  | DIP-24P-M03  | MB86951 P-G                                                              |

| 24-Pin Plastic Small Outline | FPT-24P-M02  | MB86951PF-G                                                              |

#### SIGNAL DESCRIPTIONS

| SYMBOL             | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -XCOL(XCOL)        | 0    | COLLISION PRESENCE: This output indicates that the collision inputs to the MB86951 (COL±) are active, signifying that the transceiver has detected a collision on the media. If MODE = 0, -XCOL(XCOL) is a normally low output which changes to a high state during collision detection. If MODE = 1, -XCOL(XCOL) is a normally high output which changes to a 10 MHz pulse stream during collision detection. See also Mode Control section. |

| RXD                | 0    | RECEIVED SERIAL DATA: Output NRZ serial bit stream from the Manchester decoder. Changes in the state of RXD are synchronous with the rising edge of RCKN if MODE = 0, and synchronous with the falling edge of RCKN if MODE = 1.                                                                                                                                                                                                              |

| XCD                | 0    | RECEIVED CARRIER DETECT: Assertion of this active high output indicates that a carrier has been detected at the RXDATA± inputs.                                                                                                                                                                                                                                                                                                               |

| RCKN(-RCKN)        | 0    | RECEIVED DATA CLOCK: The data clock recovered by the DPLL within the MB86951 while data is being received. RCKN(-RCKN) is a free running 10 MHz clock when the receive inputs are idle. See also Mode Control and Data Decoder sections.                                                                                                                                                                                                      |

| AC/DC              | l    | AC/DC COUPLING SELECT: AC/DC = 0 selects DC coupling, AC/DC = 1 selects AC coupling for the TXDATA± outputs. When AC coupling is selected, both TXDATA+ and TXDATA- are driven to the same output voltage level during transmit idle periods to prevent saturation of the isolation transformer.                                                                                                                                              |

| LBC                | ı    | LOOPBACK CONTROL: When this input is asserted (high) the MB86951 is placed in the loopback mode.                                                                                                                                                                                                                                                                                                                                              |

| X1                 | ı    | CRYSTAL INPUT: Connection for one side of the 20 MHz crystal or input for an external 20 MHz clock.                                                                                                                                                                                                                                                                                                                                           |

| X2                 | 0    | CRYSTAL OUTPUT: Connection for the other side of the 20 MHz crystal. Leave unconnected if an external clock is used.                                                                                                                                                                                                                                                                                                                          |

| TXD                | l    | TRANSMIT SERIAL DATA INPUT: NRZ serial data stream which is fed to the Manchester encoder. Changes in TXD should be synchronized to the rising edge of TCKN(-TCKN) if MODE = 0 and to the falling edge of TCKN(-TCKN) if MODE = 1.                                                                                                                                                                                                            |

| TCKN(-TCKN)        | 0    | TRANSMIT DATA CLOCK: 10 MHz clock output used by the controller to synchronize the TXD input to the MB86951. See also Mode Control and Data Encoder sections.                                                                                                                                                                                                                                                                                 |

| TEN                | ı    | TRANSMIT ENABLE: When asserted (high) TEN enables encoding of the transmitted data.                                                                                                                                                                                                                                                                                                                                                           |

| TXDATA+<br>TXDATA- | 0    | <b>TRANSMIT DATA:</b> These are the Manchester encoded differential outputs to the transceiver. They require $270\Omega$ pulldown resistors and are capable of driving a $78\Omega$ differential transmission line.                                                                                                                                                                                                                           |

| MODE               | ı    | MODE: MODE = 1 selects the normal (Fujitsu-controller compatible) mode. When MODE = 0, the part is functionally and electrically compatible with the National DP83910 and AMD Am7992B. See also Mode Control section.                                                                                                                                                                                                                         |

| CKOUT              | 0    | CLOCK OUTPUT: 20 MHz free running clock output.                                                                                                                                                                                                                                                                                                                                                                                               |

Note: Signal names preceded by a minus sign (-) indicate an active low state. Dual function pins have two names with the second enclosed in parentheses ().

Signal names preceded by a minus sign (-) indicate an active low state. Dual function pins have two names separated by a slash (/).

## SIGNAL DESCRIPTIONS (continued)

| SYMBOL             | TYPE | DESCRIPTION                                                                                                                                                                                                              |

|--------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -PWRDN             | -    | <b>POWER DOWN:</b> Active low input for selecting power down mode. Note: LBC (pin 7) must be 0 during power down, otherwise the device will enter a test mode used by the factory. Tie –PWRDN high for normal operation. |

| RXDATA+<br>RXDATA- | ı    | RECEIVED DATA: These are the Manchester encoded differential inputs to the MB86951 from the transceiver.                                                                                                                 |

| COL+<br>COL-       | 1    | COLLISION: These differential inputs are driven with a 10 MHz signal when the transceiver detects a collision on the medium.                                                                                             |

| V <sub>CC</sub>    |      | POWER SUPPLY: A nominal +5 V <sub>DC</sub> supply is required.                                                                                                                                                           |

| GND                |      | GROUND                                                                                                                                                                                                                   |

Note: Signal names preceded by a minus sign (-) indicate an active low state. Dual function pins have two names with the second enclosed in parentheses ().

## **FUNCTIONAL DESCRIPTION**

The block diagram highlights the major functional blocks of the MB86951: oscillator, data encoder, data decoder, collision signal detector, and loopback control. Figure 1 illustrates a typical interface for the device when driving an AUI (transceiver) cable on the network side and connected to Fujitsu's MB86950 EtherStar controller on the system side.

#### **OSCILLATOR**

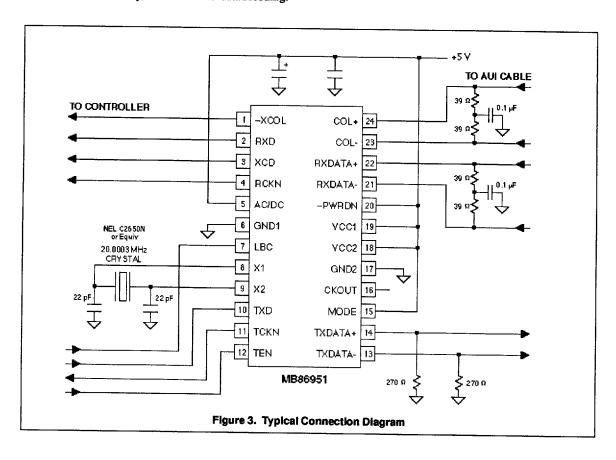

The IEEE 802.3 standard specifies a clock rate of 10 Mbits/sec. This is obtained from a 20 MHz clock generated by the oscillator, which operates from an external crystal reference connected between pins X1 and X2 of the MB86951. Crystal capacitance as specified by the manufacturer should be connected from X1 and X2 to ground, considering any stray capacitance which can vary the crystal's frequency. If an external 20 MHz clock is available, it may be applied to X1 with X2 left unconnected.

The 20 MHz oscillator output is provided on CKOUT for external use. It is also divided by two to produce the required 10 MHz clock, which is used internally and furnished on TCKN(-TCKN) for use by the network controller. The 20 MHz clock also serves as a reference

for an internal phase locked loop used for clock and data recovery in the decoder section.

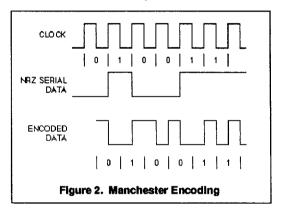

#### **DATA ENCODER**

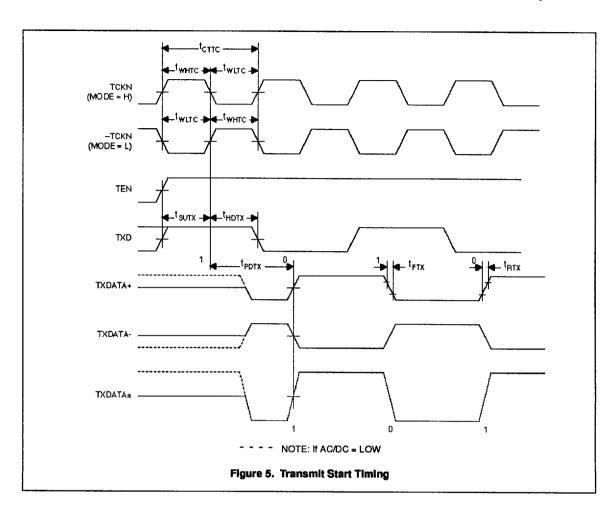

Manchester encoding is used for the transmission of data from the MB86951. Manchester encoding is a binary signaling mechanism that combines data and clock into bit symbols. Each bit symbol is split into two halves, with the signal polarity of the second half being the inverse of that of the first half. A transition always occurs in the middle of each bit symbol, with logic '0' and '1' encoded as 1-to-0 and 0-to-1 transitions respectively. See Figure 2. In the case of the MB86951, the controller asserts

transmit enable (TEN) to indicate that the outgoing packet on TXD is valid data. This NRZ serial data input must be supplied synchronously with the TCKN(-TCKN) clock as required by the setting of MODE. If MODE=1, TXD is valid during the rising edge of TCKN(-TCKN); if MODE=0, TXD is valid during the falling edge. The Manchester-encoded signals are output through a differential driver to the transceiver through TXDATA+ and TXDATA-, and are present as long as the TEN pin remains affirmed.

The differential driver is capable of driving a 50 meter segment of  $78\Omega$  interface cable, as specified in the ISO/ANSI/IEEE 8802-3 standard.  $270\Omega$  resistors are required externally to pull down TXDATA+ and TXDATA-. See Figure 3.

#### **DATA DECODER**

The data decoder section performs three functions on the data received at the differential receive inputs (RXDA-TA+ and RXDATA-) from the transceiver: carrier detection, clock recovery, and Manchester data decoding.

Clock recovery is accomplished by use of phase locked loop circuitry which uses the crystal oscillator as a reference. Use of a PLL provides the most reliable and robust clock recovery. It allows signal acquisition to be accomplished within six bit times from first detection of the signal, and permits stable operation with input signal jitter of up to  $\pm 20$  ns. Carrier detection is indicated to the controller by affirmation of the XCD output, which occurs shortly after a signal appears at the differential inputs.

The recovered clock is supplied to the controller on RCKN(-RCKN), and is also used to convert the Manchester encoded data to NRZ format, which is then output on RXD. The phase relationship between RCKN(-RCKN) and RXD is controlled by the MODE input. Transitions in the state of RXD are synchronous with the rising edge of RCKN(-RCKN) if MODE = 0, and synchronous with the falling edge of RCKN(-RCKN) if MODE = 1. RCKN(-RCKN) is a free running 10 MHz clock when no receive signal is present.

The RXDATA+ and RXDATA- differential inputs must be terminated with two 39 $\Omega$  resistors in series with a 0.1  $\mu$ F bypass capacitor at their junction, as illustrated in Figure 2.

#### **COLLISION SIGNALING DETECTOR**

As collisions are detected on the network media, the transceiver generates a 10 MHz signal on the COL+ and COL- differential inputs to the MB86951. This signal is detected by the MB86951, converted to a logic-level signal appropriate for the controller and output on -XCOL(XCOL). If MODE = 0, -XCOL(XCOL) is normally low and changes to a high state during collision detection. If MODE = 1, -XCOL(XCOL) is normally high and changes to a 10 MHz pulse stream during collision detection.

The COL+ and COL- differential inputs require  $78\Omega$   $\Omega$  termination like that for the RXDATA+ and RXDATA-inputs. See Figure 2.

#### **LOOPBACK**

The loopback control input (LBC) causes transmitted data from the controller to be routed through the internal circuits of the MB86951 and back to the received data output to test for proper system operation. While LBC is affirmed, the encoded transmit data is supplied to the data

decoder instead of the receive data from the RXDATA+ and RXDATA- inputs. Also, the differential transmit drivers and the collision signal detector are disabled. Note that changes in LBC while data is being received may cause errors in the received data output.

#### MODE CONTROL

The MODE input selects one of two modes of operation for the MB86951. The setting of this input changes the phase relationship between certain clocks and signals, and the format of the -XCOL(XCOL) output. The three signal pins which are affected are -XCOL(XCOL), RCKN(-RCKN) and TCKN(-TCKN). MODE =1 selects the normal mode in which these signals are compatible with Fujitsu controllers such as the MB86950. When MODE = 0 the MB86951 is functionally and electrically compatible with the National DP83910 and the AMD Am7992. Polarity of the three signal pins shown in their names in parentheses corresponds to MODE = 0. See the Pin Descriptions section and the timing diagrams at the end of this data sheet for additional information.

#### **POWER DOWN**

The power down mode is selected by driving both -PWRDN (pin 20), and LBC (pin 7) low. In this mode, power consumption is reduced to 6 mA typical.

# **ELECTRICAL CHARACTERISTICS**

## **ABSOLUTE MAXIMUM RATINGS**1,2,3

| Symbol           | Rating                           | Conditions                           | Min.         | Max.                  | Units |

|------------------|----------------------------------|--------------------------------------|--------------|-----------------------|-------|

| Vcc              | Supply voltage                   |                                      | -0.5         | 6.0                   | ٧     |

| V <sub>ITL</sub> | TTL level input voltage          |                                      | -0.5         | V <sub>CC</sub> + 0.5 | ٧     |

| lopf             | Differential output current      |                                      |              | -40                   | mA    |

| T <sub>STG</sub> | Storage temperature              |                                      | -40          | 125                   | °C    |

| T <sub>OP</sub>  | Operating temperature            |                                      | -25          | 85                    | °C    |

| V <sub>DCI</sub> | RxDATA± / COL± DC input voltage  |                                      | 0.5          | 16                    | ٧     |

| V <sub>DCO</sub> | TxDATA± / COL± DC output voltage | with transformer without transformer | -0.5<br>-0.5 | 16<br>10              | V     |

# **RECOMMENDED OPERATING CONDITIONS**

| Symbol          | Parameter                                        | Value           | Units |  |

|-----------------|--------------------------------------------------|-----------------|-------|--|

| TA              | Operating ambient temperature                    | 0 to +70        | °C    |  |

| V <sub>CC</sub> | Supply voltage                                   | 5.0 ± 5%        | V     |  |

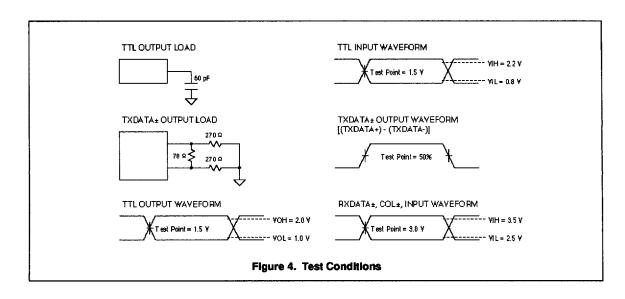

| Юн              | Maximum TTL high level output current            | -2.0            | mA    |  |

| loL             | Maximum TTL low level output current             | 3.2             | mA    |  |

| ₽L              | Driver load resistor (see Figure 4)              | 270             | Ω     |  |

| R <sub>T</sub>  | Differential termination resistor (see Figure 4) | 78              | Ω     |  |

| Cosc            | Oscillator capacitors <sup>5</sup>               | 22              | pF    |  |

| fXTAL           | Oscillator crystal frequency                     | 20.000 ± 0.005% |       |  |

# DC SPECIFICATIONS<sup>3,4</sup> (Recommended Operating Conditions Unless Otherwise Indicated)

| Symbol                                | Parameter                        | Conditions                             | Min.        | Тур.      | Max.            | Units |

|---------------------------------------|----------------------------------|----------------------------------------|-------------|-----------|-----------------|-------|

| lcc                                   | Operating power supply current   | no output load                         | T -         | 30        | 60              | mA    |

| ICCPD                                 | Power down supply current        | no output load<br>-PWRDN=0 , LBC=0     | -           | 6         | 10              | mA    |

| V <sub>IH</sub>                       | TTL high level voltage           |                                        | 2.2         | _         | V <sub>CC</sub> | ٧     |

| $V_{IL}$                              | TTL low level input voltage      |                                        | 0           | _         | 8.0             | ٧     |

| V <sub>OH</sub>                       | TTL high level output voltage    | I <sub>OH</sub> = -2.0 mA              | 4.2         | _         | Vcc             | V     |

| VoL                                   | TTL low level output voltage     | l <sub>OL</sub> = 3.2 mA               | 0           | _         | 0.4             | ٧     |

| ILI                                   | TTL input leakage current        | V <sub>IN</sub> = 0 or V <sub>CC</sub> | -10         | _         | 10              | μА    |

| V <sub>OP</sub>                       | TxDATA± peak output voltage      | R <sub>L</sub> = 270Ω Ω                | ±0.5        | _         | ±1.3            | ٧     |

| V <sub>OB</sub>                       | TxDATA± output voltage imbalance | $R_T = 78\Omega \Omega$                | _           |           | ±40             | m∨    |

| V <sub>СМО</sub>                      | TxDATA± DC common mode output    |                                        | 2.4         | 3.4       | 4.4             | V     |

| V <sub>IT1,</sub><br>V <sub>IT2</sub> | RxDATA± squelch threshold        | AC/DC=0<br>AC/DC=1                     | -80<br>-300 | 0<br>-220 | 80<br>-140      | m∨    |

# DC SPECIFICATIONS<sup>3,4</sup> (Continued)

| Symbol            | Parameter                         | Conditions                                                                                                                           | Min. | Тур. | Max. | Units |

|-------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| V <sub>IP</sub>   | RxDATA ± peak input voltage       |                                                                                                                                      | ±0.3 |      | ±1.5 | V     |

| V <sub>IB</sub>   | RxDATA ± DC input bias voltage    |                                                                                                                                      | 2.2  | 3.2  | 4.2  | ν     |

| I <sub>IHD</sub>  | RxDATA ± input high level current | V <sub>IN</sub> = V <sub>CC</sub>                                                                                                    | _    | _    | 250  | μА    |

| l <sub>ILD</sub>  | RxDATA ± input low level current  | V <sub>IN</sub> = 0                                                                                                                  | _    | _    | -400 | μΑ    |

| V <sub>ITD1</sub> | RxDATA ± input threshold          | AC/DC = Low                                                                                                                          | -80  | 0    | 80   | mV    |

| V <sub>ITD2</sub> |                                   | AC/DC = High <sup>6</sup>                                                                                                            | -300 | -220 | -140 | mV    |

| lccs              | Static power supply current       | -PWRDN = 0, X <sub>1</sub> =V <sub>CC</sub> ,<br>differential inputs open,<br>TTL inputs = 0 or V <sub>CC</sub> ,<br>no output loads | _    | _    | 100  | μΑ    |

| Icc               | Operating power supply current    | No output loads                                                                                                                      | _    | 25   | 50   | mA    |

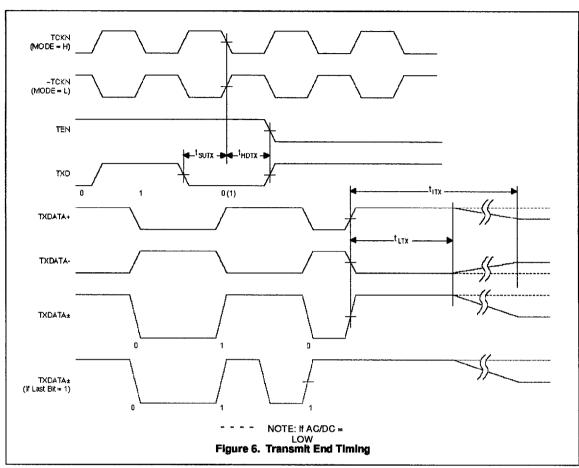

AC CHARACTERISTICS<sup>3,4</sup> (Recommended Operating Conditions Unless Otherwise Indicated) Transmit Timing

| Symbol            | Figure | Parameter Description        | Conditions   | Min.  | Тур. | Max.     | Units |

|-------------------|--------|------------------------------|--------------|-------|------|----------|-------|

| tcttc             | 5      | TCKN cycle time              |              | 99.99 | 100  | 100.01   | ns    |

| twltc             | 5      | TCKN low time                |              | 40    | 50   | 60       | ns    |

| twhtc             | 5      | TCKN high time               |              | 40    | 50   | 60       | ns    |

| t <sub>PDTX</sub> | 5      | TXDATA ± encode time         |              | _     | 95   | _        | ns    |

| t <sub>RTX</sub>  | 5      | TXDATA ± rise time           | 20% to 80%   | _     | 2    | _        | ns    |

| t <sub>FTX</sub>  | 5      | TXDATA ± fall time           | 20% to 80%   | _     | 2    | <b>—</b> | ns    |

| t <sub>LTX</sub>  | 6      | TXDATA ± level hold time     | AC/DC = High | 200   | _    |          | ns    |

| t <sub>ITX</sub>  | 6      | TXDATA ± idling time         | AC/DC = High | _     | _    | 8000     | ns    |

| tsutx             | 5,6    | TXD, TEN setup time to TCKN  |              | 20    | _    | l –      | ns    |

| t <sub>HDTX</sub> | 5,6    | TXD, TEN hold time from TCKN |              | 10    | _    |          | ns    |

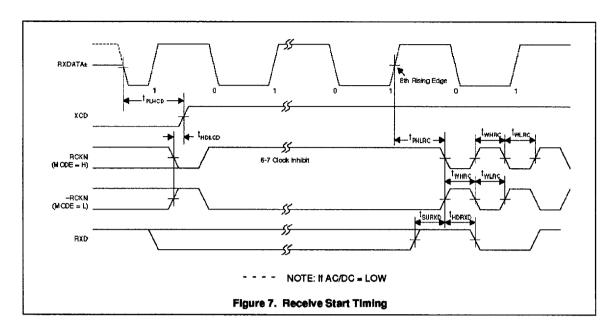

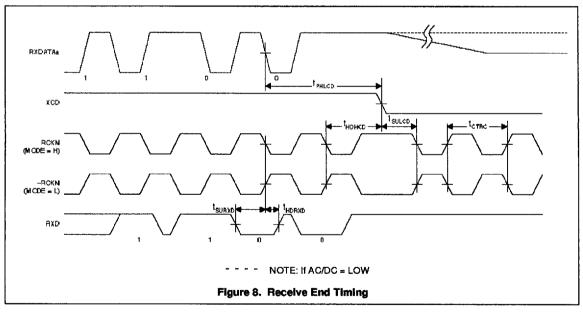

## **Receive Timing**

| Symbol             | Figure | Parameter Description       | Conditions | Min.  | Тур. | Max.   | Units |

|--------------------|--------|-----------------------------|------------|-------|------|--------|-------|

| totro              | 8      | RCKN cycle time during idle |            | 99.99 | 100  | 100.01 | ns    |

| twLRC              | 7      | RCKN low time               |            | 35    | 50   | _      | ns    |

| twhec              | 7      | RCKN high time              |            | 35    | 50   | _      | ns    |

| t <sub>PHLRC</sub> | 7      | RCKN delay time             |            | _     | 125  | _      | ns    |

| t <sub>PLHCD</sub> | 7      | XCD on delay time           |            | _     | 90   | 120    | ns    |

| tPHLCD             | 8      | XCD off delay time          |            | _     | 260  | _      | ns    |

| †HDLCD             | 7      | XCD low hold time           |            | 10    | _    | _      | ns    |

| tHDHCD             | 8      | XCD high hold time          |            | _     | 130  | _      | ns    |

| tsulcd             | 8      | XCD low setup time          |            | _     | 70   |        | ns    |

| tsurxd             | 7,8    | RXD setup time to RCKN      |            | 20    | 60   | _      | ns    |

| t <sub>HDRXD</sub> | 7,8    | RXD hold time from RCKN     |            | 10    | 20   | _      | ns    |

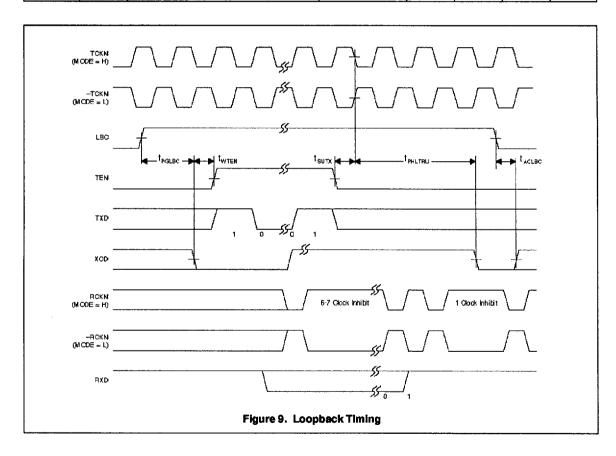

# Loopback Timing<sup>7</sup>

| Symbol  | Figure | Parameter Description              | Conditions | Min. | Тур. | Max.     | Units |

|---------|--------|------------------------------------|------------|------|------|----------|-------|

| tpglbc  | 9      | LBC receiving data purge time      |            | _    | 260  | _        | ns    |

| †ACLBC  | 9      | LBC receiving data accept time     |            | _    | 80   | <b>-</b> | ns    |

| tPHLTRU | 9      | Data through time                  |            | _    | 280  | _        | ns    |

| twten   | 9      | Wait time from XCD low to TEN high |            | 0    | _    | _        | ns    |

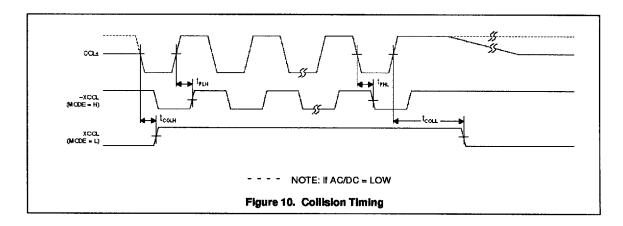

# **Collision Timing**

| Symbol           | Figure | Parameter Description                         | Conditions  | Min. | Тур. | Max. | Units |

|------------------|--------|-----------------------------------------------|-------------|------|------|------|-------|

| tpLH             | 10     | COL± to -XCOL(XCOL)<br>propagation delay time | MODE = High | _    | 15   | 50   | ns    |

| t <sub>PHL</sub> | 10     |                                               | MODE = High | _    | 15   | 50   | ns    |

| tcolh            | 10     |                                               | MODE = Low  |      | _    | 50   | ns    |

| tcoll            | 10     |                                               | MODE = Low  | _    |      | 350  | ns    |

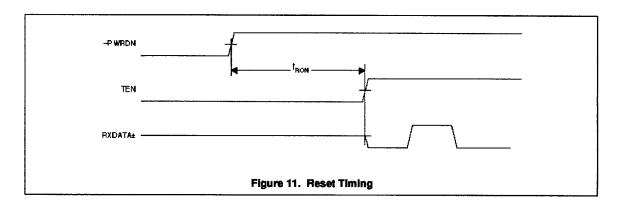

#### **Reset Timina**

| Symbol | Figure | Parameter Description     | Conditions | Min. | Тур. | Max. | Units |

|--------|--------|---------------------------|------------|------|------|------|-------|

| tron   | 11     | Start-up time after reset |            | 200  |      | _    | μs    |

#### Notes:

- Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other condition above those indicated in the operation section of this specification is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods may affect device reliability.

- This product includes circuitry specifically designed for the protection of its Internal devices from damaging effects of excessive static charge. Nonetheless, it is recommended that conventional precautions be taken to avoid applying any voltages larger than the rated maxima.

- 3.

- All voltage measurements are referenced to ground. See Figure 4 for test conditions.

Parameters are valid over specified temperature range and supply voltage range unless otherwise noted.

- The values of the oscillator capacitors may have to be tuned for a particular component layout. However, once the correct values are determined for that layout, tuning for each board is not required. Both capacitors should be adjusted for maximum voltage at X1. The threshold of RXDATA± is changed to V<sub>ITD2</sub> while AC/DC = High. (See DC Specifications for V<sub>ITD2</sub>.)

During loopback operation, the COL± and RXDATA± inputs are ignored and the TXDATA± outputs are idle. XCD remains at a High

- level if MODE = Low.

Ordering Information: MB86951P-G

# Ordering Information: MB86951PF-G