# Digital Signal Processor

**MB87064**

April 1986 Edition 1.0

#### DESCRIPTION

The Fujitsu MB87064 is a general-purpose LSI silicon gate Digital Signal Processor (DSP). The device is fabricated in low-power CMOS and features a high-speed pipelined multiplier, supports concurrent operations with compound instructions and multiple data paths, and offers flexible and expandable memory options. The MB87064 is housed in a 42-pin DIP.

Except for some changes in the instruction set and minor modifications in the hardware, the low-cost MB87064 DSP is a functional clone for Fujitsu's full-featured MB8764 DSP. The low-cost MB87064 is particularly useful in systems where the additional features of the MB8764 are simply not required. Since basic functions of the two parts are identical, this data sheet describes only those differences that affect system design. For complete functional detail pertaining to hardware and software, it is recommended that the user obtain data sheets for both parts (MB87064 and MB8764). If further information regarding Digital Signal Processing is desired, the user should request "Support Documentation for the MB8764" from the nearest Fujitsu sales office.

Both the MB87064 and the MB8764 are well suited for applications such as telecommunications, imaging work, and other signal-processing functions that require extensive computations and complex analysis.

This device contains circulity to protect the inputs against damage due to high static voltages or electric fields. However, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit.

Table 1. Comparison of Features (MB87064 and MB8764)

| Item                     | MB8764                                                                                                                                          | MB87064                                                     |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| Hardware<br>Architecture | Common Hardware Architecture  • Parallel pipelined multiply function 16 bits x 16 bits → 26 bits  • Divide function 26 bits ÷ 16 bits → 16 bits |                                                             |

| Instruction Set          | MB8764 Instruction Set                                                                                                                          | Basically the same as the MB8764 but with few modifications |

| Operation<br>Cycle Time  | 1                                                                                                                                               | 00ns                                                        |

| Package                  | PGA88 Ceramic¹<br>LCC84 Ceramic                                                                                                                 | DIP42 Ceramic <sup>1</sup>                                  |

| D                        | , ,                                                                                                                                             | rogrammable) ROM<br>ords × 24 bits                          |

| Program ROM              | External ROM of 1024 words × 24 bits selectable                                                                                                 | No External ROM function                                    |

| Data RAM                 | Built-in 2 blocks of 128 words × 16 bits<br>Expansion RAM up to 1024 words × 16 bits                                                            | S                                                           |

|                          | 16-bit Par                                                                                                                                      | allel Interface                                             |

| I/O Functions            | Three Input Modes Two Output Modes                                                                                                              | Two Input Modes One Output Mode (Brand-new)                 |

| Addressing               | Same Addressing Functions  Direct Addressing  Immediate Addressing  Indexed Addressing  Virtual Shift Addressing                                |                                                             |

| Support Tools            | Common Support Tools  • Evaluation Board  • Softwares (Assemblers, Linkers, Software Section Board)                                             | Simulators, Monitor)                                        |

| Applications             | Flexible system with external program memory     Small Volume Production with Internal/External ROM     System evaluation before Production     | High Volume Production with Mask ROM                        |

- Notes:

1. Plastic package is scheduled for the future.

2. Soon to be available.

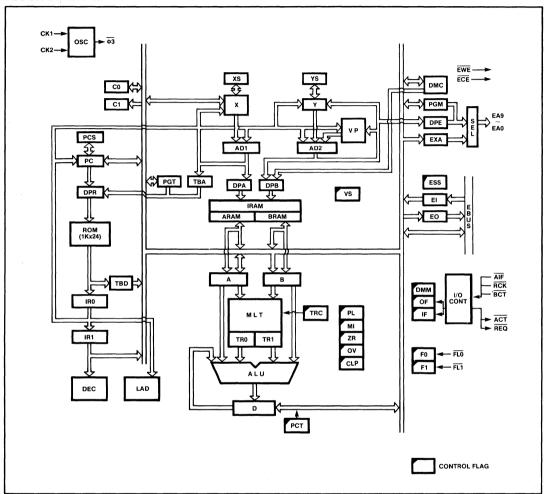

#### **BLOCK DIAGRAM**

#### PIN DESCRIPTIONS

| Pin No. | Designator      | Functio            | n            | Pin No. | Designator | Function                   |       |

|---------|-----------------|--------------------|--------------|---------|------------|----------------------------|-------|

|         |                 | Input/Output Pins: |              |         |            | Output Pins:               |       |

| 09      | D15             | Data bus           | Bit 15 (MSB) | 22      | EA9        | Expansion RAM Address      | MSB   |

| 08      | D14             | Data bus           | Bit 14       | 23      | EA8        | Expansion RAM Address      | Bit 8 |

| 07      | D13             | Data bus           | Bit 13       | 24      | EA7        | Expansion RAM Address      | Bit 7 |

| 06      | D12             | Data bus           | Bit 12       | 25      | EA6        | Expansion RAM Address      | Bit 6 |

| 05      | D11             | Data bus           | Bit 11       | 26      | EA5        | Expansion RAM Address      | Bit 5 |

| 04      | D10             | Data bus           | Bit 10       | 27      | EA4        | Expansion RAM Address      | Bit 4 |

| 03      | D9              | Data bus           | Bit 9        | 28      | EA3        | Expansion RAM Address      | Bit 3 |

| . 02    | D8              | Data bus           | Bit 8        | 29      | EA2        | Expansion RAM Address      | Bit 2 |

| 01      | D7              | Data bus           | Bit 7        | 30      | EA1        | Expansion RAM Address      | Bit 1 |

| 41      | D6              | Data bus           | Bit 6        | 31      | EA0        | Expansion RAM address      | LSE   |

| 40      | D5              | Data bus           | Bit 5        | 34      | EWE        | ERAM Write Clock Output    |       |

| 39      | D4              | Data bus           | Bit 4        | 33      | ECE        | ERAM Chip Enable Output    |       |

| 38      | D3              | Data bus           | Bit 3        | 11      | CK1        | Master Clock Input Pin 1   |       |

| 37      | D2              | Data bus           | Bit 2        | 12      | CK2        | Master Clock Input Pin 2   |       |

| 36      | D1              | Data bus           | Bit 1        | 13      | RST        | Initialization Input       |       |

| 35      | D0              | Data bus           | Bit 0 (LSB)  | 16      | AIF        | Data Input Request         |       |

| 10      | GND             | Circuit Ground     |              | 17      | RCK        | Data Read Clock Input      |       |

| 32      | GND             | Circuit Ground     |              | 18      | ACT        | Data Input Enable Output   |       |

| 42      | V <sub>CC</sub> | +5V Power Supply   |              | 20      | REQ        | Data Bus Request Output    |       |

| 21      | V <sub>CC</sub> | +5B Power Supply   |              | 19      | BCT        | Data Bus Output Enable Inp | ut    |

|         |                 |                    |              | 14      | FLO        | Flag Input                 |       |

|         |                 |                    |              | 15      | FL1        | Flag Input                 |       |

#### PIN MODIFICATIONS

Based on the pin configuration of the MB8764, the following modifications have been made for the MB87064.

Removal of pins caused by no external ROM:

PA9 ~ PA0 (10 pins)

IRM (1 pin)

P23 ~ P0 (24 pins)

TST (1 pin)

Removal of pins caused by reduction/modification of input/output mode:

ASL (1 pin)

AOF (1 pin)

WCK (1 pin)

Removal of pins caused by modification of external RAM speed control (hardware -- software):

ESS (1 pin)

Removal of unneeded power/ground pins:

GND (2 pins)

V<sub>CC</sub> (2 pins)

#### **FUNCTIONAL DESCRIPTION**

#### **Program Memory**

The program for the MB87064 is provided from the internal (mask-programmed) ROM with a capacity of 1024 words × 24 bits. The MB87064 cannot access external ROM.

#### Input/Output Modes

#### Input Modes

Two operating modes (D and P) are used to input data from an external device to the MB87064. The function and timing specification for the two input modes are the same as those in the MB8764. The selected input mode is loaded into the mode (DMM) register by the program.

#### **Output Mode**

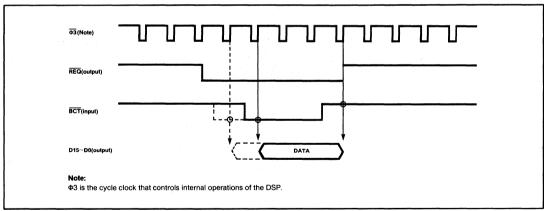

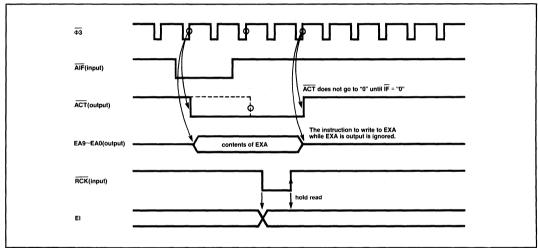

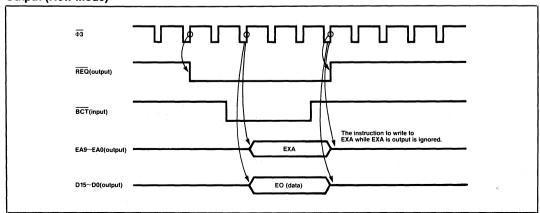

Only one output mode is provided to transfer data from the MB87064 to an external peripheral. The output mode in the MB87064 is a modified version of the E mode in the MB8764. Output mode timing is shown in the following diagram.

#### **Output Mode Timing**

#### Registers/Flags

#### **Register Omission**

Input address register EIA, output address register EA, unit register U, and address mode register ADM are not required in the MB87064.

#### **New Registers and Flags**

ESS Flag. Because the ESS pin has been removed, the MB87064 controls ERAM access speed by the ESS flag which,

in turn, is controlled by the SET/CLR instructions. The lowspeed mode (ESS = 1) is specified by the "SET ESS" instruction. It is cleared by the "CLR ESS" instruction and the highspeed mode (ESS = 0) is then specified. When the device is reset, the high-speed mode is selected by default.

## MB87064

Because the ESS pin has been removed, the MB87064 controls ERAM access speed through the ESS flag. A two cycle access is selected by setting the ESS flag (ESS = 1). and the single cycle access is selected by clearing the ESS flag (ESS = 0).

ESS is cleared upon reset (ESS = 0).

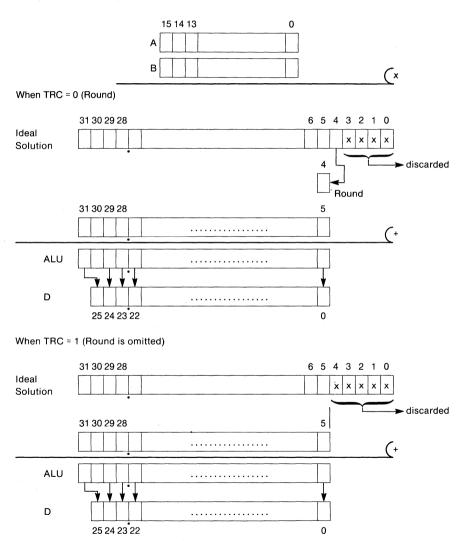

**TRC Register.** The TRC register is a 1-bit register used to control the truncation of the multiplication result. The TRC Register is controlled by the SET/CLR instructions.

When TRC is set to "1", the multiplication result is truncated to 26-bits without rounding. When TRC is set to "0", the result is rounded to 26-bits. (Same as the MB8764.)

**PCT Register.** In the MB8764, even when operating in the CLIP mode with the overflow flag set, if two maximum negative numbers are multiplied together [(8000H) × (8000H)], the resulting output from the D register to IBUS is (0000H). Also, if positive or negative overflows occur, the resulting

output may not be the maximum positive or negative values [(8000H) or (7FFFH)]. The MB87064 selects the PCT (protect mode) to avoid this overflow problem. The protect mode is controlled by the "PCT" flag. The "PCT" flag is set by the "SET PCT" instruction and cleared by the "CLR PCT" instruction.

The "PCT" flag is also cleared by a reset input. As with the MB8764, the normal mode is selected when the "PCT" flag is cleared.

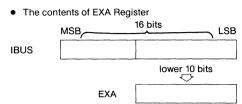

**EXA Register.** The MB8764 outputs the contents of page register PGM and data pointer register DPE to the EA9  $\sim$  EA0 pins regardless of ERAM access.

The MB87064 outputs the contents of PGM and DPE when ERAM is being accessed and outputs the contents of EXA when the I/O bus is being accessed for data transfer to-or-from an external circuit.

- · Timing Specifications

- When ERAM is accessed:

Same as MB8764 (input/output)

- When I/O bus is accessed:

See the following timing diagram:

# Input (P Mode/D Mode)

# **Output (New Mode)**

# Chip Enable Control Output (ECE)

In the MB8764,  $\overline{\text{ECE}}$  is always set to "0" (expansion RAM enable state) except when the I/O bus is being accessed for data transfer to-or-from an external circuit. In the MB87064,  $\overline{\text{ECE}}$  is set to "0" only when ERAM is being accessed. This modification helps to reduce the power consumption of ERAM.

#### Hi-Impedance State of EA9 ~ EA0

Pins EA9 ~ EA0 are placed in the high-impedance state when

#### **INSTRUCTION SET MODIFICATIONS**

The MB87064 has the same instruction set as the MB8764 except for the following modifications to the SET/CLR and MOV instructions.

#### SET/CLR Instructions

According to ADM flag removal, the following instructions are removed:

neither ERAM nor I/O bus is accessed. This avoids address bus conflicts when multiple DSPs are used.

### Reset Input According to FL0 and FL1 Status

The Reset signal (RST) must be input while FLO and FLT are set to "1". The operation of the reset input flag is the same as the MB8764.

SET ADM

The following instructions are added:

SET ESS CLR ESS SET TRC CLR TRC SET PCT CLR PCT

Object code of SET instruction

| MSB                 |       |       | LSB   |

|---------------------|-------|-------|-------|

| 1 1 1 0 1 0 0 0 0 0 | 0 0 0 | 0 0 0 |       |

|                     | a h   | С Д   | e fah |

| а | b | С | d | е | f | g | h | set register |       |

|---|---|---|---|---|---|---|---|--------------|-------|

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | DMM          |       |

| 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | PCT          | ← new |

| 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | VS           |       |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | ESS          | ← new |

| 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | CLP          |       |

| 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | TRC          | ← new |

|   |   |   |   |   |   |   |   |              |       |

Object code of CLR instruction

| MSB       |      |      |      |      |      |      |       |   | L | SB |

|-----------|------|------|------|------|------|------|-------|---|---|----|

| 1 1 1 0 0 |      |      |      |      |      |      |       |   |   |    |

|           | <br> | <br> | <br> | <br> | <br> | <br> | <br>_ | ~ | _ | _  |

# MB87064

| а | b | С | d | е | f | g | h | i | j | k | ı | m | n | 0 | р | q | r | s | cleared register |       |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|------------------|-------|

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | D                |       |

| 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | F0               |       |

| 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | F1               |       |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | DMC              |       |

| 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | Α .              |       |

| 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | В                |       |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | X                |       |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | Y                |       |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | DMM              |       |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | PCT              | ← new |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | IF               |       |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | OF               |       |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | vs               |       |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | ESS              | ← new |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | OV               |       |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | CLP              |       |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | TRC              | ← new |

• multiple registers can be specified

• execution cycle: one

#### **MOV** Instruction

According to the EXA register addition, the destination of EXA register is added to the following MOV instruction:

MOV[:arithmetic/logic operation]\$a(8)[([Y][E])],Reg[:Reg[:...]...]

machine code

MSB

LSB

0 1 0 0 - c - t - t - E Y - a - E Y

a: RAM address c: operation

t: destination

|   |   | 1 | t |   |   | destination register            |

|---|---|---|---|---|---|---------------------------------|

| 1 | 0 | 0 | 0 | 0 | 0 | EO                              |

| 0 | 1 | 0 | 0 | 0 | 0 | A                               |

| 0 | 0 | 1 | 0 | 0 | 0 | В                               |

| 0 | 0 | 0 | 1 | 0 | 0 | D                               |

| 0 | 0 | 0 | 0 | 1 | 0 | EXA (lower 10 bits of RAM data) |

← new

<sup>•</sup> Two or more destination registers can be selected at once.

#### **MOV Instruction (Cont.)**

• An arithmetic/logic operation cannot be performed when the destination register is D.

According to EXA register addition, the processing of "d → EXA" is added.

|    | ١  | ИΟ | V # | \$d, | ,Re | g |   |  |  |   |   |   |   |     |  |   |   |   |     |

|----|----|----|-----|------|-----|---|---|--|--|---|---|---|---|-----|--|---|---|---|-----|

| m  | na | ch | ine | со   | de  |   |   |  |  |   |   |   |   |     |  |   |   |   |     |

| Ν  | 18 | В  |     |      |     |   |   |  |  |   |   |   |   |     |  |   |   |   | LSB |

| [- | 1  | 1  | 1   | 1    | ļ ' | t | 1 |  |  | , | 1 | 1 | d | . 1 |  | 1 | 1 | , | 1   |

|   | t |   | processing              | mnemonic          |

|---|---|---|-------------------------|-------------------|

| 0 | 0 | 0 | d → EO                  | MOV #\$d,EO       |

| 0 | 0 | 1 | output instruction      | MOV #\$d,EA(Note) |

| 0 | 1 | 0 | $d \rightarrow D$       | MOV #\$d,D        |

| 0 | 1 | 1 | $d \rightarrow B$       | MOV #\$d,B        |

| 1 | 0 | 1 | d(lower ten bits) → EXA | MOV #\$d,EXA      |

← new

#### Note:

Though the EA register does not exist, this instruction does exist in the MB87064 to maintain compatibility of output instruction with MB8764. This instruction is only effective as an output instruction and the processing of "d -> EA" is ignored.

#### **ELECTRICAL CHARACTERISTICS**

#### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

|                       |                  | Value |                                    |      |  |  |  |  |

|-----------------------|------------------|-------|------------------------------------|------|--|--|--|--|

| Parameter             | Symbol           | Min   | Max                                | Unit |  |  |  |  |

| Power Supply Voltage  | V <sub>CC</sub>  | -0.32 | 6.0                                | V    |  |  |  |  |

| Input Voltage         | V <sub>I</sub>   | -0.32 | V <sub>CC</sub> + 0.3 <sup>2</sup> | V    |  |  |  |  |

| Output Voltage        | V <sub>O</sub>   | -0.32 | V <sub>CC</sub> + 0.3 <sup>2</sup> | V    |  |  |  |  |

| Operating Temperature | T <sub>OP</sub>  | -40   | 85                                 | °C   |  |  |  |  |

| Storage Temperature   | T <sub>STG</sub> | -55   | 150                                | °C   |  |  |  |  |

- 1. Permanent device damage may occur if the absolute maximum ratings are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2. This value applies for a steady-state condition. The incremental voltage can be increased to a value of 0.5V for periods not to exceed 20-to-30 nanoseconds.

#### RECOMMENDED OPERATING CONDITIONS

|                       |                 |     | Value |     |      |

|-----------------------|-----------------|-----|-------|-----|------|

| Parameter             | Symbol          | Min | Тур   | Max | Unit |

| Power Supply Voltage  | V <sub>CC</sub> | 4.5 | 5.0   | 5.5 | ٧    |

| Operating Temperature | T <sub>OP</sub> | -40 |       | 85  | °C   |

## **DC CHARACTERISTICS**

(Recommended Operating Conditions unless otherwise specified.)

# Operating Temperature Range = 0°C to 70°C

|                                                  |                   |                            |      | Value |                       |      |

|--------------------------------------------------|-------------------|----------------------------|------|-------|-----------------------|------|

| Parameter                                        | Symbol            | Condition                  | Min  | Тур   | Max                   | Unit |

| Input High Voltage                               | V <sub>IH</sub>   | Other than CK1, CK2        | 2.2  |       | V <sub>CC</sub> + 0.3 | V    |

| iliput riigii voltage                            | V <sub>IHCK</sub> | CK1, CK2                   | 4.0  |       | V <sub>CC</sub> + 0.3 | V    |

| Innut Law Voltage                                | V <sub>IL</sub>   | Other than CK1, CK2        | -0.3 |       | 0.8                   | V    |

| Input Low Voltage                                | V <sub>ILCK</sub> | CK1, CK2                   | -0.3 |       | 0.6                   | V    |

| Output High Voltage                              | V <sub>OH</sub>   | I <sub>OH</sub> = -0.4mA   | 2.7  |       | V <sub>CC</sub>       | V    |

| Output Low Voltage                               | V <sub>OL</sub>   | I <sub>OL</sub> = 2mA      | 0    |       | 0.4                   | V    |

| Input Leakage Current                            | ILI               | V <sub>I</sub> = 0 to 5.5V | -10  |       | 10                    | μΑ   |

| Input Leakage Current<br>(Three-state Pin Input) | I <sub>LZ</sub>   | V <sub>i</sub> = 0 to 5.5V | -20  |       | 20                    | μΑ   |

| Static Power Supply Current                      | Iccs              |                            |      | 10    |                       | μΑ   |

| Power Supply Current                             | Icc               | f <sub>OP</sub> = 8MHz     |      | 50    |                       | mA   |

#### Operating Temperature Range = -40°C to 85°C

|                                                  |                   |                                  | Value |     |                       |      |

|--------------------------------------------------|-------------------|----------------------------------|-------|-----|-----------------------|------|

| Parameter                                        | Symbol            | Condition                        | Min   | Тур | Max                   | Unit |

| Input High Voltage                               | V <sub>IH</sub>   | Other than CK1, CK2              | 2.8   |     | V <sub>CC</sub> + 0.3 | V    |

|                                                  | V <sub>IHCK</sub> | CK1, CK2                         | 4.0   |     | V <sub>CC</sub> + 0.3 | V    |

| Input Low Voltage                                | V <sub>IL</sub>   | Other than CK1, CK2              | -0.3  |     | 0.8                   | V    |

|                                                  | V <sub>ILCK</sub> | CK1, CK2                         | -0.3  |     | 0.6                   | ٧    |

| Output High Voltage                              | V <sub>OH</sub>   | I <sub>OH</sub> = -0.4mA         | 2.7   |     | V <sub>CC</sub>       | V    |

| Output Low Voltage                               | V <sub>OL</sub>   | I <sub>OL</sub> = 2mA            | 0     |     | 0.4                   | ٧    |

| Input Leakage Current                            | ILI               | V <sub>1</sub> = 0 to 5.5V -25   |       | 25  | μΑ                    |      |

| Input Leakage Current<br>(Three-state Pin Input) | I <sub>LZ</sub>   | V <sub>1</sub> = 0 to 5.5V -40 4 |       | 40  | μΑ                    |      |

| Static Power Supply Current                      | Iccs              |                                  |       | 50  |                       | μΑ   |

| Power Supply Current                             | Icc               | f <sub>OP</sub> = 8MHz           |       | 60  |                       | mA   |

#### INPUT/OUTPUT CAPACITANCE

$(V_{CC} = V_I = 0V, f_{OP} = 8MHz)$

|            |           | Symbol           |     | Value |     | Unit |

|------------|-----------|------------------|-----|-------|-----|------|

|            | Parameter |                  | Min | Тур   | Max |      |

| Input Pin  |           | C <sub>IN</sub>  |     |       | 6   | pF   |

| Output Pin |           | C <sub>OUT</sub> |     |       | 6   | pF   |

| I/O Pin    |           | C <sub>I/O</sub> |     |       | 8   | pF   |

# **Package Dimension**