# **Preliminary**

# **Advanced Products**

# **FUJITSU**

**■ MB89311**

CMOS Floppy Disk Controller/Formatter

October 1986 Edition 1.0

#### Description

The Fujitsu MB89311 is a floppy disk controller/formatter (FDC) designed as an enhanced version of the conventional MB8877A.

The MB89311 is designed based on the MB8877A architecture. Some inconveniences of the MB8877A are eliminated on the MB89311, and several new commands are added. It can support micro- (3" or 3.5" double-density), mini- (5.25" double-density), and standard (8" single- or double-density), floppy disk drives. When combined with the MB4107 variable frequency oscillator (VFO), an economical floppy disk drive interface can be created with a minimum of parts.

The MB89311 is fabricated by the silicon-gate CMOS process, and packaged in a 28-pin plastic DIP. It has TTL compatible inputs/outputs. Operation is with a single +5V power supply with low power consumption.

#### **Features**

- Single +5V power supply

- TTL compatible I/O

- IBM & ISO compatible disk formats

- Track seeking with automatic verification

- Multiple-sector read/write operation

- Track read/write/initialize operation

- Program/DMA data transfer

- Single density/double density

#### **Enhancements**

- Silicon-gate CMOS process

- 28-pin plastic DIP (Suffix -P)

- Built-in programmable write precompensation (125ns/250ns for all tracks at CLK = 8MHz, 250ns/500ns at CLK = 4MHz)

- For lost data error, abnormal termination after sector read or write completion

- Extended mode commands: Read-after-seek, write-afterseek, delay, and format commands are added.

- No restrictions on the RCLK frequency in gap between ID and data fields.

- Step rate: 1ms to 30ms, Settling time: 15ms to 60ms

- Record length: 128, 256, 512, 1024, 2048, 4096, and 8192 bytes/sector

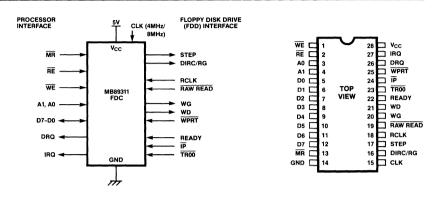

# Logic Symbol and Pin Assignment

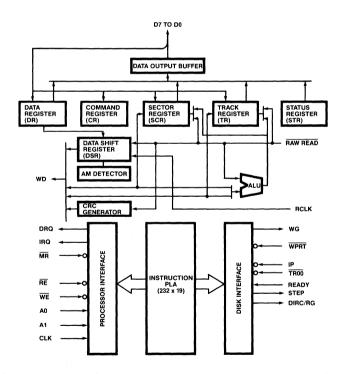

#### **Block Diagram**

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit.

#### **Pin Descriptions**

The MB89311 FDC has two interfaces: One is the processor interface; MR, RE, WE, and A1 & A0 inputs, D7-D0 inputs/outputs, and DRQ &

14

IRQ outputs which are used for the processor to control the FDC. The other is the floppy disk drive (FDD) interface; STEP, DIREC/RG,

WG, and WD outputs, and RCLK, RAW READ, WPRT, READY, TR00, IP inputs, which are used for the FDC to control the FDD.

# **Power Supply & Clock**

$V_{SS}$

IRQ

27

0

#### Name & Function Symbol Number Type 28 +5Vdc power supply pin. $V_{CC}$

| Processor | Interface |

|-----------|-----------|

| CLK | 15 | · I | 4MHz frequencies are required for 500K bits/s data transfer rate in MFM (250K bits/s in FM) and 250K bits/s in MFM (125K bits/s in FM). The CLK signal is required also during a reset. |  |  |  |  |  |

|-----|----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| MR  | 13 | 1   | Master Reset: A low level on this pin stops FDC operation, and initializes its internal state. The CLK signal is required also during                                                   |  |  |  |  |  |

a reset.

resistor.

Clock input: Basic timing clock for internal circuits. 8MHz and

Interupt Request: Set when a command completes, terminates, or a force interrupt command is specified. This pin is an

Power supply ground pin.

| RE     | 2    | ı   | Read Enable: Strobe signal for reading data from the internal register addressed by A1 and A0.                                                                                            |

|--------|------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WE     | 1    | 1   | Write Enable: Strobe signal for writing data into the internal register addressed by A1 and A0.                                                                                           |

| A1, A0 | 4, 3 | ı   | Register Select Line: Signal for addressing an internal register (CR, STR, TR, SCR, or DR).                                                                                               |

| D7-D0  | 12-5 | I/O | Data Access Line: 8-bit bidirectional three-state data bus. These lines go to a high impedance state when RE and WE are high.                                                             |

| DRQ    | 26   | 0   | Data Request: Notifies the processor when new data must be read from or written into the data register. This pin is an open-drain output and must be pulled up by an external $10k\Omega$ |

# Floppy Disk Drive Interface

| IRQ     | 27   | 0 | open-drain output and must be pulled up by an external 10k $\Omega$ resistor. Undefined at power-on.                                                                                         |

|---------|------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STEP    | 17   | 0 | Step: Signal for moving disk head. One pulse is generated to move the head by one track.                                                                                                     |

| DIRC/RO | G 16 | 0 | Direction/Read Gate: During disk head operations, when this signal is low, the head moves to the outside, and when high, to the inside. During read operations, when this signal is high, it |

| DIRC/RG  | 16   | 0   | signal is low, the head noves to the dustice, and when high, to<br>the inside. During read operations, when this signal is high, it<br>indicates that read data has been synchronized. |

|----------|------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RCLK     | 18   | ı   | Read Clock: A data window signal for the raw read data from disk. This signal is generated by an external VFO circuit.                                                                 |

| RAW REAL | D 19 | l   | Raw Read Data: Serial raw data read from disk, containing clock and data bits.                                                                                                         |

| WG       | 20   | 0   | Write Gate: This signal is high when valid data is being written to disk.                                                                                                              |

| WD       | 21   | 0   | Write Data: Serial write data pulses to be written to disk.                                                                                                                            |

| WPRT     | 25   | I   | Write Protect: Signal for inhibiting write operation to disk. When this signal is low, write operation is disabled.                                                                    |

| READY    | 22   | l , | Ready: When this signal is high, the disk drive is ready for operation. Commands except for Type I commands can be executed if this signal is high.                                    |

| TR00     | 23   | ı   | Track 00: When this signal is low, it indicates that the disk head is positioned at track 00.                                                                                          |

| ĪP       | 24   | 1   | Index Pulse: Pulsed low each time the index hole of the floppy disk is detected.                                                                                                       |

#### **Functional Description**

#### **Register Set**

The MB89311 FDC contains the following five registers to execute commands and indicate status:

- Command register (CR)Status register (STR)

- Track register (TR)

- Sector register (SR)

Data register (DR)

These registers are addressed by register select lines A1 and A0 under RE and WE control.

#### **Command Words**

The FDC's operations are defined by commands, that **Register Selection**

| A1 | AO | Read Mode (RE = 0) | Write Mode (WE = 0) |

|----|----|--------------------|---------------------|

| 0  | 0  | Status register    | Command register    |

| 0  | 1  | Track register     | Track register      |

| 1  | 0  | Sector register    | Sector register     |

| 1  | 1  | Data register      | Data register       |

are divided into four groups: Types I, II, III, and IV. Each group contains one to five command(s). Each command has flags that define detailed operation of the command.

The FDC has two command modes, the 8877 mode (which emulates the MB8877 command set) and the extended mode (in which additional commands can be used). Either of these two modes can be selected by the assign command.

#### Command Summary (1): 8877 Mode Command Set

|      |                  | MSB LSB |   |   |   |    |    |    |    | Function                           |  |  |

|------|------------------|---------|---|---|---|----|----|----|----|------------------------------------|--|--|

| Type | Name             |         |   |   |   |    |    |    | SB |                                    |  |  |

|      | Restore          | 0       | 0 | 0 | 0 | Х  | ٧  | r1 | r0 | Moves head to track 0.             |  |  |

|      | Seek             | 0       | 0 | 0 | 1 | Χ  | ٧  | r1 | r0 | Moves head to a desired track.     |  |  |

| 1    | Step             | 0       | 0 | 1 | u | Х  | ٧  | r1 | r0 | Moves head one track.              |  |  |

|      | Step-in          | 0       | 1 | 0 | u | Х  | ٧  | r1 | r0 | Moves head one track to inside.    |  |  |

|      | Step-out         | 0       | 1 | 1 | u | Х  | ٧  | r1 | r0 | Moves head one track to outside.   |  |  |

| II   | Read data        | 1       | 0 | 0 | m | S  | Ε  | С  | L  | Reads data (data field) from disk. |  |  |

| 11   | Write data       | 1       | 0 | 1 | m | S  | E  | С  | a0 | Writes data (data field) to disk.  |  |  |

|      | Read address     | .1      | 1 | 0 | 0 | 0  | E  | 0  | 0  | Reads ID field from disk.          |  |  |

| Ш    | Read track       | 1       | 1 | 1 | 0 | 0  | E  | 0  | 0  | Reads all data from one track.     |  |  |

|      | Write track      | 1       | 1 | 1 | 1 | 0  | Е  | 0  | 0  | Writes all data to one track.      |  |  |

|      | Assign parameter | 1       | 1 | 1 | 1 | 1  | 1  | 0  | 1  | Selects operation timing.          |  |  |

| IV   | Assign mode      | 1       | 1 | 1 | 1 | 1  | 1  | 1  | 0  | Selects operation mode.            |  |  |

|      | Force interrupt  | 1       | 1 | 0 | 1 | 13 | 12 | 11 | 10 | Generates interrupt (IRQ).         |  |  |

|      |                  |         |   |   |   |    |    |    |    |                                    |  |  |

# Functional Description (Continued)

## Command Summary (2): Extended Mode Command Set

|      |                  |     | od | e |   |    |    |    |    |                                       |  |  |

|------|------------------|-----|----|---|---|----|----|----|----|---------------------------------------|--|--|

| Type | Name             | MSB |    |   |   |    |    |    | SB | Function                              |  |  |

|      | Restore          | 0   | 0  | 0 | 0 | 0  | ٧  | 0  | 0  | Moves head to track 0.                |  |  |

|      | Seek             | 0   | 0  | 0 | 1 | 0  | ٧  | 0  | 0  | Moves head to a desired track.        |  |  |

| l .  | Step             | 0   | 0  | 1 | u | 0  | ٧  | 0  | 0  | Moves head one track.                 |  |  |

|      | Step-in          | 0   | 0  | 1 | u | 0  | ٧  | 0  | 1  | Moves head one track to inside.       |  |  |

|      | Step-out         | 0   | 0  | 1 | u | 0  | ٧  | 1  | 0  | Moves head one track to outside.      |  |  |

|      | Read-after-seek  | 0   | 1  | 0 | 0 | S  | 1  | С  | L  | Reads one sector data after seek.     |  |  |

|      | Write-after-seek | 0   | 1  | 1 | 0 | S  | 1  | С  | a0 | Writes one sector data after seek.    |  |  |

| 11   | Read data        | 1   | 0  | 0 | m | S  | E  | С  | L  | Reads data (data field) from disk.    |  |  |

|      | Write data       | 1   | 0  | 1 | m | S  | E  | С  | a0 | Writes data (data field) to disk.     |  |  |

|      | Read address     | 1   | 1  | 0 | 0 | 0  | Е  | 0  | 0  | Reads ID field from disk.             |  |  |

| Ш    | Read track       | 1   | 1  | 1 | 0 | 0  | E  | 0  | 0  | Reads all data from one track.        |  |  |

| 111  | Write track      | 1   | 1  | 1 | 1 | 0  | Ε  | 0  | 0  | Writes all data to one track.         |  |  |

|      | Format           | 1   | 1  | 1 | 1 | 0  | Ε  | 0  | 1  | Formats disk.                         |  |  |

|      | Delay            | 1   | 1  | 1 | 1 | 1  | 1  | 0  | 0  | Generates interrupt after a set time. |  |  |

|      | Assign parameter | 1   | 1  | 1 | 1 | 1  | 1  | 0  | 1  | Selects operation timing.             |  |  |

| IV   | Assign mode      | 1   | 1  | 1 | 1 | 1  | 1  | 1  | 0  | Selects operation mode.               |  |  |

|      | Reset            | 1   | 1  | 1 | 1 | 1  | 1  | 1  | 1  | Resets FDC.                           |  |  |

|      | Force interrupt  | 1   | 1  | 0 | 1 | 13 | 12 | 11 | 10 | Generates interrupt (IRQ).            |  |  |

## Flag Summary

| Туре | Symbol | Function                    |

|------|--------|-----------------------------|

|      | u      | Update of track register    |

| ı    | V      | Verify at destination track |

|      | r1, r0 | Step rate of STEP pulse     |

|      | m      | Multiple sectors            |

| 11   | S      | Side number                 |

|      | a0     | Data address mark           |

| 111  | С      | Side compare                |

| 111  | L      | Long read (CRC read)        |

| IV   | 13-10  | Interrupt                   |

|      |        |                             |

#### **Functional Description**

#### Status Words

Status words, which are automatically held in the status register, show the status of the executing command, executed command, and conditions of the FDD. The system processor can monitor the FDC operations

and FDD conditions, reading the status register.

When the FDC receives a command, the status register is automatically preset at the

start of the command execution. Each status bit is internally updated (set or reset) during the command execution, and the status word is established at the completion of the command.

| Status W | ord Summary                       |                                     |                                            |              |               |                   |              |                 |      |  |  |

|----------|-----------------------------------|-------------------------------------|--------------------------------------------|--------------|---------------|-------------------|--------------|-----------------|------|--|--|

|          |                                   | Status                              | s Bit                                      |              |               |                   |              |                 |      |  |  |

| Comma    | and                               | STR7                                | STR6                                       | STR5         | STR4          | STR3              | STR2         | STR1            | STRO |  |  |

| Type I   | All commands                      | Not<br>Ready                        | Write<br>Protect                           | 1            | Seek<br>Error | CRC<br>Error      | Track<br>00  | Index           | Busy |  |  |

| Type II  | Read data &<br>Read-after-seek    | Not<br>Ready                        | D/M<br>N/F                                 | Rec.<br>Type | Rec.<br>N/F   | CRC<br>Error      | Lost<br>Data | Data<br>Request | Busy |  |  |

| Type II  | Write data &<br>Write-after-seek  | Not<br>Ready                        | 0                                          | 0            | Rec.<br>N/F   | CRC<br>Error      | Lost<br>Data | Data<br>Request | Busy |  |  |

|          | Read address                      | Not<br>Ready                        | 0                                          | 0            | Rec.<br>N/F   | CRC<br>Error      | Lost<br>Data | Data<br>Request | Busy |  |  |

| Type III | Read track                        | Not<br>Ready                        | Write<br>Protect                           | 0            | 0             | 0                 | Lost<br>Data | Data<br>Request | Busy |  |  |

|          | Write track                       | Not<br>Ready                        | Write<br>Protect                           | 0            | 0             | 0                 | Lost<br>Data | Data<br>Request | Busy |  |  |

|          | Format                            | Not<br>Ready                        | Write<br>Protect                           | 0            | 0             | lllegal<br>Length | Lost<br>Data | Data<br>Request | Busy |  |  |

|          | Force —                           | In acco                             | In accordance with the executing commands. |              |               |                   |              |                 |      |  |  |

| Tuna IV  | Interrupt                         | Not<br>Ready                        | Write<br>Protect                           | 0            | 0             | 0                 | Track<br>00  | Index           | 0    |  |  |

| Type IV  | Reset command & Master reset      | In accordance with Type I commands. |                                            |              |               |                   |              |                 |      |  |  |

|          | Delay, Assign<br>Parameter & Mode | Not<br>Ready                        | 0                                          | 0            | 0             | 0                 | 0            | 0               | Busy |  |  |

Notes: Rec. = Record, N/F = Not Found

D/M N/F = Daṭa Mark Not Found. This status bit is valid in extended mode only. In 8877 mode, this bit is "0".

# Functional Description (Continued)

#### **Status Bit Function Summary**

| Command      | Status                  | Status<br>Bit | Function                                                                              |

|--------------|-------------------------|---------------|---------------------------------------------------------------------------------------|

|              | Not Ready               | STR7          | 1 = FDD is not ready: Not Ready = READY + MR.                                         |

|              | Write Protect           | STR6          | 1 = Write operation is inhibited: Write Protect = WPRT.                               |

|              | Seek Error              | STR4          | 1 = Verify operation was unsuccessful.                                                |

| Type I       | CRC Error               | STR3          | 1 = CRC check error occurred.                                                         |

|              | Track 00                | STR2          | 1 = Disk head is positioned at track 0: Track 00 = TR00.                              |

|              | index                   | STR1          | 1 = Index hole was detected. Index = INP                                              |

|              | Busy                    | STR0          | 1 = FDC is executing a command.                                                       |

|              | Not Ready               | STR7          | 1 = FDD is not ready. Not Ready = READY + MR.                                         |

|              | Write Protect           | - STR6        | 1 = Write operation is inhibited. Write Protect = WPRT.                               |

|              | Data Mark<br>Not Found* | - 51HD        | Data mark was not found within required byte interval after ID mark detection.        |

|              | Record Type             | STR5          | 1 = Data address mark was deleted data mark.                                          |

| Type II<br>& | Record<br>Not Found     | STR4          | 1 = Desired track and sector were not found.                                          |

| Type III     | CRC Error               | STR3          | 1 = CRC check error occurred.                                                         |

|              | Lost Data               | STR2          | 1 = Data was not read from or written to data register within required time interval. |

|              | Data Request            | STR1          | 1 = DRQ is currently active. Data Request = DRQ.                                      |

|              | Busy                    | STR0          | 1 = FDC is executing a command.                                                       |

<sup>\*</sup>For read data and read-after-seek commands in extended mode only.

## Absolute Maximum Ratings (Note)

#### Rating

|                       |                  | nat                  | ····9                |      |                                         |

|-----------------------|------------------|----------------------|----------------------|------|-----------------------------------------|

| Parameter             | Symbol           | Min                  | Max                  | Unit | Note                                    |

| Supply Voltage        | V <sub>CC</sub>  | V <sub>SS</sub> -0.3 | V <sub>SS</sub> +7.0 | V    |                                         |

| Supply Vollage        | V <sub>SS</sub>  |                      | 0                    | ٧    |                                         |

| Input Voltage         | V <sub>IN</sub>  | V <sub>SS</sub> -0.3 | V <sub>SS</sub> +7.0 | V    | Should not exceed V <sub>CC</sub> +0.5V |

| Output Voltage        | V <sub>OUT</sub> | V <sub>SS</sub> -0.3 | V <sub>SS</sub> +7.0 | V    | Should not exceed V <sub>CC</sub> +0.5V |

| Operating Temperature | T <sub>A</sub>   | -40                  | +85                  | °C   |                                         |

| Storage Temperature   | T <sub>STG</sub> | -55                  | +150                 | °C   |                                         |

Note: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### Recommended Operating Conditions

#### Value **Parameter** Symbol Min Тур Max Unit Note 5.0 ٧ $V_{CC}$ 4.5 5.5 Supply Voltage $\overline{\nu_{\text{SS}}}$ ٧ 0 +85 °C **Operating Temperature** $T_A$ -40

#### **DC** Characteristics

(Recommended operating conditions unless otherwise noted).  $(V_{CC} = +5V \pm 10\%, GND = 0V, T_A = -40^{\circ} C \text{ to } +85^{\circ} C)$

|                        |                  | Value                |                 |      |                                                                                              |  |

|------------------------|------------------|----------------------|-----------------|------|----------------------------------------------------------------------------------------------|--|

| Parameter              | Symbol           | Min                  | Max             | Unit | Test Condition                                                                               |  |

| Input Low Voltage      | V <sub>IL</sub>  | -0.3                 | 0.8             | V    |                                                                                              |  |

| Input High Voltage     | V <sub>IH</sub>  | 2.2                  | V <sub>CC</sub> | ٧    |                                                                                              |  |

| Output Low Voltage     | V <sub>OL</sub>  |                      | 0.45            | V    | I <sub>OL</sub> = 2.5mA                                                                      |  |

| Output High Voltage    | V <sub>OH</sub>  | 2.4                  |                 | V    | I <sub>OH</sub> = -400μA                                                                     |  |

|                        |                  | V <sub>CC</sub> -0.4 |                 | V    | I <sub>OH</sub> = -100μA                                                                     |  |

| Input Leakage Current  | I <sub>IL</sub>  | -10                  | +10             | μΑ   | $0V \le V_{IN} \le V_{CC}$                                                                   |  |

| Output Leakage Current | I <sub>OFL</sub> | -10                  | +10             | μΑ   | $0V \le V_{OUT} \le V_{CC}$                                                                  |  |

| Standby Current        | Icc              |                      | 10              | mA   |                                                                                              |  |

| Input Capacitance      | C <sub>IN</sub>  |                      | 10              | pF   | V <sub>CC</sub> = GND = 0V<br>T <sub>A</sub> = 25°C<br>All pins except<br>measured pin are 0 |  |

| Output Capacitance     | C <sub>OUT</sub> |                      | 20              | pF   |                                                                                              |  |

| I/O Capacitance        | C <sub>I/O</sub> |                      | 20              | pF   |                                                                                              |  |

# **AC Characteristics**

(Recommended operating conditions unless otherwise noted).

$(V_{CC} = +5V \pm 10\%, GND = 0V, T_A = -40^{\circ} C \text{ to } +85^{\circ} C)$

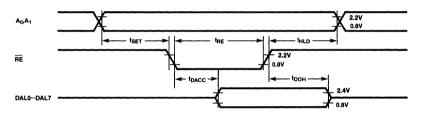

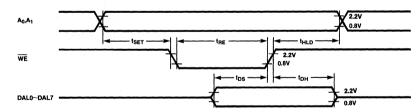

## CPU Read Timing (from FDC)

|                                        |                   | Va  | lue  |      |                        |

|----------------------------------------|-------------------|-----|------|------|------------------------|

| Parameter                              | Symbol            | Min | Max  | Unit | <b>Test Condition</b>  |

| Address Setup Time (to REI)            | t <sub>SET</sub>  | 50  |      | ns   |                        |

| Address Hold Time (from(RE1)           | t <sub>HLD</sub>  | 15  |      | ns   |                        |

| RE Pulse Width                         | t <sub>RE</sub>   | 150 |      | ns   |                        |

| Data Delay Time (from REI)             | tDACC             |     | 120  | ns   | C <sub>L</sub> = 150pF |

| Data Hold Time (from RE1)              | t <sub>DOH</sub>  | 10  | 75   | ns   | C <sub>L</sub> = 150pF |

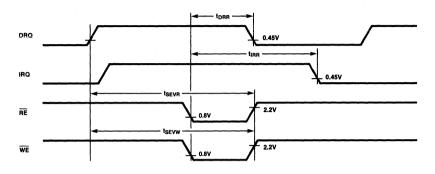

| DRQ Service Time (from DRQ to REt)     | t <sub>SEVR</sub> |     | 13.5 | μs   | t <sub>C</sub> = 2μs   |

| DRQ Release Time<br>(from REI to DQRI) | t <sub>DRR</sub>  |     | 150  | ns   |                        |

| IRQ Release Time<br>(from RE↓ to IRQ↓) | t <sub>IRR</sub>  |     | 500  | ns   |                        |

### **CPU Write Timing (to FDC)**

|                   | Value                       |                                                                                                                                                                                                    |                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                |

|-------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol            | Min                         | Max                                                                                                                                                                                                | Unit                                                                                                                                                                                                                                               | <b>Test Condition</b>                                                                                                                                                                                                                                                                                                                          |

| t <sub>SET</sub>  | 50                          |                                                                                                                                                                                                    | ns                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                |

| t <sub>HLD</sub>  | 10                          |                                                                                                                                                                                                    | ns                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                |

| t <sub>WE</sub>   | 100                         |                                                                                                                                                                                                    | ns '                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                |

| t <sub>DS</sub>   | 100                         |                                                                                                                                                                                                    | ns                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                |

| t <sub>DH</sub>   | 0                           |                                                                                                                                                                                                    | ns                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                |

| t <sub>SEVW</sub> |                             | 9.5*                                                                                                                                                                                               | μs                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                |

| t <sub>DRR</sub>  |                             | 150                                                                                                                                                                                                | ns                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                |

| t <sub>IRR</sub>  |                             | 500                                                                                                                                                                                                | ns                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                |

|                   | tset thld twe tDs tDH tsevw | Symbol         Min           t <sub>SET</sub> 50           t <sub>HLD</sub> 10           t <sub>WE</sub> 100           t <sub>DS</sub> 100           t <sub>DH</sub> 0           t <sub>SEVW</sub> | Symbol         Min         Max           t <sub>SET</sub> 50           t <sub>HLD</sub> 10           t <sub>WE</sub> 100           t <sub>DS</sub> 100           t <sub>DH</sub> 0           t <sub>SEVW</sub> 9.5*           t <sub>DRR</sub> 150 | Symbol         Min         Max         Unit           t <sub>SET</sub> 50         ns           t <sub>HLD</sub> 10         ns           t <sub>WE</sub> 100         ns '           t <sub>DS</sub> 100         ns           t <sub>DH</sub> 0         ns           t <sub>SEVW</sub> 9.5*         μs           t <sub>DRR</sub> 150         ns |

<sup>\*</sup> This value is doubled when CLK = 4MHz.

AC Characteristics

(Continued)

(Recommended operating conditions unless otherwise noted.)

(V<sub>CC</sub> = +5V ± 10%, GND = 0V, T<sub>A</sub> = -40°C to +85°C)

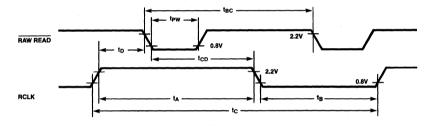

### FDC Read Timing (from FDD)

|                                                             |                 | Value    |        |        |      |                       |

|-------------------------------------------------------------|-----------------|----------|--------|--------|------|-----------------------|

| Parameter                                                   | Symbol          | Min      | Тур    | Max    | Unit | <b>Test Condition</b> |

| RAW READ Pulse Width                                        | t <sub>PW</sub> | 100      |        |        | ns   |                       |

| RAW READ Cycle Time                                         | t <sub>BC</sub> | *2,*3,*4 |        |        | μs   | MFM                   |

| HAW READ Cycle Time                                         |                 |          | *2, *4 | *2, *4 |      | FM                    |

| RCLK Setup Time<br>(from RCLK Change to<br>to RAW READ I)   | t <sub>D</sub>  | 40       |        |        | ns   |                       |

| RCLK <u>Hold Time</u><br>(from RAW READ↓<br>to RCLK Change) | t <sub>CD</sub> | 40       |        |        | ns   |                       |

| RCLK High Time                                              | t <sub>A</sub>  | 0.8      | 1*     | 8      | μs   | MFM                   |

| NOLK HIGH TIME                                              |                 | 0.8      | 2*     | 8      |      | FM                    |

| RCLK Low Time                                               | t <sub>B</sub>  | 0.8      | 1*     | 8      | μs   | MFM                   |

|                                                             |                 | 0.8      | 2*     | 8      |      | FM                    |

| RCLK Cycle Time                                             |                 | 2*       |        |        | MFM  |                       |

|                                                             | t <sub>C</sub>  |          | 4*     |        | μs   | FM                    |

<sup>\*</sup> These values are doubled when the CLK = 4MHz.

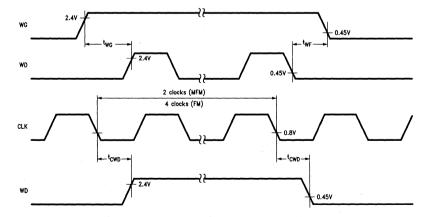

## FDC Write Timing (to FDD)

| Parameter                          |                 |     | Value |     | Unit | Test Condition |

|------------------------------------|-----------------|-----|-------|-----|------|----------------|

|                                    | Symbol          | Min | Тур   | Max |      |                |

| WD Pulse Width                     |                 | 450 | 500   | 550 | ns   | CLK=8MHz, FM   |

|                                    | t <sub>WD</sub> | 200 | 250   | 300 |      | CLK=8MHz, MFM  |

| WG Setup Time<br>(from WGt to WDt) | •               | 2   |       |     |      | CLK=8MHz, FM   |

|                                    | twg             |     | 1     |     | μs   | CLK=8MHz, MFM  |

| WG Hold Time<br>(from WDI to WGI)  | •               | 2   |       |     | 110  | CLK=8MHz, FM   |

|                                    | t <sub>WF</sub> | 1   |       | 2   | μs   | CLK=8MHz, MFM  |

| WD Output Delay                    | tCWD            | 20  |       | 100 | ns   |                |

#### **AC Characteristics**

(Continued)

(Recommended operating conditions unless otherwise noted.) ( $V_{CC}$  = +5V  $\pm$  10%, GND = 0V,  $T_A$  = -40° C to +85° C)

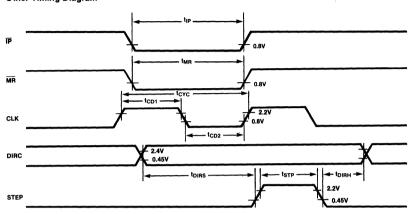

### Other Timing

| Parameter        | Symbol            | Min | Тур | Max | Unit | <b>Test Condition</b> |

|------------------|-------------------|-----|-----|-----|------|-----------------------|

| CLK Cycle Time   | t <sub>CYC</sub>  | 125 |     | 500 | ns   |                       |

| CLK Low Time     | t <sub>CD1</sub>  | 55  |     | 250 | ns   |                       |

| CLK High Time    | t <sub>CD2</sub>  | 55  |     | 250 | ns   |                       |

| STEP Pulse Width |                   | 6*  |     |     | 446  | MFM                   |

|                  | t <sub>STP</sub>  | 12* |     |     | μs   | FM                    |

| DIRC Setup Time  | t <sub>DIRS</sub> | 12* |     |     | μs   |                       |

| DIRC Hold Time   | t <sub>DIRH</sub> | 6*  |     |     | μs   |                       |

| MR Pulse Width   | t <sub>MR</sub>   | 50* |     |     | μs   |                       |

| IP Pulse Width   | t <sub>iP</sub>   | 10* |     |     | μs   |                       |

|                  |                   |     |     |     |      |                       |

<sup>\*</sup> These values are doubled when CLK = 4MHz.

### **Timing Diagrams**

### **CPU Read Timing Diagram**

#### **CPU Write Timing Diagram**

# Timing Diagrams (Continued)

DRQ, IRQ Service and Release Timing Diagram

## **FDC Read Timing Diagram**

### **FDC Write Timing Diagram**

# Timing Diagrams (Continued)

## Other Timing Diagram

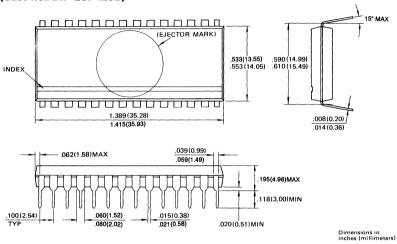

# Package Dimensions Dimensions in Inches

(millimeters)

28-Lead Plastic Dual In-Line Package (Case No.: DIP-28P-M02)

© 1986 FUJITSU LIMITED D28006S-1C