## **FUJITSU SEMICONDUCTOR** CONTROLLER MANUAL

CM44-10118-2E

## F<sup>2</sup>MC<sup>™</sup>-16LX **16-BIT MICROCONTROLLER MB90385 Series** HARDWARE MANUAL

DataShe

DataSheet4U.com

eet4U.com Fl

DataSheet4U.com

www.DataSheet4U.com

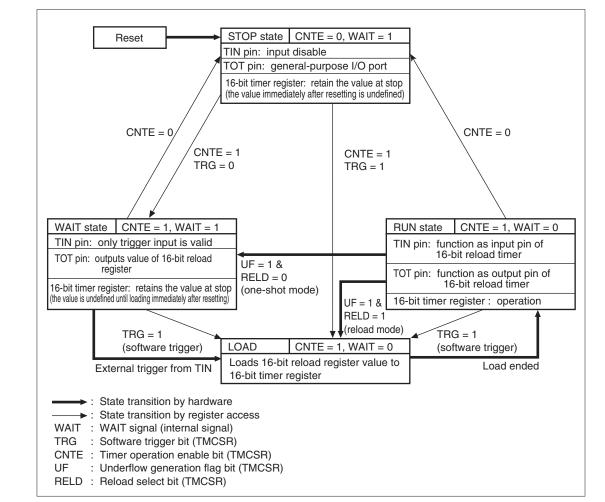

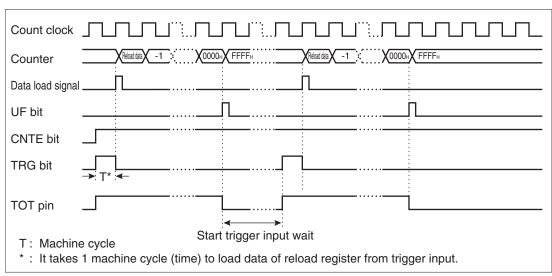

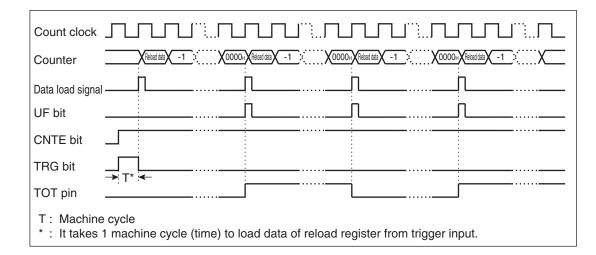

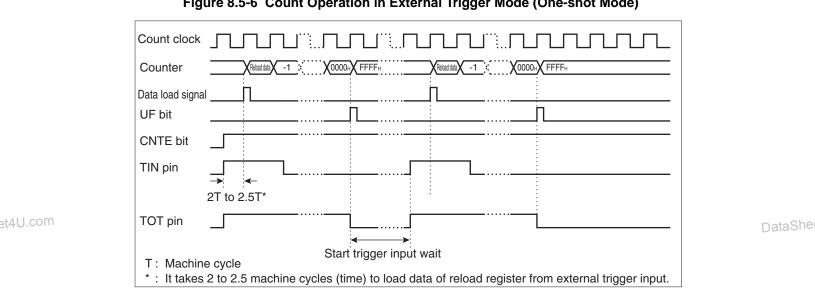

et4U.com

DataSheet4U.com

DataSheet4U.com

www.DataSheet4U.com

## F<sup>2</sup>MC<sup>TM</sup>-16LX 16-BIT MICROCONTROLLER MB90385 Series HARDWARE MANUAL

et4U.com

DataShee

DataSheet4U.com

**FUJITSU LIMITED**

DataSheet4U.com

www.DataSheet4U.com

DataSheet4U.com

www.DataSheet4U.com

et4U.com

DataSheet4U.com

DataSheet4U.com

www.DataSheet4U.com

## PREFACE

## Manual Objectives and Readers

Thank you very much for your continued patronage of Fujitsu semiconductor products.

The MB90385 series is one of the general-purpose products in the F<sup>2</sup>MC<sup>TM</sup>-16LX family of 16-bit singlechip microcontrollers that is developed by using an application-specific integrated circuit (ASIC).

This manual covers the functions and operations of the MB90385 series for engineers to develop LSIs using this series.

## Trademarks

et4U.com

$F^2MC$  is the abbreviation of FUJITSU Flexible Microcontroller.

Other system and product names in this manual are trademarks of respective companies or organizations.

The symbols <sup>TM</sup> and <sup>®</sup> are sometimes omitted in this manual.

- The contents of this document are subject to change without notice.

- Customers are advised to consult with FUJITSU sales representatives before ordering.

- The information, such as descriptions of function and application circuit examples, in this document are presented solely for the purpose of reference to show examples of operations and uses of Fujitsu semiconductor device; Fujitsu does not warrant proper operation of the device with respect to use based on such information. When you develop equipment incorporating the device based on such information, you must assume any responsibility arising out of such use of the information. Fujitsu assumes no liability for any damages whatsoever arising out of the use of the information.

- Any information in this document, including descriptions of function and schematic diagrams, shall not be construed as license of the use or exercise of any intellectual property right, such as patent right or copyright, or any other right of Fujitsu or any third party or does Fujitsu warrant non-infringement of any third-party's intellectual property right or other right by using such information. Fujitsu assumes no liability for any infringement of the intellectual property rights or other rights of third parties which would result from the use of information contained herein.

- The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite).

Please note that Fujitsu will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products.

- Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

- If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Law of Japan, the prior authorization by Japanese government will be required for export of those products from Japan.

DataSheet4U.com ©2005 FUJITSU LIMITED Printed in Japan

## HOW TO READ THIS MANUAL

## ■ Page Structure

Each section content can be read easily because it is mentioned within one page or double spread.

A summary under the title in each section outlines the section contents.

The top-level title at the top of a double spread indicates where you are reading without returning to the table of contents or the chapter title page.

## How to Find Information

To find information in each section, use the following index in addition to general table of contents and index.

#### Register index

This index helps you find the page containing the explanation of the corresponding register from a register name or related resource name. You can also check the mapped addresses on memory and reset values.

• Pin function index

et4U.com

This index helps you find the page containing the explanation or block diagram of the corresponding pin from a pin number, pin name, or related resource name. You can also check the circuit types.

Interrupt vector index

DataSheet4U.com

This index helps you find the page containing the explanation of a corresponding interrupt from a name of resource generating the interrupt or an interrupt number. You can also check the names and addresses of interrupt control registers (ICRs), and the interrupt vector addresses.

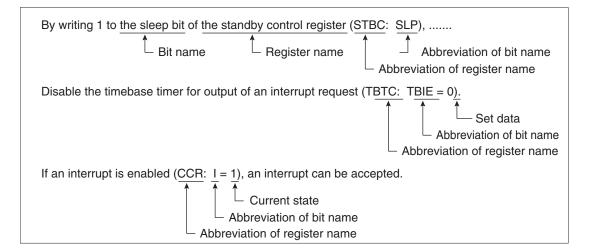

## Representation of Register Name and Pin Name

Representation of register name and bit name

DataSheet4U.com

• Representation of dual-purpose pin

#### P25/SCK pin

Some pins are dual-purpose pins which functions can be switched by the setting of program. A slash (/) separates and represents the names corresponding to the functions of the dual-purpose pins.

## Register Representation

The  $F^2MC-16LX$  family is a CPU with a 16-bit bus width. The bit position of each control register and data register is given in 16 bits.

In 16-bit registers, bits 15 to 8 are allocated to odd addresses and bits 7 to 0 even addresses.

Even in 8-bit registers, the position of bits allocated to odd addresses is given in bits 15 to 8.

The  $F^2MC-16LX$  family enables access to 8-bit data in order to increase the efficiency of programs. So, if odd-address registers are accessed in 8 bits, bits 7 to 0 in data correspond to bits 15 to 8 in the manual representation.

et4U.com

DataSheet4U.com

DataShe

www.DataSheet4U.com

et4U.com

DataSheet4U.com

DataSheet4U.com

## CONTENTS

| CHAPTE              | R 1 OVERVIEW                                     | 1      |

|---------------------|--------------------------------------------------|--------|

| 1.1                 | Features of MB90385 Series                       | 2      |

| 1.2                 | Product Lineup for MB90385 Series                | 5      |

| 1.3                 | Block Diagram of MB90385 Series                  | 8      |

| 1.4                 | Pin Assignment                                   | 9      |

| 1.5                 | Package Dimension 1                              | 10     |

| 1.6                 | Pin Description 1                                | 11     |

| 1.7                 | I/O Circuit 1                                    | 14     |

| СНАРТЕ              | R 2 HANDLING DEVICES 1                           | 7      |

| 2.1                 | Precautions when Handling Devices 1              |        |

| СНАРТЕ              | R 3 CPU                                          | 21     |

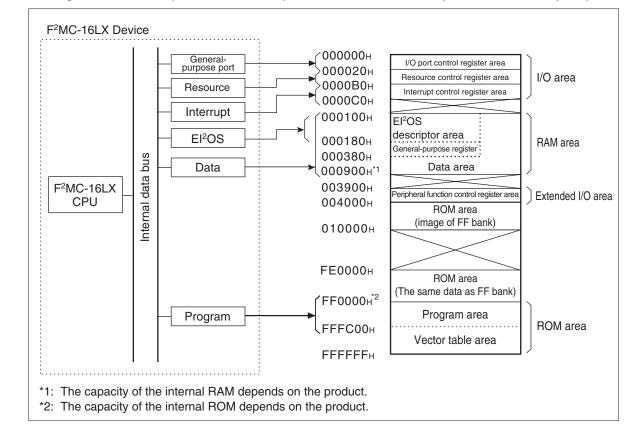

| 3.1                 | Memory Space                                     | 22     |

| 3.1.1               | Mapping of and Access to Memory Space            |        |

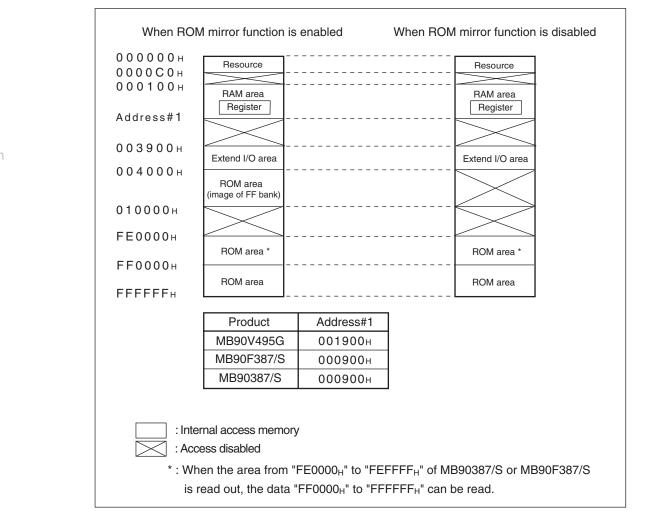

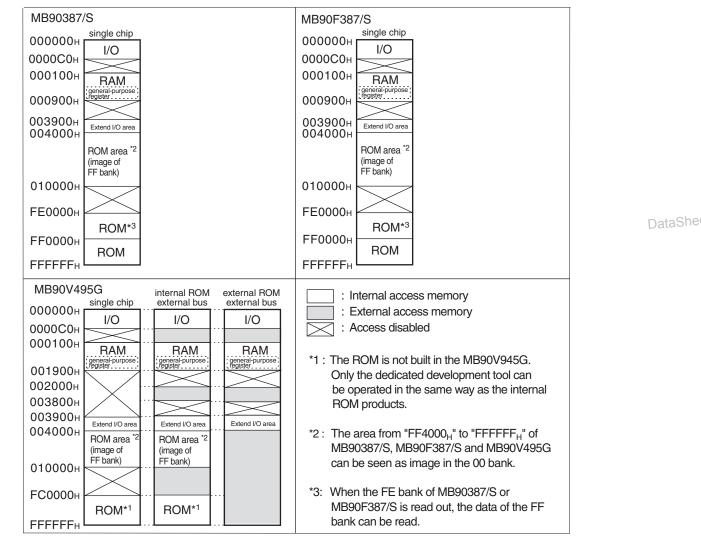

| 3.1.2               | Memory Map                                       |        |

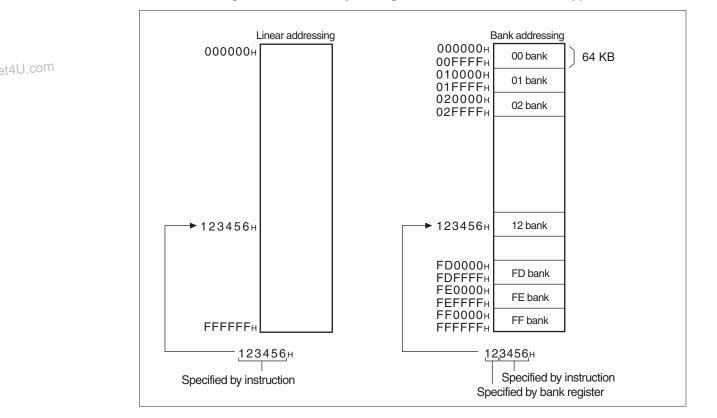

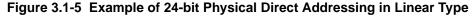

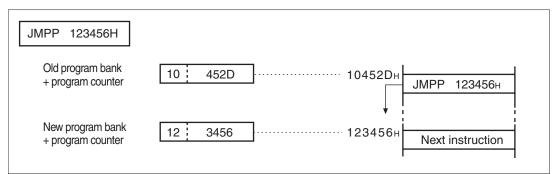

| 3.1.3               | Addressing                                       | 27     |

| 3.1.4               | Linear Addressing                                | DotaSt |

| 3.1.5               | Bank Addressing                                  |        |

| 3.1.6               | Allocation of Multi-byte Data on Memory          |        |

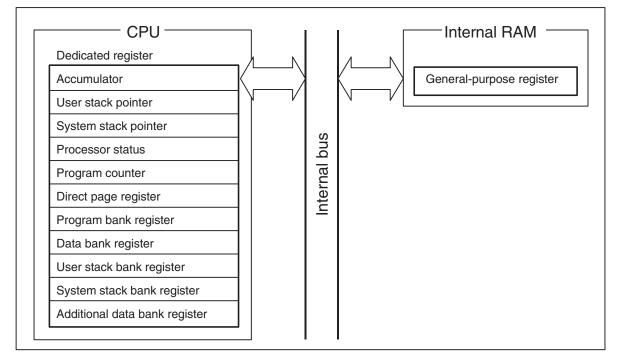

| 3.2                 | Dedicated Registers                              |        |

| 3.2.1               | Dedicated Registers and General-purpose Register |        |

| 3.2.2               | Accumulator (A)                                  |        |

| 3.2.3               | Stack Pointer (USP, SSP)                         |        |

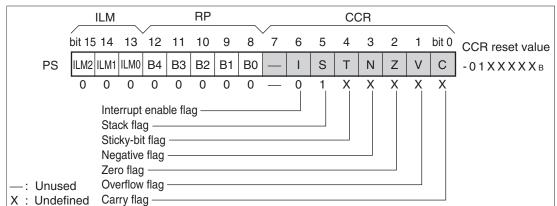

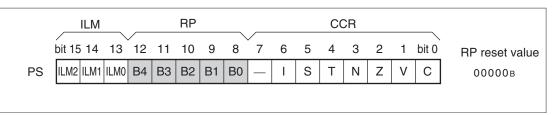

| 3.2.4               | Processor Status (PS)                            |        |

| 3.2.                |                                                  |        |

| 3.2.                |                                                  |        |

| 3.2.                |                                                  |        |

| 3.2.5               | Program Counter (PC)                             |        |

| 3.2.6               | Direct Page Register (DPR)                       |        |

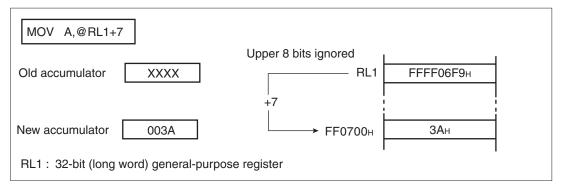

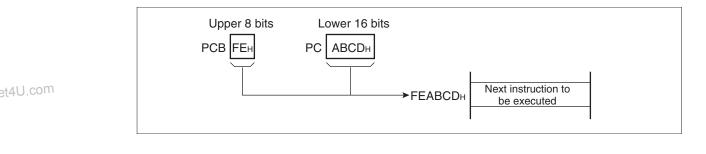

| 3.2.7               | Bank Register (PCB, DTB, USB, SSB, and ADB) 4    |        |

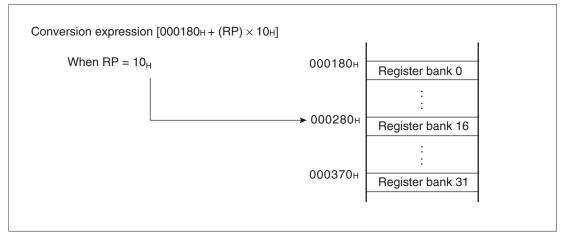

| 3.3                 | General-purpose Register                         |        |

| 3.4                 | Prefix Codes                                     |        |

| 3.4.1               | Bank Select Prefix (PCB, DTB, ADB, and SPB)      |        |

| 3.4.2               | Common Register Bank Prefix (CMR)                |        |

| 3.4.3               | Flag Change Inhibit Prefix (NCC)                 |        |

| 3.4.4               | Restrictions on Prefix Code                      |        |

| 3.5                 | Interrupt                                        |        |

| 3.5.1               | Interrupt Factor and Interrupt Vector            |        |

| 3.5.2               | Interrupt Control Registers and Resources        |        |

| 3.5.3               | Interrupt Control Register (ICR00 to ICR15)      |        |

| 3.5.4               | Function of Interrupt Control Register           |        |

| 1U.con <b>3.5.5</b> | Hardware Interrupt                               |        |

| 3.5.6   | Operation of Hardware Interrupt                       | 74       |             |

|---------|-------------------------------------------------------|----------|-------------|

| 3.5.7   | Procedure for Use of Hardware Interrupt               |          |             |

| 3.5.8   | Multiple Interrupts                                   |          |             |

| 3.5.9   | Software Interrupt                                    |          |             |

| 3.5.10  | Interrupt by El <sup>2</sup> OS                       |          |             |

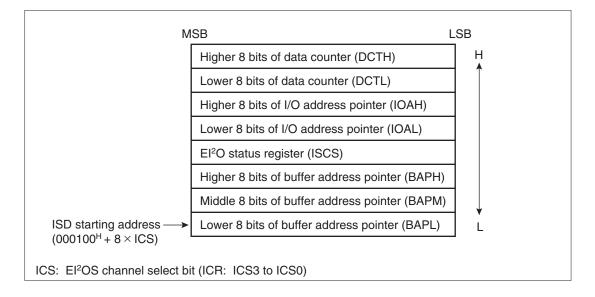

| 3.5.11  | El <sup>2</sup> OS Descriptor (ISD)                   |          |             |

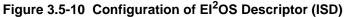

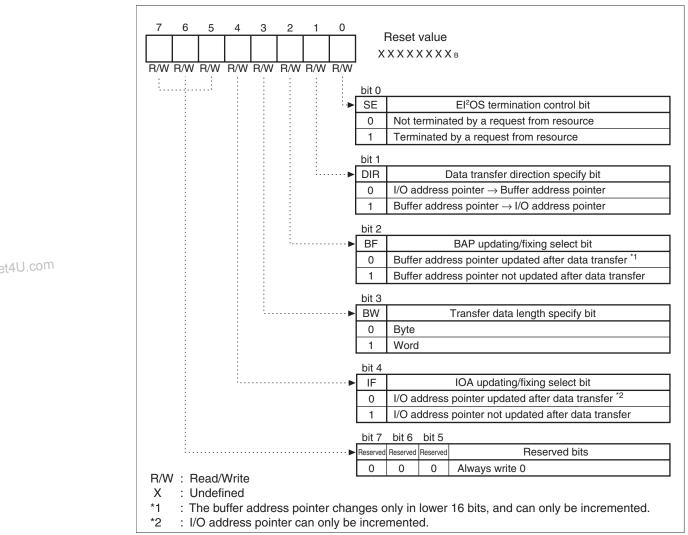

| 3.5.12  | Each Register of El <sup>2</sup> OS Descriptor (ISD)  |          |             |

| 3.5.12  | Operation of El <sup>2</sup> OS                       |          |             |

| 3.5.14  | Procedure for Use of El <sup>2</sup> OS               |          |             |

| 3.5.15  | El <sup>2</sup> OS Processing Time                    |          |             |

| 3.5.16  | Exception Processing Interrupt                        |          |             |

| 3.5.17  | Time Required to Start Interrupt Processing           |          |             |

| 3.5.18  | Stack Operation for Interrupt Processing              |          |             |

| 3.5.19  | Program Example of Interrupt Processing               |          |             |

|         | eset                                                  |          |             |

| 3.6.1   | Reset Factors and Oscillation Stabilization Wait Time |          |             |

| 3.6.2   | External Reset Pin                                    |          |             |

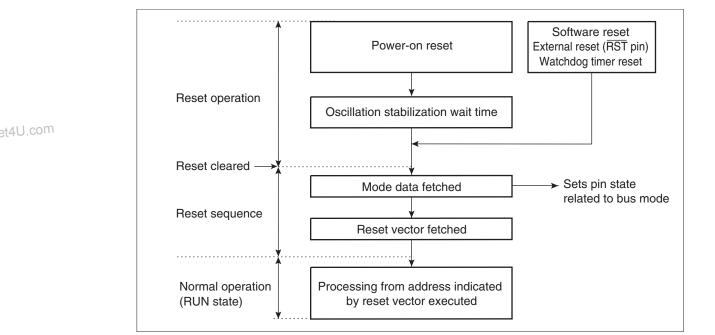

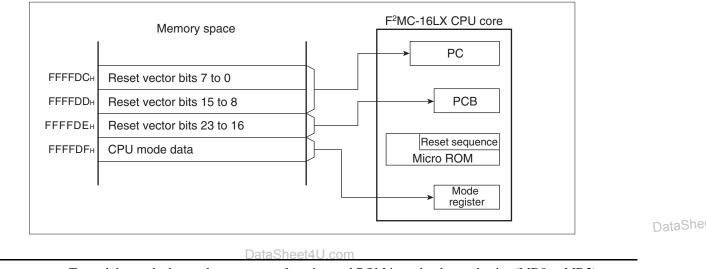

| 3.6.3   | Reset Operation                                       |          |             |

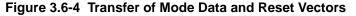

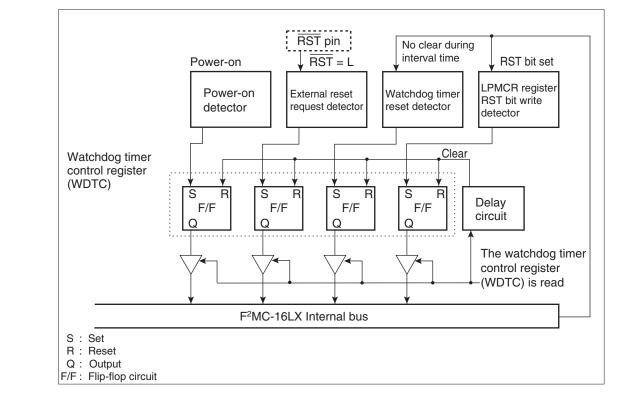

| 3.6.4   | Reset Factor Bit                                      |          |             |

| 3.6.5   | State of Each Pin at Reset                            |          |             |

|         | locks                                                 |          |             |

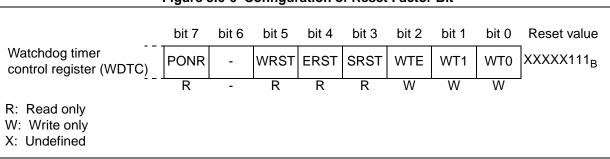

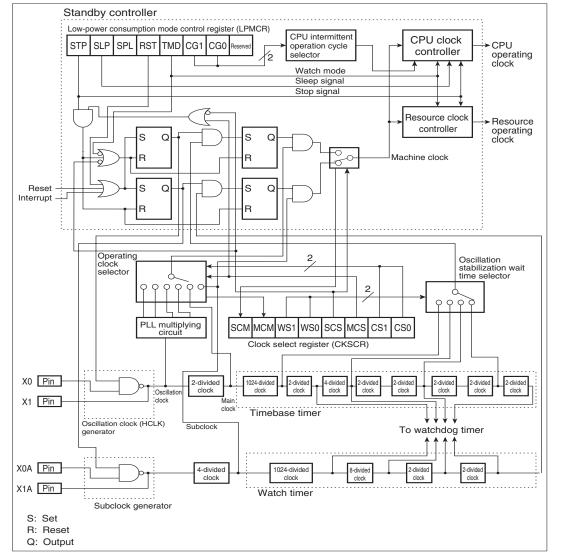

| 3.7.1   | Block Diagram of Clock Generation Section             |          |             |

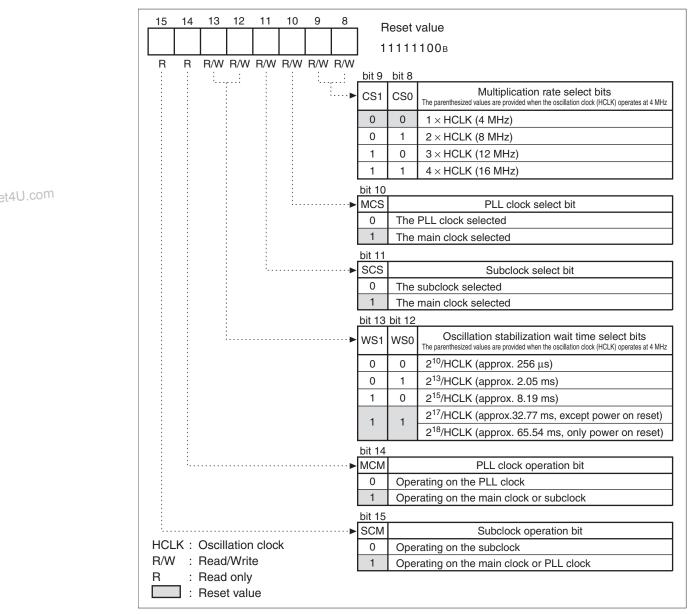

| 3.7.2   | Register in Clock Generation Section                  |          | DataShe     |

| 3.7.3   | Clock Select Register (CKSCR) DataSheet4U.com         |          |             |

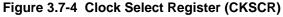

| 3.7.4   | Clock Mode                                            |          |             |

| 3.7.5   | Oscillation Stabilization Wait Time                   |          |             |

| 3.7.6   | Connection of Oscillator and External Clock           | 123      |             |

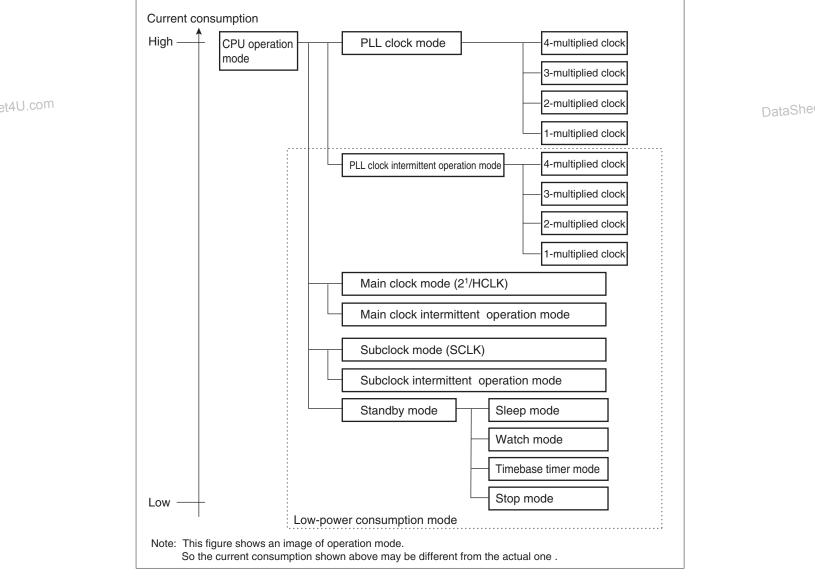

| 3.8 L   | ow-power Consumption Mode                             | 124      |             |

| 3.8.1   | Block Diagram of Low-power Consumption Circuit        | 127      |             |

| 3.8.2   | Registers for Setting Low-power Consumption Modes     | 129      |             |

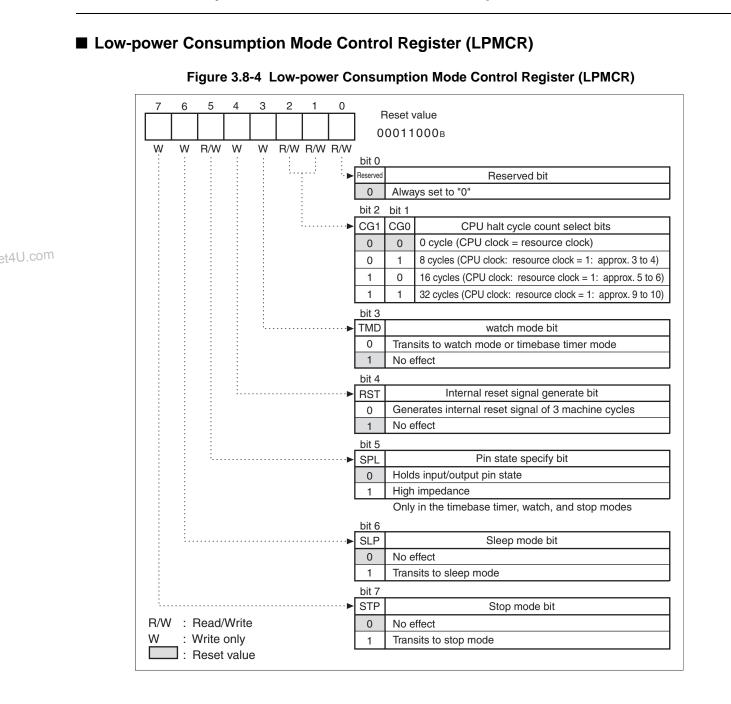

| 3.8.3   | Low-power Consumption Mode Control Register (LPMCR)   | 130      |             |

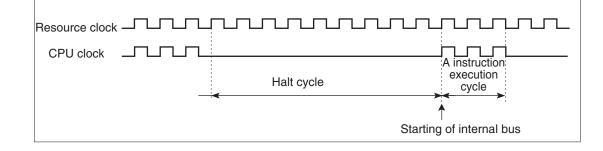

| 3.8.4   | CPU Intermittent Operation Mode                       | 133      |             |

| 3.8.5   | Standby Mode                                          | 134      |             |

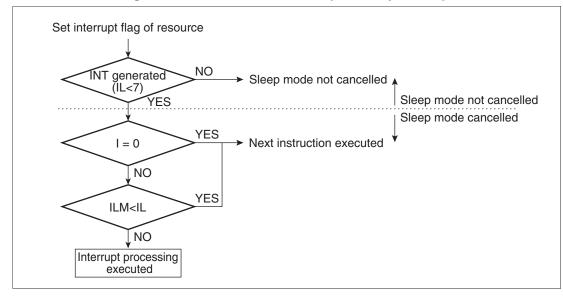

| 3.8.5.  | 1 Sleep Mode                                          | 135      |             |

| 3.8.5.  | 2 Watch mode                                          | 137      |             |

| 3.8.5.  | 3 Timebase Timer Mode                                 | 139      |             |

| 3.8.5.  | 4 Stop Mode                                           | 141      |             |

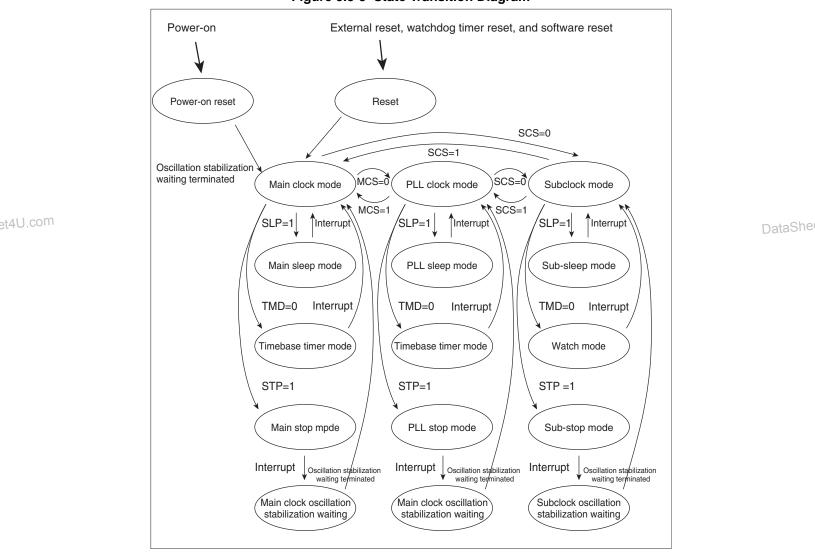

| 3.8.6   | State Transition in Standby Mode                      | 144      |             |

| 3.8.7   | Pin State in Standby Mode, at Reset                   | 145      |             |

| 3.8.8   | Precautions when Using Low-power Consumption Mode     | 146      |             |

| 3.9 C   | PU Mode                                               | 149      |             |

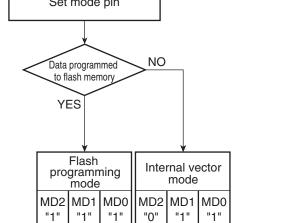

| 3.9.1   | Mode Pins (MD2 to MD0)                                | 150      |             |

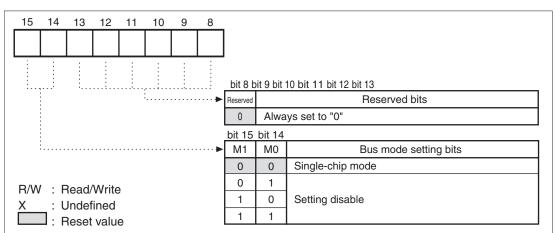

| 3.9.2   | Mode Data                                             | 152      |             |

| 3.9.3   | Memory Access Mode                                    |          |             |

| 3.9.4   | Selection of Memory Access Mode                       | 155      |             |

|         |                                                       |          |             |

| CHAPTER | R 4 I/O PORT                                          | 157      | oot III som |

| J.com   | 1949A                                                 | m.ngrg2U | cc(40.00M   |

et4U.com

|           | 4.1           | Overview of I/O Port                                                               | . 158                 |           |

|-----------|---------------|------------------------------------------------------------------------------------|-----------------------|-----------|

|           | 4.2           | Registers of I/O Port                                                              | . 160                 |           |

|           | 4.3           | Port 1                                                                             | . 161                 |           |

|           | 4.3.1         | Registers for Port 1 (PDR1, DDR1)                                                  | . 163                 |           |

|           | 4.3.2         | Operation of Port 1                                                                | . 164                 |           |

|           | 4.4           | Port 2                                                                             | . 166                 |           |

|           | 4.4.1         | Registers for Port 2 (PDR2, DDR2)                                                  | . 168                 |           |

|           | 4.4.2         |                                                                                    |                       |           |

|           | 4.5           | Port 3                                                                             |                       |           |

|           | 4.5.1         | Registers for Port 3 (PDR3, DDR3)                                                  |                       |           |

|           | 4.5.2         |                                                                                    |                       |           |

|           | 4.6           | Port 4                                                                             |                       |           |

|           | 4.6.1         | Registers for Port 4 (PDR4, DDR4)                                                  |                       |           |

|           | 4.6.2         |                                                                                    |                       |           |

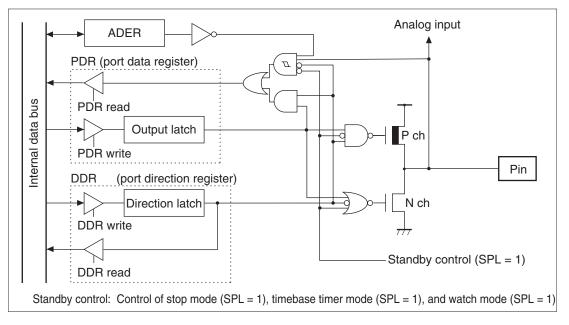

|           | 4.7           | Port 5                                                                             |                       |           |

|           | 4.7.1         | Registers for Port 5 (PDR5, DDR5, ADER)                                            |                       |           |

|           | 4.7.2         |                                                                                    |                       |           |

|           | <b>Τ.1.</b> Ζ |                                                                                    | 100                   |           |

|           | CHAPTE        | ER 5 TIMEBASE TIMER                                                                | 187                   |           |

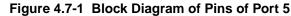

|           | 5.1           | Overview of Timebase Timer                                                         |                       |           |

|           |               |                                                                                    |                       |           |

| (4) L 00M | 5.2           | Block Diagram of Timebase Timer                                                    |                       |           |

| et4U.com  | 5.3           | Configuration of Timebase Timer                                                    |                       | DataShe   |

|           | 5.3.1         | Timebase Timer Control Register (TBTC)<br>Timebase Timer Interrupt DataSheet4U.com |                       |           |

|           | 5.4           |                                                                                    |                       |           |

|           | 5.5           | Explanation of Operation of Timebase Timer                                         |                       |           |

|           | 5.6           | Precautions when Using Timebase Timer                                              |                       |           |

|           | 5.7           | Program Example of Timebase Timer                                                  | . 201                 |           |

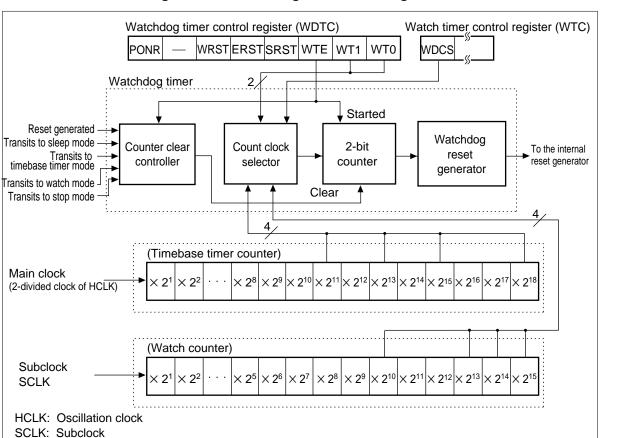

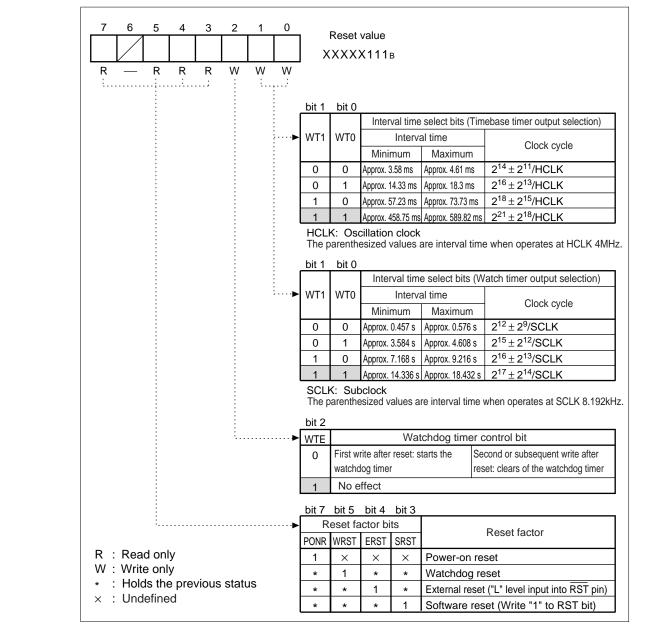

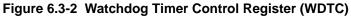

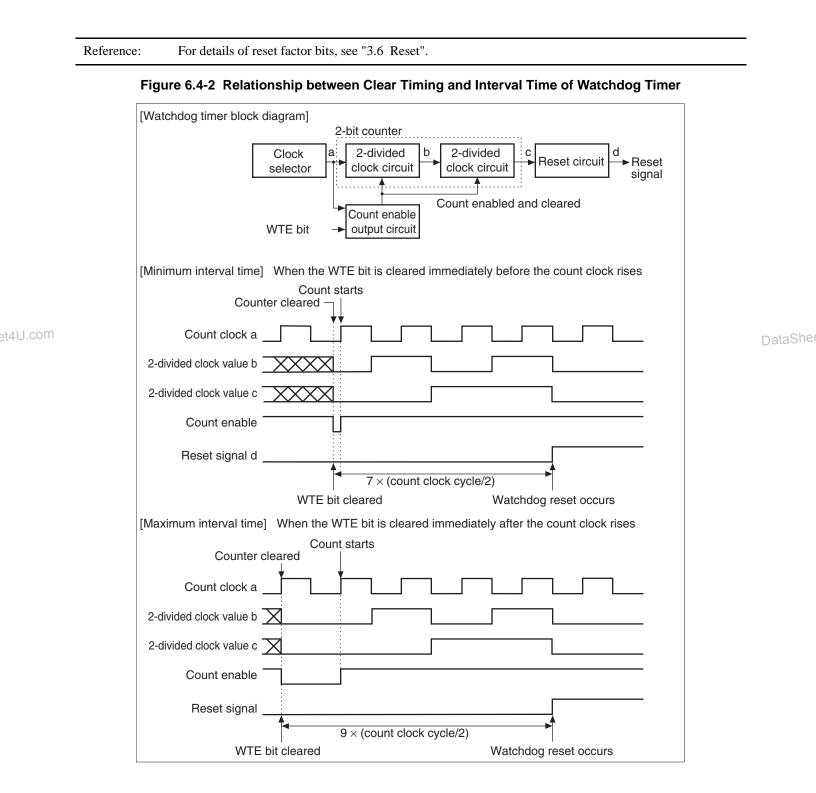

|           | CHAPTE        | ER 6 WATCHDOG TIMER                                                                | 203                   |           |

|           | 6.1           | Overview of Watchdog Timer                                                         | . 204                 |           |

|           | 6.2           | Configuration of Watchdog Timer                                                    |                       |           |

|           | 6.3           | Watchdog Timer Registers                                                           |                       |           |

|           | 6.3.1         | Watchdog Timer Control Register (WDTC)                                             |                       |           |

|           | 6.4           | Explanation of Operation of Watchdog Timer                                         |                       |           |

|           | 6.5           | Precautions when Using Watchdog Timer                                              |                       |           |

|           | 6.6           | Program Examples of Watchdog Timer                                                 |                       |           |

|           |               |                                                                                    |                       |           |

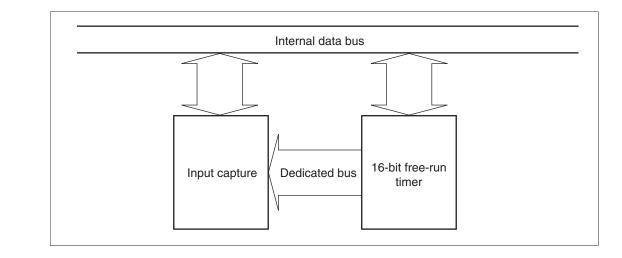

|           | CHAPTE        | ER 7 16-BIT INPUT/OUTPUT TIMER                                                     | 215                   |           |

|           | 7.1           | Overview of 16-bit Input/Output Timer                                              |                       |           |

|           | 7.2           | Block Diagram of 16-bit Input/Output Timer                                         | . 217                 |           |

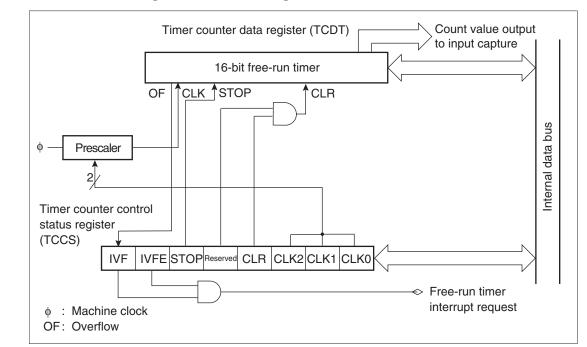

|           | 7.2.1         | Block Diagram of 16-bit Free-run Timer                                             | . 218                 |           |

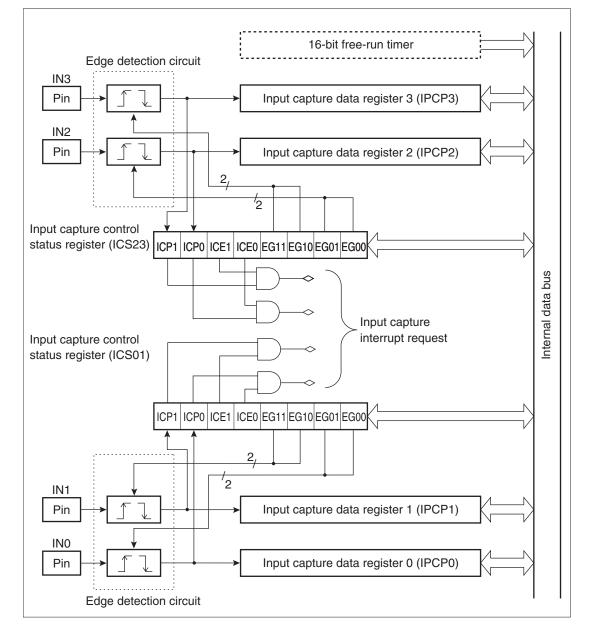

|           | 7.2.2         | Block Diagram of Input Capture                                                     | . 220                 |           |

|           | 7.3           | Configuration of 16-bit Input/Output Timer                                         | . 222                 |           |

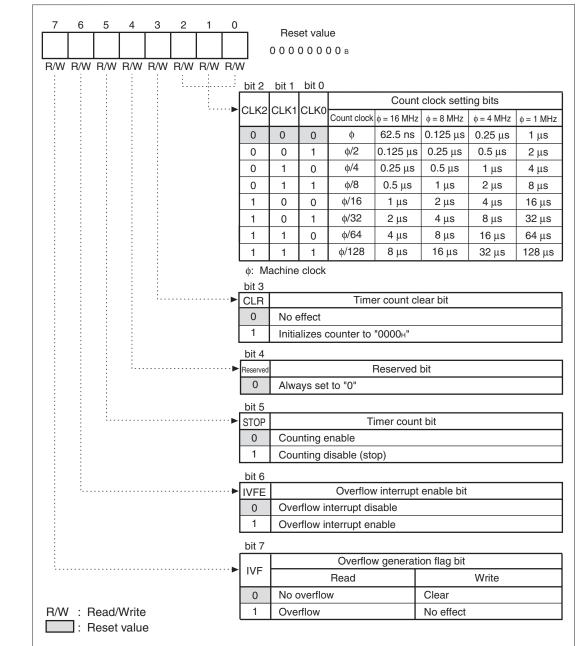

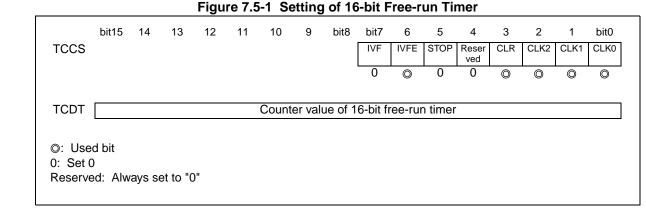

|           | 7.3.1         | Timer Counter Control Status Register (TCCS)                                       | . 225                 |           |

|           | 7.3.2         | Timer Counter Data Register (TCDT)                                                 | . 227                 |           |

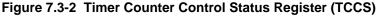

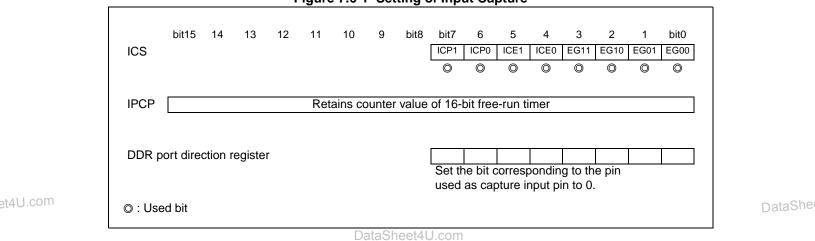

|           | 7.3.3         | Input Capture Control Status Registers (ICS01 and ICS23)                           | . 229                 |           |

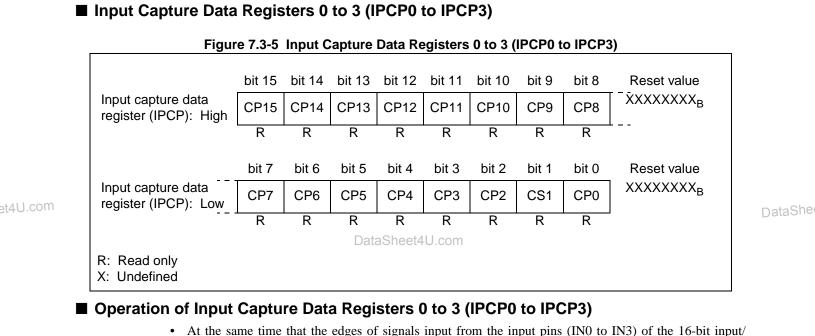

| DataSheet | 7.3.4         | Input Capture Data Registers 0 to 3 (IPCP0 to IPCP3)                               | D <mark>232</mark> 5h | eet4U.com |

| DataOneel |               |                                                                                    |                       |           |

DataSheet4U.com

|          | 7.4    |         | ots of 16-bit Input/Output Timer                          |     |

|----------|--------|---------|-----------------------------------------------------------|-----|

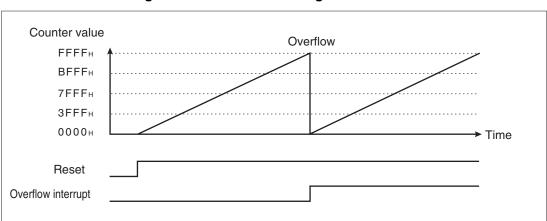

|          | 7.5    | •       | ation of Operation of 16-bit Free-run Timer               |     |

|          | 7.6    |         | ation of Operation of Input Capture                       |     |

|          | 7.7    |         | itions when Using 16-bit Input/Output Timer               |     |

|          | 7.8    | Progra  | m Example of 16-bit Input/Output Timer                    | 240 |

|          | СНАРТІ | ER 8    | 16-BIT RELOAD TIMER                                       | 243 |

|          | 8.1    | Overvi  | ew of 16-bit Reload Timer                                 | 244 |

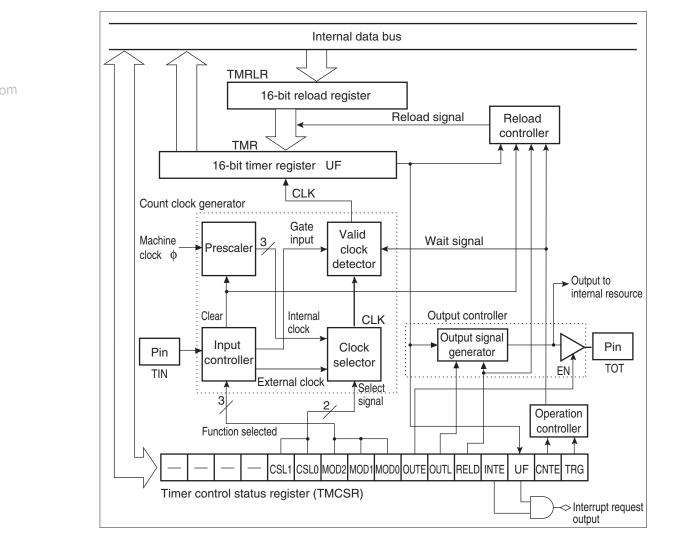

|          | 8.2    | Block [ | Diagram of 16-bit Reload Timer                            | 246 |

|          | 8.3    | Config  | uration of 16-bit Reload Timer                            | 248 |

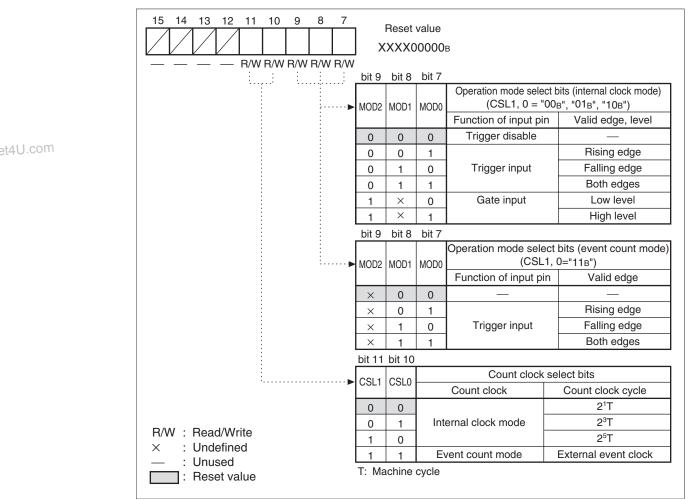

|          | 8.3.1  | Tim     | er Control Status Registers (High) (TMCSR0: H, TMCSR1: H) | 251 |

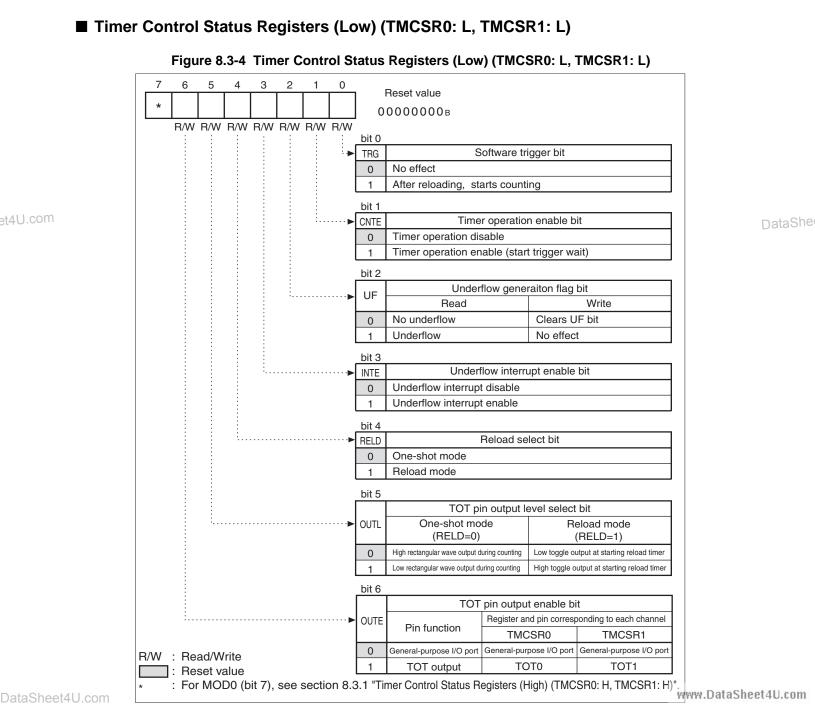

|          | 8.3.2  | Tim     | er Control Status Registers (Low) (TMCSR0: L, TMCSR1: L)  | 253 |

|          | 8.3.3  | 16-l    | pit Timer Registers (TMR0, TMR1)                          | 255 |

|          | 8.3.4  | 16-l    | pit Reload Registers (TMRLR0, TMRLR1)                     | 256 |

|          | 8.4    | Interru | ots of 16-bit Reload Timer                                | 257 |

|          | 8.5    | Explan  | ation of Operation of 16-bit Reload Timer                 | 258 |

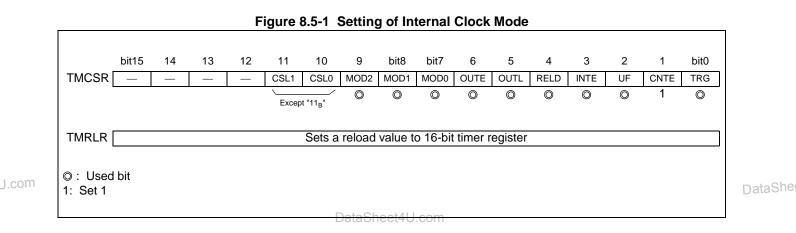

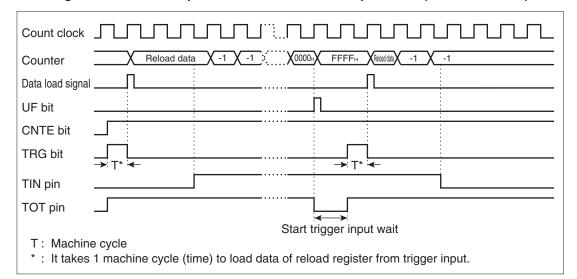

|          | 8.5.1  | Ope     | eration in Internal Clock Mode                            | 260 |

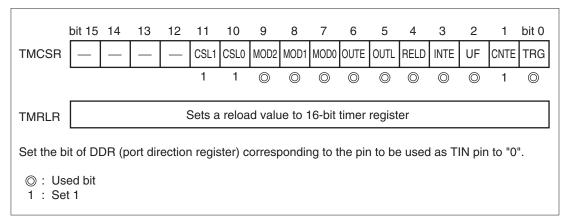

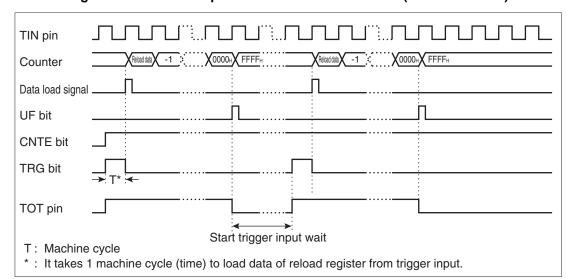

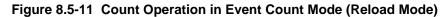

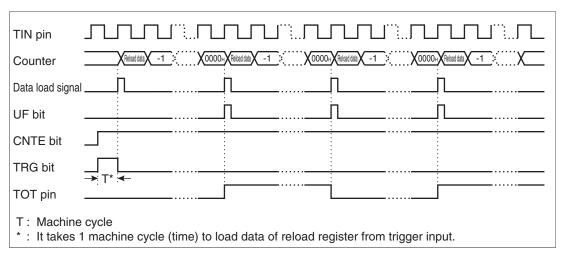

|          | 8.5.2  | Ope     | eration in Event Count Mode                               | 265 |

|          | 8.6    | Precau  | tions when Using 16-bit Reload Timer                      | 268 |

|          | 8.7    | Progra  | m Example of 16-bit Reload Timer                          | 269 |

| et4U.com | CHAPTI | ER 9    | WATCH TIMER                                               | 273 |

|          | 9.1    | Overvi  | ew of Watch Timer                                         | 274 |

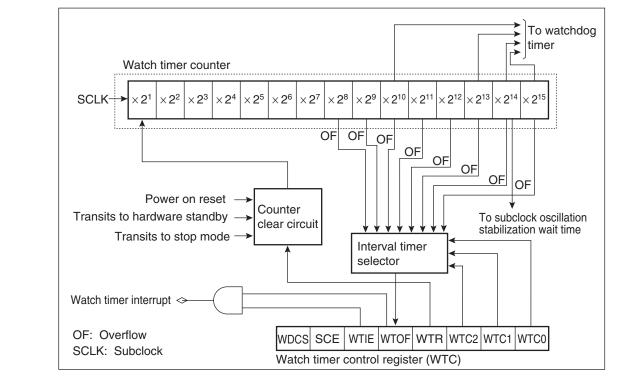

|          | 9.2    | Block [ | Diagram of Watch Timer                                    | 276 |

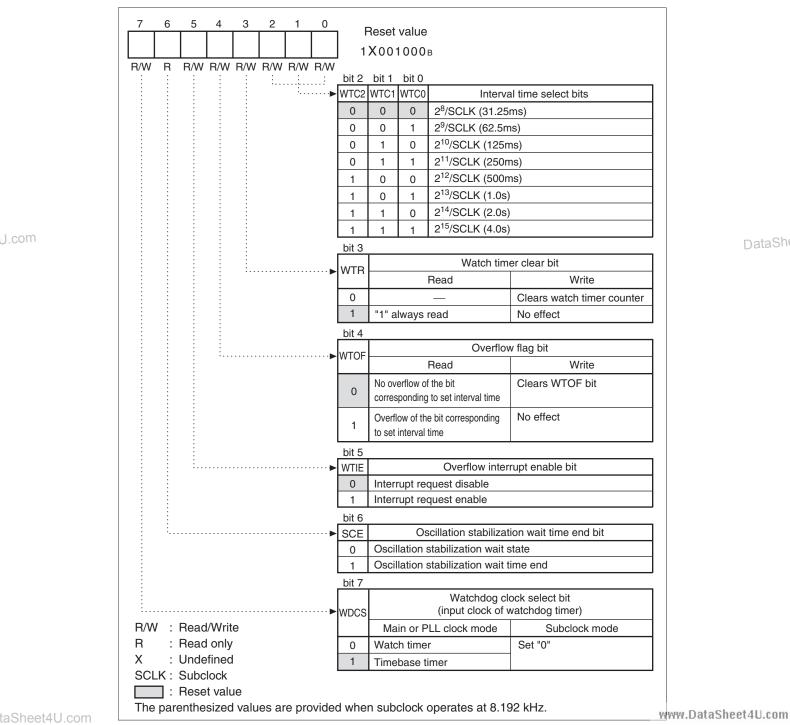

|          | 9.3    |         | uration of Watch Timer                                    |     |

|          | 9.3.1  | -       | tch Timer Control Register (WTC)                          |     |

|          | 9.4    |         | Timer Interrupt                                           |     |

|          | 9.5    |         | ation of Operation of Watch Timer                         |     |

|          | 9.6    | •       | m Example of Watch Timer                                  |     |

|          | СНАРТІ | =R 10   | 8-/16-BIT PPG TIMER                                       | 285 |

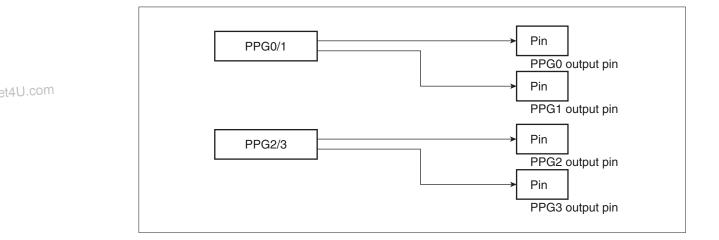

|          | 10.1   |         | ew of 8-/16-bit PPG Timer                                 |     |

|          | 10.1   |         | Diagram of 8-/16-bit PPG Timer                            |     |

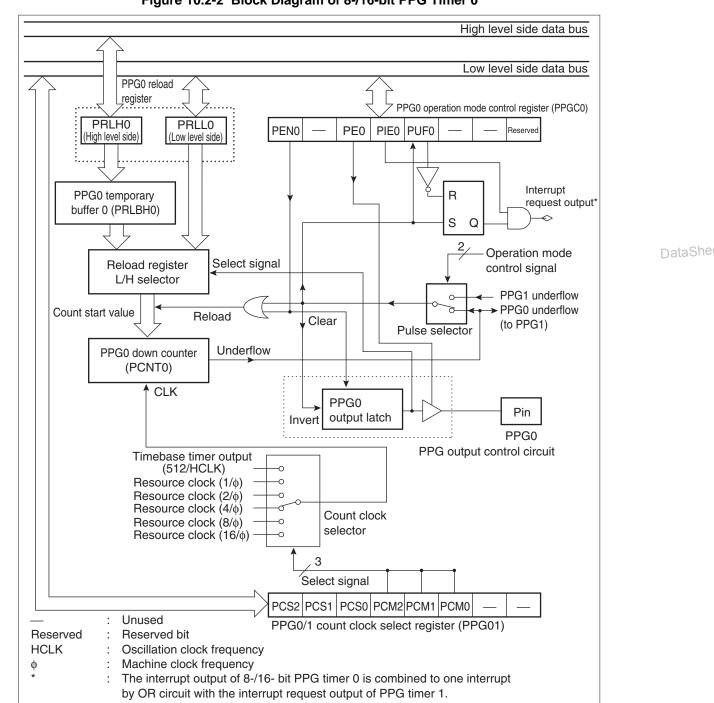

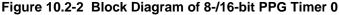

|          | 10.2   |         | ck Diagram for 8-/16-bit PPG Timer 0                      |     |

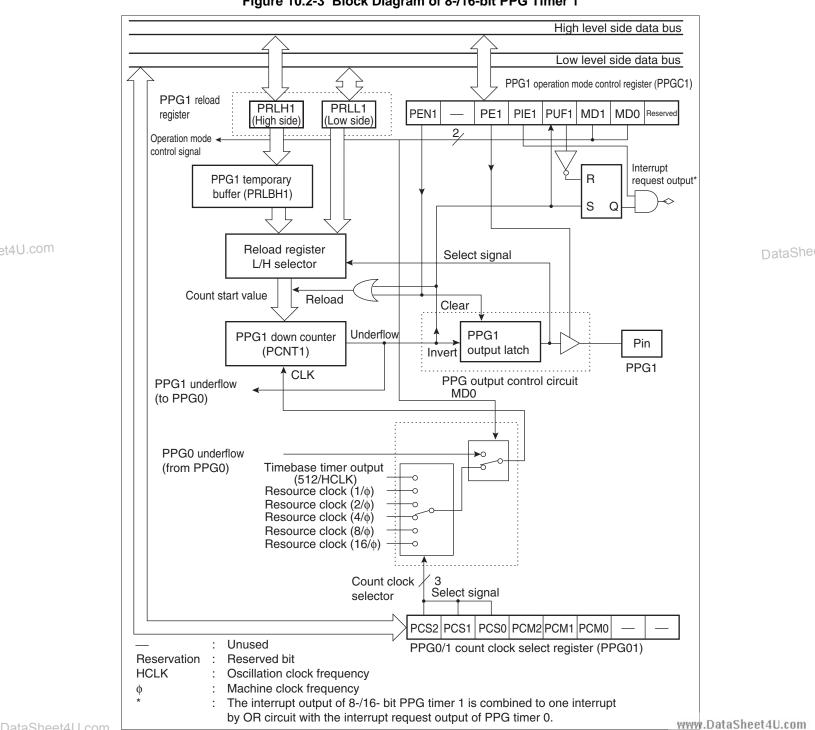

|          | 10.2.  |         | ck Diagram of 8-/16-bit PPG Timer 1                       |     |

|          | 10.2   |         | uration of 8-/16-bit PPG Timer                            |     |

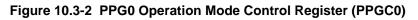

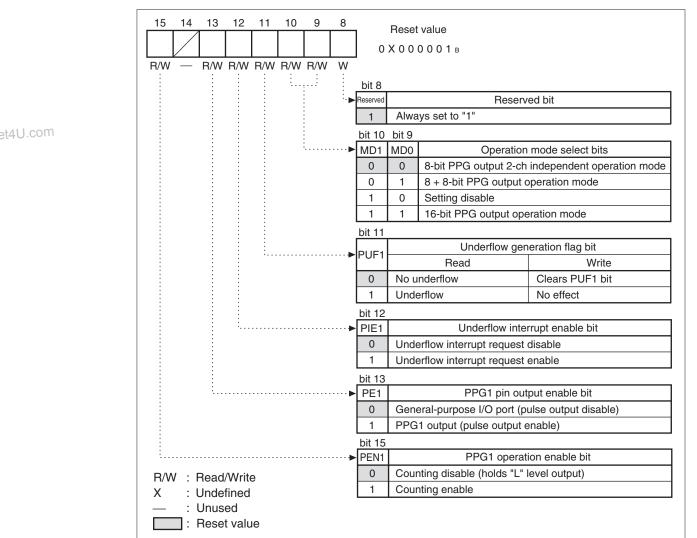

|          | 10.3   | -       | G0 Operation Mode Control Register (PPGC0)                |     |

|          | 10.3.  |         | G1 Operation Mode Control Register (PPGC1)                |     |

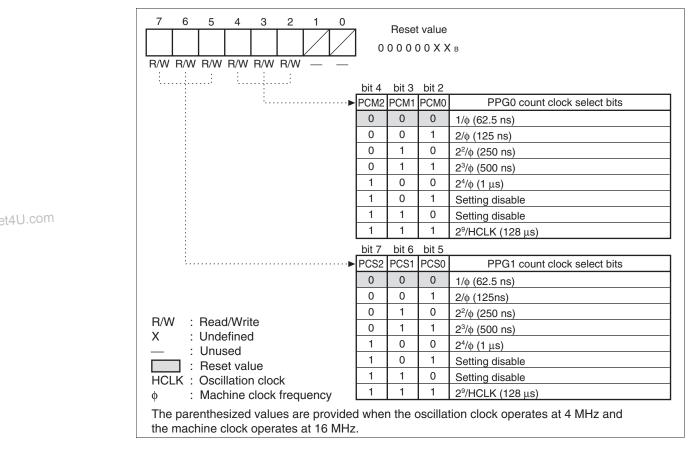

|          | 10.3.  |         | G0/1 Count Clock Select Register (PPG01)                  |     |

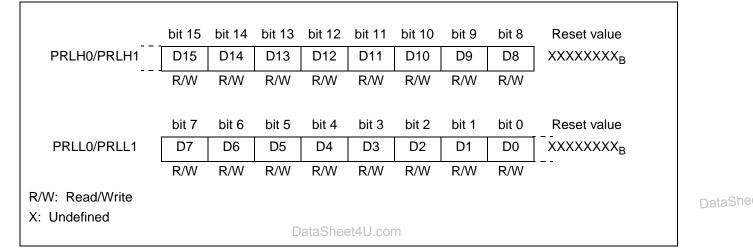

|          | 10.3.  |         | G Reload Registers (PRLL0/PRLH0, PRLL1/PRLH1)             |     |

|          | 10.3.  |         | ots of 8-/16-bit PPG Timer                                |     |

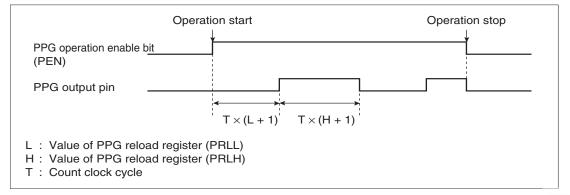

|          | 10.4   |         | ation of Operation of 8-/16-bit PPG Timer                 |     |

|          | 10.5   |         | t PPG Output 2-channel Independent Operation Mode         |     |

|          | 10.5.  |         | bit PPG Output 2-channel independent Operation Node       |     |

|          | 10.5.  |         | -bit PPG Output Operation Mode                            |     |

|          | 10.5.  |         | tions when Using 8-/16-bit PPG Timer                      |     |

|          | 10.0   | Fieldu  | 110113 WHEH USHIY U7/10-DILFFG TIIIEI                     | 510 |

DataSheet4U.com

| CHAPTER 11 DELAYED INTERRUPT GENERATION MODULE                                                                                         |     |

|----------------------------------------------------------------------------------------------------------------------------------------|-----|

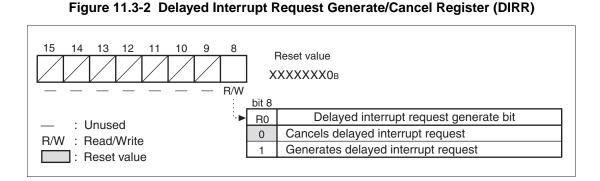

| 11.1 Overview of Delayed Interrupt Generation Module                                                                                   |     |

| 11.2 Block Diagram of Delayed Interrupt Generation Module                                                                              |     |

| 11.3 Configuration of Delayed Interrupt Generation Module                                                                              |     |

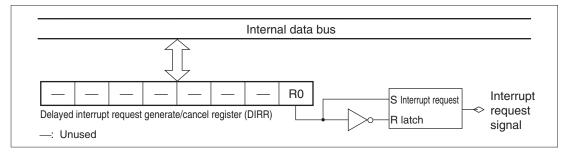

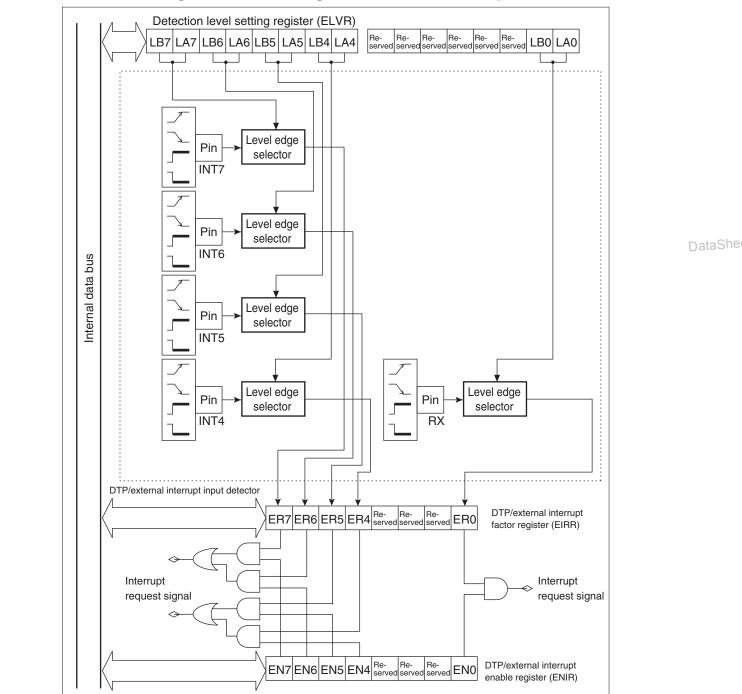

| 11.3.1 Delayed Interrupt Request Generate/Cancel Register (DIRR)                                                                       |     |

| 11.4 Explanation of Operation of Delayed Interrupt Generation Module                                                                   |     |

| 11.5 Precautions when Using Delayed Interrupt Generation Module                                                                        | 325 |

| 11.6 Program Example of Delayed Interrupt Generation Module                                                                            | 326 |

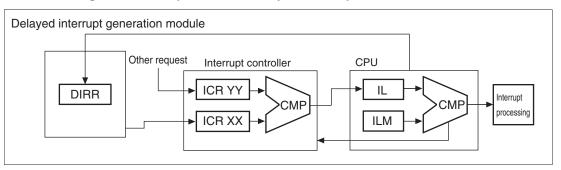

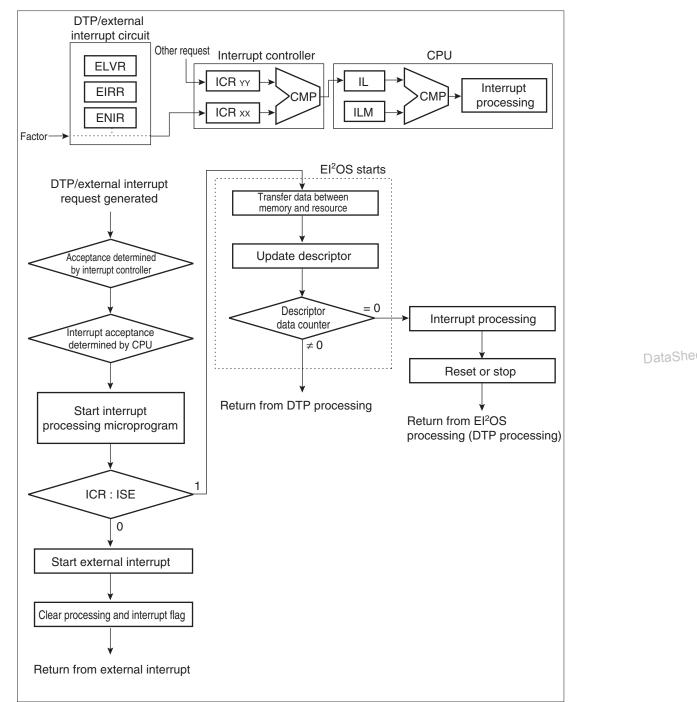

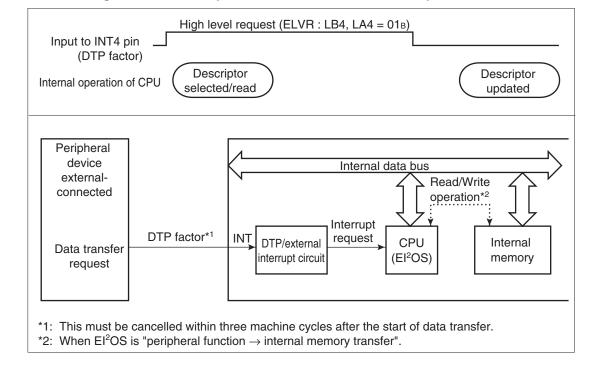

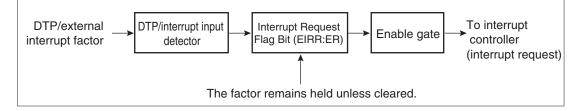

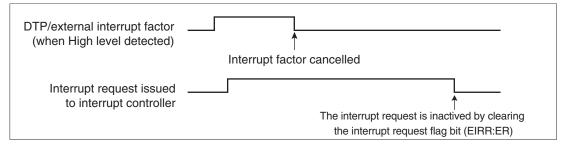

| CHAPTER 12 DTP/EXTERNAL INTERRUPT                                                                                                      | 327 |

| 12.1 Overview of DTP/External Interrupt                                                                                                |     |

| 12.2 Block Diagram of DTP/External Interrupt                                                                                           |     |

| 12.3 Configuration of DTP/External Interrupt                                                                                           |     |

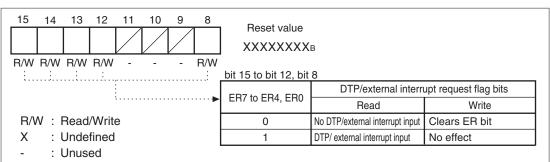

| 12.3.1 DTP/External Interrupt Factor Register (EIRR)                                                                                   |     |

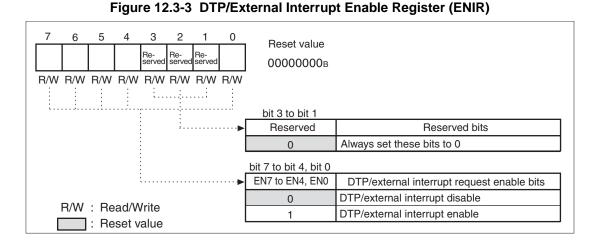

| 12.3.2 DTP/External Interrupt Enable Register (ENIR)                                                                                   |     |

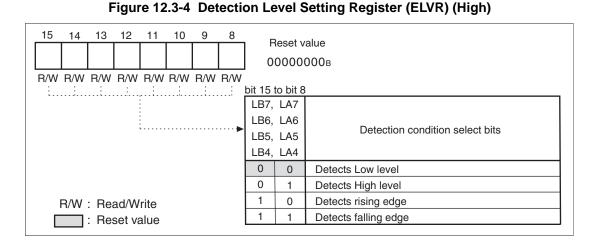

| 12.3.3 Detection Level Setting Register (ELVR) (High)                                                                                  |     |

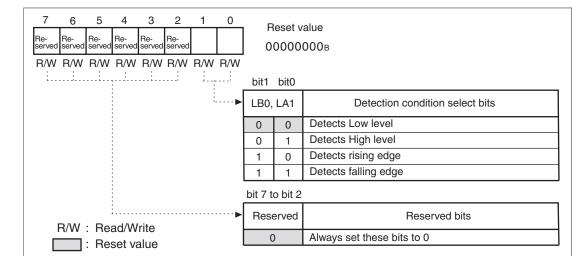

| 12.3.4 Detection Level Setting Register (ELVR) (Low)                                                                                   |     |

| 12.4 Explanation of Operation of DTP/External Interrupt                                                                                |     |

| 12.4.1 External Interrupt Function                                                                                                     |     |

| 12.4.1 External memory Function                                                                                                        |     |

|                                                                                                                                        |     |

| <ul> <li>12.5 Precautions when Using DTP/External Interrupt</li> <li>12.6 Program Example of DTP/External Interrupt Circuit</li> </ul> |     |

| CHAPTER 13 8-/10-BIT A/D CONVERTER                                                                                                     | 347 |

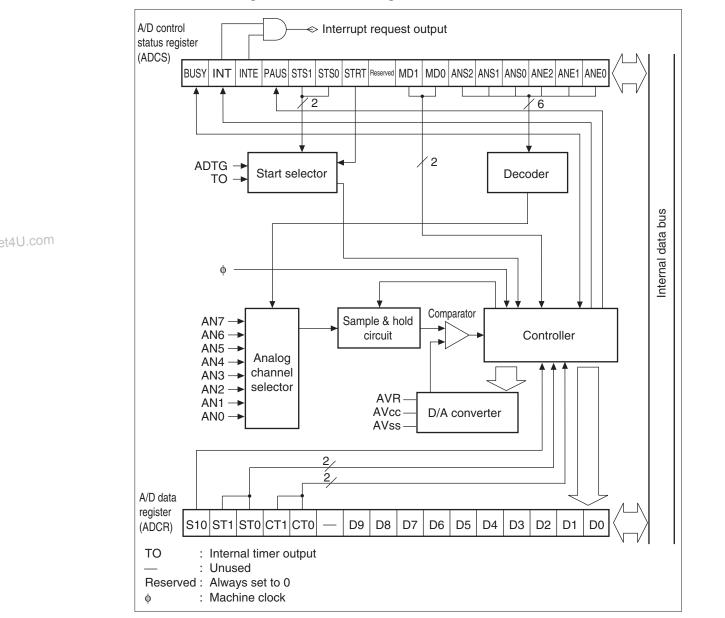

| 13.1 Overview of 8-/10-bit A/D Converter                                                                                               |     |

| 13.2 Block Diagram of 8-/10-bit A/D Converter                                                                                          |     |

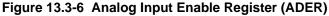

| 13.3 Configuration of 8-/10-bit A/D Converter                                                                                          |     |

| -                                                                                                                                      |     |

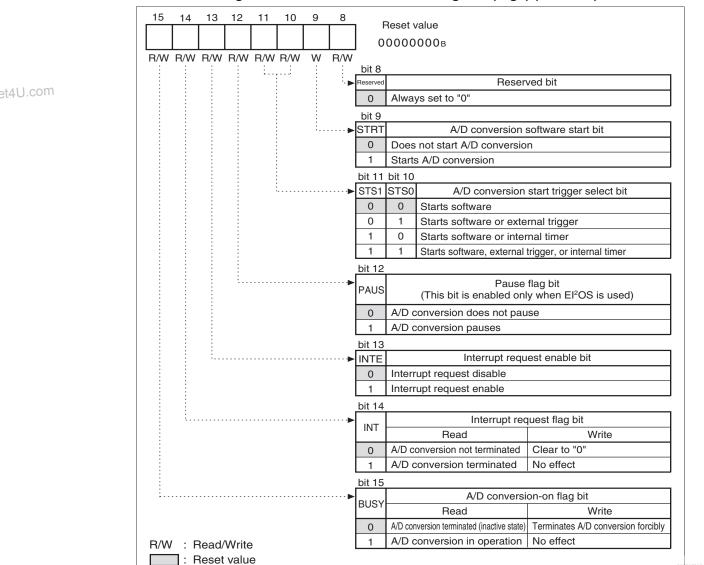

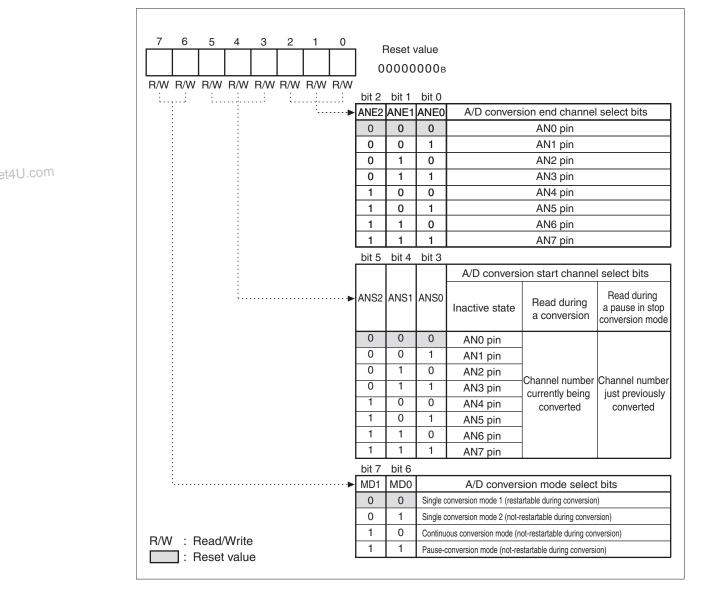

| <b>o ( o )</b> ( <b>)</b>                                                                                                              |     |

| 13.3.2 A/D Control Status Register (Low) (ADCS: L)                                                                                     |     |

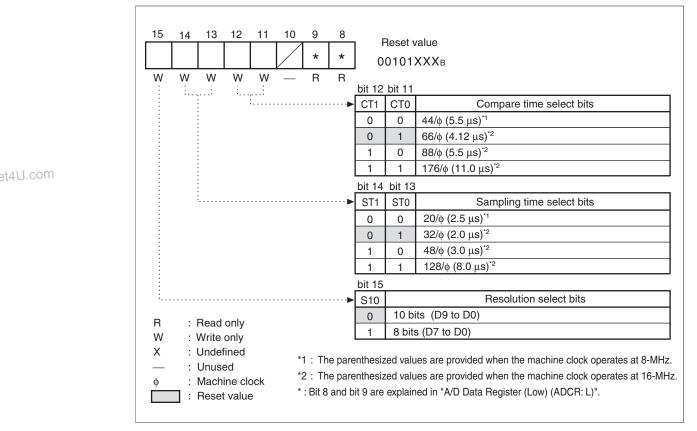

| 13.3.3 A/D Data Register (High) (ADCR: H)                                                                                              |     |

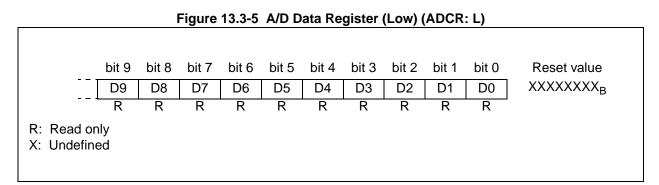

| 13.3.4 A/D Data Register (Low) (ADCR: L)                                                                                               |     |

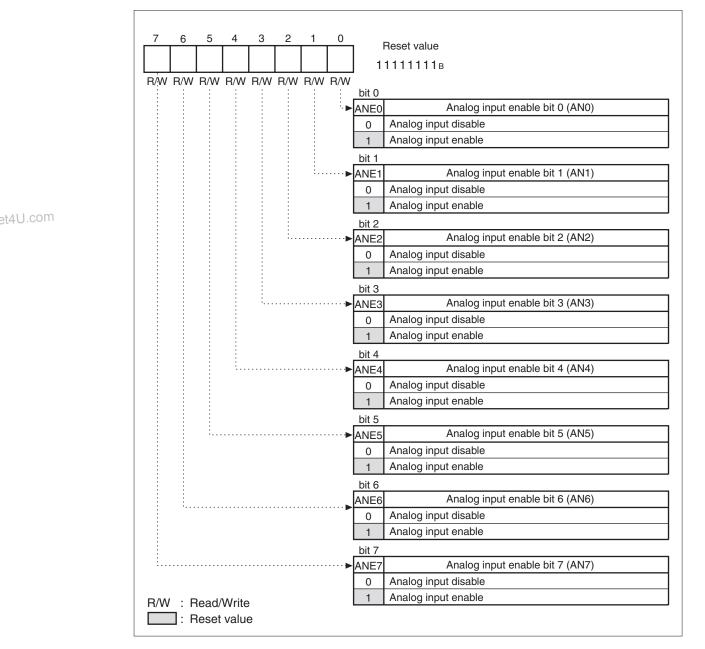

| 13.3.5 Analog Input Enable Register (ADER)                                                                                             |     |

| 13.4 Interrupt of 8-/10-bit A/D Converter                                                                                              |     |

| 13.5 Explanation of Operation of 8-/10-bit A/D Converter                                                                               |     |

| 13.5.1 Single Conversion Mode                                                                                                          |     |

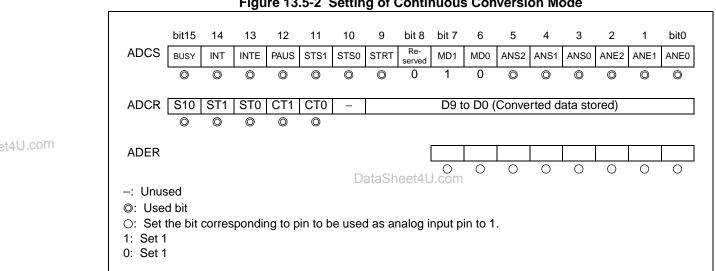

| 13.5.2 Continuous Conversion Mode                                                                                                      |     |

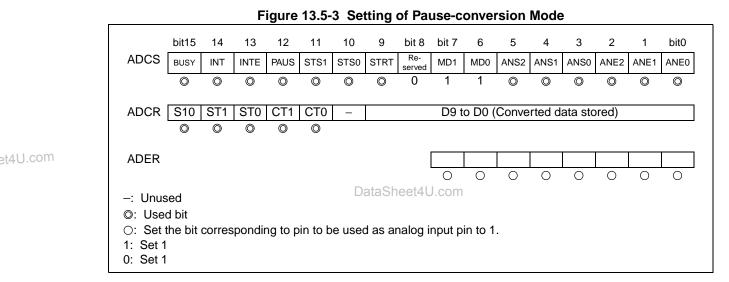

| 13.5.3 Pause-conversion Mode                                                                                                           |     |

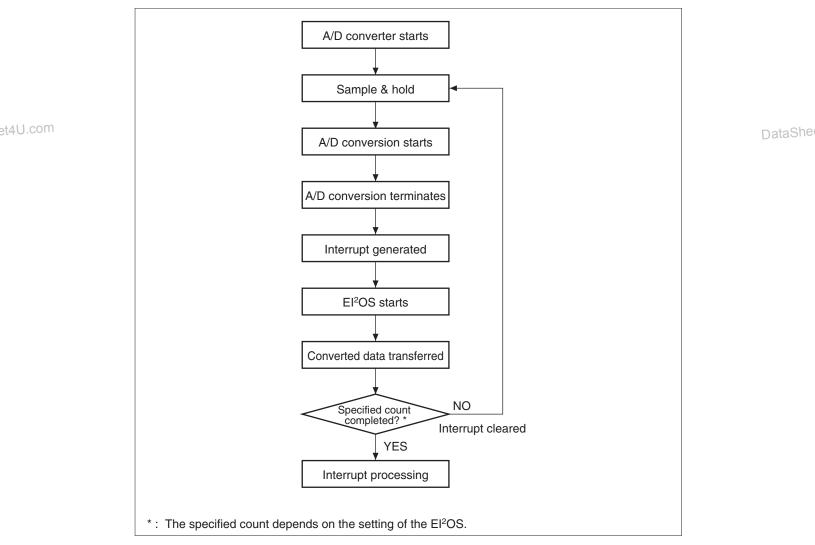

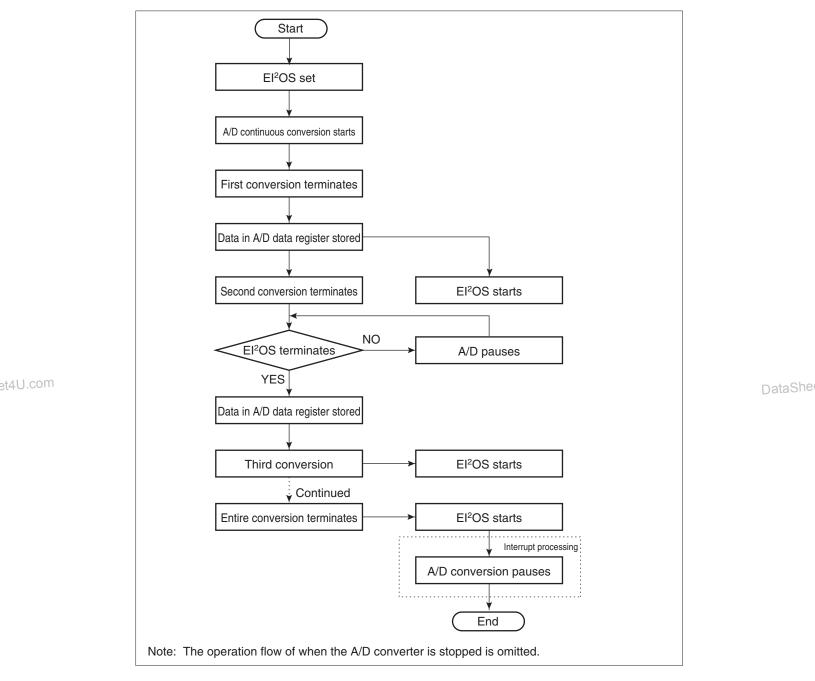

| 13.5.4 Conversion Using EI <sup>2</sup> OS Function                                                                                    |     |

| 13.5.5 A/D-converted Data Protection Function                                                                                          |     |

| 13.6 Precautions when Using 8-/10-bit A/D Converter                                                                                    | 375 |

| CHAPTER 14 UART1                                                                                                                       |     |

| 14.1 Overview of UART1                                                                                                                 |     |

|                                                                                                                                        |     |

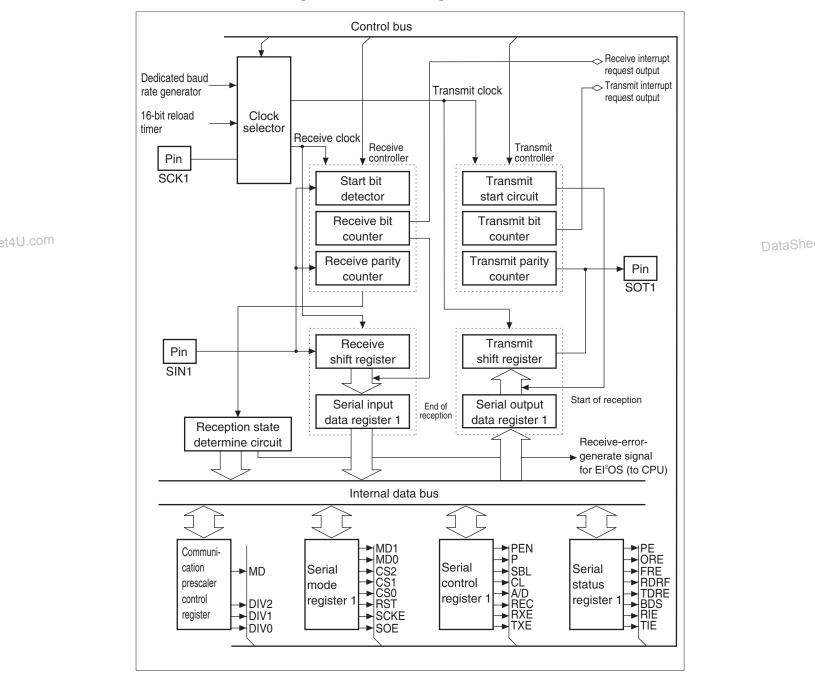

| 14.Z BIOCK DIADRAM OF UAR LT                                                                                                           |     |

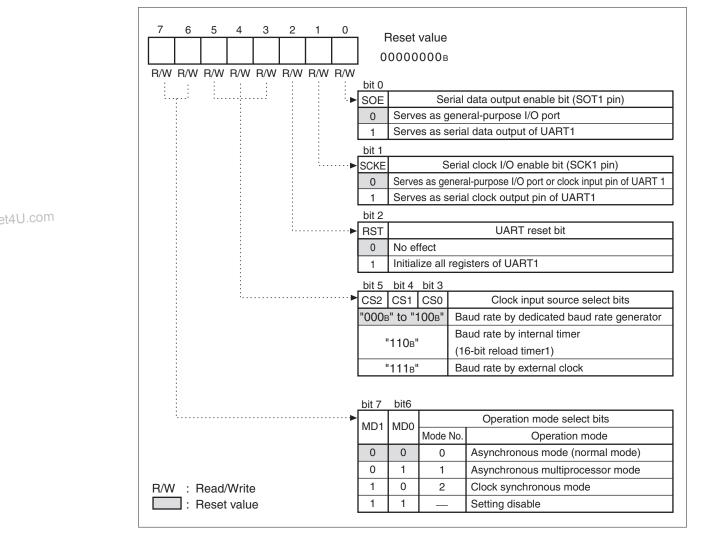

| 14.2 Block Diagram of UART1                                                                                                            | 283 |

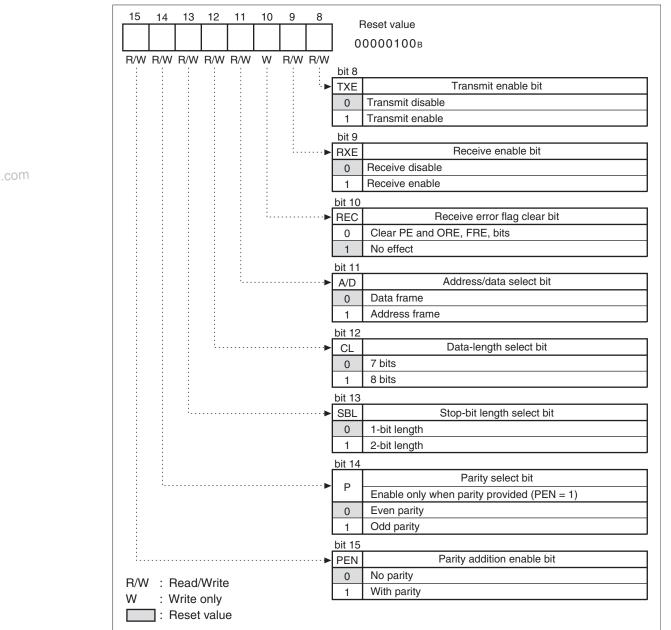

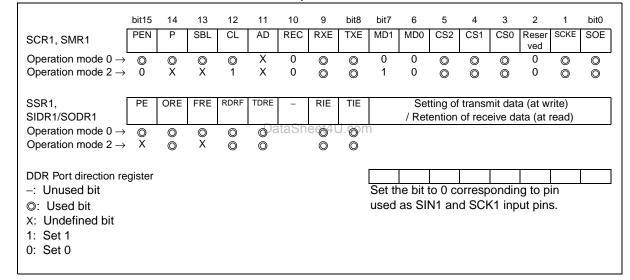

| 14.2 Block Diagram of UART1<br>14.3 Configuration of UART1<br>14.3.1 Serial Control Register 1 (SCR1)                                  |     |

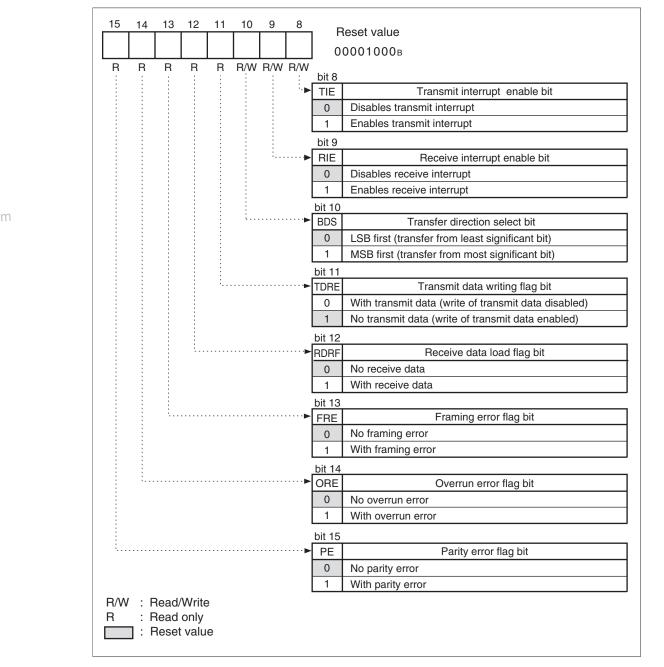

| 14.3.3 Serial Status Register 1 (SSR1)                                          |                     |

|---------------------------------------------------------------------------------|---------------------|

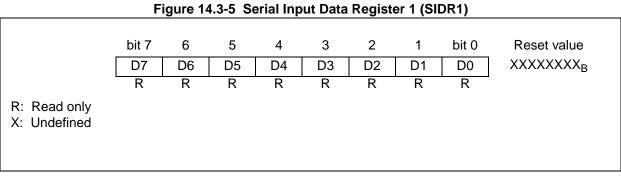

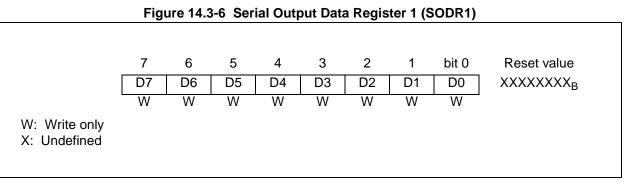

| 14.3.4 Serial Input Data Register 1 (SIDR1) and Serial Output Data Register     | 1 (SODR1) 391       |

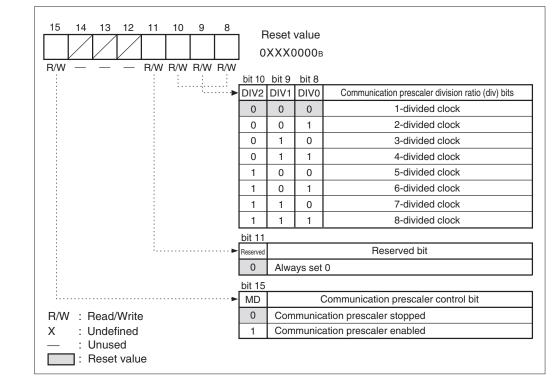

| 14.3.5 Communication Prescaler Control Register 1 (CDCR1)                       |                     |

| 14.4 Interrupt of UART1                                                         |                     |

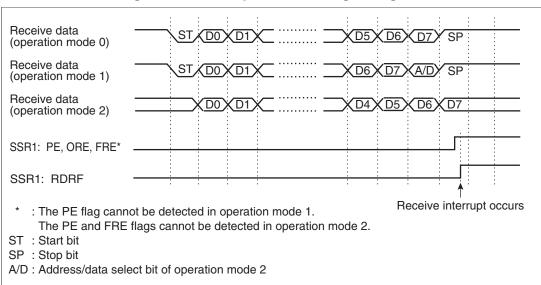

| 14.4.1 Generation of Receive Interrupt and Timing of Flag Set                   |                     |

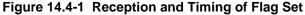

| 14.4.2 Generation of Transmit Interrupt and Timing of Flag Set                  |                     |

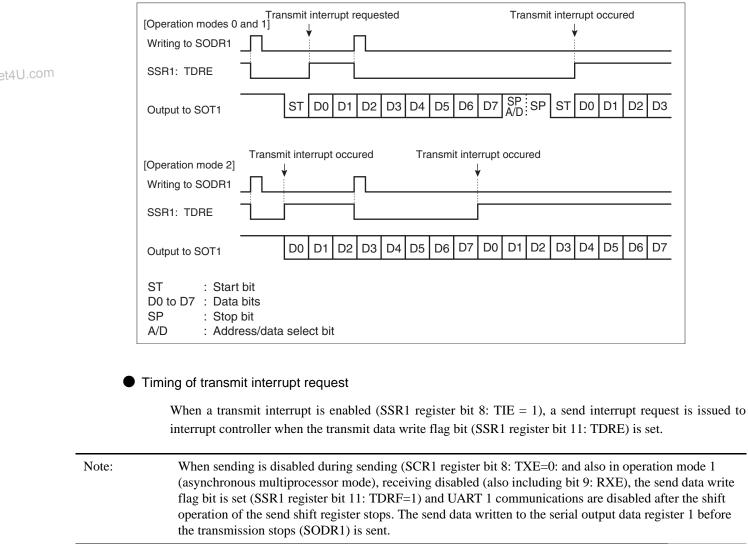

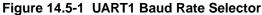

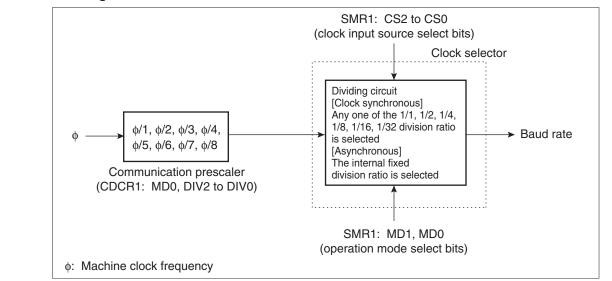

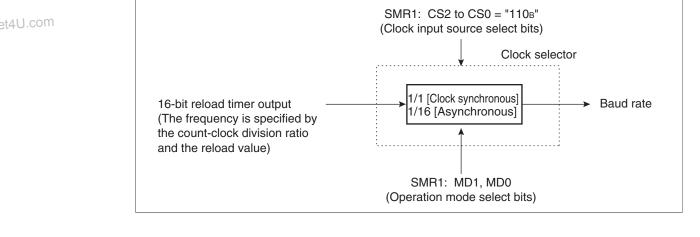

| 14.5 Baud Rate of UART1                                                         | 400                 |

| 14.5.1 Baud Rate by Dedicated Baud Rate Generator                               | 402                 |

| 14.5.2 Baud Rate by Internal Timer (16-bit Reload Timer)                        | 405                 |

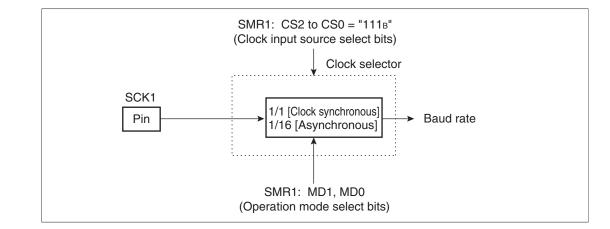

| 14.5.3 Baud Rate by External Clock                                              | 407                 |

| 14.6 Explanation of Operation of UART1                                          | 408                 |

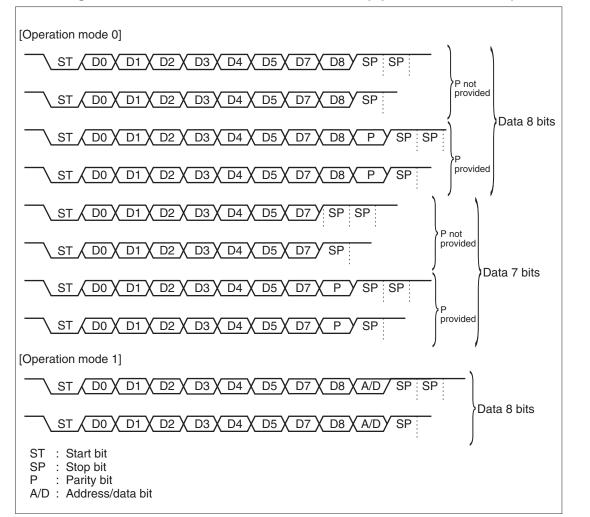

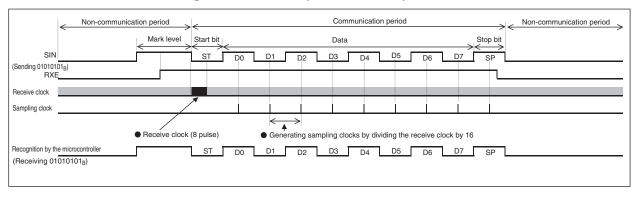

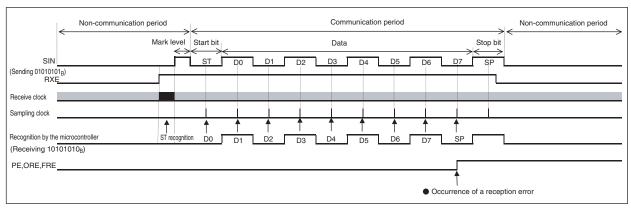

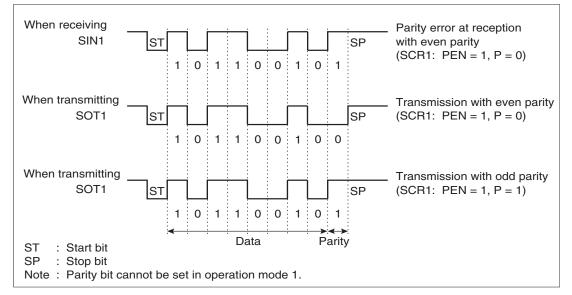

| 14.6.1 Operation in Asynchronous Mode (Operation Mode 0 or 1)                   | 410                 |

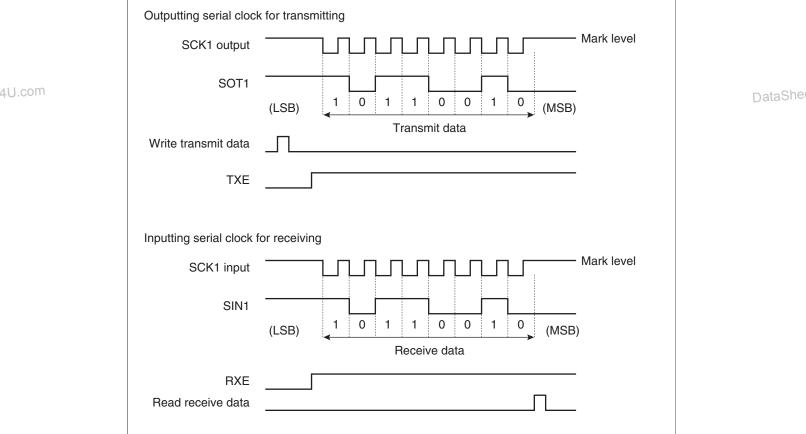

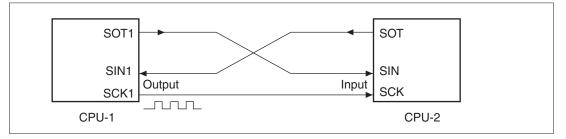

| 14.6.2 Operation in Clock Synchronous Mode (Operation Mode 2)                   | 415                 |

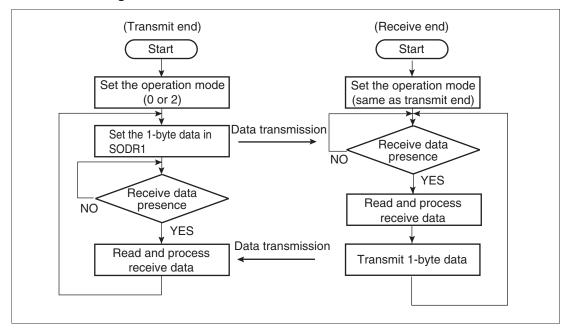

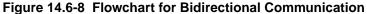

| 14.6.3 Bidirectional Communication Function (Operation Modes 0 and 2)           | 418                 |

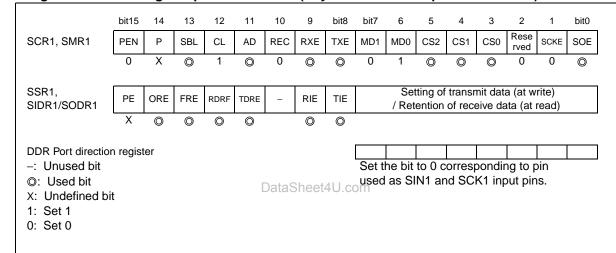

| 14.6.4 Master/Slave Type Communication Function (Multiprocessor Mode) .         | 420                 |

| 14.7 Precautions when Using UART1                                               | 423                 |

| 14.8 Program Example for UART1                                                  | 424                 |

| CHAPTER 15 CAN CONTROLLER                                                       |                     |

| 15.1 Overview of CAN Controller                                                 |                     |

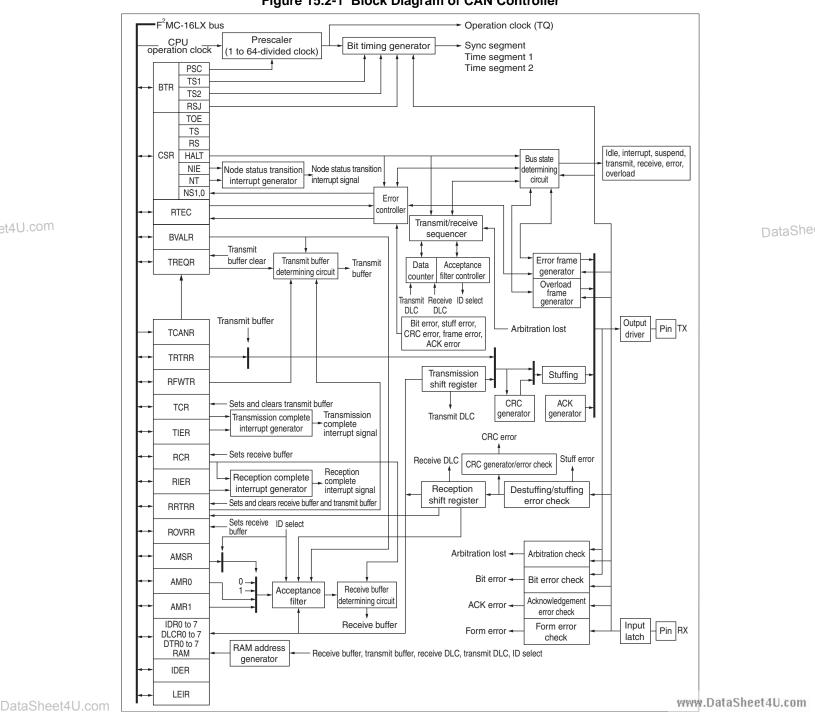

| 15.2 Block Diagram of CAN Controller                                            |                     |

| et4U.com 15.3 Configuration of CAN Controller                                   | 100                 |

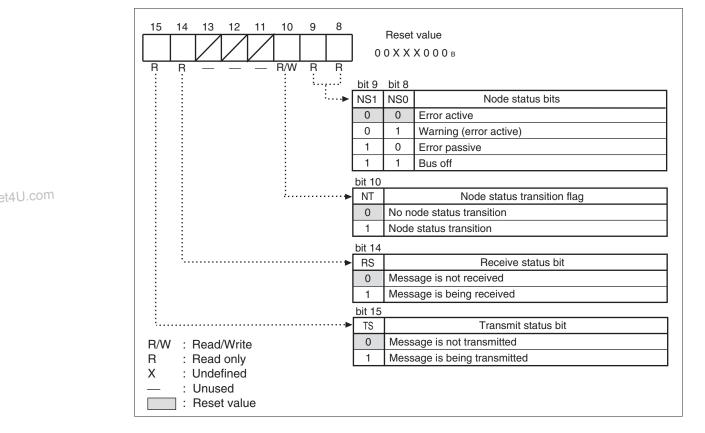

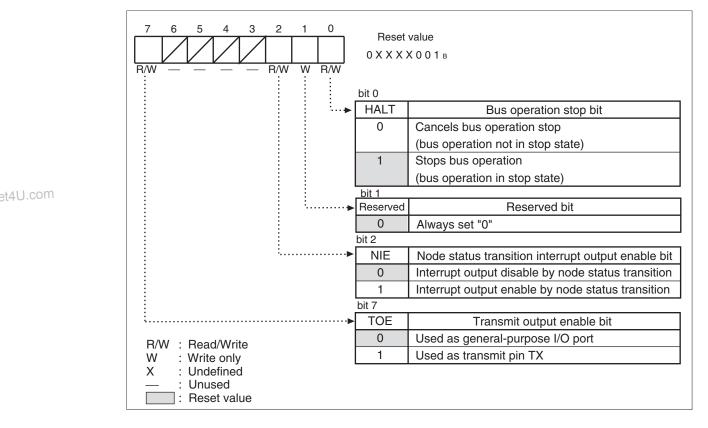

| 15.3.1 Control Status Register (High) (CSR: H)                                  | Dataone             |

| 15.3.2 Control Status Register (Low) (CSR <sup>1</sup> L <sup>Sheet4U.com</sup> |                     |

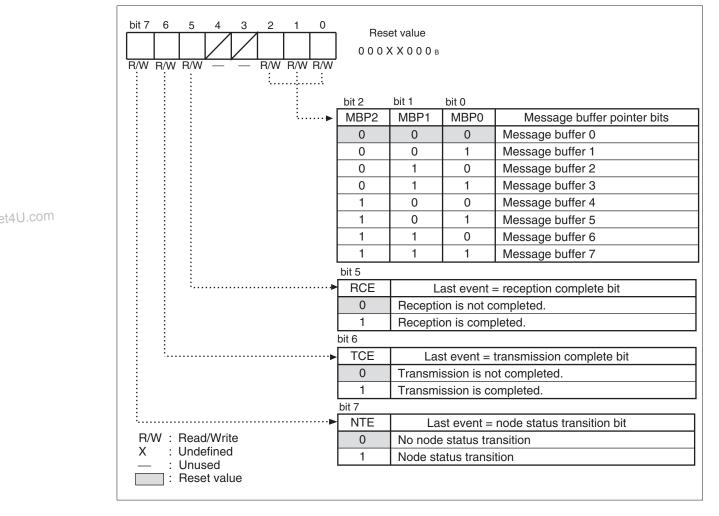

| 15.3.3 Last Event Indicate Register (LEIR)                                      |                     |

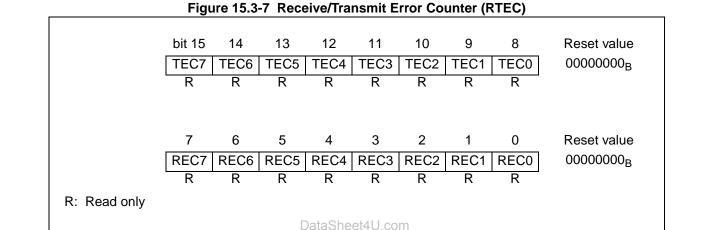

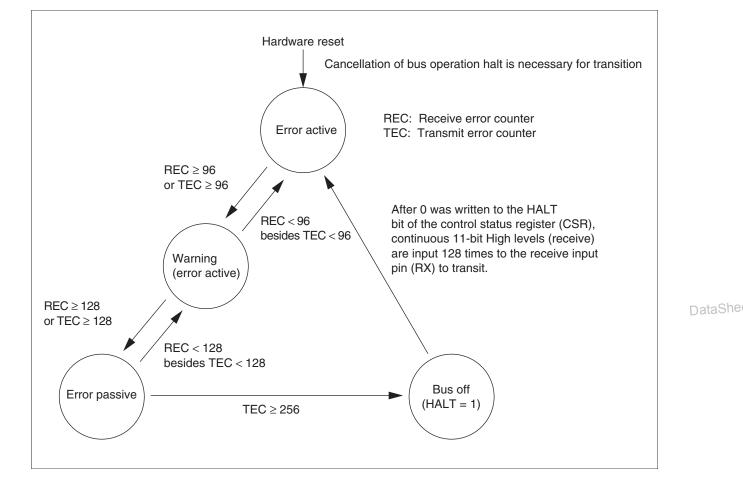

| 15.3.4 Receive/Transmit Error Counter (RTEC)                                    |                     |

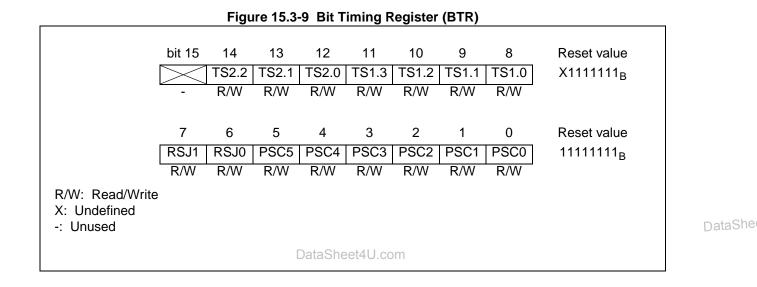

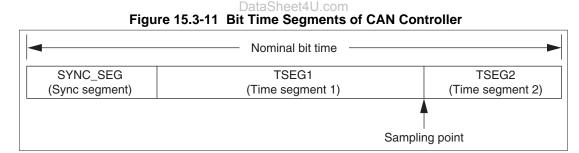

| 15.3.5 Bit Timing Register (BTR)                                                |                     |

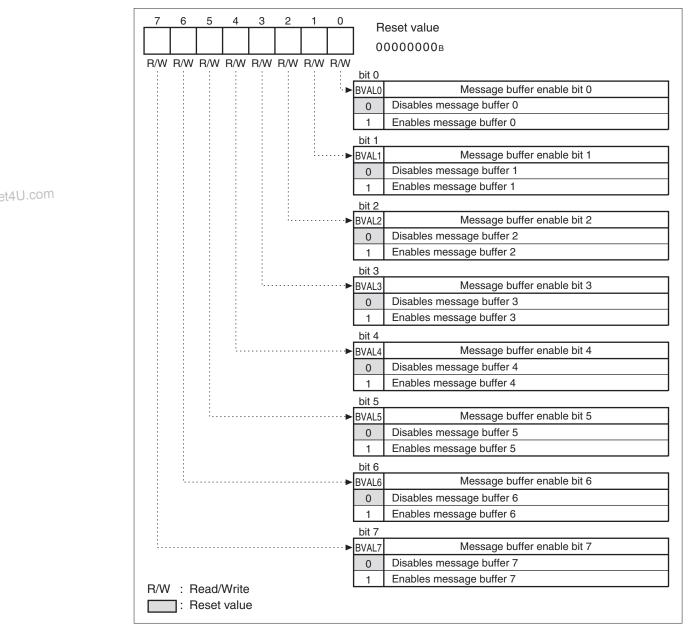

| 15.3.6 Message Buffer Valid Register (BVALR)                                    |                     |

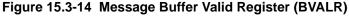

| 15.3.7 IDE Register (IDER)                                                      |                     |

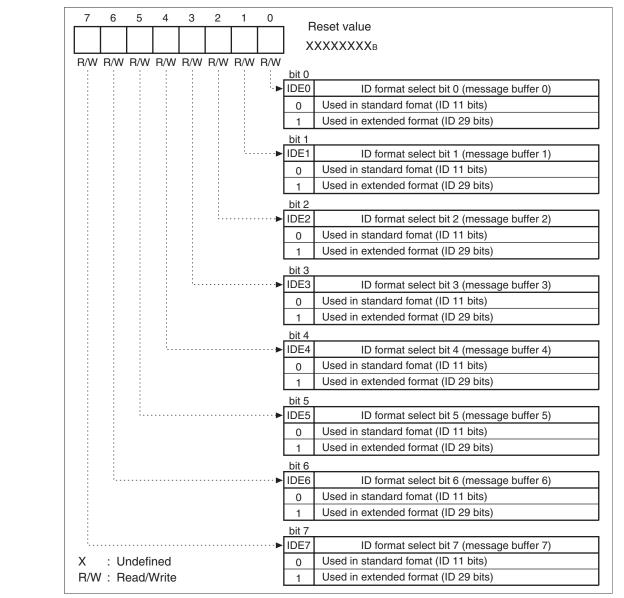

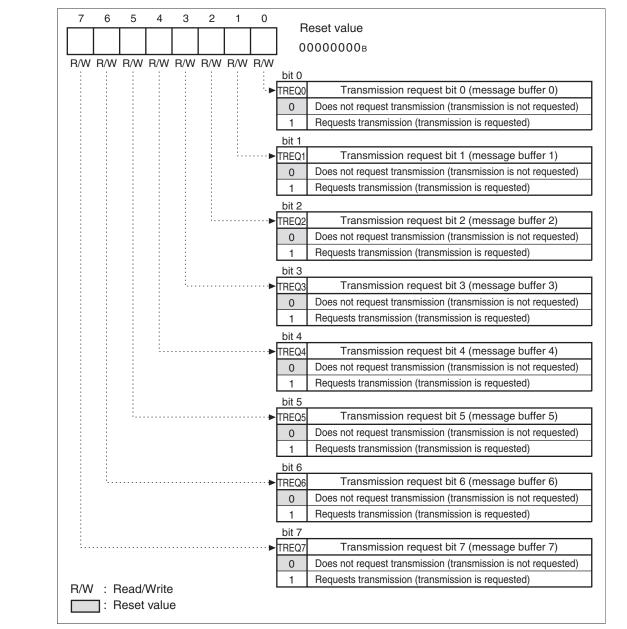

| 15.3.8 Transmission Request Register (TREQR)                                    |                     |

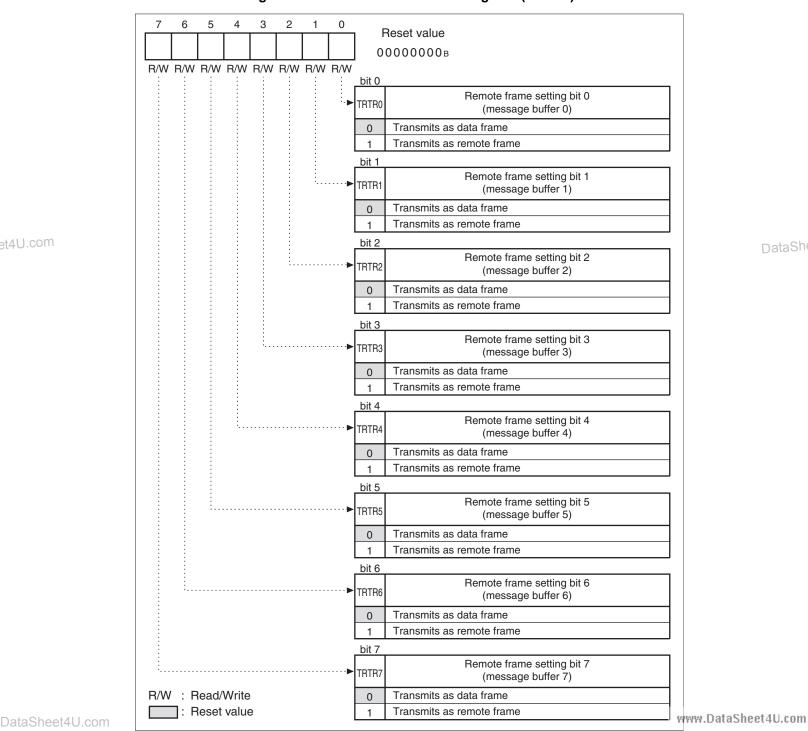

| 15.3.9 Transmission RTR Register (TRTRR)                                        |                     |

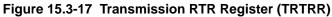

| 15.3.10 Remote Frame Receiving Wait Register (RFWTR)                            |                     |

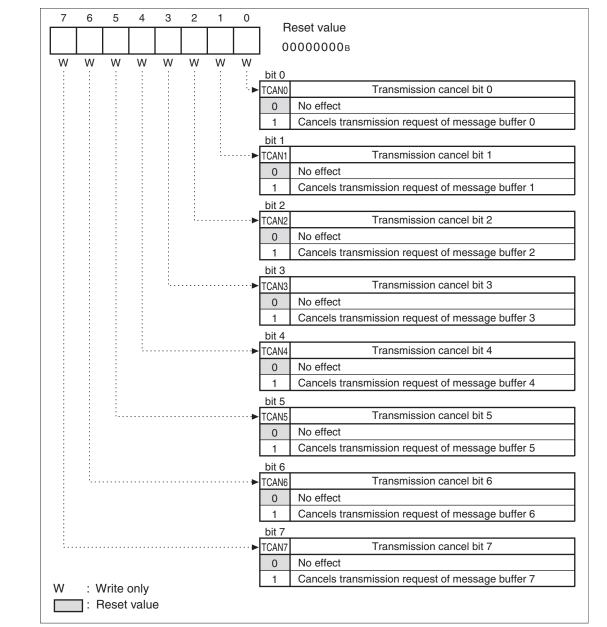

| 15.3.11 Transmission Cancel Register (TCANR)                                    |                     |

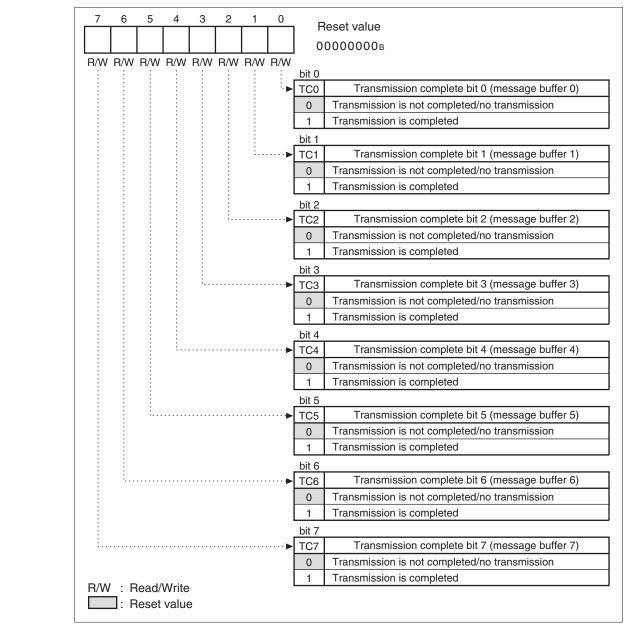

| 15.3.12 Transmission Complete Register (TCR)                                    |                     |

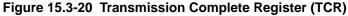

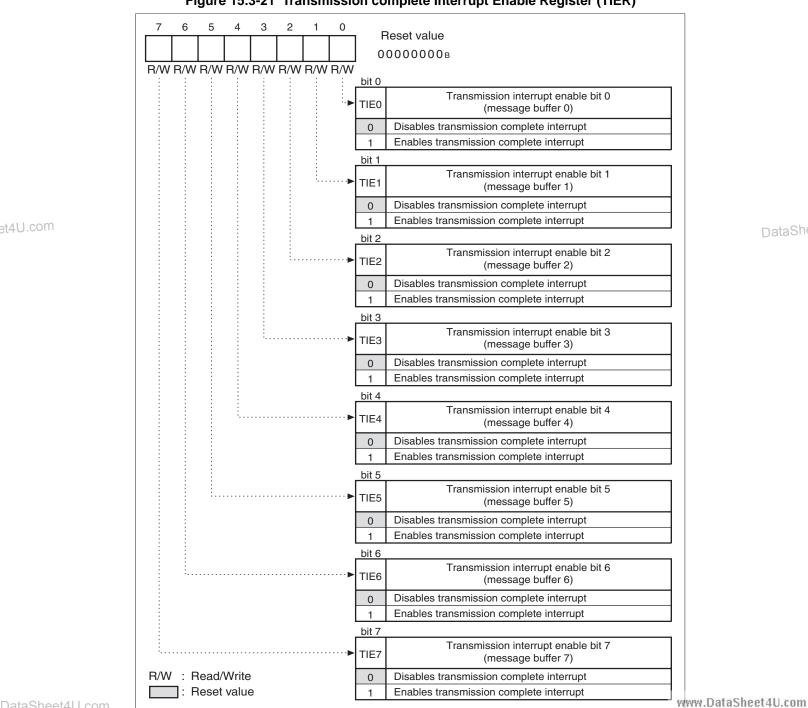

| 15.3.13 Transmission Complete Interrupt Enable Register (TIER)                  |                     |

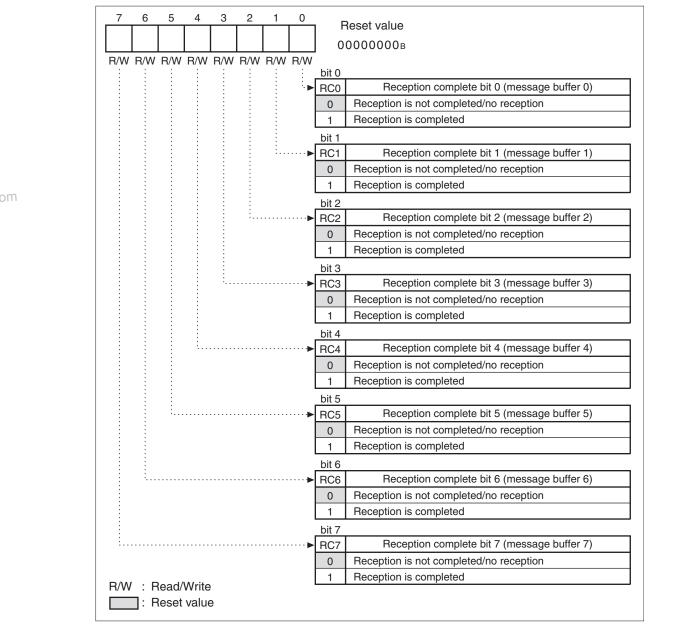

| 15.3.14 Reception Complete Register (RCR)                                       |                     |

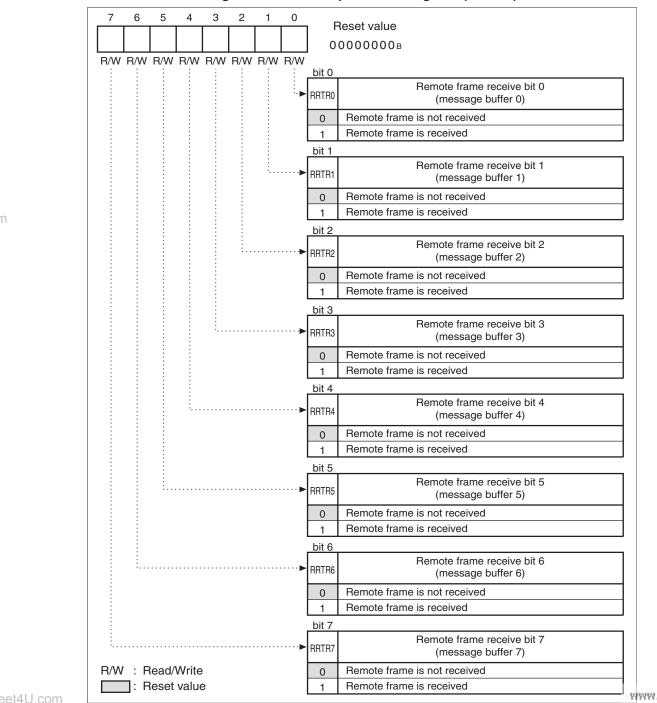

| 15.3.15 Reception RTR Register (RRTRR)                                          |                     |

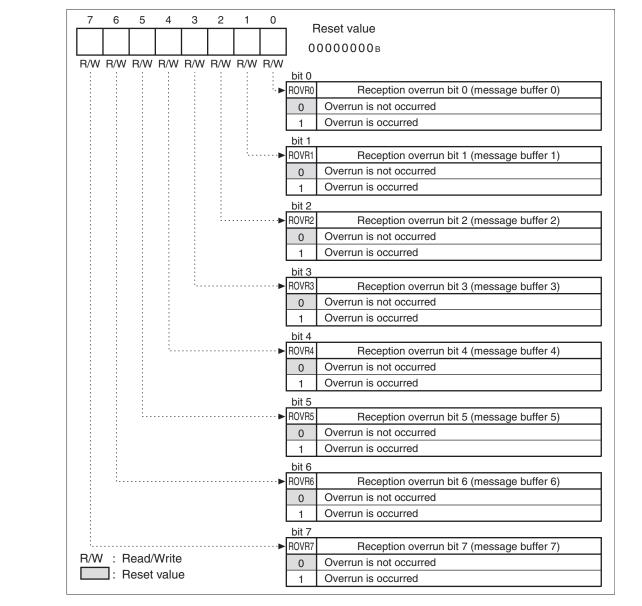

| 15.3.16 Reception Overrun Register (ROVRR)                                      |                     |

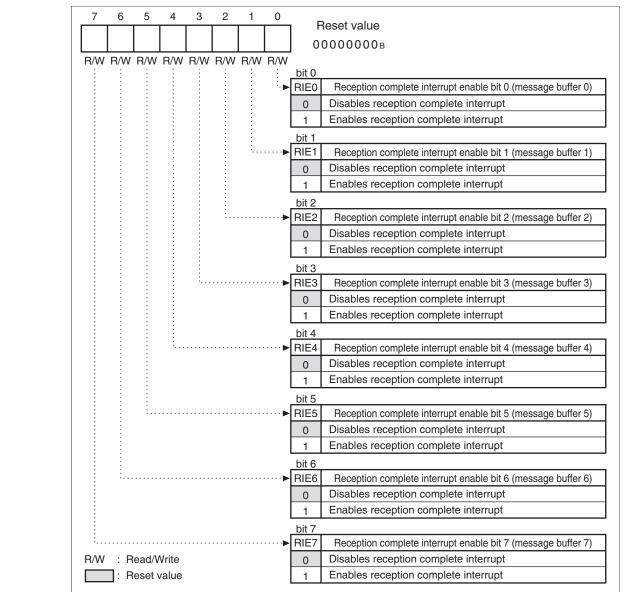

| 15.3.17 Reception Complete Interrupt Enable Register (RIER)                     |                     |

| 15.3.18 Acceptance Mask Select Register (AMSR)                                  |                     |

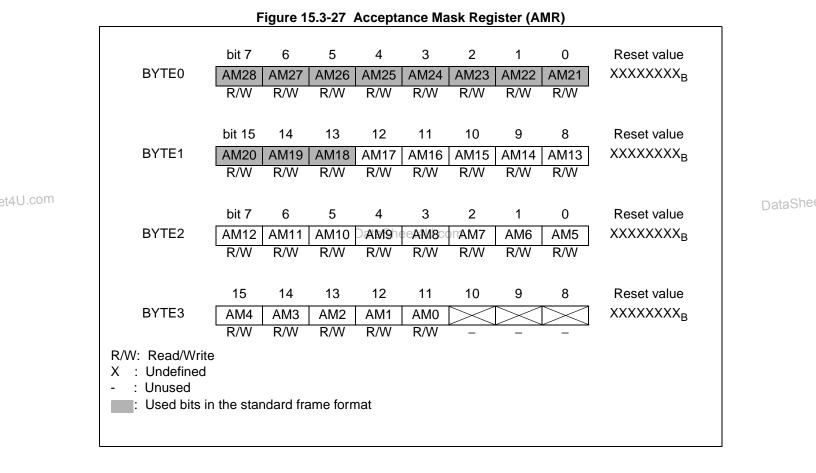

| 15.3.19 Acceptance Mask Register (AMR)                                          |                     |

| 15.3.20 Message Buffers                                                         |                     |

| -                                                                               |                     |

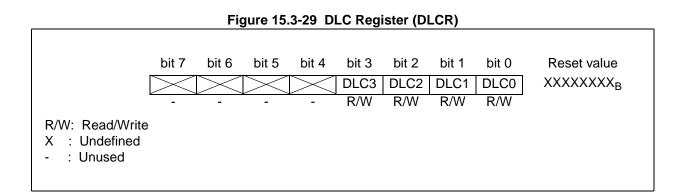

| 15.3.21 ID Register (IDRx, x = 7 to 0)<br>15.3.22 DLC Register (DLCR)           |                     |

| <b>-</b> . , ,                                                                  |                     |

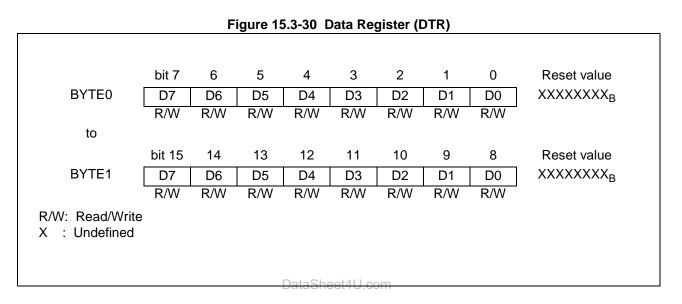

| 15.3.23 Data Register (DTR)<br>15.4 Interrupts of CAN Controller                |                     |

|                                                                                 |                     |

| 15.5 Explanation of Operation of CAN Controller<br>DataSheet4U.com              | www.DataSheet4U.com |

х

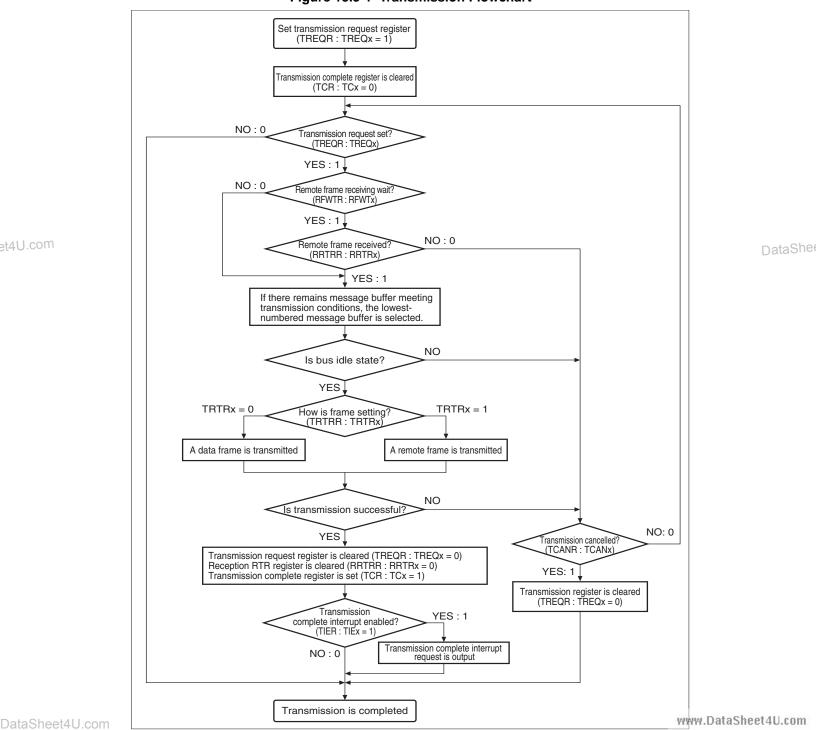

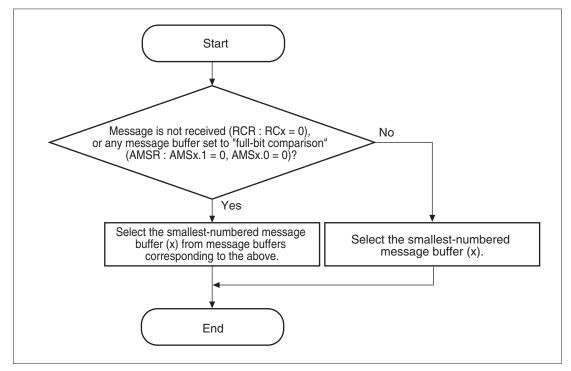

|                | 15.5.1 Transmission                                                                             | 487             |           |

|----------------|-------------------------------------------------------------------------------------------------|-----------------|-----------|

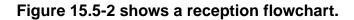

|                | 15.5.2 Reception                                                                                |                 |           |

|                | 15.5.3 Procedures for Transmitting and Receiving                                                |                 |           |

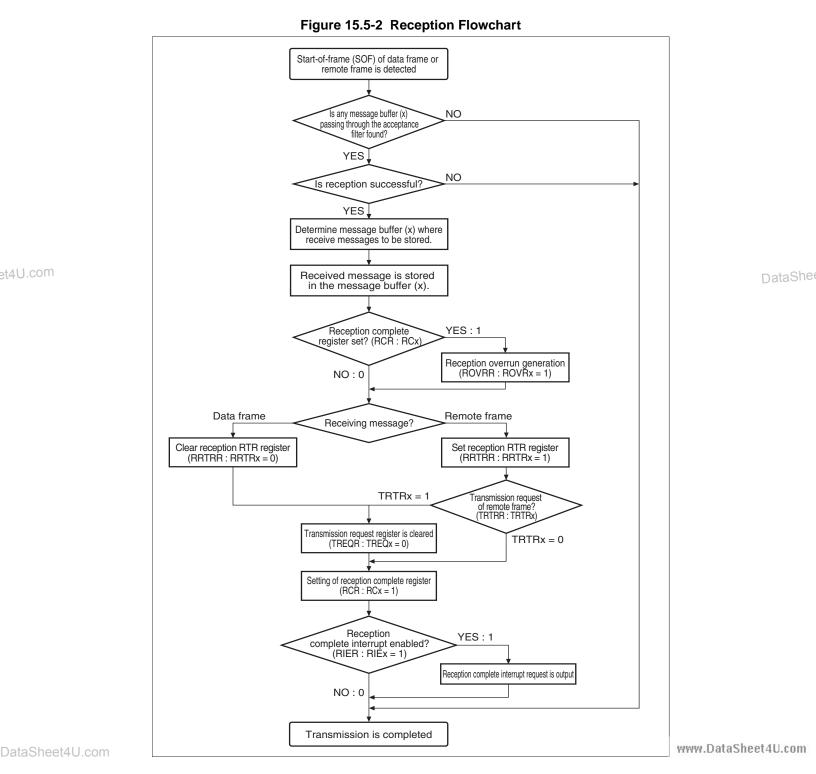

|                | 15.5.4 Setting Multiple Message Receiving                                                       |                 |           |

|                | 15.6 Precautions when Using CAN Controller                                                      |                 |           |

|                | 15.7 Program Example of CAN Controller                                                          |                 |           |

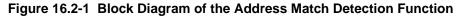

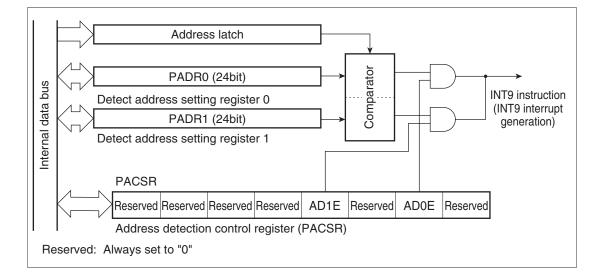

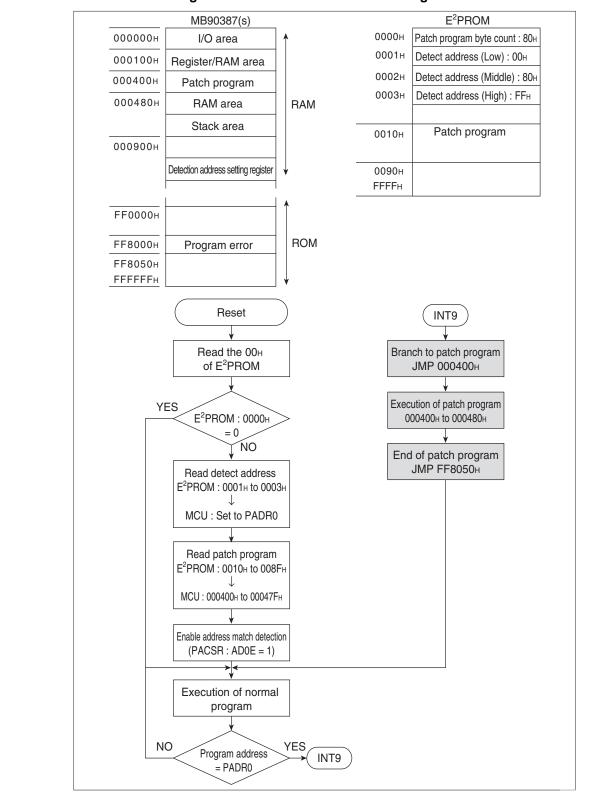

| CH             | APTER 16 8/16 ADDRESS MATCH DETECTION FUNCTION                                                  | 507             |           |

|                | 16.1 Overview of Address Match Detection Function                                               |                 |           |

|                | 16.2 Block Diagram of Address Match Detection Function                                          |                 |           |

|                | 16.3 Configuration of Address Match Detection Function                                          |                 |           |

|                | 16.3.1 Address Detection Control Register (PACSR)                                               |                 |           |

|                | 16.3.2 Detect Address Setting Registers (PADR0 and PADR1)                                       |                 |           |

|                | 16.4 Explanation of Operation of Address Match Detection Function                               |                 |           |

|                | 16.4.1 Example of using Address Match Detection Function                                        |                 |           |

|                | 16.5 Program Example of Address Match Detection Function                                        |                 |           |

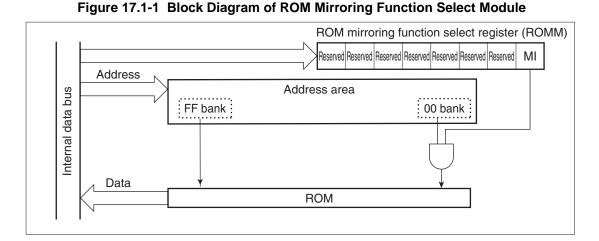

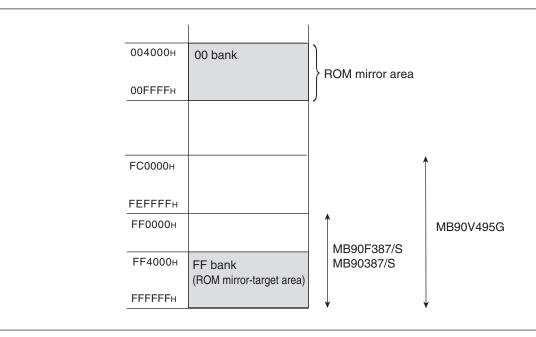

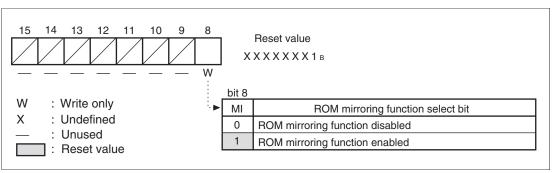

| CH             | APTER 17 ROM MIRRORING FUNCTION SELECT MODULE                                                   | 523             |           |

| _              | 17.1 Overview of ROM Mirroring Function Select Module                                           |                 |           |

|                | 17.2     ROM Mirroring Function Select Register (ROMM)                                          |                 |           |

| et4U.com       | IAPTER 18 512 KBIT FLASH MEMORY                                                                 | 507             | D. I. Cho |

| UI UI          |                                                                                                 |                 | DataShe   |

|                | <ul> <li>18.1 Overview of 512 Kbit Flash Memory</li></ul>                                       | 520             |           |

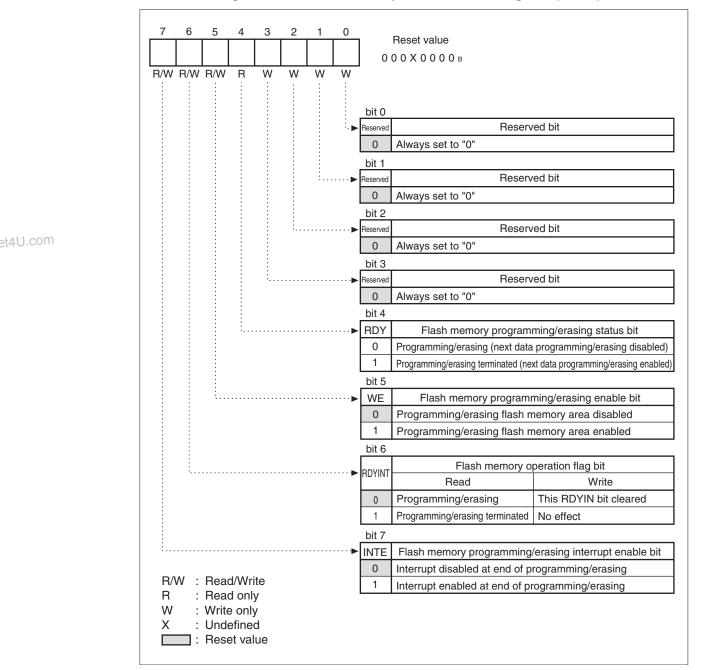

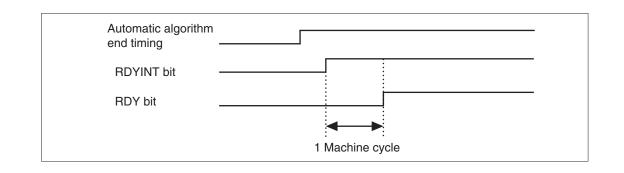

|                | 18.3       Flash Memory Control Status Register (FMCS)                                          |                 |           |

|                | 18.4       How to Start Automatic Algorithm of Flash Memory                                     |                 |           |

|                | 18.5 Check the Execution State of Automatic Algorithm                                           |                 |           |

|                | 18.5.1 Data Polling Flag (DQ7)                                                                  |                 |           |

|                | 18.5.2 Toggle Bit Flag (DQ6)                                                                    |                 |           |

|                | 18.5.3 Timing Limit Over Flag (DQ5)                                                             |                 |           |

|                | 18.5.4 Sector Erase Timer Flag (DQ3)                                                            |                 |           |

|                | 18.5.5 Toggle Bit 2 Flag (DQ2)                                                                  |                 |           |

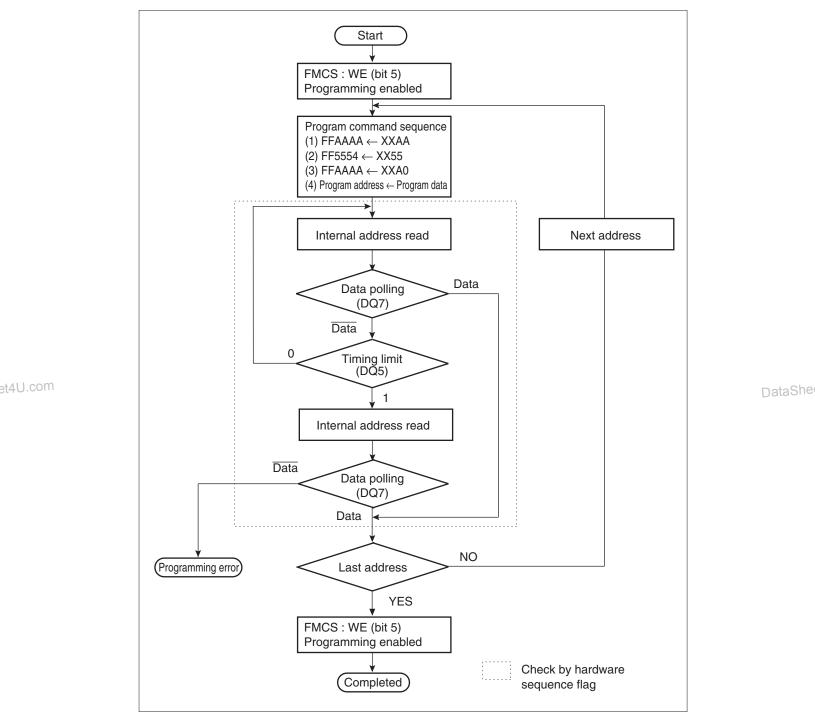

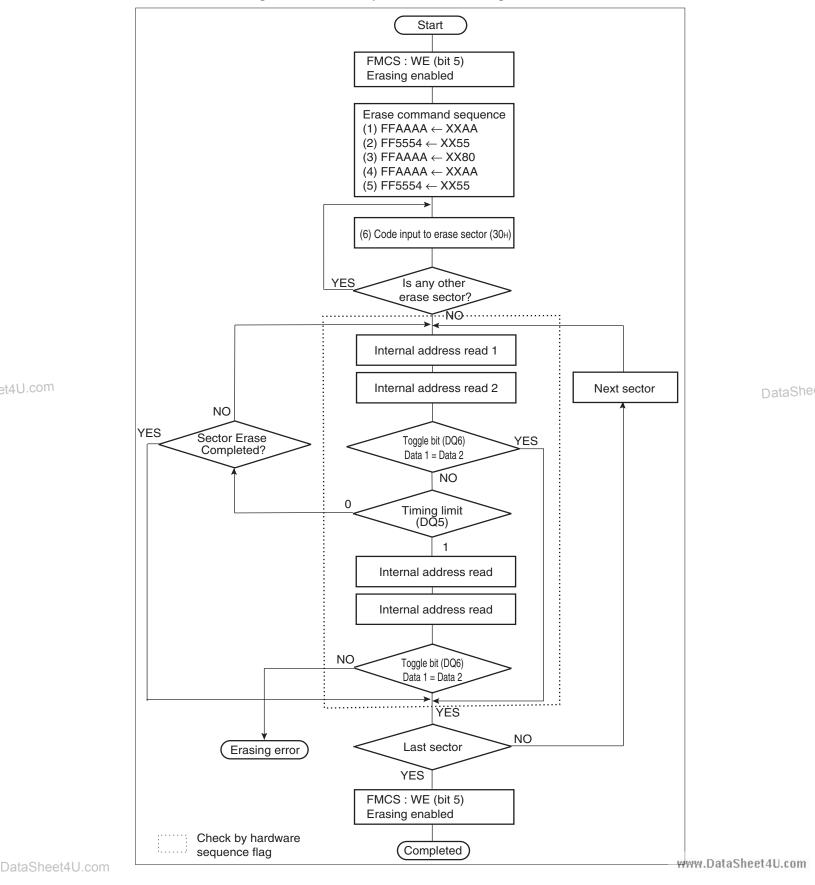

|                | 18.6 Details of Programming/Erasing Flash Memory                                                |                 |           |

|                | 18.6.1 Read/Reset State in Flash Memory                                                         |                 |           |

|                | 18.6.2 Data Programming to Flash Memory                                                         |                 |           |

|                | 18.6.3 Data Erase from Flash Memory (Chip Erase)                                                |                 |           |

|                | 18.6.4 Erasing Any Data in Flash Memory (Sector Erasing)                                        |                 |           |

|                | 18.6.5 Sector Erase Suspension in Flash Memory                                                  |                 |           |

|                | 18.6.6 Sector Erase Resumption in Flash Memory                                                  |                 |           |

|                | 18.7 Program Example of 512 Kbit Flash Memory                                                   |                 |           |

|                |                                                                                                 |                 |           |

|                | IAPTER 19 FLASH SERIAL PROGRAMMING CONNECTION                                                   |                 |           |

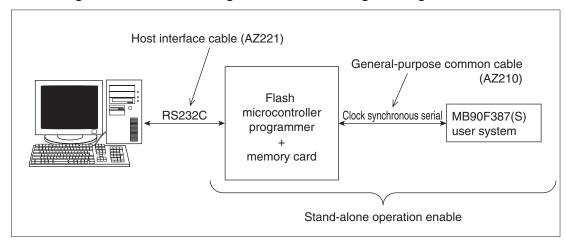

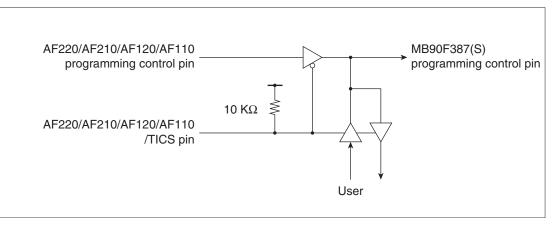

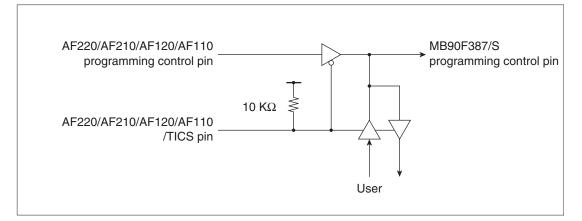

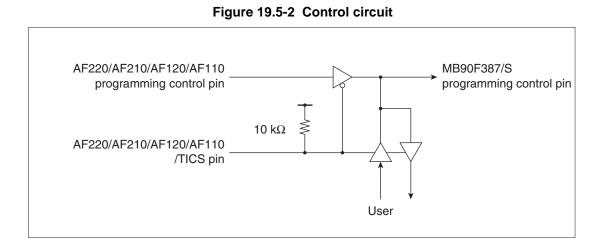

|                | 19.1 Basic Configuration of Serial Programming Connection for F <sup>2</sup> MC-16LX MB90F387/S |                 |           |

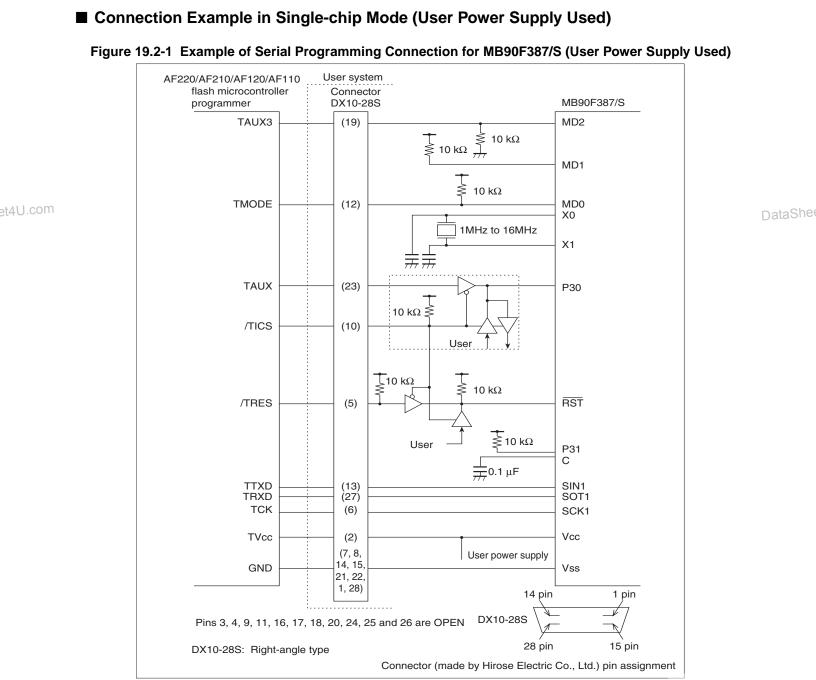

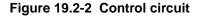

|                | 19.2 Connection Example in Single-chip Mode (User Power Supply)                                 |                 |           |

|                | 19.3 Connection Example in Single-chip Mode (Writer Power Supply)                               |                 |           |

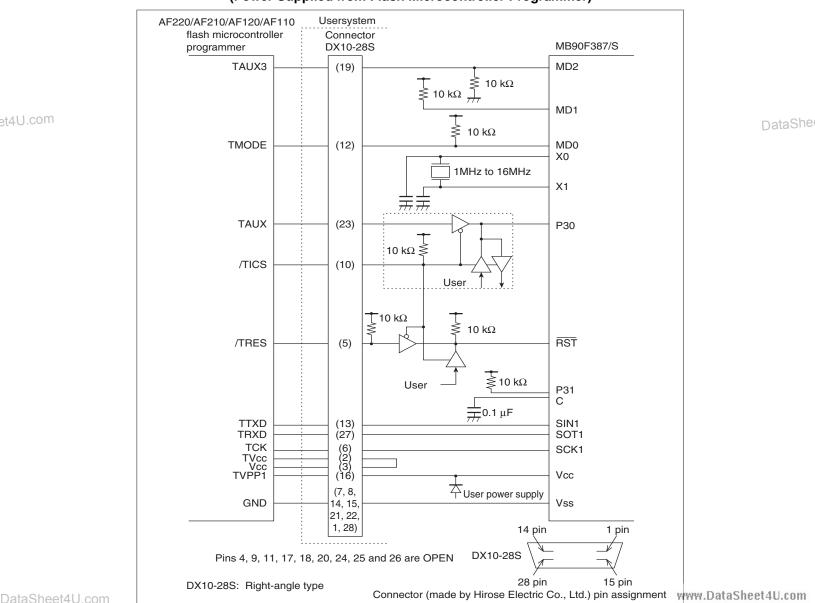

|                | 19.4 Example of Minimum Connection to Flash Microcontroller Programmer (User Power Supply)      |                 |           |

| DataSheet4U.co | 19.5 Example of Minimum Connection to Flash Microcontroller Programmer (Writer Power Supply)    | ) <b>56</b> 73h | eet4U.com |

| AF | PEND  | DIX                                     | 569 |

|----|-------|-----------------------------------------|-----|

|    |       | DIX A Instructions                      |     |

|    | A.1   | Instruction Types                       | 571 |

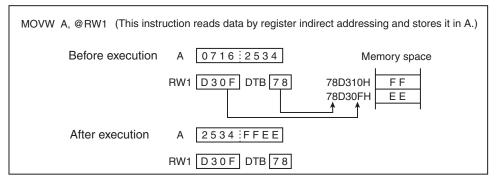

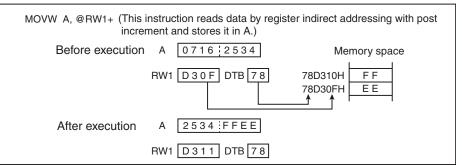

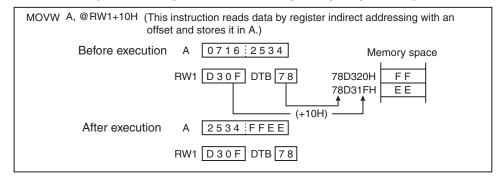

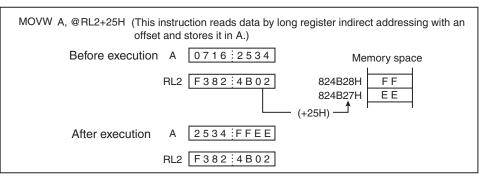

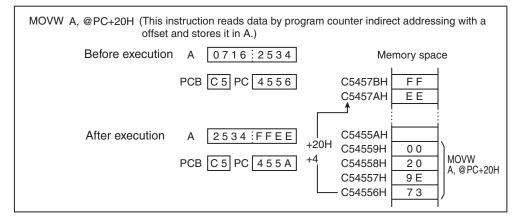

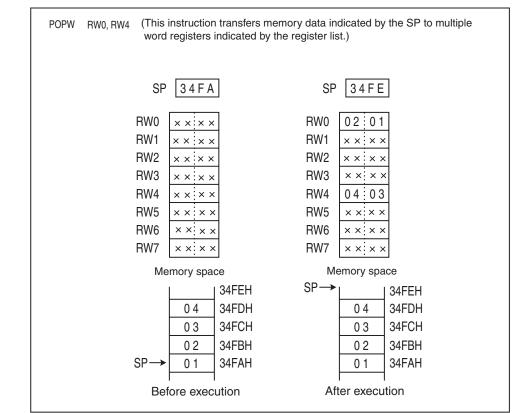

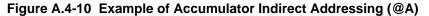

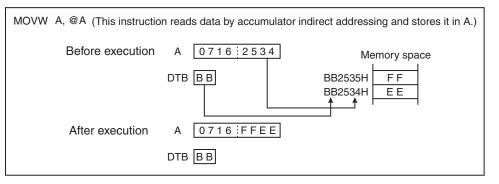

|    | A.2   | Addressing                              | 572 |

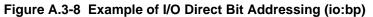

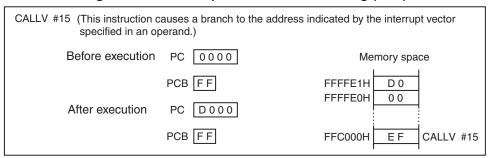

|    | A.3   | Direct Addressing                       | 574 |

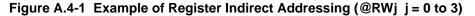

|    | A.4   | Indirect Addressing                     | 580 |

|    | A.5   | Execution Cycle Count                   |     |

|    | A.6   | Effective Address Field                 | 590 |

|    | A.7   | How to Read the Instruction List        |     |

|    |       | F <sup>2</sup> MC-16LX Instruction List |     |

|    |       | Instruction Map                         |     |

|    | APPEN | DIX B Register Index                    | 631 |

|    |       | DIX C Pin Function Index                |     |

|    | APPEN | IDIX D Interrupt Vector Index           | 642 |

|    |       |                                         |     |

DataSheet4U.com

www.DataSheet4U.com

This chapter describes the features and basic specifications of the MB90385 series.

- 1.1 Features of MB90385 Series

- 1.2 Product Lineup for MB90385 Series

- 1.3 Block Diagram of MB90385 Series

- 1.4 Pin Assignment

- 1.5 Package Dimension

- 1.6 Pin Description

- 1.7 I/O Circuit

et4U.com

1

## 1.1 Features of MB90385 Series

The MB90385 series is a general-purpose, high-performance 16-bit microcontroller designed for control of processors such as consumer products requiring high-speed real-time processing. This series has a full CAN interface.

The instruction system is based on the architecture of the F<sup>2</sup>MC family and provides additional high-level language instructions, extended addressing modes, enhanced multiply/divide instructions, and enriched bit processing instructions. A 32-bit accumulator enables long-word data (32 bits) processing.

## Features of MB90385 Series

Clock

- Built-in PLL clock multiplying circuit

- Machine clock (PLL clock) selectable from 1/2 frequency of oscillation clock or 1 to 4-multiplied oscillation clock (4 MHz to 16 MHz when oscillation clock is 4 MHz)

- Subclock operation (8.192 kHz) (MB90387, MB90F387)

- Minimum instruction execution time: 62.5 ns (4-MHz oscillation clock, 4-multiplied PLL clock)

16-MB CPU memory space

• Internal 24-bit addressing

Instruction system optimized for controllers

- Various data types (bit, byte, word, long word)

- 23 types of addressing modes

- Enhanced signed instructions of multiplication/division and RETI instruction function

- High-accuracy operations enhanced by 32-bit accumulator

- Instruction system for high-level language (C language)/multitask

- System stack pointer

- Enhanced pointer indirect instructions

- Barrel shift instructions

- Higher execution speed

- 4-byte instruction queue

- Powerful interrupt function

- Powerful interrupt function with 8 levels and 34 factors

DataSheet4U.com

et4U.com

- CPU-independent automatic data transfer function

- Extended intelligent I/O service (EI<sup>2</sup>OS): Maximum 16 channels

- Lower-power consumption (standby) modes

- Sleep mode (stops CPU clock)

- Timebase timer mode (operates only oscillation clock and subclock, timebase timer and watch timer)

- Watch mode (operates only subclock and watch timer)

- Stop mode (stops oscillation clock and subclock)

- CPU Intermittent operation mode

- Process

- CMOS Technology

- I/O ports

- General-purpose I/O ports (CMOS output): 34 ports (for M90387 or M90F387) (included 4 output ports for high current)

Note : 36 ports (for MB90387S or MB90F387S) on condition of unusing sub-clock.

#### Timers

et4U.com

DataShe

- Timebase timer, watch timer, watchdog timer: 1 channel

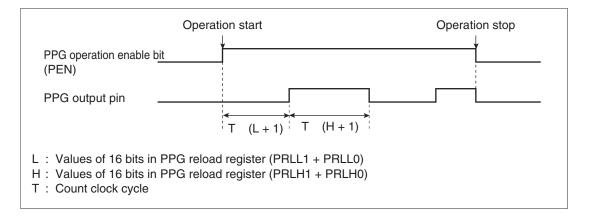

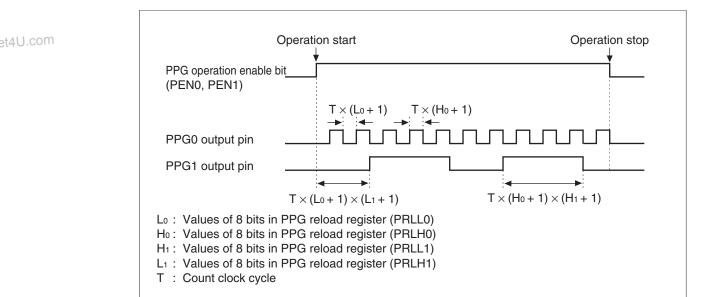

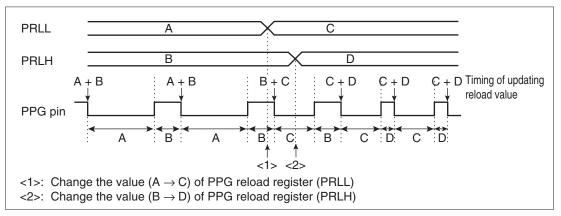

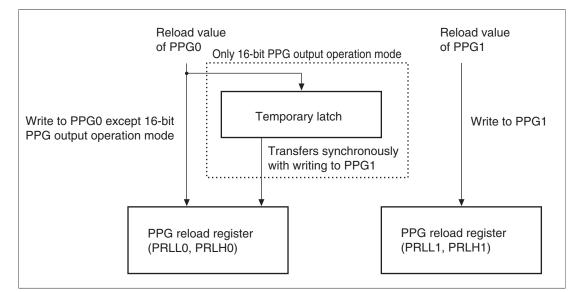

- 8/16-bit PPG timer: 8 bits  $\times$  4 channels or 16 bits  $\times$  2 channels

- 16-bit reload timer: 2 channels

- 16-bit I/O timer

- 16-bit free-run timer: 1 channel

- 16-bit input capture (ICU): 4 channels

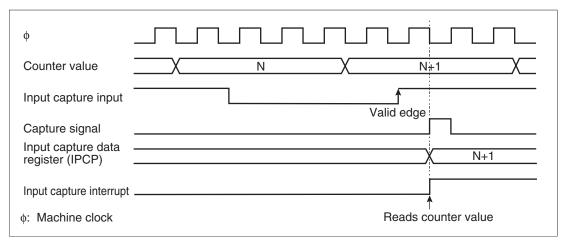

By detecting the edge of the pin input, the count value of the 16-bit free-run timer is latched to generate an interrupt request.

#### CAN Controller: 1 channel

- Conforms to CAN Specification Ver. 2.0A and Ver. 2.0B.

- Built-in 8 message buffers

- Transfer rate: 10 Kbps to 1 Mbps (at 16-MHz machine clock frequency)

- CAN wake-up

- UART1 (SCI): 1 channel

- Full-duplex double buffer

- Clock asynchronous or clock synchronous serial transfer

- DTP/external interrupt: 4 channels

- External input to start EI<sup>2</sup>OS and external interrupt generation module

- Delayed interrupt generation module

- Generates interrupt request for task switching

- 8-/10-bit A/D converter: 8 channels

- 8-bit and 10-bit resolutions

- Start by external trigger input

- Conversion time: 6.125µs (including sampling time at 16-MHz machine clock frequency)

- Program patch function

- Detects address match for two address pointers

et4U.com

DataSheet4U.com

DataShe

4

## 1.2 Product Lineup for MB90385 Series

## The MB90385 series is available in three types. This section provides the product lineup, CPU, and resources.

## ■ Product Lineup for MB90385 Series

| Table 1.2-1 | Product | Lineup for | MB90385 | Series |

|-------------|---------|------------|---------|--------|

|-------------|---------|------------|---------|--------|

|                                          | -                                                       |                                                                          |                                                                       |

|------------------------------------------|---------------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------------|

|                                          | MB90V495G                                               | MB90F387/S                                                               | MB90387/S                                                             |

| Classification                           | Evaluation product                                      | Flash ROM                                                                | Mask ROM                                                              |

| ROM Size                                 |                                                         | 64                                                                       | KB                                                                    |

| RAM Size                                 | 6 KB                                                    | 21                                                                       | КВ                                                                    |

| Clock                                    | Dual system products                                    | MB90F387: dual system<br>products<br>MB90F387S: single system<br>product | MB90387: dual system<br>products<br>MB90387S:single system<br>product |

| Process                                  |                                                         | CMOS                                                                     |                                                                       |

| Package                                  | PGA256DataSheet4U.com LQFP-48 (with 0.50-mm pin pitch), |                                                                          | 50-mm pin pitch),                                                     |

| Operating supply voltage                 | 4.5 V to 5.5 V                                          | 3.5 V t                                                                  | o 5.5 V                                                               |

| Power supply for emulator * Not provided |                                                         | -                                                                        |                                                                       |

\*: Setting of DIP Switch (S2) when using emulation pod (MB2145-507). For details, refer to the MB2145-507 Hardware Manual (Section 2.7 Emulator-specific Power Supply).

et4U.com

## ■ CPU and Resources for MB90385 Series

## Table 1.2-2 CPU and Resources for MB90385 Series (1/2)

|                                             |               | MB90V495G                                                                                                                                                         | MB90F387/S                                                      | MB90387/S                             |

|---------------------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|---------------------------------------|

| CPU Function                                |               | Basic instruction count: 351<br>Instruction bit length: 8 or 1<br>Instruction length: 1 to 7 by<br>Data bit length: 1, 8, or 16 b                                 | 6 bits<br>tes                                                   |                                       |

|                                             |               | Minimum instruction execut                                                                                                                                        | tion time: 62.5 ns (at 16-MHz                                   | machine clock frequency)              |

|                                             |               | Interrupt processing time: 1.                                                                                                                                     | 5 µs (at 16-MHz machine clo                                     | ock frequency)                        |

| Low-power consu<br>(standby) modes          | mption        | Sleep mode, watch mode, tin<br>operation mode                                                                                                                     | mebase timer mode, stop mod                                     | le, CPU intermittent                  |

| I/O Ports                                   |               | General-purpose I/O ports (                                                                                                                                       | CMOS output):34 ports (36 p<br>included 4 outj<br>(P14 to P17)  | orts *)<br>put ports for high current |

| Timebase timer                              |               | 18-bit free-run counter<br>Interrupt cycle: 1.024, 4.096<br>(at 4-MHz oscillation clock                                                                           |                                                                 |                                       |

| Watchdog timer                              |               | Reset cycle: 3.58, 14.33, 57.23, 458.75 ms<br>(at 4-MHz oscillation clock frequency)                                                                              |                                                                 |                                       |

| 16-bit I/O timers 16-bit free-<br>run timer |               | Channel count: 1<br>Overflow interrupt                                                                                                                            |                                                                 |                                       |

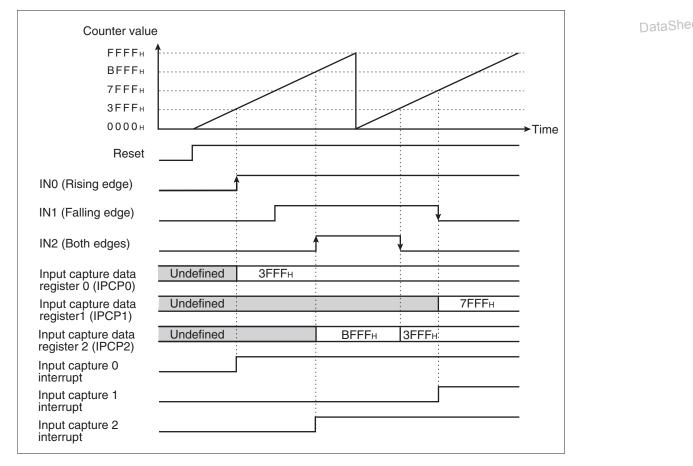

|                                             | Input capture | Channel count: 4<br>Free-run timer values saved by pin input (rising edge, falling edge, both edges)                                                              |                                                                 |                                       |

| 16-bit reload timer                         |               | Channel count: 2<br>Operation of 16-bit reload ti<br>Count clock cycle: 0.25µs, 0<br>(at 16-MHz machine clock f<br>External event countable                       | ).5μs, 2.0μs                                                    |                                       |

| Watch timer                                 |               | 15-bit free-run counter<br>Interrupt cycle: 31.25, 62.5,<br>frequency)                                                                                            | 12, 250, 500 ms, and 1.0 s, 2.                                  | .0 s (at 8.192-kHz subclock           |

| 8-/16-bit PPG timer                         |               | Channel count: 2 (operable<br>PPG operable with 8 bits x <sup>4</sup><br>Pulse waveform output at ar<br>Count clock: 62.5 ns to 1µs<br>(at 16-MHz machine clock f | t channels or 16 bits x 1 chan<br>bitrary cycle and duty        | nel                                   |

| Delayed interrupt generation module         |               | Interrupt generation module for switching task<br>Used for Real-time OS                                                                                           |                                                                 |                                       |

| DTP/external interrupt                      |               | • • •                                                                                                                                                             | es and by High- or Low-level<br>led intelligent I/O service (EI |                                       |

DataSheet4U.com

et4U.com

## Table 1.2-2 CPU and Resources for MB90385 Series (2/2)

|                         | MB90V495G                                                                                                                                                                                                                                                                                                                                                                                                                                                | MB90F387/S | MB90387/S |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------|

| 8-/10-bit A/D converter | Channel count: 8<br>Resolution: 10 or 8 bits<br>Conversion time: 6.125µs (including sampling time at 16-MHz machine clock<br>frequency)<br>Two or more continuous channels can be converted sequentially (up to 8 channels)<br>Single conversion mode: Selected channel converted once only<br>Continuous conversion mode: Selected channel converted continuously<br>Stop conversion mode: Selected channel converted and temporary stopped alternately |            |           |

| UART 1                  | Channel count: 1<br>Clock synchronous transfer: 62.5 Kbps to 2 Mbps<br>Clock asynchronous transfer: 9,615 bps to 500 kbps<br>Two-way serial communication function, master/slave-connected communication                                                                                                                                                                                                                                                 |            |           |

| CAN                     | Conforms to CAN Specification Ver. 2.0A and Ver. 2.0B<br>Transmit/receive message buffer: 8<br>Transfer bit rate: 10 Kbps to 1 Mbps (at 16-MHz machine clock)<br>CAN wake-up                                                                                                                                                                                                                                                                             |            | e clock)  |

\*: MB90387S, MB90F387S

et4U.com

DataSheet4U.com

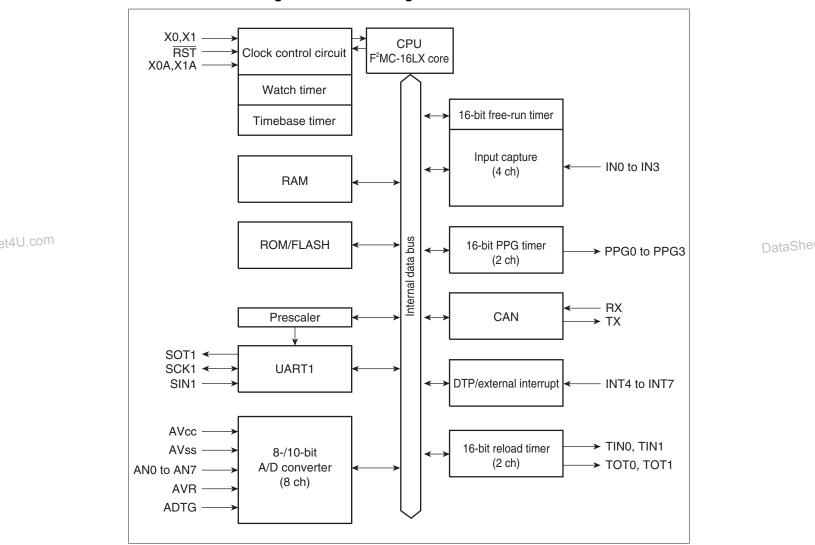

## 1.3 Block Diagram of MB90385 Series

Block diagram of the MB90385 series is shown in the figure below.

## Block Diagram of MB90385 Series

DataSheet4U.com

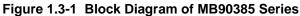

## 1.4 Pin Assignment

Pin assignment of the MB90385 series is shown in the figure below.

## ■ Pin Assignment (FPT-48P-M26)

DataSheet4U.com

et4U.com

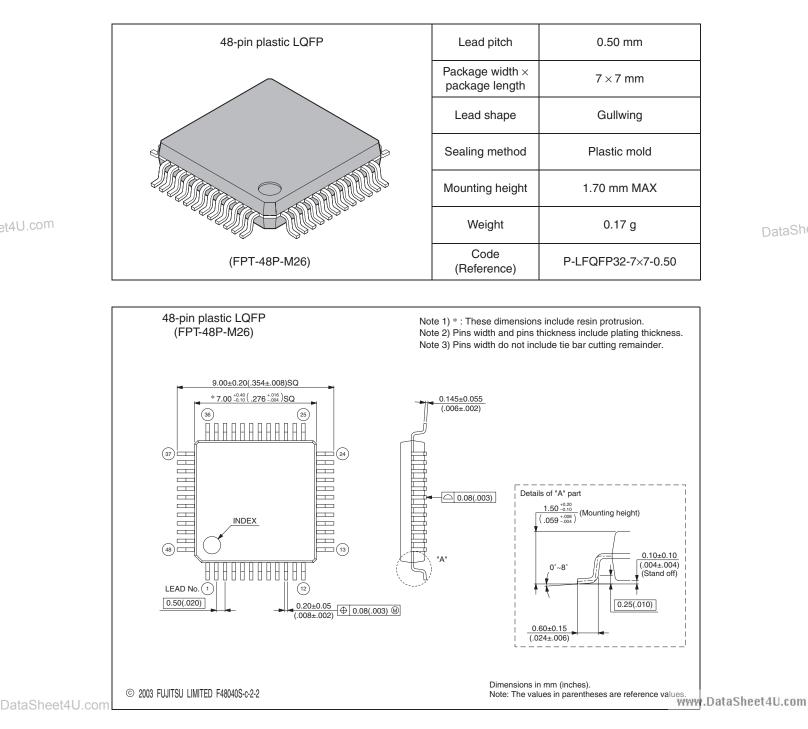

#### **Package Dimension** 1.5

The MB90385 series is available in one type of package.

The package dimensions below are for reference only. Contact Fujitsu for the nominal package dimensions.

## Package Dimension of FPT-48P-M26

## **1.6 Pin Description**

This section describes the I/O pins and their functions of the MB90385 series.

## Pin Description

## Table 1.6-1 Pin Description (1/3)

| Pin Name Type Functi<br>AV <sub>CC</sub> V <sub>CC</sub> power input pin for A/D co<br>Power (Vref+) input pin for A/D |                               |

|------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| Power (Vref⊥) input pin for ∆/                                                                                         | nverter                       |

| Power (Vref+) input pin for A/D                                                                                        |                               |

| AVR                                                                                                                    | converter. The power<br>eding |

| P50 to P57 General-purpose I/O port                                                                                    |                               |

| 10     E     Analog input pin for A/D convert the analog input is set to "enable"                                      |                               |

| P37 General-purpose I/O port.                                                                                          | Data                          |

| ADTG DataShe External trigger input pin for A/I be set to "input port".                                                | D converter. This pin should  |

| P20 General-purpose I/O port.                                                                                          |                               |

| D Event input pin for reload timer "input port."                                                                       | 0. This pin should be set to  |

| P21 General-purpose I/O port.                                                                                          |                               |

| TOT0 D Event output pin for reload times when the output setting is "enabled"                                          |                               |

| P22 General-purpose I/O port.                                                                                          |                               |

| TIN1 D Event input pin for reload timer "input port."                                                                  | 1. This pin should be set to  |

| P23 General-purpose I/O port.                                                                                          |                               |

| TOT1 D Event output pin for reload times when the output setting is "enable                                            |                               |

| P24 to P27 General-purpose I/O port.                                                                                   |                               |

| D External interrupt input pins. Th "input port."                                                                      | ese pins should be set to     |

| MD2 F Input pin for selecting operation                                                                                | mode                          |

| MD1 C Input pin for selecting operation                                                                                | mode                          |

| 2 MD0 C Input pin for selecting operation                                                                              | mode www.DataSheet4U.         |

et4U.com

DataSheet4U.com

| Pin No.  | Pin Name Circuit |         | Function                                                                                                                       |

|----------|------------------|---------|--------------------------------------------------------------------------------------------------------------------------------|

| M26      | FIIINAINE        | Туре    | Function                                                                                                                       |

| 23       | RST              | В       | Input pin for external reset                                                                                                   |

| 24       | V <sub>CC</sub>  |         | Power (5 V) input pin.                                                                                                         |

| 25       | V <sub>SS</sub>  |         | Power (0 V) input pin                                                                                                          |

| 26       | С                |         | Capacity pin for stabilizing power supply. This pin should be connected to a ceramic capacitor of approx. 0.1µF.               |

| 27       | X0               | А       | High-speed oscillation pin                                                                                                     |

| 28       | X1               | А       | High-speed oscillation pin                                                                                                     |

|          | P10 to P13       | D       | General-purpose I/O ports.                                                                                                     |

| 29 to 32 | IN0 to IN3       |         | Trigger input pins for input capture channels 0 to 3. These pins should be set to "input port".                                |

|          | P14 to P17       | G       | General-purpose I/O ports. High current output port.                                                                           |

| 33 to 36 | PPG0 to PPG3     |         | Output pins for PPG timers 01 and 23. These pins are enabled when the output setting is "enabled."                             |

| 37       | P40              | DataShe | General-purpose I/O port                                                                                                       |

|          | SIN1             |         | Serial data input pin for UART1. This pin should be set to "input port."                                                       |

|          | P41              | D       | General-purpose I/O port.                                                                                                      |

| 38       | SCK1             |         | Serial clock I/O pin for UART1. This pin is enabled only<br>when the serial clock I/O setting of the UART1 is "enabled."       |

|          | P42              | D       | General-purpose I/O port.                                                                                                      |

| 39       | SOT1             |         | Serial data output pin for UART1. This pin functions only<br>when the serial data output setting of the UART1 is<br>"enabled". |

|          | P43              | D       | General-purpose I/O port.                                                                                                      |

| 40       | ТХ               |         | CAN transmission output pin. This pin is enabled only when<br>the output setting is "enabled".                                 |

| 41       | P44              | D       | General-purpose I/O port.                                                                                                      |

|          | RX               |         | CAN reception input pin. This pin should be set to "input port."                                                               |

| 42 to 45 | P30 to P33       | D       | General-purpose I/O port.                                                                                                      |

| 46       | X0A*             | А       | Low-speed oscillation pin.                                                                                                     |

|          | P35*             | D       | General-purpose I/O port.                                                                                                      |

## Table 1.6-1 Pin Description (2/3)

et4U.com

DataSheet4U.com

www.DataSheet4U.com

#### Table 1.6-1 Pin Description (3/3)

| Pin No. | - Pin Name       | Circuit<br>Type | Function                                          |

|---------|------------------|-----------------|---------------------------------------------------|

| M26     |                  |                 |                                                   |

| 47      | X1A*             | А               | Low-speed oscillation pin.                        |

|         | P36*             | D               | General-purpose I/O port.                         |

| 48      | AV <sub>SS</sub> |                 | V <sub>SS</sub> power input pin for A/D converter |

\*: MB90387, MB90F387 : X1A, X0A MB90387S, MB90F387S : P36, P35

et4U.com

DataShe

DataSheet4U.com

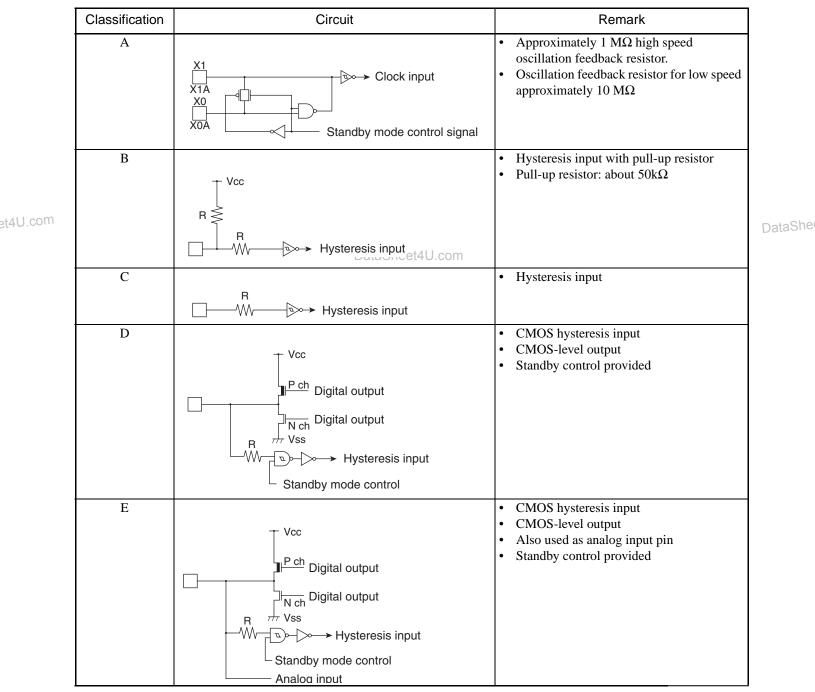

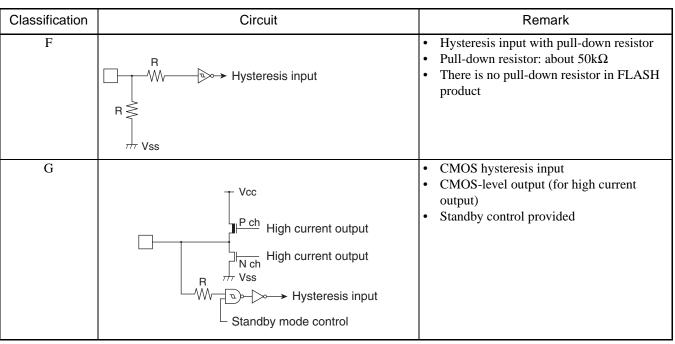

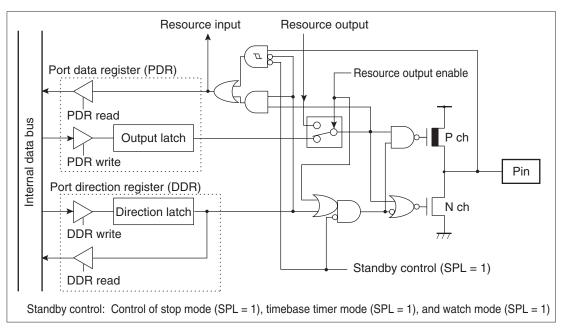

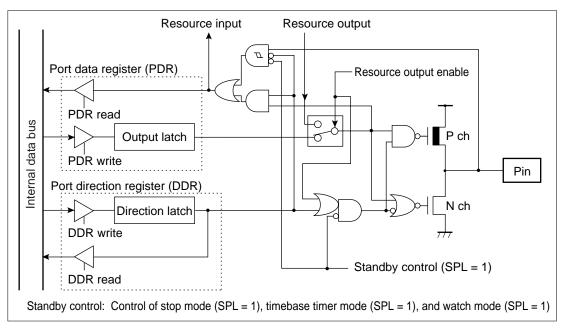

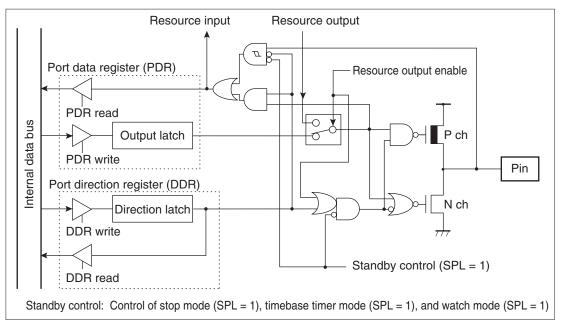

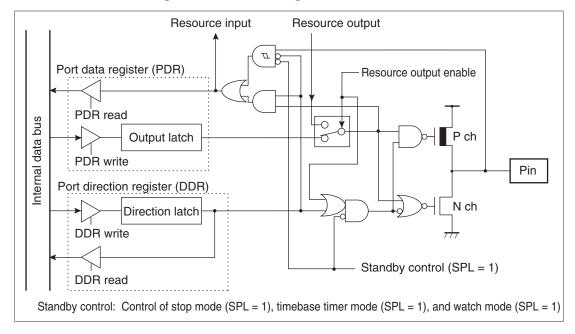

## 1.7 I/O Circuit

## I/O circuit of the MB90385 series is shown in the figure below.

## ■ I/O Circuit

## Table 1.7-1 I/O Circuit (1/2)

DataSheet4U.com

### Table 1.7-1 I/O Circuit (2/2)

et4U.com

DataSheet4U.com

DataSheet4U.com

et4U.com

DataSheet4U.com

DataSheet4U.com

DataSheet4U.com

DataShe

# CHAPTER 2 HANDLING DEVICES

This chapter describes the precautions when handling general-purpose one chip microcontroller.

2.1 Precautions when Handling Devices

et4U.com

DataSheet4U.com

DataSheet4U.com

## 2.1 Precautions when Handling Devices

## This section describes the precautions against the power supply voltage of the device and processing of pin.

## Precautions when Handling Devices

- Voltage not exceeding maximum ratings (preventing latch-up)

- For a CMOS IC, latch-up may occur when a voltage higher than V<sub>CC</sub> or a voltage lower than V<sub>SS</sub> is impressed to the I/O pin other than medium-/high-voltage withstand I/O pins, or when a voltage that exceeds the rated voltage is impressed between V<sub>CC</sub> and V<sub>SS</sub>.

- Latch-up may cause a sudden increase in power supply current, resulting in thermal damage to the device. Therefore, the maximum voltage ratings must not be exceeded.

- When turning the analog power supply on and off, the analog power supply voltage (AV<sub>CC</sub> and AVR) and the analog input voltage should not exceed the digital power supply voltage (V<sub>CC</sub>).

- Handling not-used pins

- If unused input pins remain open, a malfunction or latch-up may cause permanent damage, so take countermeasures such as pull-up or pull-down using a 2 k $\Omega$  or larger resistor.

DataShe

www.DataSheet4U.com

Leave unused input pins open in the output state or, if left in the input state, treat them in the same manner as for input pins in use.

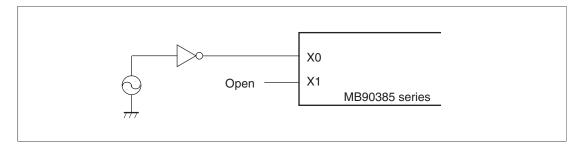

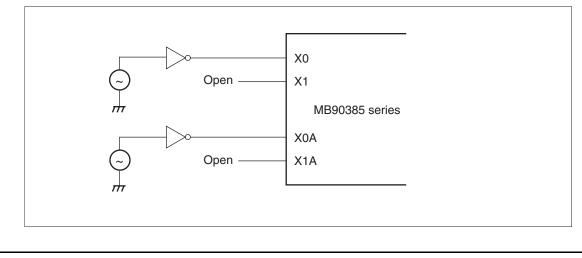

Precautions of using external clock

When an external clock is used, drive only the X0 pin and open the X1 pin. Figure 2.1-1 shows an use example of external clock.

#### Figure 2.1-1 Example of Using External Clock

#### Precautions of non-use of subclock

If an oscillator is not connected to the X0A and X1A pins, connect the X0A pin to Pull-down and leave the X1A pin open.

DataSheet4U.com

et4U.com

18

Precautions during operation of PLL clock mode

If the PLL clock mode is selected, the microcontroller attempt to be working with the self-oscillating circuit even when there is no external oscillator or external clock input is stopped. Performance of this operation, however, cannot be guaranteed.

- Power pins

- When plural  $V_{CC}$  pins and  $V_{SS}$  pins are provided, pins designed to be at the same electric potential are internally connected to the device to prevent malfunctions such as latch-up. However, always connect all same electric potential pins to power supply and ground outside the device to prevent decrease of unnecessary radiation, the malfunction of the strobe signal due to a rise of ground level, and follow the standards of total output current.

- The power pins should be connected to V<sub>CC</sub> and V<sub>SS</sub> of the MB90385 series device at the lowest possible impedance from the current supply source.

- It is best to connect approximately 0.1µF capacitor between V<sub>CC</sub> and V<sub>SS</sub> as a bypass capacitor near the pins of the MB90385 series device.

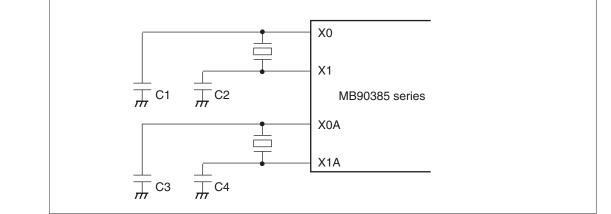

- Crystal oscillator circuit

- Noise near the X0 and X1 pins may cause the MB90385 series to malfunction. Design the PC board so that the X0 and X1 pins, the crystal (or ceramic) oscillator, and the bypass capacitor to ground are as close as possible to each other, and so the wiring of the X0 and X1 pins and other wiring do not cross.

- For stable operation, the PC board is recommended to have the artwork with the X0 and X1 pins enclosed by a ground line.

DataShe

- Procedure of A/D converter/analog input power-on

- Always apply a power to the A/D converter power and the analog input (AN0 to AN7 pins) after or concurrently with the digital power (V<sub>CC</sub>)-on.

- Always turn off the A/D converter power and the analog input before or concurrently with the digital power-down.

- Note that AVR should not exceed AV<sub>CC</sub> at turn on or off. (The analog power and digital power can be simultaneously turned on or off with no problem.)

- Handling pins when not using A/D converter

When not using the A/D converter, the pins should be connected so that  $AV_{CC} = AVR = V_{CC}$  and  $AV_{SS} = V_{SS}$ .

Precautions at power on

To prevent a malfunction of the internal step-down circuit, the voltage rise time at power-on should be  $50 \ \mu s$  or more (between 0.2 V and 2.7 V).

DataSheet4U.com

et4U.com

#### CHAPTER 2 HANDLING DEVICES

#### Stabilization of supply voltage

If the power supply voltage varies acutely even within the operation assurance range of the  $V_{CC}$  power supply voltage, a malfunction may occur. The  $V_{CC}$  power supply voltage must therefore be stabilized.

As stabilization guidelines, stabilize the power supply voltage so that  $V_{CC}$  ripple fluctuations (peak to peak value) in the commercial frequencies (50 Hz to 60 Hz) fall within 10% of the standard  $V_{CC}$  power supply voltage and the transient fluctuation rate becomes 0.1V/ms or less in instantaneous fluctuation for power supply switching.

et4U.com

DataSheet4U.com

DataSheet4U.com

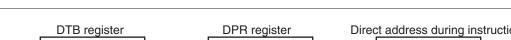

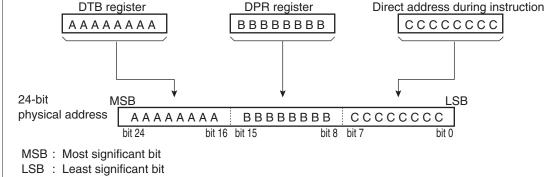

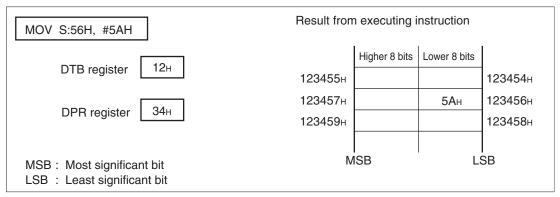

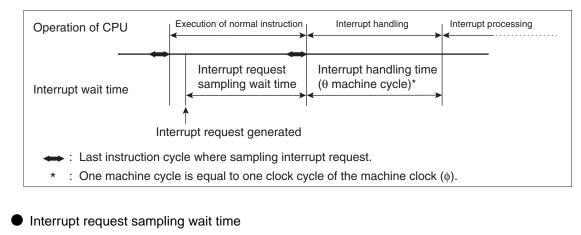

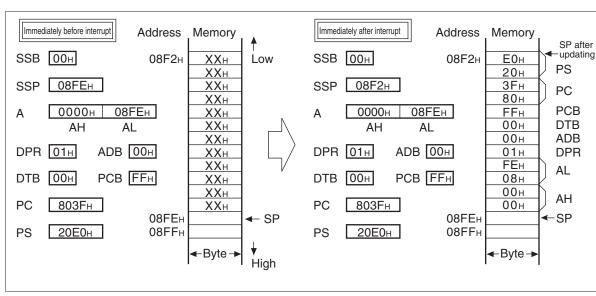

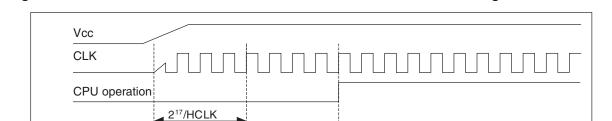

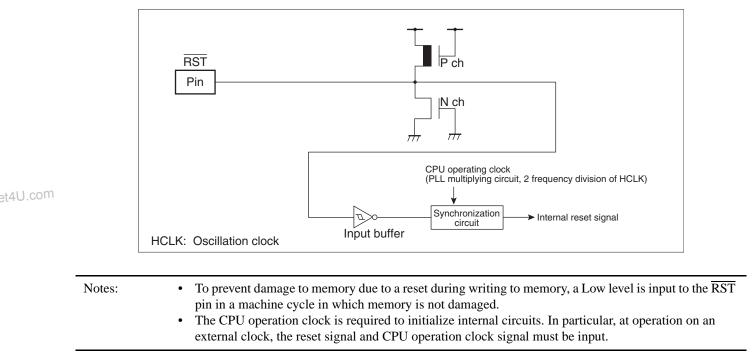

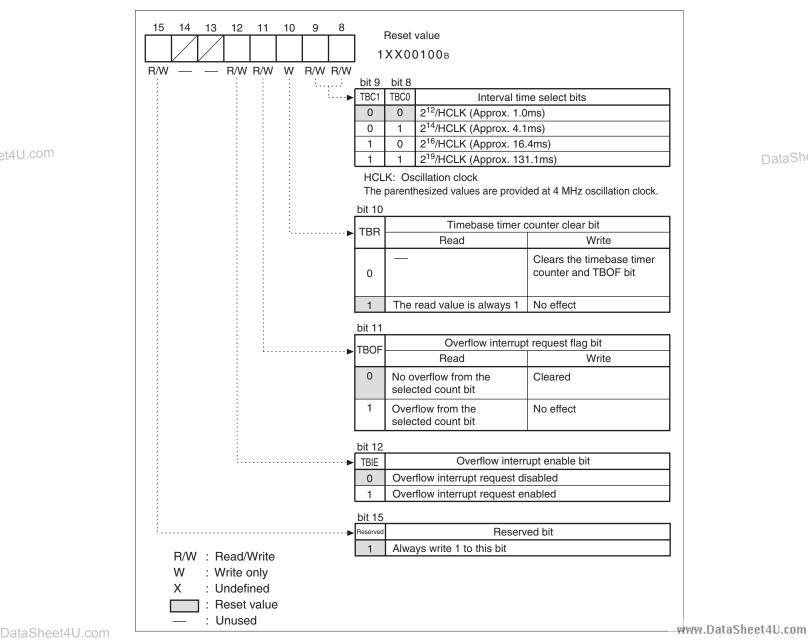

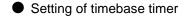

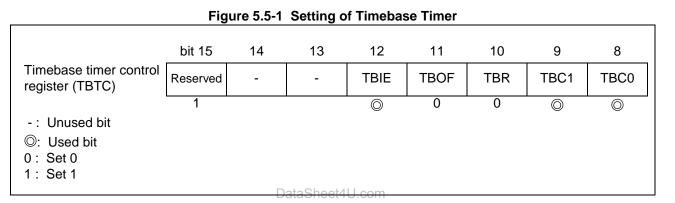

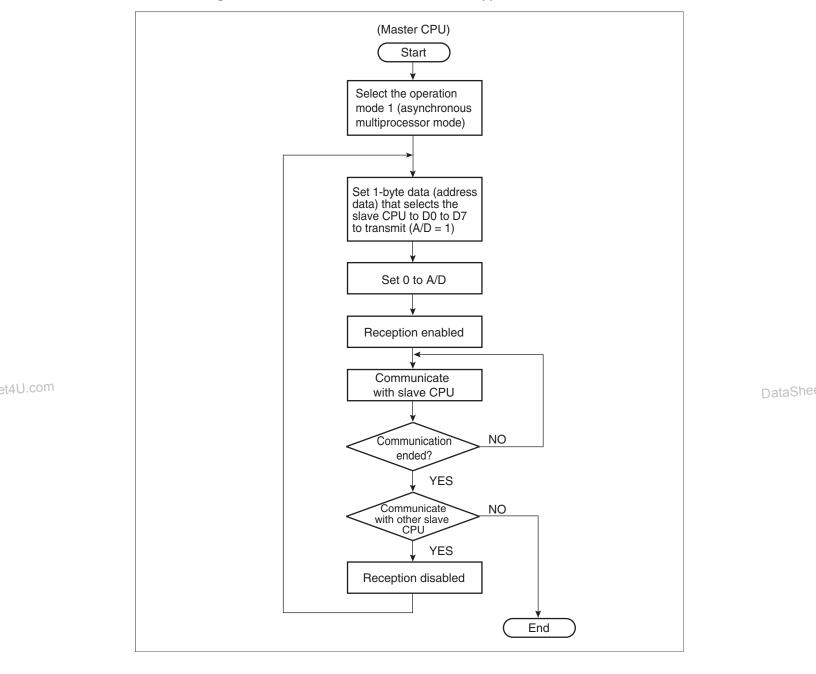

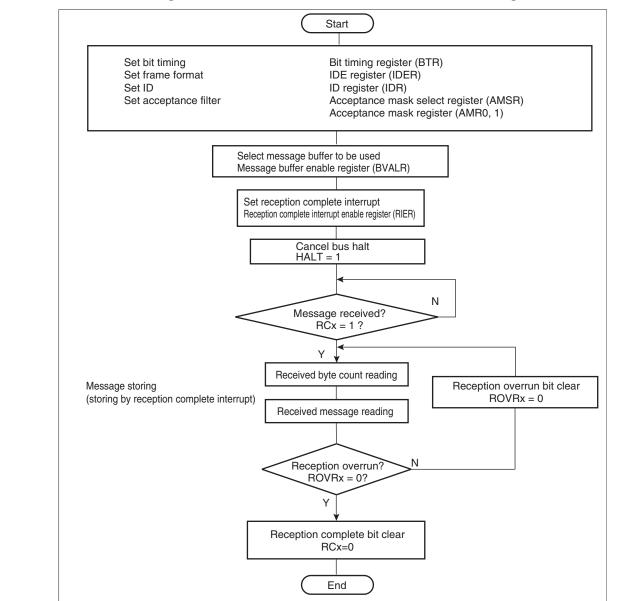

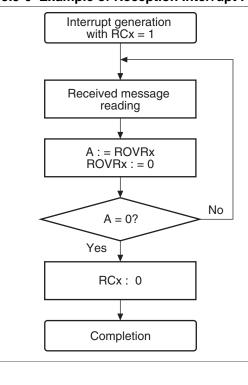

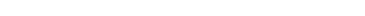

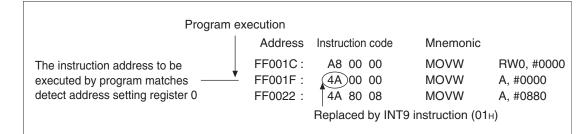

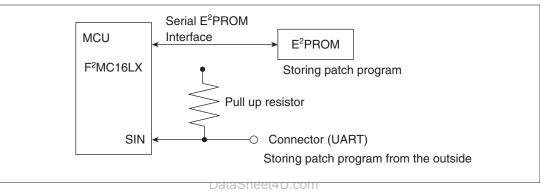

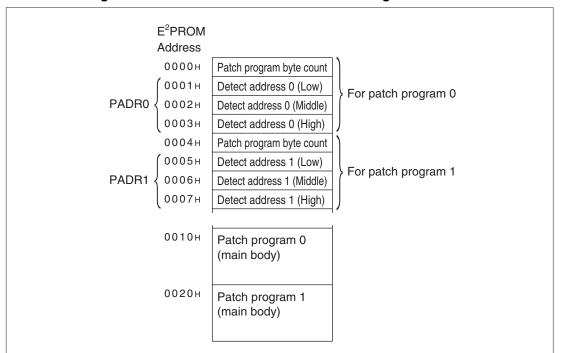

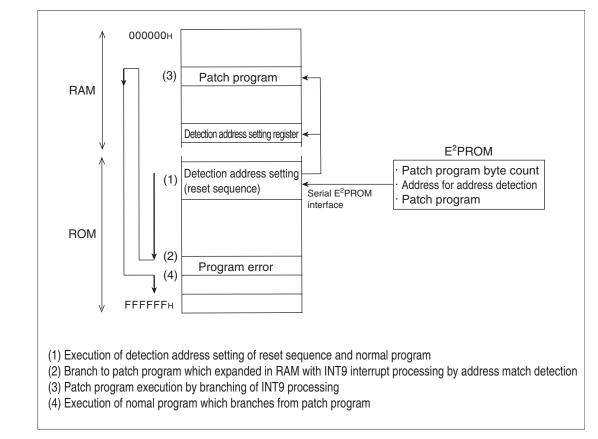

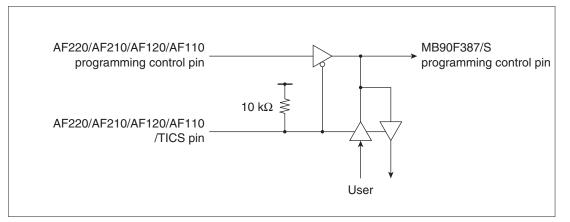

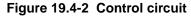

www.DataSheet4U.com