## 16-bit Microcontroller

**CMOS**

# F<sup>2</sup>MC-16LX MB90960 Series

# MB90F962(S)/V340E-101/V340E-102

#### **■ DESCRIPTION**

The MB90960-series is a 16-bit general-purpose microcontroller. Fujitsu now offers on-chip Flash-ROM program memory up to 64 Kbytes.

The power supply (3 V) is supplied to the internal MCU core from an internal regulator circuit. This creates a major advantage in terms of EMI and power consumption.

The unit features a 4 channel input capture unit, 1 channel 16-bit free-run timer, 2-channel LIN-UART, and 16-channel 8/10-bit A/D converter as the peripheral resource.

Note: F2MC is the abbreviation of FUJITSU Flexible Microcontroller.

#### **■ FEATURES**

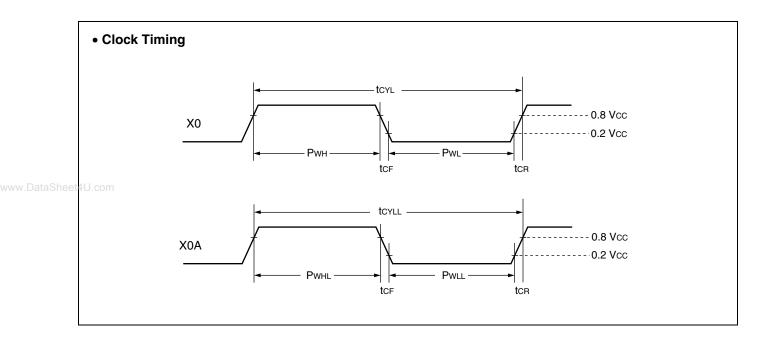

#### Clock

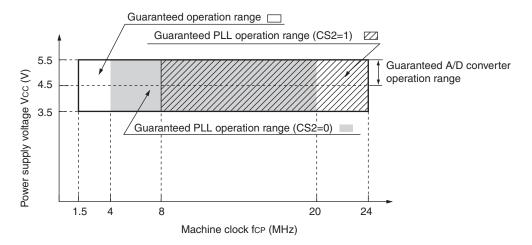

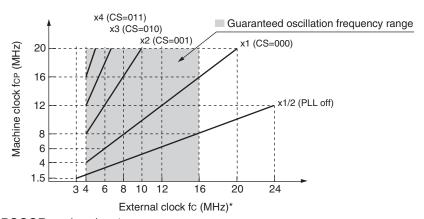

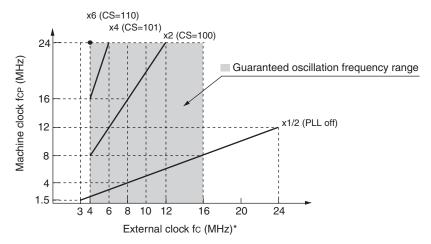

- Built-in PLL clock frequency multiplying circuit

- Machine clock (PLL clock) selectable from frequency division by 2 of oscillation clock or 1 to 6-multiplied oscillation clock (4 MHz to 24 MHz when oscillation clock is 4 MHz).

- Sub clock operation: Up to 50 kHz (devices without S-suffix only)

- Minimum instruction execution time: 42 ns (4 MHz oscillation clock and 6-multiplied PLL clock).

(Continued)

Be sure to refer to the "Check Sheet" for the latest cautions on development.

"Check Sheet" is seen at the following support page

URL: http://www.fujitsu.com/global/services/microelectronics/product/micom/support/index.html

"Check Sheet" lists the minimal requirement items to be checked to prevent problems beforehand in system development.

#### • Instruction system optimized controllers

- 16 Mbytes CPU memory space : Internal 24-bit addressing

- Various data types (bit, byte, word, and long word)

- Various addressing modes (23 types)

- Enhanced signed instructions of multiplication/division and RETI

- Enhanced high-accuracy operations by 32-bit accumulator

#### • Instruction system for high-level language (C language) / multitask

- · System stack pointer

- Enhanced pointer indirect instructions

- www.DataSheet4U.comBarrel shift instructions

#### Higher execution speed

• 4-byte instruction queue

#### Powerful interrupt function

- Powerful interrupt function with 8 levels and 34 factors

- Corresponds to 8-channel external interrupt

#### • CPU-independent automatic data transfer function

• Expanded intelligent I/O service function (El2OS) : Maximum 16 channels

#### • Low-power consumption mode

· Clock mode

PLL clock mode (a PLL clock that is a multiple of the oscillation clock is used to operate the CPU and peripheral functions.)

Main clock mode (the main clock, with the oscillation clock frequency divided by 2 is used to operate the CPU and peripheral functions.)

Sub clock mode (the sub clock is used to operate the CPU and peripheral functions.)

Standby mode

Sleep mode (stops the operation clock to the CPU.)

Watch mode (operates the sub clock and watch timer only.)

Time-base timer mode (operates the oscillation clock, sub clock, time-base timer and watch timer only.)

Stop mode (stops the operates the oscillation clock and sub clock.)

• CPU intermittent operation mode

#### • I/O port

- General-purpose input/output ports (CMOS output)

- 34 ports (products without S-suffix)

- 36 ports (products with S-suffix)

#### Sub clock pin (X0A, X1A)

- Yes: (external oscillator used), products without S-suffix

- No : products with S-suffix

#### Timer

- Time-base timer, watch timer (products without S-suffix), watchdog timer: 1 channel

- 8/16-bit PPG timer : 8-bit × 4 channels or 16-bit × 2 channels

- 16-bit reload timer: 2 channels

- 16- bit input/output timer

- 16-bit free-run timer : 1 channel

- 16- bit input capture (ICU) : 4 channels

(Continued)

#### (Continued)

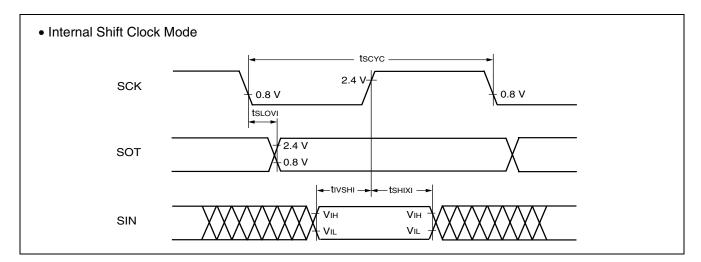

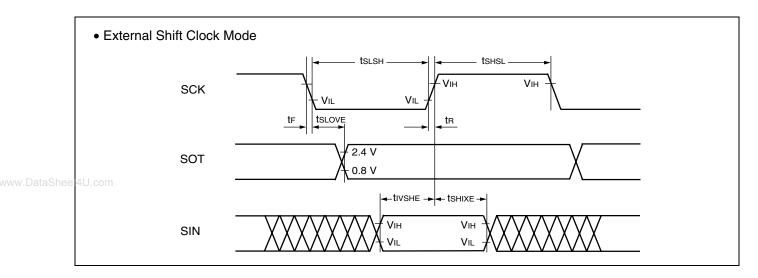

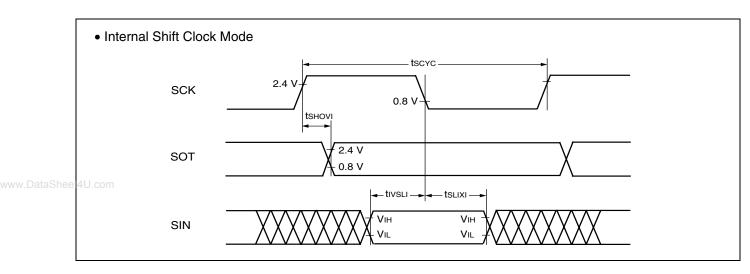

#### • LIN-UART (LIN/SCI) : Maximum 2 channels

- Full-duplex double buffer

- Clock-asynchronous or clock-synchronous serial transfer

#### • DTP/External interrupt : 8 channels

• Module for activation of expanded intelligent I/O service (El<sup>2</sup>OS) and generation of external interrupt by external input.

#### • Delayed interrupt generator module

· Generates interrupt request for task switching.

#### www.DataSheet 8/10-bit A/D converter : 16 channels

- 8-bit and 10-bit resolution.

- Start by external trigger input.

- Conversion time: 3 µs (frequency, including sampling time at 24 MHz machine clock)

#### Program patch function

Detects address match for 6 address pointers.

#### • Changeable port input voltage level

• Automotive input level/CMOS Schmitt input level (initial value in single-chip mode is Automotive level).

### **■ PRODUCT LINEUP**

| Part number Parameter       | MB90F962                                                                                                                                                                                                          | MB90F962S                                                                                                                                                                                      | MB90V340E-101                                         | MB90V340E-102                                            |  |  |  |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------|--|--|--|

| Туре                        | Flash mem                                                                                                                                                                                                         | ory product                                                                                                                                                                                    | Evaluation product                                    |                                                          |  |  |  |

| CPU                         |                                                                                                                                                                                                                   | F <sup>2</sup> MC-16                                                                                                                                                                           | SLX CPU                                               |                                                          |  |  |  |

| System clock                |                                                                                                                                                                                                                   | PLL clock multiplier ( $\times$ 1, $\times$ 2, $\times$ 3, $\times$ 4, $\times$ 6, 1/2 when PLL stops)<br>Minimum instruction execution time : 42 ns (4 MHz oscillation clock, PLL $\times$ 6) |                                                       |                                                          |  |  |  |

| ROM                         | Flash memory<br>64 Kbytes (60 Kbytes                                                                                                                                                                              | + 4 Kbytes Sectors)                                                                                                                                                                            | Exte                                                  | ernal                                                    |  |  |  |

| RAM capacitance             | 3 Kb                                                                                                                                                                                                              | oytes                                                                                                                                                                                          | 30 K                                                  | bytes                                                    |  |  |  |

| Power supply for emulator*1 | _                                                                                                                                                                                                                 | _                                                                                                                                                                                              | Y                                                     | es                                                       |  |  |  |

| Sub clock pin<br>(X0A, X1A) | Yes                                                                                                                                                                                                               | N                                                                                                                                                                                              | 0                                                     | Yes                                                      |  |  |  |

| Operating voltage range     | 3.5 V to 5.5 V : at normal operation (not using A/D converter and not doing flash programming) 4.0 V to 5.5 V : at normal operation                                                                               |                                                                                                                                                                                                | 5 V ± 10%                                             |                                                          |  |  |  |

| Operating temperature range | – 40 °C to + 125°C *2                                                                                                                                                                                             |                                                                                                                                                                                                | _                                                     |                                                          |  |  |  |

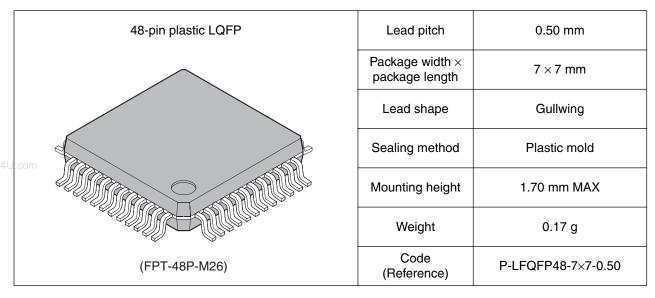

| Package                     | LQFP-48P                                                                                                                                                                                                          |                                                                                                                                                                                                | PGA-299C                                              |                                                          |  |  |  |

|                             | 2 channels                                                                                                                                                                                                        |                                                                                                                                                                                                | 5 channels                                            |                                                          |  |  |  |

| LIN-UART                    | Wide range of baud rate settings using a dedicated reload timer Special synchronous options for adapting to different synchronous serial protocols LIN functionality working either as master or slave LIN device |                                                                                                                                                                                                |                                                       |                                                          |  |  |  |

| 8/10-bit                    | 16 cha                                                                                                                                                                                                            | annels                                                                                                                                                                                         | 24 channels                                           |                                                          |  |  |  |

| A/D Converter               | 10-bit or 8-bit resolution<br>Conversion time: Min. 3 µs includes sample time (per one channel)                                                                                                                   |                                                                                                                                                                                                |                                                       |                                                          |  |  |  |

|                             | 2 cha                                                                                                                                                                                                             | innels                                                                                                                                                                                         | 4 channels                                            |                                                          |  |  |  |

| 16-bit Reload Timer         | Operation clock freque Supports External Ev                                                                                                                                                                       |                                                                                                                                                                                                | , fsys/2 <sup>5</sup> (fsys = Machine clock frequency |                                                          |  |  |  |

|                             | 1 cha                                                                                                                                                                                                             | annel                                                                                                                                                                                          | 4 cha                                                 | nnels                                                    |  |  |  |

| 16-bit I/O Timer            | Signals an interrupt v<br>Operating clock frequ<br>(fsys = Machine clock                                                                                                                                          | uency: fsys/21, fsys/22,                                                                                                                                                                       | fsys/2³, fsys/2⁴, fsys/2                              | <sup>5</sup> , fsys/2 <sup>6</sup> , fsys/2 <sup>7</sup> |  |  |  |

|                             | 4 cha                                                                                                                                                                                                             | innels                                                                                                                                                                                         | 6 channels                                            |                                                          |  |  |  |

| 16-bit Input Capture        | Maintains I/O timer va<br>and generates interru                                                                                                                                                                   | alue by pin input (rising                                                                                                                                                                      | g edge, falling edge, o                               | r both edge),                                            |  |  |  |

(Continued)

### (Continued)

| Part number                      | MB90F962                                                                                                                                                                                                                                                                                           | MB90F962S                                                                         | MB90V340E-101                                                                                                              | MB90V340E-102   |  |  |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|

| Parameter                        | 1112001 002                                                                                                                                                                                                                                                                                        | MB001 0020                                                                        | 11120070102 101                                                                                                            | 11120010102 102 |  |  |

| 8/16-bit<br>PPG timer            | 8-bit reload<br>8-bit reload<br>"L" pulse<br>8-bit reload<br>"H" pulse<br>Supports 8-bit and                                                                                                                                                                                                       | / 4 channels (8-bit) counters × 4 registers for width × 4 registers for width × 4 | 8-bit reload counters × 16 8-bit reload registers for "L" pulse width × 16 8-bit reload registers for "H" pulse width × 16 |                 |  |  |

|                                  | A pair of 8-bit reload counters can be configured as one 16-bit reload counter or as 8-bit prescaler + 8-bit reload counter.  Operating clock frequency: fsys, fsys/2¹, fsys/2², fsys/2³, fsys/2⁴, or 128 μs  @ fosc = 4 MHz  (fsys = Machine clock frequency, fosc = Oscillation clock frequency) |                                                                                   |                                                                                                                            |                 |  |  |

|                                  | 8 channels                                                                                                                                                                                                                                                                                         |                                                                                   |                                                                                                                            |                 |  |  |

| External Interrupts              | Can be used rising edge, falling edge, starting up by "H"/"L" level input, external input, extended intelligent I/O services (El <sup>2</sup> OS) and DMA.                                                                                                                                         |                                                                                   |                                                                                                                            |                 |  |  |

| Corresponding evaluation product | MB90V340E-102                                                                                                                                                                                                                                                                                      | MB90V340E-101                                                                     | _                                                                                                                          | _               |  |  |

<sup>\*1 :</sup> It is setting of Jumper switch (TOOL Vcc) when emulator (MB2147-01) is used. Please refer to the Emulator hardware manual for the details.

$<sup>^*2</sup>$ : If used exceeding  $T_A = +105^{\circ}C$ , be sure to contact Fujitsu for reliability limitations.

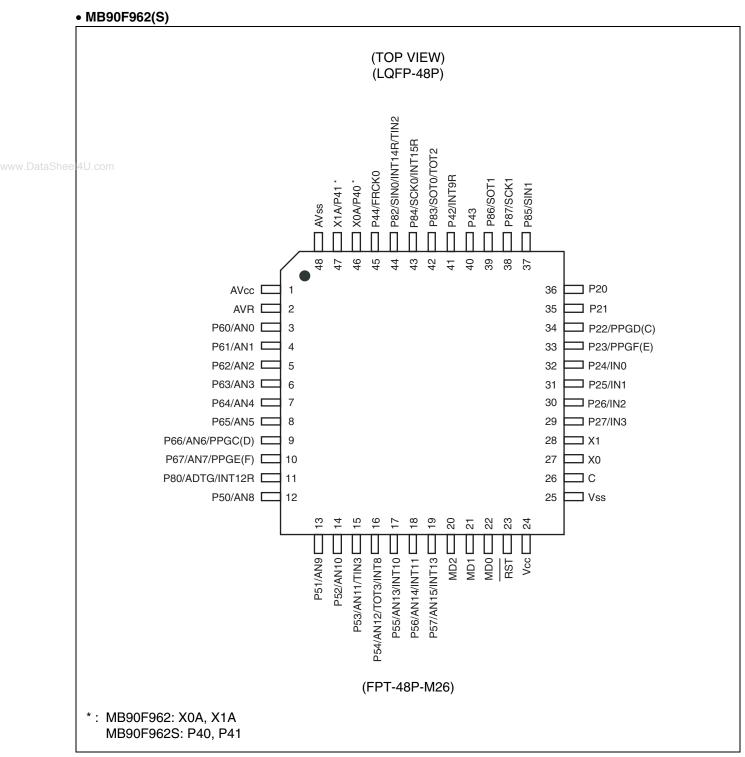

#### **■ PIN ASSIGNMENT**

### **■ PIN DESCRIPTION**

| ataShee <mark>⊯∪</mark> | 1 2 3 to 8 5 to 10 9, 10 | AVcc AVR P60 to P65 AN0 to AN5 P66, P67 | Circuit type  I  H | Function  Vcc power input pin for analog circuit.  Power (Vref+) input pin for A/D converter.  AVR should not exceed Vcc.           |

|-------------------------|--------------------------|-----------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| ataSheel <del>4U</del>  | 2<br>3 to 8              | AVR P60 to P65 AN0 to AN5               | _                  | Power (Vref+) input pin for A/D converter.  AVR should not exceed Vcc.                                                              |

| ataSheel <del>मU</del>  | 3 to 8                   | P60 to P65<br>AN0 to AN5                | Н                  | AVR should not exceed Vcc.                                                                                                          |

| ataShee <del>l≠∪</del>  | J.com                    | AN0 to AN5                              | Н                  |                                                                                                                                     |

| ataSheel <del>4∪</del>  | J.com                    |                                         | П                  | General-purpose I/O ports.                                                                                                          |

| ataShee <del>l4U</del>  |                          | P66, P67                                |                    | Analog input pins for A/D converter.                                                                                                |

|                         | 9, 10                    |                                         |                    | General-purpose I/O ports.                                                                                                          |

|                         | 0, 10                    | AN6, AN7                                | Н                  | Analog input pins for A/D converter.                                                                                                |

|                         |                          | PPGC (D) ,<br>PPGE (F)                  |                    | Output pins for PPG.                                                                                                                |

|                         |                          | P80                                     |                    | General-purpose I/O port.                                                                                                           |

|                         | 11                       | ADTG                                    | F                  | Trigger input pin for A/D converter.                                                                                                |

|                         |                          | INT12R                                  |                    | External interrupt request input pin for INT12R.                                                                                    |

|                         | 12 to 14                 | P50 to P52                              | Н                  | General-purpose I/O ports (I/O circuit type of P50 is different from that of MB90V340E) .                                           |

|                         |                          | AN8 to AN10                             |                    | Analog input pins for A/D converter.                                                                                                |

|                         |                          | P53                                     | Н                  | General-purpose I/O port.                                                                                                           |

|                         | 15                       | AN11                                    |                    | Analog input pin for A/D converter.                                                                                                 |

|                         |                          | TIN3                                    |                    | Event input pin for reload timer 3.                                                                                                 |

|                         |                          | P54                                     |                    | General-purpose I/O port.                                                                                                           |

|                         | 16                       | AN12                                    | Н                  | Analog input pin for A/D converter.                                                                                                 |

|                         | 10                       | ТОТ3                                    | П                  | Output pin for reload timer 3.                                                                                                      |

|                         |                          | INT8                                    |                    | External interrupt request input pin for INT8.                                                                                      |

|                         |                          | P55 to P57                              |                    | General-purpose I/O ports.                                                                                                          |

|                         | 17 to 19                 | AN13 to AN15                            | Н                  | Analog input pins for A/D converter.                                                                                                |

|                         |                          | INT10, INT11,<br>INT13                  |                    | External interrupt request input pins for INT10, INT11, INT13.                                                                      |

|                         | 20                       | MD2                                     | D                  | Input pin for selecting operation mode.                                                                                             |

|                         | 21, 22                   | MD1, MD0                                | С                  | Input pins for selecting operation mode.                                                                                            |

|                         | 23                       | RST                                     | E                  | Reset input.                                                                                                                        |

|                         | 24                       | Vcc                                     | _                  | Power input pin (3.5 V to 5.5 V) .                                                                                                  |

|                         | 25                       | Vss                                     | _                  | Power input pin (0 V) .                                                                                                             |

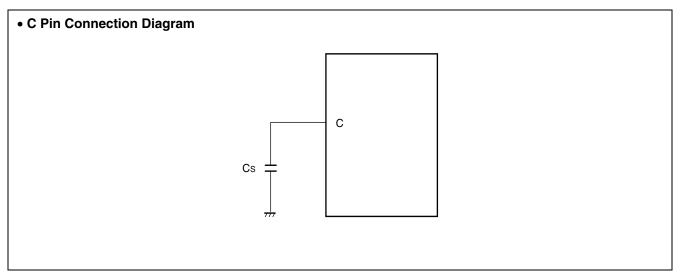

|                         | 26                       | С                                       | ı                  | Capacity pin for stabilizing power supply. It should be connected to a higher than or equal to 0.1 $\mu\text{F}$ ceramic capacitor. |

|                         | 27                       | X0                                      | ٨                  | Oscillation input pin.                                                                                                              |

|                         | 28                       | X1                                      | Α                  | Oscillation output pin.                                                                                                             |

(Continued)

| Pin No.             |                        |              |                                                                                                                                                 |  |  |  |

|---------------------|------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| LQFP-48P*           | Pin name               | Circuit type | Function                                                                                                                                        |  |  |  |

| 29 to 32            | P27 to P24             | G            | General-purpose I/O ports. The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.   |  |  |  |

|                     | IN3 to IN0             |              | Event input pins for input capture 0 to 3.                                                                                                      |  |  |  |

| 4U.cc <b>33, 34</b> | P23, P22               | G            | General-purpose I/O ports.  The register can be set to select whether to use a pull-up resistor.  This function is enabled in single-chip mode. |  |  |  |

|                     | PPGF (E) ,<br>PPGD (C) |              | Output pins for PPG.                                                                                                                            |  |  |  |

| 35, 36              | P21, P20               | G            | General-purpose I/O ports.  The register can be set to select whether to use a pull-up resistor.  This function is enabled in single-chip mode. |  |  |  |

| 37                  | P85                    | К            | General-purpose I/O port.                                                                                                                       |  |  |  |

| 37                  | SIN1                   |              | Serial data input pin for LIN-UART1.                                                                                                            |  |  |  |

| 38                  | P87                    | F            | General-purpose I/O port.                                                                                                                       |  |  |  |

| 36                  | SCK1                   | 1            | Clock I/O pin for LIN-UART1.                                                                                                                    |  |  |  |

| 39                  | P86                    | F            | General-purpose I/O port.                                                                                                                       |  |  |  |

| 39                  | SOT1                   | Ī            | Serial data output pin for LIN-UART1.                                                                                                           |  |  |  |

| 40                  | P43                    | F            | General-purpose I/O port.                                                                                                                       |  |  |  |

| 41                  | P42                    | F            | General-purpose I/O port.                                                                                                                       |  |  |  |

| 41                  | INT9R                  | <u>Г</u>     | External interrupt request input pin for INT9R.                                                                                                 |  |  |  |

|                     | P83                    |              | General-purpose I/O port.                                                                                                                       |  |  |  |

| 42                  | SOT0                   | F            | Serial data output pin for LIN-UART0.                                                                                                           |  |  |  |

|                     | TOT2                   |              | Output pin for reload timer 2                                                                                                                   |  |  |  |

|                     | P84                    |              | General-purpose I/O port.                                                                                                                       |  |  |  |

| 43                  | SCK0                   | F            | Clock I/O pin for LIN-UART0.                                                                                                                    |  |  |  |

|                     | INT15R                 |              | External interrupt request input pin for INT15R.                                                                                                |  |  |  |

|                     | P82                    |              | General-purpose I/O port.                                                                                                                       |  |  |  |

| 4.4                 | SIN0                   | V            | Serial data input pin for LIN-UART0.                                                                                                            |  |  |  |

| 44                  | INT14R                 | K            | External interrupt request input pin for INT14R.                                                                                                |  |  |  |

|                     | TIN2                   |              | Event input pin for reload timer 2.                                                                                                             |  |  |  |

| 45                  | P44                    | F            | General-purpose I/O port (I/O circuit type of P44 is different from that of MB90V340E) .                                                        |  |  |  |

|                     | FRCK0                  |              | Free-run timer 0 clock input pin.                                                                                                               |  |  |  |

(Continued)

#### (Continued)

|       | Pin No.          | Pin name     | Circuit type | Function                                                                                                                               |  |

|-------|------------------|--------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------|--|

|       |                  | Pili lialile | Circuit type | i dilction                                                                                                                             |  |

| •     |                  | P40, P41     | F            | General-purpose I/O ports.<br>(products with S-suffix and MB90V340E-101)                                                               |  |

|       | 46, 47           | X0A, X1A     | В            | X0A: Oscillation input pin for sub clock<br>X1A: Oscillation output pin for sub clock<br>(products without S-suffix and MB90V340E-102) |  |

| 3Shee | 4U.com <b>48</b> | AVss         | I            | Vss power input pin for analog circuit.                                                                                                |  |

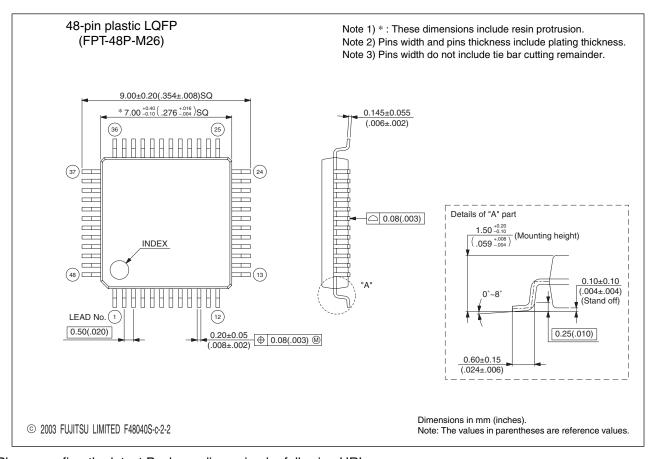

\*: FPT-48P-M26

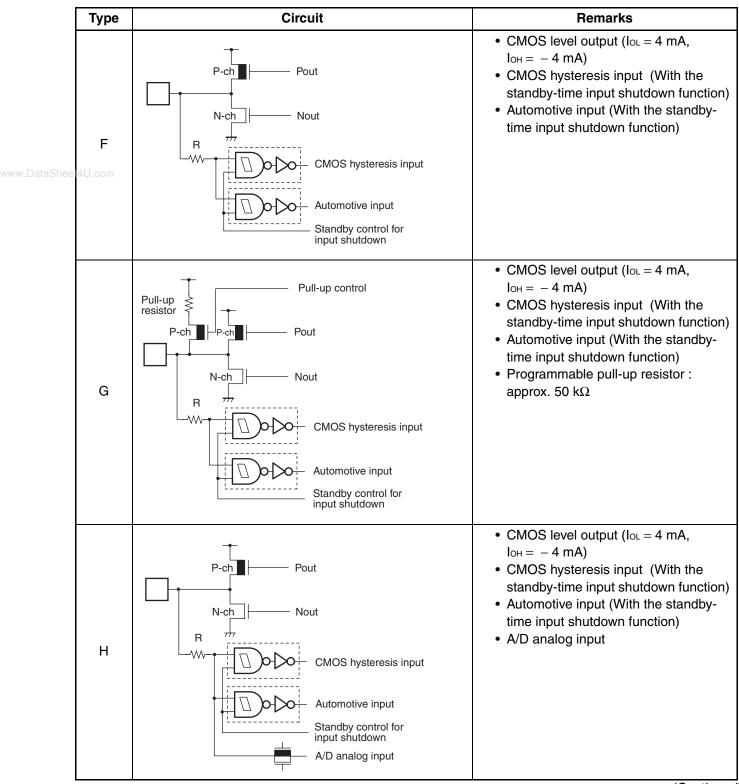

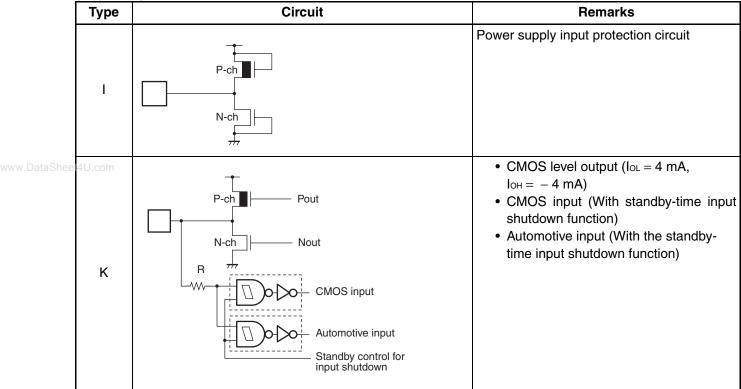

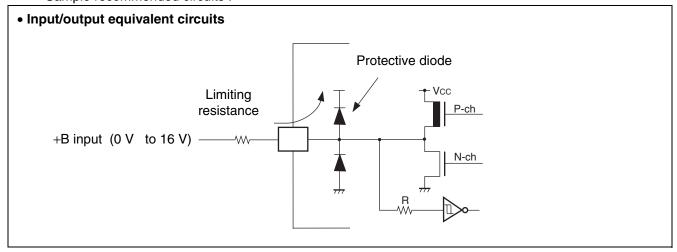

### ■ I/O CIRCUIT TYPE

| Туре                  | Circuit                                      | Remarks                                                                            |

|-----------------------|----------------------------------------------|------------------------------------------------------------------------------------|

| <b>A</b><br>eel4U.com | X1 Xout  X0 Standby control signal           | Oscillation circuit High-speed oscillation feedback resistor = approx. 1 MΩ        |

| В                     | X1A Xout  X0A Standby control signal         | Oscillation circuit Low-speed oscillation feedback resistor = approx. 10 $M\Omega$ |

| С                     | CMOS Hysteresis inputs                       | CMOS input                                                                         |

| D                     | R CMOS Hysteresis inputs  Pull-down resistor | CMOS input     No Pull-down                                                        |

| E                     | Pull-up resistor  R  CMOS Hysteresis inputs  | CMOS hysteresis input Pull-up resistor value : approx. 50 kΩ                       |

(Continued)

(Continued)

#### (Continued)

#### **■ HANDLING DEVICES**

#### Special care is required for the following when handling the device :

- · Preventing latch-up

- Treatment of unused pins

- Using external clock

- · Notes on during operation of PLL clock mode

- Power supply pins (Vcc/Vss)

- Pull-up/down resistors

- · Crystal oscillator circuit

- Turning-on sequence of power supply to A/D converter and analog inputs

- Connection of unused pins of A/D converter

- · Notes on energization

- Stabilization of power supply voltage

- Initialization

- Correspondence with +105 °C or more

#### 1. Preventing latch-up

CMOS IC chips may suffer latch-up under the following conditions:

- A voltage higher than Vcc or lower than Vss is applied to an input or output pin.

- A voltage higher than the rated voltage is applied between Vcc and Vss.

- The AVcc power supply is applied before the Vcc voltage.

Latch-up may increase the power supply current drastically, causing thermal damage to the device.

When used, note that maximum rated voltage is not exceeded.

For the same reason, also be careful not to let the analog power-supply voltage (AVcc, AVR) exceed the digital power-supply voltage.

#### 2. Treatment of unused pins

Leaving unused input pins open may result in misbehavior or latch-up and possible permanent damage of the device. Therefore, they must be pulled up or pulled down through resistors. In this case, those resistors should be more than  $2 \ k\Omega$ .

Unused bidirectional pins should be set to the output state and can be left open, or the input state with the above described connection.

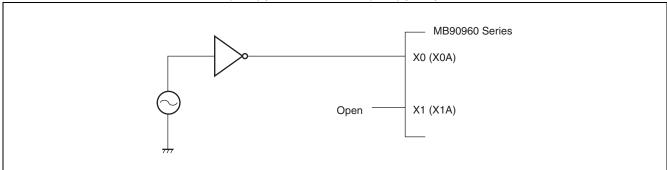

#### 3. Using external clock

To use external clock, drive the X0 (X0A) pin and leave X1 (X1A) pin open.

#### 4. Notes on during operation of PLL clock mode

On this microcontroller, if in case the crystal oscillator breaks off or an external reference clock input stops while the PLL clock mode is selected, a self-oscillator circuit contained in the PLL may continue its operation at its self-running frequency. However, Fujitsu will not guarantee results of operations if such failure occurs.

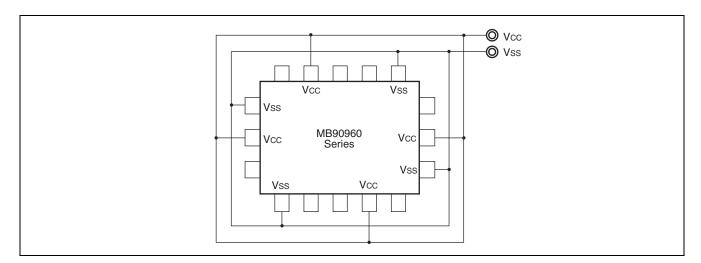

#### 5. Power supply pins (Vcc/Vss)

- If there are multiple Vcc and Vss pins, from the point of view of device design, pins to be of the same potential are connected the inside of the device to prevent such malfunctioning as latch-up.

- To reduce unnecessary radiation, prevent malfunctioning of the strobe signal due to the rise of ground level, and to keep the recommended DC characteristics specified as the total output current, be sure to connect the www.DataSheet4U.coVcc and Vss pins to the power supply and ground externally.

- Connect Vcc and Vss to the device from the power supply source with lowest possible impedance.

- It is recommended to connect a capacitor of about 0.1  $\mu$ F as a bypass capacitor between Vcc and Vss in the vicinity of Vcc and Vss pins of the device.

#### 6. Pull-up/down resistors

The MB90960 series does not support internal pull-up/down resistors (except Port 2 : programmable pull-up resistors) . Use pull-up/down handling where needed.

#### 7. Crystal oscillator circuit

Noises around X0 or X1 pins may be possible causes of abnormal operations. Make sure to provide bypass capacitors via shortest distance from X0, X1 pins, crystal oscillator (or ceramic resonator) and ground lines, and make sure, to the utmost effort, that lines of oscillation circuit do not cross the lines of other circuits. It is highly recommended to provide a printed circuit board artwork surrounding X0 and X1 pins with a ground area for stabilizing the operation.

#### 8. Turning-on sequence of power supply to A/D converter and analog inputs

Make sure to turn on the A/D converter power supply (AV $_{\rm CC}$ , AVR) and analog inputs (AN0 to AN15) after turning-on the digital power supply (V $_{\rm CC}$ ). Turn-off the digital power supply after turning off the A/D converter power supply and analog inputs. In this case, make sure that the voltage does not exceed AVR or AV $_{\rm CC}$  (turning on/off the analog and digital power supplies simultaneously is acceptable).

#### 9. Connection of unused pins of A/D converter if A/D converter is not used

Connect unused pins of A/D converter to AVcc = Vcc, AVss = AVR = Vss.

#### 10. Notes on energization

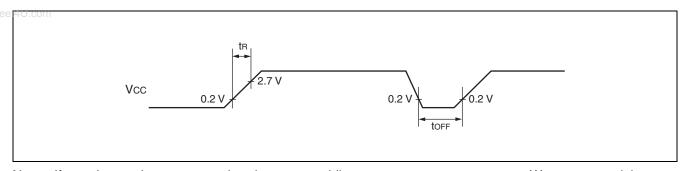

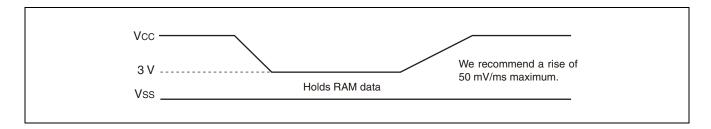

To prevent malfunction of the internal voltage regulator , supply voltage profile while turning on the power supply should be slower than 50  $\mu$ s (0.2 V to 2.7 V) .

#### 11. Stabilization of power supply voltage

If the power supply voltage varies acutely even within the operation assurance range of the  $V_{\rm CC}$  power supply voltage, a malfunction may occur. The  $V_{\rm CC}$  power supply voltage must therefore be stabilized. As stabilization guide lines, stabilize the power supply voltage so that  $V_{\rm CC}$  ripple fluctuations (peak to peak value) in the commercial frequencies (50 Hz/60 Hz) fall within 10% of the standard  $V_{\rm CC}$  power supply voltage and the transient fluctuation rate becomes 0.1 V/ms or less in instantaneous fluctuation for power supply switching.

#### 12. Initialization

In the device, there are internal registers which are initialized only by a power-on reset. To initialize these registers, turn on the power again.

#### 13. Correspondence with +105 °C or more

If used exceeding  $T_A = +105$  °C, please contact Fujitsu for reliability limitations.

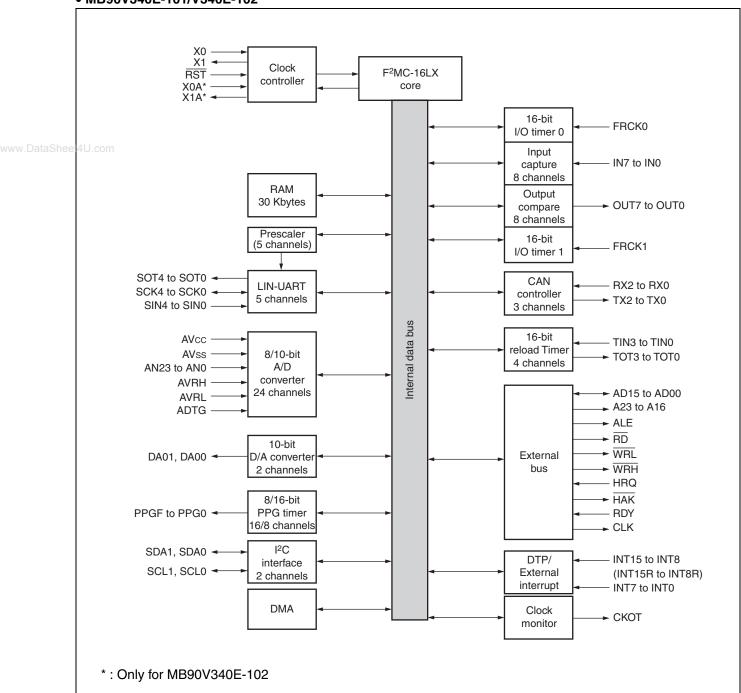

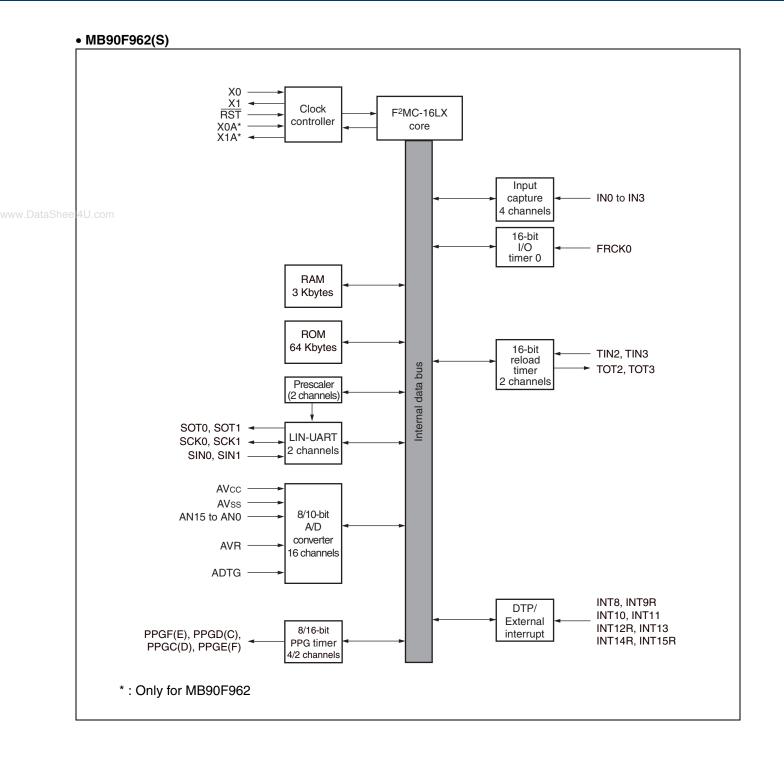

#### **■ BLOCK DIAGRAMS**

#### • MB90V340E-101/V340E-102

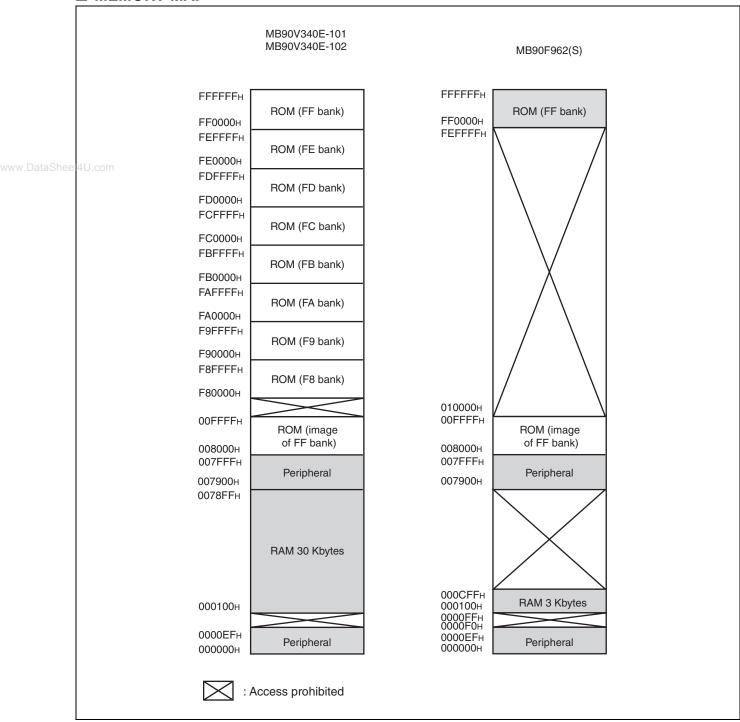

#### **■ MEMORY MAP**

Note: The high-order portion of bank 00 gives the image of the FF bank ROM to make the small model of the C compiler effective. Since the low-order 16 bits are the same, the table in ROM can be referred without using the far specification in the pointer declaration.

For example, an attempt to access 00C000H accesses the value at FFC000H in ROM.

The ROM area in bank FF exceeds 32 Kbytes, and its entire image cannot be shown in bank 00.

The image between FF8000 $_{\rm H}$  and FFFFFH is visible in bank 00, while the image between FF0000 $_{\rm H}$  and FF7FFFH is visible only in bank FF.

### ■ I/O MAP

| Address                  | Register                            | Abbreviation | Access | Resource name   | Initial value         |  |

|--------------------------|-------------------------------------|--------------|--------|-----------------|-----------------------|--|

| 000000н,<br>000001н      |                                     | Reserved     | d      |                 | •                     |  |

| 000002н                  | Port 2 Data Register                | PDR2         | R/W    | Port 2          | XXXXXXXX              |  |

| 000003н                  |                                     | Reserved     |        |                 |                       |  |

| 000004н                  | Port 4 Data Register                | PDR4         | R/W    | Port 4          | XXXXXXX               |  |

| 000005н                  | Port 5 Data Register                | PDR5         | R/W    | Port 5          | XXXXXXX               |  |

| 000006н                  | Port 6 Data Register                | PDR6         | R/W    | Port 6          | XXXXXXX               |  |

| 000007н                  |                                     | Reserved     | t      |                 |                       |  |

| 000008н                  | Port 8 Data Register                | PDR8         | R/W    | Port 8          | XXXXXXX               |  |

| 000009н,<br>00000Ан      |                                     | Reserved     | t      |                 |                       |  |

| 00000Вн                  | Port 5 Analog Input Enable Register | ADER5        | R/W    | Port 5, A/D     | 11111111В             |  |

| 00000Сн                  | Port 6 Analog Input Enable Register | ADER6        | R/W    | Port 6, A/D     | 111111111             |  |

| 00000Дн                  | Reserved                            |              |        |                 |                       |  |

| 00000Ен                  | Input Level Select Register 0       | ILSR0        | R/W    | Port 2, 4, 5, 6 | X000X0XX <sub>B</sub> |  |

| 00000Fн                  | Input Level Select Register 1       | ILSR1        | R/W    | Port 8          | XXXXXXX0 <sub>B</sub> |  |

| 0000010н,<br>000011н     |                                     | Reserved     | b      |                 |                       |  |

| 000012н                  | Port 2 Direction Register           | DDR2         | R/W    | Port 2          | 0000000В              |  |

| 000013н                  |                                     | Reserved     | t      |                 | <u> </u>              |  |

| 000014н                  | Port 4 Direction Register           | DDR4         | R/W    | Port 4          | ХХХ00000в             |  |

| 000015н                  | Port 5 Direction Register           | DDR5         | R/W    | Port 5          | 0000000В              |  |

| 000016н                  | Port 6 Direction Register           | DDR6         | R/W    | Port 6          | 0000000В              |  |

| 000017н                  |                                     | Reserved     | d      |                 |                       |  |

| 000018н                  | Port 8 Direction Register           | DDR8         | R/W    | Port 8          | 000000Х0в             |  |

| 000019н                  |                                     | Reserved     | d      |                 |                       |  |

| 00001Ан                  | Port A Direction Register           | DDRA         | W      | Port A          | XXX00XXX <sub>B</sub> |  |

| 00001Вн<br>to<br>00001Dн |                                     | Reserved     |        |                 |                       |  |

| 00001Ен                  | Port 2 Pull-up Control Register     | PUCR2        | R/W    | Port 2          | 0000000В              |  |

| 00001Fн                  |                                     | Reserved     | d      |                 |                       |  |

(Continued)

| Address                  | Register                                     | Abbreviation | Access       | Resource name             | Initial value |

|--------------------------|----------------------------------------------|--------------|--------------|---------------------------|---------------|

| 000020н                  | Serial Mode Register 0                       | SMR0         | W, R/W       |                           | 0000000В      |

| 000021н                  | Serial Control Register 0                    | SCR0         | W, R/W       |                           | 0000000В      |

| 000022н                  | Reception/Transmission Data Register 0       | RDR0/TDR0    | R/W          |                           | 0000000В      |

| 000023н                  | Serial Status Register 0                     | SSR0         | R, R/W       |                           | 00001000в     |

| 000024н                  | Extended Communication Control<br>Register 0 | ECCR0        | R, W,<br>R/W | LIN-UART0                 | 000000XXB     |

| 000025н                  | Extended Status Control Register 0           | ESCR0        | R/W          |                           | 00000100в     |

| 000026н                  | Baud Rate Generator Register 00              | BGR00        | R/W, R       |                           | 0000000В      |

| 000027н                  | Baud Rate Generator Register 01              | BGR01        | R/W, R       |                           | 0000000В      |

| 000028н                  | Serial Mode Register 1                       | SMR1         | W, R/W       |                           | 0000000В      |

| 000029н                  | Serial Control Register 1                    | SCR1         | W, R/W       |                           | 0000000В      |

| 00002Ан                  | Reception/Transmission Data Register 1       | RDR1/TDR1    | R/W          |                           | 0000000В      |

| 00002Вн                  | Serial Status Register 1                     | SSR1         | R, R/W       |                           | 00001000в     |

| 00002Сн                  | Extended Communication Control<br>Register 1 | ECCR1        | R, W,<br>R/W | LIN-UART1                 | 000000XXB     |

| 00002Dн                  | Extended Status Control Register 1           | ESCR1        | R/W          |                           | 00000100в     |

| 00002Ен                  | Baud Rate Generator Register 10              | BGR10        | R/W, R       |                           | 0000000В      |

| 00002Fн                  | Baud Rate Generator Register 11              | BGR11        | R/W, R       |                           | 0000000В      |

| 000030н<br>to<br>00003Ан |                                              | Reserved     |              |                           |               |

| 00003Вн                  | Address Detect Control Register 1            | PACSR1       | R/W          | Address Match Detection 1 | 0000000В      |

| 00003Сн<br>to<br>000047н |                                              | Reserved     |              |                           |               |

| 000048н                  | PPGC Operation Mode Control Register         | PPGCC        | W, R/W       |                           | 0Х000ХХ1в     |

| 000049н                  | PPGD Operation Mode Control Register         | PPGCD        | W, R/W       | 16-bit PPG C/D            | 0Х00001в      |

| 00004Ан                  | PPGC/PPGD Count Clock Select<br>Register     | PPGCD        | R/W          | 10 51111 0 0/2            | 000000Х0в     |

| 00004Вн                  |                                              | Reserved     | •            |                           | •             |

| 00004Сн                  | PPGE Operation Mode Control Register         | PPGCE        | W, R/W       |                           | 0Х000ХХ1в     |

| 00004Dн                  | PPGF Operation Mode Control Register         | PPGCF        | W, R/W       | 16-bit PPG E/F            | 0Х00001в      |

| 00004Ен                  | PPGE/PPGF Count Clock Select<br>Register     | PPGEF        | R/W          |                           | 000000Х0в     |

|                          |                                              |              |              | •                         |               |

(Continued)

| Address                  | Register                                       | Abbreviation | Access | Resource name                               | Initial value         |  |

|--------------------------|------------------------------------------------|--------------|--------|---------------------------------------------|-----------------------|--|

| 000050н                  | Input Capture Control Status 0/1               | ICS01        | R/W    | Input Conture 0/1                           | 0000000В              |  |

| 000051н                  | Input Capture Edge 0/1                         | ICE01        | R/W, R | Input Capture 0/1                           | XXX0X0XX              |  |

| 000052н                  | Input Capture Control Status 2/3               | ICS23        | R/W    | Innest Content 0/0                          | 0000000В              |  |

| 000053н                  | Input Capture Edge 2/3                         | ICE23        | R      | Input Capture 2/3                           | XXXXXXX               |  |

| 000054н<br>to<br>000063н |                                                | Reserv       | /ed    |                                             |                       |  |

| 000064н                  | Timer Control Status 2                         | TMCSR2       | R/W    | 16-bit Reload Timer 2                       | 0000000В              |  |

| 000065н                  | Timer Control Status 2                         | TMCSR2       | R/W    | TO BILLICIONA TIME! 2                       | XXXX0000e             |  |

| 000066н                  | Timer Control Status 3                         | TMCSR3       | R/W    | 16-bit Reload Timer 3                       | 0000000В              |  |

| 000067н                  | Timer Control Status 3                         | TMCSR3       | R/W    | TO-DITTIEIOAU TIITIEI 3                     | XXXX0000i             |  |

| 000068н                  | A/D Control Status 0                           | ADCS0        | R/W    |                                             | 000XXXX0e             |  |

| 000069н                  | A/D Control Status 1                           | ADCS1        | R/W, W | A/D Converter                               | 000000XB              |  |

| 00006Ан                  | A/D Data Register 0                            | ADCR0        | R      |                                             | 0000000B              |  |

| 00006Вн                  | A/D Data Register 1                            | ADCR1        | R      |                                             | XXXXXX00              |  |

| 00006Сн                  | A/D Converter Setting 0                        | ADSR0        | R/W    |                                             | 0000000B              |  |

| 00006Dн                  | A/D Converter Setting 1                        | ADSR1        | R/W    |                                             | 0000000e              |  |

| 00006Ен                  | Reserved                                       |              |        |                                             |                       |  |

| 00006Fн                  | ROM Mirror Function Select                     | ROMM         | W      | ROM Mirror                                  | XXXXXXX1              |  |

| 000070н<br>to<br>00009Dн |                                                | Reserv       | /ed    |                                             |                       |  |

| 00009Ен                  | Address Detect Control Register 0              | PACSR0       | R/W    | Address Match<br>Detection 0                | 00000000              |  |

| 00009Fн                  | Delayed Interrupt/Release Register             | DIRR         | R/W    | Delayed Interrupt generation module         | XXXXXXX0              |  |

| 0000А0н                  | Low-power Consumption Mode<br>Control Register | LPMCR        | W, R/W | Low-Power<br>consumption<br>Control Circuit | 00011000 <sub>B</sub> |  |

| 0000А1н                  | Clock Selection Register                       | CKSCR        | R, R/W | Low-Power<br>consumption<br>Control Circuit | 11111100₅             |  |

| 0000A2н<br>to<br>0000A7н |                                                | Reserv       | /ed    |                                             |                       |  |

| 0000А8н                  | Watchdog Timer Control Register                | WDTC         | R, W   | Watchdog Timer                              | XXXXX111              |  |

| 0000А9н                  | Time-base Timer Control Register               | TBTC         | W, R/W | Time-base Timer                             | 1XX00100              |  |

(Continued)

| Address                  | Register                         | Abbreviation | Access | Resource name        | Initial value |  |  |  |  |  |

|--------------------------|----------------------------------|--------------|--------|----------------------|---------------|--|--|--|--|--|

| 0000ААн                  | Watch Timer Control Register     | WTC          | R, R/W | Watch Timer          | 1Х001000в     |  |  |  |  |  |

| 0000ABн<br>to<br>0000ADн |                                  | Reserved     |        |                      |               |  |  |  |  |  |

| 0000АЕн                  | Flash Control Status             | FMCS         | R, R/W | Flash Memory         | 000Х0000в     |  |  |  |  |  |

| 0000АГн                  | Reserved                         |              |        |                      |               |  |  |  |  |  |

| 0000В0н                  | Interrupt Control Register 00    | ICR00        | W, R/W |                      | 00000111в     |  |  |  |  |  |

| 0000В1н                  | Interrupt Control Register 01    | ICR01        | W, R/W |                      | 00000111в     |  |  |  |  |  |

| 0000В2н                  | Interrupt Control Register 02    | ICR02        | W, R/W |                      | 00000111в     |  |  |  |  |  |

| 0000ВЗн                  | Interrupt Control Register 03    | ICR03        | W, R/W |                      | 00000111в     |  |  |  |  |  |

| 0000В4н                  | Interrupt Control Register 04    | ICR04        | W, R/W |                      | 00000111в     |  |  |  |  |  |

| 0000В5н                  | Interrupt Control Register 05    | ICR05        | W, R/W |                      | 00000111в     |  |  |  |  |  |

| 0000В6н                  | Interrupt Control Register 06    | ICR06        | W, R/W |                      | 00000111в     |  |  |  |  |  |

| 0000В7н                  | Interrupt Control Register 07    | ICR07        | W, R/W | Interrupt Control    | 00000111в     |  |  |  |  |  |

| 0000В8н                  | Interrupt Control Register 08    | ICR08        | W, R/W | - Interrupt Control  | 00000111в     |  |  |  |  |  |

| 0000В9н                  | Interrupt Control Register 09    | ICR09        | W, R/W |                      | 00000111в     |  |  |  |  |  |

| 0000ВАн                  | Interrupt Control Register 10    | ICR10        | W, R/W |                      | 00000111в     |  |  |  |  |  |

| 0000ВВн                  | Interrupt Control Register 11    | ICR11        | W, R/W |                      | 00000111в     |  |  |  |  |  |

| 0000ВСн                  | Interrupt Control Register 12    | ICR12        | W, R/W |                      | 00000111в     |  |  |  |  |  |

| 0000ВДн                  | Interrupt Control Register 13    | ICR13        | W, R/W |                      | 00000111в     |  |  |  |  |  |

| 0000ВЕн                  | Interrupt Control Register 14    | ICR14        | W, R/W |                      | 00000111в     |  |  |  |  |  |

| 0000ВГн                  | Interrupt Control Register 15    | ICR15        | W, R/W |                      | 00000111в     |  |  |  |  |  |

| 0000C0н<br>to<br>0000C9н |                                  | Reserv       | ed     |                      |               |  |  |  |  |  |

| 0000САн                  | DTP/External Interrupt Enable 1  | ENIR1        | R/W    |                      | 0000000B      |  |  |  |  |  |

| 0000СВн                  | DTP/External Interrupt Source 1  | EIRR1        | R/W    |                      | XXXXXXXXB     |  |  |  |  |  |

| 0000ССн                  | Detection Level Setting 1        | ELVR1        | R/W    | External Interrupt 1 | 0000000В      |  |  |  |  |  |

| 0000СDн                  | Detection Level Setting 1        | ELVR1        | R/W    |                      | 0000000В      |  |  |  |  |  |

| 0000СЕн                  | External Interrupt factor Select | EISSR        | R/W    |                      | 0000000В      |  |  |  |  |  |

| 0000СFн                  | PLL/Sub clock Control Register   | PSCCR        | W      | PLL                  | XXXX0000B     |  |  |  |  |  |

| 0000D0н<br>to<br>0000FFн |                                  | Reserv       | ed     |                      |               |  |  |  |  |  |

(Continued)

| Address                  | Register               | Abbreviation     | Access | Resource name      | Initial value |  |  |

|--------------------------|------------------------|------------------|--------|--------------------|---------------|--|--|

| 007900н<br>to<br>007917н |                        | Reserve          | ed     |                    |               |  |  |

| 007918н                  | Reload Register LC     | PRLLC            | R/W    |                    | XXXXXXXX      |  |  |

| 007919н                  | Reload Register HC     | PRLHC            | R/W    | 10 hit DDC C/D     | XXXXXXXXB     |  |  |

| 00791Ан                  | Reload Register LD     | PRLLD            | R/W    | 16-bit PPG C/D     | XXXXXXXX      |  |  |

| 400791Вн                 | Reload Register HD     | PRLHD            | R/W    |                    | XXXXXXXX      |  |  |

| 00791Сн                  | Reload Register LE     | PRLLE            | R/W    |                    | XXXXXXXX      |  |  |

| 00791Dн                  | Reload Register HE     | PRLHE            | R/W    | 40 k# DDO E/E      | XXXXXXXX      |  |  |

| 00791Ен                  | Reload Register LF     | PRLLF            | R/W    | 16-bit PPG E/F     | XXXXXXXX      |  |  |

| 00791Fн                  | Reload Register HF     | PRLHF            | R/W    |                    | XXXXXXXX      |  |  |

| 007920н                  | Input Capture 0        | IPCP0            | R      |                    | XXXXXXXX      |  |  |

| 007921н                  | Input Capture 0        | IPCP0            | R      | 110                | XXXXXXXX      |  |  |

| 007922н                  | Input Capture 1        | IPCP1            | R      | Input Capture 0/1  | XXXXXXXX      |  |  |

| 007923н                  | Input Capture 1        | IPCP1            | R      |                    | XXXXXXXX      |  |  |

| 007924н                  | Input Capture 2        | IPCP2            | R      |                    | XXXXXXXX      |  |  |

| 007925н                  | Input Capture 2        | IPCP2            | R      | Innest Contest 0/0 | XXXXXXXX      |  |  |

| 007926н                  | Input Capture 3        | IPCP3            | R      | Input Capture 2/3  | XXXXXXXX      |  |  |

| 007927н                  | Input Capture 3        | IPCP3            | R      |                    | XXXXXXXX      |  |  |

| 007928н<br>to<br>00793Fн |                        | Reserve          | ed     |                    |               |  |  |

| 007940н                  | Timer Data 0           | TCDT0            | R/W    |                    | 0000000В      |  |  |

| 007941н                  | Timer Data 0           | TCDT0            | R/W    | 1/O T' O           | 0000000В      |  |  |

| 007942н                  | Timer Control Status 0 | TCCSL0           | R/W    | I/O Timer 0        | 0000000в      |  |  |

| 007943н                  | Timer Control Status 0 | TCCSH0           | R/W    |                    | 0XXXXXXXB     |  |  |

| 007944н<br>to<br>00794Вн |                        | Reserved         |        |                    |               |  |  |

| 00794Сн                  | Times 0/Deleged 0      | TMD0/TMDLD0      | R/W    | 16-bit Reload      | XXXXXXXX      |  |  |

| 00794Dн                  | - Timer 2/Reload 2     | TMR2/TMRLR2      | R/W    | Timer 2            | XXXXXXXX      |  |  |

| 00794Ен                  | Time of O/Dalamata     | TA ADO/TA ADI DO | R/W    | 16-bit Reload      | XXXXXXXX      |  |  |

| 00794Fн                  | Timer 3/Reload 3       | TMR3/TMRLR3      | R/W    | Timer 3            | XXXXXXXX      |  |  |

| 007950н<br>to<br>0079DFн |                        | Reserve          | ed     |                    |               |  |  |

(Continued)

#### (Continued)

|               | Address                  | Register                 | Abbreviation | Access | Resource name             | Initial value |

|---------------|--------------------------|--------------------------|--------------|--------|---------------------------|---------------|

|               | 0079Е0н                  | Detect Address Setting 0 | PADR0        | R/W    |                           | XXXXXXXXB     |

|               | 0079Е1н                  | Detect Address Setting 0 | PADR0        | R/W    |                           | XXXXXXX       |

|               | 0079Е2н                  | Detect Address Setting 0 | PADR0        | R/W    |                           | XXXXXXX       |

|               | 0079ЕЗн                  | Detect Address Setting 1 | PADR1        | R/W    |                           | XXXXXXX       |

|               | 0079Е4н                  | Detect Address Setting 1 | PADR1        | R/W    | Address Match Detection 0 | XXXXXXX       |

|               | 0079Е5н                  | Detect Address Setting 1 | PADR1        | R/W    | Botootion                 | XXXXXXX       |

| www.DataSheet | 0079Е6н                  | Detect Address Setting 2 | PADR2        | R/W    |                           | XXXXXXX       |

|               | 0079Е7н                  | Detect Address Setting 2 | PADR2        | R/W    |                           | XXXXXXX       |

|               | 0079Е8н                  | Detect Address Setting 2 | PADR2        | R/W    |                           | XXXXXXX       |

|               | 0079Е9н<br>to<br>0079ЕFн |                          | Reserve      | ed     |                           |               |

| ·             | 0079F0н                  | Detect Address Setting 3 | PADR3        | R/W    |                           | XXXXXXXXB     |

|               | 0079F1н                  | Detect Address Setting 3 | PADR3        | R/W    |                           | XXXXXXX       |

|               | 0079F2н                  | Detect Address Setting 3 | PADR3        | R/W    |                           | XXXXXXX       |

|               | 0079F3н                  | Detect Address Setting 4 | PADR4        | R/W    |                           | XXXXXXX       |

|               | 0079F4н                  | Detect Address Setting 4 | PADR4        | R/W    | Address Match Detection 1 | XXXXXXX       |

|               | 0079F5н                  | Detect Address Setting 4 | PADR4        | R/W    | Botootion 1               | XXXXXXX       |

|               | 0079F6н                  | Detect Address Setting 5 | PADR5        | R/W    |                           | XXXXXXX       |

|               | 0079F7н                  | Detect Address Setting 5 | PADR5        | R/W    |                           | XXXXXXX       |

|               | 0079F8н                  | Detect Address Setting 5 | PADR5        | R/W    |                           | XXXXXXX       |

|               | 0079F9н<br>to<br>007FFFн |                          | Reserve      | ed     |                           |               |

Notes: • Initial value of "X" represents unknown value.

• Any write access to reserved addresses in I/O map should not be performed. A read access to reserved addresses results in reading "X".

## ■ INTERRUPT FACTORS, INTERRUPT VECTORS, INTERRUPT CONTROL REGISTER

| Interrupt cause             | El <sup>2</sup> OS | Interru | ot vector           |        | t control<br>ister |  |

|-----------------------------|--------------------|---------|---------------------|--------|--------------------|--|

| ·                           | corresponding      | Number  | Address             | Number | Address            |  |

| Reset                       | N                  | #08     | FFFFDCH             | _      | _                  |  |

| INT9 instruction            | N                  | #09     | FFFFD8 <sub>H</sub> |        |                    |  |

| Exception processing        | N                  | #10     | FFFFD4 <sub>H</sub> | _      | _                  |  |

| Reserved                    | N                  | #11     | FFFFD0 <sub>H</sub> | ICR00  | 0000В0н            |  |

| Reserved                    | N                  | #12     | FFFFCCH             | ICHUU  | ООООВОН            |  |

| Reserved                    | N                  | #13     | FFFFC8 <sub>H</sub> | ICR01  | 0000В1н            |  |

| Reserved                    | N                  | #14     | FFFFC4 <sub>H</sub> | ICHUI  | ООООБІН            |  |

| Reserved                    | N                  | #15     | FFFFC0 <sub>H</sub> | ICR02  | 0000В2н            |  |

| Reserved                    | N                  | #16     | FFFFBCH             | ICHUZ  | ООООБИ             |  |

| Reserved                    | N                  | #17     | FFFFB8 <sub>H</sub> | ICR03  | 000000             |  |

| Reserved                    | N                  | #18     | FFFFB4 <sub>H</sub> | ICHUS  | 0000ВЗн            |  |

| 16-bit reload timer 2       | Y1                 | #19     | FFFFB0 <sub>H</sub> | ICR04  | 0000В4н            |  |

| 16-bit reload timer 3       | Y1                 | #20     | FFFFAC⊢             | ICN04  |                    |  |

| Reserved                    | N                  | #21     | FFFFA8 <sub>H</sub> | ICR05  | 0000В5н            |  |

| Reserved                    | N                  | #22     | FFFFA4 <sub>H</sub> | ICHUS  | НСОООО             |  |

| PPG C/D                     | N                  | #23     | FFFFA0 <sub>H</sub> | ICR06  | 0000В6н            |  |

| PPG E/F                     | N                  | #24     | FFFF9C <sub>H</sub> | ICHUU  | ООООВОН            |  |

| Time-base timer             | N                  | #25     | FFFF98⊦             | ICR07  | 0000В7н            |  |

| External interrupt 8 to 11  | Y1                 | #26     | FFFF94 <sub>H</sub> | ICHU/  | 0000Б7н            |  |

| Watch Timer                 | N                  | #27     | FFFF90 <sub>H</sub> | ICR08  | 0000B8             |  |

| External interrupt 12 to 15 | Y1                 | #28     | FFFF8C <sub>H</sub> | 101100 | 0000В8н            |  |

| A/D converter               | Y1                 | #29     | FFFF88 <sub>H</sub> | ICR09  | 0000В9н            |  |

| I/O timer 0                 | N                  | #30     | FFFF84 <sub>H</sub> | 101109 | ООООБЭН            |  |

| Reserved                    | N                  | #31     | FFFF80 <sub>H</sub> | ICR10  | 0000ВАн            |  |

| Reserved                    | N                  | #32     | FFFF7C <sub>H</sub> | 101110 | ООООВАН            |  |

| Input capture 0 to 3        | Y1                 | #33     | FFFF78 <sub>H</sub> | ICR11  | 0000ВВн            |  |

| Reserved                    | N                  | #34     | FFFF74 <sub>H</sub> | 101111 | 0000BBH            |  |

| LIN-UART 0 reception        | Y2                 | #35     | FFFF70 <sub>H</sub> | ICR12  | 0000ВСн            |  |

| LIN-UART 0 transmission     | Y1                 | #36     | FFFF6C <sub>H</sub> | 101112 | UUUUBCH            |  |

| LIN-UART 1 reception        | Y2                 | #37     | FFFF68 <sub>H</sub> | ICR13  | 0000ВДн            |  |

| LIN-UART 1 transmission     | Y1                 | #38     | FFFF64 <sub>H</sub> | 10.110 | 000000             |  |

(Continued)

www.DataSheet465om

#### (Continued)

| Interrupt cause                     | El <sup>2</sup> OS corresponding | Interrup | t vector            | Interrupt control register |         |  |

|-------------------------------------|----------------------------------|----------|---------------------|----------------------------|---------|--|

|                                     | corresponding                    | Number   | Address             | Number                     | Address |  |

| Reserved                            | N                                | #39      | FFFF60⊦             | ICR14                      | 0000ВЕн |  |

| Reserved                            | N                                | #40      | FFFF5C <sub>H</sub> | ION14                      | UUUUBEH |  |

| Flash memory                        | N                                | #41      | FFFF58⊦             | ICR15                      | 0000BFн |  |

| Delayed interrupt generation module | N                                | #42      | FFFF54 <sub>H</sub> | ICHIS                      | UUUUDFH |  |

www.DataSheet4U.**Yo1**n: Usable

Y2: Usable, with El<sup>2</sup>OS stop function

N : Unusable

Notes: • The peripheral resources sharing the ICR register have the same interrupt level.

• When 2 peripheral resources share the ICR register, only one can use extended intelligent I/O service at a time.

• When either of the 2 peripheral resources sharing the ICR register specifies extended intelligent I/O service, the other one cannot use interrupts.

### **■ ELECTRICAL CHARACTERISTICS**

### 1. Absolute Maximum Ratings

| Parameter                                | Symbol                   | Rat       | ing       | Unit  | Remarks      |  |

|------------------------------------------|--------------------------|-----------|-----------|-------|--------------|--|

| Faiailletei                              | Syllibol                 | Min       | Max       | Oilit | nemarks      |  |

|                                          | Vcc                      | Vss - 0.3 | Vss + 6.0 | V     |              |  |

| Power supply voltage*1                   | AVcc                     | Vss - 0.3 | Vss + 6.0 | V     | Vcc = AVcc*2 |  |

|                                          | AVR                      | Vss - 0.3 | Vss + 6.0 | V     | AVcc ≥ AVR*2 |  |

| Input voltage*1                          | Vı                       | Vss - 0.3 | Vss + 6.0 | V     | *3           |  |

| Output voltage*1                         | Vo                       | Vss - 0.3 | Vss + 6.0 | V     | *3           |  |

| Maximum clamp current                    | <b>I</b> CLAMP           | -2.0      | +2.0      | mA    | *4           |  |

| Total Maximum clamp current              | $\Sigma$ I $ $ CLAMP $ $ | _         | 40        | mA    | *4           |  |

| "L" level maximum output current         | Іоь                      | _         | 15        | mA    | *4           |  |

| "L" level average output current         | lolav                    | _         | 4         | mA    | *4           |  |

| "L" level maximum overall output current | ΣΙοι                     |           | 125       | mA    | *4           |  |

| "L" level average overall output current | ΣIOLAV                   | _         | 40        | mA    | *4           |  |

| "H" level maximum output current         | Іон                      | _         | -15       | mA    | *4           |  |

| "H" level average output current         | Іонач                    | _         | -4        | mA    | *4           |  |

| "H" level maximum overall output current | ΣІон                     | _         | -125      | mA    | *4           |  |

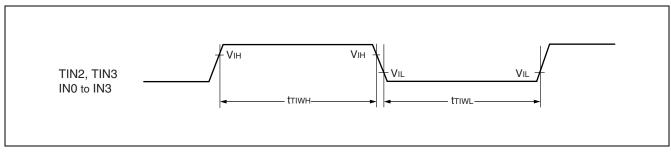

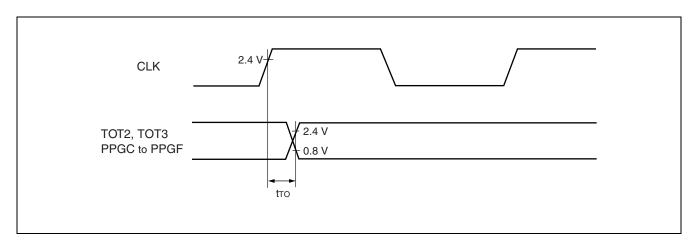

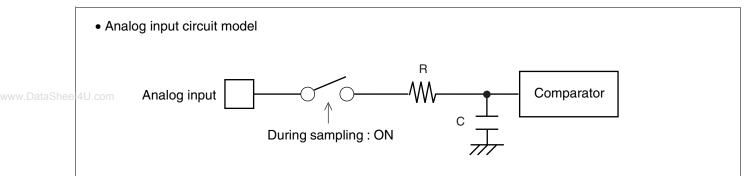

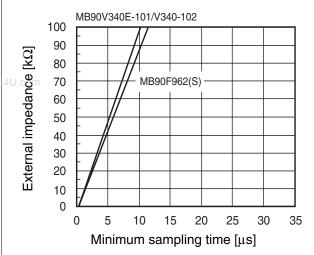

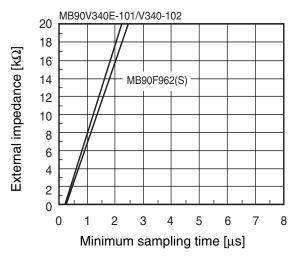

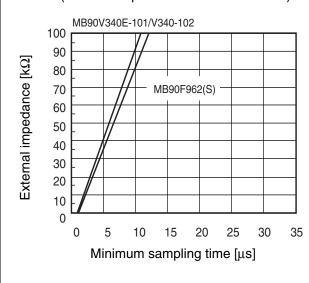

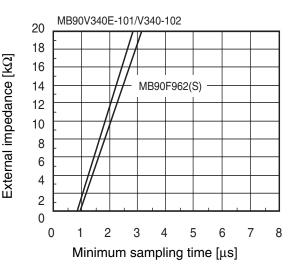

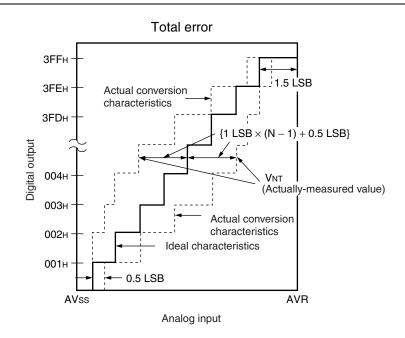

| "H" level average overall output current | ΣΙομαν                   | _         | -40       | mA    | *4           |  |