# FR60 32-BIT MICROCONTROLLER MB91313A Series HARDWARE MANUAL

# FR60 32-BIT MICROCONTROLLER MB91313A Series HARDWARE MANUAL

For the information for microcontroller supports, see the following web site. This web site includes the **"Customer Design Review Supplement"** which provides the latest cautions on system development and the minimal requirements to be checked to prevent problems before the system development.

http://edevice.fujitsu.com/micom/en-support/

FUJITSU SEMICONDUCTOR LIMITED

## Preface

#### Purpose of This Document and Intended Reader

Thank you very much for your continued patronage of Fujitsu Semiconductor products.

FR family is a line of single-chip microcontrollers based on the 32-bit high-performance RISC CPU while integrating a variety of I/O resources for embedded control applications which require high-performance, high-speed CPU processing.

This manual describes the functions and operation of the MB91313A series for engineers who actually use this semiconductor to design products. Please read this manual first.

FR, the abbreviation of FUJITSU RISC controller, is a line of products of FUJITSU SEMICONDUCTOR LIMITED.

#### ■ Trademark

The company names and brand names herein are the trademarks or registered trademarks of their respective owners.

#### Organization of This Manual

This manual consists of the following 19 chapters and appendix.

#### CHAPTER 1 OVERVIEW

This chapter explains the features and basic specification of the MB91313A series.

#### CHAPTER 2 CPU AND CONTROL BLOCK

This chapter provides the CPU core of the FR family, covering its architecture, specifications, and instructions.

#### CHAPTER 3 EXTERNAL BUS INTERFACE

This chapter explains the features, block diagram, I/O pins, and registers of the external bus interface.

#### CHAPTER 4 I/O PORTS

This chapter gives an overview of I/O ports and describes their register configuration and functions.

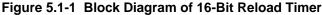

#### CHAPTER 5 16-BIT RELOAD TIMER

This chapter explains an overview, register configuration/functions and operations of the 16-bit reload timer.

#### CHAPTER 6 PPG (PROGRAMMABLE PULSE GENERATOR)

This chapter gives an outline of the PPG (Programmable Pulse Generator) timer and explains the register configuration and functions and the timer operations.

#### CHAPTER 7 16-BIT PULSE WIDTH COUNTER

This chapter gives an overview of the 16-bit pulse width counter and explains the register configuration and functions and the counter operation.

#### CHAPTER 8 MULTIFUNCTION TIMER

This chapter gives an overview of the multifunction timer and explains the register configuration and functions and the timer operation.

#### CHAPTER 9 OTHER TIMERS

This chapter explains the main oscillation stabilization wait timer, interval timer, and watch timer.

#### CHAPTER 10 INTERRUPT CONTROLLER

This chapter gives an overview of the interrupt controller and explains its register configuration/functions and its operations.

#### CHAPTER 11 EXTERNAL INTERRUPT CONTROL UNIT

This chapters gives an overview of the external interrupt control unit and describes its register configuration/functions and its operations.

#### CHAPTER 12 DELAY INTERRUPT MODULE

This chapter explains the overview of the delay interrupt module, configuration/functions of the registers, and operations of the module.

#### CHAPTER 13 BIT SEARCH MODULE

This chapter explains the overview of the bit search module, configurations/functions of the registers, and operations of the module.

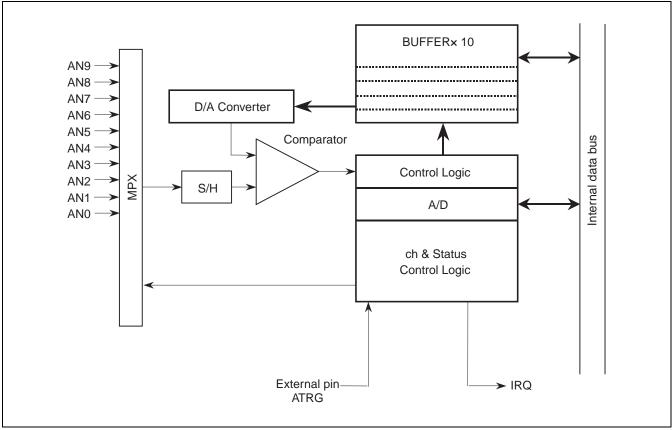

#### CHAPTER 14 10-BIT A/D CONVERTER

This chapter gives an overview of the 10-bit A/D converter, register configuration and functions, and 10-bit A/D converter operation.

#### CHAPTER 15 MULTI FUNCTION SERIAL INTERFACE

This chapter describes the functions and operations of the multi function serial interface.

#### CHAPTER 16 DMAC (DMA CONTROLLER)

This chapter gives an overview of the DMA controller (DMAC) and describes its register configuration and its operations.

#### CHAPTER 17 REMOTE CONTROL RECEPTION

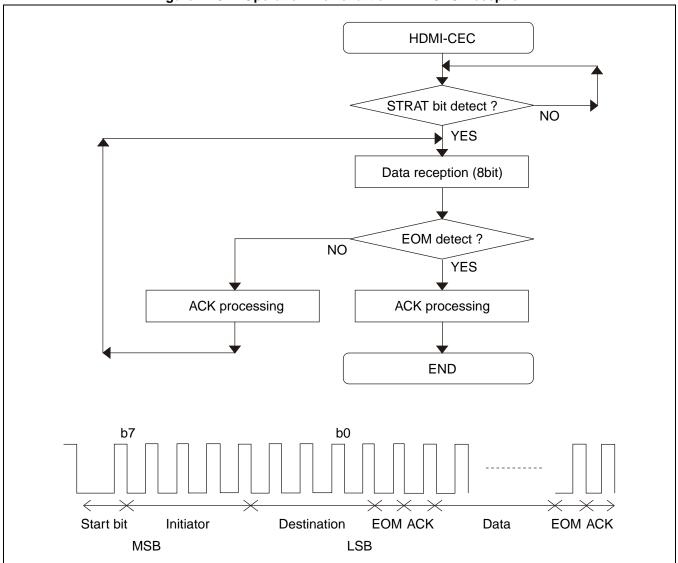

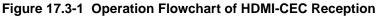

This chapter describes the functions and operations of HDMI-CEC reception, ACK automatic a response, and the remote control reception.

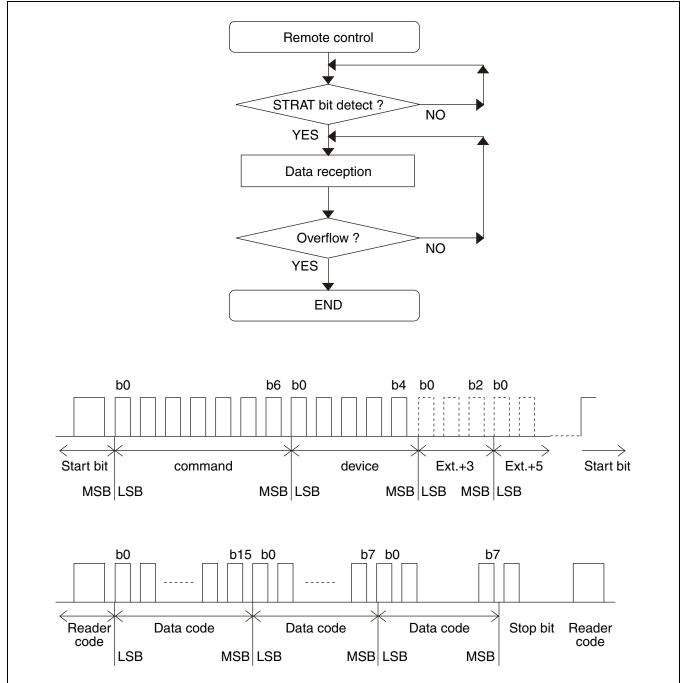

#### CHAPTER 18 FLASH MEMORY

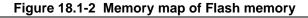

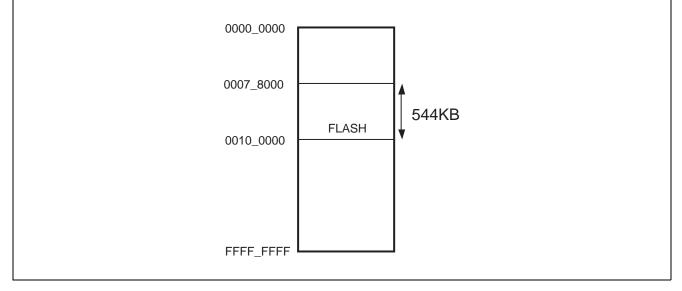

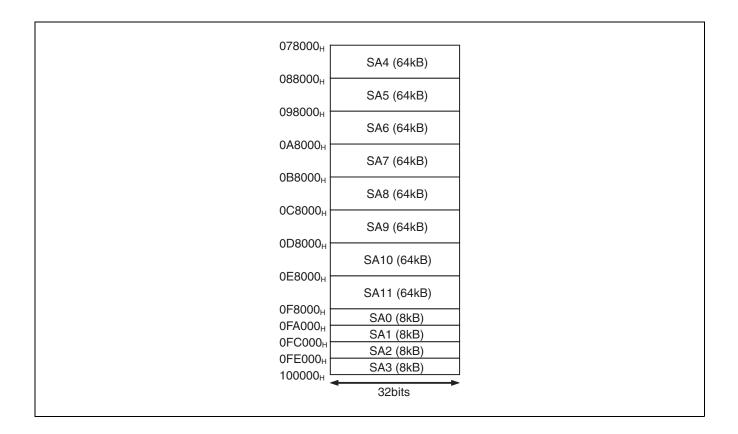

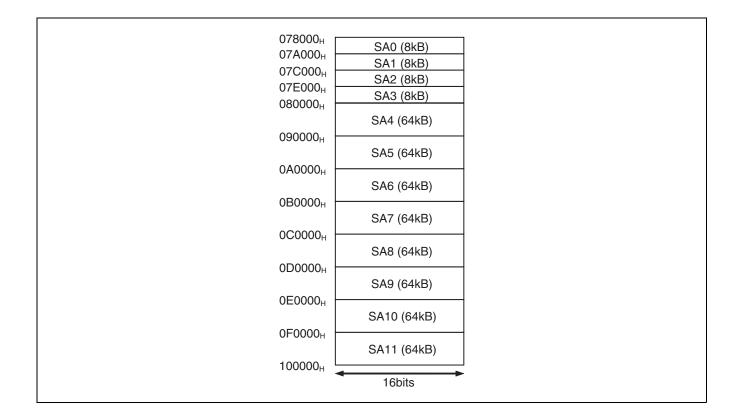

This chapter provides an outline of flash memory and explains its register configuration, register functions, and operations.

#### CHAPTER 19 MB91313A SERIAL PROGRAMMING CONNECTION

This chapter explains the serial programming connection for MB91313A.

#### APPENDIX

This appendix explains the details not covered in the main topics and other referential information for programming about the I/O map, interrupt vector, pin status of the CPU state, notes and instructions list when using the little endian area.

• The contents of this document are subject to change without notice. Customers are advised to consult with sales representatives before ordering.

- The information, such as descriptions of function and application circuit examples, in this document are presented solely for the purpose of reference to show examples of operations and uses of FUJITSU SEMICONDUCTOR device; FUJITSU SEMICONDUCTOR does not warrant proper operation of the device with respect to use based on such information. When you develop equipment incorporating the device based on such information, you must assume any responsibility arising out of such use of the information. FUJITSU SEMICONDUCTOR assumes no liability for any damages whatsoever arising out of the use of the information.

- Any information in this document, including descriptions of function and schematic diagrams, shall not be construed as license of the use or exercise of any intellectual property right, such as patent right or copyright, or any other right of FUJITSU SEMICONDUCTOR or any third party or does FUJITSU SEMICONDUCTOR warrant non-infringement of any third-party's intellectual property right or other right by using such information. FUJITSU SEMICONDUCTOR assumes no liability for any infringement of the intellectual property rights or other rights of third parties which would result from the use of information contained herein.

- The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite).

Please note that FUJITSU SEMICONDUCTOR will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products.

- Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

- Exportation/release of any products described in this document may require necessary procedures in accordance with the regulations of the Foreign Exchange and Foreign Trade Control Law of Japan and/or US export control laws.

- The company names and brand names herein are the trademarks or registered trademarks of their respective owners.

Copyright ©2007-2010 FUJITSU SEMICONDUCTOR LIMITED All rights reserved.

## CONTENTS

| CHAPTE | ER 1 OVERVIEW                                         | . 1 |

|--------|-------------------------------------------------------|-----|

| 1.1    | Features                                              | . 2 |

| 1.2    | Block Diagram                                         | . 5 |

| 1.3    | Pin Assignment                                        | . 6 |

| 1.4    | Package Dimensions                                    | . 7 |

| 1.5    | List of Pin Functions                                 | . 8 |

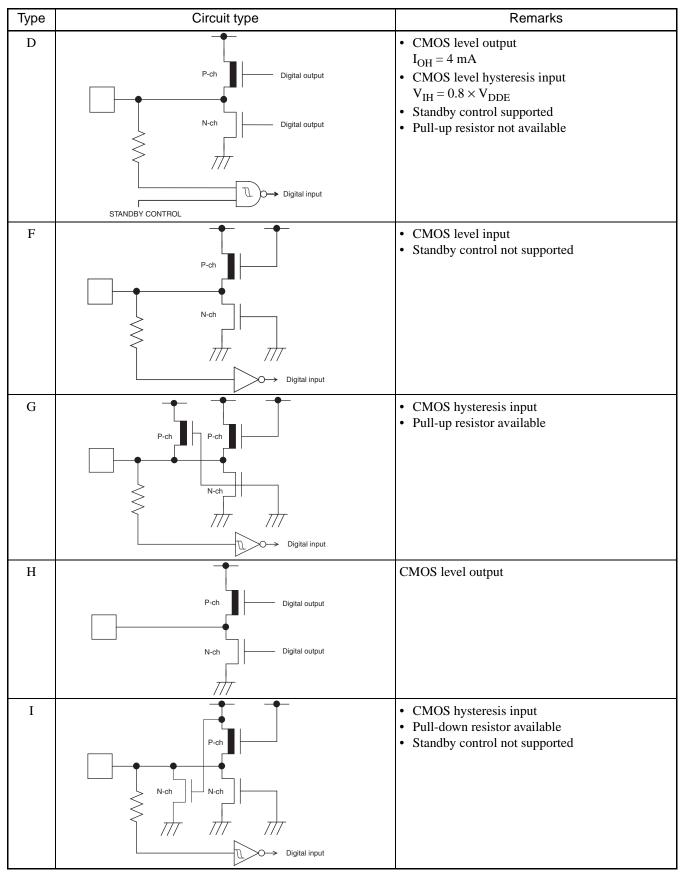

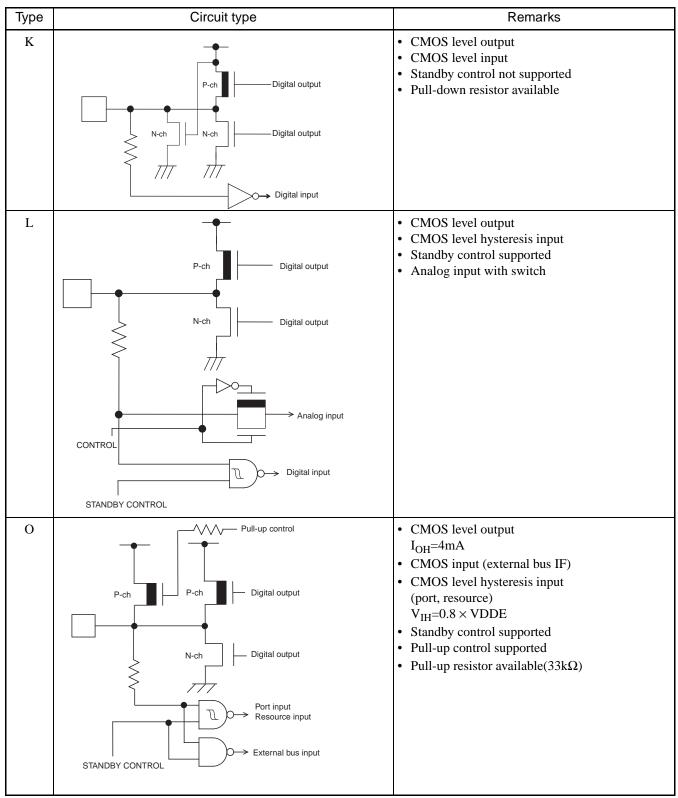

| 1.6    | I/O Circuit Types                                     | 16  |

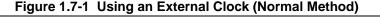

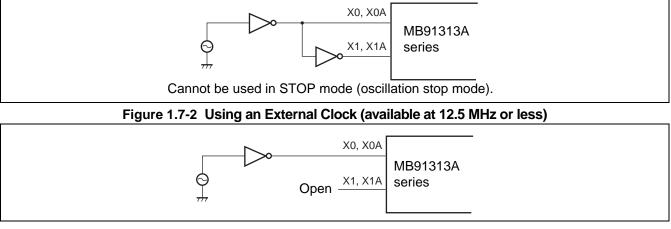

| 1.7    | Precautions on Handling the Device                    | 19  |

| СНАРТЕ | ER 2 CPU AND CONTROL BLOCK                            | 25  |

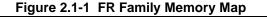

| 2.1    | Memory Space                                          | 26  |

| 2.2    | Internal Architecture                                 | 28  |

| 2.3    | Instructions                                          | 32  |

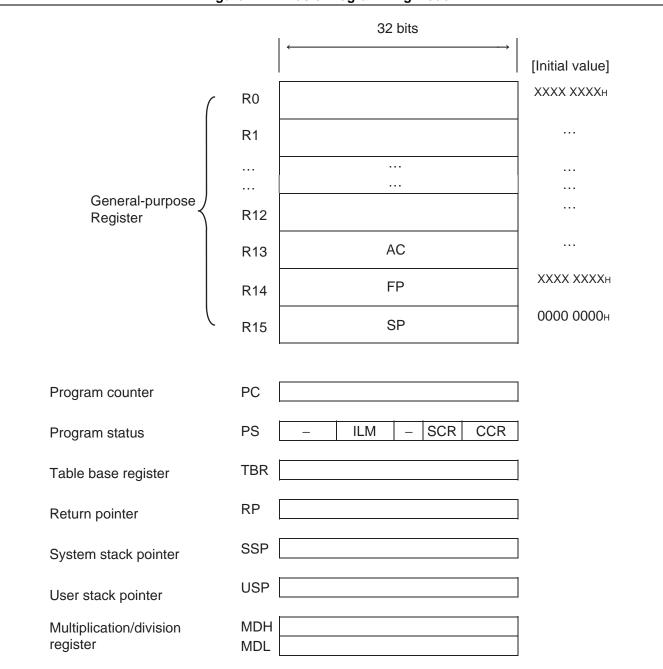

| 2.4    | Programming Model                                     | 34  |

| 2.4.1  | General-purpose Register                              | 35  |

| 2.4.2  | Dedicated Register                                    | 36  |

| 2.5    | Data Structure                                        | 43  |

| 2.6    | Branch Instruction                                    | 45  |

| 2.6.1  | Operation with a Delay Slot                           | 46  |

| 2.6.2  | Operation with No Delay Slot                          | 48  |

| 2.7    | EIT (Exception, Interruption, and Trap)               | 49  |

| 2.7.1  | EIT Interrupt Levels                                  | 50  |

| 2.7.2  | ICR (Interrupt Control Register)                      | 52  |

| 2.7.3  | SSP (System Stack Pointer)                            | 53  |

| 2.7.4  | TBR (Table Base Register)                             | 54  |

| 2.7.5  | Multiple EIT Processing                               | 58  |

| 2.7.6  | Operations of EIT                                     | 60  |

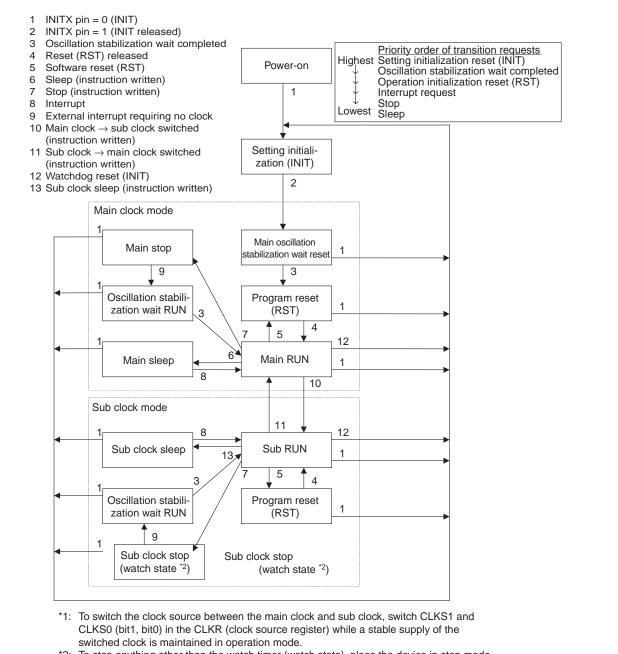

| 2.8    | Reset (Device Initialization)                         | 64  |

| 2.8.1  | Reset Level                                           | 65  |

| 2.8.2  | Reset Sources                                         | 66  |

| 2.8.3  | Reset Sequence                                        | 68  |

| 2.8.4  | Oscillation Stabilization Wait Time                   | 69  |

| 2.8.5  | Reset Operation Modes                                 | 71  |

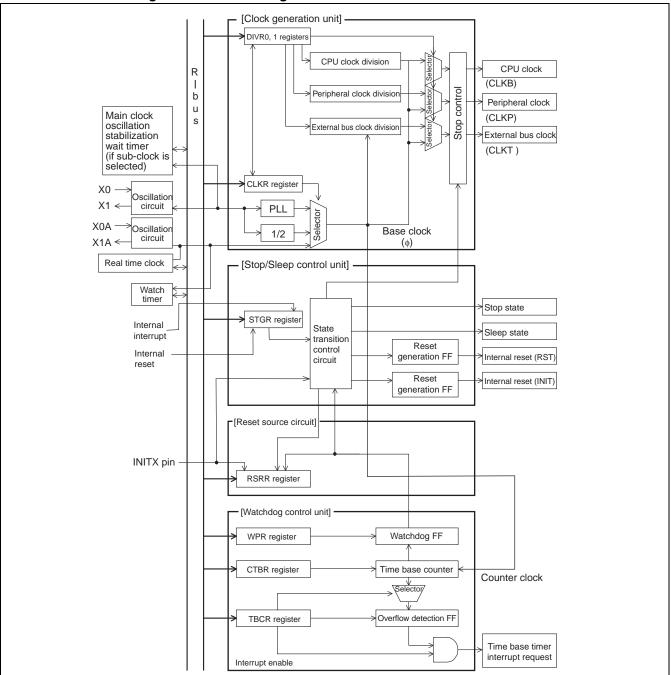

| 2.9    | Clock Generation Control                              | 73  |

| 2.9.1  | PLL Control                                           | 74  |

| 2.9.2  | Oscillation Stabilization Wait and PLL Lock Wait Time | 76  |

| 2.9.3  | Clock Distribution                                    | 78  |

| 2.9.4  | Clock Division                                        | 80  |

| 2.9.5  | Block Diagram of Clock Generation Control Block       | 81  |

| 2.9.6  | Registers of Clock Generation Control Block           | 82  |

| 2.9.7  | Peripheral Circuits in Clock Control Block 1          | 02  |

| 2.10   | Device State Control 1                                | 106 |

| 2.10.1 | 1 Low-power Consumption Mode 1                        | 10  |

| 2.11  | Operating Mode                                               | 115 |

|-------|--------------------------------------------------------------|-----|

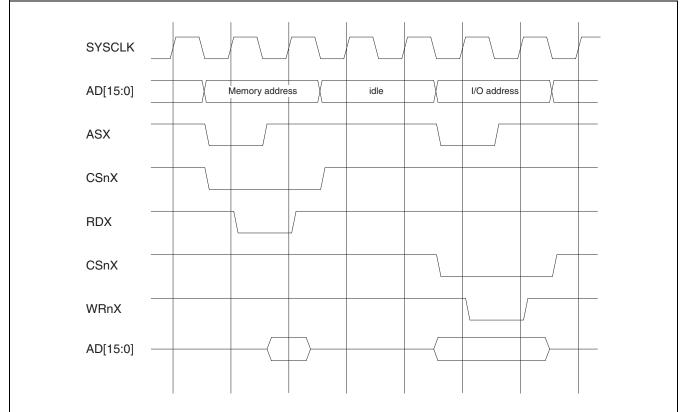

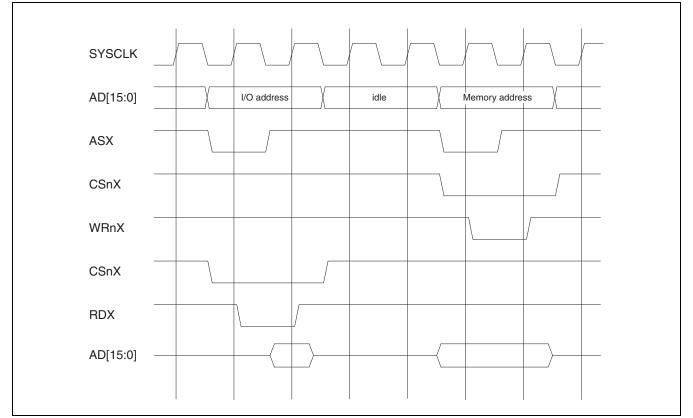

| СНАРТ | TER 3 EXTERNAL BUS INTERFACE                                 | 117 |

| 3.1   | Overview of External Bus Interface                           | 118 |

| 3.2   | Explanation of Registers of External Bus Interface           | 121 |

| 3.3   | Chip Select Area                                             | 132 |

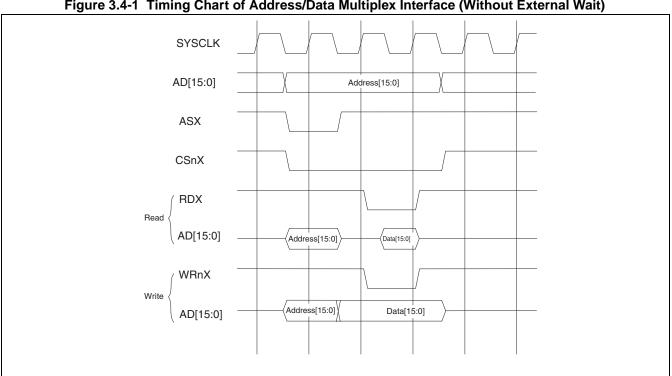

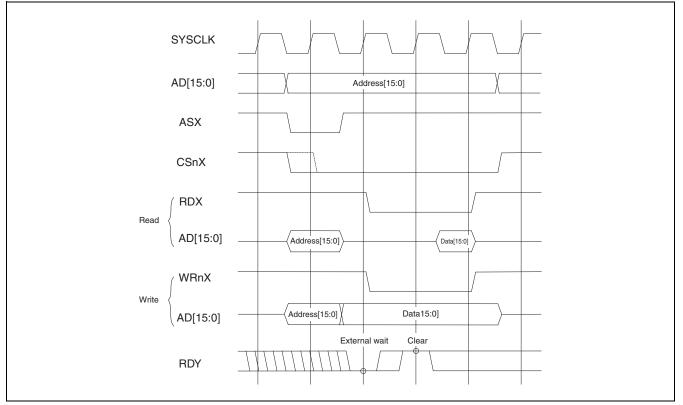

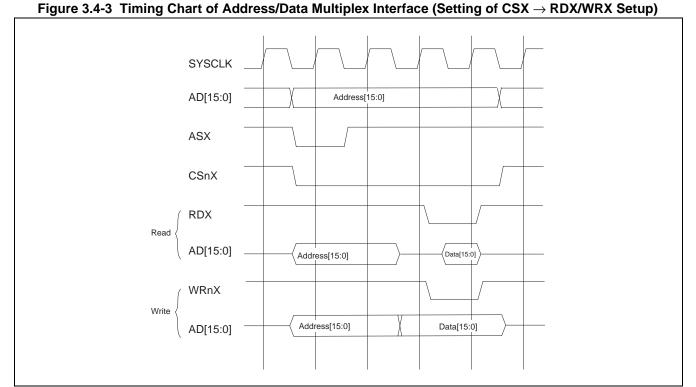

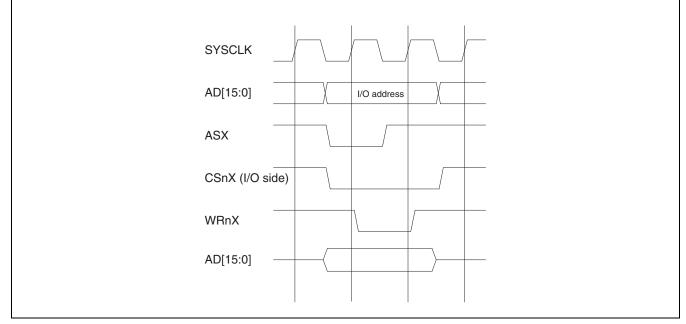

| 3.4   | Address/Data Multiplex Interface                             | 133 |

| 3.5   | DMA Access                                                   | 136 |

| 3.6   | Register Setting Procedure                                   | 139 |

| 3.7   | Note on Using External Bus Interface                         | 140 |

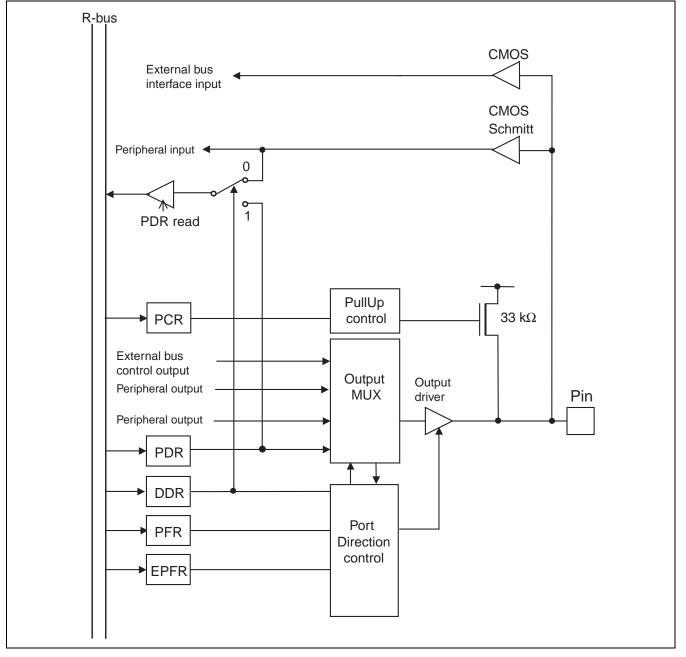

| СНАРТ | TER 4 I/O PORTS                                              | 141 |

| 4.1   | Overview of I/O Ports                                        | 142 |

| 4.2   | Settings of Port Data Registers                              | 144 |

| 4.3   | Settings of Data Direction Registers                         | 145 |

| 4.4   | Settings of Extra Port Control Registers                     | 146 |

| 4.5   | Pull-up Control Register                                     | 160 |

| 4.6   | External Bus, I <sup>2</sup> C Bridge, ADER Control Register | 161 |

| 4.7   | Noise Filter Control Register for I <sup>2</sup> C           | 162 |

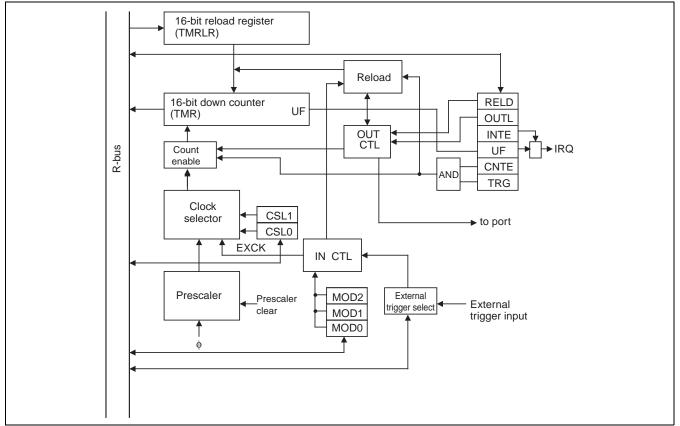

| CHAPT | TER 5 16-BIT RELOAD TIMER                                    | 163 |

| 5.1   | Overview of 16-Bit Reload Timer                              | 164 |

| 5.2   | Registers of 16-Bit Reload Timer                             | 165 |

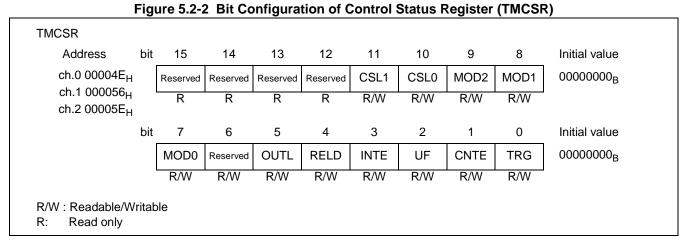

| 5.2.  | 1 Control Status Register (TMCSR)                            | 166 |

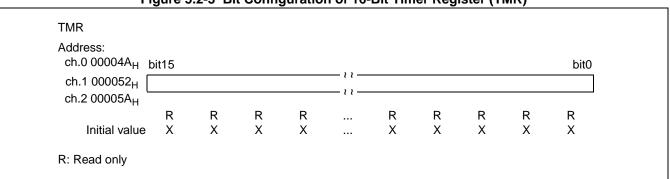

| 5.2.  | 2 16-Bit Timer Register (TMR)                                | 169 |

| 5.2.  | 3 16-Bit Reload Register (TMRLR)                             | 170 |

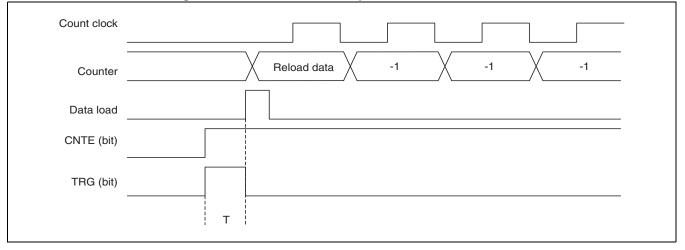

| 5.3   | Operations of 16-Bit Reload Timer                            | 171 |

| 5.4   | Operating Status of Counter                                  | 175 |

| 5.5   | Notes on Using 16-Bit Reload Timer                           | 176 |

| CHAPT | TER 6 PPG (PROGRAMMABLE PULSE GENERATOR)                     | 177 |

| 6.1   | Outline of the PPG Timer                                     | 178 |

| 6.2   | Operation of the PPG Timer                                   | 186 |

| 6.3   | Precautions on Using the PPG Timer                           | 189 |

| CHAPT | TER 7 16-BIT PULSE WIDTH COUNTER                             | 191 |

| 7.1   | Overview of the PWC Timer                                    | 192 |

| 7.2   | Operation of the PWC Timer                                   | 198 |

| CHAPT | TER 8 MULTIFUNCTION TIMER                                    | 201 |

| 8.1   | Overview of the Multifunction Timer                          | 202 |

| 8.2   | Registers of the Multifunction Timer                         | 204 |

| 8.3   | Multifunction Timer Operation                                |     |

| CHAPT | TER 9 OTHER TIMERS                                           | 217 |

| 9.1   | Main Oscillation Stabilization Wait Timer                    | 218 |

|       |                                                              |     |

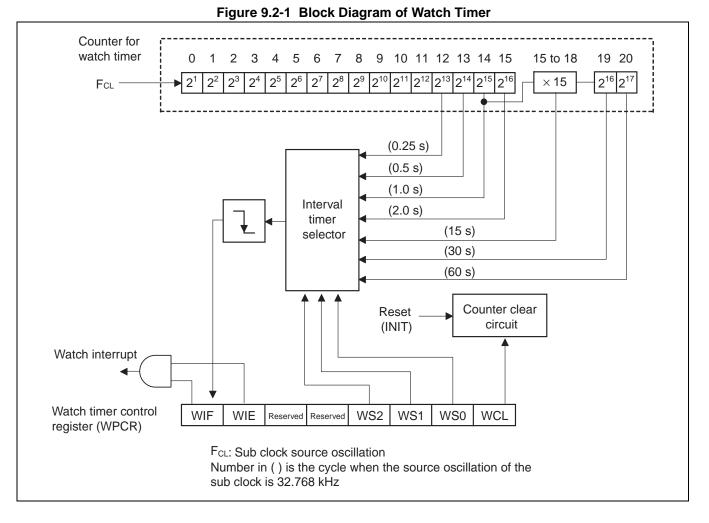

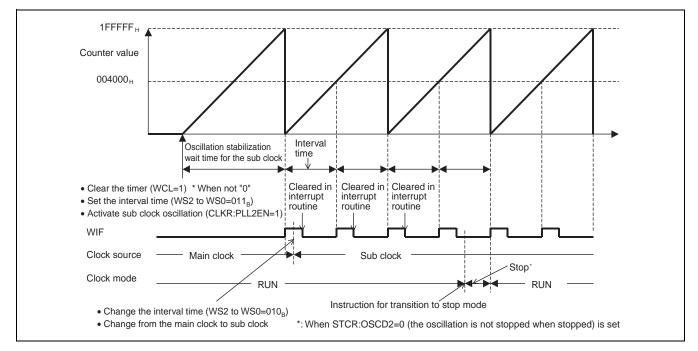

| 9.2   | Watch Timer                                                      | 225 |

|-------|------------------------------------------------------------------|-----|

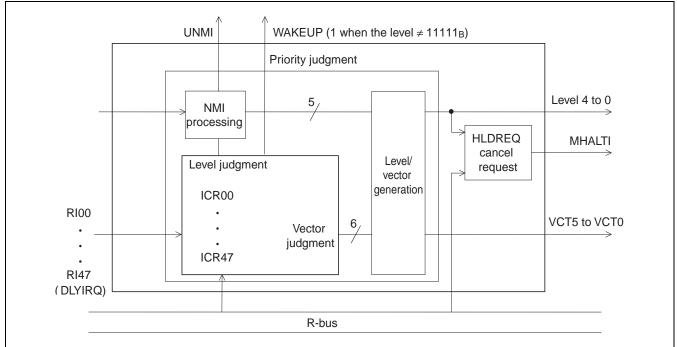

| СНАРТ | ER 10 INTERRUPT CONTROLLER                                       | 231 |

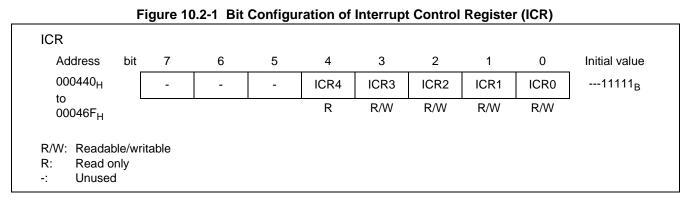

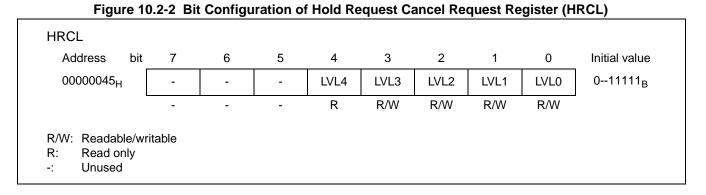

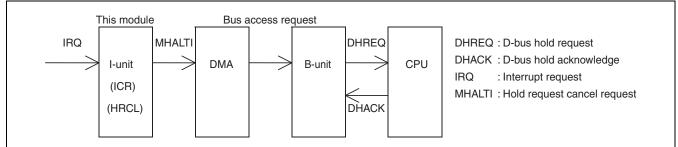

| 10.1  | Overview of Interrupt Controller                                 |     |

| 10.2  | Registers of Interrupt Controller                                |     |

| 10.2  |                                                                  |     |

| 10.2  |                                                                  |     |

| 10.3  | Operations of Interrupt Controller                               |     |

|       |                                                                  |     |

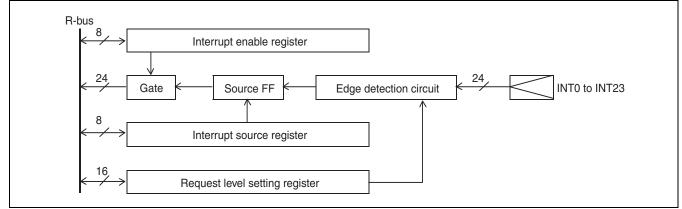

| CHAPT | ER 11 EXTERNAL INTERRUPT CONTROL UNIT                            | 243 |

| 11.1  | Overview of External Interrupt Control Unit                      | 244 |

| 11.2  | Registers of External Interrupt Control Unit                     | 245 |

| 11.2  | 1 Interrupt Enable Register (ENIR)                               | 246 |

| 11.2  | 2 External Interrupt Source Register (EIRR)                      | 247 |

| 11.2  | .3 External Interrupt Request Level Setting Register (ELVR)      | 248 |

| 11.3  | Operations of External Interrupt Control Unit                    |     |

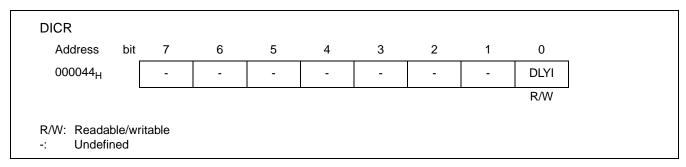

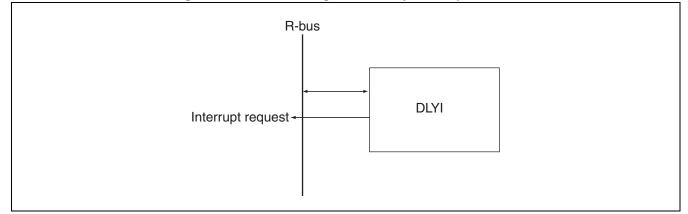

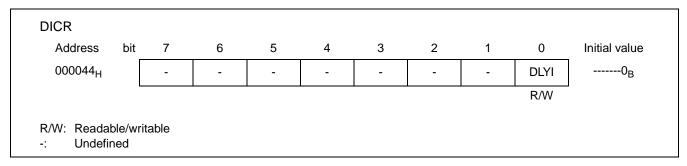

| снарт | ER 12 DELAY INTERRUPT MODULE                                     | 253 |

|       |                                                                  |     |

| 12.1  | Overview of Delay Interrupt Module                               |     |

| 12.2  | Registers of Delay Interrupt Module                              |     |

| 12.3  | Operations of Delay Interrupt Module                             | 250 |

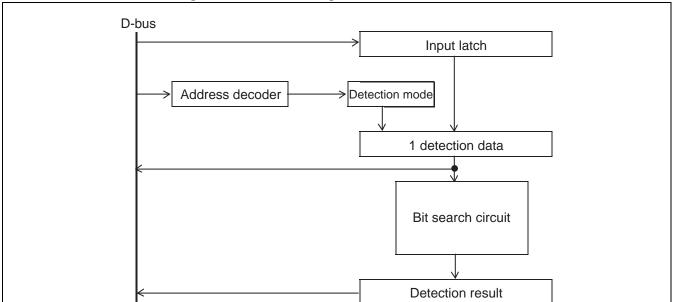

| СНАРТ | ER 13 BIT SEARCH MODULE                                          | 257 |

| 13.1  | Overview of Bit Search Module                                    | 258 |

| 13.2  | Registers of Bit Search Module                                   | 259 |

| 13.3  | Operations of Bit Search Module                                  | 261 |

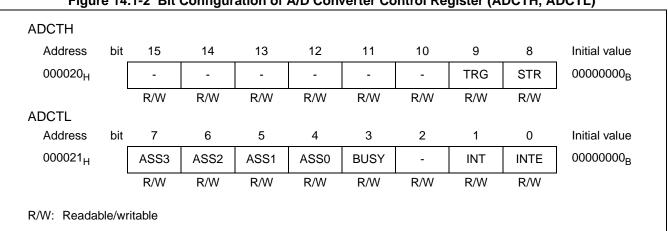

| СНАРТ | ER 14 10-BIT A/D CONVERTER                                       | 265 |

| 14.1  | Overview of the 10-Bit A/D Converter                             |     |

|       |                                                                  |     |

| CHAPT | ER 15 MULTI FUNCTION SERIAL INTERFACE                            | 273 |

| 15.1  | Overview of the Multi Function Serial Interface                  | 275 |

| 15.2  | Functions of UART (Asynchronous Multi Function Serial Interface) | 277 |

| 15.3  | Registers of UART (Asynchronous Multi Function Serial Interface) | 278 |

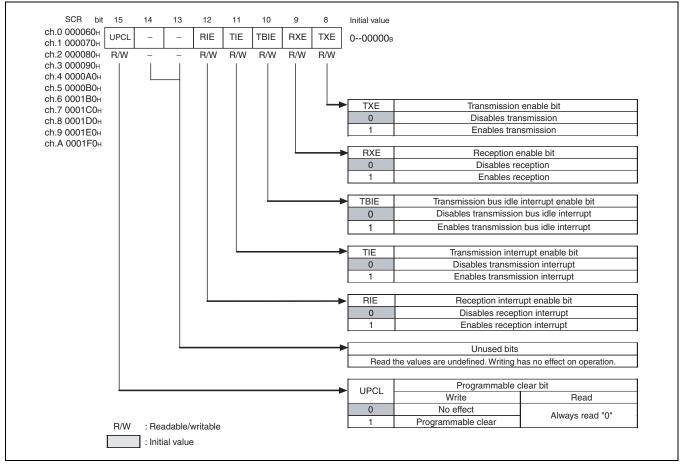

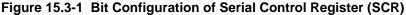

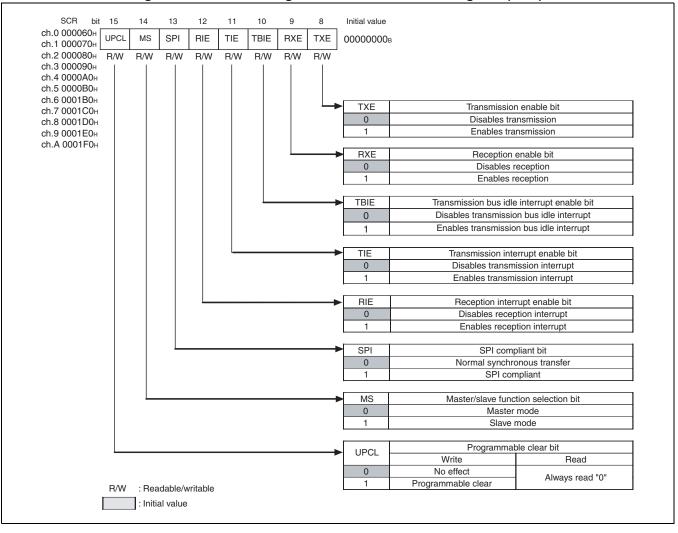

| 15.3  | 1 Serial Control Register (SCR)                                  | 280 |

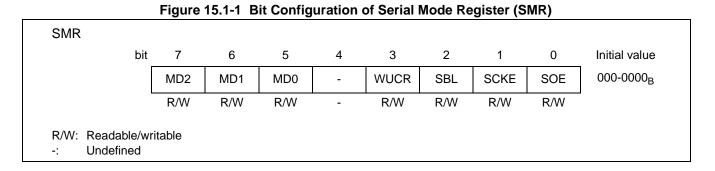

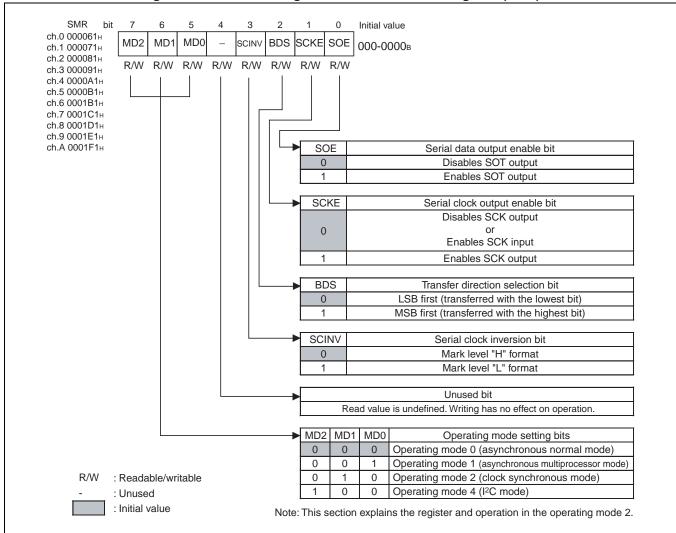

| 15.3  | 2 Serial Mode Register (SMR)                                     | 282 |

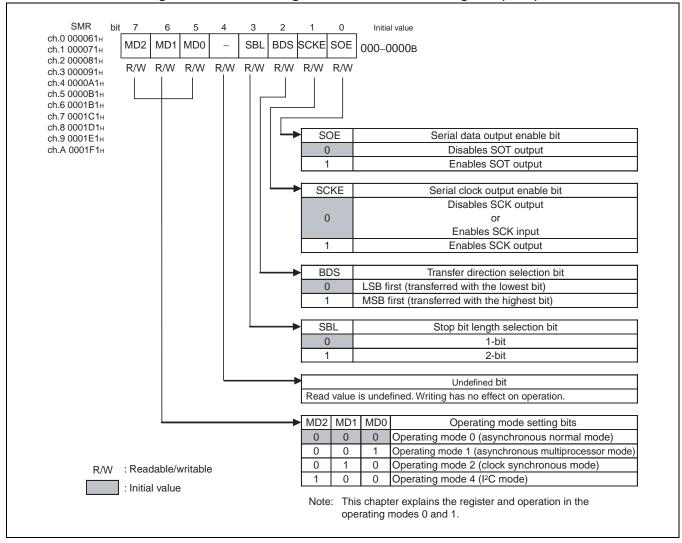

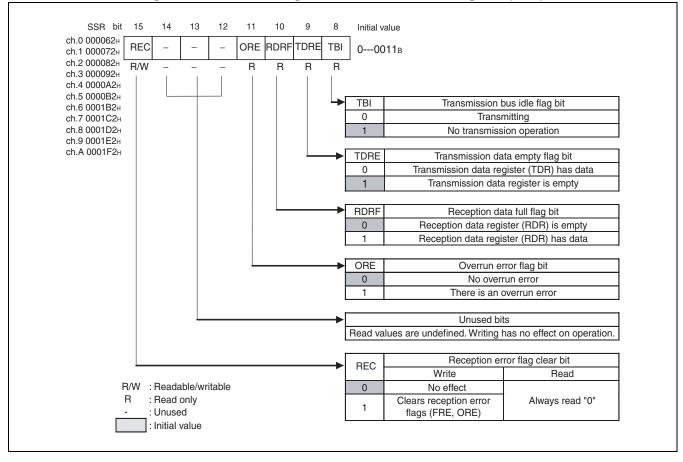

| 15.3  | 3 Serial Status Register (SSR)                                   | 284 |

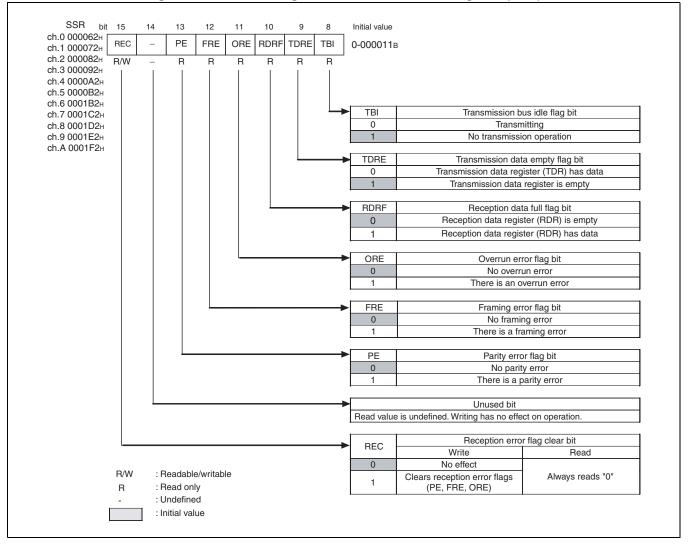

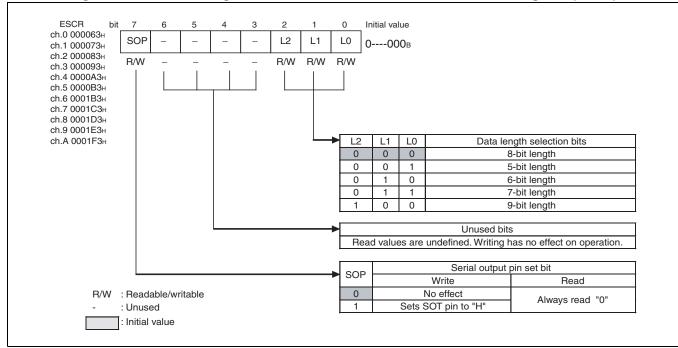

| 15.3  | 4 Extended Communication Control Register (ESCR)                 | 287 |

| 15.3  | .5 Reception/Transmission Data Registers (RDR/TDR)               | 289 |

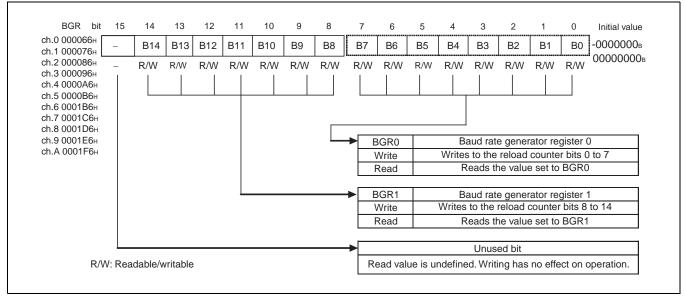

| 15.3  | 6 Baud Rate Generator Registers 1, 0 (BGR1/BGR0)                 | 293 |

| 15.3  |                                                                  |     |

| 15.3  |                                                                  |     |

| 15.3  |                                                                  |     |

| 15.4  | Interrupts of UART                                               |     |

| 15.4  | •                                                                |     |

| 15.4  |                                                                  |     |

| 15.4  |                                                                  |     |

| 15.4. | 4 Interrupt Generation and Flag Set Timing When Using Transmission FIFO                       | 308 |

|-------|-----------------------------------------------------------------------------------------------|-----|

| 15.5  | Operations of UART                                                                            | 309 |

| 15.6  | UART Dedicated Baud Rate Generator                                                            | 314 |

| 15.6. | 1 Baud Rate Setting                                                                           | 315 |

| 15.7  | Setting Procedure and Program Flow for Operating Mode 0 (Asynchronous Normal Mode)            | 319 |

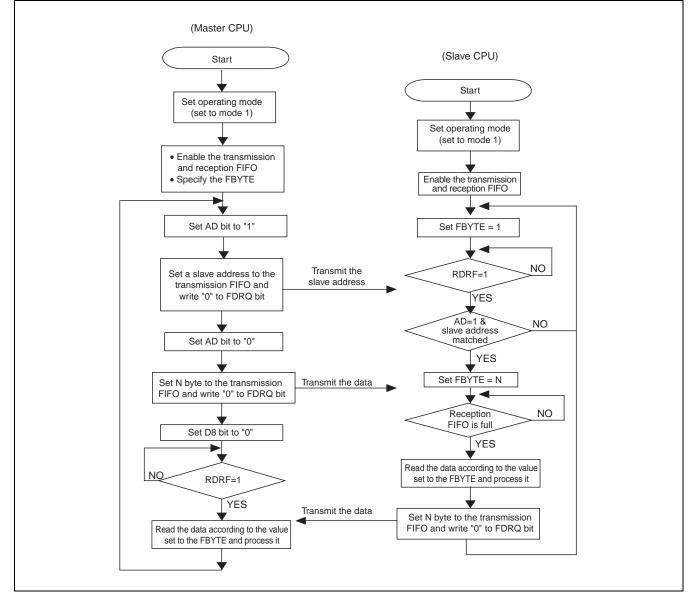

| 15.8  | Setting Procedure and Program Flow for Operating Mode 1 (Asynchronous Multiprocessor Mode     |     |

| 45.0  |                                                                                               |     |

| 15.9  | Notes on UART Mode                                                                            |     |

| 15.10 | Overview of CSIO (Clock Synchronous Multi Function Serial Interface)                          |     |

|       | Registers of CSIO (Clock Synchronous Multi Function Serial Interface)                         |     |

|       | .1 Serial Control Register (SCR)                                                              |     |

|       | .2 Serial Mode Register (SMR)                                                                 |     |

|       | .3 Serial Status Register (SSR)                                                               |     |

|       | .4 Extended Communication Control Register (ESCR)                                             |     |

|       | .5 Reception Data Register/Transmission Data Register (RDR/TDR)                               |     |

|       | .6 Baud Rate Generator Registers 1, 0 (BGR1/BGR0)                                             |     |

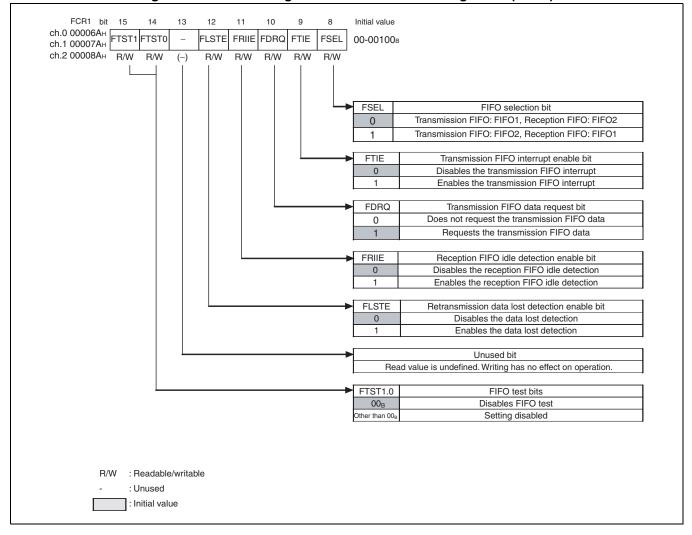

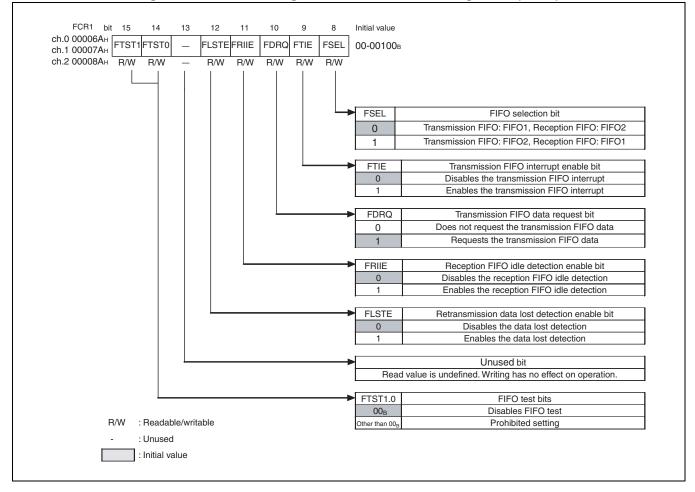

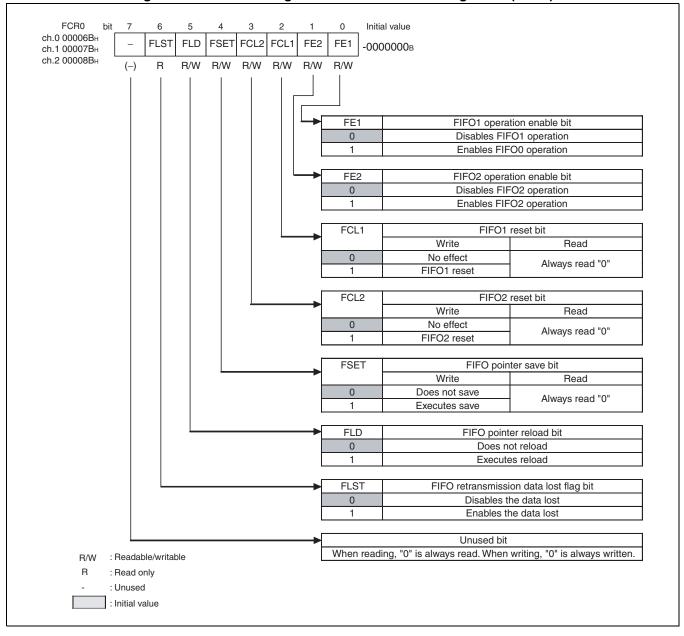

|       | .7 FIFO Control Register 1 (FCR1)                                                             |     |

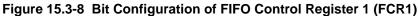

|       | .8 FIFO Control Register 0 (FCR0)                                                             |     |

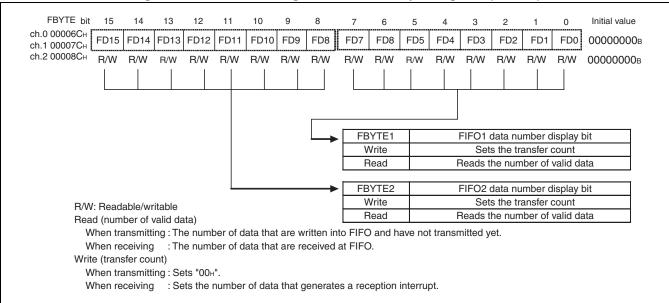

|       | .9 FIFO Byte Register (FBYTE)                                                                 |     |

|       | Interrupts of CSIO (Clock Synchronous Multi Function Serial Interface)                        |     |

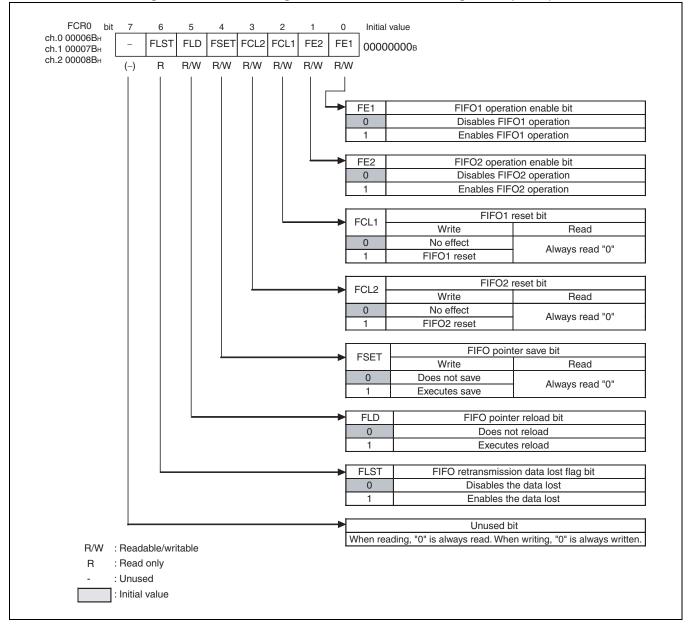

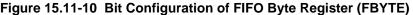

|       | 2.1 Reception Interrupt Generation and Flag Set Timing                                        |     |

|       | 2.2 Interrupt Generation and Flag Set Timing When Using Reception FIFO                        |     |

|       | 2.3 Transmission Interrupt Generation and Flag Set Timing                                     |     |

|       | 2.4 Interrupt Generation and Flag Set Timing When Using Transmission FIFO                     |     |

|       | Operations of CSIO (Clock Synchronous Multi Function Serial Interface)                        |     |

|       | CSIO Dedicated Baud Rate Generator                                                            |     |

|       | Setting Procedure and Program Flow for CSIO (Clock Synchronous Multi Function Serial Interfac |     |

| 15.15 |                                                                                               | ,   |

| 15.16 | Notes on CSIO Mode                                                                            |     |

| 15.17 |                                                                                               |     |

| 15.18 | Registers of the I <sup>2</sup> C Interface                                                   |     |

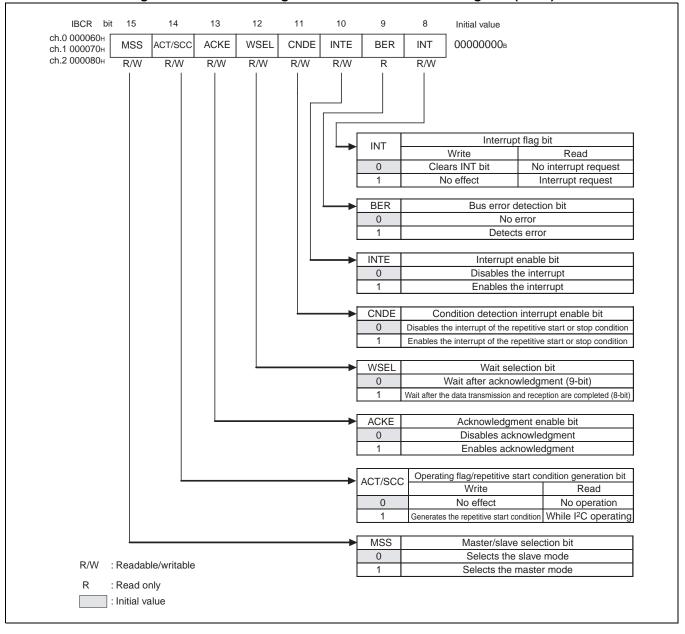

|       | B.1 I <sup>2</sup> C Bus Control Register (IBCR)                                              |     |

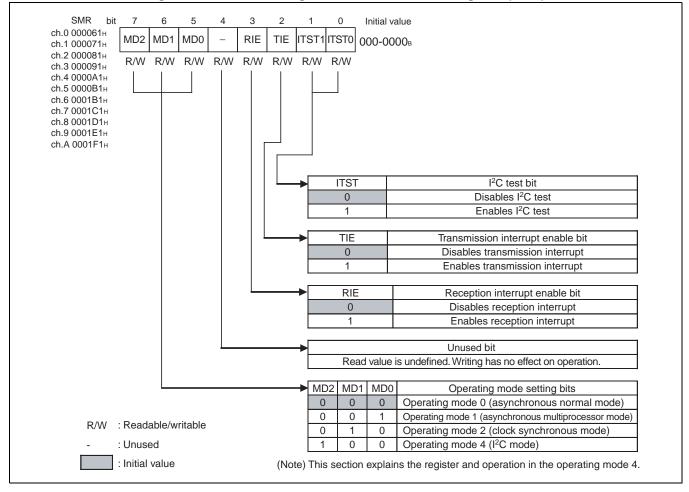

|       | 3.2 Serial Mode Register (SMR)                                                                |     |

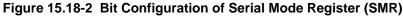

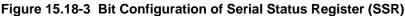

|       | 3.3 Serial Status Register (SSR)                                                              |     |

|       | 3.4 I <sup>2</sup> C Bus Status Register (IBSR)                                               |     |

|       | 3.5 Reception/Transmission Data Registers (RDR/TDR)                                           |     |

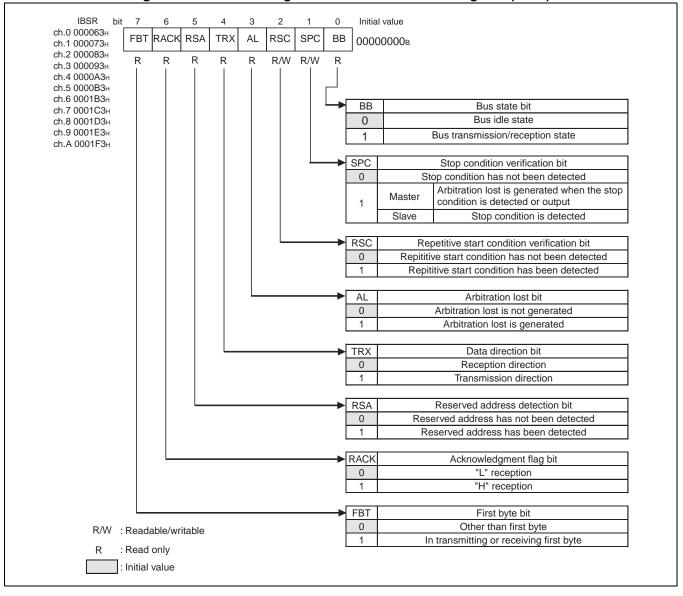

|       | B.6 Baud Rate Generator Registers 1, 0 (BGR1/BGR0)                                            |     |

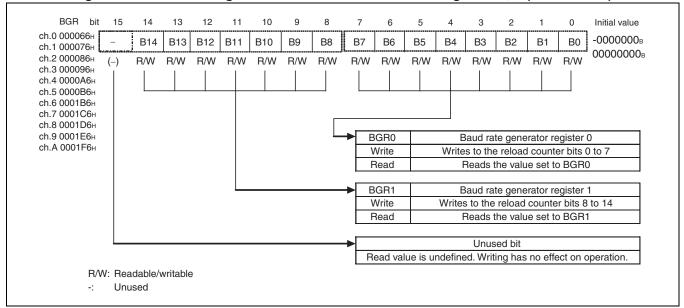

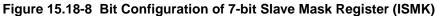

|       | 3.7 7-bit Slave Address Mask Register (ISMK)                                                  |     |

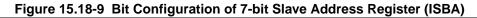

|       | 3.8 7-bit Slave Address Register (ISBA)                                                       |     |

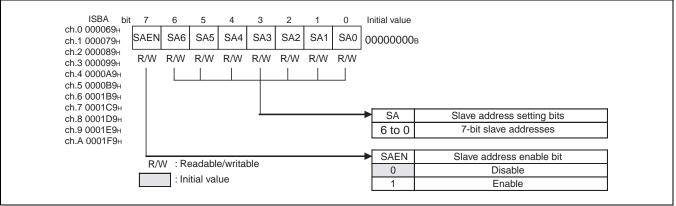

|       | 3.9 FIFO Control Register 1 (FCR1)                                                            |     |

| 15.18 | 3.10 FIFO Control Register 0 (FCR0)                                                           | 397 |

|       | 3.11 FIFO Byte Register (FBYTE)                                                               |     |

|       | Interrupts of the I <sup>2</sup> C Interface                                                  |     |

|       | Operations of I <sup>2</sup> C Interface Communication                                        |     |

|       | .1 Master Mode                                                                                |     |

| 15.20 | 0.2 Slave Mode                                                                                | 424 |

| 15.20 | 0.3 Bus Error                                                                                 | 428 |

|       |                                                                                               |     |

| 15.21 | Dedicated Baud Rate Generator                                               | 429 |

|-------|-----------------------------------------------------------------------------|-----|

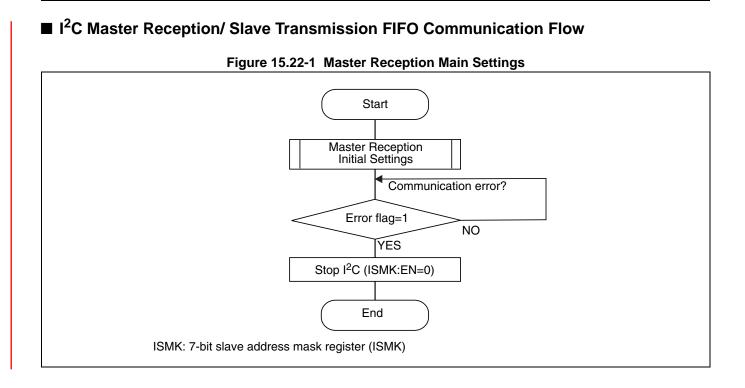

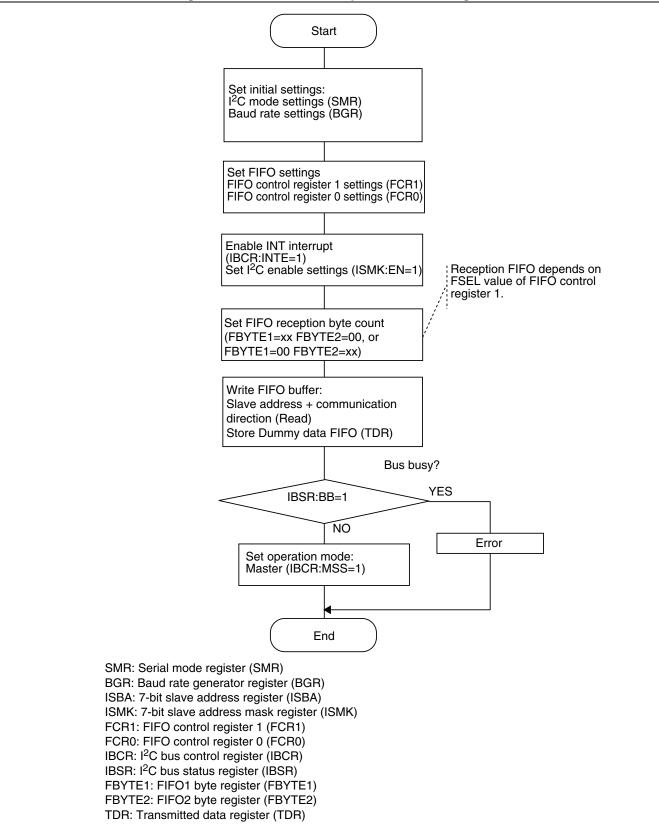

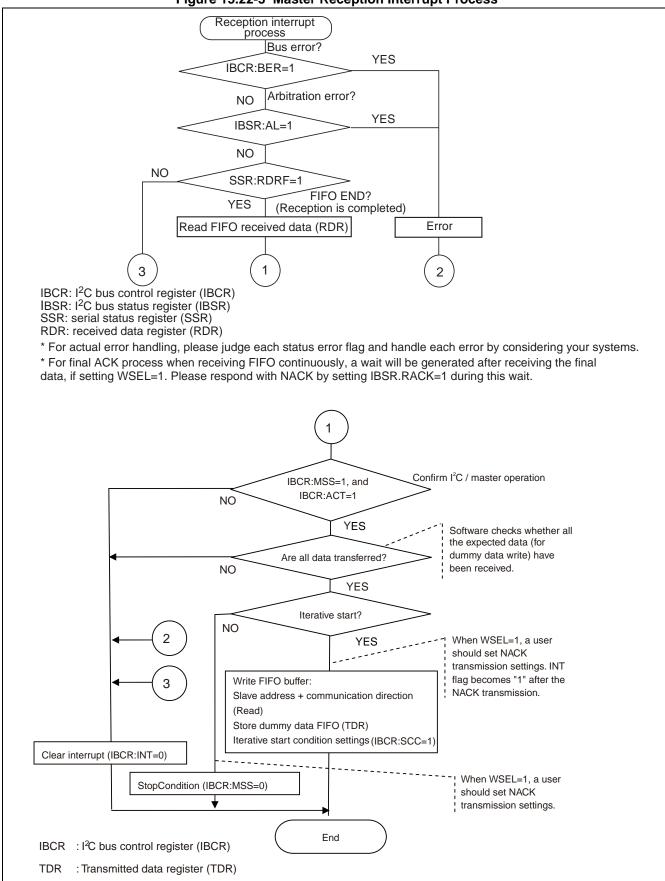

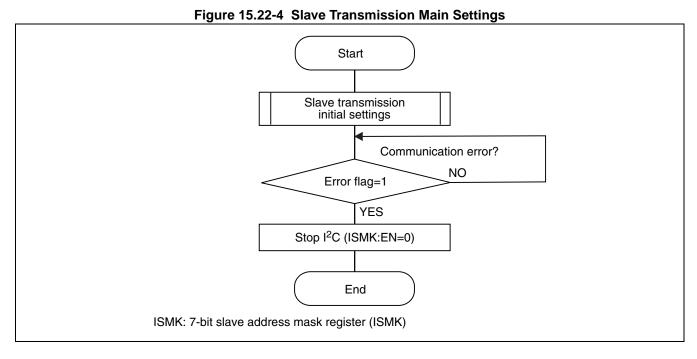

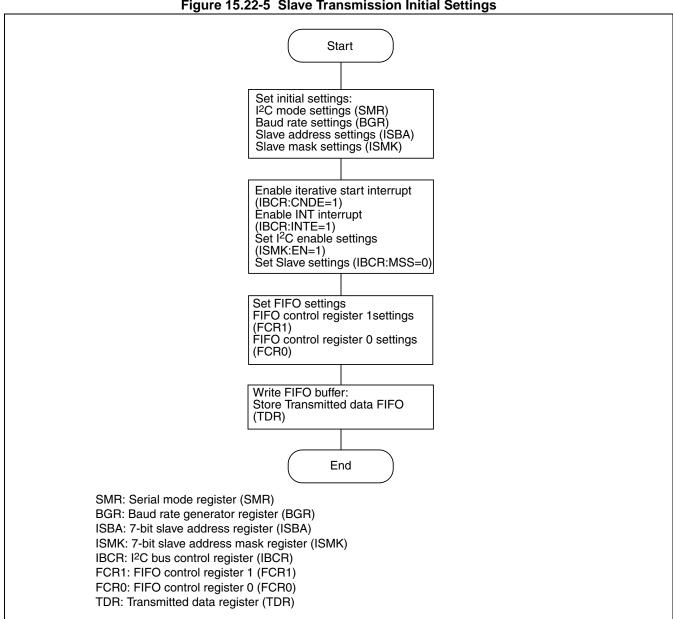

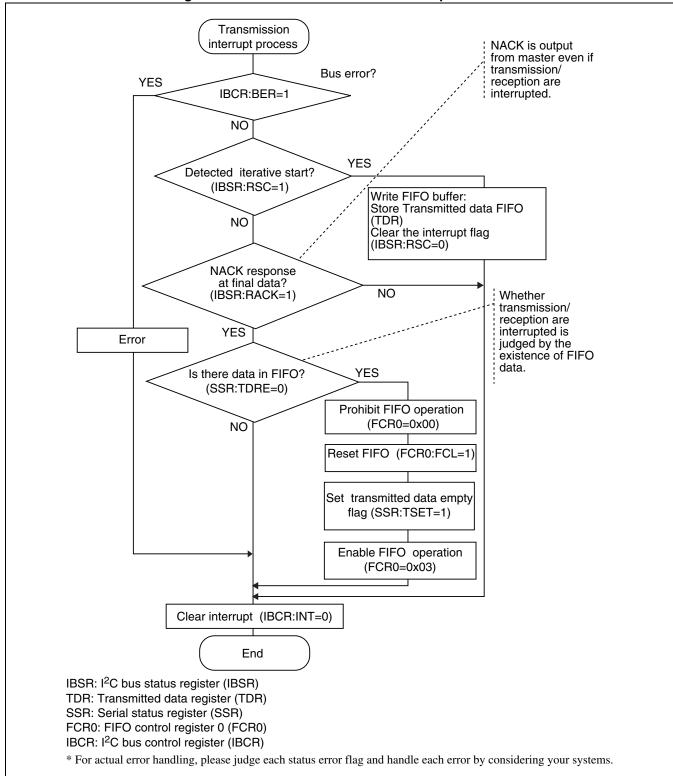

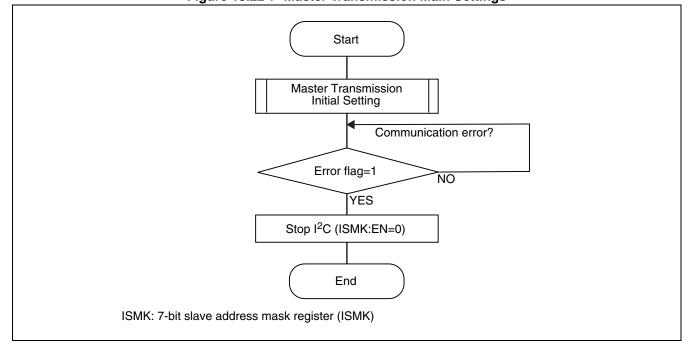

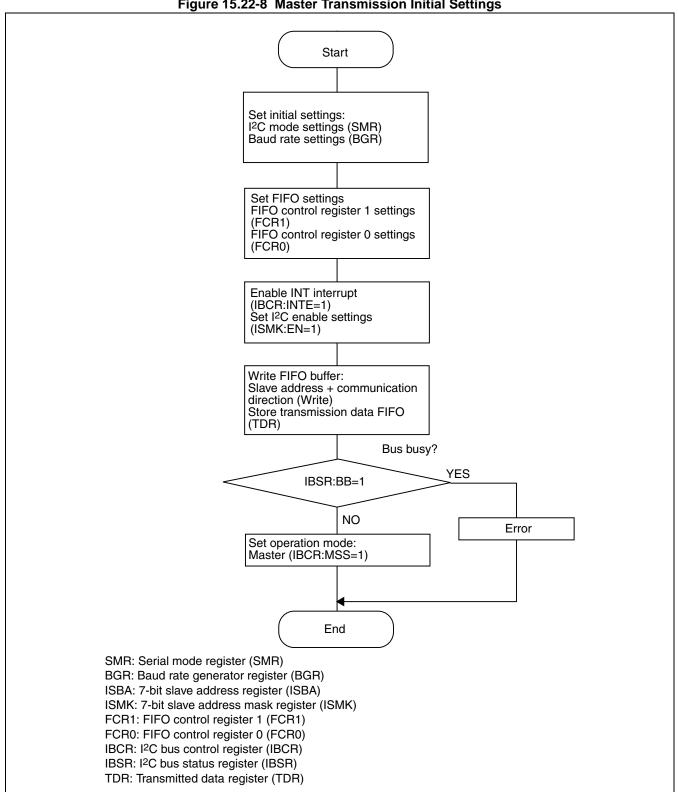

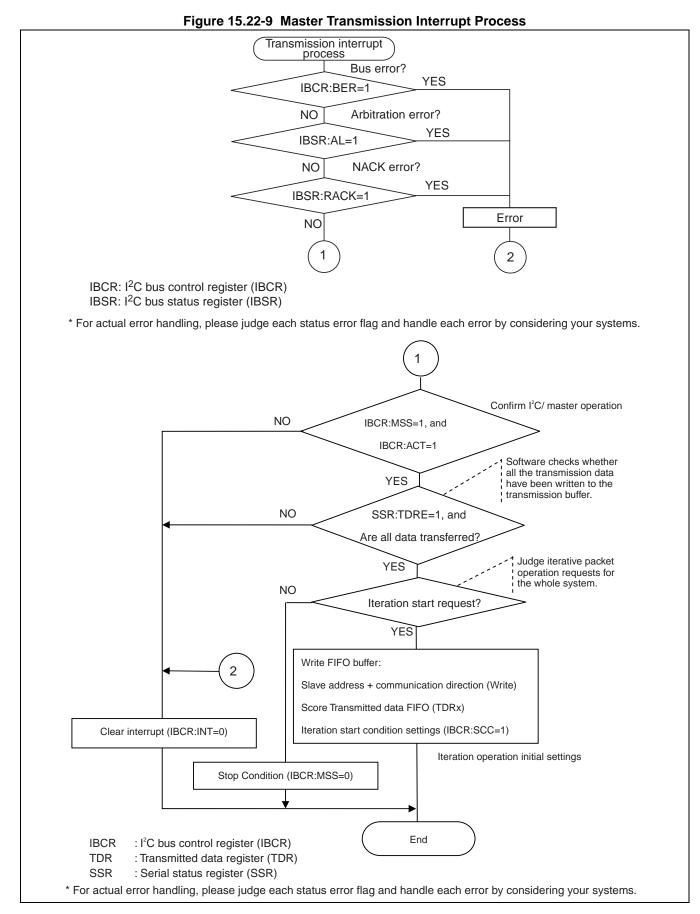

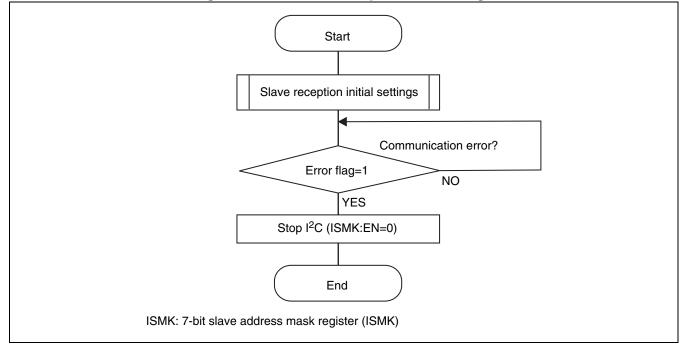

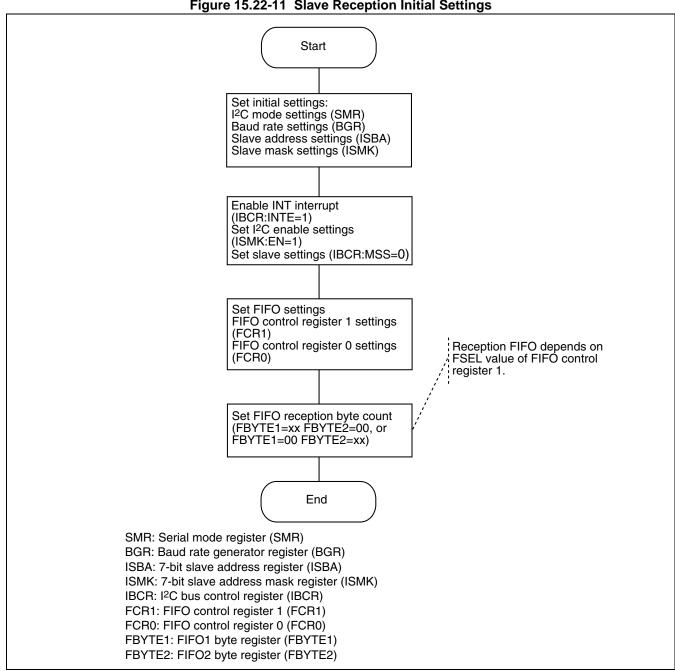

| 15.22 | Examples of I <sup>2</sup> C Flowchart                                      | 431 |

| 15.23 | Notes on I <sup>2</sup> C Mode                                              | 443 |

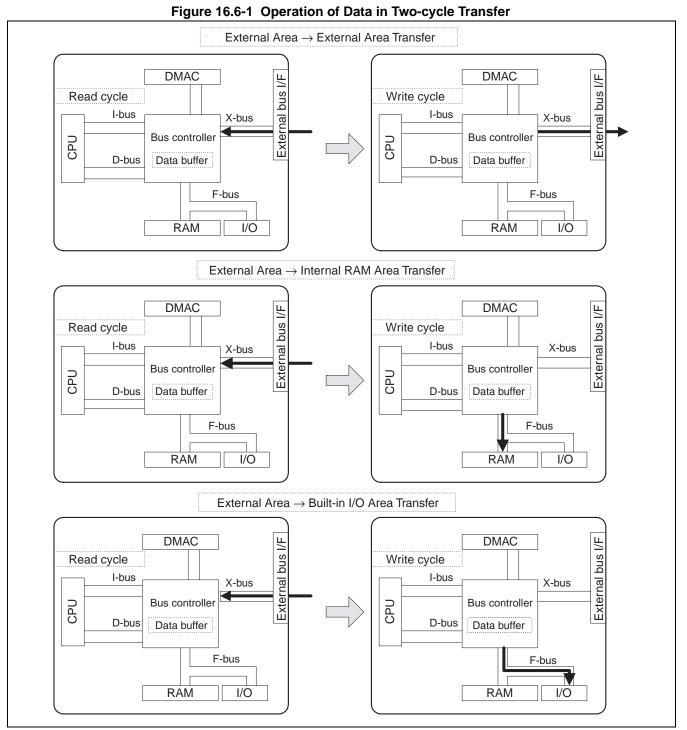

| CHAPT | ER 16 DMAC (DMA CONTROLLER)                                                 | 445 |

| 16.1  | Overview of DMA Controller                                                  |     |

| 16.2  | Operations of DMA Controller                                                |     |

| 16.3  | Setting of Transfer Request                                                 |     |

| 16.4  | Transfer Sequence                                                           | 466 |

| 16.5  | Operation Flowcharts                                                        | 477 |

| 16.6  | Data Bus                                                                    | 479 |

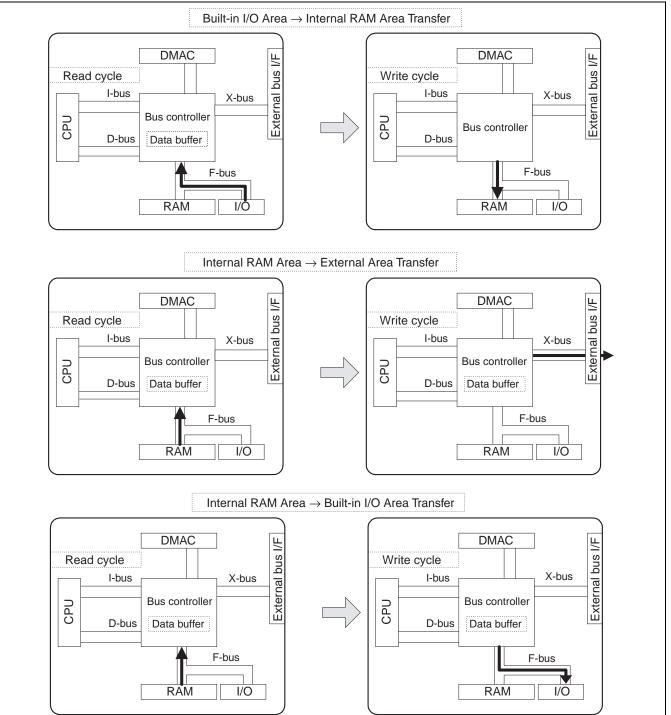

| СНАРТ | ER 17 REMOTE CONTROL RECEPTION                                              | 481 |

| 17.1  | Overview of Remote Control Reception                                        |     |

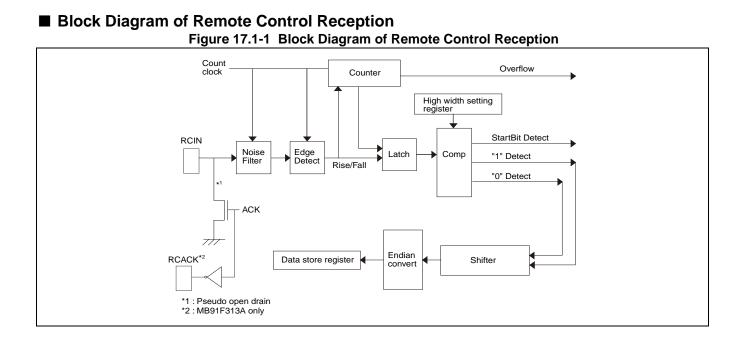

| 17.2  | Register of Remote Control Reception                                        |     |

| 17.2. | -                                                                           |     |

| 17.2. |                                                                             |     |

| 17.2. |                                                                             |     |

| 17.2. |                                                                             |     |

| 17.2. |                                                                             |     |

| 17.2. | $\mathbf{c}$                                                                |     |

| 17.2. |                                                                             |     |

| 17.2. |                                                                             |     |

| 17.3  | Explanation of Operations and Setting Procedure Examples                    |     |

|       | ER 18 FLASH MEMORY                                                          | 400 |

|       |                                                                             |     |

| 18.1  | Outline of Flash Memory                                                     |     |

| 18.2  | Flash Memory Registers                                                      |     |

| 18.2. | 5 ( )                                                                       |     |

| 18.2. | 5 ( )                                                                       |     |

| 18.3  | Flash Memory Access Modes                                                   |     |

| 18.4  | Automatic Algorithm of Flash Memory                                         |     |

| 18.5  | Execution Status of the Automatic Algorithm                                 |     |

| 18.6  | Data Writing to and Erasing from Flash Memory                               |     |

| 18.6. |                                                                             |     |

| 18.6. |                                                                             |     |

| 18.6. | 5 ( 1 )                                                                     |     |

| 18.6. | 5                                                                           |     |

| 18.6. |                                                                             |     |

| 18.6. |                                                                             |     |

| 18.7  | Restrictions on Data Polling Flag (DQ7) and How to Avoid Erroneous Judgment |     |

| 18.8  | Restriction and Notes                                                       | 531 |

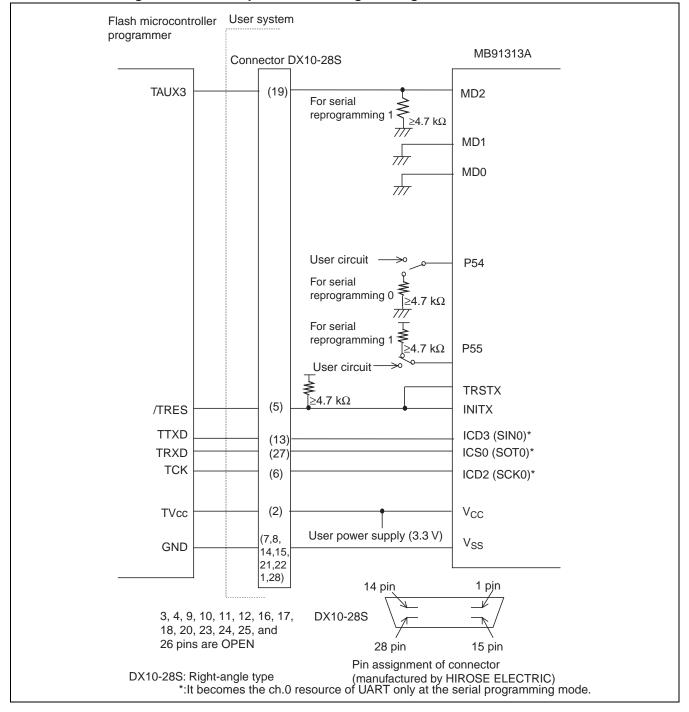

| CHAPT | ER 19 MB91313A SERIAL PROGRAMMING CONNECTION                                | 533 |

| 19.1  | Basic Configuration of Serial Programming                                   | 534 |

| 19.2  | Example of Serial Programming Connection                                    | 536 |

ix

System Configuration of Flash Microcontroller Programmer ...... 537

19.3

| 19.4 Additional Notes                   | 538 |

|-----------------------------------------|-----|

| APPENDIX                                | 539 |

| APPENDIX A I/O Map                      | 540 |

| APPENDIX B Vector Table                 | 551 |

| APPENDIX C Pin Status In Each CPU State |     |

| APPENDIX D Instruction Lists            | 566 |

| INDEX                                   | 581 |

## Main changes in this edition

| Page          | Section                                                                                       | Change Results                                                                                                        |

|---------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| -             | -                                                                                             | Changed Series name.<br>MB91313/A → MB91313A                                                                          |

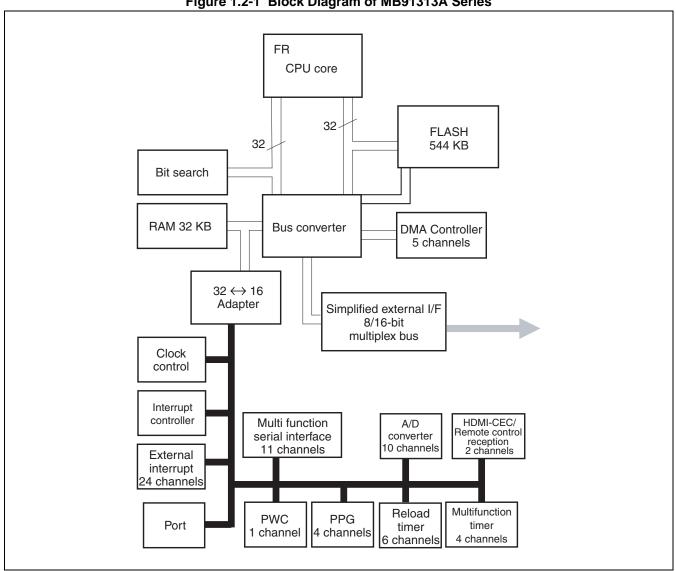

| 5             | CHAPTER 1 OVERVIEW<br>1.2 Block Diagram                                                       | Changed Figure 1.2-1.                                                                                                 |

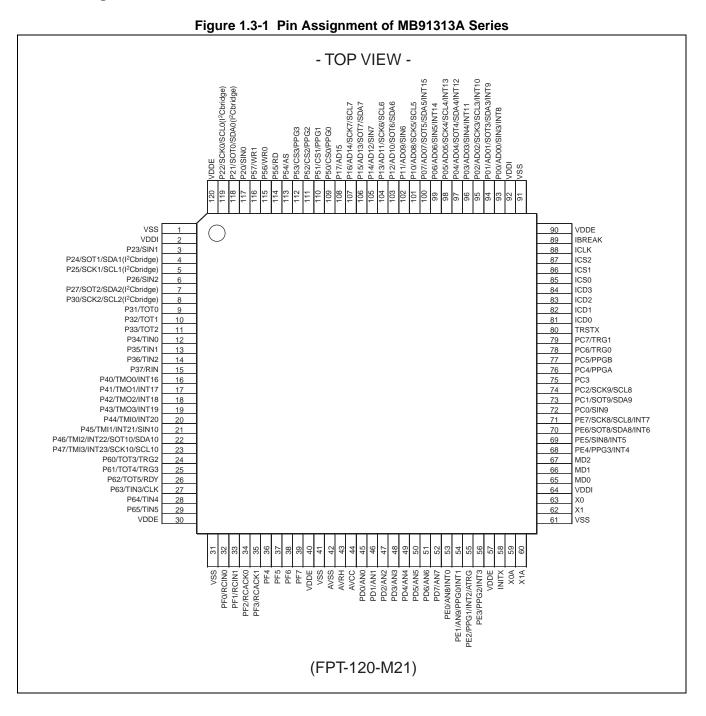

| 6             | CHAPTER 1 OVERVIEW<br>1.3 Pin Assignment                                                      | Corrected Figure 1.3-1.                                                                                               |

| 10            | CHAPTER 1 OVERVIEW<br>1.5 List of Pin Functions                                               | Corrected Table 1.5-1.<br>I/O circuit type of pin number 32, 33<br>$D/B \rightarrow B$                                |

| 20            | CHAPTER 1 OVERVIEW<br>1.7 Precautions on Handling the Device                                  | Added The explanation.<br>Turning on/off these power supplies (VDDI/Analog/VDDE)<br>simultaneously causes no problem. |

| 23            |                                                                                               | Deleted "• External interrupt INT17, INT19 (MB91F313 only)".                                                          |

| 166           | CHAPTER 5 16-BIT RELOAD TIMER<br>5.2.1 Control Status Register (TMCSR)                        | Corrected Figure 5.2-2.                                                                                               |

| 325           | CHAPTER 15 MULTI FUNCTION SERIAL<br>INTERFACE<br>15.9 Notes on UART Mode                      | Added Item.                                                                                                           |

| 373           | CHAPTER 15 MULTI FUNCTION SERIAL<br>INTERFACE<br>15.16 Notes on CSIO Mode                     | Added Item.                                                                                                           |

| 431 to<br>442 | CHAPTER 15 MULTI FUNCTION SERIAL<br>INTERFACE<br>15.22 Examples of I <sup>2</sup> C Flowchart | Corrected Flowchart.                                                                                                  |

| 443,<br>444   | CHAPTER 15 MULTI FUNCTION SERIAL<br>INTERFACE<br>15.23 Notes on I <sup>2</sup> C Mode         | Added Item.                                                                                                           |

| 499 to<br>531 | CHAPTER 18 FLASH MEMORY                                                                       | The overall revision.                                                                                                 |

The vertical lines marked in the left side of the page show the changes.

# CHAPTER 1 OVERVIEW

This chapter explains the features and basic specification of the MB91313A series.

- 1.1 Features

- 1.2 Block Diagram

- 1.3 Pin Assignment

- 1.4 Package Dimensions

- 1.5 List of Pin Functions

- 1.6 I/O Circuit Types

- 1.7 Precautions on Handling the Device

### 1.1 Features

The FR family is a line of microcontrollers based on a 32-bit high-performance RISC CPU and integrating a variety of I/O resources for embedded control applications which require high-performance, high-speed processing by the CPU.

The microcontrollers are equipped with the multiple channels of the communication macro and most suitable for embedded applications such as television control.

#### FR CPU

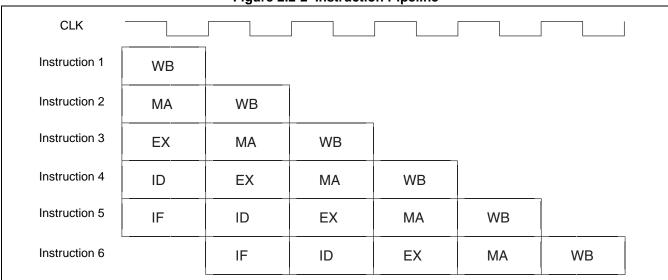

- 32-bit RISC, load/store architecture, 5-stage pipeline

- Operating frequency of 33 MHz [PLL used: 16.5-MHz oscillation frequency: multiply by 2]

- 16-bit fixed-length instructions (basic instructions), one instruction per cycle

- Memory-to-memory transfer, bit manipulation, barrel shift, and other instructions ... Instructions appropriate for embedded applications

- Function entry/exit instructions, multi-register load/store instructions ... Instructions compatible with high-level languages

- Register interlock function ... Facilitating assembly-language coding

- Built-in multiplier/instruction-level support: Signed 32-bit multiplication ... 5 cycles

Signed 16-bit multiplication ... 3 cycles

- Interrupts (saving of PC and PS) ... 6 cycles, 16 priority levels

- · Harvard architecture enabling simultaneous execution of program access and data access

- 4 words queuing in CPU enabling advanced fetch of instructions

- Instruction-compatible with the FR family

#### Simplified External Bus Interface

Setting in the program enables the 8-bit or 16-bit multiplex bus to run.

- Maximum operating frequency of 16.5 MHz

- 8-/16- bit data/address multiplex I/O

- Totally independent 4-area chip select output that can be defined at a minimum of 64 KB

- Basic bus cycle ... 3 cycles

- Automatic wait cycle generator that can be programmed for each area

- Unused data/address/control signal pins can be used for general-purpose I/O

#### Built-in Memory

• Flash memory 544 KB, RAM/32 KB

#### DMAC (DMA Controller)

- 5 channels

- 2 transfer sources: internal peripheral/software

- Addressing mode: 20/24-bit full address specifications (increase/decrease/fixed)

- Transfer mode: burst transfer/step transfer/block transfer

- Transfer data size: can be selected from 8, 16, or 32 bits

#### ■ Bit Search Module (Used by REALOS)

Searches for the position of the first bit varying between 1 and 0 in the MSB of a word.

#### ■ 16-bit Reload Timer (Including One Channel for REALOS)

- 6 channels

- Internal clock: selectable from among results of dividing the machine clock frequency by 2, 8, and 32

#### Multi Function Serial Interface

- 11 channels

- Full-duplex double buffer

- 4 types communication mode: asynchronous (start-stop synchronous), clock-synchronous communication (maximum 8.25 Mbps), I<sup>2</sup>C standard mode (maximum 100 kbps), and I<sup>2</sup>C high-speed mode (maximum 400 kbps)

- Parity selectable from enabled or disabled

- Built-in baud rate generator for each channel

- Various error detection functions: parity, frame, overrun

- External clock that can be used as transfer clock

- ch.0 to ch.2 : the DMA transfer / the FIFO function with 16 bytes for each of the transmission and reception

- ch.8 to ch.10 : 5-V tolerant.

- ch.8 : the open drain output

- I<sup>2</sup>C bridge function (among 0 channel, 1 channel, and 2 channel)

- SPI mode

#### Interrupt Controller

- Total of 24 external interrupts (external interrupt pins INT23 to INT0)

- Interrupts from internal peripherals

- Programmable priority level (16 levels)

- Available for wakeup in STOP mode

#### 10-bit A/D Converter

- 10 channels

- Successive approximation type: conversion time : approximately 7.94 µs

- Conversion modes: single conversion mode and scan conversion mode

- Activation sources: software and external trigger

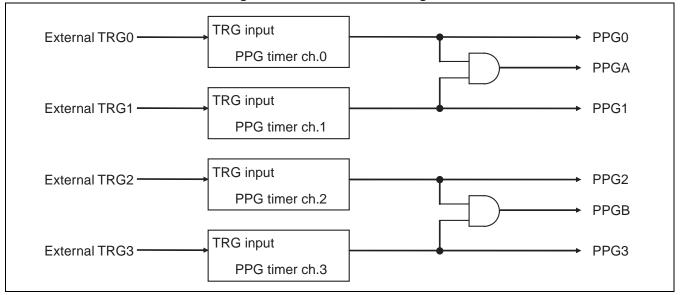

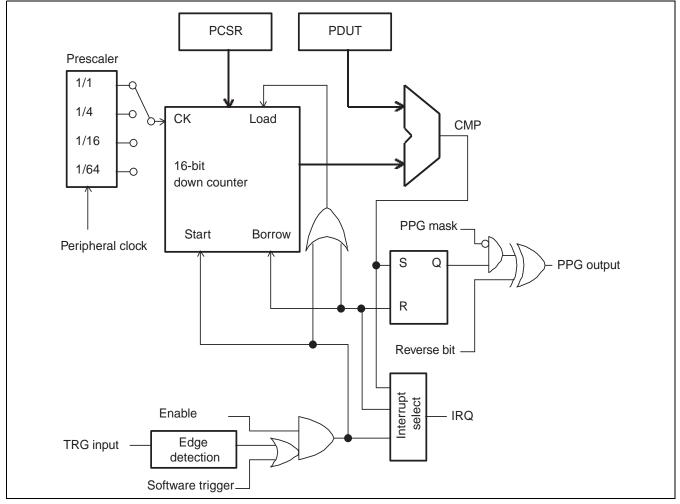

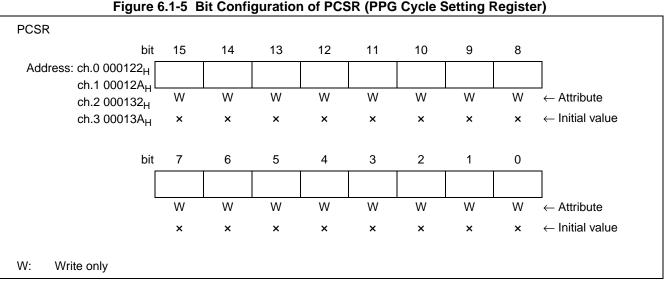

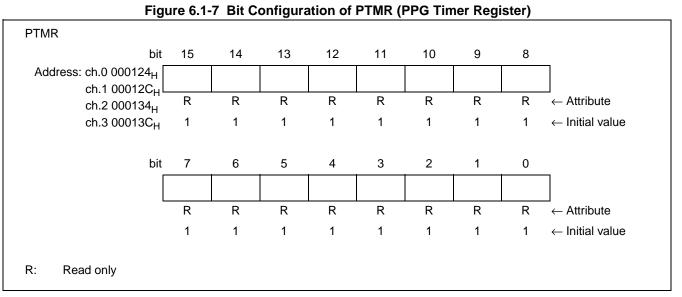

#### PPG

## **MB91313A Series**

- 4 channels

- 16-bit counter, 16-bit data register with buffer to set the cycle

- Internal clock: selectable from among results of dividing the machine clock frequency by 1, 4, 16, and 64

- Automatic cycle setting supported with the DMA transfer

- Remote control transmission support function

- · Open drain output

#### ■ PWC

- 1 channel (1 input)

- 16-bit up counter

- Simplified LOWPASS filter

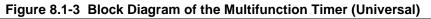

#### Multifunction Timer

- 4 channels

- · Removes the noise, if lower than specified clock, using the Low Pass filter

- Pulse width can be measured using 7 types of clock signal

- Event count function from pin input

- Interval timer function using 7 types of clock and external input clock

- Built-in HSYNC counter mode

#### ■ HDMI-CEC/Remote Control Reception

- 2 channels

- HDMI-CEC reception function (with automatic ACK response function)

- Remote control reception function (with 4 byte reception buffers)

#### Other Interval Timers

- Watch timer (32 kHz, Max 60 s count)

- Watchdog timer

#### I/O Ports

Maximum 86 ports

#### ■ Other Features

- Built-in oscillation circuit as a clock source

- INITX provided as a reset pin

- Watchdog timer and software resets available

- · Supporting stop mode and sleep mode as low-power consumption modes

- Gear function

- Built-in time-base timer

- 5 V tolerant I/O (for a part of pins)

- Package: LQFP-120, 0.5 mm pitch, 16 mm × 16 mm

- CMOS technology: 0.18 µm

- Power supply voltage 3.3±0.3 V, 1.8±0.15 V, 2 power supply units

- I<sup>2</sup>C license

Purchase of Fujitsu I<sup>2</sup>C components conveys a license under the Philips I<sup>2</sup>C Patent Rights to use, these components in an I<sup>2</sup>C system provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

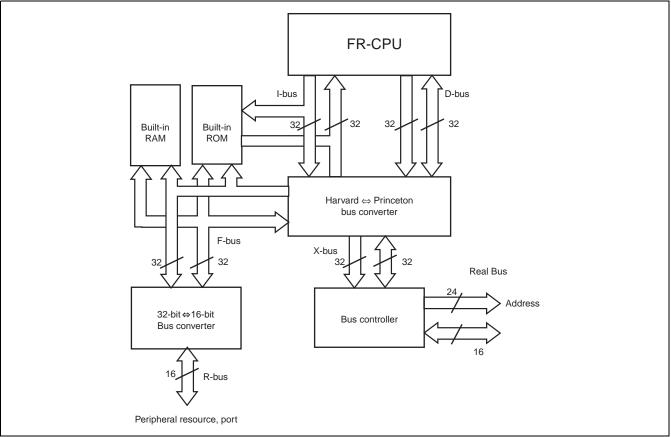

#### 1.2 **Block Diagram**

#### Figure 1.2-1 shows a block diagram of MB91313A Series.

#### Block Diagram of MB91313A Series

#### Figure 1.2-1 Block Diagram of MB91313A Series

## 1.3 Pin Assignment

#### Figure 1.3-1 shows the pin assignment of MB91313A Series.

#### Pin Assignment of MB91313A Series

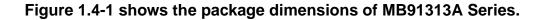

## 1.4 Package Dimensions

Figure 1.4-1 Package Dimensions of MB91313A Series

Please check the latest package dimensions at the following URL.

http://edevice.fujitsu.com/package/en-search/

## **1.5 List of Pin Functions**

#### Table 1.5-1 lists the pin functions of MB91313A Series.

#### ■ Pin Functions of MB91313A Series

#### Table 1.5-1 List of Pin Functions (1 / 8)

| Pin No. | Pin name                               | I/O circuit<br>type <sup>*1</sup> | Function                                                                       |

|---------|----------------------------------------|-----------------------------------|--------------------------------------------------------------------------------|

| 1       | VSS                                    | -                                 | GND pin                                                                        |

| 2       | VDDI                                   | -                                 | 1.8 V power supply pin                                                         |

| 3       | P23                                    | D                                 | General-purpose port                                                           |

| 5       | SIN1                                   |                                   | Serial data input pin                                                          |

|         | P24                                    |                                   | General-purpose port                                                           |

| 4       | SOT1/SDA1<br>(I <sup>2</sup> C bridge) | L                                 | Serial data output pin<br>I <sup>2</sup> C data I/O pin                        |

|         | P25                                    |                                   | General-purpose port                                                           |

| 5       | SCK1/SCL1<br>(I <sup>2</sup> C bridge) | L                                 | Clock pulse I/O pin for serial communication<br>I <sup>2</sup> C clock I/O pin |

| (       | P26                                    | D                                 | General-purpose port                                                           |

| 6       | SIN2                                   | – D                               | Serial data input pin                                                          |

|         | P27                                    | L                                 | General-purpose port                                                           |

| 7       | SOT2/SDA2<br>(I <sup>2</sup> C bridge) |                                   | Serial data output pin<br>I <sup>2</sup> C data I/O pin                        |

|         | P30                                    |                                   | General-purpose port                                                           |

| 8       | SCK2/SCL2<br>(I <sup>2</sup> C bridge) | L                                 | Clock pulse I/O pin for serial communication<br>I <sup>2</sup> C clock I/O pin |

| 9       | P31                                    | D                                 | General-purpose port                                                           |

| 7       | ТОТ0                                   |                                   | Output pin for reload timer                                                    |

| 10      | P32                                    | D                                 | General-purpose port                                                           |

| 10      | TOT1                                   | D                                 | Output pin for reload timer                                                    |

| 11      | P33                                    | D                                 | General-purpose port                                                           |

| 11      | TOT2                                   |                                   | Output pin for reload timer                                                    |

| 12      | P34                                    | D                                 | General-purpose port                                                           |

| 12      | TINO                                   |                                   | Event input pin for reload timer                                               |

| 13      | P35                                    | D                                 | General-purpose port                                                           |

|         | TIN1                                   |                                   | Event input pin for reload timer                                               |

| 14      | P36                                    | D                                 | General-purpose port                                                           |

| 14      | TIN2                                   |                                   | Event input pin for reload timer                                               |

#### Table 1.5-1 List of Pin Functions (2 / 8)

| Pin No. | Pin name    | I/O circuit<br>type <sup>*1</sup> | Function                                                                             |

|---------|-------------|-----------------------------------|--------------------------------------------------------------------------------------|

| 15      | P37         | D                                 | General-purpose port                                                                 |

| 15      | RIN         | – D                               | PWC input pin                                                                        |

|         | P40         |                                   | General-purpose port                                                                 |

| 16      | TMO0        | В                                 | Multifunction timer output pin                                                       |

|         | INT16       |                                   | External interrupt request input pin                                                 |

|         | P41         |                                   | General-purpose port                                                                 |

| 17      | TMO1        | В                                 | Multifunction timer output pin                                                       |

|         | INT17       |                                   | External interrupt request input pin                                                 |

|         | P42         |                                   | General-purpose port                                                                 |

| 18      | TMO2        | В                                 | Multifunction timer output pin                                                       |

|         | INT18       | -                                 | External interrupt request input pin                                                 |

|         | P43         |                                   | General-purpose port                                                                 |

| 19      | ТМО3        | В                                 | Multifunction timer output pin                                                       |

|         | INT19       | -                                 | External interrupt request input pin                                                 |

|         | P44         | В                                 | General-purpose port                                                                 |

| 20      | TMI0        |                                   | Multifunction timer input pin                                                        |

|         | INT20       | -                                 | External interrupt request input pin                                                 |

|         | P45         | - B                               | General-purpose port                                                                 |

| 21      | TMI1        |                                   | Multifunction timer input pin                                                        |

| 21      | INT21       |                                   | External interrupt request input pin                                                 |

|         | SIN10       |                                   | Serial data input pin                                                                |

|         | P46         | В                                 | General-purpose port                                                                 |

|         | TMI2        |                                   | Multifunction timer input pin                                                        |

| 22      | INT22       |                                   | External interrupt request input pin                                                 |

|         | SOT10/SDA10 |                                   | Serial data output pin<br>I <sup>2</sup> C data I/O pin                              |

|         | P47         |                                   | General-purpose port                                                                 |

|         | TMI3        |                                   | Multifunction timer input pin                                                        |

| 23      | INT23       | В                                 | External interrupt request input pin                                                 |

|         | SCK10/SCL10 |                                   | Clock pulse input/output pin for serial communication I <sup>2</sup> C clock I/O pin |

|         | P60         |                                   | General-purpose port                                                                 |

| 24      | ТОТ3        | С                                 | Output pin for reload timer                                                          |

|         | TRG2        |                                   | PPG trigger input pin                                                                |

#### Table 1.5-1 List of Pin Functions (3 / 8)

| Pin No. | Pin name | I/O circuit<br>type <sup>*1</sup> | Function                                |

|---------|----------|-----------------------------------|-----------------------------------------|

|         | P61      |                                   | General-purpose port                    |

| 25      | TOT4     | С                                 | Output pin for reload timer             |

|         | TRG3     |                                   | PPG trigger input pin                   |

|         | P62      |                                   | General-purpose port                    |

| 26      | TOT5     | С                                 | Output pin for reload timer             |

|         | RDY      |                                   | External ready input pin                |

|         | P63      |                                   | General-purpose port                    |

| 27      | TIN3     | С                                 | Event input pin for reload timer        |

|         | CLK      |                                   | External clock output pin               |

| 29      | P64      | G                                 | General-purpose port                    |

| 28      | TIN4     | C                                 | Event input pin for reload timer        |

| 20      | P65      | G                                 | General-purpose port                    |

| 29      | TIN5     | C                                 | Event input pin for reload timer        |

| 30      | VDDE     | -                                 | 3.3 V power supply                      |

| 31      | VSS      | -                                 | GND pin                                 |

| 22      | PF0      | D                                 | General-purpose port                    |

| 32      | RCIN0    | В                                 | HDMI-CEC/Remote control 0 I/O pin       |

| 22      | PF1      | — В                               | General-purpose port                    |

| 33      | RCIN1    |                                   | HDMI-CEC/Remote control 1 I/O pin       |

| 24      | PF2      | D                                 | General-purpose port                    |

| 34      | RCACK0   | D                                 | HDMI-CEC/Remote control 0ACK output pin |

| 25      | PF3      | D                                 | General-purpose port                    |

| 35      | RCACK1   | D                                 | HDMI-CEC/Remote control 1ACK output pin |

| 36      | PF4      | D                                 | General-purpose port                    |

| 37      | PF5      | D                                 | General-purpose port                    |

| 38      | PF6      | D                                 | General-purpose port                    |

| 39      | PF7      | D                                 | General-purpose port                    |

| 40      | VDDE     | -                                 | 3.3 V power supply                      |

| 41      | VSS      | -                                 | GND pin                                 |

| 42      | AVSS     | -                                 | A/D converter GND pin                   |

| 43      | AVRH     | -                                 | A/D converter reference voltage pin     |

| 44      | AVCC     | -                                 | A/D converter power supply pin          |

| 45      | PD0      | L                                 | General-purpose port pin                |

| 45      | AN0      |                                   | A/D converter analog input pin          |

| 46      | PD1      | L                                 | General-purpose port                    |

| 40      | AN1      |                                   | A/D converter analog input pin          |

#### Table 1.5-1 List of Pin Functions (4 / 8)

| Pin No. | Pin name           | I/O circuit<br>type <sup>*1</sup> | Function                             |

|---------|--------------------|-----------------------------------|--------------------------------------|

| 47      | PD2                | т                                 | General-purpose port                 |

| 47      | AN2                | – L                               | A/D converter analog input pin       |

| 48      | PD3                | L                                 | General-purpose port                 |

| 40      | AN3                |                                   | A/D converter analog input pin       |

| 49      | PD4                | L                                 | General-purpose port                 |

| 49      | AN4                |                                   | A/D converter analog input pin       |

| 50      | PD5                | L                                 | General-purpose port                 |

| 30      | AN5                |                                   | A/D converter Analog input pin       |

| 51      | PD6                | L                                 | General-purpose port                 |

| 51      | AN6                |                                   | A/D converter Analog input pin       |

| 52      | PD7                | L                                 | General-purpose port                 |

| 32      | AN7                |                                   | A/D converter Analog input pin       |

|         | PE0                |                                   | General-purpose port                 |

| 53      | AN8                | L                                 | A/D converter Analog input pin       |

|         | INT0               |                                   | External interrupt request input pin |

|         | PE1                | L                                 | General-purpose port                 |

| 54      | AN9                |                                   | A/D converter Analog input pin       |

| 54      | PPG0 <sup>*2</sup> |                                   | Output pin for PPG                   |

|         | INT1               |                                   | External interrupt request input pin |

|         | PE2                | B                                 | General-purpose port                 |

| 55      | PPG1 *2            |                                   | Output pin for PPG                   |

| 55      | INT2               |                                   | External interrupt request input pin |

|         | ATRG               |                                   | Trigger input pin for A/D converter  |

|         | PE3                |                                   | General-purpose port                 |

| 56      | PPG2 *2            | В                                 | Output pin for PPG                   |

|         | INT3               |                                   | External interrupt request input pin |

| 57      | VDDE               | -                                 | 3.3 V power supply                   |

| 58      | INITX              | G                                 | Initial reset pin                    |

| 59      | X0A                | А                                 | Sub clock input pin                  |

| 60      | X1A                | А                                 | Sub clock output pin                 |

| 61      | VSS                | -                                 | GND pin                              |

| 62      | X1                 | А                                 | Main clock output pin                |

| 63      | X0                 | А                                 | Main clock input pin                 |

| 64      | VDDI               | -                                 | 1.8 V power supply                   |

| 65      | MD0                | F                                 | Mode pin                             |

| 66      | MD1                | F                                 | Mode pin                             |

#### Table 1.5-1 List of Pin Functions (5 / 8)

| Pin No. | Pin name  | I/O circuit<br>type <sup>*1</sup> | Function                                                                             |

|---------|-----------|-----------------------------------|--------------------------------------------------------------------------------------|

| 67      | MD2       | F                                 | Mode pin                                                                             |

|         | PE4       |                                   | General-purpose port                                                                 |

| 68      | PPG3 *2   | В                                 | Output pin for PPG                                                                   |

|         | INT4      |                                   | External interrupt request input pin                                                 |

|         | PE5       |                                   | General-purpose port                                                                 |

| 69      | SIN8      | В                                 | Serial data input pin                                                                |

|         | INT5      |                                   | External interrupt request input pin                                                 |

|         | PE6       |                                   | General-purpose port                                                                 |

| 70      | SOT8/SDA8 | В                                 | External interrupt request input pin I <sup>2</sup> C data I/O pin                   |

|         | INT6      |                                   | Serial data output pin                                                               |

|         | PE7       |                                   | General-purpose port                                                                 |

| 71      | SCK8/SCL8 | В                                 | Clock pulse input/output pin for serial communication I <sup>2</sup> C clock I/O pin |

|         | INT7      | -                                 | External interrupt request input pin                                                 |

| 70      | PC0       |                                   | General-purpose port                                                                 |

| 72      | SIN9      | – B                               | Serial data input pin                                                                |

|         | PC1       | В                                 | General-purpose port                                                                 |

| 73      | SOT9/SDA9 |                                   | Serial data output pin<br>I <sup>2</sup> C data I/O pin                              |

|         | PC2       |                                   | General-purpose port                                                                 |

| 74      | SCK9/SCL9 | В                                 | Clock pulse input/output pin for serial communication I <sup>2</sup> C clock I/O pin |

| 75      | PC3       | В                                 | General-purpose port                                                                 |

| 76      | PC4       | D                                 | General-purpose port                                                                 |

| 76      | PPGA      | – B                               | Output pin for PPG                                                                   |

| 77      | PC5       | D                                 | General-purpose port                                                                 |

| 77      | PPGB      | – B                               | Output pin for PPG                                                                   |

| 70      | PC6       | D                                 | General-purpose port                                                                 |

| 78      | TRG0      | – B                               | PPG trigger input                                                                    |

| 79      | PC7       | В                                 | General-purpose port                                                                 |

| 19      | TRG1      | D                                 | PPG trigger input                                                                    |

| 80      | TRSTX     | G                                 | Reset pin for development tool                                                       |

| 81      | ICD0      | K                                 | Data pin for development tool                                                        |

| 82      | ICD1      | K                                 | Data pin for development tool                                                        |

| 83      | ICD2      | K                                 | Data pin for development tool                                                        |

| 84      | ICD3      | K                                 | Data pin for development tool                                                        |

#### Table 1.5-1 List of Pin Functions (6 / 8)

| Pin No. | Pin name  | I/O circuit<br>type <sup>*1</sup> | Function                                                                             |  |

|---------|-----------|-----------------------------------|--------------------------------------------------------------------------------------|--|

| 85      | ICS0      | Н                                 | Status pin for development tool                                                      |  |

| 86      | ICS1      | Н                                 | Status pin for development tool                                                      |  |

| 87      | ICS2      | Н                                 | Status pin for development tool                                                      |  |

| 88      | ICLK      | Н                                 | Clock pin for development tool                                                       |  |

| 89      | IBREAK    | Ι                                 | Break pin for development tool                                                       |  |

| 90      | VDDE      | -                                 | 3.3 V power supply                                                                   |  |

| 91      | VSS       | -                                 | GND pin                                                                              |  |

| 92      | VDDI      | -                                 | 1.8 V power supply                                                                   |  |

|         | P00       |                                   | General-purpose port                                                                 |  |

| 93      | AD00      | с                                 | External address/data bus I/O pin                                                    |  |

| 95      | SIN3      | - C                               | Serial data input pin                                                                |  |

|         | INT8      |                                   | External interrupt request input pin                                                 |  |

|         | P01       |                                   | General-purpose port                                                                 |  |

|         | AD01      |                                   | External address/data bus I/O pin                                                    |  |

| 94      | SOT3/SDA3 | С                                 | Serial data output pin<br>I <sup>2</sup> C data I/O pin                              |  |

|         | INT9      |                                   | External interrupt request input pin                                                 |  |

|         | P02       | C                                 | General-purpose port                                                                 |  |

|         | AD02      |                                   | External address/data bus I/O pin                                                    |  |

| 95      | SCK3/SCL3 |                                   | Clock pulse input/output pin for serial communication I <sup>2</sup> C clock I/O pin |  |

|         | INT10     |                                   | External interrupt request input pin                                                 |  |

|         | P03       | - C                               | General-purpose port                                                                 |  |

| 96      | AD03      |                                   | External address/data bus I/O pin                                                    |  |

| 90      | SIN4      |                                   | Serial data input pin                                                                |  |

|         | INT11     |                                   | External interrupt request input pin                                                 |  |

|         | P04       |                                   | General-purpose port                                                                 |  |

|         | AD04      |                                   | External address/data bus I/O pin                                                    |  |

| 97      | SOT4/SDA4 | С                                 | Serial data output pin<br>I <sup>2</sup> C data I/O pin                              |  |

|         | INT12     |                                   | External interrupt request input pin                                                 |  |

| 98      | P05       | с                                 | General-purpose port                                                                 |  |

|         | AD05      |                                   | External address/data bus I/O pin                                                    |  |

|         | SCK4/SCL4 |                                   | Clock pulse input/output pin for serial communication I <sup>2</sup> C clock I/O pin |  |

|         | INT13     |                                   | External interrupt request input pin                                                 |  |

#### Table 1.5-1 List of Pin Functions (7 / 8)

| Pin No. | Pin name  | I/O circuit<br>type *1 | Function                                                                             |

|---------|-----------|------------------------|--------------------------------------------------------------------------------------|

| 99      | P06       | - C                    | General-purpose port                                                                 |

|         | AD06      |                        | External address/data bus I/O pin                                                    |

|         | SIN5      |                        | Serial data input pin                                                                |

|         | INT14     |                        | External interrupt request input pin                                                 |

| 100     | P07       | С                      | General-purpose port                                                                 |

|         | AD07      |                        | External address/data bus I/O pin                                                    |

|         | SOT5/SDA5 |                        | Serial data output pin<br>I <sup>2</sup> C data I/O pin                              |

|         | INT15     |                        | External interrupt request input pin                                                 |

|         | P10       |                        | General-purpose port                                                                 |

| 101     | AD08      | С                      | External address/data bus I/O pin                                                    |

| 101     | SCK5/SCL5 |                        | Clock pulse input/output pin for serial communication I <sup>2</sup> C clock I/O pin |

|         | P11       | С                      | General-purpose port                                                                 |

| 102     | AD09      |                        | External address/data bus I/O pin                                                    |

|         | SIN6      |                        | Serial data input pin                                                                |

|         | P12       |                        | General-purpose port                                                                 |

| 103     | AD10      | С                      | External address/data bus I/O pin                                                    |

|         | SOT6/SDA6 |                        | Serial data output pin<br>I <sup>2</sup> C data I/O pin                              |

|         | P13       | С                      | General-purpose port                                                                 |

| 104     | AD11      |                        | External address/data bus I/O pin                                                    |

| 104     | SCK6/SCL6 |                        | Clock pulse input/output pin for serial communication I <sup>2</sup> C clock I/O pin |

|         | P14       |                        | General-purpose port                                                                 |

| 105     | AD12      | С                      | External address/data bus I/O pin                                                    |

|         | SIN7      |                        | Serial data input pin                                                                |

|         | P15       |                        | General-purpose port                                                                 |

| 106     | AD13      | С                      | External address/data bus I/O pin                                                    |

|         | SOT7/SDA7 |                        | Serial data output pin<br>I <sup>2</sup> C data I/O pin                              |

|         | P16       | С                      | General-purpose port                                                                 |

| 107     | AD14      |                        | External address/data bus I/O pin                                                    |

|         | SCK7/SCL7 |                        | Clock pulse input/output pin for serial communication I <sup>2</sup> C clock I/O pin |

| 108     | P17       | С                      | General-purpose port                                                                 |

| 108     | AD15      |                        | External address/data bus I/O pin                                                    |

#### Table 1.5-1 List of Pin Functions (8 / 8)

| Pin No. | Pin name                               | I/O circuit<br>type <sup>*1</sup> | Function                                                                             |

|---------|----------------------------------------|-----------------------------------|--------------------------------------------------------------------------------------|

| 109     | P50                                    |                                   | General-purpose port                                                                 |

|         | CS0X                                   | С                                 | External chip select pin                                                             |

|         | PPG0 *2                                |                                   | Output pin for PPG                                                                   |

| 110     | P51                                    |                                   | General-purpose port                                                                 |

|         | CS1X                                   | С                                 | External chip select pin                                                             |

|         | PPG1 *2                                |                                   | Output pin for PPG                                                                   |

|         | P52                                    |                                   | General-purpose port                                                                 |

| 111     | CS2X                                   | С                                 | External chip select pin                                                             |

|         | PPG2 *2                                |                                   | Output pin for PPG                                                                   |

|         | P53                                    | С                                 | General-purpose port                                                                 |

| 112     | CS3X                                   |                                   | External chip select pin                                                             |

|         | PPG3 *2                                |                                   | Output pin for PPG                                                                   |

| 113     | P54                                    | - C                               | General-purpose port                                                                 |

| 115     | ASX                                    |                                   | External address strobe output pin                                                   |

| 114     | P55                                    | С                                 | General-purpose port                                                                 |

| 114     | RDX                                    |                                   | External read strobe output pin                                                      |

| 115     | P56                                    | С                                 | General-purpose port                                                                 |

| 115     | WR0X                                   |                                   | External data bus write strobe output pin                                            |

| 116     | P57                                    | - C                               | General-purpose port                                                                 |

| 110     | WR1X                                   |                                   | External data bus write strobe output pin                                            |

| 117     | P20                                    | D                                 | General-purpose port                                                                 |

| 117     | SIN0                                   |                                   | Serial data input pin                                                                |

|         | P21                                    |                                   | General-purpose port                                                                 |

| 118     | SOT0/SDA0<br>(I <sup>2</sup> C bridge) | L                                 | Serial data output pin<br>I <sup>2</sup> C data I/O pin                              |

| 119     | P22                                    | L                                 | General-purpose port                                                                 |

|         | SCK0/SCL0<br>(I <sup>2</sup> C bridge) |                                   | Clock pulse input/output pin for serial communication I <sup>2</sup> C clock I/O pin |

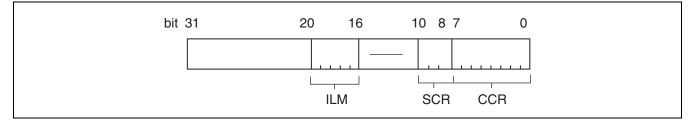

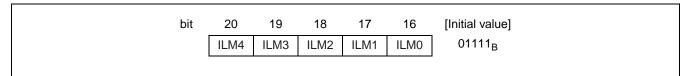

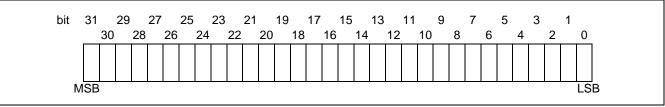

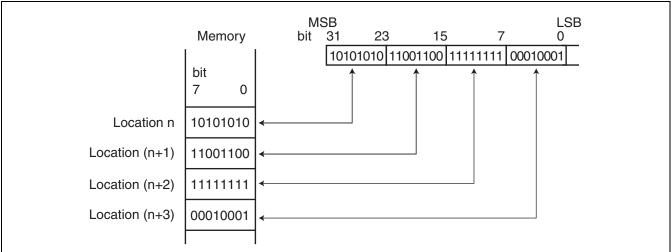

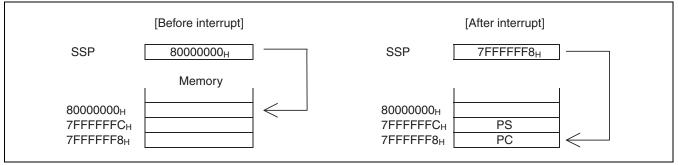

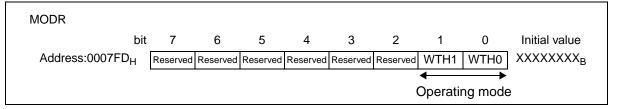

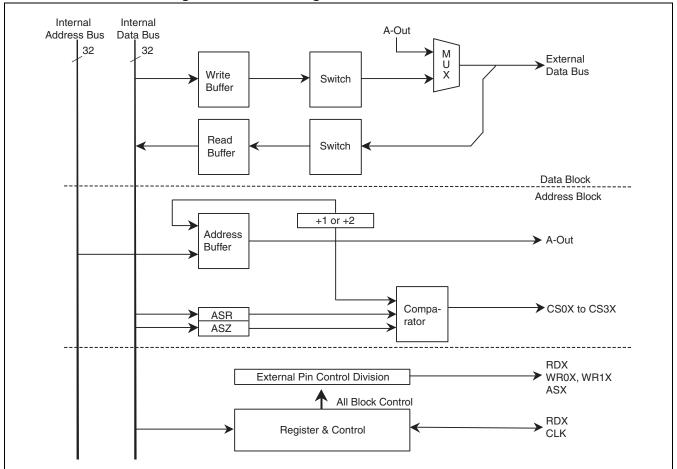

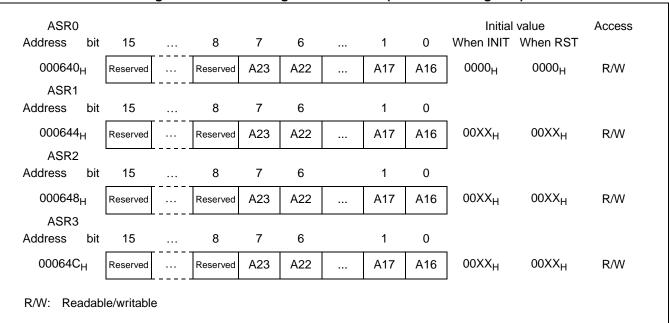

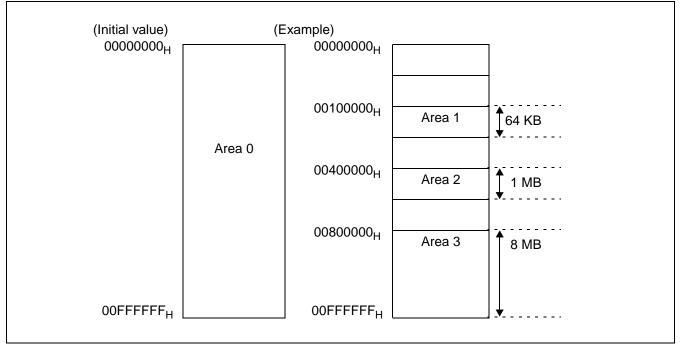

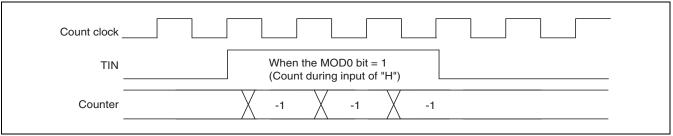

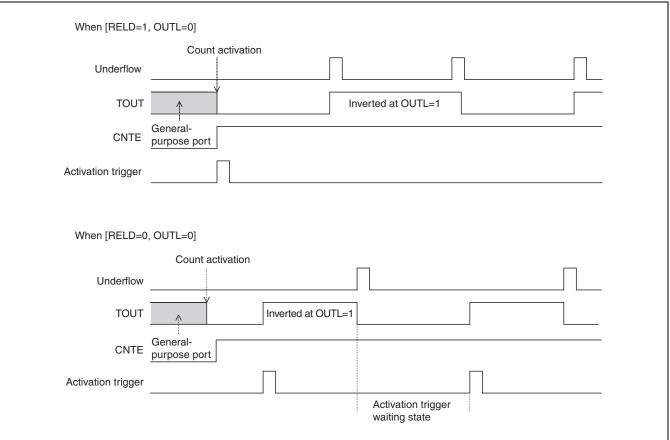

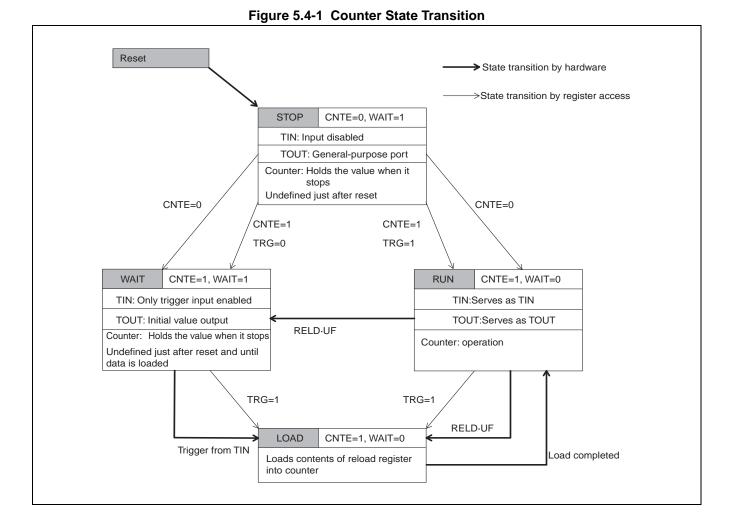

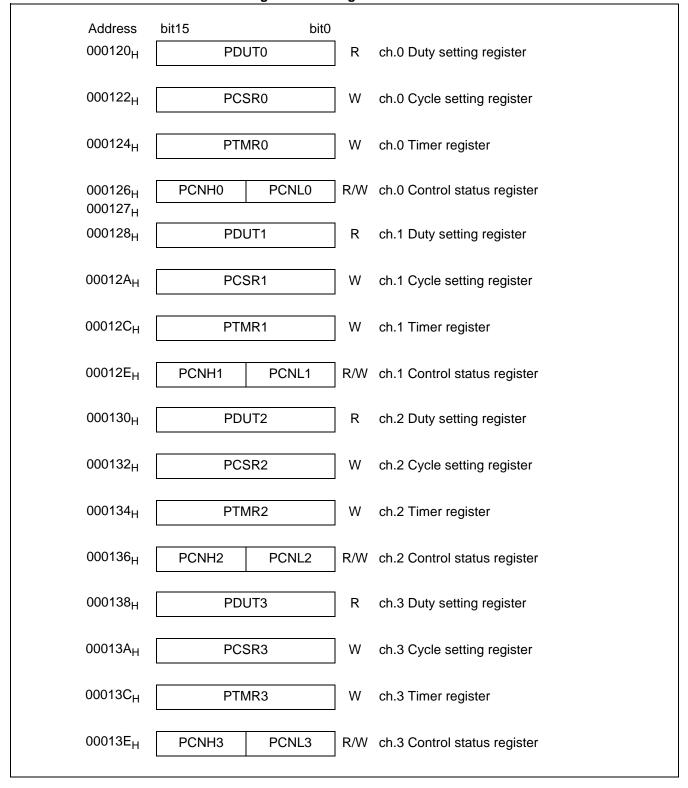

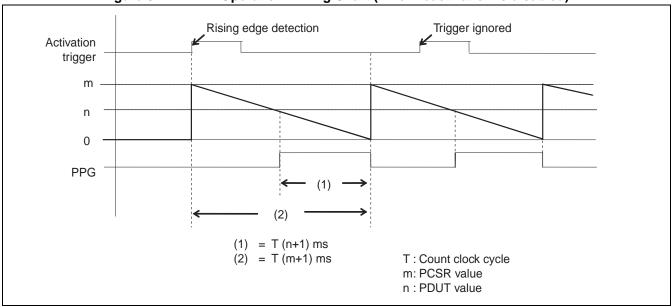

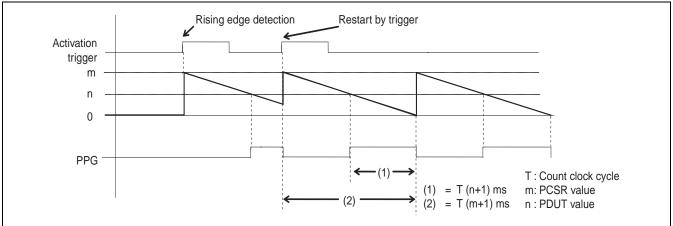

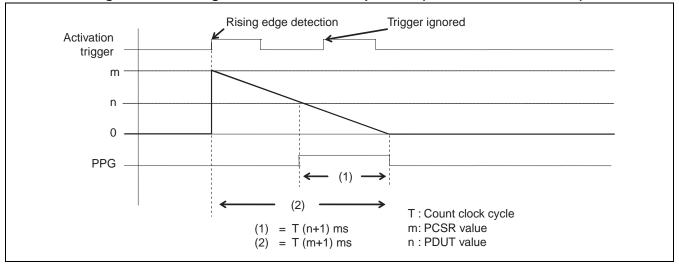

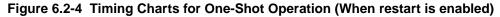

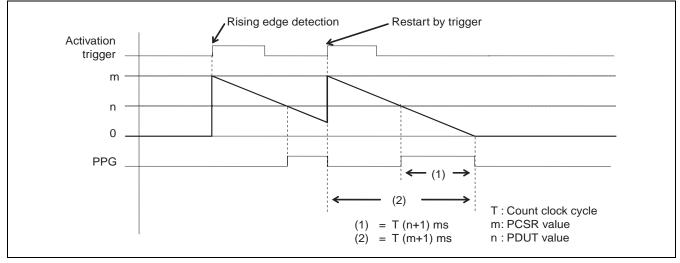

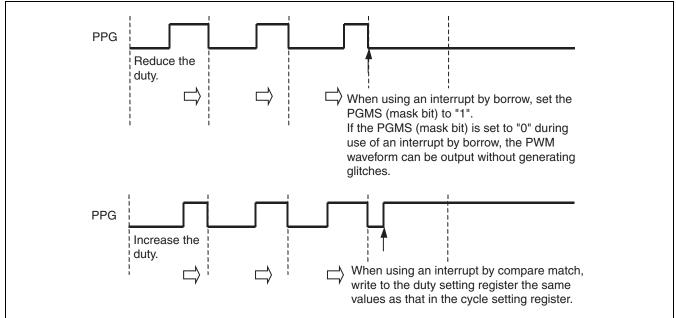

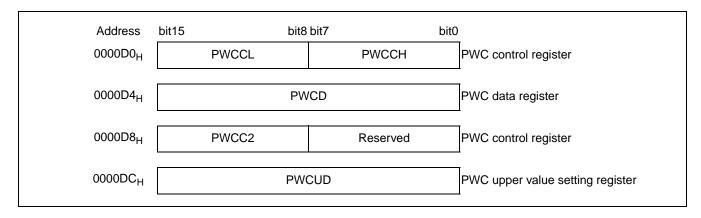

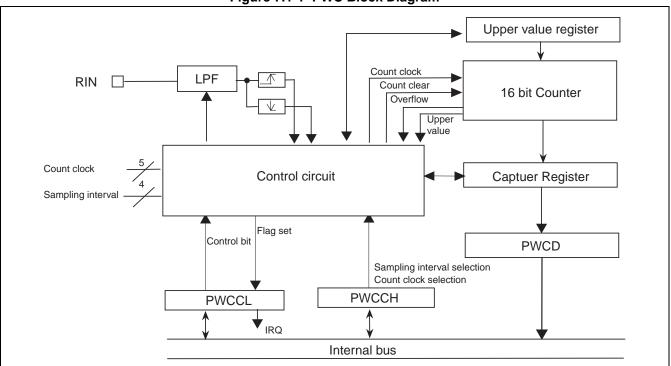

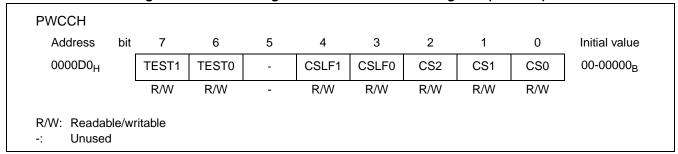

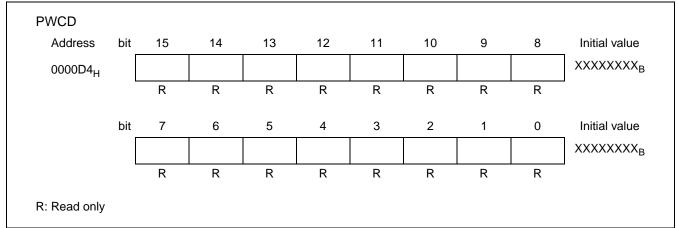

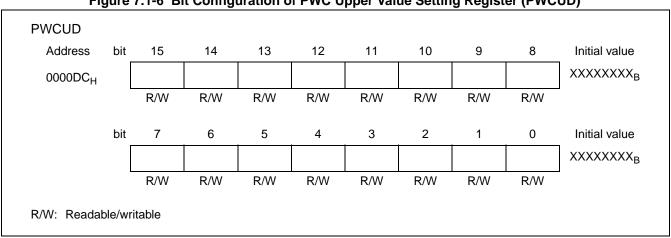

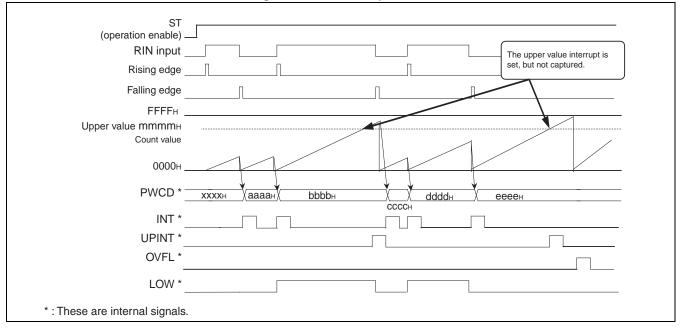

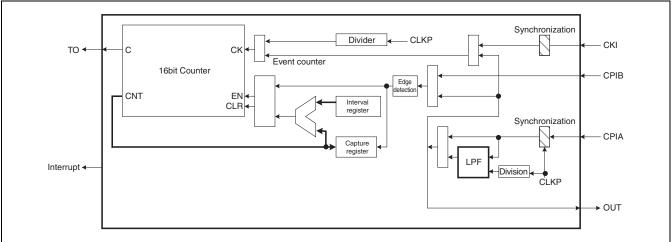

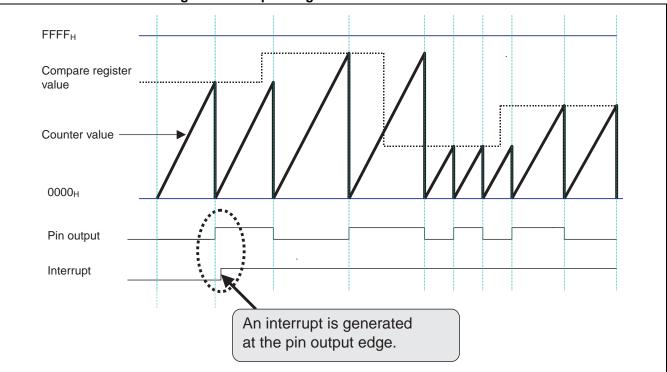

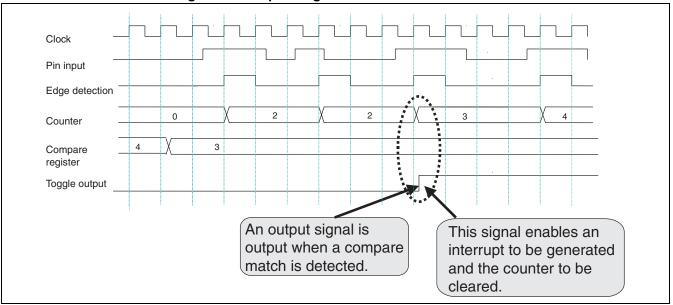

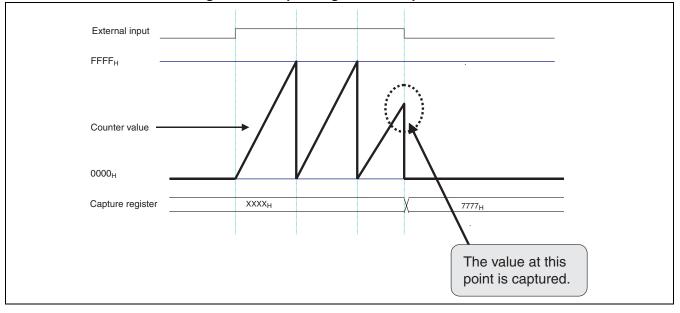

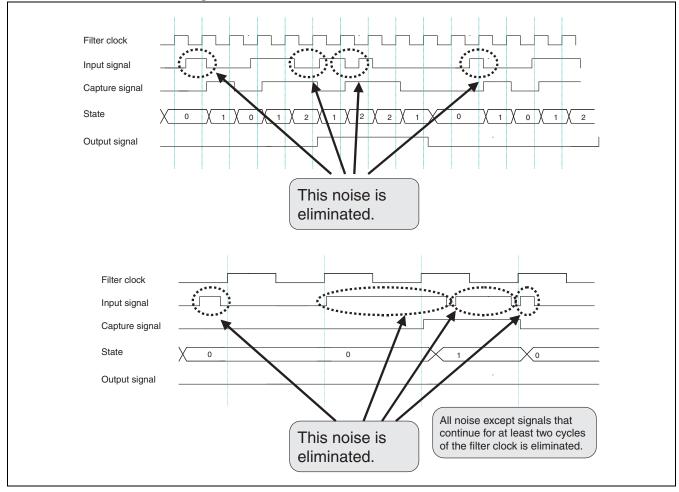

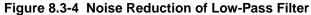

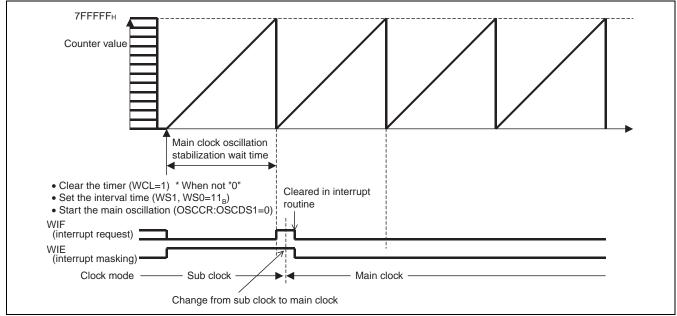

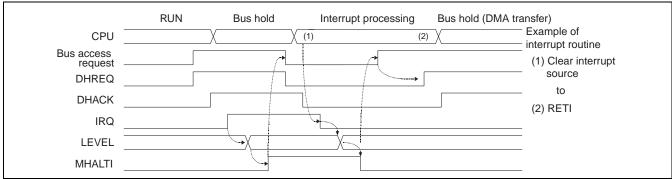

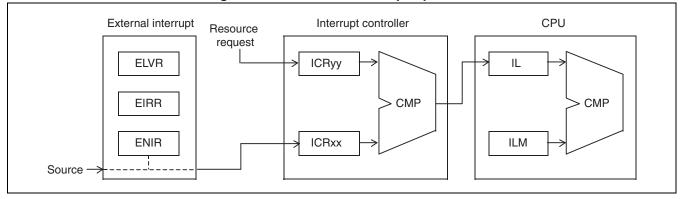

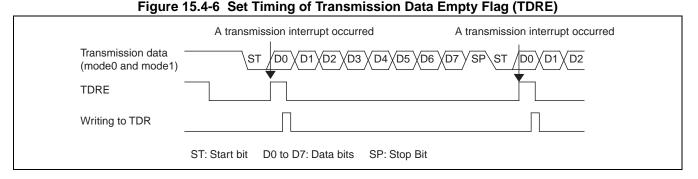

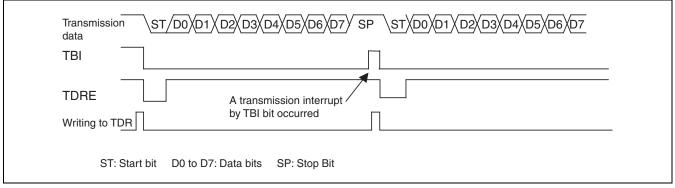

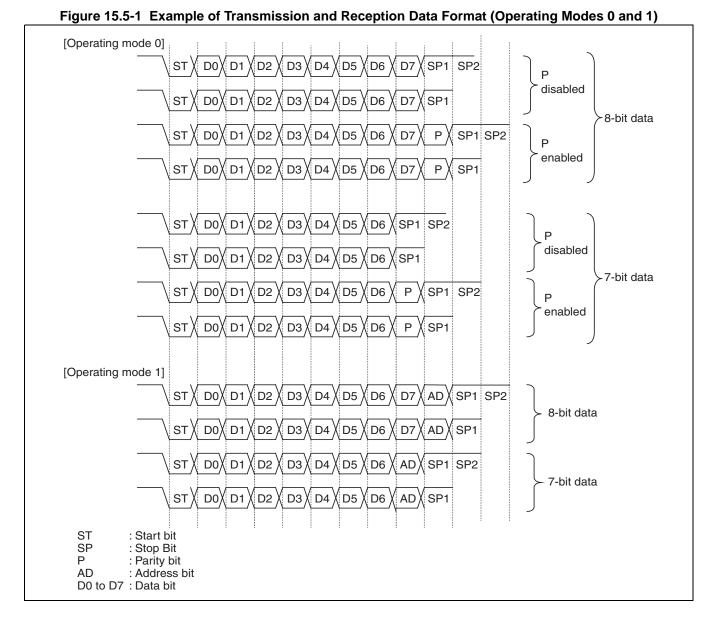

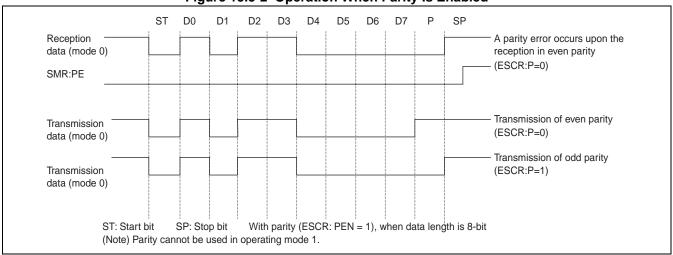

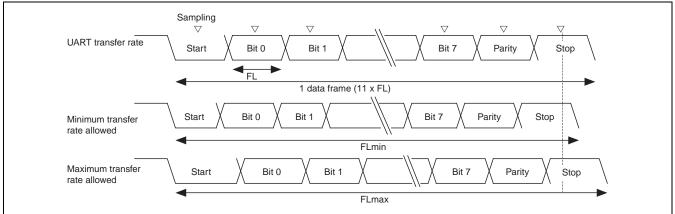

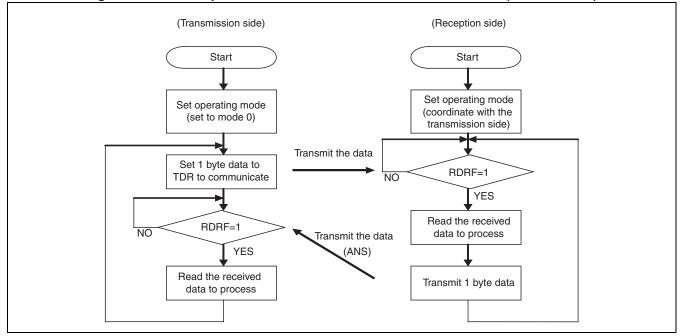

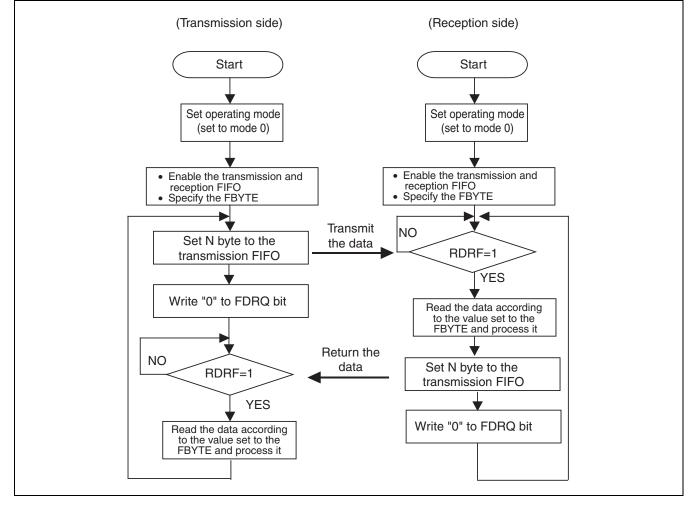

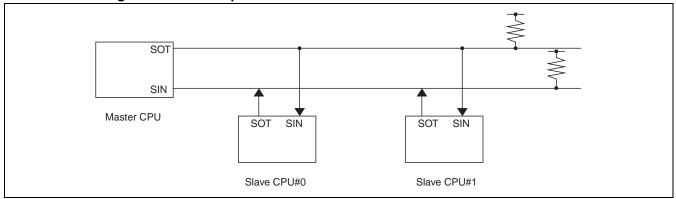

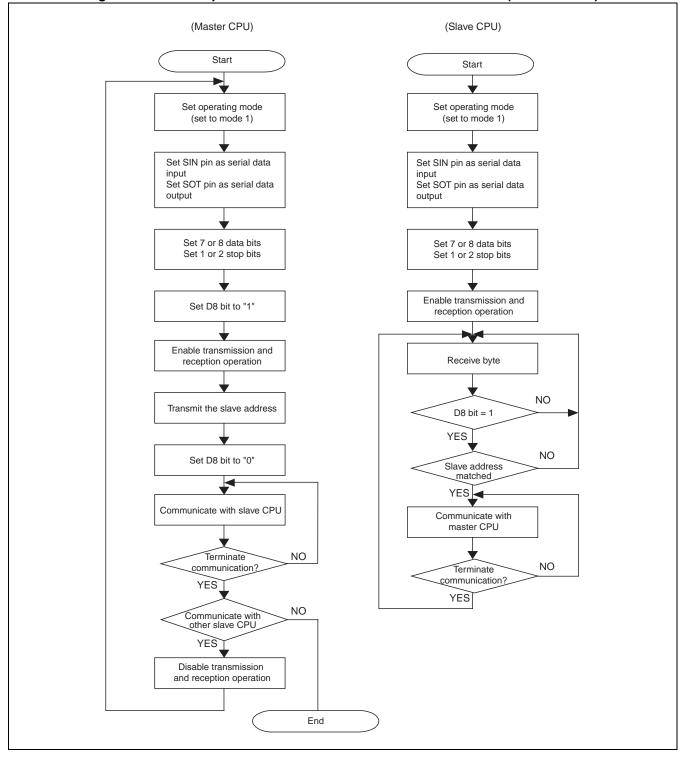

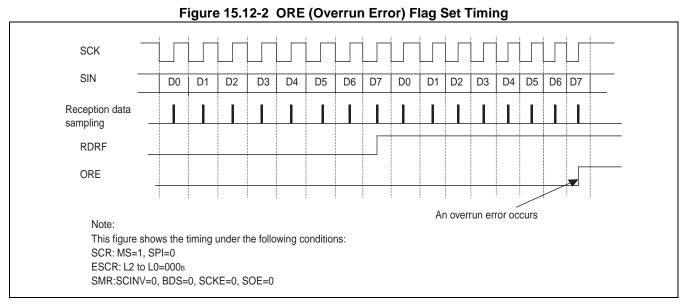

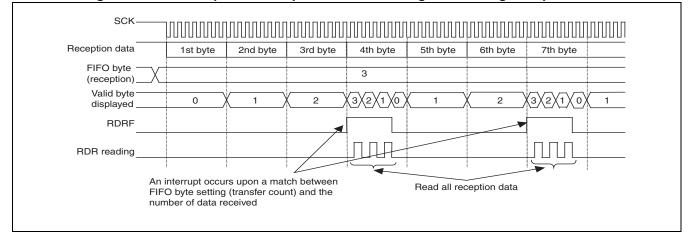

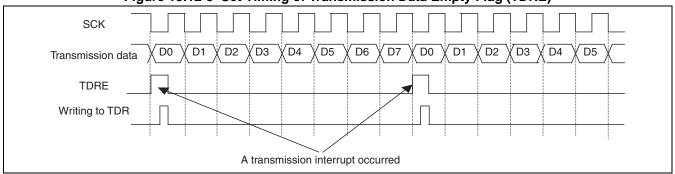

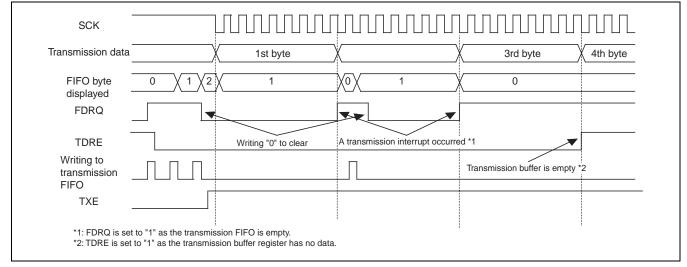

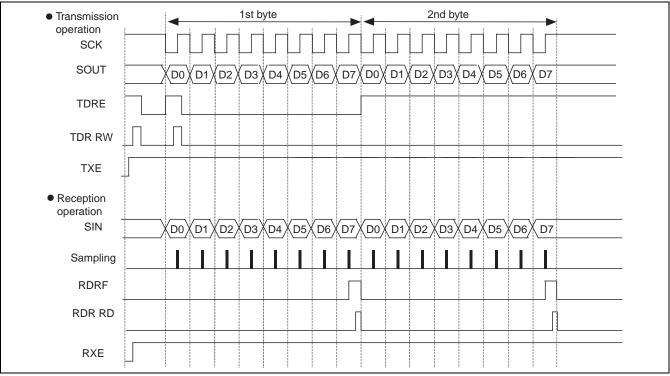

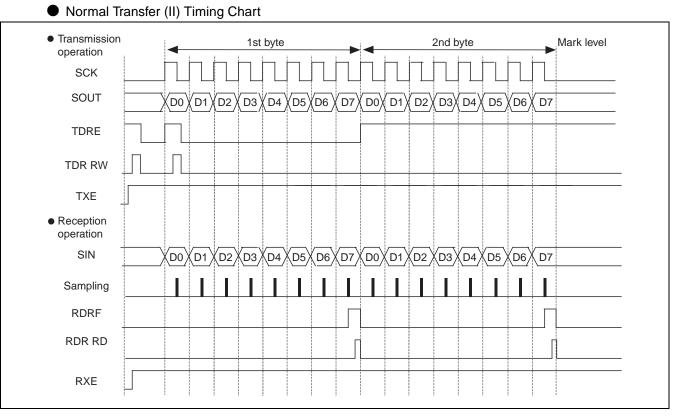

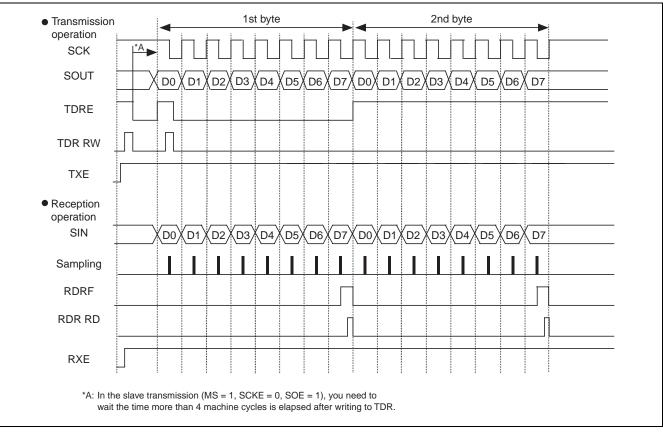

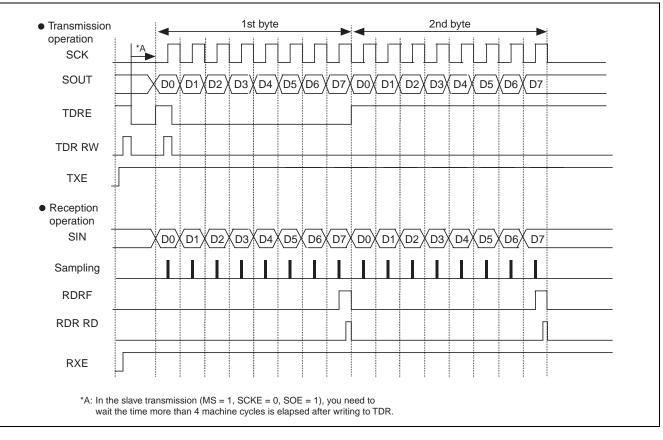

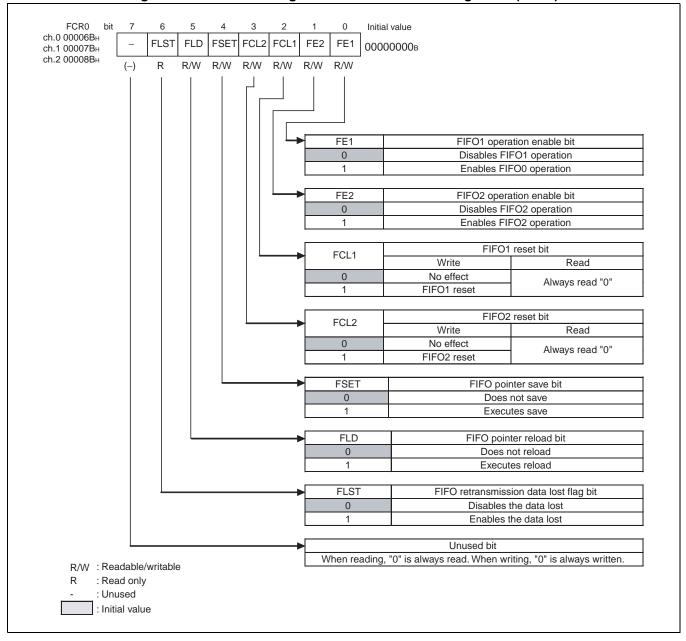

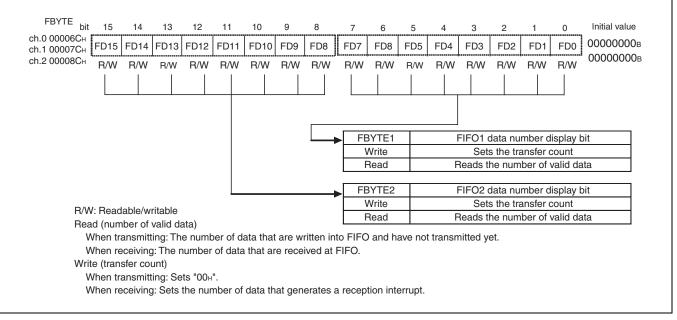

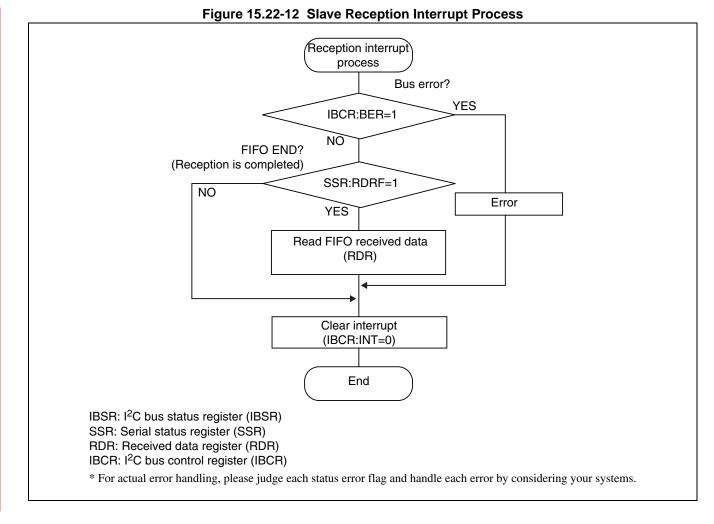

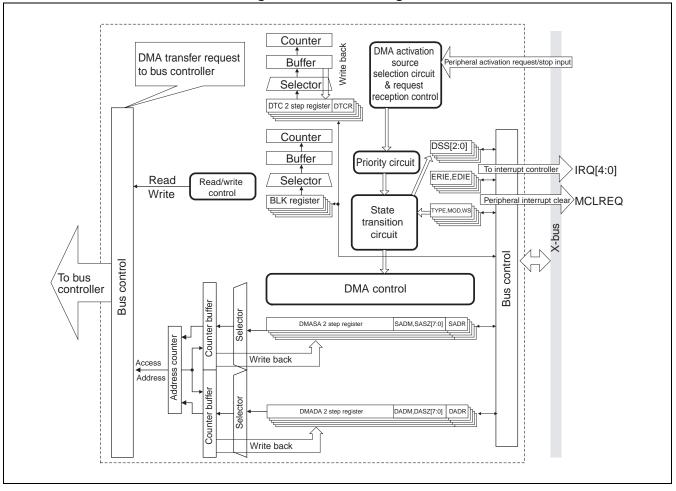

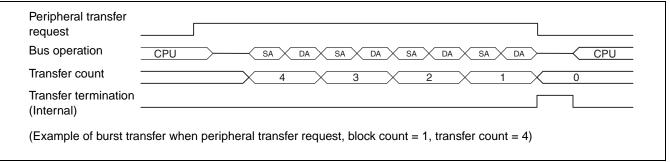

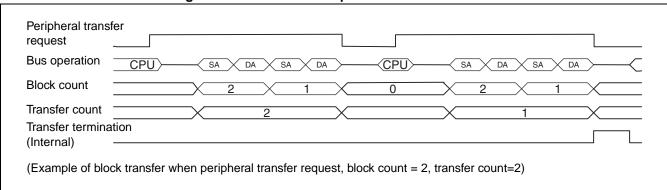

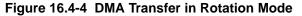

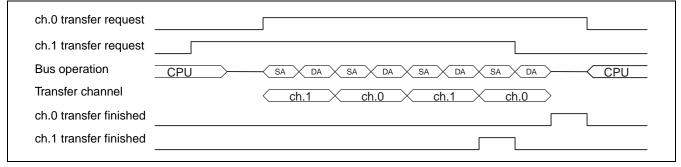

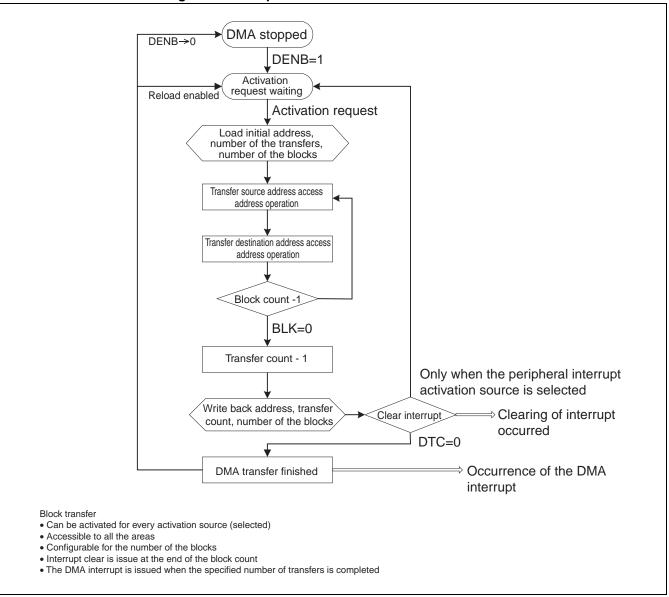

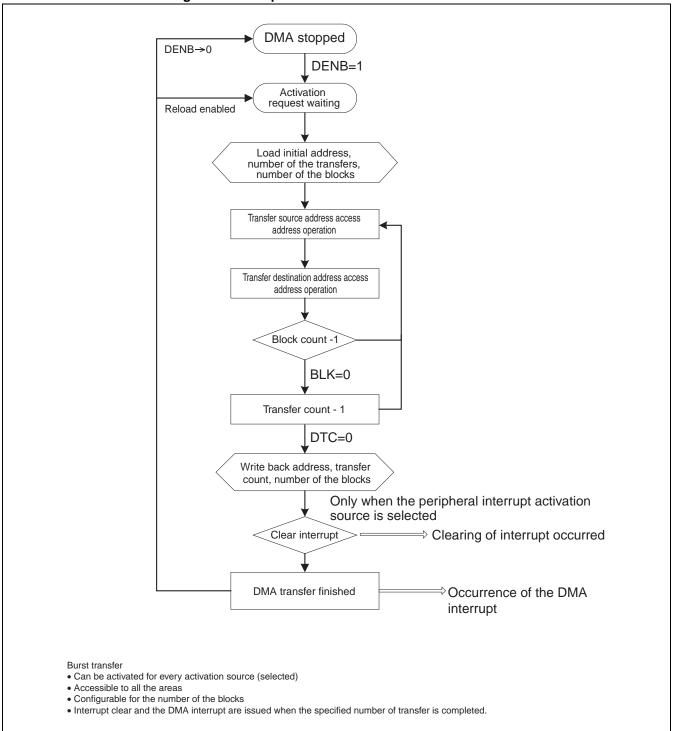

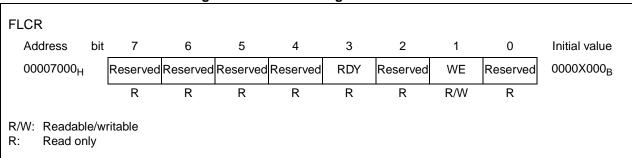

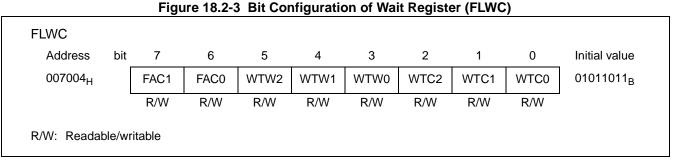

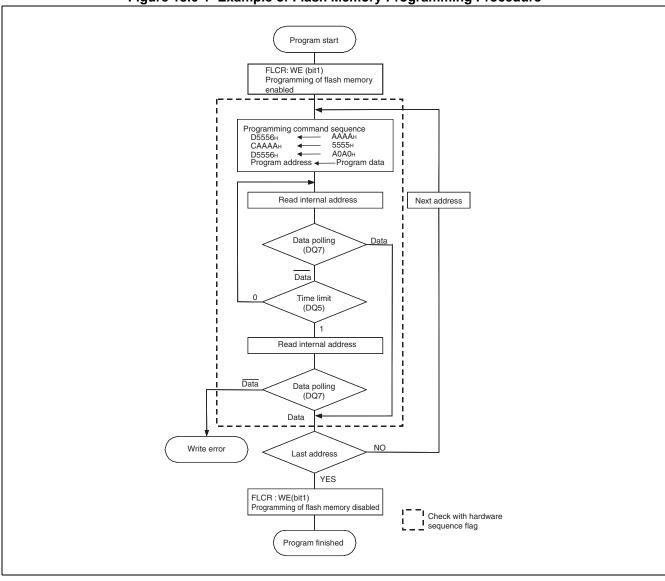

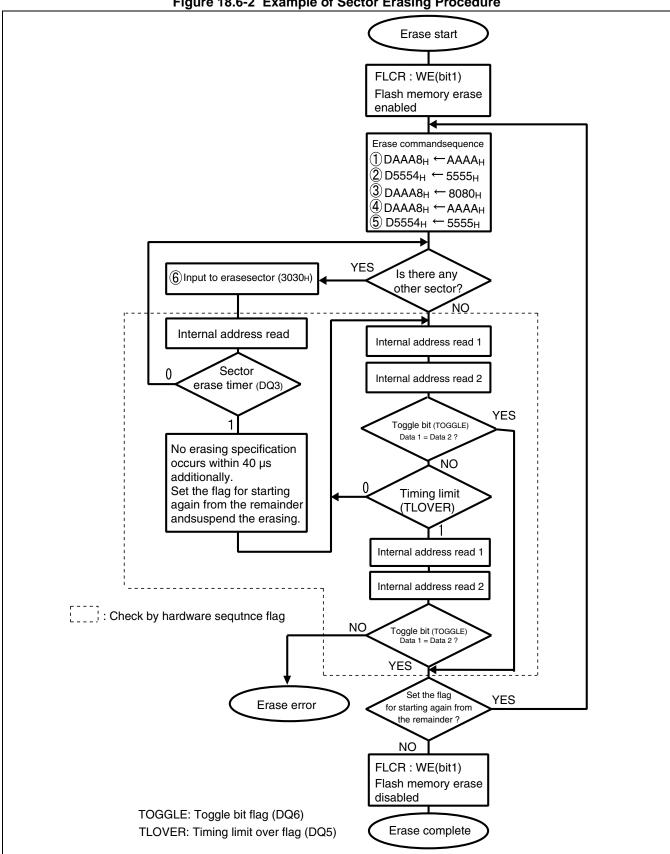

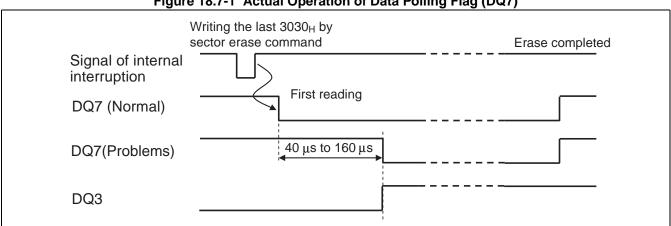

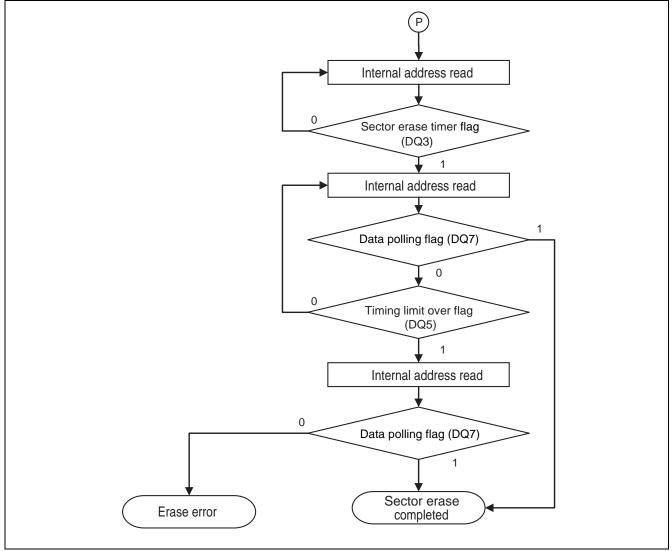

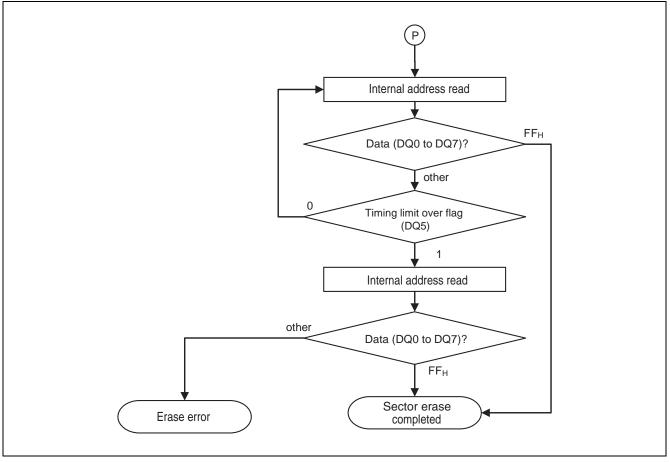

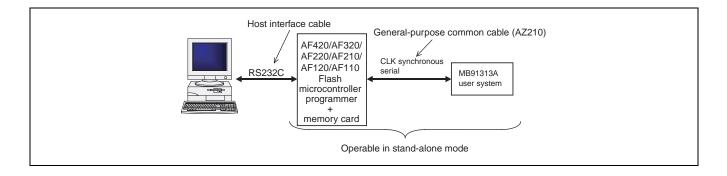

| 120     | VDDE                                   | -                                 | 3.3 V power supply pin                                                               |