# FR50 32-BIT MICROCONTROLLER MB91360 Series HARDWARE MANUAL

# FR50 32-BIT MICROCONTROLLER MB91360 Series HARDWARE MANUAL

**FUJITSU LIMITED**

## PREFACE

#### Objectives and Intended Readership

The MB91360 was developed as a product in the FR50 series of 32-bit, single-chip microcontrollers. The MB91360 contains a RISC architecture CPU core and is suitable for embedded applications requiring a high level of CPU processing power.

This manual describes the functions and operation of the MB91360 and is written for engineers who are developing actual products using MB91360 family products. Refer to the "*FR Family Instruction Manual*" for further information on the MB91360 instruction set.

Note: FR: Fujitsu RISC

#### Configuration of This Manual

This manual consists of the following chapters:

#### CHAPTER 1 MB91360 DESCRIPTION

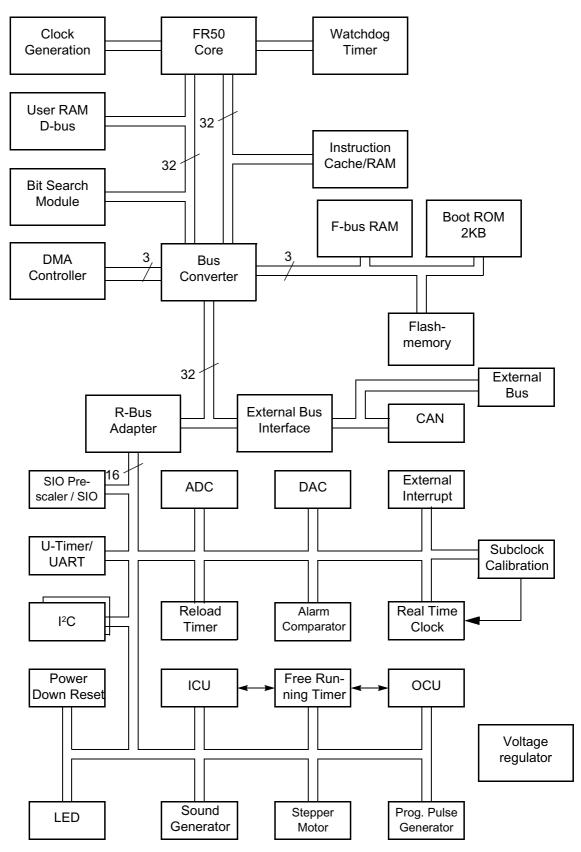

This chapter provides an overview of the MB91360 and describes key information such as the features, block diagram, and function description.

#### CHAPTER 2 CPU

This chapter describes key information about the functions of the FR50 series CPU core including the architecture, specifications, and instructions.

#### CHAPTER 3 INSTRUCTION CACHE

This chapter describes the instruction cache memory included in MB91360 family members and it operation. This only applies to MB91FV360GA.

#### CHAPTER 4 BOOT ROM / CONFIGURATION REGISTER

This chapter describes the functionality of the embedded boot ROM which is used in single chip mode.

#### CHAPTER 5 CLOCK GENERATION AND DEVICE STATES

This chapter describes details about generation and control of the clock used to control the MB91360. In addition device states and low power modes are explained. This chapter assumes operation without subclock. For a description of subclock operation see the corresponding chapter.

#### CHAPTER 6 CLOCK MODULATOR

This chapter provides an overview of the Clock Modulator and its features. It describes the register structure and operation of the Clock Modulator.

#### CHAPTER 7 I/O PORTS

This chapter provides an overview of I/O ports, lists the registers, and describes conditions for using external pins as I/O ports.

#### CHAPTER 8 EXTERNAL BUS INTERFACE

This Chapter describes in detail basic information about the external bus interface, the register structure and functions, bus operation basics and bus timing.

#### CHAPTER 9 INTERRUPT CONTROLLER

This Chapter provides an overview of the interrupt controller, describes the register structure and functions, and describes the interrupt controller operation

#### CHAPTER 10 EXTERNAL INTERRUPT/NMI CONTROLLER

This chapter provides an overview of the external interrupt/NMI controller, describes the register structure and functions, and describes the operation of the external interrupt/NMI controller.

#### CHAPTER 11 DMA CONTROLLER (DMAC)

This Chapter provides an overview of the DMA controller (DMAC), describes the register structure and functions, and describes the operation of the DMA controller.

#### CHAPTER 12 MODULES FOR OS SUPPORT

This Chapter provides an overview of the delayed interrupt and the bit search module and describes their register structure and functions, operation, and save and restore processing for the search module.

#### CHAPTER 13 PWM TIMER

This chapter provides an overview of the PWM timer, describes the register structure and functions, and describes the operation of the PWM timer.

#### CHAPTER 14 A/D CONVERTER

This chapter provides an overview of the A/D converter, describes the register structure and functions, and describes the operation of the A/D converter.

#### CHAPTER 15 16-BIT RELOAD TIMER

This chapter provides an overview of the 16-bit reload timer, describes the register structure/ functions, and describes the operation of the 16-bit reload timer.

#### CHAPTER 16 CAN CONTROLLER

This Chapter provides an overview of the CAN Interface, describes the register structure and functions, and describes the operation of the CAN Interface.

#### CHAPTER 17 D/A CONVERTER

This Chapter provides an overview of the D/A converter, describes the register structure and functions, and describes the operarton of the D/A converter.

#### CHAPTER 18 100 kHz I2C INTERFACE

This section describes the functions and operation of the MB91360 series basic I2C interface. This interface allows operation up to 100 kHz and 8-bit-addressing.

#### CHAPTER 19 400 kHz I2C INTERFACE

This section describes the functions and operation of the fast I2C interface.

#### CHAPTER 20 16-BIT I/O TIMER

The MB91360 Series contains two 16-bit free-running timer modules, two output compare modules, and two input capture modules and supports four input channels and four output channels.

#### CHAPTER 21 ALARM COMPARATOR

This chapter provides an overview of the Alarm Comparator (also called Under/Overvoltage Detection), describes the register structure and functions, and describes the operation of the Alarm Comparator.

#### CHAPTER 22 POWER DOWN RESET

This Chapter provides an overview of the Power Down Reset, describes the register structure and functions, and describes the operation of the Power Down Reset Module

#### CHAPTER 23 SERIAL I/O INTERFACE (SIO)

This Chapter provides an overview of the Serial I/O Interface (SIO), describes the register structure and functions, and describes the operation of the SIO.

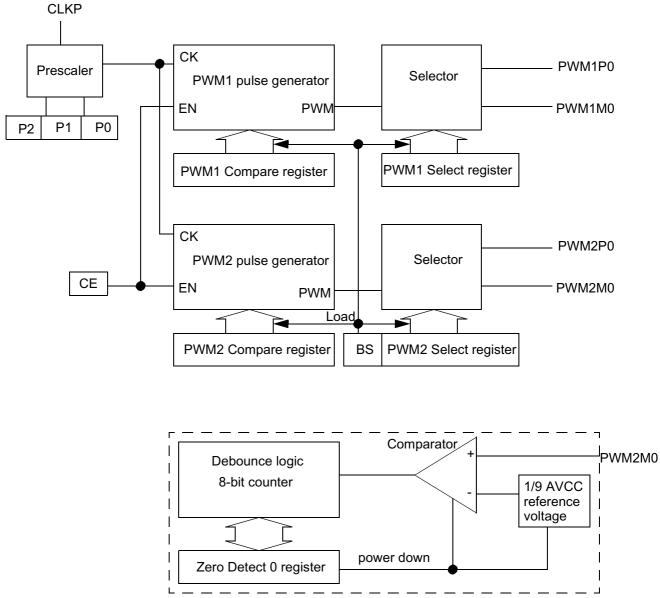

#### CHAPTER 24 SOUND GENERATOR

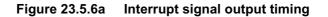

This Chapter provides an overview of the Sound Generator, describes the register structure and functions, and describe the operation of the Sound Generator.

#### CHAPTER 25 STEPPER MOTOR CONTROLLER

This Chapter provides an overview of the Stepper Motor Control Module, describe the register structure and functions, and described the operation of the Stepper Motor Control Module.

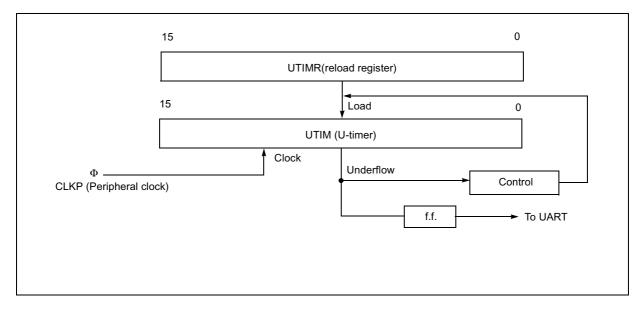

#### CHAPTER 26 U-TIMER

The U-timer (U-TIMER) is a 16-bit timer used to generate the baud rate for the UART. This chapter provides an overview of the U-timer, describes the register structure and functions, and describes the operation of the U-timer.

#### CHAPTER 27 UART

The UART is a serial I/O port for performing asynchronous (start bit synchronization) communications. This chapter provides an overview of the UART, describes the register structure and functions, and describes the operation of the UART.

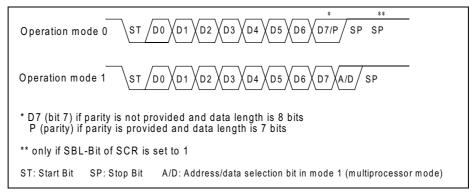

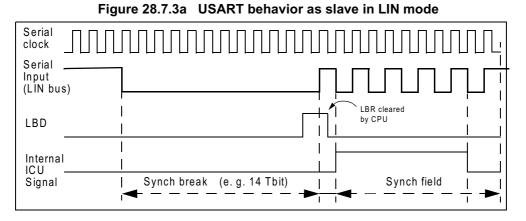

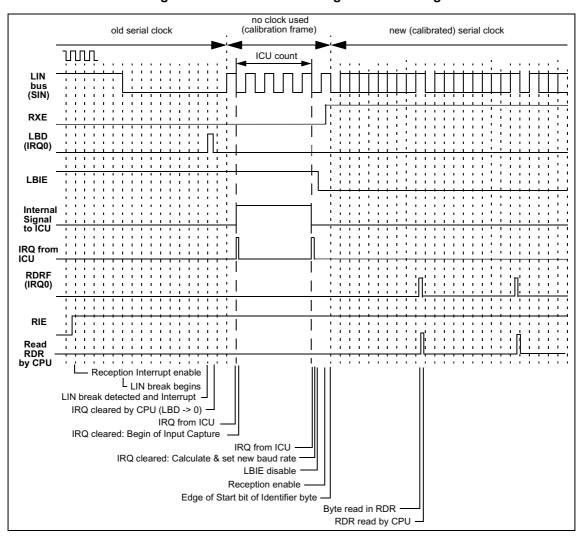

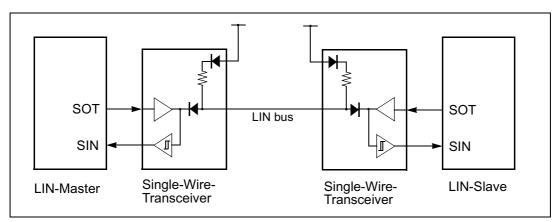

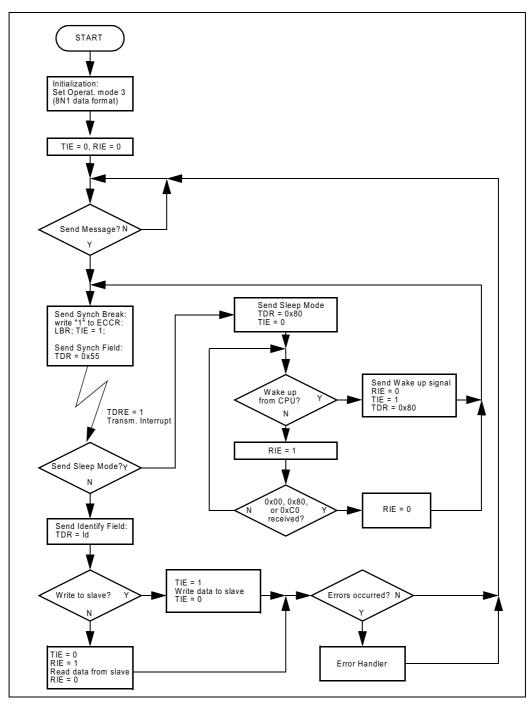

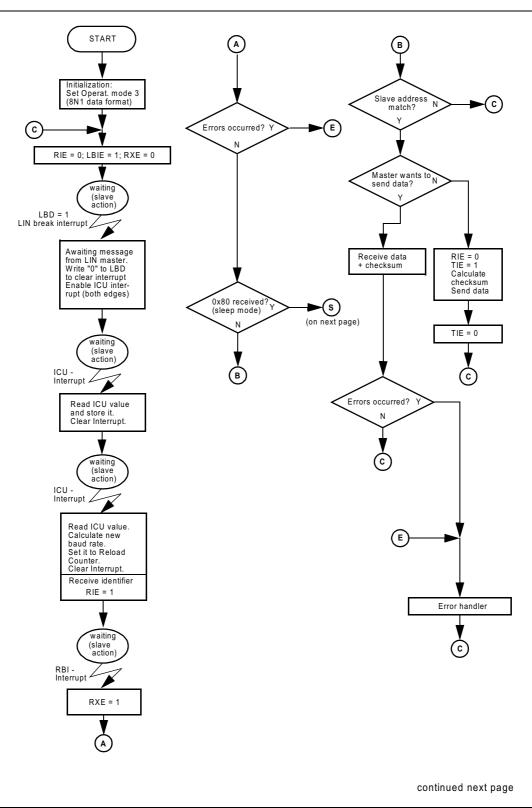

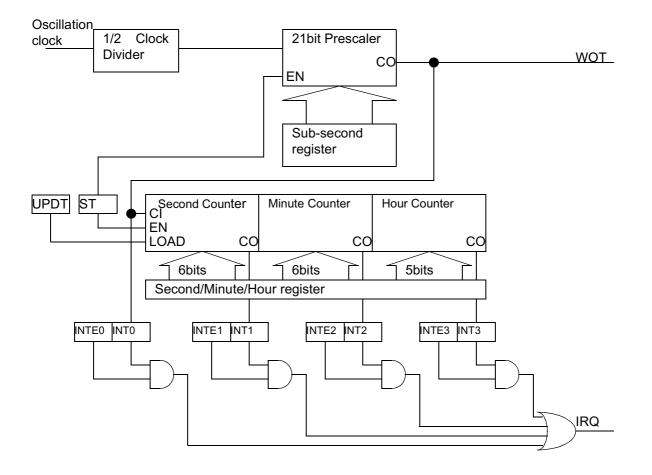

#### CHAPTER 28 USART WITH LIN-FUNCTIONALITY

This chapter explains the functions and operation of USART. The USART with LIN (Local Interconnect Network) - Function is a general-purpose serial data communication interface for performing synchronous or asynchronous communication with external devices.

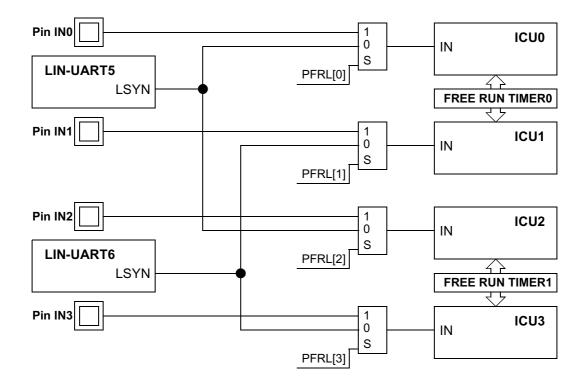

#### CHAPTER 29 REAL TIME CLOCK

This Chaper provides an overview of the Real Time Clock (also called Watchtimer), describes the register structure and functions, and describes the operation of RTC module.

#### CHAPTER 30 SUBCLOCK

This section describes the functions and operation of the subclock

#### CHAPTER 31 32kHz CLOCK CALIBRATION UNIT

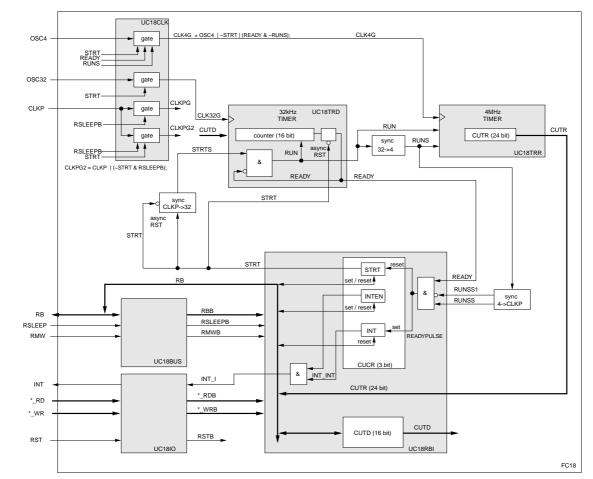

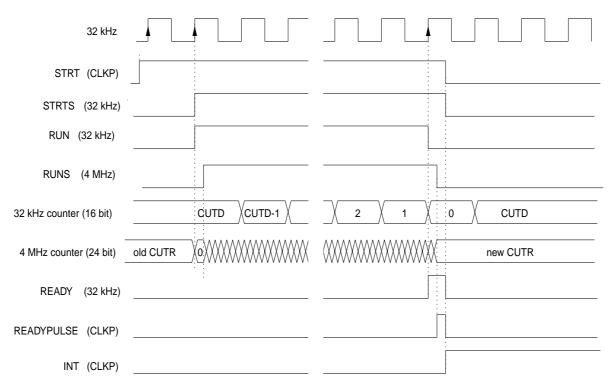

The 32kHz Clock Calibration Module provides possibilities to calibrate the 32kHz oscillation clock with respect to the 4MHz oscillation clock. This chapter gives an overview of the calibration unit, describes the registers and provides some application notes.

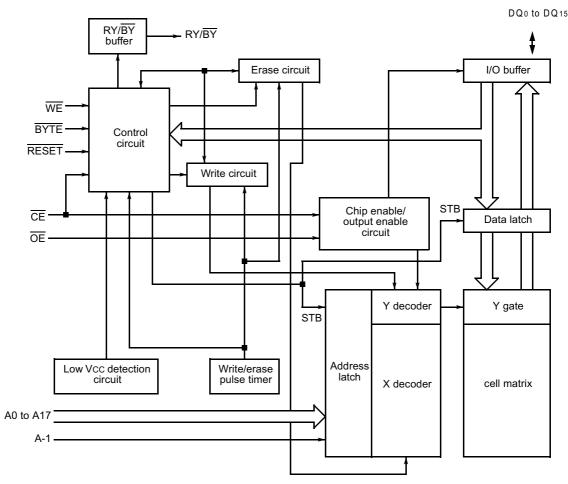

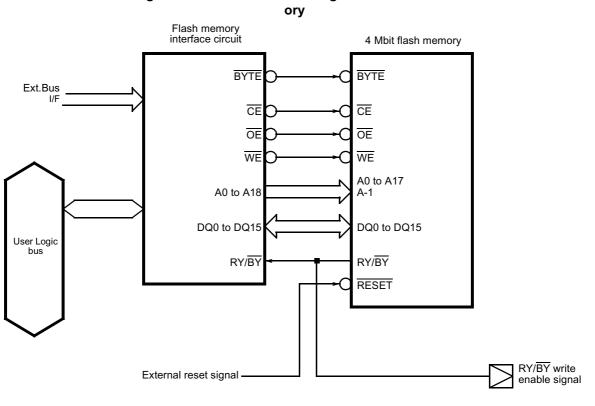

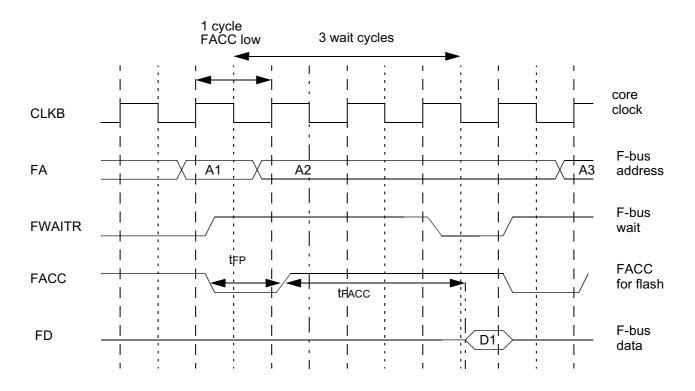

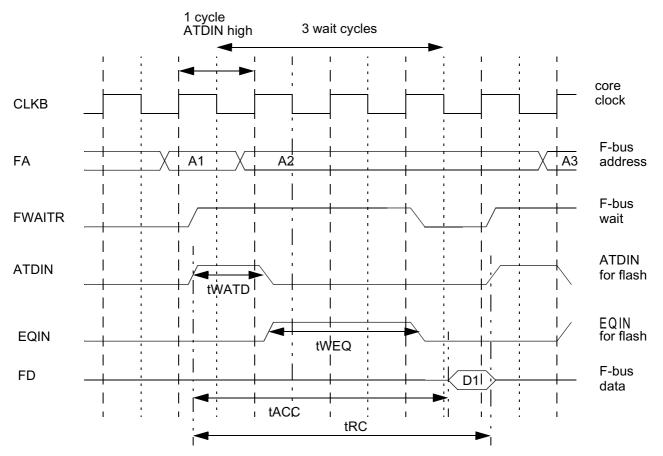

#### CHAPTER 32 FLASH MEMORY

MB91360 devices feature 256 KB, 512 KB or 768 KB of embedded flash memory. It is connected to the F-bus.

#### CHAPTER 33 EDSU

The Embedded Debug Support Unit (EDSU) is a module which enables basic in circuit debugging support functions on single chip FLASH MCU devices.

#### CHAPTER 34 ELECTRICAL SPECIFICATION

This Chapter provides information on maximum ratings, operating conditions and AC

specifications.

#### Appendices

The appendices contain details that could not be included in the main text and reference information for programming. These include the "I/O Map, " "Interrupt Vectors, " "Pin States in Each CPU State, and "Instructions".

#### Trademarks

FR is an abbreviation for FUJITSU RISC controller, and is a product of Fujitsu, Ltd.

<sup>•</sup> The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before ordering.

The information and circuit diagrams in this document are presented as examples of semiconductor device applications, and are not intended to be incorporated in devices for actual use. Also, FUJITSU is unable to assume responsibility for infringement of any patent rights or other rights of third parties arising from the use of this information or circuit diagrams.

<sup>•</sup> The products described in this document are designed, and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite).

Please note that Fujitsu will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products.

Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

<sup>•</sup> If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Law of Japan, the prior authorization by Japanese government will be required for export of those products from Japan.

# CONTENTS

| 1 | MB91 | 60 DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                  | 1                                      |

|---|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|   | 1.1  | MB91360 FEATURES                                                                                                                                                                                                                                                                                                                                                                                | . 2                                    |

|   | 1.2  | MB91360 PRODUCT LINEUP                                                                                                                                                                                                                                                                                                                                                                          | . 4                                    |

|   | 1.3  | PACKAGE DIMENSIONS                                                                                                                                                                                                                                                                                                                                                                              | . 8                                    |

|   | 1.4  | MB91360 BLOCK STRUCTURE                                                                                                                                                                                                                                                                                                                                                                         | . 9                                    |

|   | 1.5  | PIN ASSIGNMENT                                                                                                                                                                                                                                                                                                                                                                                  | 17                                     |

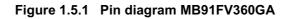

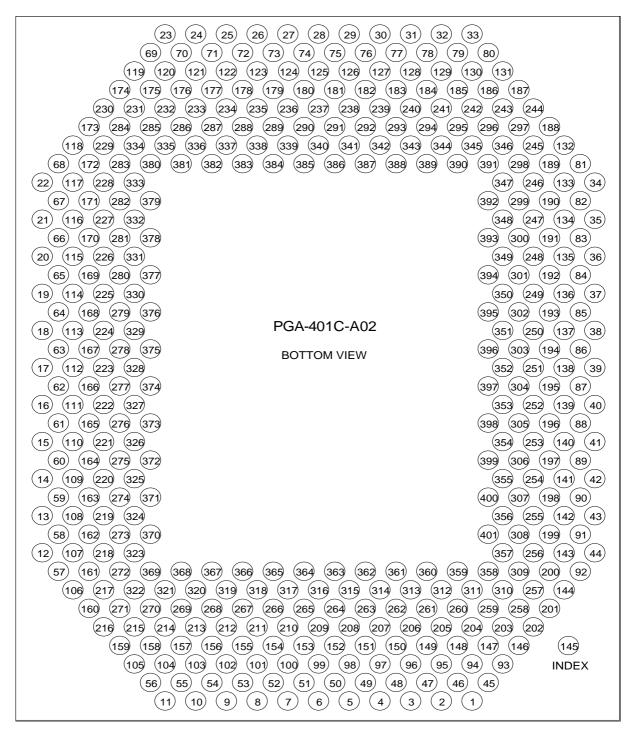

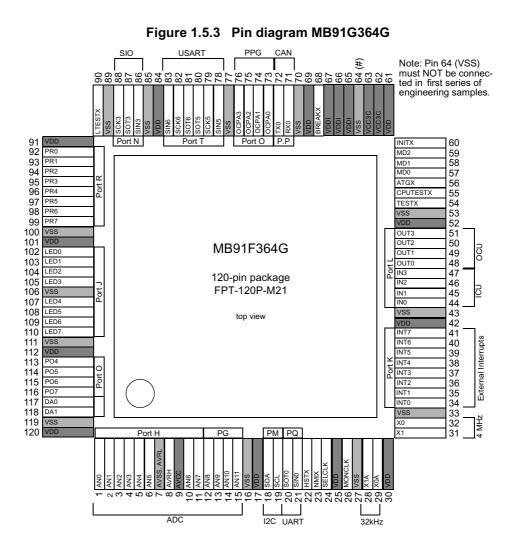

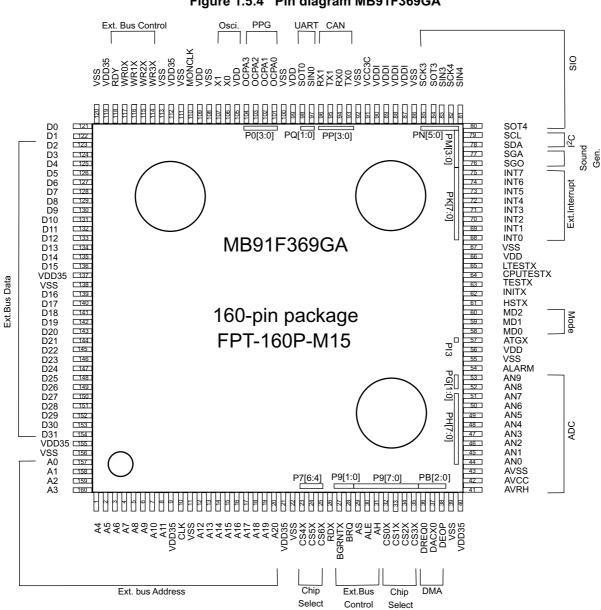

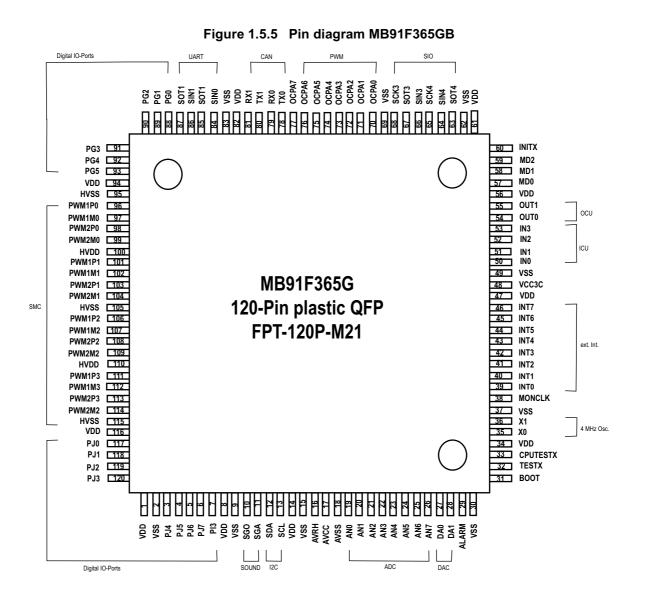

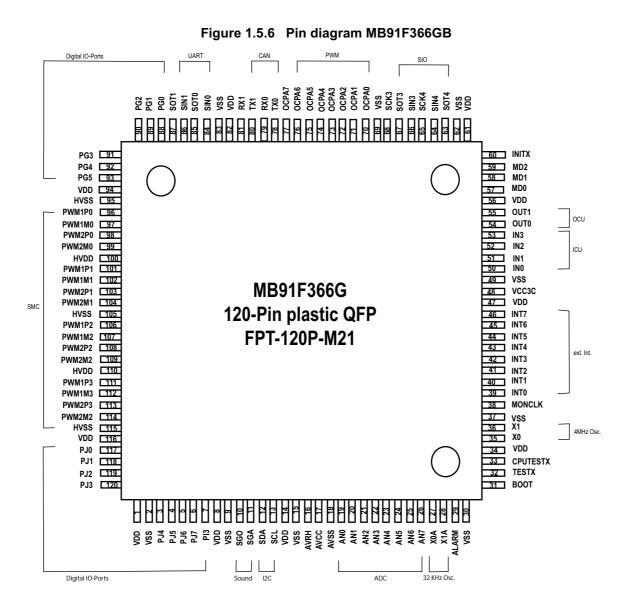

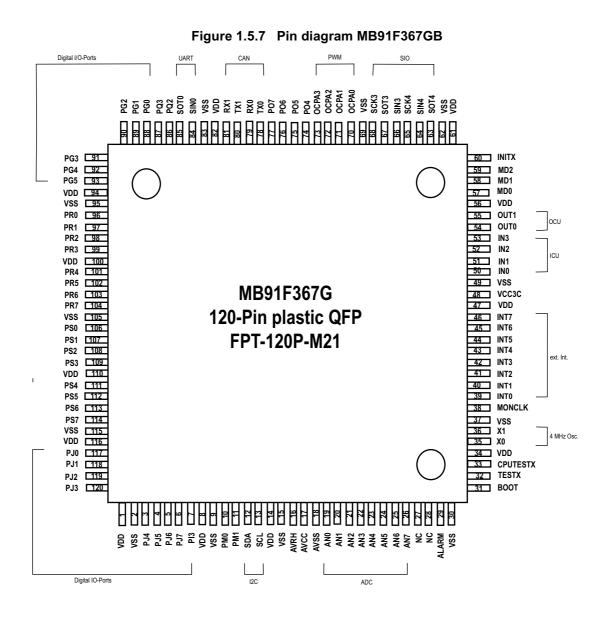

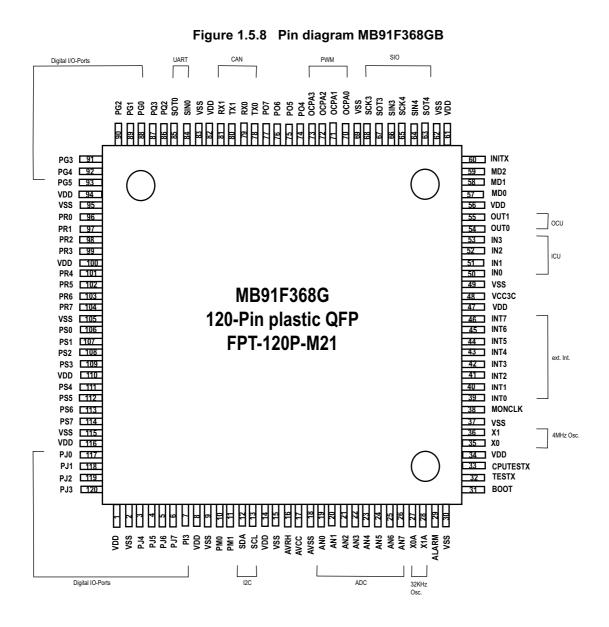

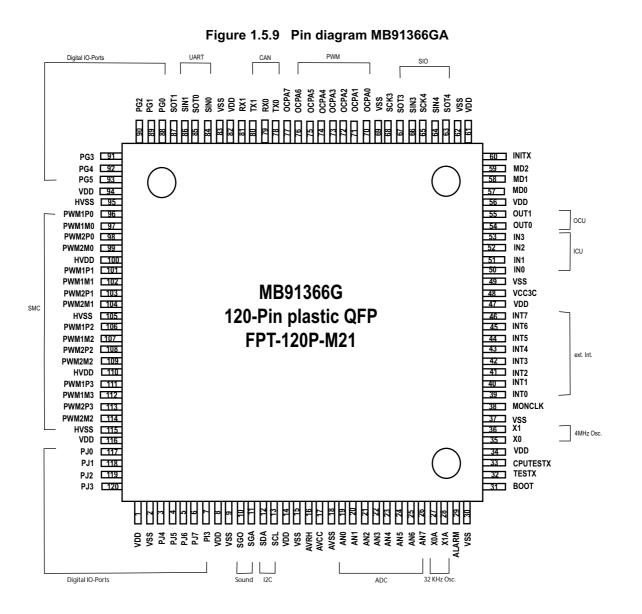

|   |      | <ul> <li>1.5.1 Pin Diagram MB91FV360GA</li> <li>1.5.2 Pin Diagram MB91F362GB</li> <li>1.5.3 Pin Diagram MB91F364G</li> <li>1.5.4 Pin Diagram MB91F369GA</li> <li>1.5.5 Pin Diagram MB91F365GB</li> <li>1.5.6 Pin Diagram MB91F366GB/MB91F376G</li> <li>1.5.7 Pin Diagram MB91F367GB</li> <li>1.5.8 Pin Diagram MB91F368GB</li> <li>1.5.9 Pin Diagram MB91F366GA</li> </ul>                      | 18<br>19<br>20<br>21<br>22<br>23<br>24 |

|   | 1.6  | I/O PINS AND THEIR FUNCTION                                                                                                                                                                                                                                                                                                                                                                     | 26                                     |

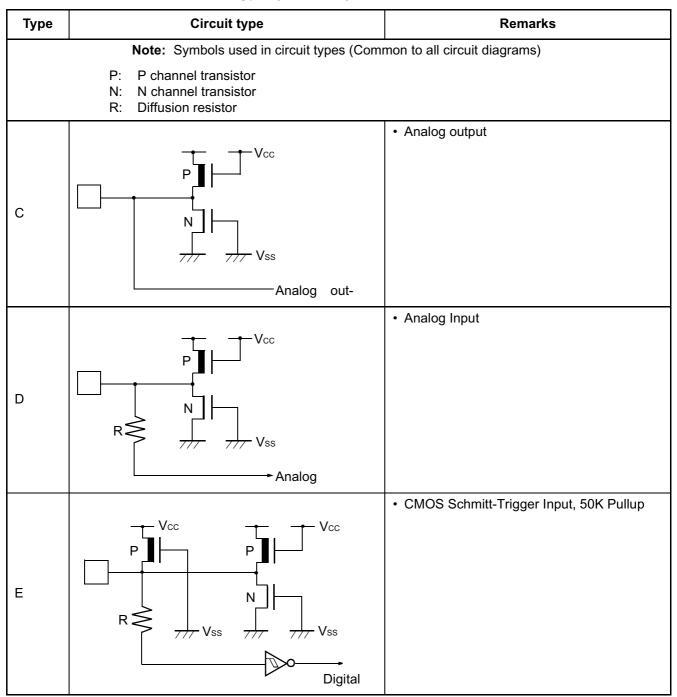

|   |      | <ul> <li>1.6.1 MB91FV360GA I/O Pins and Their Function</li> <li>1.6.2 MB91F362GB I/O Pins and Their Function</li> <li>1.6.3 MB91F364G I/O Pins and Their Function</li> <li>1.6.4 MB91F369GA I/O Pins and Their Function</li> <li>1.6.5 MB91F365GB/F366GB/F376G, MB91366GA I/O Pins</li> <li>1.6.6 MB91F367GB/F368GB I/O Pins and Their Function</li> <li>1.6.7 I/O Circuit Type List</li> </ul> | 38<br>44<br>48<br>53<br>57             |

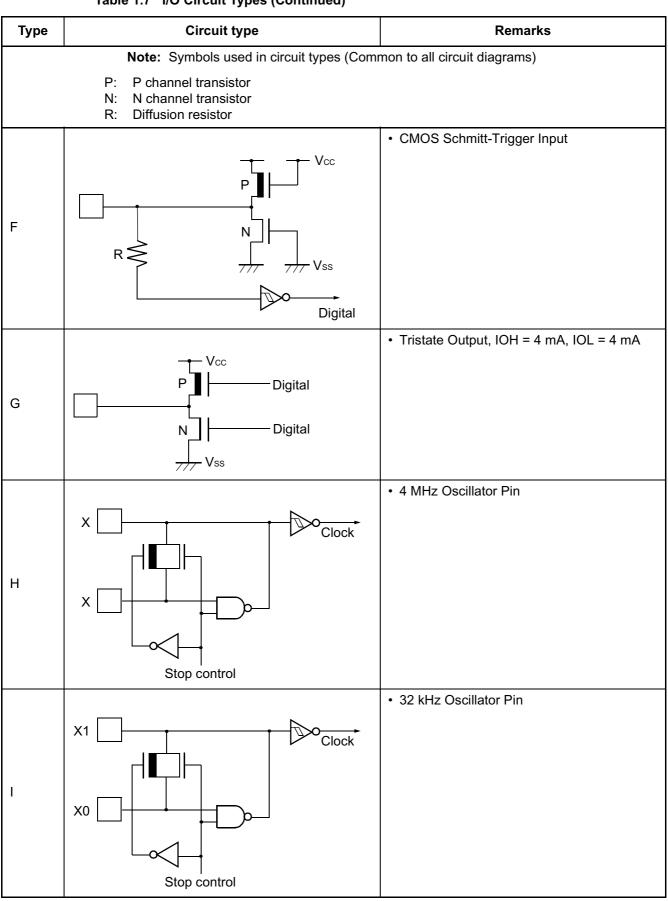

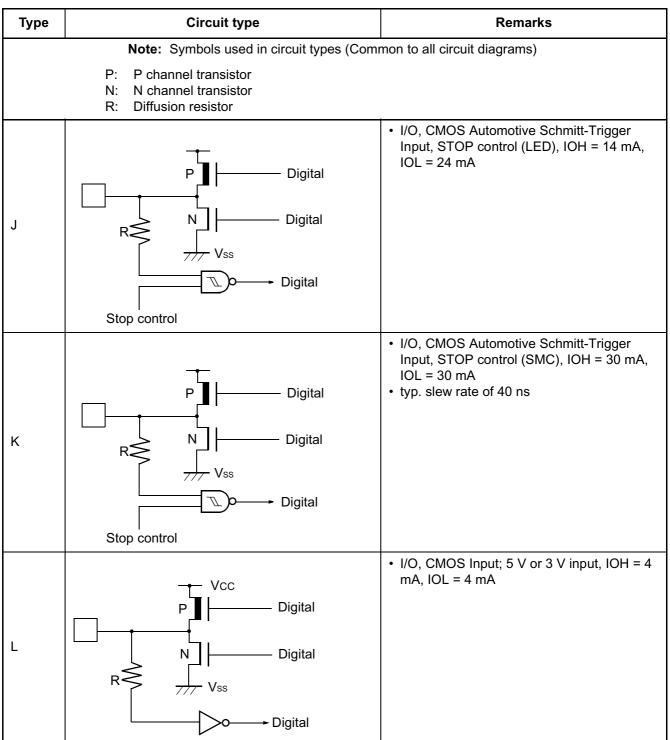

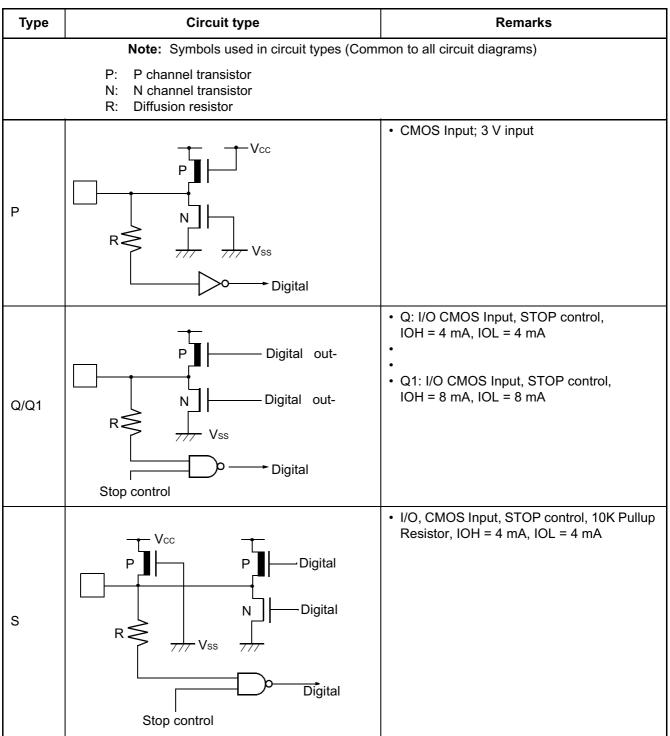

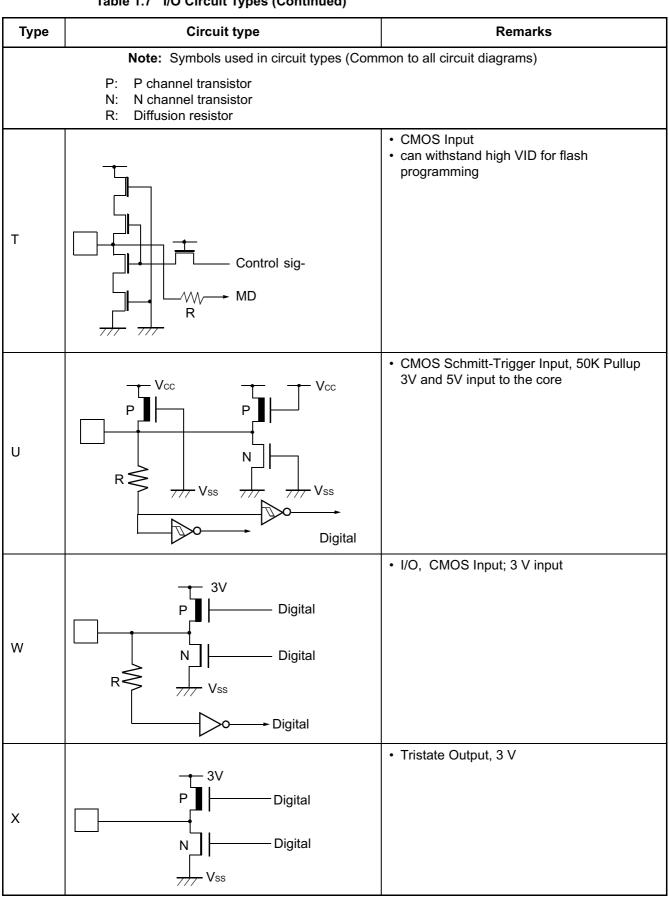

|   | 1.7  | I/O CIRCUIT TYPES                                                                                                                                                                                                                                                                                                                                                                               | 62                                     |

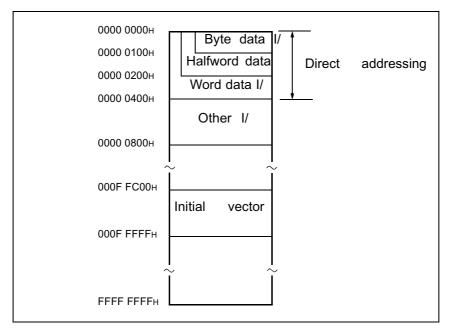

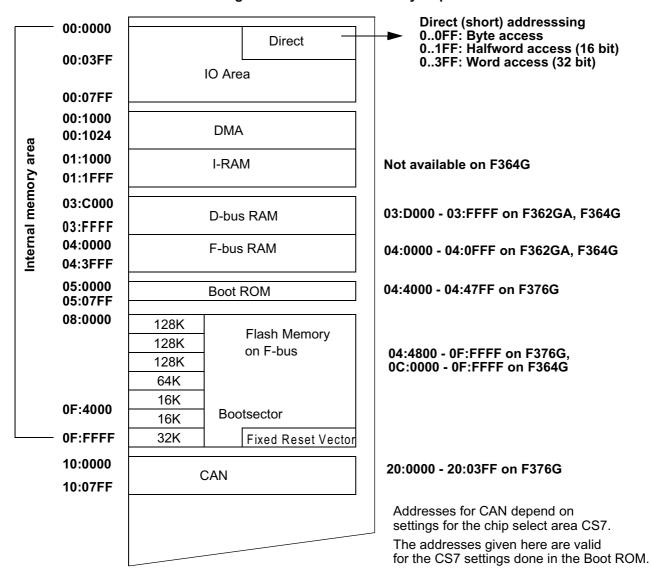

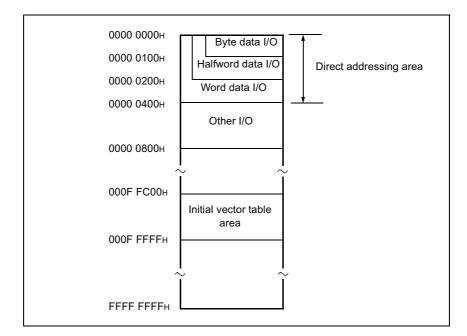

|   | 1.8  | MEMORY SPACE                                                                                                                                                                                                                                                                                                                                                                                    | 70                                     |

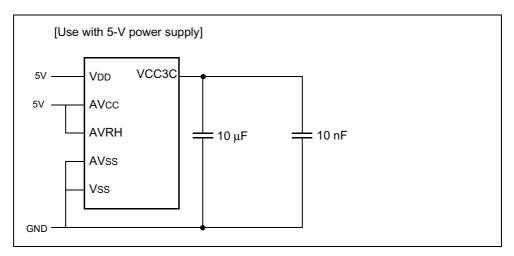

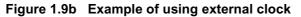

|   | 1.9  | HANDLING DEVICES                                                                                                                                                                                                                                                                                                                                                                                | 71                                     |

| 2 | CPU  |                                                                                                                                                                                                                                                                                                                                                                                                 | 75                                     |

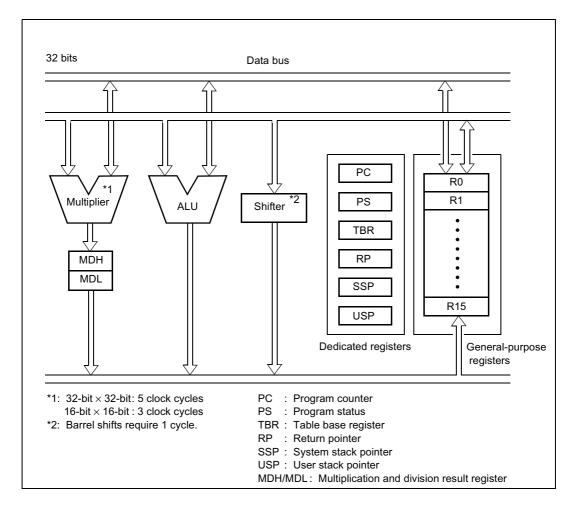

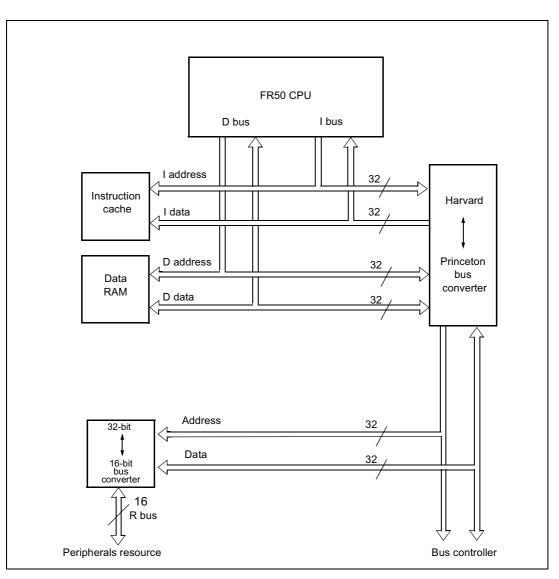

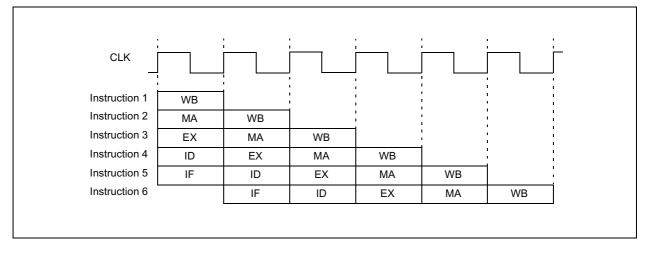

| - | 2.1  | CPU ARCHITECTURE                                                                                                                                                                                                                                                                                                                                                                                | -                                      |

|   | 2.2  | CPU HARDWARE STRUCTURE                                                                                                                                                                                                                                                                                                                                                                          |                                        |

|   | 2.3  | INTERNAL ARCHITECTURE OF THE FR50                                                                                                                                                                                                                                                                                                                                                               |                                        |

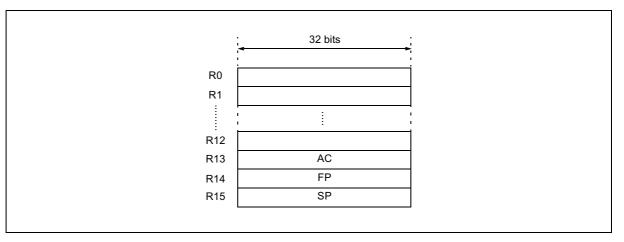

|   | 2.4  | PROGRAMMING MODEL                                                                                                                                                                                                                                                                                                                                                                               | 83                                     |

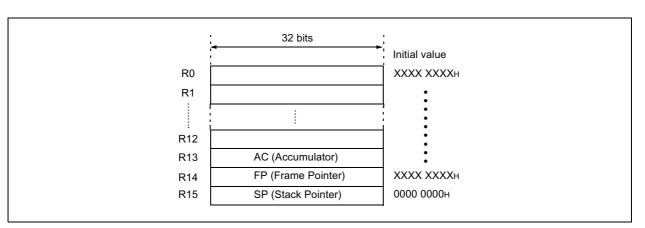

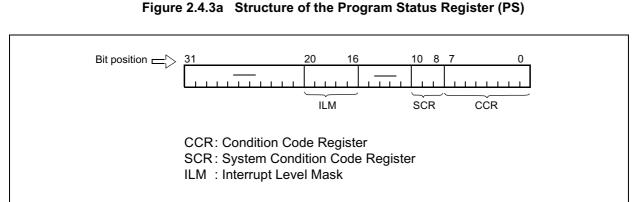

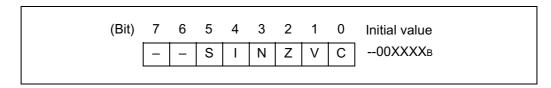

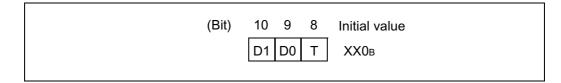

|   |      | <ul> <li>2.4.1 General-purpose Registers</li> <li>2.4.2 Dedicated Registers</li> <li>2.4.3 Program Status Register (PS)</li> </ul>                                                                                                                                                                                                                                                              | 85                                     |

|   | 2.5  | DATA STRUCTURE                                                                                                                                                                                                                                                                                                                                                                                  | 92                                     |

|   |      | 2.5.1 Word Alignment                                                                                                                                                                                                                                                                                                                                                                            | 93                                     |

|   | 2.6  | MEMORY MAP                                                                                                                                                                                                                                                                                                                                                                                      | 94                                     |

|   | 2.7  | INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                                    | 96                                     |

|   |      | <ul> <li>2.7.1 Overview of Instructions and Basic Instructions</li></ul>                                                                                                                                                                                                                                                                                                                        |                                        |

|   | 2.8  | EIT (EXCEPTIONS, INTERRUPT, TRAP)1                                                                                                                                                                                                                                                                                                                                                              | 05                                     |

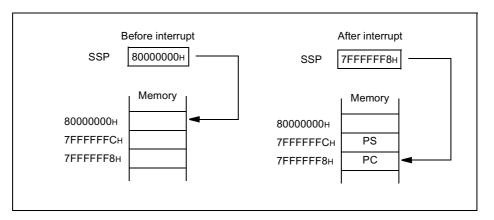

|   |      | 2.8.1 Multiple EIT Processing                                                                                                                                                                                                                                                                                                                                                                   | 11                                     |

|   |      | 2.8.2          | EIT Operation                                                                        | 113 |

|---|------|----------------|--------------------------------------------------------------------------------------|-----|

|   | 2.9  | RESET (I       | DEVICE INITIALIZATION)                                                               | 117 |

|   |      | 2.9.1          | Outline                                                                              | 117 |

|   |      | 2.9.2          | Reset Level                                                                          |     |

|   |      | 2.9.3          | Reset Source                                                                         |     |

|   |      | 2.9.4<br>2.9.5 | Reset Sequence<br>Oscillation Stabilization Waiting Time                             |     |

|   |      | 2.9.6          | Reset Mode                                                                           |     |

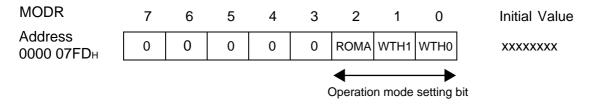

|   | 2.10 | OPERAT         | ING MODES                                                                            |     |

|   |      | 2.10.1         | Bus mode                                                                             |     |

|   |      | 2.10.1         | Mode Setting                                                                         |     |

|   |      | 2.10.3         | Fixed Vector                                                                         |     |

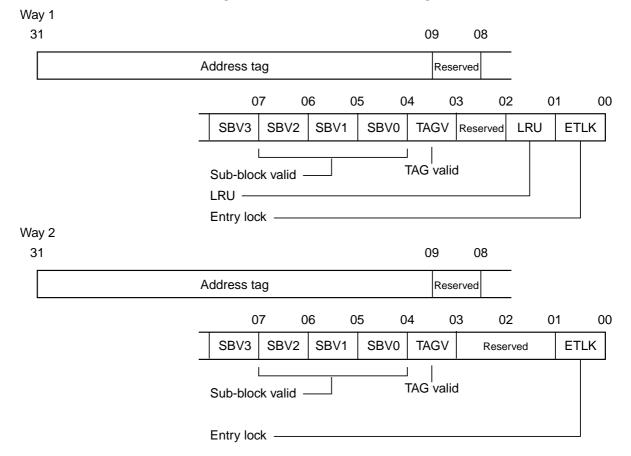

| 3 | INST | RUCTION        | N CACHE                                                                              | 129 |

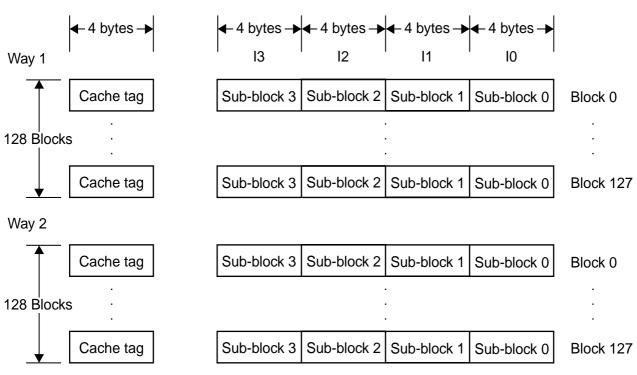

|   | 3.1  | GENERA         | AL DESCRIPTION                                                                       |     |

|   | 3.2  |                | DDY STRUCTURE                                                                        |     |

|   | 3.3  |                | S OPERATING MODE CONDITIONS                                                          |     |

|   | 3.4  |                | CTION CACHE SPACE FOR CACHING                                                        |     |

|   | 3.5  |                | FOR FR50 I-CACHE USAGE                                                               |     |

| _ |      |                |                                                                                      |     |

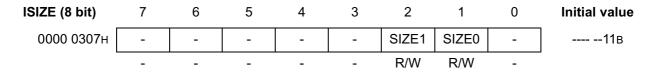

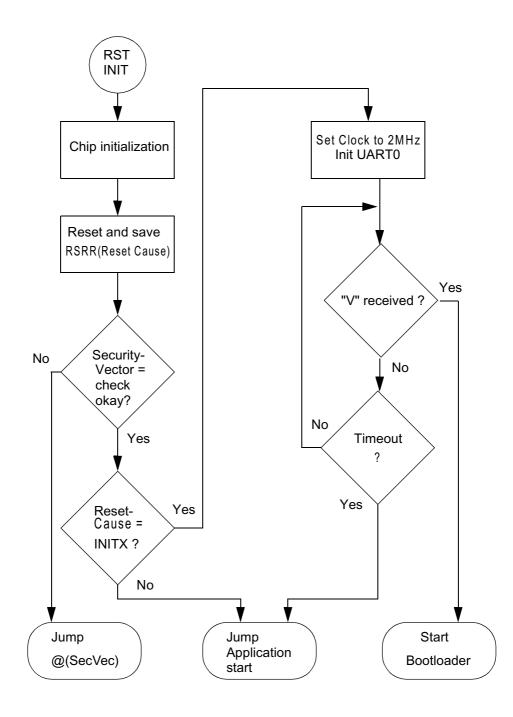

| 4 |      |                | CONFIGURATION REGISTER                                                               |     |

|   | 4.1  |                | OM                                                                                   |     |

|   | 4.2  | CONFIG         | URATION REGISTER (F362 MODE REGISTER F362MD)                                         | 144 |

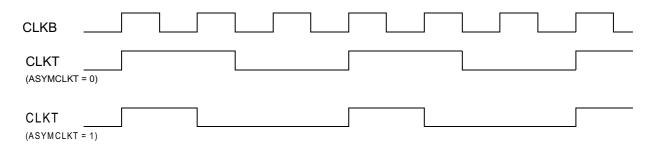

| 5 | CLOC | K GENE         | RATION AND DEVICE STATES                                                             | 147 |

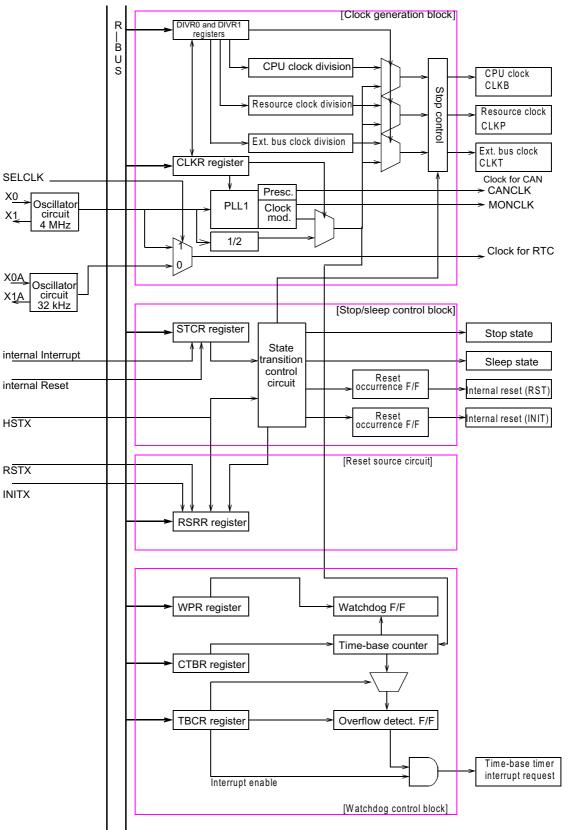

|   | 5.1  | CLOCK (        | GENERATION OUTLINE                                                                   | 149 |

|   | 5.2  | BASE CL        | OCK GENERATION                                                                       | 149 |

|   | 5.3  | PLL CON        | ITROL                                                                                | 150 |

|   |      | 5.3.1          | PLL Oscillation Enable/Disable                                                       |     |

|   |      | 5.3.2          | PLL Multiply Rate                                                                    |     |

|   | 5.4  |                | GIMES                                                                                |     |

|   | 5.5  | CLOCK [        | DISTRIBUTION                                                                         | 153 |

|   | 5.6  | CLOCK          | PULSE DIVISION                                                                       | 155 |

|   | 5.7  | CLOCK (        | GENERATION CONTROL                                                                   | 156 |

|   | 5.8  | REGISTE        | ERS IN CLOCK GENERATION CONTROL BLOCK                                                | 157 |

|   |      | 5.8.1          | RSRR: Reset Source Register, Watchdog Timer Control Register                         |     |

|   |      | 5.8.2<br>5.8.3 | STCR: Standby Control Register<br>TBCR: Time-base counter control register           |     |

|   |      | 5.8.4          | CTBR: Time-base counter clear register                                               |     |

|   |      | 5.8.5          | CLKR: Clock source control register                                                  |     |

|   |      | 5.8.6          | WPR Watchdog reset generation postponement register                                  |     |

|   |      | 5.8.7          | DIVR0: Base clock division setting register 0                                        |     |

|   |      | 5.8.8<br>5.8.9 | DIVR1: Base clock division setting register 1<br>CMCR: Clock Control for CAN Modules |     |

|   |      | 5.8.10         | MONCLK pin                                                                           |     |

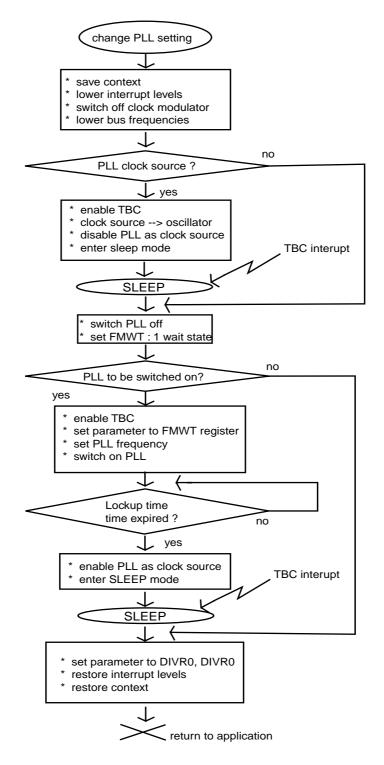

|   | 5.9  | SWITCH         | ING FROM/TO CLOCK SOURCE PLL                                                         |     |

|   |      | 5.9.1          | Introduction                                                                         |     |

|   |      |                |                                                                                      |     |

|   |      | 5.9.2<br>5.9.3<br>5.9.4              | Reduction of Internal Voltage Change<br>Clock Modulator<br>Procedure                                   | 174        |

|---|------|--------------------------------------|--------------------------------------------------------------------------------------------------------|------------|

|   | 5.10 | CLOCK                                | CONTROL SECTION RESOURCES                                                                              | 176        |

|   |      | 5.10.1                               | Time-base Counter                                                                                      | 176        |

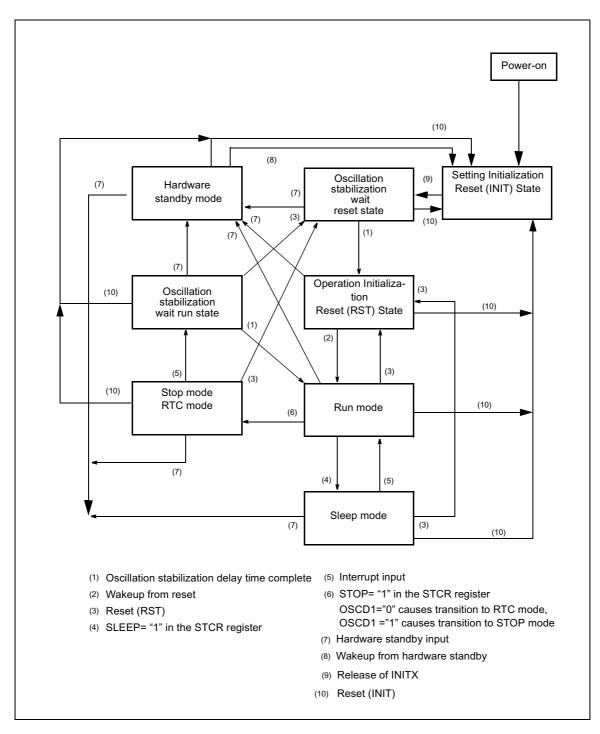

|   | 5.11 | DEVICE                               | E STATE CONTROL                                                                                        | 179        |

|   |      | 5.11.1<br>5.11.2                     | Device States and State Transition<br>Priority Of Each State Transition Request                        |            |

|   | 5.12 | LOW PO                               | OWER CONSUMPTION MODES                                                                                 | 182        |

|   |      | 5.12.1<br>5.12.2<br>5.12.3<br>5.12.4 | Sleep Mode<br>Stop Mode/RTC Mode<br>Hardware Standby Mode<br>Transition from 4MHz RTC Mode to RUN Mode | 184<br>185 |

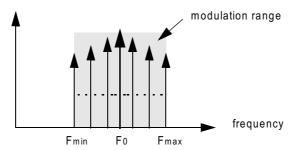

| 6 |      |                                      | OULATOR                                                                                                |            |

| U | 6.1  |                                      |                                                                                                        | -          |

|   | 6.2  |                                      | IEW                                                                                                    |            |

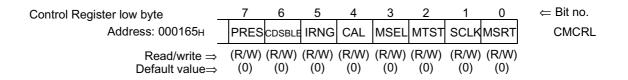

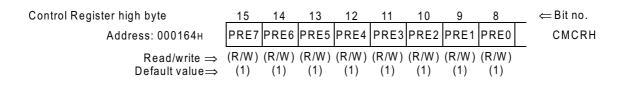

|   | 0.2  |                                      | Control Register (CMCR)                                                                                |            |

|   |      | 6.2.1<br>6.2.2                       | Modulation Parameter Register (CMPR)                                                                   |            |

|   |      | 6.2.3                                | Frequency Resolution Setting Register (CMLS03)                                                         |            |

|   |      | 6.2.4                                | Random Number Generator and Observer Register (CMLT03)                                                 | 200        |

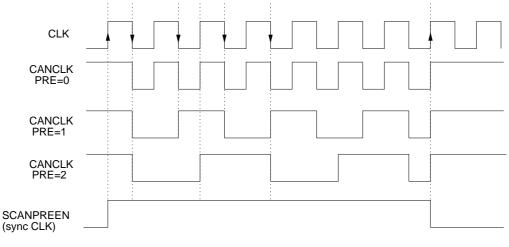

|   |      | 6.2.5                                | Automatic Calibration Reload Timer Value (CMAC)                                                        |            |

|   |      | 6.2.6                                | Status Register (CMTS)                                                                                 |            |

|   | 6.3  |                                      | DIX                                                                                                    |            |

|   |      | 6.3.1                                | Modulation Parameter selection                                                                         |            |

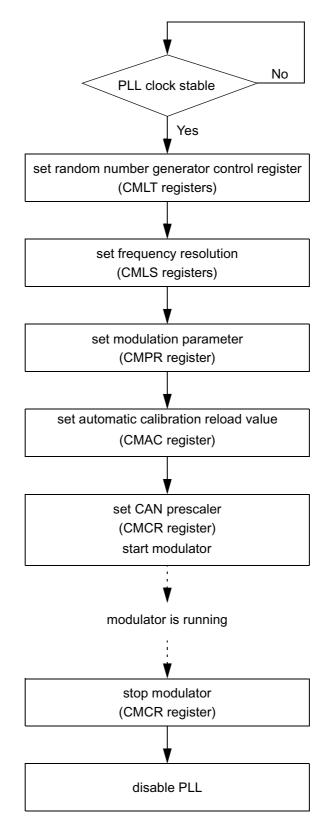

|   |      | 6.3.2                                | Configuration Flowchart                                                                                |            |

|   |      | 6.3.3<br>6.3.4                       | Example program<br>Possible Settings                                                                   |            |

| - |      |                                      | ·                                                                                                      |            |

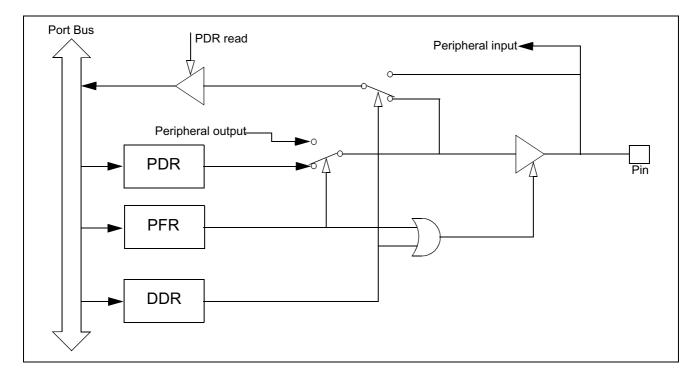

| 7 |      |                                      |                                                                                                        |            |

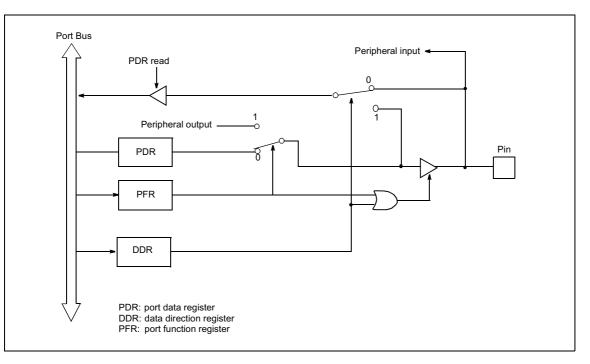

|   | 7.1  | I/O POF                              | RTS AND REGISTER CONFIGURATION                                                                         |            |

|   |      | 7.1.1                                | Port Data Registers                                                                                    |            |

|   |      | 7.1.2<br>7.1.3                       | Data Direction Registers (DDR)                                                                         |            |

|   | 7.0  |                                      |                                                                                                        |            |

|   | 7.2  | PORTE                                | FUNCTION REGISTER SETTINGS                                                                             |            |

| 8 | EXTE | RNAL E                               | BUS INTERFACE                                                                                          | 229        |

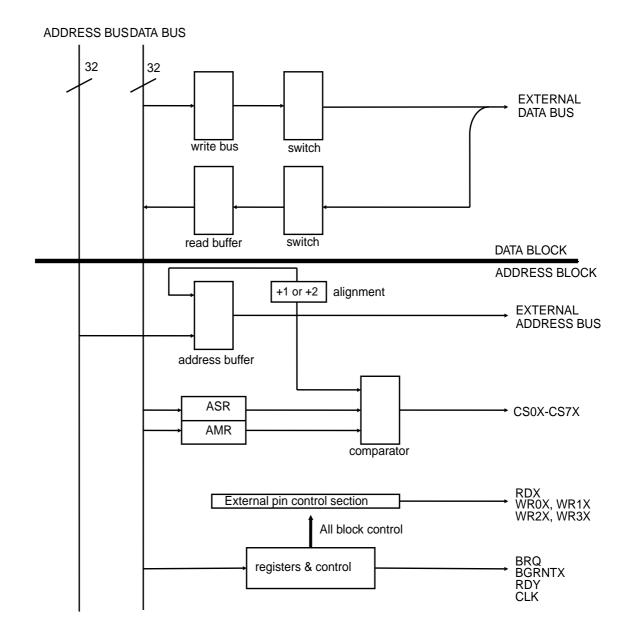

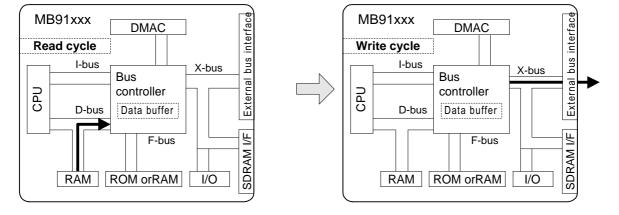

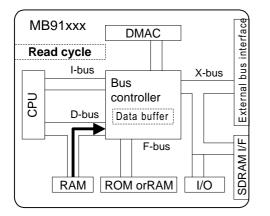

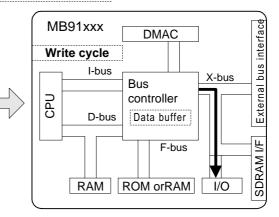

|   | 8.1  | BUS IN                               | TERFACE                                                                                                | 230        |

|   |      | 8.1.1                                | Features                                                                                               | 230        |

|   |      | 8.1.2                                | Block Diagram                                                                                          |            |

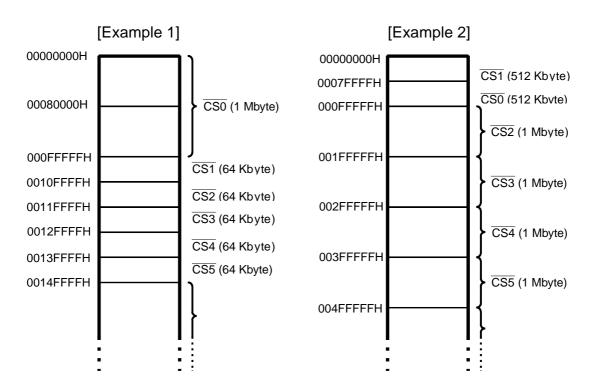

|   |      | 8.1.3                                | Overview                                                                                               |            |

|   |      | 8.1.4<br>8.1.5                       | Register List<br>Description of Registers                                                              |            |

|   | 0.0  |                                      |                                                                                                        |            |

|   | 8.2  |                                      |                                                                                                        |            |

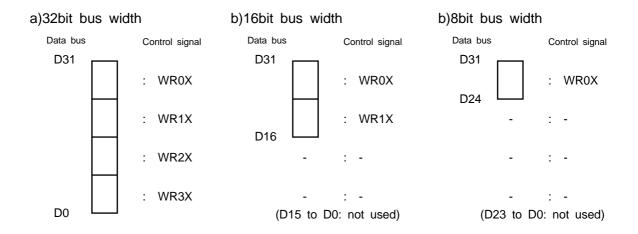

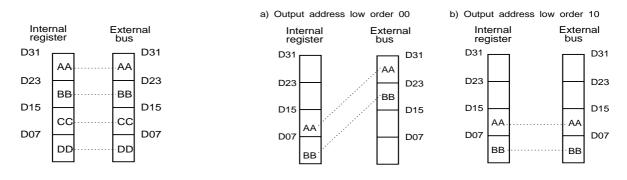

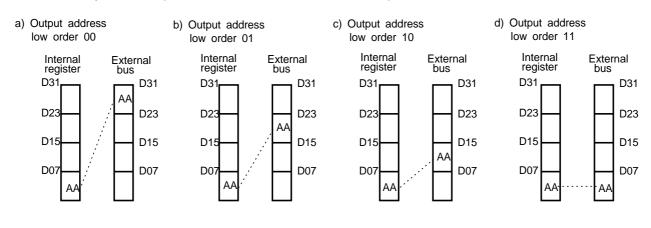

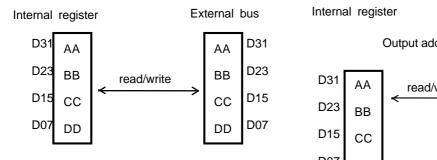

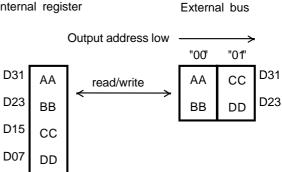

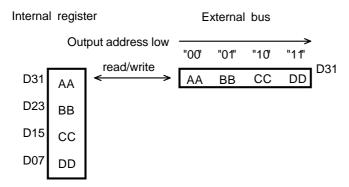

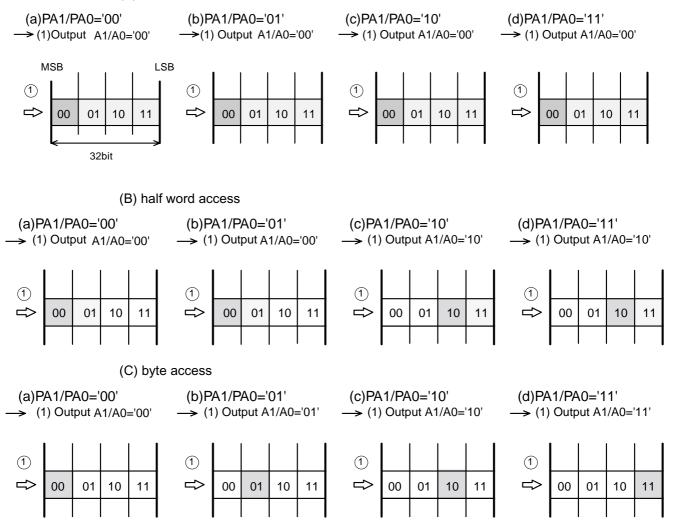

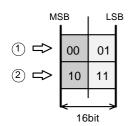

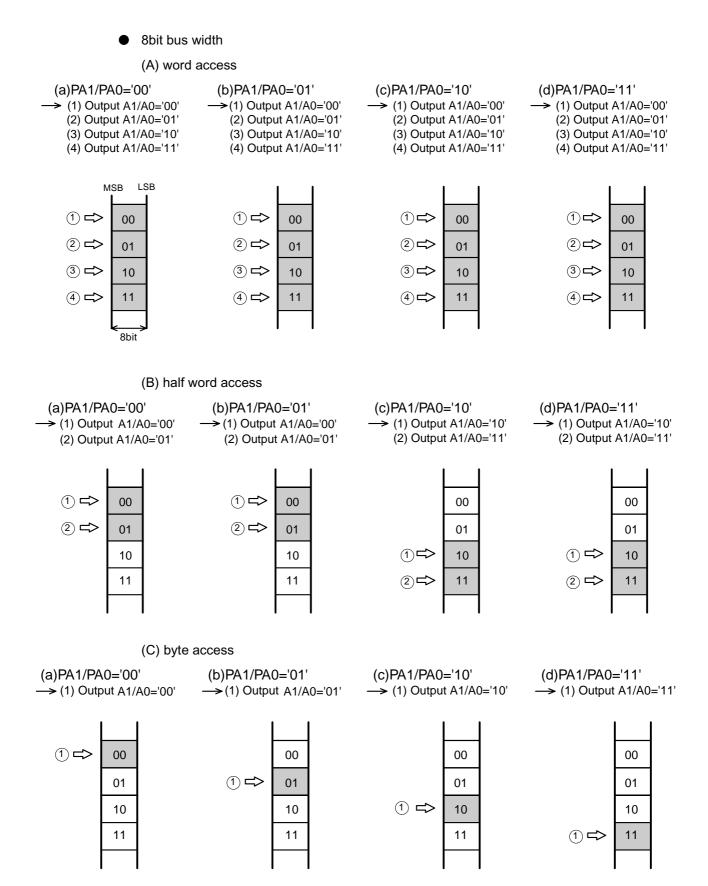

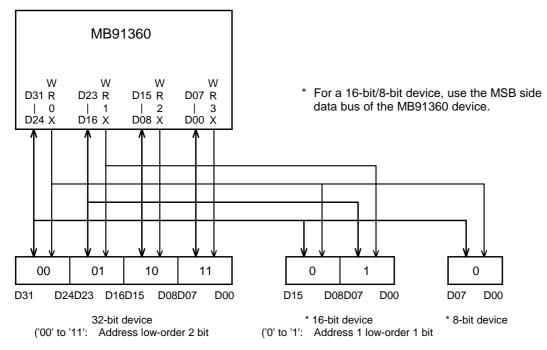

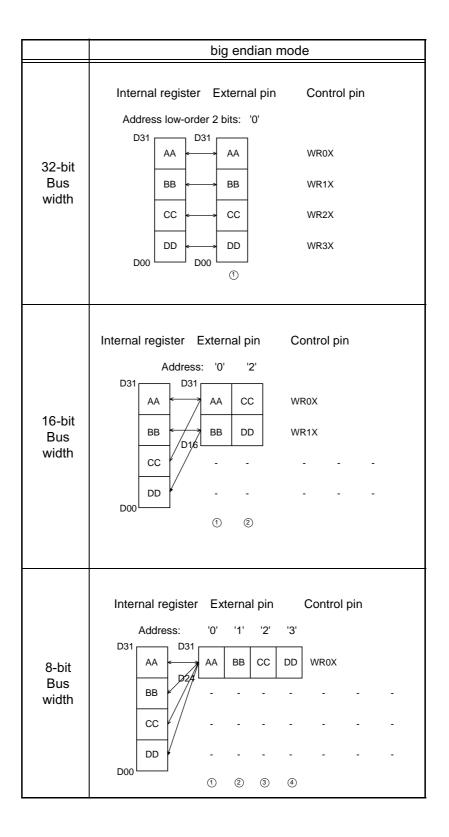

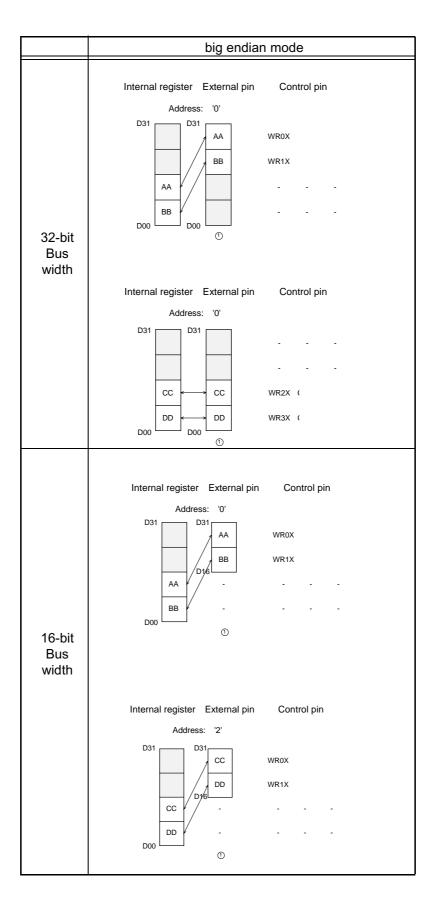

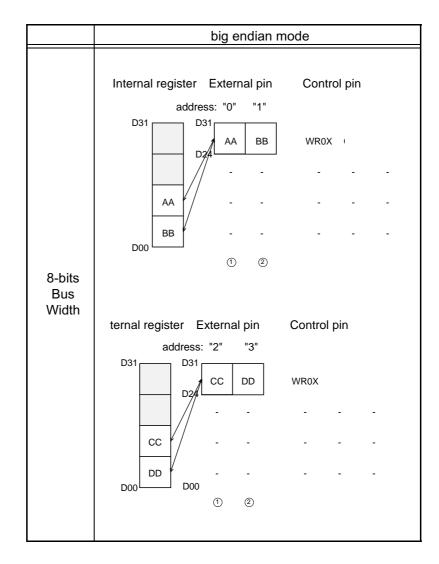

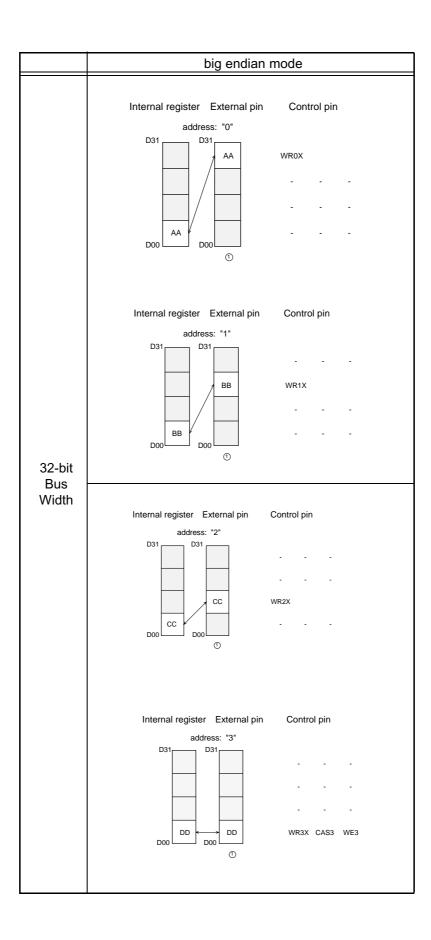

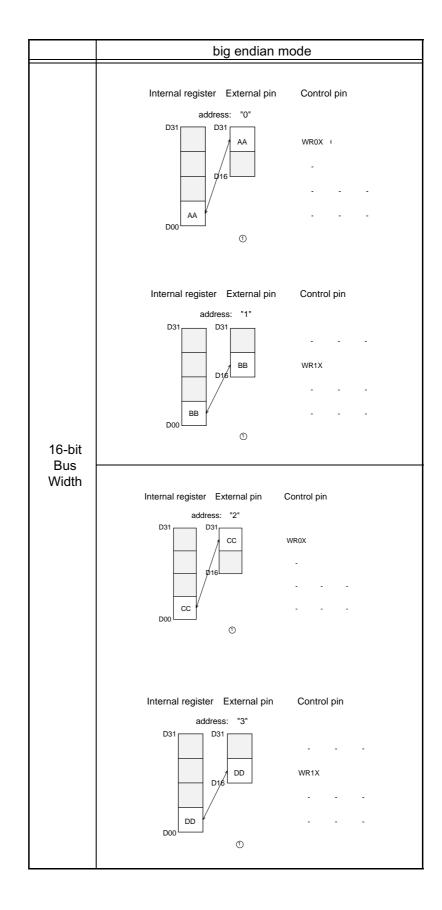

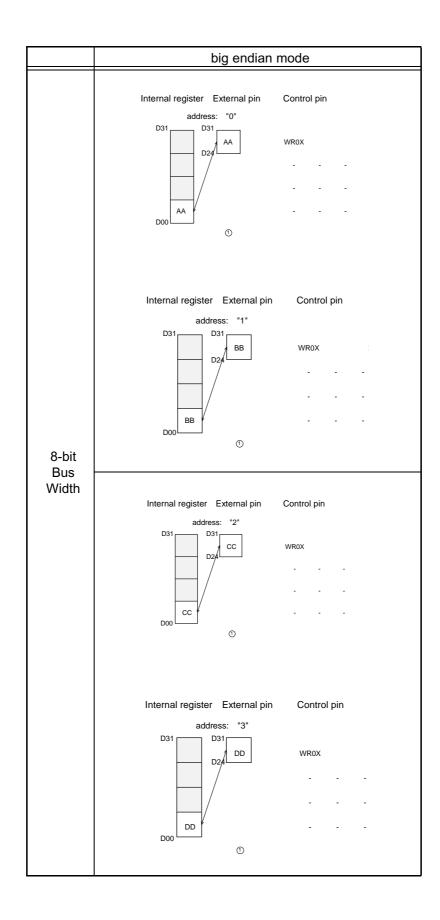

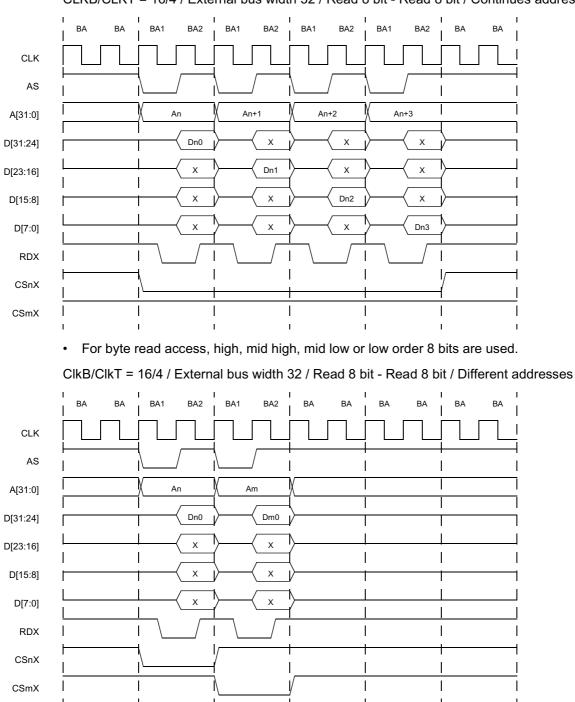

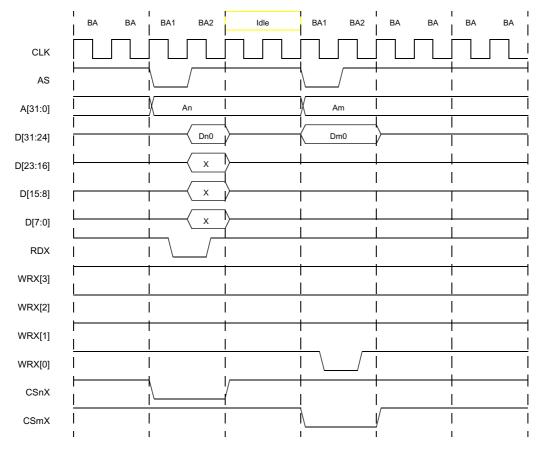

|   |      | 8.2.1<br>8.2.2                       | Relationship between Data Bus Width and Control Signal<br>Big-endian Bus Access                        |            |

|   |      | 8.2.2<br>8.2.3                       | External Bus Access                                                                                    |            |

|   | 8.3  |                                      | <br>GNALS                                                                                              |            |

|   | 0.0  | 200.00                               |                                                                                                        |            |

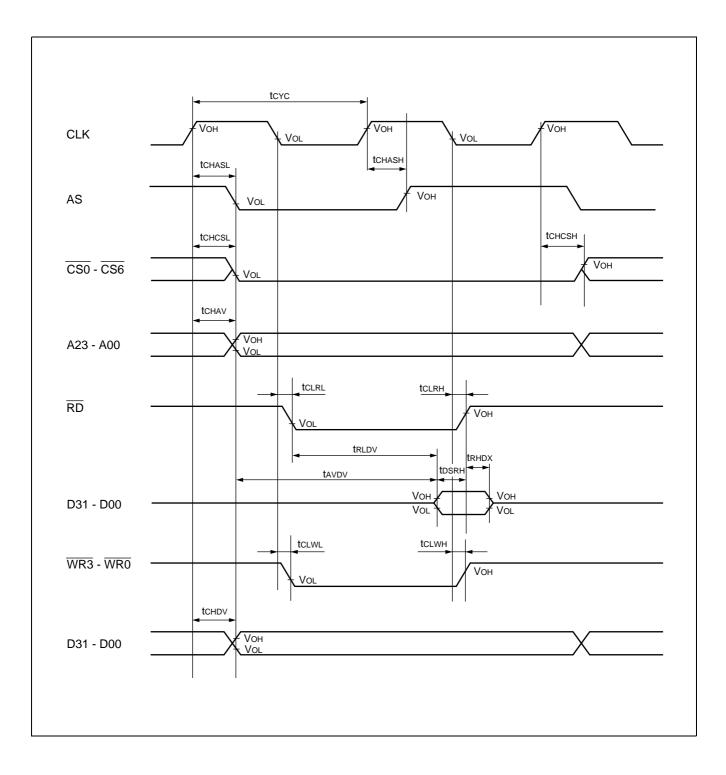

|    | 8.4   | BUS TIMING                                     |                                                                                                                                                                                                                                                      |            |  |

|----|-------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|

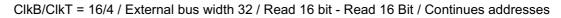

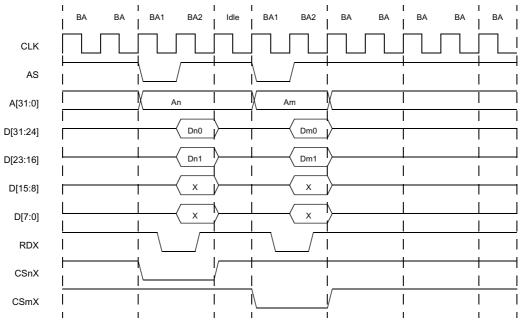

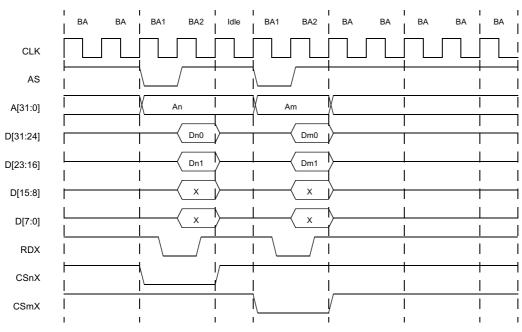

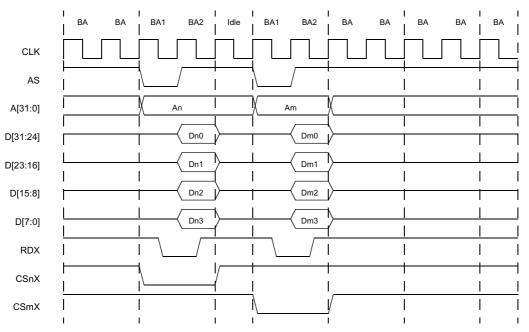

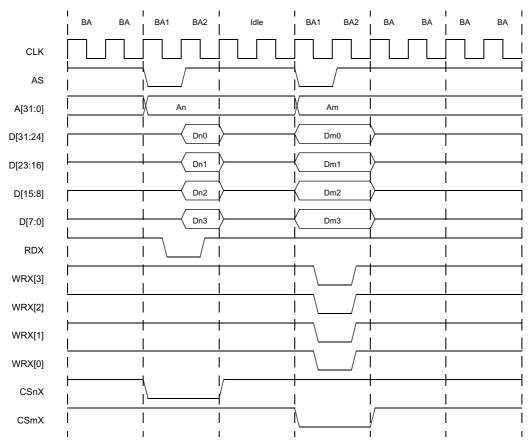

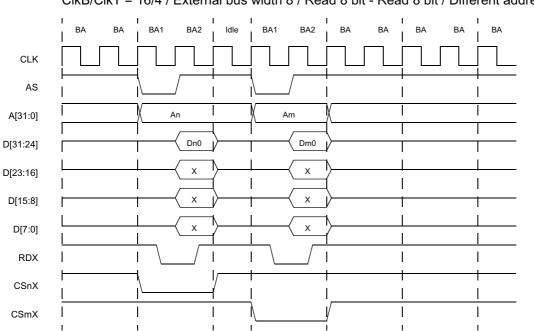

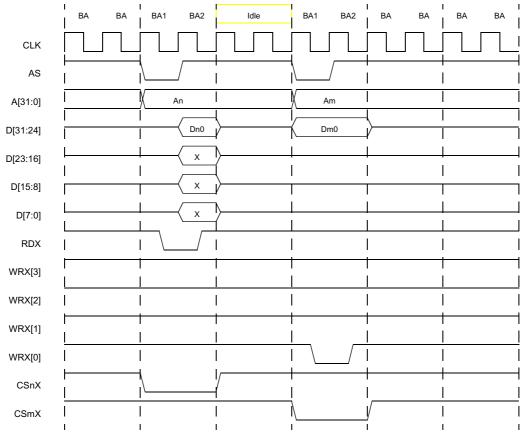

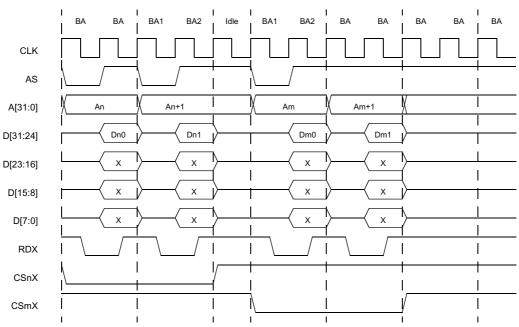

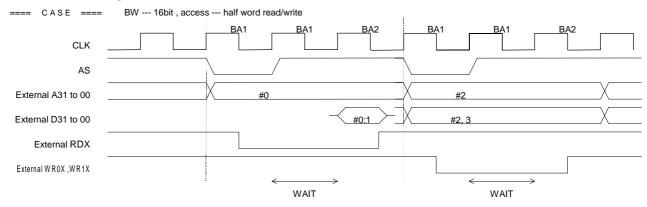

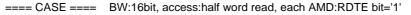

|    |       | 8.4.1<br>8.4.2<br>8.4.3<br>8.4.4               | Normal Bus Access<br>32 Bit Bus Width<br>8 Bit Bus Width<br>Idle Cycles                                                                                                                                                                              | 262<br>266 |  |

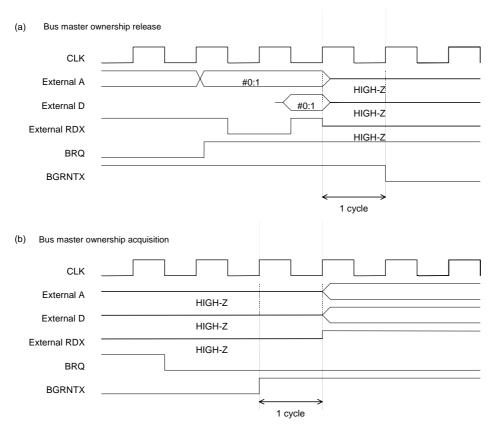

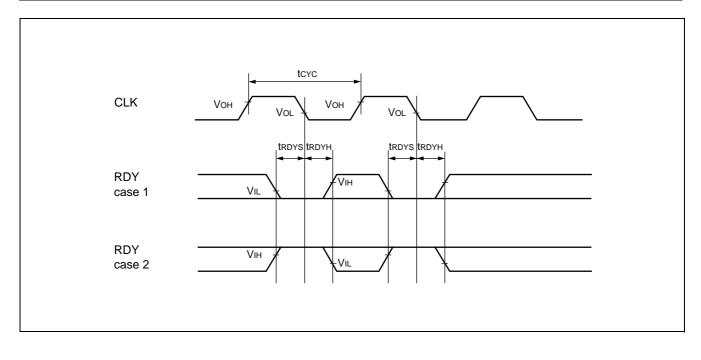

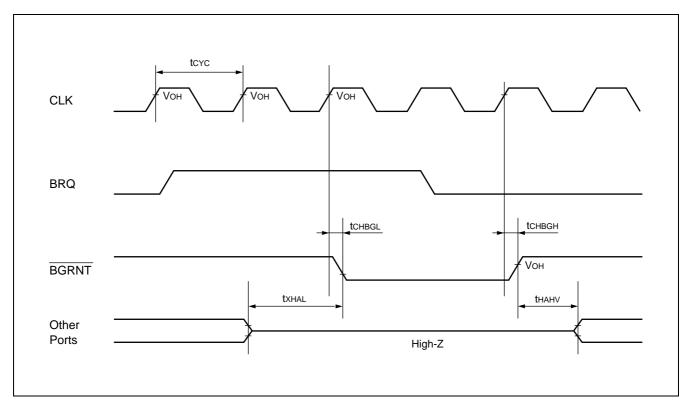

|    |       | 8.4.5<br>8.4.6                                 | Wait Cycle Operation<br>External Bus Request                                                                                                                                                                                                         |            |  |

|    | 8.5   |                                                | HE BUS INTERFACE AS GENERAL I/O PORTS                                                                                                                                                                                                                |            |  |

|    |       | 8.5.1                                          | Introduction                                                                                                                                                                                                                                         |            |  |

|    |       | 8.5.2                                          | Precausions                                                                                                                                                                                                                                          |            |  |

|    |       | 8.5.3<br>8.5.4                                 | Used Registers<br>Software Workaround, if CAN is not used                                                                                                                                                                                            |            |  |

|    |       | 8.5.5                                          | Software Workaround, if CAN is used                                                                                                                                                                                                                  |            |  |

| 9  | INTEF |                                                | CONTROLLER                                                                                                                                                                                                                                           | 277        |  |

|    | 9.1   | OVERVIE                                        | EW                                                                                                                                                                                                                                                   |            |  |

|    | 9.2   | LIST OF I                                      | REGISTERS                                                                                                                                                                                                                                            |            |  |

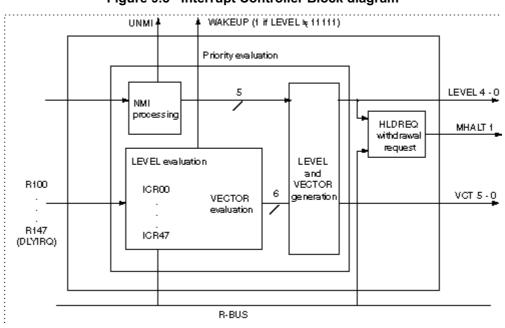

|    | 9.3   | BLOCK D                                        | DIAGRAM                                                                                                                                                                                                                                              |            |  |

|    | 9.4   | DETAILE                                        | D EXPLANATION OF REGISTERS                                                                                                                                                                                                                           | 282        |  |

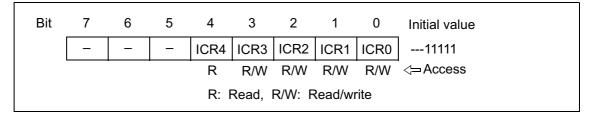

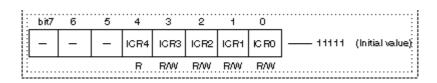

|    |       | 9.4.1                                          | ICR (Interrupt Control Register)                                                                                                                                                                                                                     |            |  |

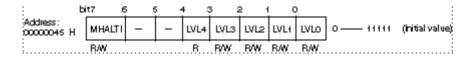

|    |       | 9.4.2                                          | HRCL (Hold Request Cancel Level register)                                                                                                                                                                                                            |            |  |

|    | 9.5   |                                                |                                                                                                                                                                                                                                                      |            |  |

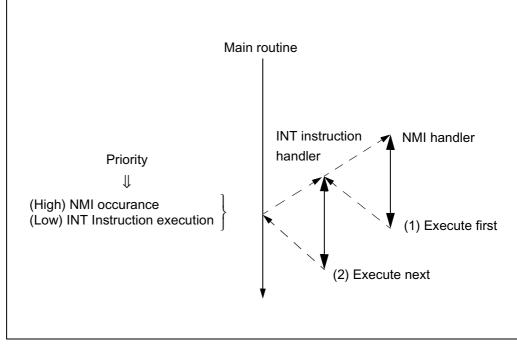

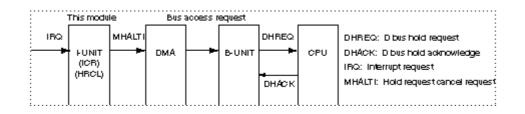

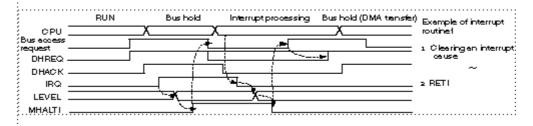

|    |       | 9.5.1<br>9.5.2<br>9.5.3<br>9.5.4<br>9.5.5      | Priority evaluation<br>NMI (Non-Maskable Interrupt)<br>Hold request cancel request (HRCL)<br>Recovery from standby mode (stop/sleep)<br>Example of using the HRCL function                                                                           |            |  |

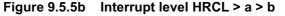

| 10 | EXTE  | RNAL IN                                        | ITERRUPT/NMI CONTROLLER                                                                                                                                                                                                                              | 289        |  |

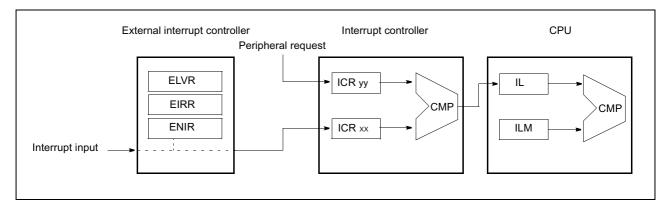

|    | 10.1  | OVERVIE                                        | W OF THE EXTERNAL INTERUPT CONTROLLER                                                                                                                                                                                                                | 290        |  |

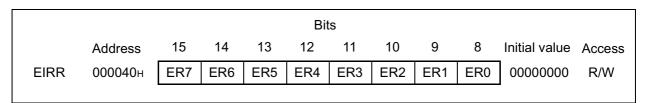

|    | 10.2  | EXTERN                                         | AL INTERRUPT CONTROLLER REGISTERS                                                                                                                                                                                                                    |            |  |

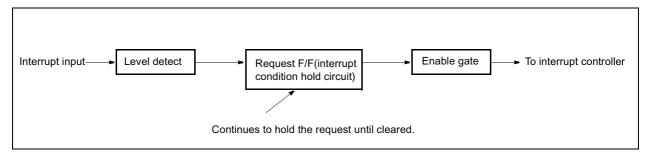

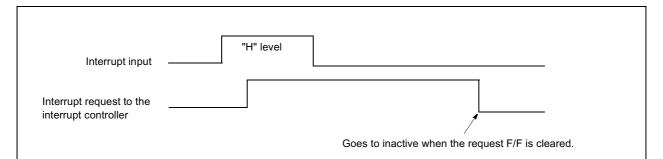

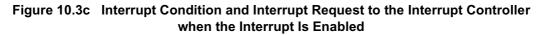

|    | 10.3  | OPERAT                                         | ION OF THE EXT. INTERRUPT CONTROLLER                                                                                                                                                                                                                 | 293        |  |

| 11 | DMA   | CONTRO                                         | DLLER (DMAC)                                                                                                                                                                                                                                         | 297        |  |

|    | 11.1  |                                                |                                                                                                                                                                                                                                                      |            |  |

|    | 11.2  | OUTLINE                                        | OF REGISTERS                                                                                                                                                                                                                                         | 300        |  |

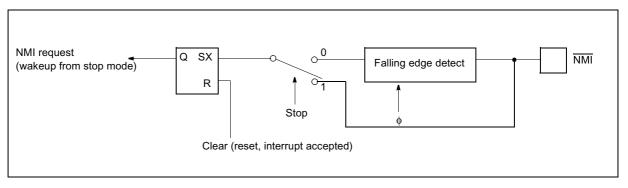

|    | 11.3  | BLOCK D                                        | DIAGRAM                                                                                                                                                                                                                                              | 301        |  |

|    | 11.4  |                                                |                                                                                                                                                                                                                                                      |            |  |

|    |       | 11.4.1<br>11.4.2<br>11.4.3<br>11.4.4<br>11.4.5 | Notes on setting registers<br>DMAC - Channel 0,1,2,3,4 control/status register A<br>DMAC - Channel 0,1,2,3,4 control/status register B<br>DMAC - Ch.0-4 transfer source/destination address reg<br>DMAC - Channel 0,1,2,3,4 overall control register |            |  |

|    | 11.5  | OPERAT                                         | ION                                                                                                                                                                                                                                                  | 315        |  |

|    |       | 11.5.1<br>11.5.2<br>11.5.3<br>11.5.4           | Outline<br>Setting a transfer request<br>Transfer sequence<br>General DMA transfer                                                                                                                                                                   | 317<br>318 |  |

|    |       | 11.5.5            | Addressing mode                                             | 323 |  |  |

|----|-------|-------------------|-------------------------------------------------------------|-----|--|--|

|    |       | 11.5.6            | Data type                                                   |     |  |  |

|    |       | 11.5.7            | Controlling the transfer count                              |     |  |  |

|    |       | 11.5.8            | Controlling the CPU                                         |     |  |  |

|    |       | 11.5.9<br>11.5.10 | Hold intervention Operation start                           |     |  |  |

|    |       | 11.5.10           | Accepting a transfer request and performing transfer        |     |  |  |

|    |       | 11.5.12           | Clearing a peripheral interrupt by the DMA                  |     |  |  |

|    |       | 11.5.13           | Temporary stop                                              |     |  |  |

|    |       | 11.5.14           | Operation termination/stop                                  |     |  |  |

|    |       | 11.5.15           | Stop due to an error                                        | 328 |  |  |

|    |       | 11.5.16           | DMAC interrupt control                                      |     |  |  |

|    |       | 11.5.17           | DMA transfer during sleep                                   |     |  |  |

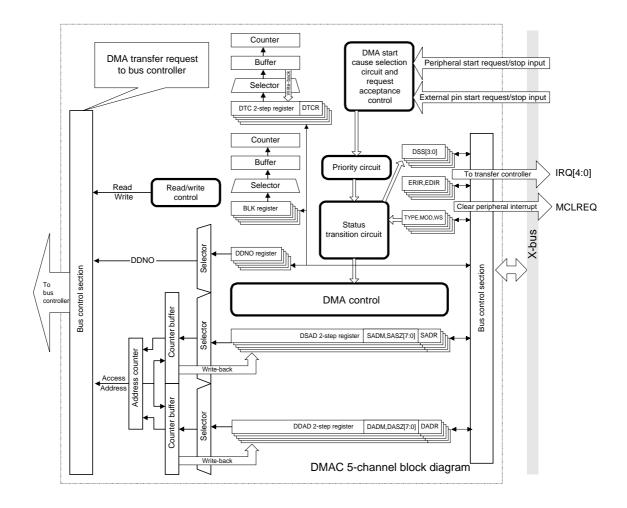

|    |       | 11.5.18           | Channel selection and control                               |     |  |  |

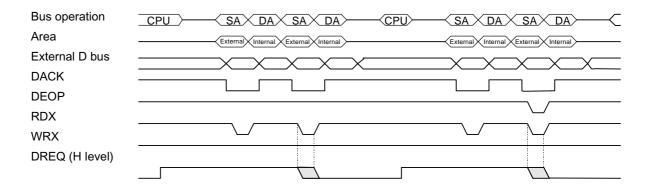

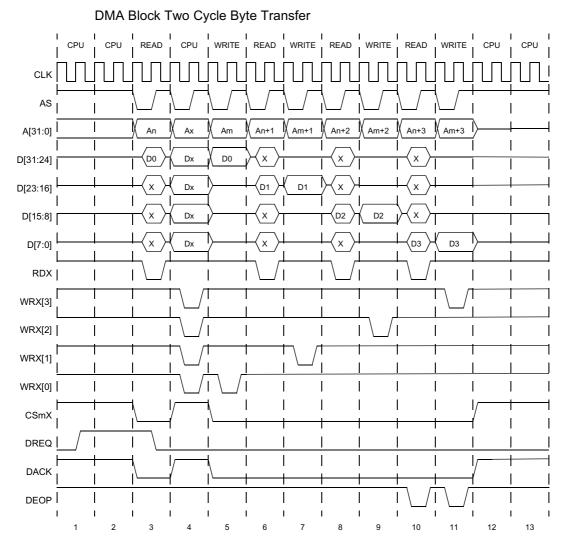

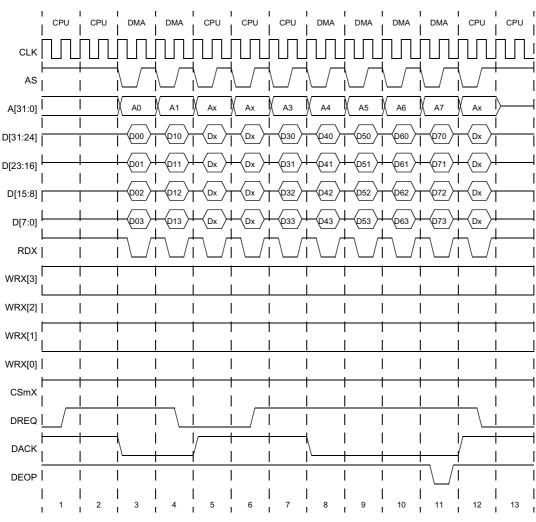

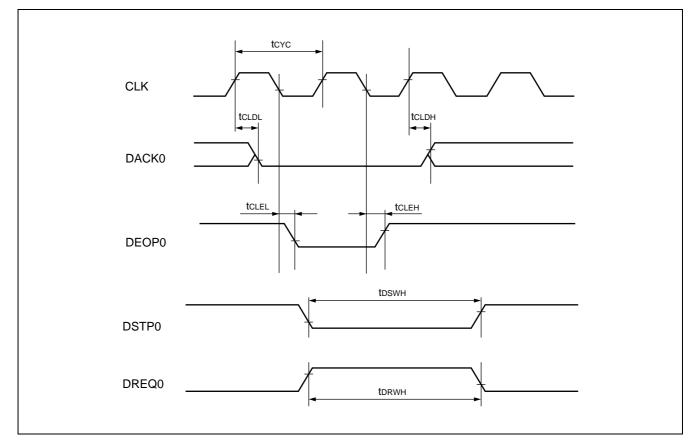

|    |       | 11.5.19           | External Pin and Internal Operation Timing                  |     |  |  |

|    | 11.6  | OPERAT            | ION FLOW                                                    | 334 |  |  |

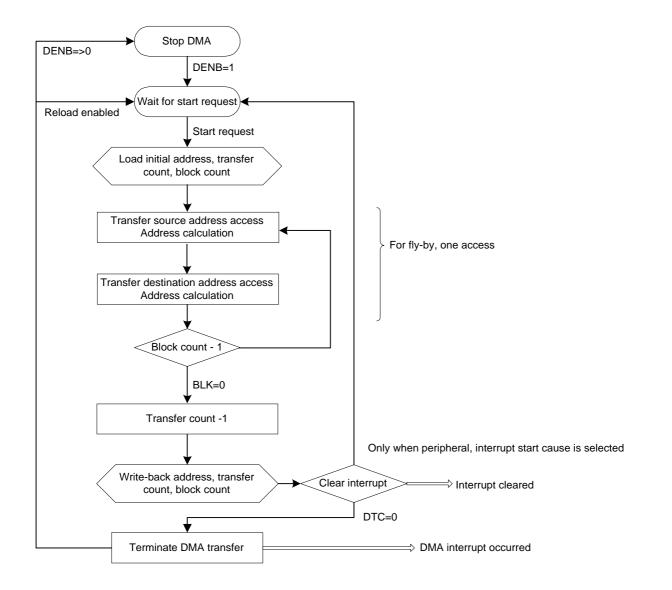

|    |       | 11.6.1            | Block transfer                                              | 334 |  |  |

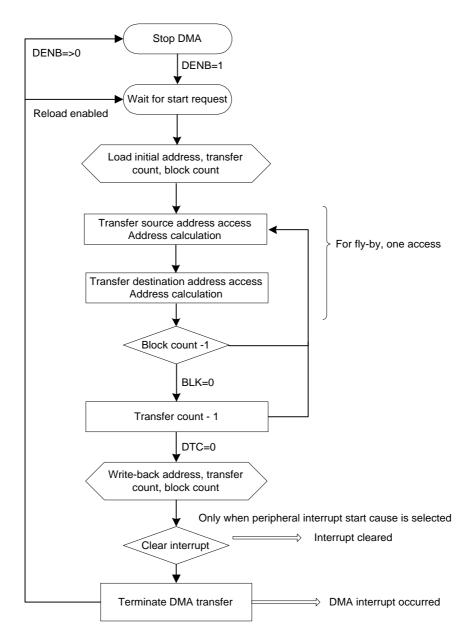

|    |       | 11.6.2            | Burst transfer                                              | 335 |  |  |

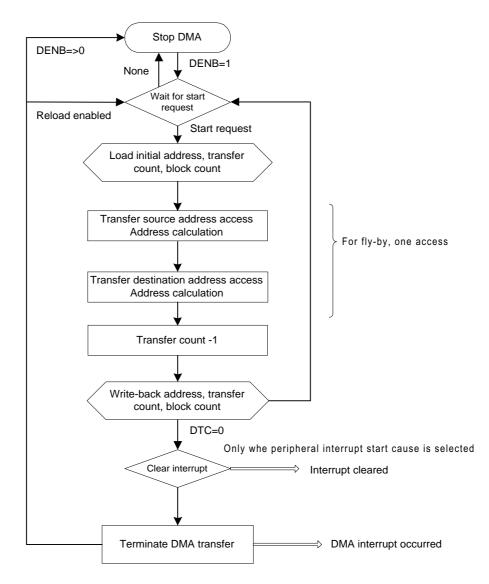

|    |       | 11.6.3            | Demand transfer                                             | 336 |  |  |

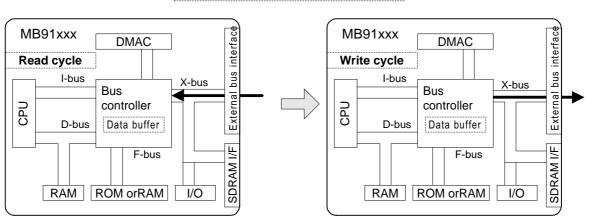

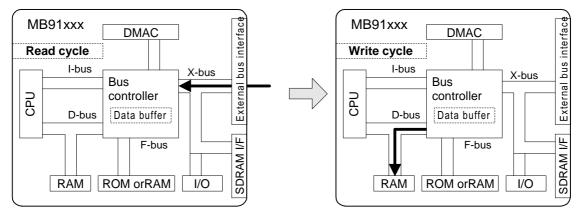

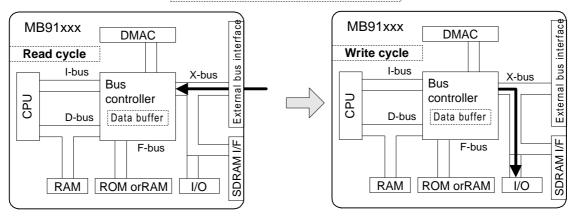

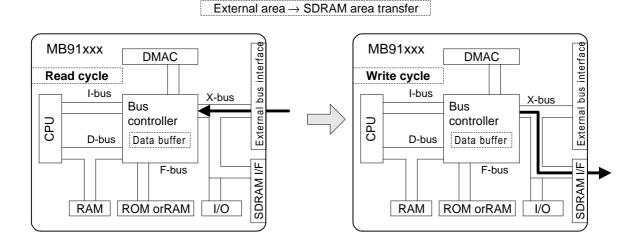

|    | 11.7  | DATA BL           | JS                                                          | 337 |  |  |

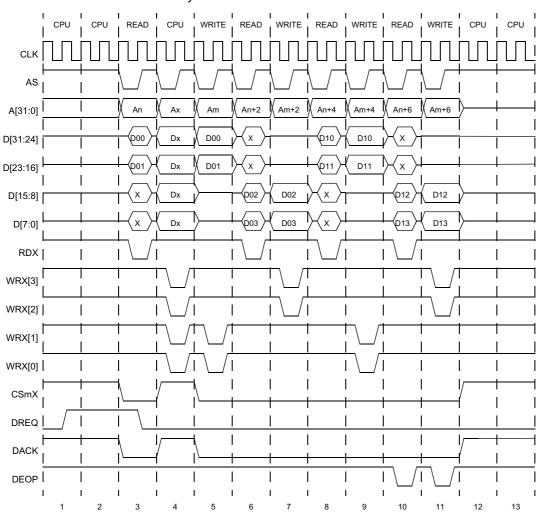

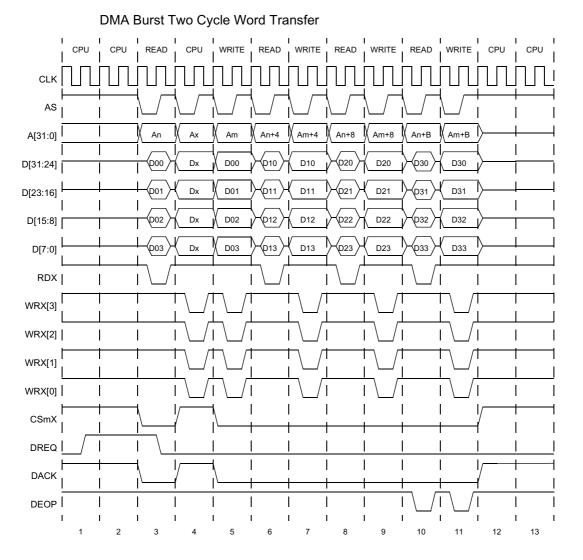

|    |       | 11.7.1            | Data flow for two-cycle transfer                            |     |  |  |

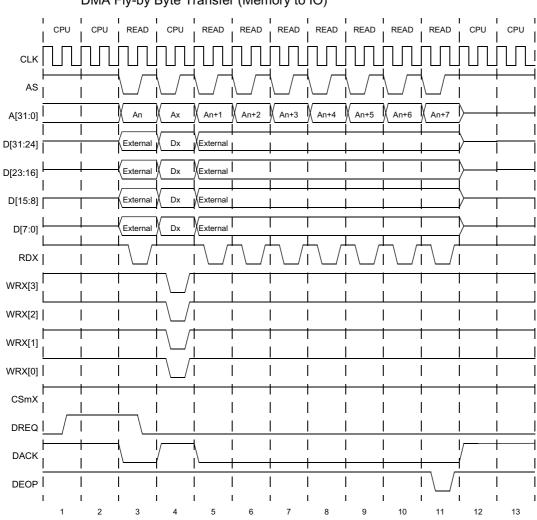

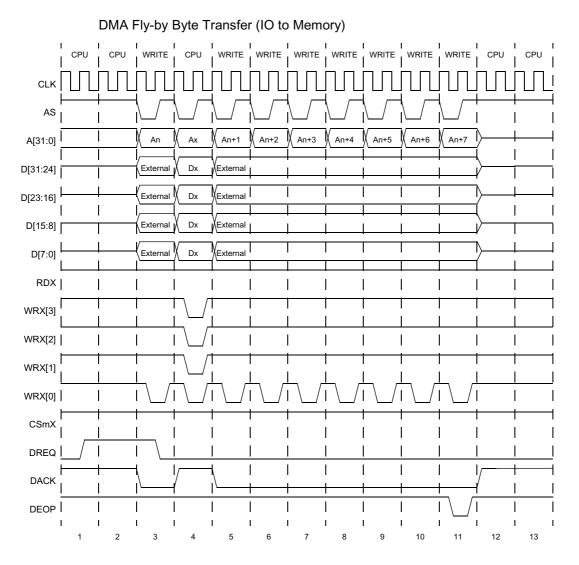

|    |       | 11.7.2            | Data flow for fly-by transfer                               |     |  |  |

|    | 11.8  | EXTERN            | AL DMA SIGNALS                                              | 340 |  |  |

|    | 11.9  | EXAMPL            | ES                                                          |     |  |  |

| 40 |       |                   | OR OS SUPPORT                                               |     |  |  |

| 12 |       |                   |                                                             |     |  |  |

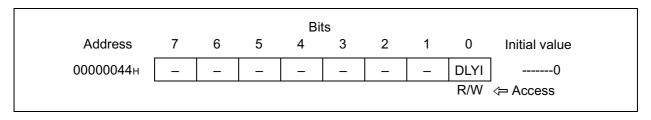

|    | 12.1  | DELAYED INTERRUPT |                                                             |     |  |  |

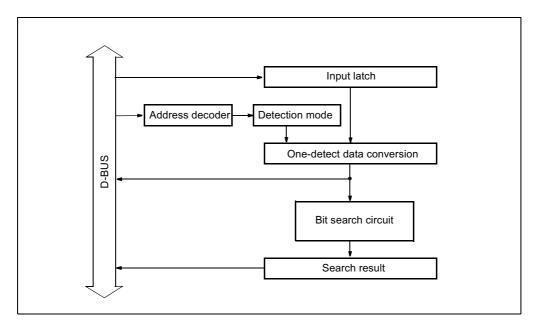

|    | 12.2  | BIT SEAF          | RCH MODULE                                                  | 349 |  |  |

|    |       | 12.2.1            | Overview of the Bit Search Module                           | 349 |  |  |

|    |       | 12.2.2            | Bit Search Module Registers                                 |     |  |  |

|    |       | 12.2.3            | Bit Search Module Operation and Save and Restore Processing | 351 |  |  |

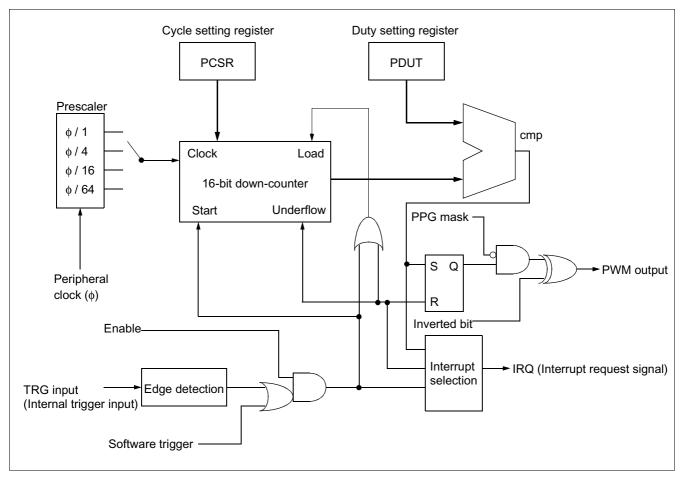

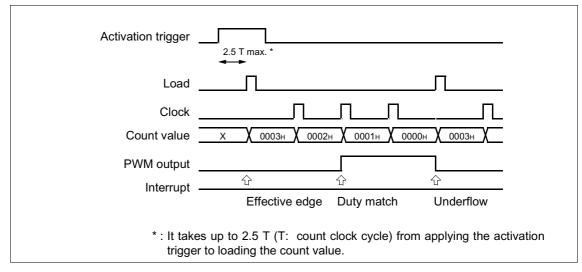

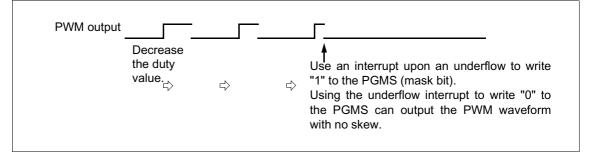

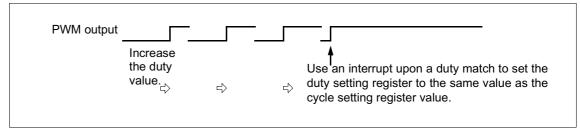

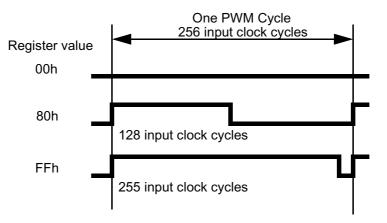

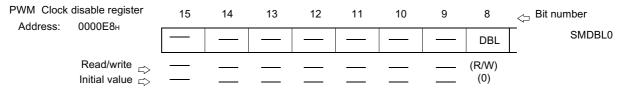

| 13 | PWM   | TIMER             |                                                             | 355 |  |  |

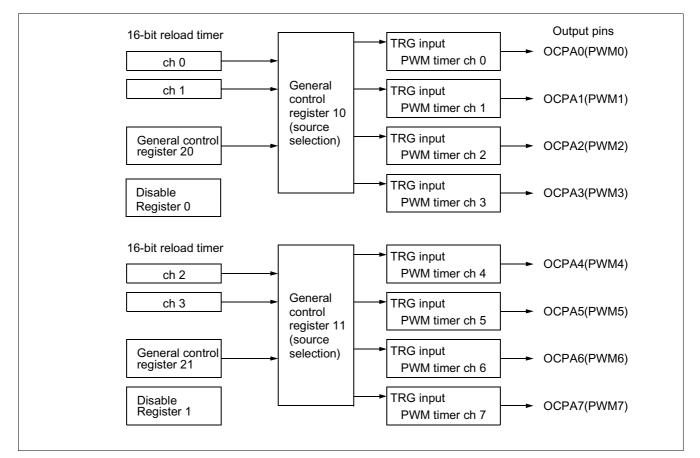

|    | 13.1  | OVERVIE           | EW OF THE PWM TIMER                                         | 356 |  |  |

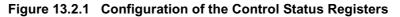

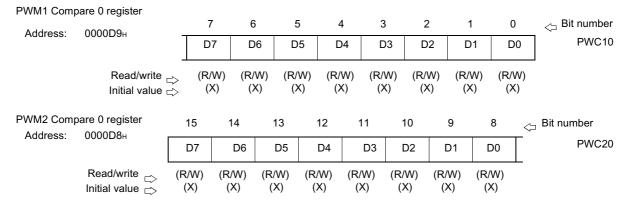

|    | 13.2  | PWM TIM           | IER REGISTERS                                               | 359 |  |  |

|    |       | 13.2.1            | Control Status Registers (PCNH, PCNL)                       | 361 |  |  |

|    |       | 13.2.1            | PWM Cycle Setting Register (PCSR)                           |     |  |  |

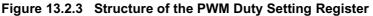

|    |       | 13.2.3            | PWM Duty Setting Register (PDUT)                            |     |  |  |

|    |       | 13.2.4            | PWM Timer Register (PTMR)                                   |     |  |  |

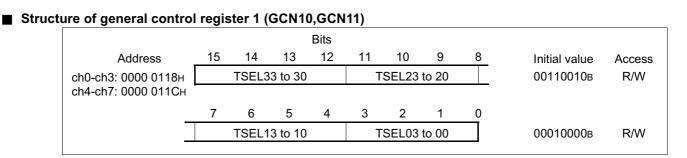

|    |       | 13.2.5            | General Control Register 1 (GCN10,GCN11)                    |     |  |  |

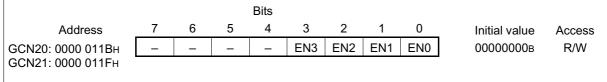

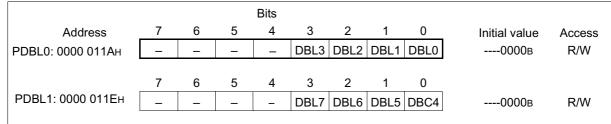

|    |       | 13.2.6            | Disable/General Control Register 2 (GCN20, GCN21)           | 372 |  |  |

|    | 13.3  | PWM TIM           | IER OPERATION                                               | 373 |  |  |

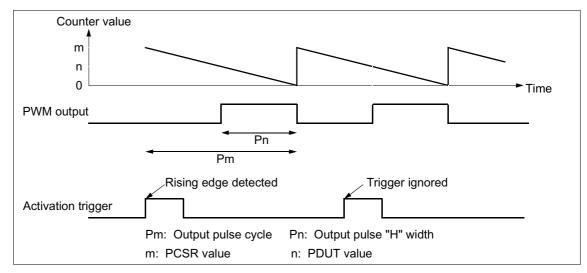

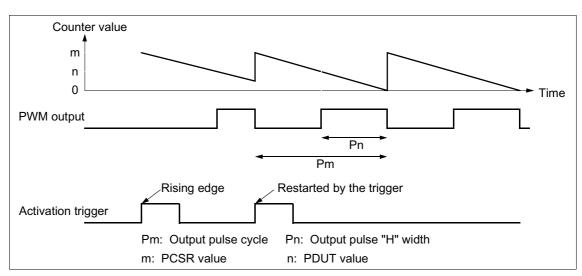

|    |       | 13.3.1            | PWM Operation                                               | 374 |  |  |

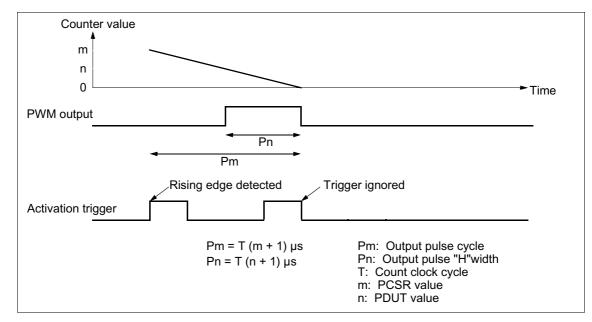

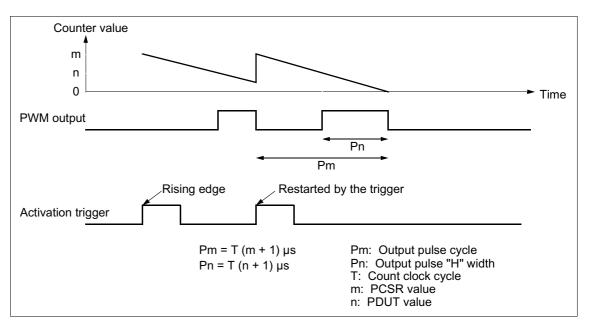

|    |       | 13.3.2            | One-Shot Operation                                          |     |  |  |

|    |       | 13.3.3            |                                                             |     |  |  |

|    |       | 13.3.4            | All "L" and All "H" PWM Outputs                             |     |  |  |

|    |       | 13.3.5            | Activating Multiple PWM Timer Channels                      |     |  |  |

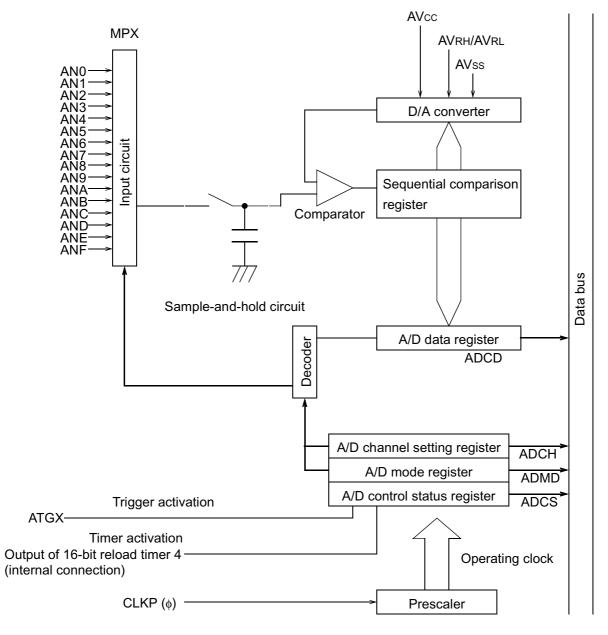

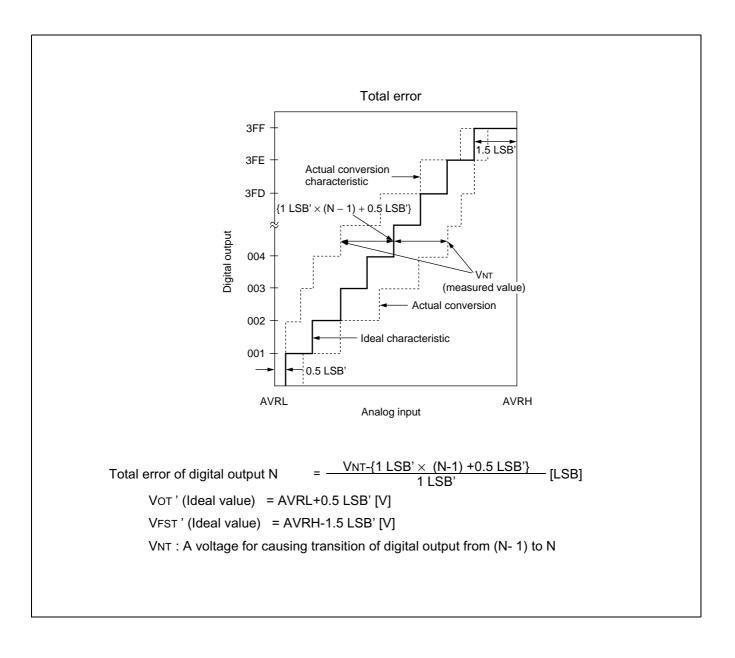

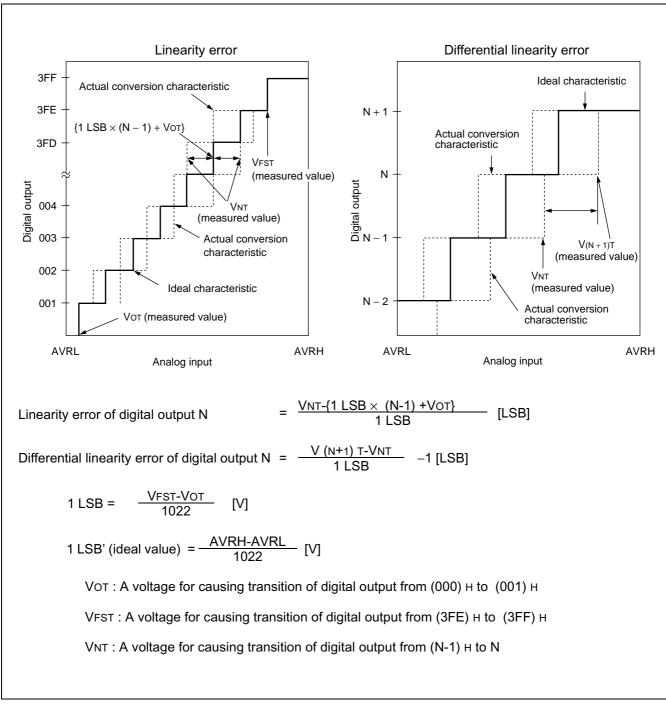

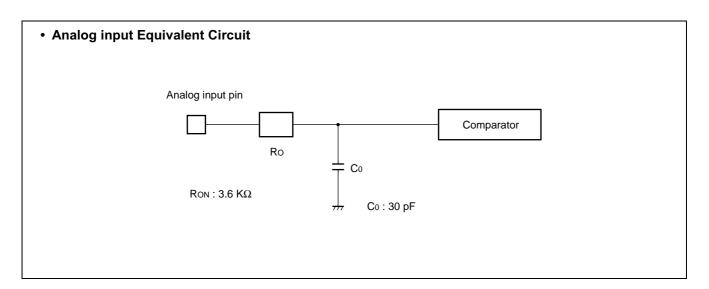

| 14 | A/D C | ONVER             | TER                                                         | 383 |  |  |

|    | 14.1  | OVERVIE           | EW                                                          |     |  |  |

|    |       |                   |                                                             |     |  |  |

|    | 14.2   | REGISTE                                                                                           | R LIST                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 385                                                                |

|----|--------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

|    | 14.3   | BLOCK D                                                                                           | IAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 386                                                                |

|    | 14.4   | DETAILED                                                                                          | D REGISTER DESCRIPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                          | . 387                                                                |

|    |        | 14.4.1<br>14.4.2<br>14.4.3<br>14.4.4<br>14.4.5                                                    | ADCH (A/D Channel Setting Register)<br>ADMD (A/D Mode Register)<br>ADCS (A/D Control Status Register)<br>ADCD (A/D Data Register)<br>ADBL (A/D Disable Register)                                                                                                                                                                                                                                                                                 | . 389<br>. 391<br>. 393                                              |

|    | 14.5   | ADC OPE                                                                                           | RATION                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                      |

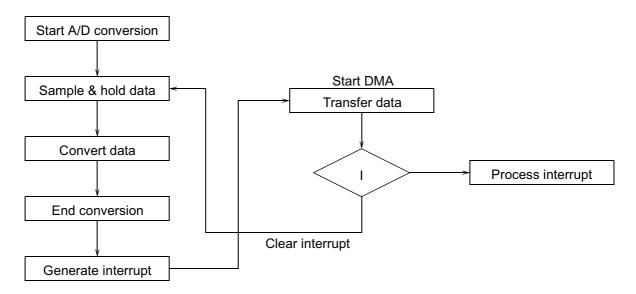

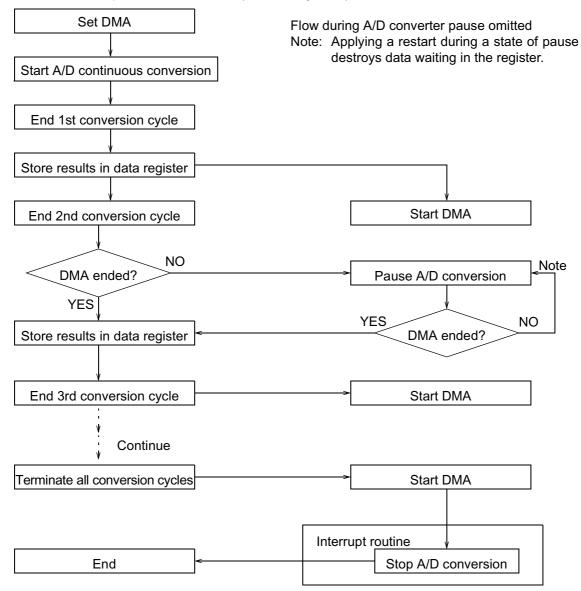

|    |        | 14.5.1<br>14.5.2<br>14.5.3<br>14.5.4<br>14.5.5                                                    | Single Mode<br>Continuous Mode<br>Stop Mode<br>Conversion Operations Using DMA<br>Conversion Data Protection Function                                                                                                                                                                                                                                                                                                                            | . 394<br>. 394<br>. 395<br>. 395                                     |

|    | 14.6   | OTHER P                                                                                           | RECAUTIONARY INFORMATION                                                                                                                                                                                                                                                                                                                                                                                                                         | . 397                                                                |

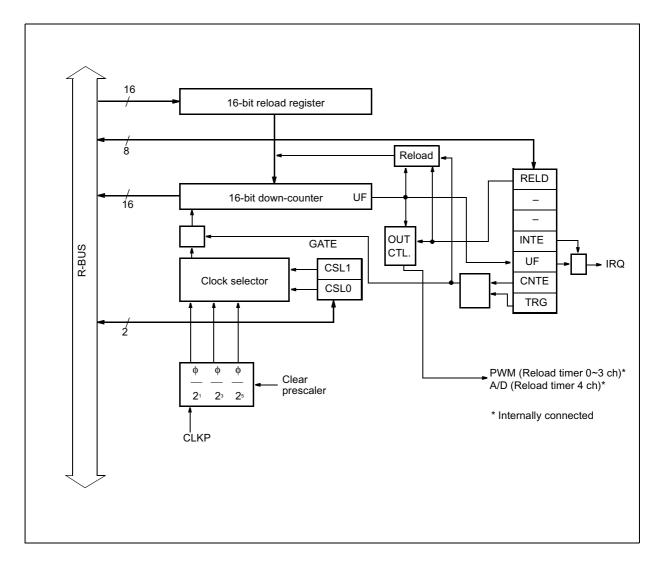

| 15 | 16-BI1 | RELOA                                                                                             | D TIMER                                                                                                                                                                                                                                                                                                                                                                                                                                          | 399                                                                  |

|    | 15.1   | OVERVIE                                                                                           | W OF THE 16-BIT RELOAD TIMER                                                                                                                                                                                                                                                                                                                                                                                                                     | . 400                                                                |

|    | 15.2   | 16-BIT RE                                                                                         | LOAD TIMER REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                      |

|    |        | 15.2.1<br>15.2.2<br>15.2.3                                                                        | Control Status Register (TMCSR)<br>16-bit Timer Register (TMR)<br>16-bit Reload Register (TMRLR)                                                                                                                                                                                                                                                                                                                                                 | . 403                                                                |

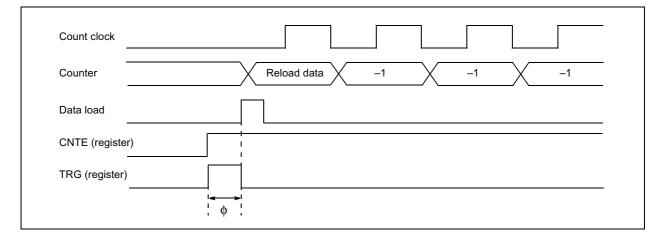

|    | 15.3   | OPERATI                                                                                           | ON OF THE 16-BIT RELOAD TIMER                                                                                                                                                                                                                                                                                                                                                                                                                    | . 405                                                                |

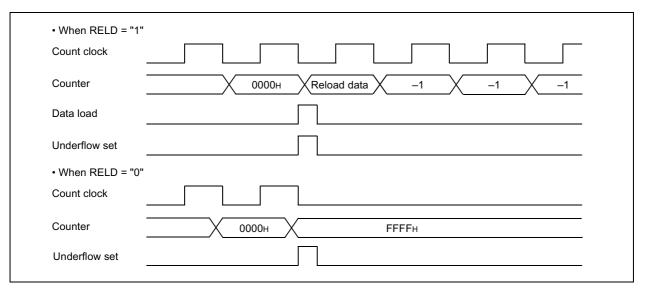

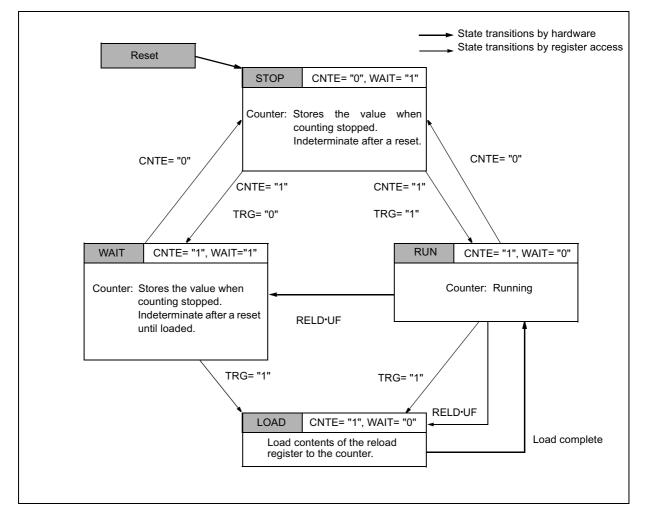

|    |        | 15.3.1<br>15.3.2<br>15.3.3<br>15.3.4                                                              | Internal Clock Operation<br>Underflow Operation<br>Counter Operation States<br>Other Operations                                                                                                                                                                                                                                                                                                                                                  | . 405<br>. 406                                                       |

| 16 | CAN    | CONTRO                                                                                            | LLER                                                                                                                                                                                                                                                                                                                                                                                                                                             | 409                                                                  |

|    | 16.1   | LIST OF C                                                                                         | CONTROL REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                | . 411                                                                |

|    | 16.2   | MESSAGE                                                                                           | E BUFFERS                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 413                                                                |

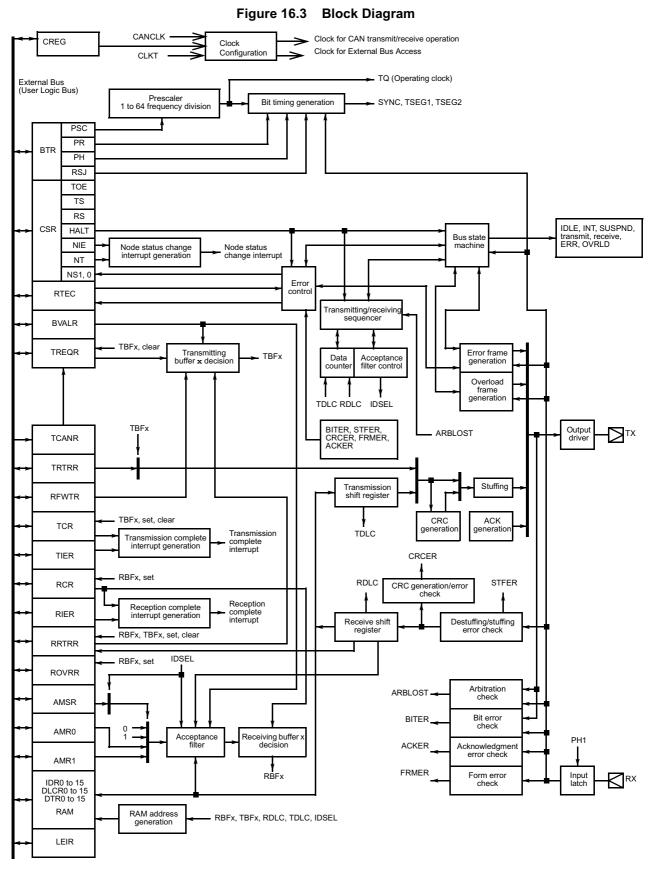

|    | 16.3   | BLOCK D                                                                                           | IAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 419                                                                |

|    | 16.4   | OVERALL                                                                                           | CONTROL REGISTER                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 420                                                                |

|    |        | 16.4.1<br>16.4.2                                                                                  | CSR: Control Status Register<br>LEIR: Last Event Indicator Register                                                                                                                                                                                                                                                                                                                                                                              | . 423                                                                |

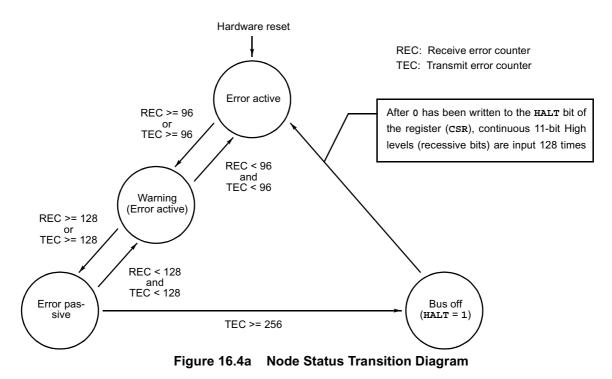

|    | 16.5   | RTEC: RE                                                                                          | CEIVE AND TRANSMIT ERROR COUNTERS                                                                                                                                                                                                                                                                                                                                                                                                                | . 424                                                                |

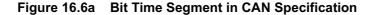

|    | 16.6   |                                                                                                   | TIMING REGISTER                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                      |

|    | 16.7   |                                                                                                   | E BUFFER CONTROL REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      |

|    |        | 16.7.1<br>16.7.2<br>16.7.3<br>16.7.4<br>16.7.5<br>16.7.6<br>16.7.7<br>16.7.8<br>16.7.9<br>16.7.10 | BVALR: Message Buffer Valid Register         IDER: IDE register         TREQR: Transmission Request Register         TRTRR: Transmission RTR Register         RFWTR: Remote Frame Receiving Wait Register         TCANR: Transmission Cancel Register         TCR: Transmission Complete Register         TIER: Transmission Interrupt Enable Register         RCR: Reception Complete Register         RRTRR: Remote Request Receiving Register | . 427<br>. 428<br>. 429<br>. 429<br>. 430<br>. 430<br>. 431<br>. 431 |

|    |        | 16.7.11<br>16.7.12 | ROVRR: Receive Overrun Register<br>RIER: Reception Interrupt Enable Register    |     |

|----|--------|--------------------|---------------------------------------------------------------------------------|-----|

|    |        | 16.7.13            | AMSR: Acceptance Mask Select Register                                           | 434 |

|    |        | 16.7.14            | AMR0 and AMR1: Acceptance Mask Registers 0 and 1                                |     |

|    | 16.8   | MESSAG             | GE BUFFERS                                                                      | 437 |

|    |        | 16.8.1             | IDRx: ID Register x (x = 0 to 15)                                               |     |

|    |        | 16.8.2<br>16.8.3   | DLCRx: DLC Register x (x = 0 to 15)<br>DTRx: Data Register x (x = 0 to 15)      |     |

|    | 10.0   |                    |                                                                                 |     |

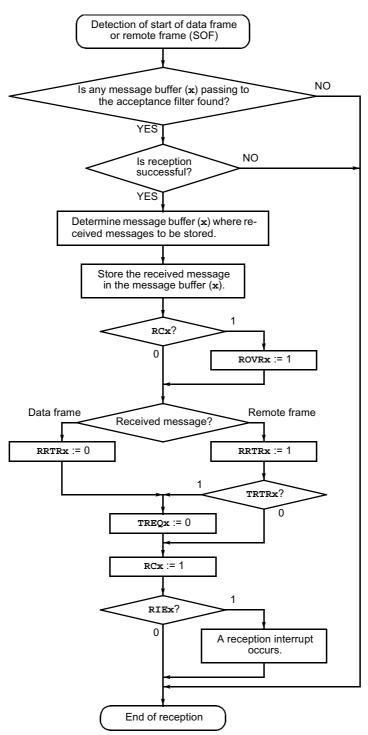

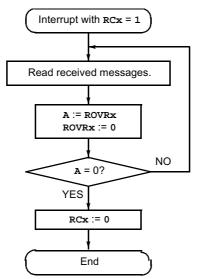

|    | 16.9   |                    |                                                                                 |     |

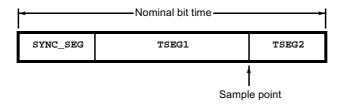

|    | 16.10  |                    | /ISSION                                                                         |     |

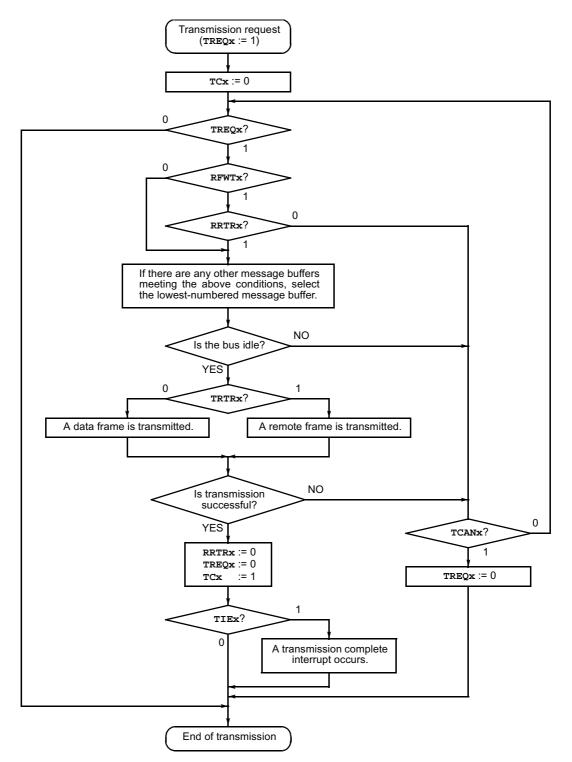

|    | 16.11  |                    | TION                                                                            |     |

|    | 16.12  |                    | PROCEDURE                                                                       |     |

|    |        | 16.12.1            | Setting Bit Timing                                                              |     |

|    |        | 16.12.2<br>16.12.3 | Setting Frame Format                                                            |     |

|    |        | 16.12.4            | Setting Acceptance Filter                                                       |     |

|    |        | 16.12.5            | Procedure for Transmission by Message Buffer (x)                                | 449 |

|    |        | 16.12.6            | Procedure for Reception by Message Buffer (x)                                   |     |

|    |        | 16.12.7            | Setting Configuration of Multi-level Message Buffer                             |     |

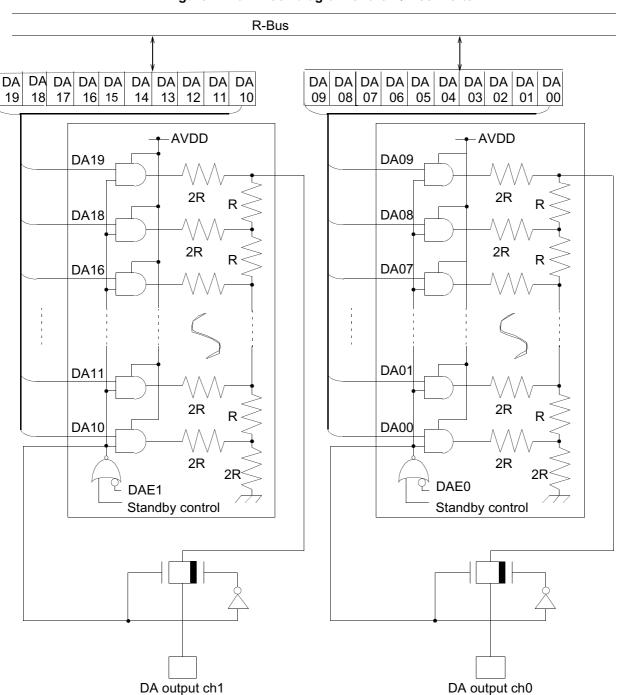

| 17 | D/A C  | ONVER              | TER                                                                             | 455 |

|    | 17.1   | BLOCK D            | DIAGRAM                                                                         | 456 |

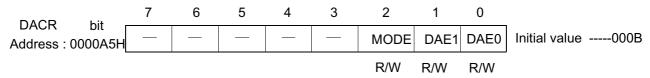

|    | 17.2   | REGISTE            | ERS                                                                             | 457 |

|    | 17.3   | REGISTE            | ER DETAILS                                                                      | 457 |

|    |        | 17.3.1             | DACR (D/A control register)                                                     | 457 |

|    |        | 17.3.2             | DADR (D/A data register)                                                        | 458 |

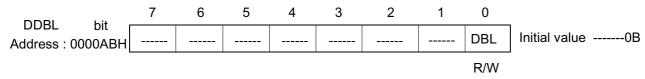

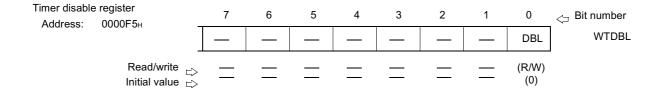

|    |        | 17.3.3             | DDBL (D/A clock control register)                                               |     |

|    | 17.4   | OPERAT             | FIONS                                                                           | 459 |

| 18 | 100 kl | Hz I2C II          | NTERFACE                                                                        | 461 |

|    | 18.1   | I2C INTE           | ERFACE OVERVIEW                                                                 | 462 |

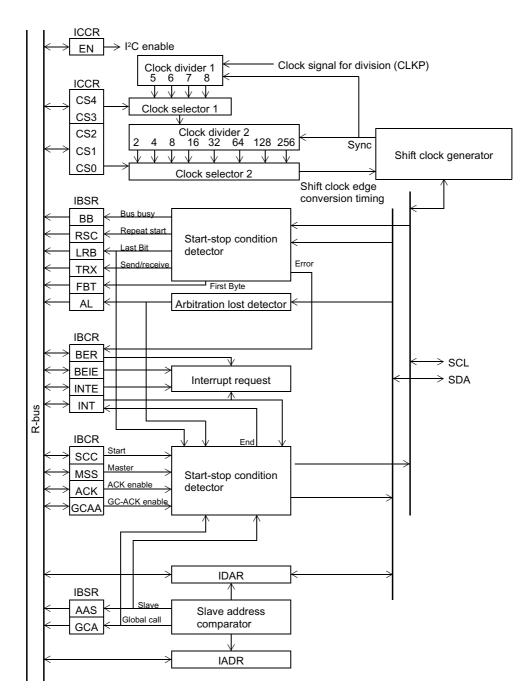

|    | 18.2   | I2C INTE           | ERFACE BLOCK DIAGRAM                                                            | 464 |

|    | 18.3   | I2C REG            | SISTERS                                                                         | 465 |

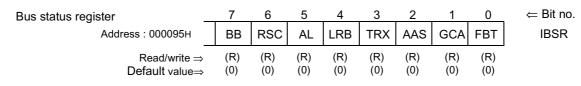

|    |        | 18.3.1             | Bus Status Register (IBSR)                                                      | 465 |

|    |        | 18.3.2             | Bus Ccontrol Register (IBCR)                                                    |     |

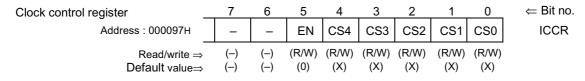

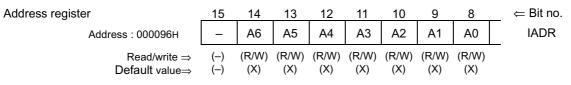

|    |        | 18.3.3<br>18.3.4   | Clock Control Register (ICCR)<br>Address Register (IADR) / Data Register (IDAR) |     |

|    | 18.4   |                    | ERFACE OPERATION                                                                |     |

|    |        |                    |                                                                                 |     |

| 19 | 400 kl | _                  | NTERFACE                                                                        | _   |

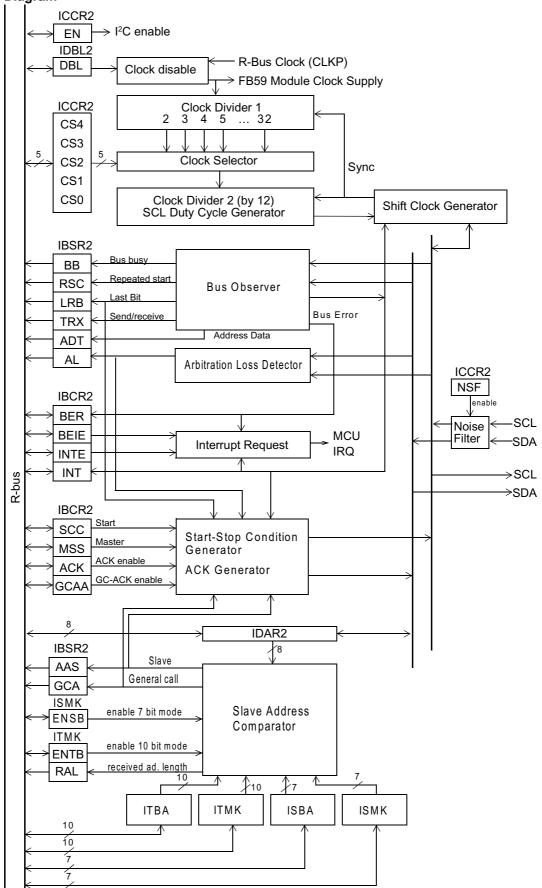

|    | 19.1   | I2C INTE           | ERFACE OVERVIEW                                                                 | 476 |

|    | 19.2   | I2C INTE           | ERFACE REGISTERS                                                                | 478 |

|    |        | 19.2.1             | Bus Status Register (IBSR2)                                                     |     |

|    |        | 19.2.2             | Bus Control Register (IBCR2)                                                    |     |

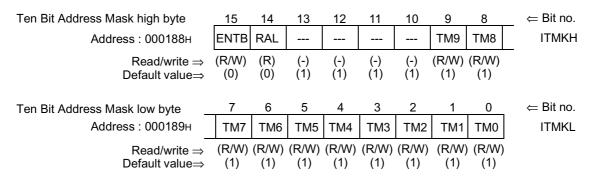

|    |        | 19.2.3<br>19.2.4   | Ten Bit Slave Address Register (ITBA)<br>Ten Bit Address Mask Register (ITMK)   |     |

|    |        | 19.2.4             | Seven Bit Slave Address Register (ISBA)                                         |     |

|    |        | 19.2.6             | Seven Bit Slave Address Mask Register (ISMK)                                    |     |

#### CONTENTS

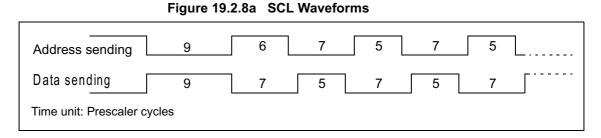

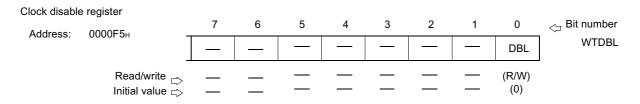

|    |        | 19.2.7<br>19.2.8<br>19.2.9           | Data Register (IDAR2)<br>Clock Control Register (ICCR2)<br>Clock Disable Register (IDBL2)                                                    | . 492          |

|----|--------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|    | 19.3   | I2C INTER                            |                                                                                                                                              | . 495          |

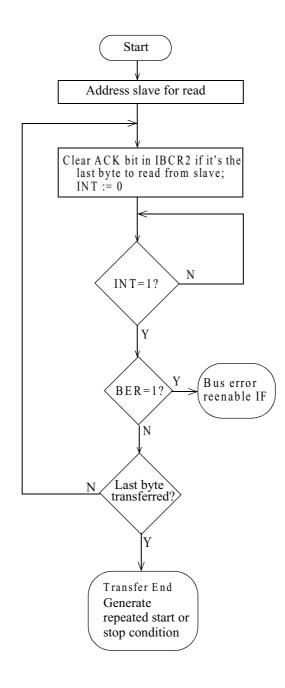

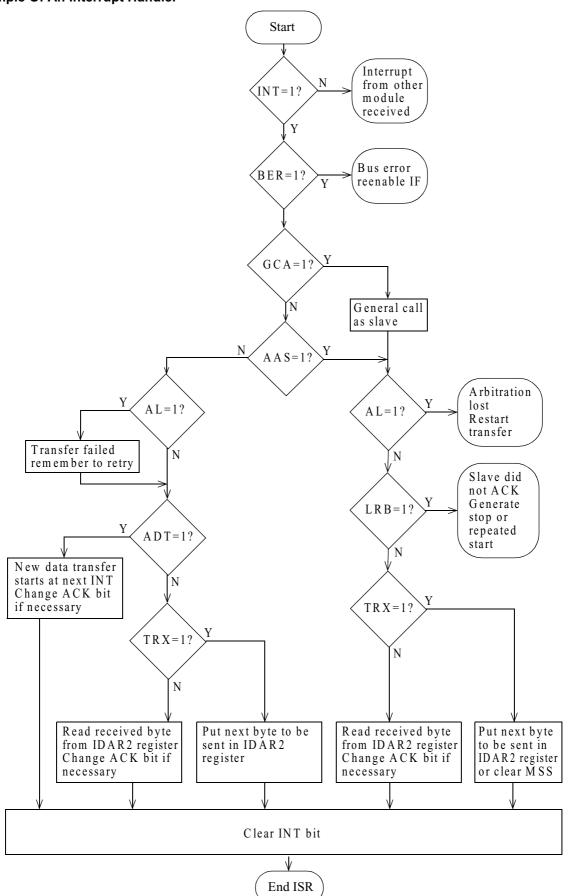

|    | 19.4   | PROGRA                               | MMING FLOW CHARTS                                                                                                                            | . 498          |

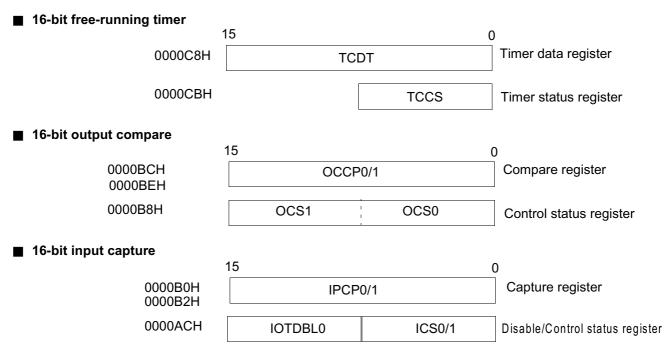

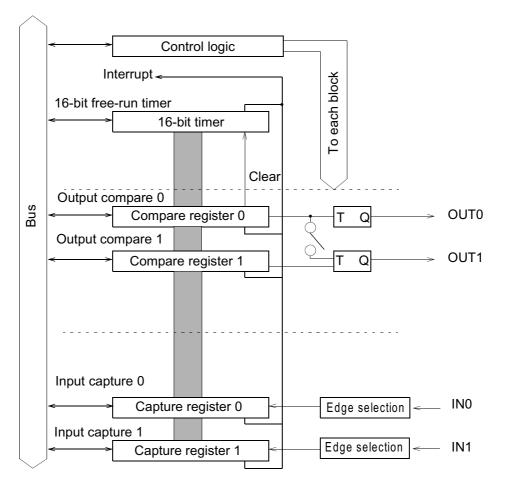

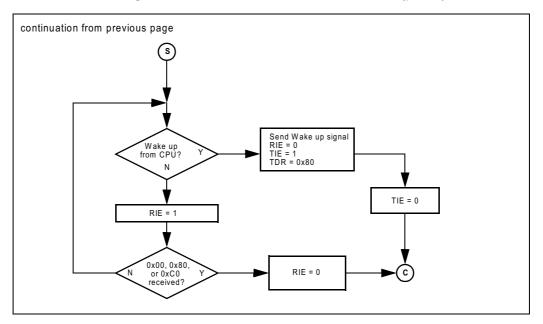

| 20 | 16-BI1 | Г І/О ТІМ                            | ER                                                                                                                                           | 501            |

|    | 20.1   | FUNCTIO                              |                                                                                                                                              | . 502          |

|    | 20.2   | REGISTE                              | RS                                                                                                                                           | . 503          |

|    | 20.3   | BLOCK D                              | IAGRAM                                                                                                                                       | . 503          |

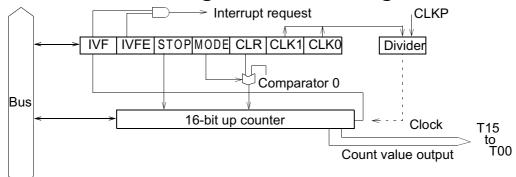

|    | 20.4   | 16-BIT FR                            | REE-RUNNING TIMER                                                                                                                            | . 504          |

|    |        | 20.4.1<br>20.4.2<br>20.4.3           | 16-bit Free-Running Timer Block Diagram<br>16-bit Free-Running Timer Data register (TCDT)<br>16-bit FR. Timer Control/Status Register (TCCS) | . 504          |

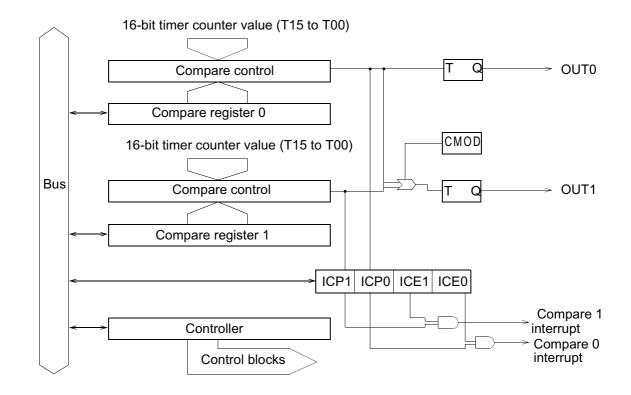

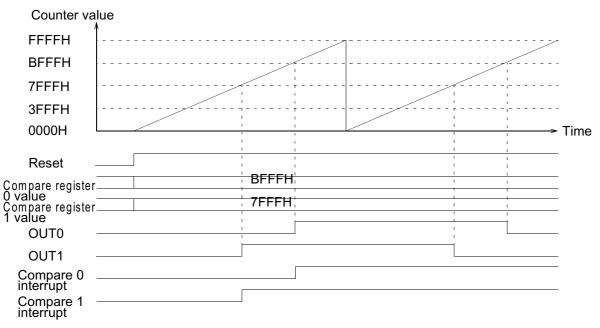

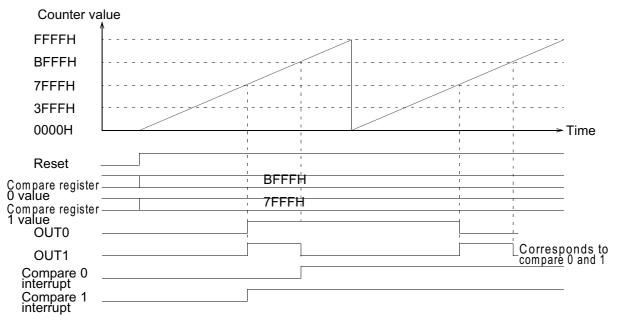

|    | 20.5   |                                      | COMPARE                                                                                                                                      |                |

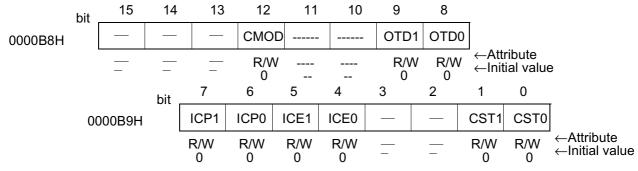

|    |        | 20.5.1<br>20.5.2<br>20.5.3           | Output Compare Block Diagram         Output Compare Comparision Register (OCCP)         Output Compare Control status register (OCS01)       | . 507          |

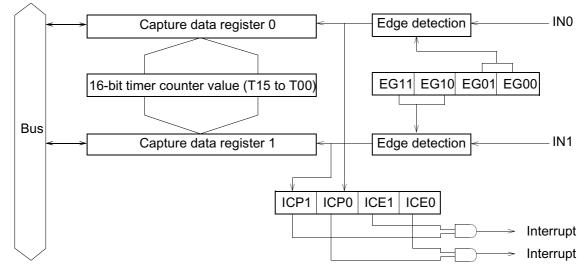

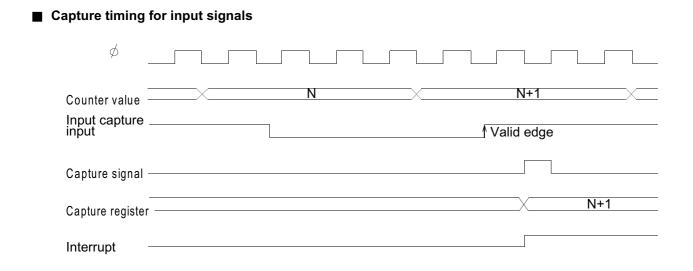

|    | 20.6   | INPUT CA                             | APTURE                                                                                                                                       | . 510          |

|    |        | 20.6.1<br>20.6.2<br>20.6.3           | Input Capture Block Diagram<br>Input Capture Data Register (IPCP)<br>Input Capture Control Status Register (ICS)                             | . 510<br>. 511 |

|    | 20.7   | 20.6.4                               | Input Capture Disable Register (IOTDBL)<br>ONS                                                                                               |                |

|    | 20.7   | 20.7.1                               | 16-bit Free-Running Timer                                                                                                                    |                |

|    |        | 20.7.2<br>20.7.3                     | 16-bit Output Compare                                                                                                                        | . 514          |

|    | 20.8   | TIMING                               |                                                                                                                                              | . 516          |

|    |        | 20.8.1<br>20.8.2<br>20.8.3           | 16-bit Free-Running Timer Count Timing<br>Output Compare Timing<br>Input Capture Input Timing                                                | . 517          |

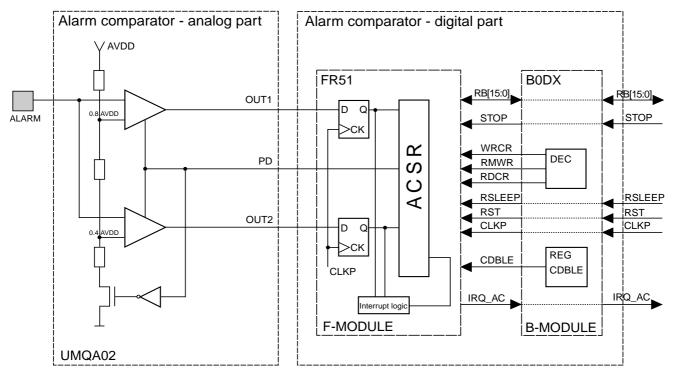

| 21 | ALAR   | м сомр                               | PARATOR                                                                                                                                      | 519            |

|    | 21.1   | BLOCK D                              | IAGRAM                                                                                                                                       | . 520          |

|    | 21.2   | REGISTE                              | RS                                                                                                                                           | . 521          |

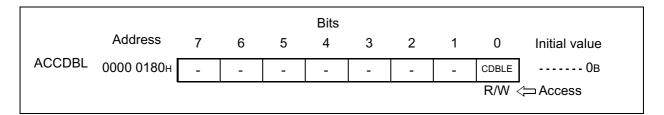

|    |        | 21.2.1<br>21.2.2                     | Alarm Comparator Clock Disable Register (ACCDBL)<br>Alarm Comparator Status Disable Register (ACSR)                                          |                |

|    | 21.3   | OPERATI                              | ON MODES                                                                                                                                     |                |

|    |        | 21.3.1<br>21.3.2<br>21.3.3<br>21.3.4 | Interrupt Mode (IEN=1)<br>Polling Mode (IEN=0)<br>Setting and Resetting of IRQ-Flagbit<br>Power Down Modes of the Alarm Comparator           | . 523<br>. 523 |

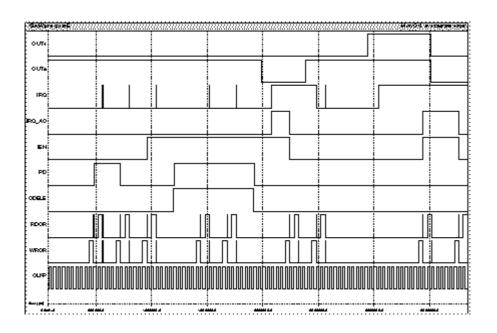

|    | 21.4   | SIMULAT                              | ION OF THE VERILOG MODEL OF ALARM                                                                                                            | . 524          |

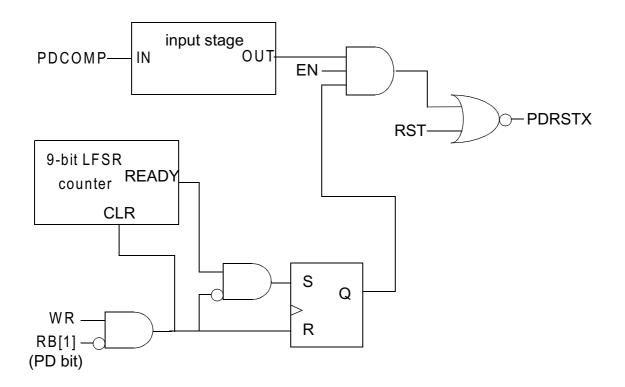

| 22 | POWE   |                                      | N RESET                                                                                                                                      | 525            |

|    | 22.1   | OVERVIE                              | W                                                                                                                                            | . 526          |

|    | 22.2   | REGISTE                              | R                                                                                                                                            | . 527          |

|     | 22.3                                                                     | OPERAT           | ION MODES                                                                             | 528 |  |  |

|-----|--------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------|-----|--|--|

|     |                                                                          | 22.3.1<br>22.3.2 | Run Modes<br>Low Power Modes                                                          |     |  |  |

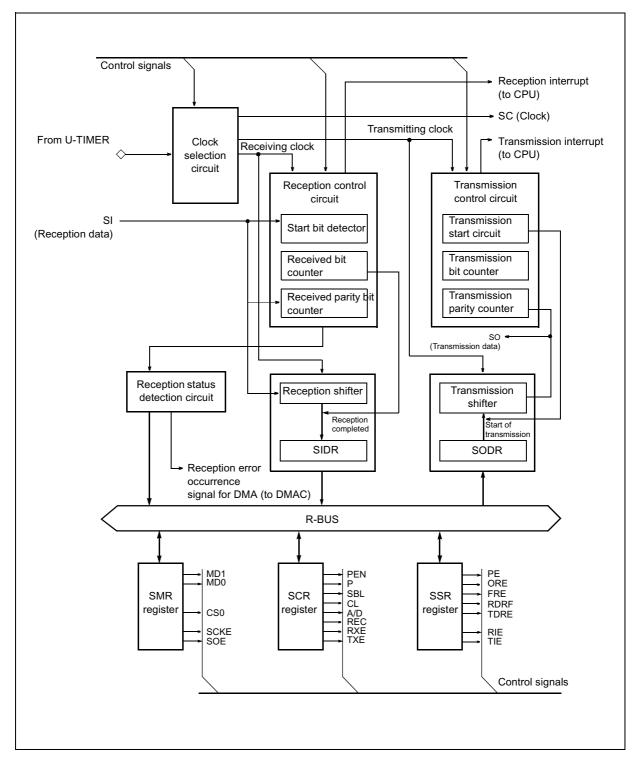

| 23  | SERIA                                                                    | AL I/O IN        | ITERFACE (SIO)                                                                        | 529 |  |  |

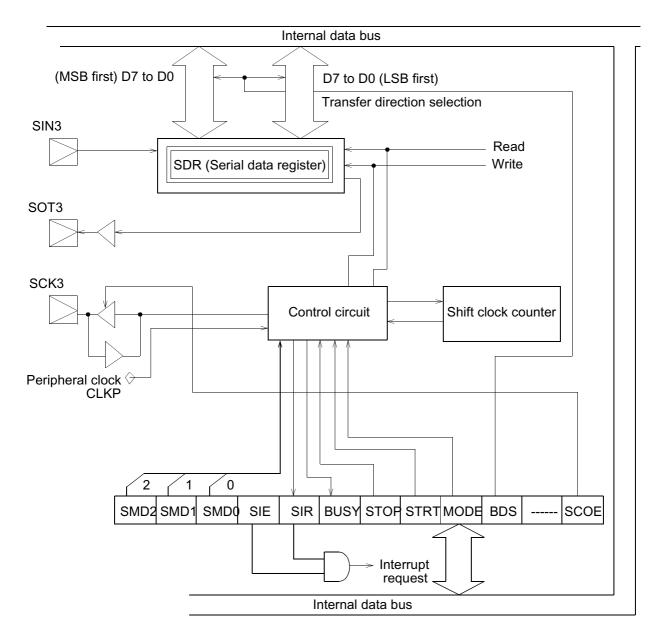

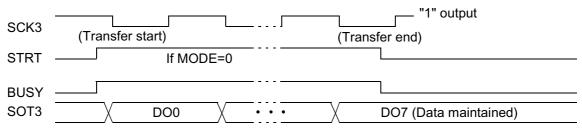

|     | 23.1                                                                     | BLOCK D          | DIAGRAM                                                                               | 530 |  |  |

|     | 23.2                                                                     | REGISTE          | ERS                                                                                   | 531 |  |  |

|     | 23.3                                                                     | REGISTE          | ER DETAILS                                                                            | 531 |  |  |

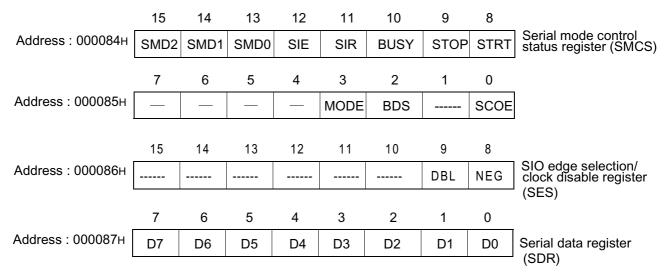

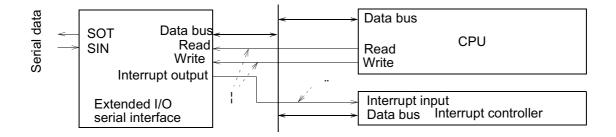

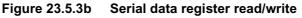

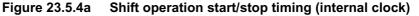

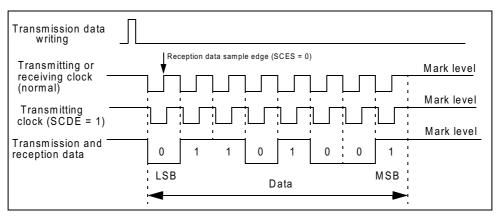

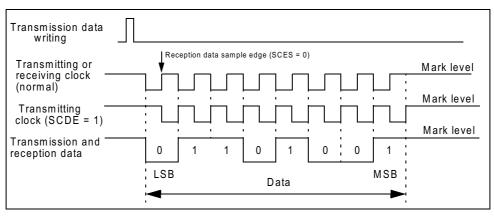

|     |                                                                          | 23.3.1           | Serial Mode Control Status Register (SMCS)                                            |     |  |  |

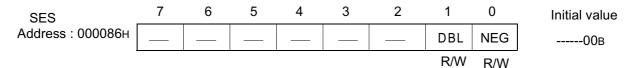

|     |                                                                          | 23.3.2<br>23.3.3 | Serial Shift Data Register (SDR)<br>SIO Edge Selection / Clock Disable Register (SES) |     |  |  |

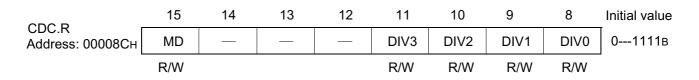

|     | 23.4                                                                     | SERIAL I         | /O PRESCALER                                                                          | 535 |  |  |

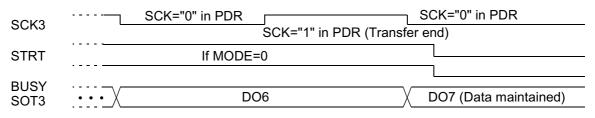

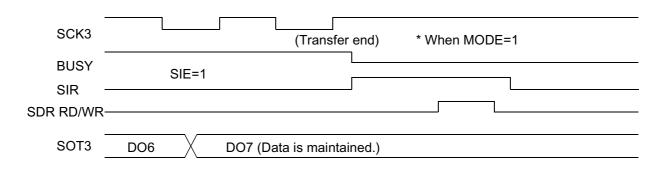

|     | 23.5                                                                     | OPERAT           | IONS                                                                                  | 536 |  |  |