# 8-bit Microcontroller

CMOS

# F<sup>2</sup>MC-8FX MB95200H/210H Series

### MB95F204H/F204K/F203H/F203K/F202H/F202K MB95F214H/F214K/F213H/F213K/F212H/F212K

#### DESCRIPTION

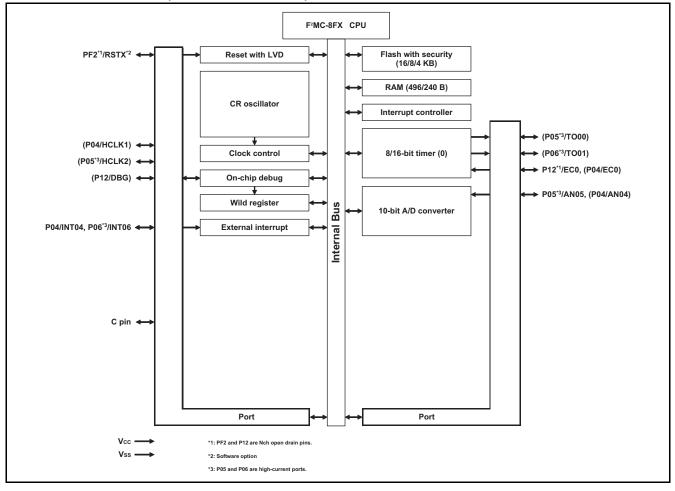

MB95200H/210H is a series of general-purpose, single-chip microcontrollers. In addition to a compact instruction set, the microcontrollers of this series contain a variety of peripheral resources.

Note: F<sup>2</sup>MC is the abbreviation of FUJITSU Flexible Microcontroller.

#### ■ FEATURES

#### • F<sup>2</sup>MC-8FX CPU core

Instruction set optimized for controllers

- Multiplication and division instructions

- 16-bit arithmetic operations

- Bit test branch instructions

- Bit manipulation instructions, etc.

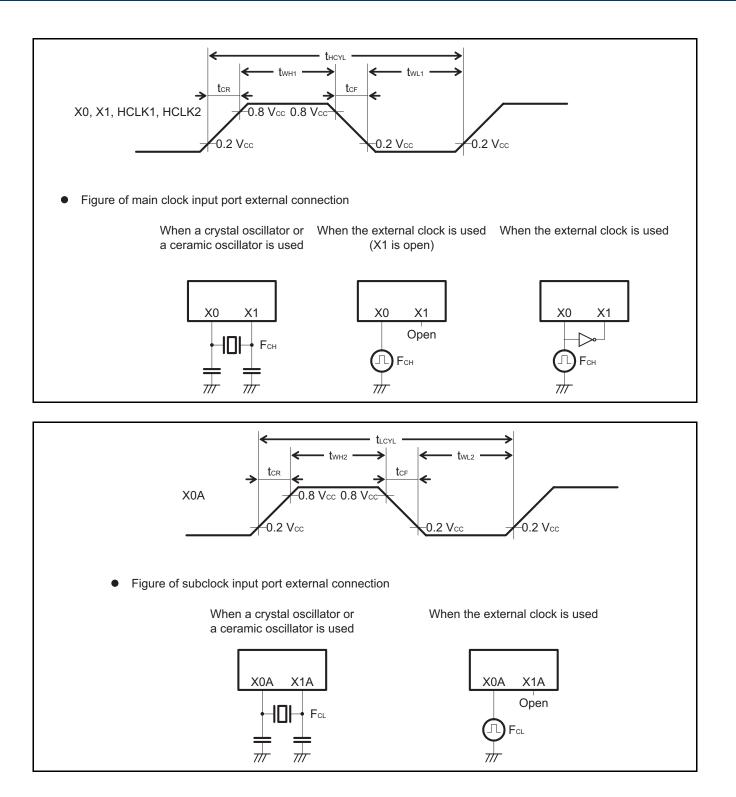

- Clock

- Selectable main clock source Main OSC clock (up to 16.25 MHz, maximum machine clock frequency: 8.125 MHz) External clock (up to 32.5 MHz, maximum machine clock frequency: 16.25 MHz) Main internal CR clock (1/8/10/12.5 MHz ± 2%, maximum machine clock frequency: 12.5 MHz)

- Selectable subclock source Sub-OSC clock (32.768 kHz) External clock (32.768 kHz) Sub-internal CR clock (typ: 100 kHz, min: 50 kHz, max: 200 kHz)

(Continued)

The information for microcontroller supports is shown in the following homepage. Be sure to refer to the "Check Sheet" for the latest cautions on development.

### "Check Sheet" is seen at the following support page

"Check Sheet" lists the minimal requirement items to be checked to prevent problems beforehand in system development.

http://edevice.fujitsu.com/micom/en-support/

- Timer

- 8/16-bit composite timer

- Timebase timer

- Watch prescaler

- LIN-UART (MB95F204H/F204K/F203H/F203K/F202H/F202K)

- Full duplex double buffer

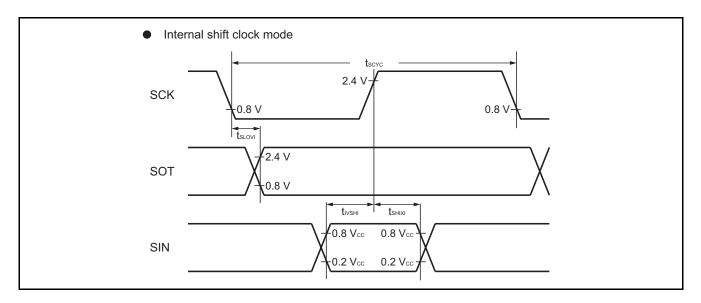

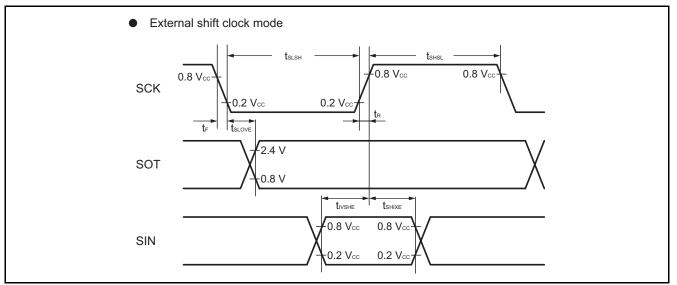

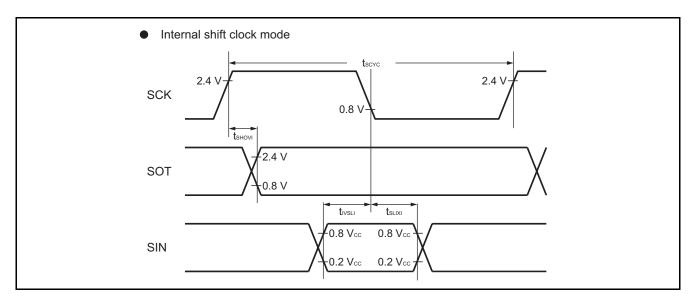

- Capable of clock-synchronized serial data transfer and clock-asynchronized serial data transfer

- External interrupt

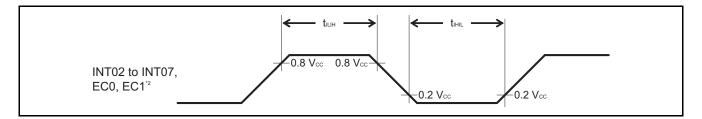

- Interrupt by edge detection (rising edge, falling edge, and both edges can be selected)

- Can be used to wake up the device from different low-power consumption (standby) modes

- 8/10-bit A/D converter

- 8-bit or 10-bit resolution can be selected.

- Low power consumption (standby) mode

- Stop mode

- Sleep mode

- Watch mode

- Timebase timer mode

- I/O port (max: 17) (MB95F204K/F203K/F202K)

- General-purpose I/O ports (max): CMOS I/O: 15, N-ch open drain: 2

- I/O port (max: 16) (MB95F204H/F203H/F202H)

- General-purpose I/O ports (max): CMOS I/O: 15, N-ch open drain: 1

- I/O port (max: 5) (MB95F214K/F213K/F212K)

- General-purpose I/O ports (max): CMOS I/O: 3, N-ch open drain: 2

- I/O port (max: 4) (MB95F214H/F213H/F212H)

- General-purpose I/O ports (max):

- CMOS I/O: 3, N-ch open drain: 1

- On-chip debug

- 1-wire serial control

- Serial writing supported (asynchronous mode)

- Hardware/software watchdog timer

- Built-in hardware watchdog timer

- Low-voltage detection reset circuit

- Built-in low-voltage detector

- Clock supervisor counter

- Built-in clock supervisor counter function

- Programmable port input voltage level

- CMOS input level / hysteresis input level

- Flash memory security function

- Protects the contents of flash memory

#### ■ PRODUCT LINE-UP

| MB95<br>F212K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| F212K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| 4 KB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |

| 240 B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| elect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| : 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |

| : 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| 6 ch. 2 ch.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| Clock-synchronized serial data transfer and clock-asynchronized serial data transfer is enabled.       No LIN-UART         The LIN function can be used as a LIN master or a LIN slave.       2 ch.         6 ch.       2 ch.         8-bit or 10-bit resolution can be selected.       2 ch.         2 ch.       1 ch.         The timer can be configured as an "8-bit timer x 2 channels" or a "16-bit timer x 1 channel".         It has built-in timer function, PWC function, PWM function and input capture function.         Count clock: it can be selected from internal clocks (seven types) and external clocks.         It can output square wave.         6 ch.       2 ch.         Interrupt by edge detection (rising edge, falling edge, or both edges can be selected.)         It can be used to wake up the device from standby modes.         1-wire serial control         It supports serial writing. (asynchronous mode) |  |  |  |  |  |  |  |  |

| (Continucu)                                  |                                                        |                                                                                                                                                                                                                                                                                                                                                                                                      |               |               |               |               |               |               |               |               |               |               |

|----------------------------------------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|

| Part number                                  | MB95<br>F204H                                          | MB95<br>F203H                                                                                                                                                                                                                                                                                                                                                                                        | MB95<br>F202H | MB95<br>F204K | MB95<br>F203K | MB95<br>F202K | MB95<br>F214H | MB95<br>F213H | MB95<br>F212H | MB95<br>F214K | MB95<br>F213K | MB95<br>F212K |

| Parameter                                    |                                                        |                                                                                                                                                                                                                                                                                                                                                                                                      |               |               |               |               |               |               |               |               |               |               |

| Watch<br>prescaler                           | Eight di                                               | fferent ti                                                                                                                                                                                                                                                                                                                                                                                           | me inter      | vals car      | be sele       | ected.        |               |               |               |               |               |               |

|                                              | write/era<br>It has a<br>Number<br>Data re<br>For writ | It supports automatic programming, Embedded Algorithm,<br>write/erase/erase-suspend/resume commands.<br>It has a flag indicating the completion of the operation of Embedded Algorithm.<br>Number of write/erase cycles (min): 100000<br>Data retention time: 20 years<br>For write/erase, external Vpp(+10 V) input is required.<br>Flash Security Feature for protecting the contents of the flash |               |               |               |               |               |               |               |               |               |               |

| Standby mode                                 | Sleep n                                                | node, sto                                                                                                                                                                                                                                                                                                                                                                                            | op mode       | , watch       | mode, ti      | mebase        | timer m       | ode           |               |               |               |               |

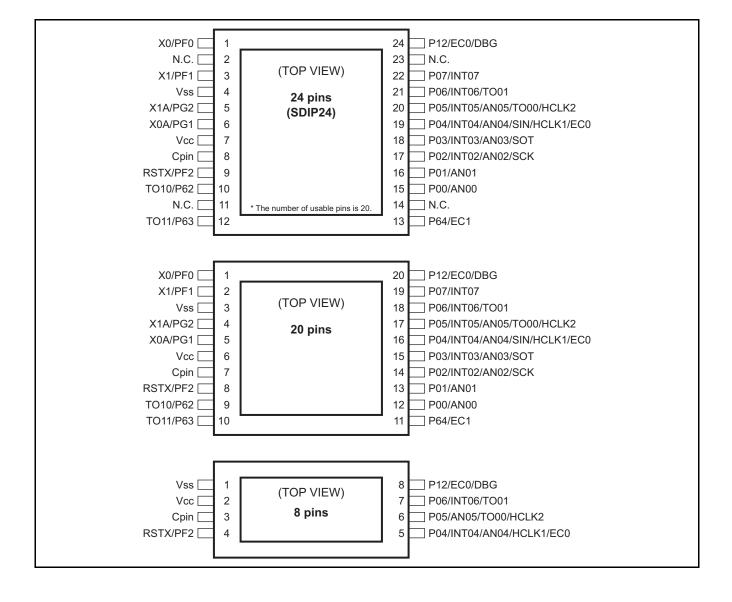

| Package<br>(Width, Length,<br>Height, Pitch) |                                                        |                                                                                                                                                                                                                                                                                                                                                                                                      | -             | P-24<br>P-20  |               |               |               |               |               | P-8<br>P-8    |               |               |

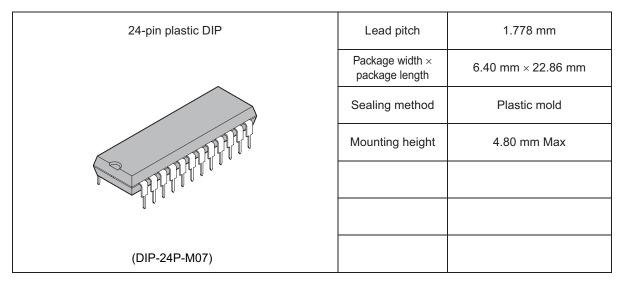

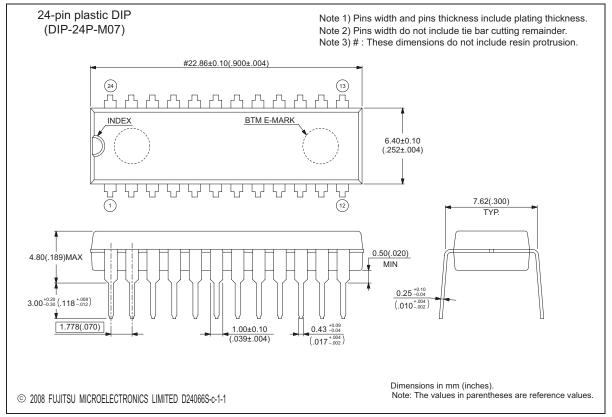

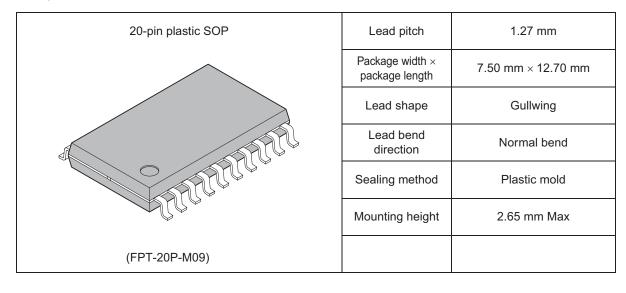

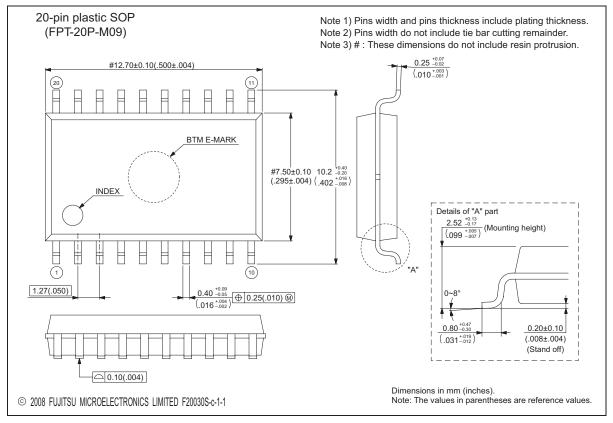

### ■ PACKAGES AND CORRESPONDING PRODUCTS

| Part number<br>Package | MB95<br>F204H | MB95<br>F203H | MB95<br>F202H | MB95<br>F204K | MB95<br>F203K | MB95<br>F202K | MB95<br>F214H | MB95<br>F213H | MB95<br>F212H | MB95<br>F214K | MB95<br>F213K | MB95<br>F212K |

|------------------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|

| 24-pin plastic<br>SDIP | 0             | 0             | 0             | 0             | 0             | 0             | Х             | Х             | х             | Х             | Х             | Х             |

| 20-pin plastic<br>SOP  | 0             | 0             | 0             | 0             | 0             | 0             | Х             | Х             | Х             | Х             | Х             | Х             |

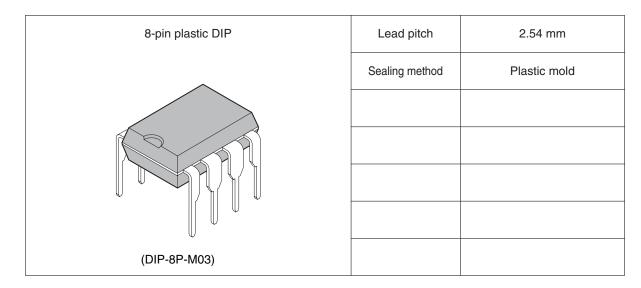

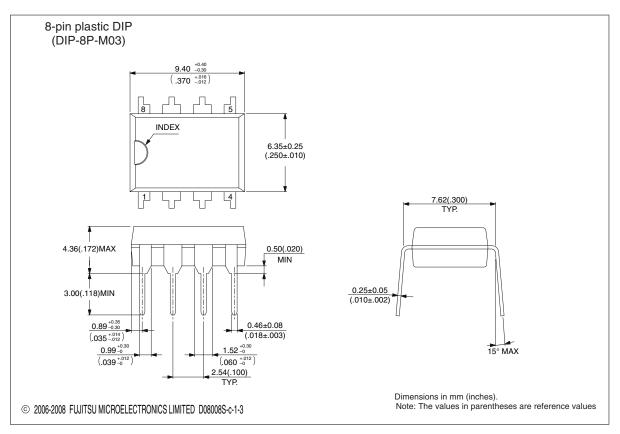

| 8-pin plastic DIP      | Х             | Х             | Х             | Х             | Х             | Х             | 0             | 0             | 0             | 0             | 0             | 0             |

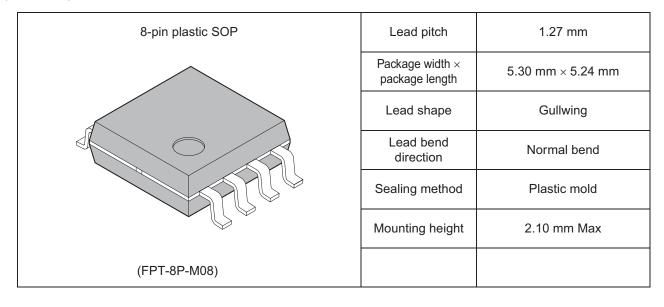

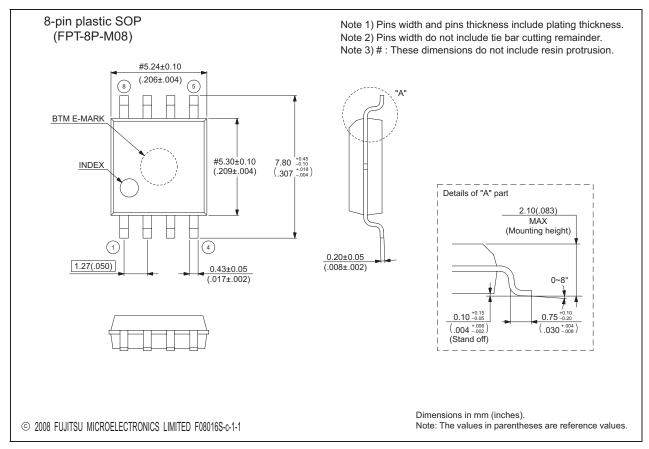

| 8-pin plastic SOP      | Х             | Х             | Х             | Х             | Х             | Х             | 0             | 0             | 0             | 0             | 0             | 0             |

O : Available

X : Unavailable

#### ■ DIFFERENCES AMONG PRODUCTS AND NOTES ON PRODUCT SELECTION

Current consumption

When using the on-chip debug function, take account of the current consumption of flash erase/program. For details of current consumption, see "■ ELECTRICAL CHARACTERISTICS".

Package

For details of information on each package, see "■ PACKAGES AND CORRESPONDING PRODUCTS" and "■ PACKAGE DIMENSION".

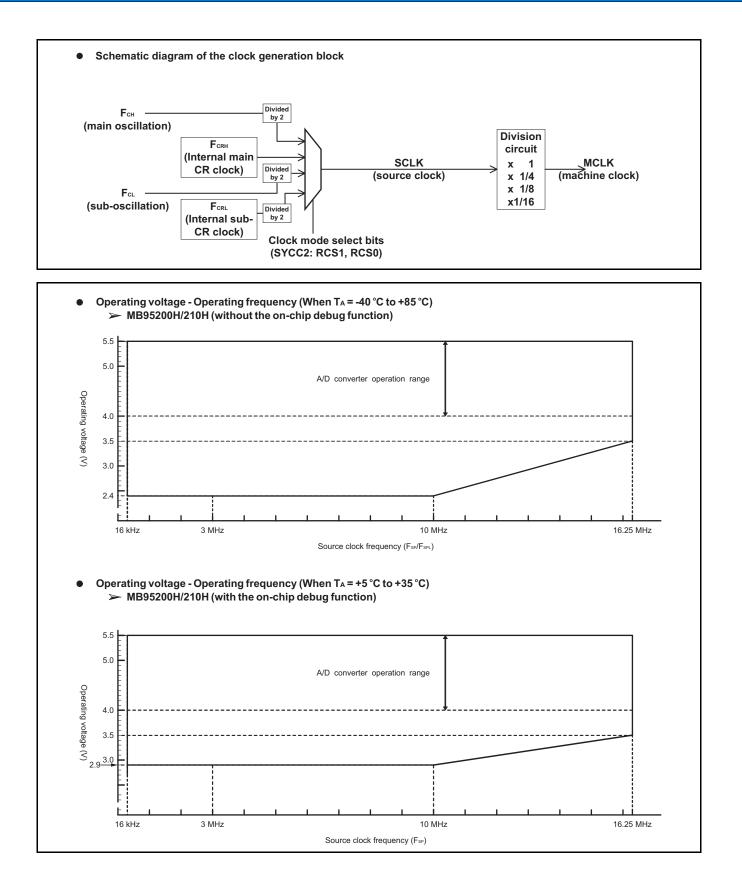

Operating voltage

The operating voltage varies, depending on whether the on-chip debug function is used or not.

For details of the operating voltage, see "■ ELECTRICAL CHARACTERISTICS".

• On-chip debug function

The on-chip debug function requires that  $V_{CC}$ ,  $V_{SS}$  and 1 serial-wire be connected to an evaluation tool. In addition, if the flash memory data has to be updated, the RSTX/PF2 pin must also be connected to the same evaluation tool.

### PRELIMINARY

# MB95200H/210H Series

#### ■ PIN ASSIGNMENT

### ■ PIN DESCRIPTION (MB95200H Series)

| Pin no. | Pin name                         | I/O<br>circuit<br>type* | Function                                                                                                                                                                                                                                                                                                                              |

|---------|----------------------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | PF0/X0                           | В                       | General-purpose I/O port<br>This pin is also used as the main clock input oscillation pin.                                                                                                                                                                                                                                            |

| 2       | PF1/X1                           | В                       | General-purpose I/O port<br>This pin is also used as the main clock input/output oscillation pin.                                                                                                                                                                                                                                     |

| 3       | Vss                              | —                       | Power supply pin (GND)                                                                                                                                                                                                                                                                                                                |

| 4       | PG2/X1A                          | С                       | General-purpose I/O port<br>This pin is also used as the subclock input/output oscillation pin.                                                                                                                                                                                                                                       |

| 5       | PG1/X0A                          | С                       | General-purpose I/O port<br>This pin is also used as the subclock input oscillation pin.                                                                                                                                                                                                                                              |

| 6       | Vcc                              |                         | Power supply pin                                                                                                                                                                                                                                                                                                                      |

| 7       | Cpin                             |                         | Capacitor connection pin                                                                                                                                                                                                                                                                                                              |

| 8       | PF2/RSTX                         | А                       | General-purpose I/O port<br>This pin is also used as a reset pin.<br>This pin is a dedicated reset pin in MB95F204H/F203H/F202H.                                                                                                                                                                                                      |

| 9       | P62/TO10                         | D                       | General-purpose I/O port<br>High-current port<br>This pin is also used as the 8/16-bit composite timer ch. 1 output.                                                                                                                                                                                                                  |

| 10      | P63/TO11                         | D                       | General-purpose I/O port<br>High-current port<br>This pin is also used as the 8/16-bit composite timer ch. 1 output.                                                                                                                                                                                                                  |

| 11      | P64/EC1                          | D                       | General-purpose I/O port<br>This pin is also used as the 8/16-bit composite timer ch. 1 clock input.                                                                                                                                                                                                                                  |

| 12      | P00/AN00                         | E                       | General-purpose I/O port<br>This pin is also used as the A/D converter analog input.                                                                                                                                                                                                                                                  |

| 13      | P01/AN01                         | E                       | General-purpose I/O port<br>This pin is also used as the A/D converter analog input.                                                                                                                                                                                                                                                  |

| 14      | P02/INT02/AN02/<br>SCK           | E                       | General-purpose I/O port<br>This pin is also used as the external interrupt input.<br>This pin is also used as the A/D converter analog input.<br>This pin is also used as the LIN-UART clock I/O.                                                                                                                                    |

| 15      | P03/INT03/AN03/<br>SOT           | E                       | General-purpose I/O port<br>This pin is also used as the external interrupt input.<br>This pin is also used as the A/D converter analog input.<br>This pin is also used as the LIN-UART data output.                                                                                                                                  |

| 16      | P04/INT04/AN04/<br>SIN/HCLK1/EC0 | F                       | General-purpose I/O port<br>This pin is also used as the external interrupt input.<br>This pin is also used as the A/D converter analog input.<br>This pin is also used as the LIN-UART data input.<br>This pin is also used as the external clock input.<br>This pin is also used as the 8/16-bit composite timer ch. 0 clock input. |

(Continued)

| Pin no. | Pin name                      | I/O<br>circuit<br>type* | Function                                                                                                                                                                                                                                                                                         |

|---------|-------------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17      | P05/INT05/AN05/<br>TO00/HCLK2 | E                       | General-purpose I/O port<br>High-current port<br>This pin is also used as the external interrupt input.<br>This pin is also used as the A/D converter analog input.<br>This pin is also used as the 8/16-bit composite timer ch. 0 output.<br>This pin is also used as the external clock input. |

| 18      | P06/INT06/TO01                | G                       | General-purpose I/O port<br>High-current port<br>This pin is also used as the external interrupt input.<br>This pin is also used as the 8/16-bit composite timer ch. 0 output.                                                                                                                   |

| 19      | P07/INT07                     | G                       | General-purpose I/O port<br>This pin is also used as the external interrupt input.                                                                                                                                                                                                               |

| 20      | P12/EC0/DBG                   | Н                       | General-purpose I/O port<br>This pin is also used as the DBG input pin.<br>This pin is also used as the 8/16-bit composite timer ch. 0 clock input.                                                                                                                                              |

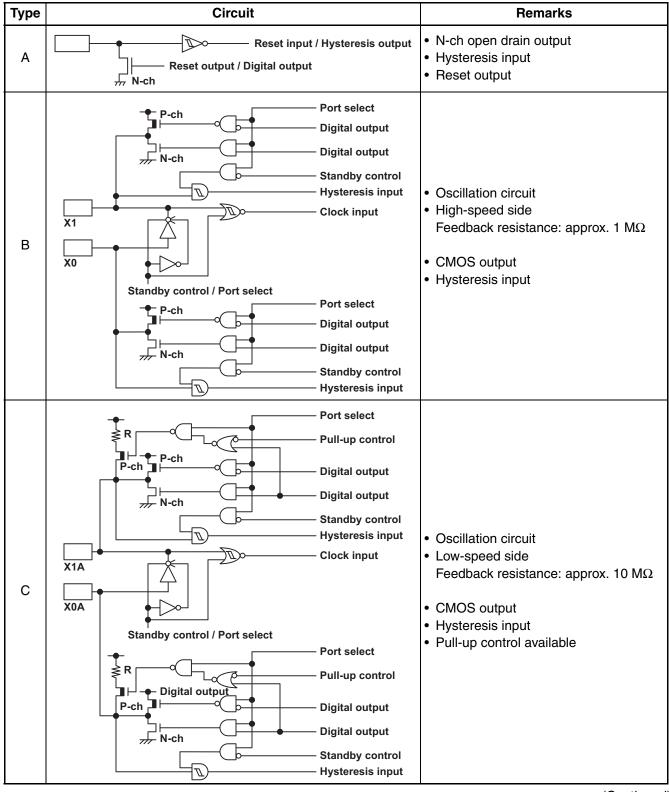

\* : For the I/O circuit types, see "■ I/O CIRCUIT TYPE".

### ■ PIN DESCRIPTION (MB95210H Series)

| Pin no. | Pin name                     | I/O<br>circuit<br>type* | Function                                                                                                                                                                                                                                                                         |

|---------|------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | Vss                          |                         | Power supply pin (GND)                                                                                                                                                                                                                                                           |

| 2       | Vcc                          |                         | Power supply pin                                                                                                                                                                                                                                                                 |

| 3       | Cpin                         |                         | Capacitor connection pin                                                                                                                                                                                                                                                         |

| 4       | RSTX/PF2                     | А                       | General-purpose I/O port<br>This pin is also used as a reset pin.<br>This pin is a dedicated reset pin in MB95F214H/F213H/F212H.                                                                                                                                                 |

| 5       | P04/INT04/AN04/<br>HCLK1/EC0 | E                       | General-purpose I/O port<br>This pin is also used as the external interrupt input.<br>This pin is also used as the A/D converter analog input.<br>This pin is also used as the external clock input.<br>This pin is also used as the 8/16-bit composite timer ch. 0 clock input. |

| 6       | P05/AN05/TO00/<br>HCLK2      | E                       | General-purpose I/O port<br>High-current port<br>This pin is also used as the A/D converter analog input.<br>This pin is also used as the 8/16-bit composite timer ch. 0 output.<br>This pin is also used as the external clock input.                                           |

| 7       | P06/INT06/TO01               | G                       | General-purpose I/O port<br>High-current port<br>This pin is also used as the external interrupt input.<br>This pin is also used as the 8/16-bit composite timer ch. 0 output.                                                                                                   |

| 8       | P12/EC0/DBG                  | Н                       | General-purpose I/O port<br>This pin is also used as the DBG input pin.<br>This pin is also used as the 8/16-bit composite timer ch. 0 clock input.                                                                                                                              |

\* : For the I/O circuit types, see "■ I/O CIRCUIT TYPE".

#### ■ I/O CIRCUIT TYPE

| Туре | Circuit                        |                                                                                                                                                                                                       | Remarks                                                                                                          |

|------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| D    | P-ch<br>P-ch<br>N-ch           | — Digital output<br>— Digital output<br>— Standby control<br>— Hysteresis input                                                                                                                       | <ul><li>CMOS output</li><li>Hysteresis input</li></ul>                                                           |

| E    | R<br>P-ch<br>N-ch              | <ul> <li>Pull-up control</li> <li>Digital output</li> <li>Digital output</li> <li>Analog input</li> <li>A/D control</li> <li>Standby control</li> <li>Hysteresis input</li> </ul>                     | <ul> <li>CMOS output</li> <li>Hysteresis input</li> <li>Pull-up control available</li> </ul>                     |

| F    | R<br>P-ch<br>P-ch<br>T<br>N-ch | <ul> <li>Pull-up control</li> <li>Digital output</li> <li>Digital output</li> <li>Analog input</li> <li>A/D control</li> <li>Standby control</li> <li>Hysteresis input</li> <li>CMOS input</li> </ul> | <ul> <li>CMOS output</li> <li>Hysteresis input</li> <li>CMOS input</li> <li>Pull-up control available</li> </ul> |

| G    | R<br>P-ch<br>N-ch              | — Pull-up control<br>— Digital output<br>— Digital output<br>— Standby control<br>— Hysteresis input                                                                                                  | <ul> <li>Hysteresis input</li> <li>CMOS output</li> <li>Pull-up control available</li> </ul>                     |

| Н    | Digital output                 | — Standby control<br>— Hysteresis input                                                                                                                                                               | <ul><li>N-ch open drain output</li><li>Hysteresis input</li></ul>                                                |

#### NOTES ON DEVICE HANDLING

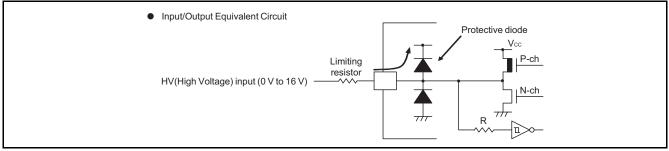

Preventing latch-ups

When using the device, ensure that the voltage applied does not exceed the maximum voltage rating. In a CMOS IC, if a voltage higher than  $V_{CC}$  or a voltage lower than  $V_{SS}$  is applied to an input/output pin that is neither a medium-withstand voltage pin nor a high-withstand voltage pin, or if a voltage out of the rating range of power supply voltage mentioned in "1. Absolute Maximum Ratings" of ELECTRICAL CHARACTERISTICS" is applied to the V<sub>CC</sub> pin or the V<sub>SS</sub> pin, a latch-up may occur.

When a latch-up occurs, power supply current increases significantly, which may cause a component to be thermally destroyed.

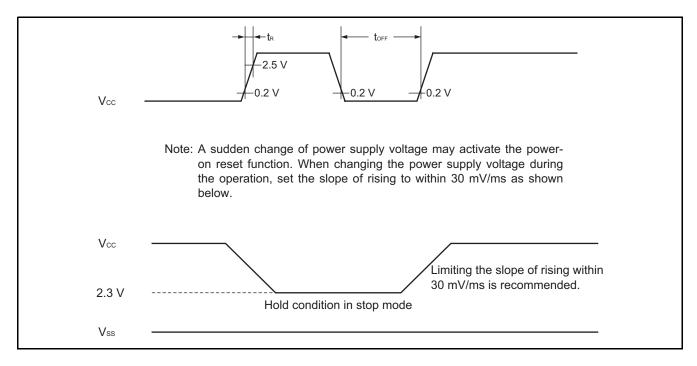

• Stabilizing supply voltage

Supply voltage must be stabilized.

A malfunction may occur when power supply voltage fluctuates rapidly even though the fluctuation is within the guaranteed operating range of the Vcc power supply voltage.

As a rule of voltage stabilization, suppress voltage fluctuation so that the fluctuation in V<sub>cc</sub> ripple (p-p value) at the commercial frequency (50 Hz/60 Hz) does not exceed 10% of the standard V<sub>cc</sub> value, and the transient fluctuation rate does not exceed 0.1 V/ms at a momentary fluctuation such as switching the power supply.

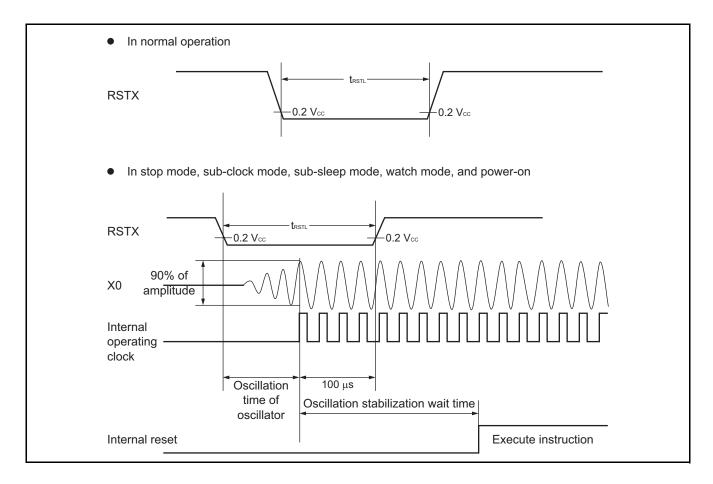

#### • Notes on using the external clock

When an external clock is used, oscillation stabilization wait time is required for power-on reset, wake-up from subclock mode or stop mode.

#### PIN CONNECTION

• Treatment of unused pins

If an unused input pin is left unconnected, a component may be permanently damaged due to malfunctions or latch-ups. Always pull up or pull down an unused input pin through a resistor of at least 2 k $\Omega$ . Set an unused input/output pin to the output state and leave it unconnected, or set it to the input state and treat it the same as an unused input pin. If there is an unused output pin, leave it unconnected.

• Power supply pins

To reduce unnecessary electro-magnetic emission, prevent malfunctions of strobe signals due to an increase in the ground level, and conform to the total output current standard, always connect the V<sub>cc</sub> pin and the V<sub>ss</sub> pin to the power supply and ground outside the device. In addition, connect the current supply source to the V<sub>cc</sub> pin and the V<sub>ss</sub> pin and the V<sub>ss</sub> pin with low impedance.

It is also advisable to connect a ceramic bypass capacitor of approximately 0.1  $\mu$ F between the V<sub>cc</sub> pin and the V<sub>ss</sub> pin at a location close to this device.

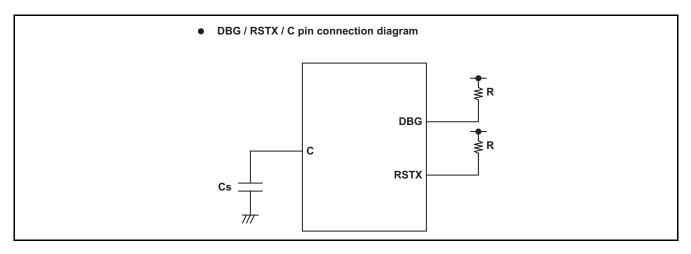

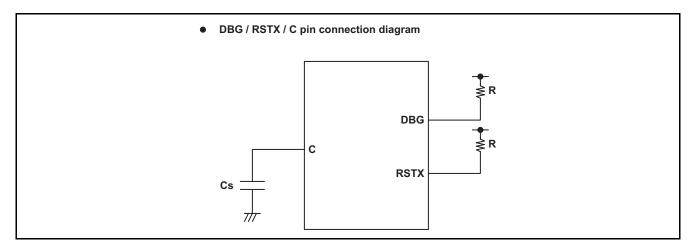

DBG pin

Connect the DBG pin directly to an external pull-up resistor.

To prevent the device from unintentionally entering the debug mode due to noise, minimize the distance between the DBG pin and the V<sub>cc</sub> or V<sub>ss</sub> pin when designing the layout of the printed circuit board.

The DBG pin should not stay at "L" level after power-on until the reset output is released.

#### RSTX pin

Connect the RSTX pin directly to an external pull-up resistor.

To prevent the device from unintentionally entering the reset mode due to noise, minimize the distance between the RSTX pin and the Vcc or Vss pin when designing the layout of the printed circuit board.

The RSTX/PF2 pin functions as the reset input/output pin after power-on. In addition, the reset output can be enabled by the RSTOE bit of the SYSC register, and the reset input function or the general purpose I/O function can be selected by the RSTEN bit of the SYSC register.

#### • C pin

Use a ceramic capacitor or a capacitor with equivalent frequency characteristics. The bypass capacitor for the V<sub>CC</sub> pin must have a capacitance larger than C<sub>s</sub>. For the connection to a smoothing capacitor C<sub>s</sub>, see the diagram below. To prevent the device from unintentionally entering an unknown mode due to noise, minimize the distance between the C pin and C<sub>s</sub> and the distance between C<sub>s</sub> and the V<sub>ss</sub> pin when designing the layout of a printed circuit board.

#### ■ PROGRAMMING FLASH MEMORY MICROCONTROLLERS USING SERIAL PROGRAMMER

#### • Serial programmers and adapters supported

The following table shows serial programmers and adapters supported.

| Package | Applicable adapter model | Serial programmer |

|---------|--------------------------|-------------------|

| SDIP 24 | TBD                      | TBD               |

| SOP 20  | TBD                      | TBD               |

| DIP 8   | TBD                      | TBD               |

| SOP 8   | TBD                      | TBD               |

#### • Programming method

TBD

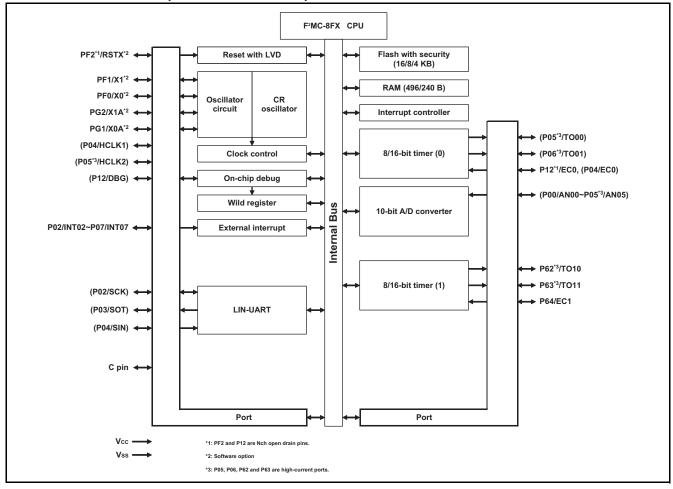

#### ■ BLOCK DIAGRAM (MB95200H Series)

#### ■ BLOCK DIAGRAM (MB95210H Series)

### ■ CPU CORE

#### 1. Memory Space

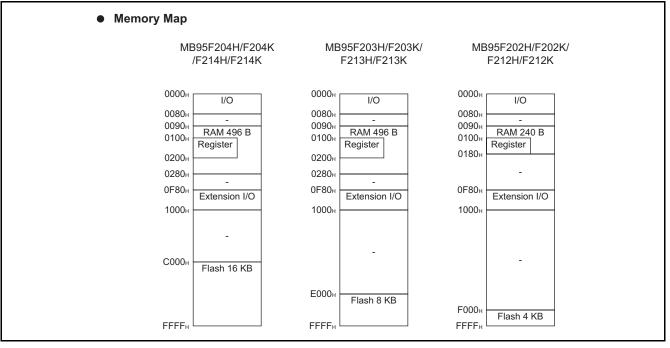

The memory space of the MB95200H/210H Series is 64 KB in size, and consists of an I/O area, a data area, and a program area. The memory space includes areas intended for specific purposes such as general-purpose registers and a vector table. The memory maps of the MB95200H/210H Series are shown below.

### ■ I/O MAP (MB95200H Series)

| Address       | Register abbreviation | Register name                                               | R/W           | Initial value         |

|---------------|-----------------------|-------------------------------------------------------------|---------------|-----------------------|

| 0000н         | PDR0                  | Port 0 data register                                        | R/W           | 0000000в              |

| <b>0001</b> н | DDR0                  | Port 0 direction register                                   | R/W           | 0000000в              |

| 0002н         | PDR1                  | Port 1 data register                                        | R/W           | 0000000в              |

| 0003н         | DDR1                  | Port 1 direction register                                   | R/W           | 0000000в              |

| 0004н         |                       | (Disabled)                                                  |               |                       |

| 0005н         | WATR                  | Oscillation stabilization wait time setting register        | R/W           | 11111111в             |

| 0006н         |                       | (Disabled)                                                  |               |                       |

| 0007н         | SYCC                  | System clock control register                               | R/W           | XXXXXX11 <sub>B</sub> |

| 0008н         | STBC                  | Standby control register                                    | R/W           | 00000XXX <sub>B</sub> |

| 0009н         | RSRR                  | Reset source register                                       | R             | XXXXXXXXB             |

| 000Ан         | TBTC                  | Timebase timer control register                             | R/W           | 0000000в              |

| 000Вн         | WPCR                  | Watch prescaler control register                            | R/W           | 0000000в              |

| 000Сн         | WDTC                  | Watchdog timer control register                             | R/W           | 0000000в              |

| 000Dн         | SYCC2                 | System clock control register 2                             | R/W           | XX100011 <sub>B</sub> |

| 000Eн         |                       |                                                             |               |                       |

| to            | —                     | (Disabled)                                                  |               | —                     |

| 0015H         |                       |                                                             | <b>D</b> 0.0/ |                       |

| 0016н         | PDR6                  | Port 6 data register                                        | R/W           | 0000000в              |

| <b>0017</b> н | DDR6                  | Port 6 direction register                                   | R/W           | 0000000в              |

| 0018⊦<br>to   |                       | (Disabled)                                                  |               |                       |

| 0027н         |                       |                                                             |               |                       |

| 0028н         | PDRF                  | Port F data register                                        | R/W           | 0000000в              |

| 0029н         | DDRF                  | Port F direction register                                   | R/W           | 0000000в              |

| 002Ан         | PDRG                  | Port G data register                                        | R/W           | 0000000в              |

| 002Вн         | DDRG                  | Port G direction register                                   | R/W           | 0000000в              |

| 002Сн         | PUL0                  | Port 0 pull-up register                                     | R/W           | 0000000в              |

| 002Dн         |                       |                                                             |               |                       |

| to            |                       | (Disabled)                                                  | —             | —                     |

| 0034н         |                       |                                                             |               |                       |

| 0035н         | PULG                  | Port G pull-up register                                     | R/W           | 0000000в              |

| 0036н         | T01CR1                | 8/16-bit composite timer 01 control status register 1 ch. 0 | R/W           | 0000000в              |

| 0037н         | T00CR1                | 8/16-bit composite timer 00 control status register 1 ch. 0 | R/W           | 0000000в              |

| 0038н         | T11CR1                | 8/16-bit composite timer 11 control status register 1 ch. 1 | R/W           | 0000000в              |

| 0039н         | T10CR1                | 8/16-bit composite timer 10 control status register 1 ch. 1 | R/W           | 0000000в              |

| 003A⊦<br>to   |                       | (Disabled)                                                  |               |                       |

| ю<br>0048н    |                       |                                                             |               |                       |

| 0049н         | EIC10                 | External interrupt circuit control register ch. 2/ch. 3     | R/W           | 0000000в              |

(Continued)

| Address              | Register abbreviation | Register name                                                     | R/W | Initial value |