MN704-00006-2v0-E

FUJITSU SEMICONDUCTOR CONTROLLER MANUAL

# F<sup>2</sup>MC-16FX 16-BIT MICROCONTROLLER MB96610/620 series HARDWARE MANUAL

FUJITSU SEMICONDUCTOR LIMITED

# F<sup>2</sup>MC-16FX 16-BIT MICROCONTROLLER MB96610/620 series HARDWARE MANUAL

For the information for microcontroller supports, see the following web site.

This web site includes the **"Customer Design Review Supplement"** which provides the latest cautions on system development and the minimal requirements to be checked to prevent problems before the system development.

http://edevice.fujitsu.com/micom/en-support/

FUJITSU SEMICONDUCTOR LIMITED

# Preface

#### Objectives and intended reader

Thank you very much for your continued patronage of Fujitsu semiconductor products.

The MB96600 Super series has been developed as a general-purpose version of the  $F^2MC-16FX$  series, which is an original 16-bit single-chip microcontroller compatible with the Application Specific IC (ASIC).

This manual explains the functions and operation of the MB96600 Super series for designers who actually use the MB96600 Super series to design products.

Please read this manual first and refer to the respective "Data Sheet" of devices for device-specific details..

#### Trademark

$F^2MC$  is the abbreviation of FUJITSU Flexible Microcontroller. Other system and product names in this manual are trademarks of respective companies or organizations. The symbols <sup>TM</sup> and <sup>®</sup> are sometimes omitted in this manual. • The contents of this document are subject to change without notice. Customers are advised to consult with sales representatives before ordering.

- The information, such as descriptions of function and application circuit examples, in this document are presented solely for the purpose of reference to show examples of operations and uses of FUJITSU SEMICONDUCTOR device; FUJITSU SEMICONDUCTOR does not warrant proper operation of the device with respect to use based on such information. When you develop equipment incorporating the device based on such information, you must assume any responsibility arising out of such use of the information. FUJITSU SEMICONDUCTOR assumes no liability for any damages whatsoever arising out of the use of the information.

- Any information in this document, including descriptions of function and schematic diagrams, shall not be construed as license of the use or exercise of any intellectual property right, such as patent right or copyright, or any other right of FUJITSU SEMICONDUCTOR or any third party or does FUJITSU SEMICONDUCTOR warrant non-infringement of any third-party's intellectual property right or other right by using such information. FUJITSU SEMICONDUCTOR assumes no liability for any infringement of the intellectual property rights or other rights of third parties which would result from the use of information contained herein.

- The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite). Please note that FUJITSU SEMICONDUCTOR will not be liable against you and/or any third party for any claims or

Please note that FUJITSU SEMICONDUCTOR will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products.

- Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

- Exportation/release of any products described in this document may require necessary procedures in accordance with the regulations of the Foreign Exchange and Foreign Trade Control Law of Japan and/or US export control laws.

- The company names and brand names herein are the trademarks or registered trademarks of their respective owners.

Copyright ©2011 FUJITSU SEMICONDUCTOR LIMITED All rights reserved.

# **Related Manuals**

The manuals related to this series are listed below. See the manual appropriate to the applicable conditions.

The contents of these manuals are subject to change without notice. Contact us to check the latest versions available.

#### Hardware Manual

· F<sup>2</sup>MC-16FX FAMILY MB96610/620 SERIES HARDWARE MANUAL (this manual)

#### Data sheet

For details about device-specific, Pin Assignments, electrical characteristics, package dimensions, ordering information etc., see the following document.

#### · 16-bit PROPRIETARY MICROCONTROLLER F<sup>2</sup>MC-16FX FAMILY DATA SHEET

\* The data sheets for each series are provided. Please see the appropriate data sheet for the series that you are using.

#### ■ CPU Programming manual

For details about the functions and operations of 16FX-CPU, see the following document.

#### • F<sup>2</sup>MC-16FX 16-BIT MICROCONTROLLER PROGRAMMING MANUAL

# How to Use This Manual

#### Finding a Function

The following methods can be used to search for the explanation of a desired function in this manual:

- Search from the table of the contents The table of the contents lists the manual contents in the order of description.

- Search from the register

The address where each register is located is not described in the text. To verify the address of a register, see "I/O Map" in Appendixes.

#### Terminology

This manual uses the following terminology.

| Term      | Explanation                           |  |

|-----------|---------------------------------------|--|

| Word      | Indicates access in units of 32 bits. |  |

| Half word | Indicates access in units of 16 bits. |  |

| Byte      | Indicates access in units of 8 bits.  |  |

#### Notations

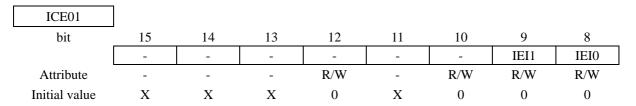

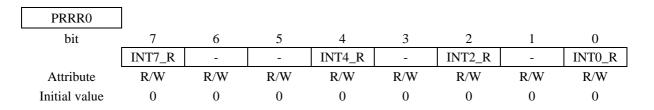

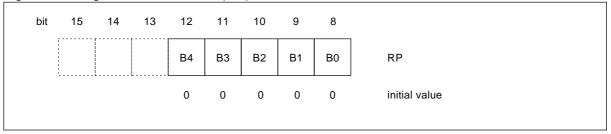

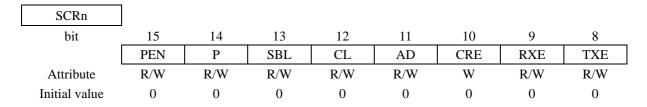

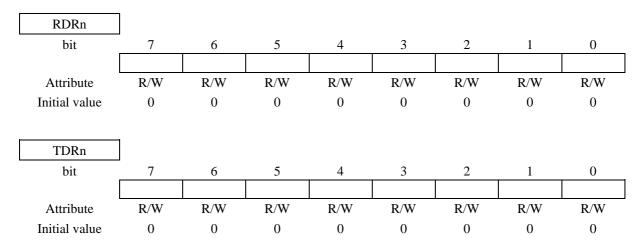

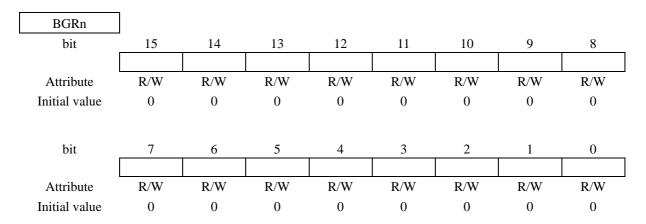

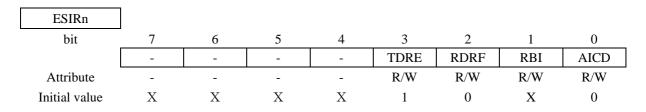

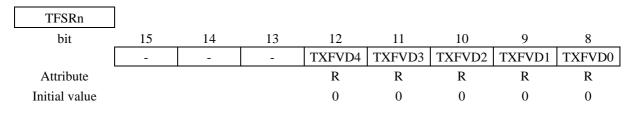

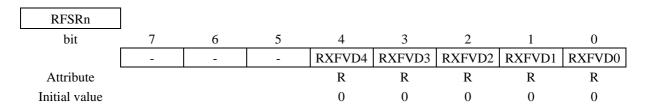

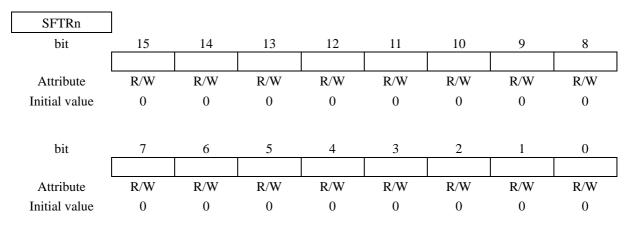

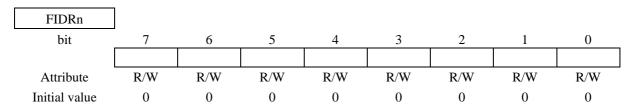

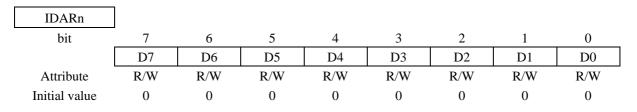

- · The notations in bit configuration of the register explanation of this manual are written as follows.

- bit : bit number

- · Attribute : Attributes for read and write of each bit

- $\cdot$  R : Read only

- $\cdot$  W : Write only

- · R/W : Readable/Writable

- $\cdot$  : Undefined

- · Initial value : Initial value of the register after reset

- $\cdot$  0 : Initial value is "0"

- $\cdot \ 1$  : Initial value is "1"

- $\cdot$  X : Initial value is undefined

- The multiple bits are written as follows in this manual. Example : bit7:0 indicates the bits from bit7 to bit0

- The values such as for addresses are written as follows in this manual.

- Hexadecimal number : "0x" is attached in the beginning of a value as a prefix (example : 0xFFFF)

- Binary number : "0b" is attached in the beginning of a value as a prefix (example: 0b1111)

- Decimal number : Written using numbers only (example : 1000)

# CONTENTS

| 1. Features22. Super Series Lineup43. Block Diagram of MB96F610/F62054. General Note on Using This Document75. 16-bit I/O-Timer Configuration86. Input Capture Unit Source Select for LIN-USART97. Peripheral Resource Pin Relocation15CHAPTER 2: CPU251. Overview262. Hardware Structure273. Memory Space313.1. Memory Areas323.2. Linear Addressing Method36                                                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

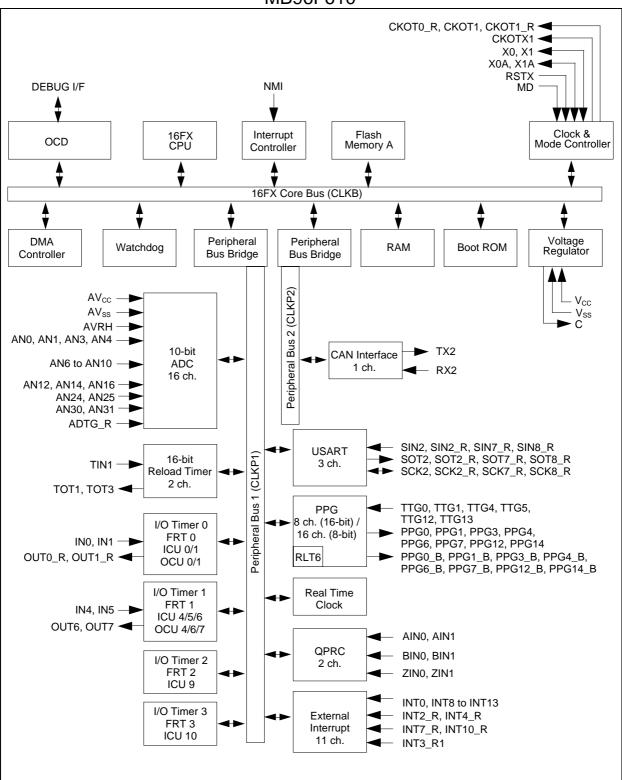

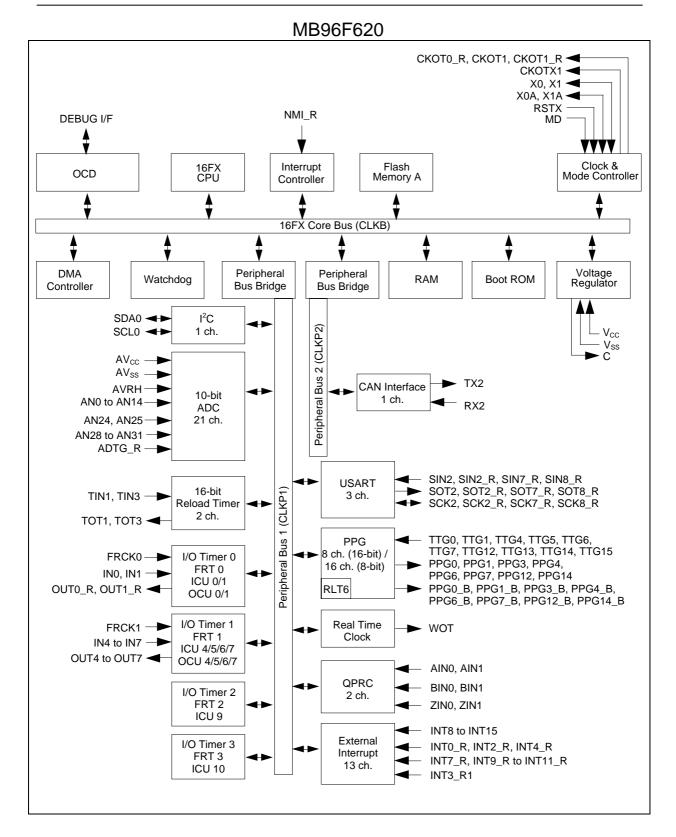

| 3. Block Diagram of MB96F610/F620       5         4. General Note on Using This Document       7         5. 16-bit I/O-Timer Configuration       8         6. Input Capture Unit Source Select for LIN-USART       9         7. Peripheral Resource Pin Relocation       15         CHAPTER 2: CPU       25         1. Overview       26         2. Hardware Structure       27         3. Memory Space       31         3.1. Memory Areas       32         3.2. Linear Addressing Method       35 |

| 4. General Note on Using This Document       7         5. 16-bit I/O-Timer Configuration       8         6. Input Capture Unit Source Select for LIN-USART       9         7. Peripheral Resource Pin Relocation       15         CHAPTER 2: CPU       25         1. Overview       26         2. Hardware Structure       27         3. Memory Space       31         3.1. Memory Areas       32         3.2. Linear Addressing Method       35                                                   |

| 5. 16-bit I/O-Timer Configuration       8         6. Input Capture Unit Source Select for LIN-USART       9         7. Peripheral Resource Pin Relocation       15         CHAPTER 2: CPU       25         1. Overview       26         2. Hardware Structure       27         3. Memory Space       31         3.1. Memory Areas       32         3.2. Linear Addressing Method       35                                                                                                          |

| 6. Input Capture Unit Source Select for LIN-USART                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 7. Peripheral Resource Pin Relocation       15         CHAPTER 2: CPU       25         1. Overview       26         2. Hardware Structure       27         3. Memory Space       31         3.1. Memory Areas       32         3.2. Linear Addressing Method       35                                                                                                                                                                                                                              |

| 7. Peripheral Resource Pin Relocation       15         CHAPTER 2: CPU       25         1. Overview       26         2. Hardware Structure       27         3. Memory Space       31         3.1. Memory Areas       32         3.2. Linear Addressing Method       35                                                                                                                                                                                                                              |

| 1. Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2. Hardware Structure    27      3. Memory Space    31      3.1. Memory Areas    32      3.2. Linear Addressing Method    35                                                                                                                                                                                                                                                                                                                                                                       |

| 2. Hardware Structure    27      3. Memory Space    31      3.1. Memory Areas    32      3.2. Linear Addressing Method    35                                                                                                                                                                                                                                                                                                                                                                       |

| 3.1. Memory Areas    32      3.2. Linear Addressing Method    35                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3.1. Memory Areas    32      3.2. Linear Addressing Method    35                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3.3. Bank Addressing Method                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.4. Multi-byte Data in Memory Space                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

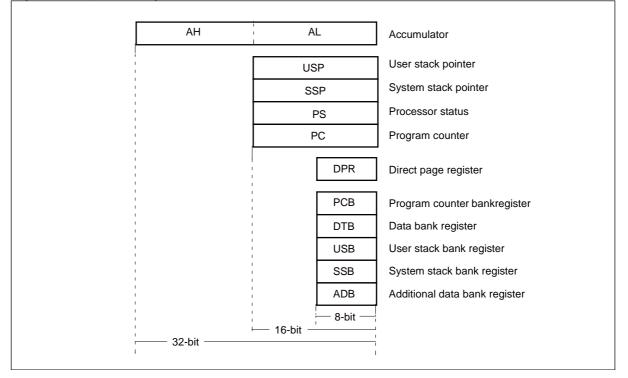

| 4. Special Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4.1. Accumulator (A)42<br>4.2. User Stack Pointer (USP) and System Stack Pointer (SSP)44                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4.3. Processor Status (PS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

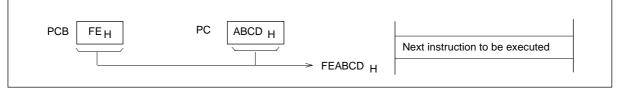

| 4.4. Program Counter (PC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

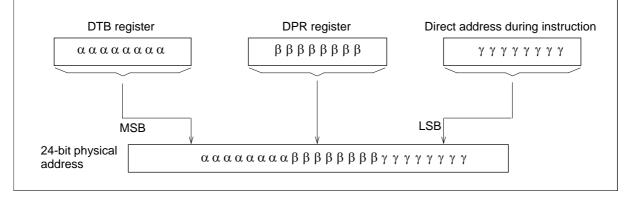

| 4.5. Direct Page Register (DPR)50                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4.6. Bank Register (PCB, DTB, ADB, USB, SSB)51                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

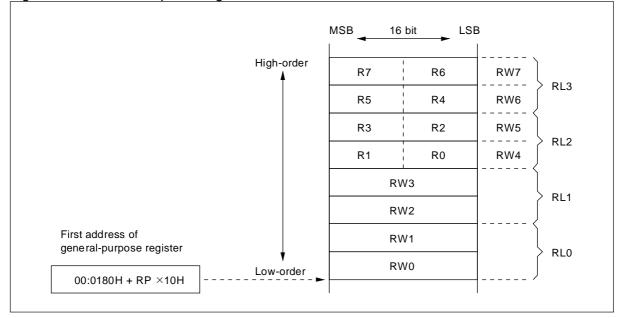

| 5. General-Purpose Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5.1. Register Bank                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5.2. Addressing General-Purpose Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6. Prefix Codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6.2. Common Register Bank Prefix (CMR)                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 6.3. Flag Change Inhibit Prefix (NCC)                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6.4. Prefix Code Restrictions                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

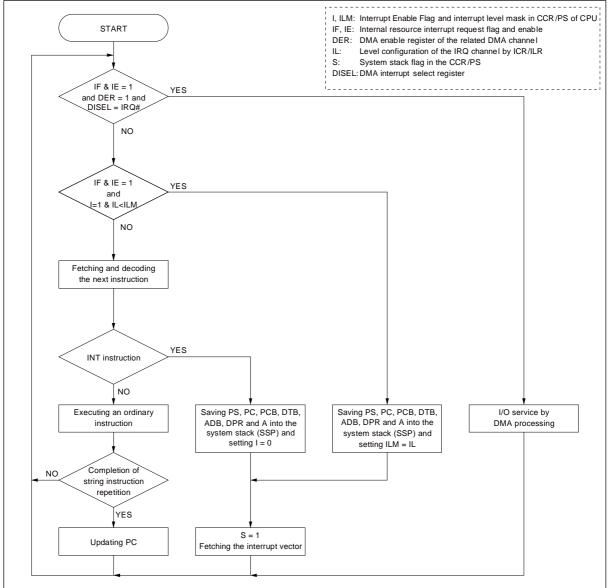

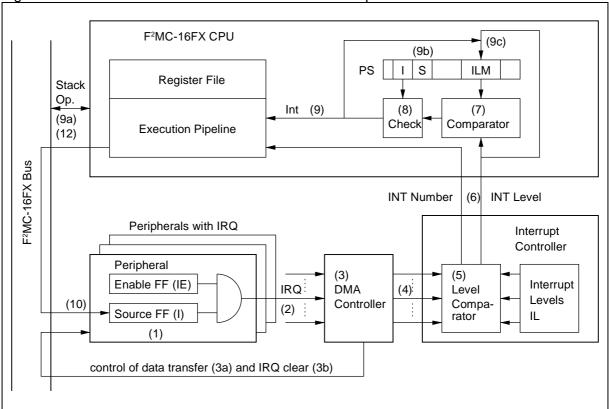

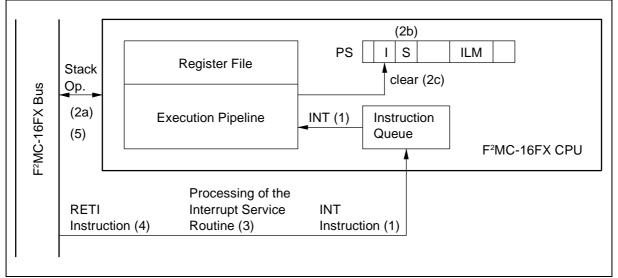

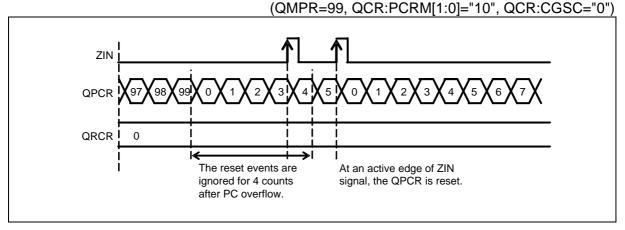

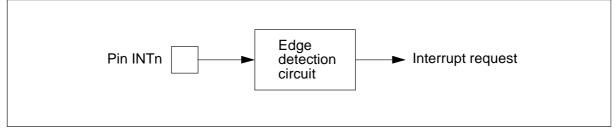

| CHAPTER 3: INTERRUPTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1. Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2. Interrupt Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3. Hardware Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4. Software Interrupts71                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5. Multiple Interrupts73                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6. Exceptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 7. Interrupt Vector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

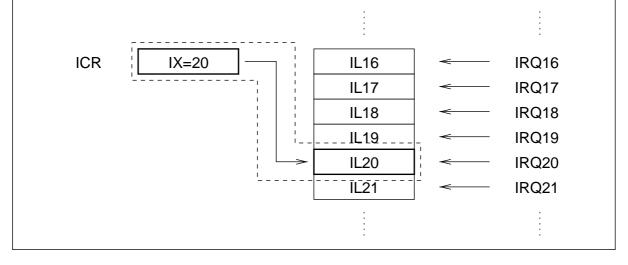

| 8. Interrupt Control Registers (ICR)                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

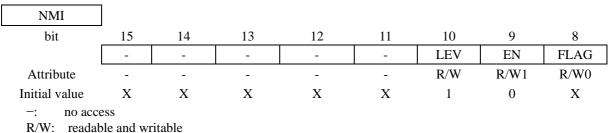

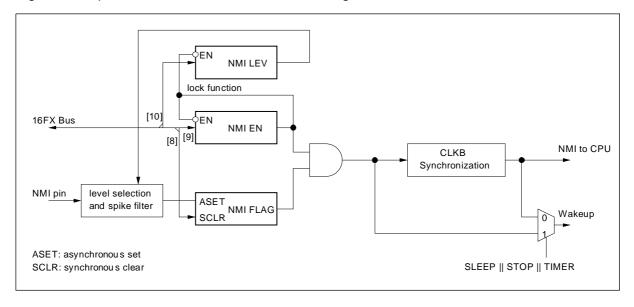

| 9. Non Maskable Interrupt (NMI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

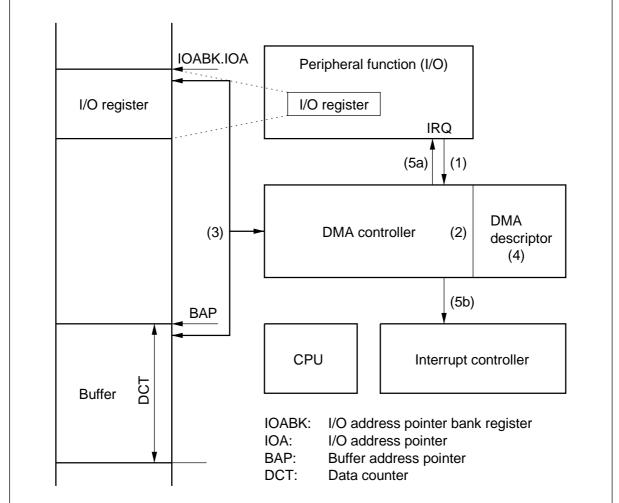

| CHAPTER 4: DMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 91                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 1. Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 92                                     |

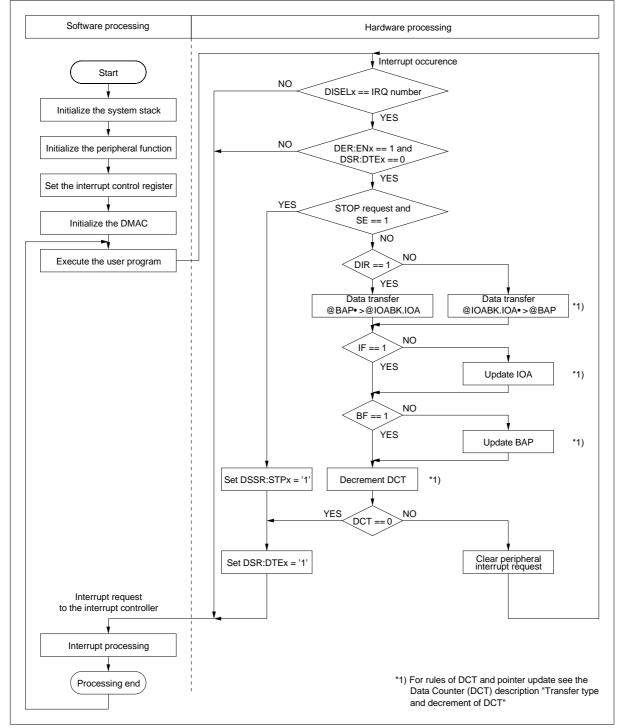

| 2. Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 94                                     |

| 3. Descriptor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 96                                     |

| 3.1. DMA Register List                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 98                                     |

| 3.2. DMA I/O Address Pointer Bank Select (IOABK)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                        |

| 3.3. Data Count Register (DCT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                        |

| 3.4. I/O Register Address Pointer (IOA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                        |

| 3.5. DMA Control Register (DMACS)<br>3.6. Buffer Address Pointer (BAP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                        |

| 4. Registers<br>4.1. DMA Interrupt Request Select Register (DISEL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                        |

| 4.2. DMA Interrupt Request Select Register (DISEL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                        |

| 4.3. DMA Stop Status Register (DSSR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                        |

| 4.4. DMA Enable Register (DER)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                        |

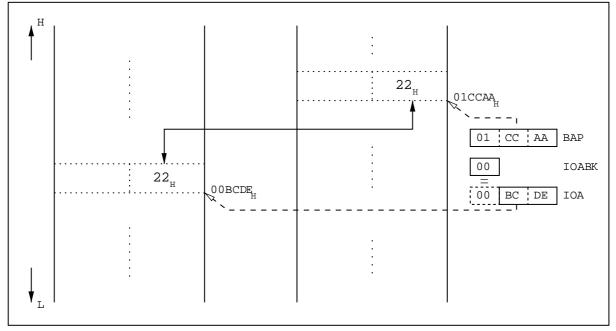

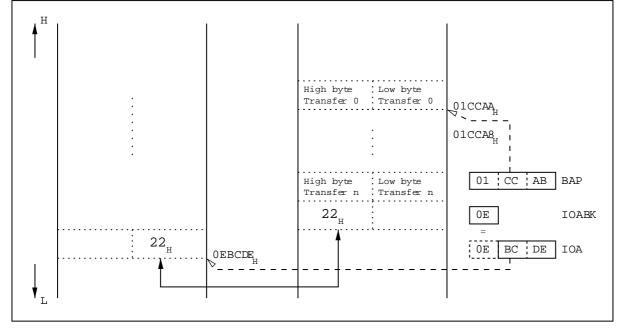

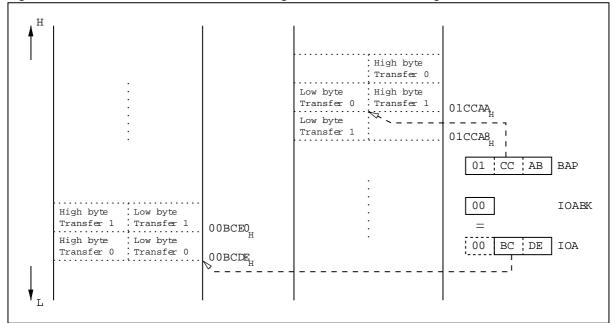

| 5. Examples of DMA Transfers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        |

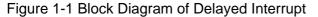

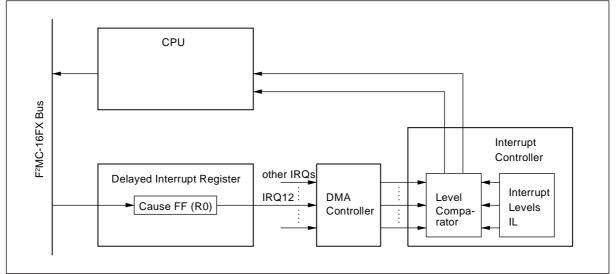

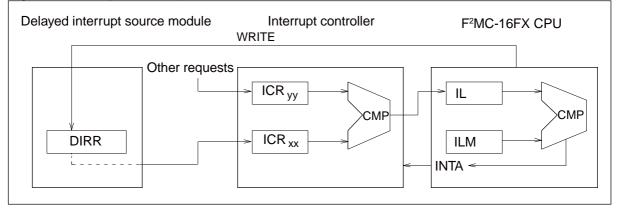

| CHAPTER 5: DELAYED INTERRUPT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                        |

| 1. Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                        |

| 2. Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        |

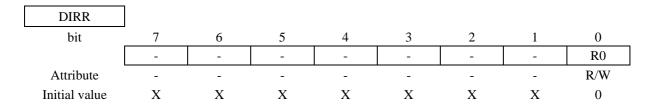

| <ol> <li>Register</li></ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 116                                    |

| Cancellation Register (DIRR: Delayed Interrupt Request Register)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 117                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 44.0                                   |

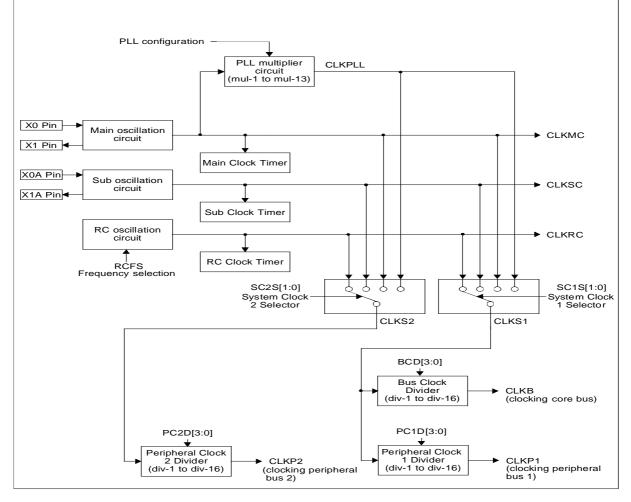

| CHAPTER 6: CLOCKS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                        |

| 1. Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 120                                    |

| 1. Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 120<br>122                             |

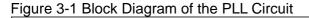

| 1. Overview<br>2. Clock Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 120<br>122<br>124                      |

| <ol> <li>Overview</li> <li>Clock Modes</li> <li>Configuration of the PLL</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 120<br>122<br>124<br>126               |

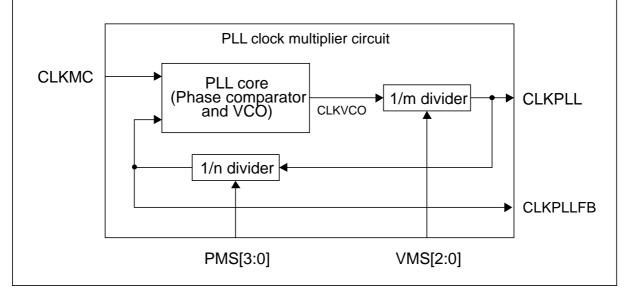

| <ol> <li>Overview</li></ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 120<br>122<br>124<br>126<br>128        |

| <ol> <li>Overview</li></ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 120<br>122<br>124<br>126<br>128<br>130 |

| <ol> <li>Overview</li></ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                        |

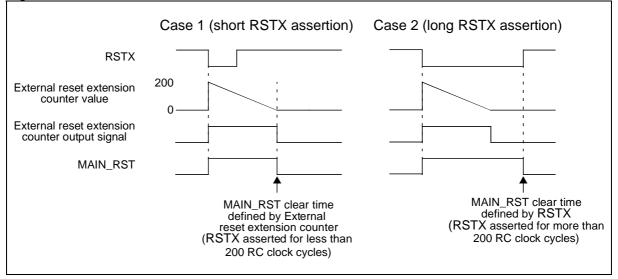

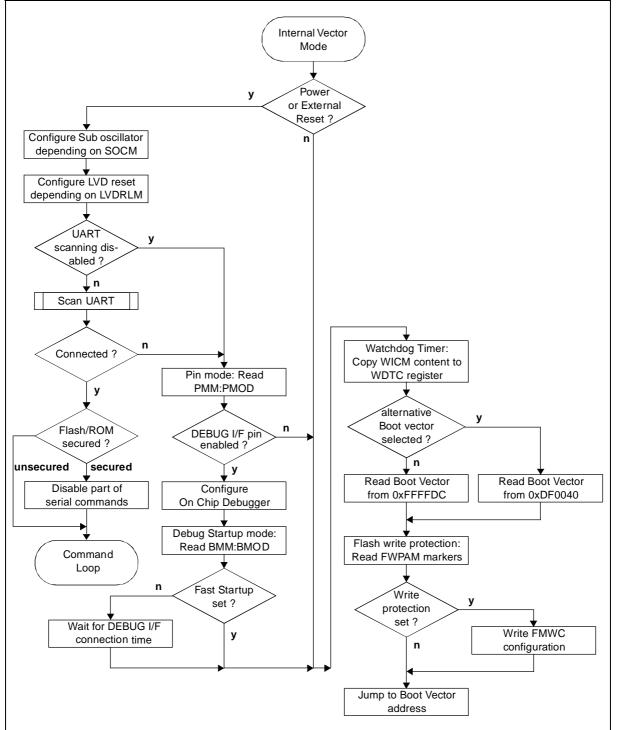

| <ol> <li>Overview</li> <li>Clock Modes</li> <li>Configuration of the PLL</li> <li>Oscillation Stabilization Wait Time</li> <li>Connection of an Oscillator or an External Clock to the Microcontroller</li> <li>Registers</li> <li>Clock Selection Register (CKSR)</li> <li>Clock Monitor Register (CKMR)</li> <li>Clock Stabilization Select Register (CKSSR)</li> <li>Clock Stabilization Select Register (CKSR)</li> <li>Clock Frequency Control Register (CKSR)</li> <li>Clock Frequency Control Register (CKFCR)</li> <li>PLL Control Register (PLLCR)</li> </ol> CHAPTER 7: RESETS AND STARTUP <ol> <li>Overview</li> <li>Reset, System Clock and Stabilization Wait Times</li> <li>Startup after Power and External Reset</li> </ol> |                                        |

| <ol> <li>Overview</li></ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                        |

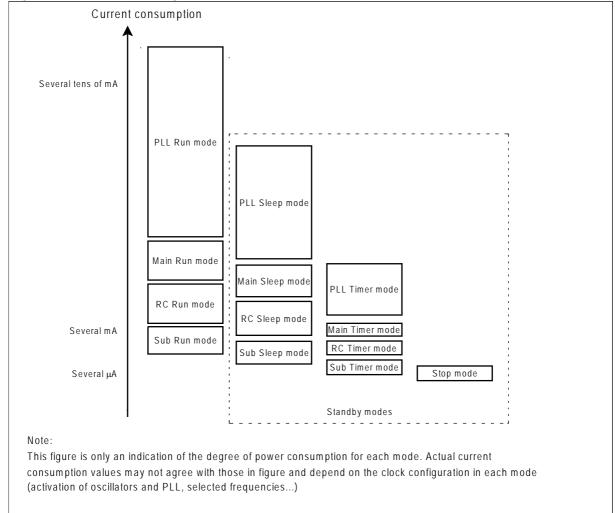

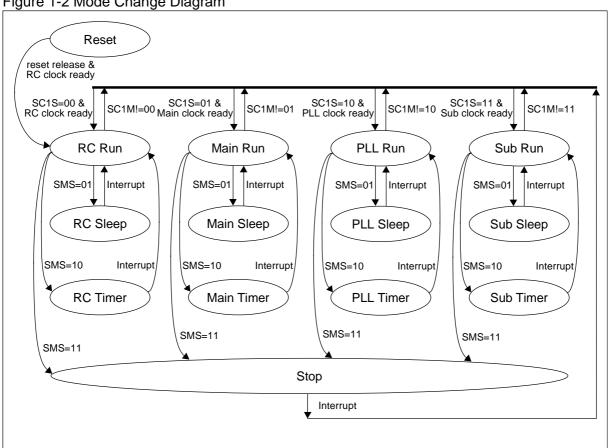

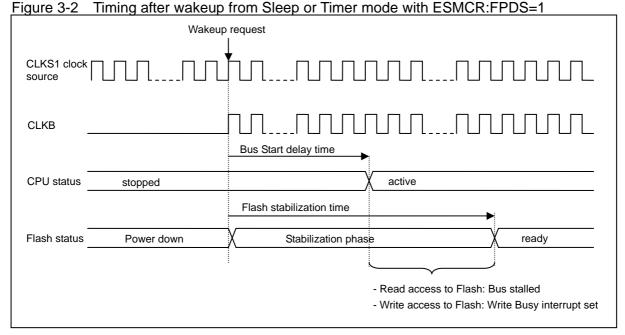

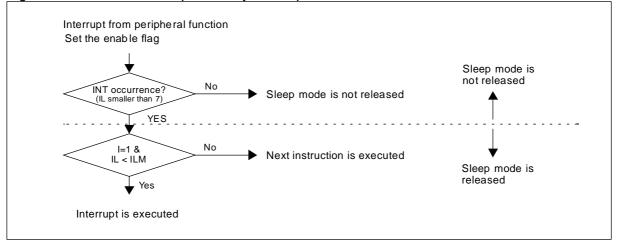

| CHAPTER 8: STANDBY MODE AND VOLTAGE REGULATOR CONTROL CIRCUIT                                         | 177 |

|-------------------------------------------------------------------------------------------------------|-----|

| 1. Overview                                                                                           | 178 |

| 2. Usage Notes on Standby Mode                                                                        | 182 |

| 3. Using the Extended Standby Mode Control Register                                                   | 184 |

| 4. Voltage Regulator Operation                                                                        | 187 |

| 4.1. Changing the Voltage Regulator operation mode                                                    |     |

| 4.2. Setting the Voltage Regulator Output Voltage                                                     | 190 |

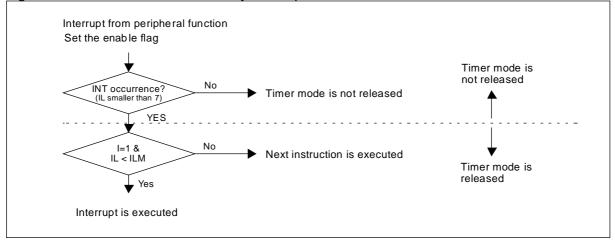

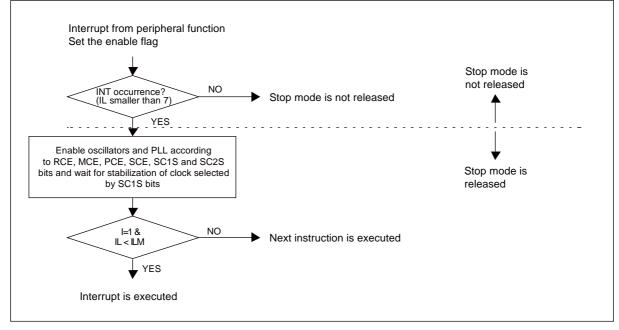

| 5. Standby Modes                                                                                      |     |

| 5.1. Sleep mode (RC Sleep, Main Sleep, PLL Sleep, Sub Sleep Mode)                                     |     |

| 5.2. Timer Mode (RC Timer, Main Timer, PLL Timer, Sub Timer mode)                                     |     |

| 5.3. Stop Mode                                                                                        |     |

| 6. Mode Change Table and Operation Status                                                             |     |

| 7. Registers                                                                                          |     |

| 7.1. Standby Mode Control Register (SMCR)                                                             |     |

| 7.2. Extended Standby Mode Control Register (ESMCR)<br>7.3. Voltage Regulator Control Register (VRCR) |     |

|                                                                                                       |     |

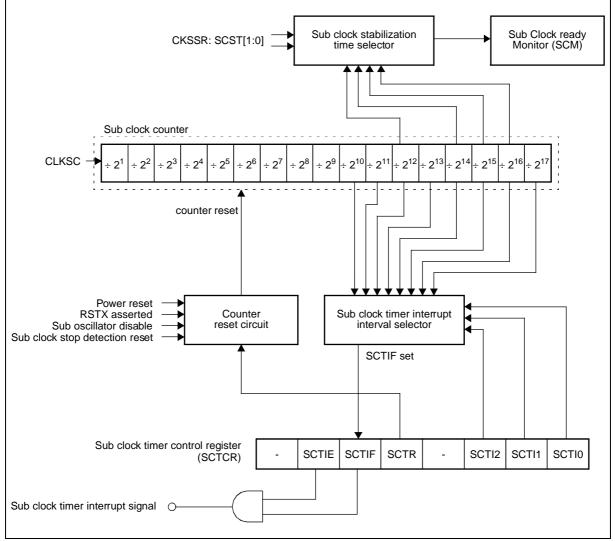

| CHAPTER 9: SOURCE CLOCK TIMERS                                                                        | 211 |

| 1. Overview                                                                                           | 212 |

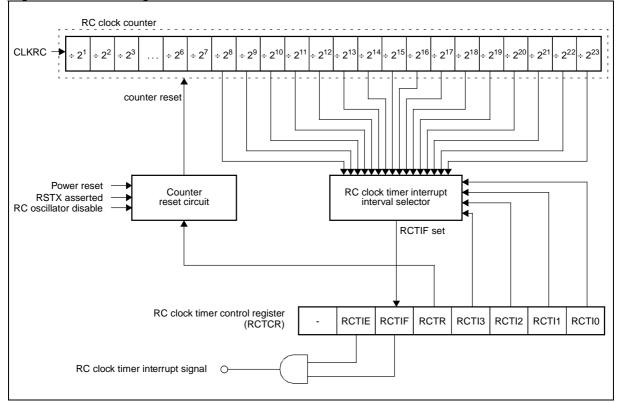

| 2. RC Clock Timer                                                                                     | 213 |

| 2.1. Operations                                                                                       |     |

| 2.2. RC Clock Timer Control Register (RCTCR)                                                          | 215 |

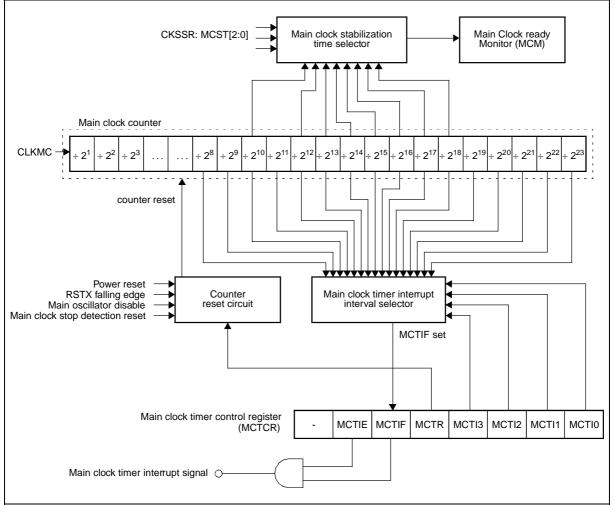

| 3. Main Clock Timer                                                                                   |     |

| 3.1. Operations                                                                                       |     |

| 3.2. Main Clock Timer Control Register (MCTCR)                                                        |     |

| 4. Sub Clock Timer                                                                                    |     |

| 4.1. Operations<br>4.2. Sub Clock Timer Control Register (SCTCR)                                      |     |

|                                                                                                       |     |

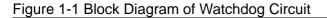

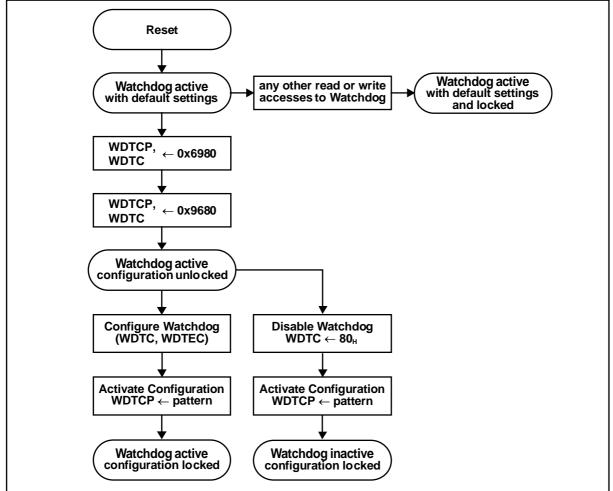

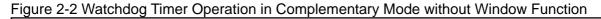

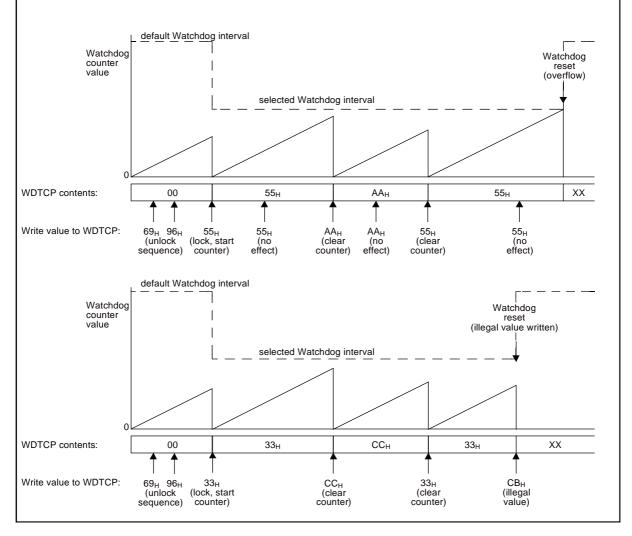

| CHAPTER 10: WATCHDOG TIMER AND WATCHDOG RESET                                                         | 225 |

| 1. Overview                                                                                           | 226 |

| 2. Operation                                                                                          | 227 |

| 3. Registers                                                                                          | 233 |

| 3.1. Watchdog Timer Configuration Register (WDTC)                                                     |     |

| 3.2. Watchdog Timer Extended Configuration Register (WDTEC)                                           |     |

| 3.3. Watchdog Timer Clear Pattern Register (WDTCP)                                                    | 241 |

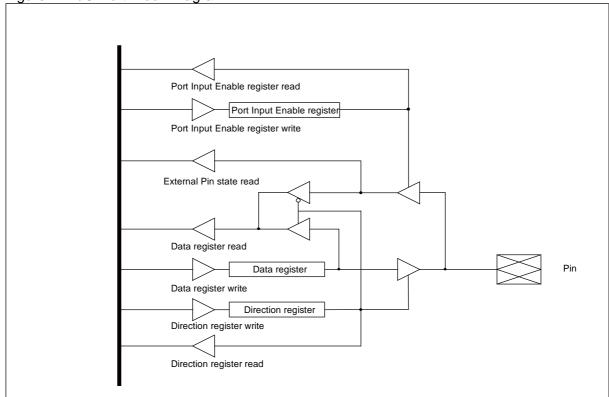

| CHAPTER 11: I/O PORTS                                                                                 | 243 |

| 1. Overview                                                                                           | 244 |

| 2. Registers                                                                                          | 245 |

| 2.1. Port Data Register (PDRnn)                                                                       | 246 |

| 2.2. External Pin State Register (EPSRnn)                                                             |     |

| 2.3. Data Direction Register (DDRnn)                                                                  |     |

| 2.4. Port Input Enable Register (PIERnn)                                                              |     |

| 2.5. Port High Drive Register (PHDRnn)                                                                |     |

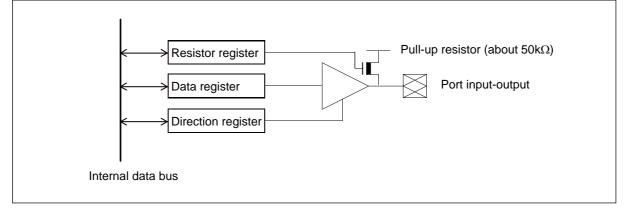

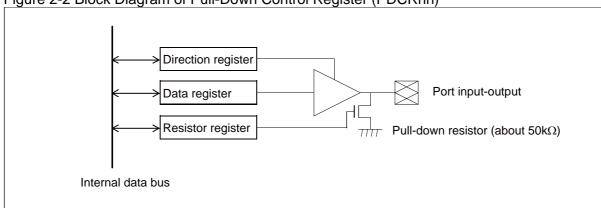

| 2.6. Pull-Up Control Register (PUCRnn)<br>2.7. Pull-Down Control Register (PDCRnn)                    |     |

|                                                                                                       |     |

| 3. Register Usage                                                                                     | 204 |

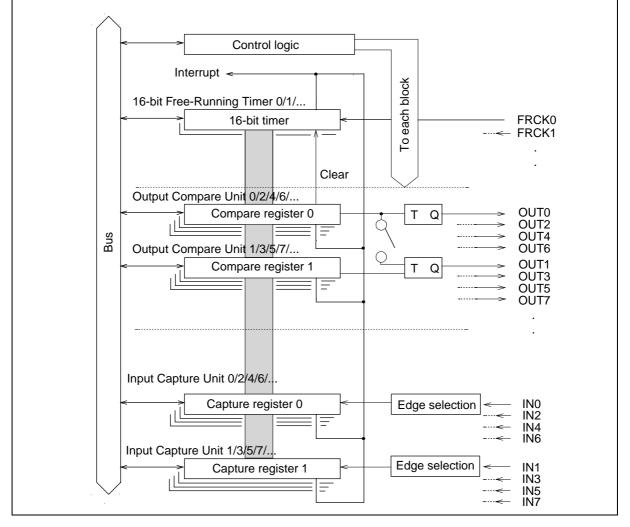

| CHAPTER 12: 16-BIT I/O TIMER                                                             | 255 |

|------------------------------------------------------------------------------------------|-----|

| 1. Overview                                                                              | 256 |

| 2. 16-bit I/O Timer Registers                                                            | 258 |

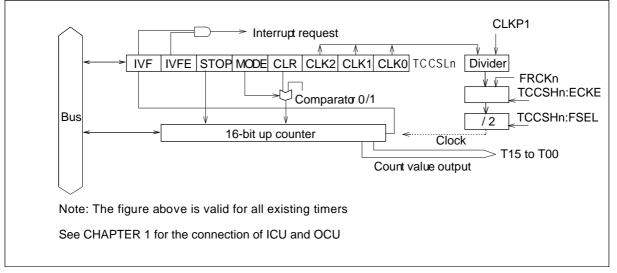

| 3. 16-bit Free-Running Timer                                                             | 260 |

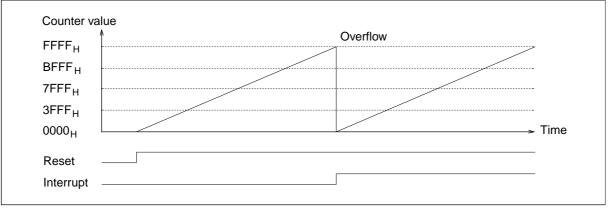

| 3.1. Operation                                                                           | 261 |

| 3.2. Data Register (TCDTn)                                                               | 263 |

| 3.3. Control Status Register (TCCSLn)                                                    | 264 |

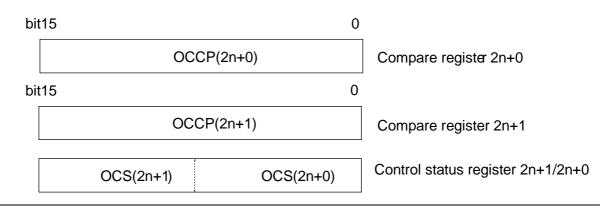

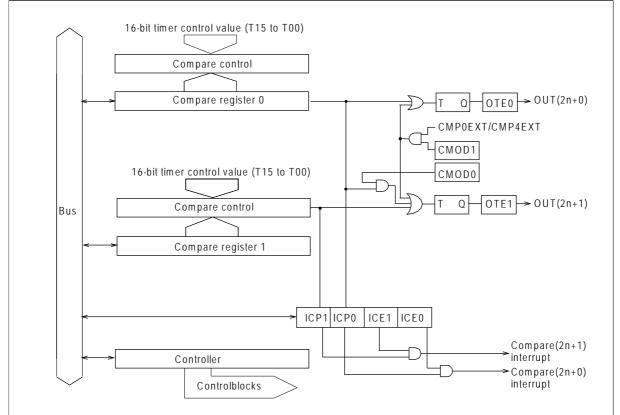

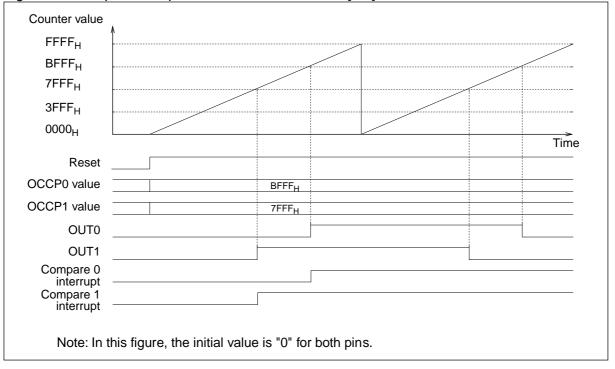

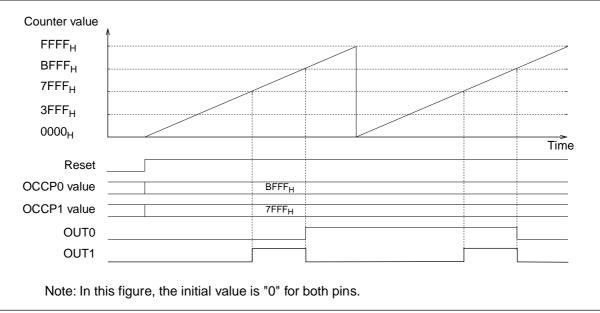

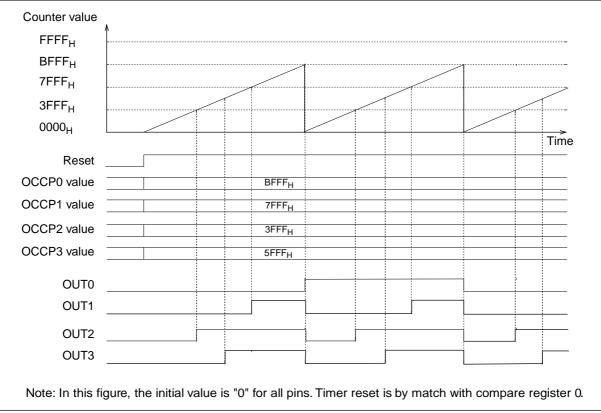

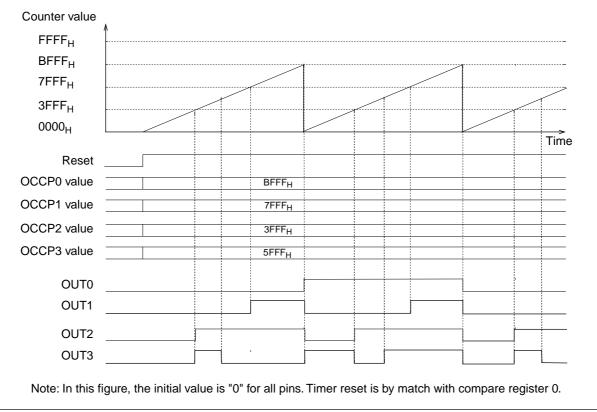

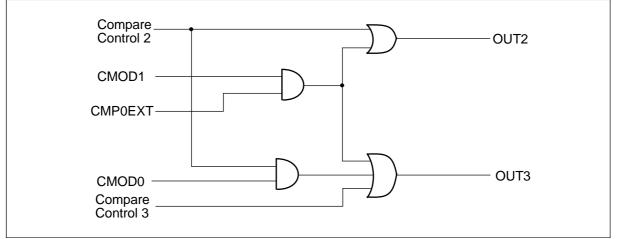

| 4. Output Compare Unit                                                                   | 267 |

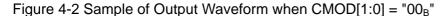

| 4.1. Operation                                                                           |     |

| 4.2. Output Compare Register (OCCP(2n) / OCCP(2n+1))                                     | 273 |

| 4.3. Control Status Registers of Output Compare (OCS(2n) / OCS(2n+1))                    | 274 |

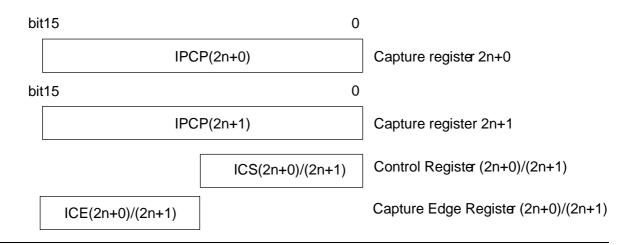

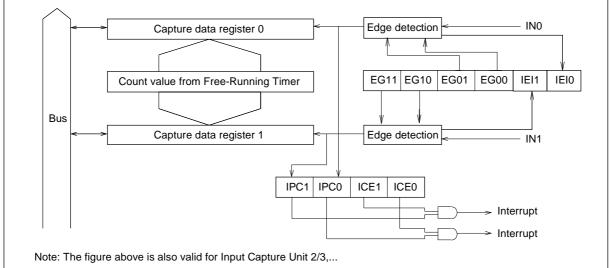

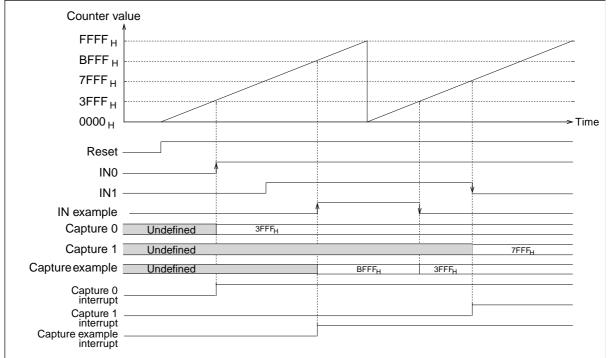

| 5. Input Capture Unit                                                                    |     |

| 5.1. Operation                                                                           | 281 |

| 5.2. Input Capture Data Register (IPCPn)                                                 |     |

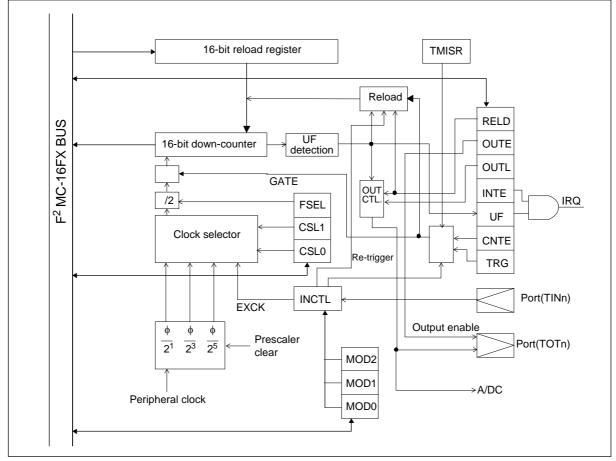

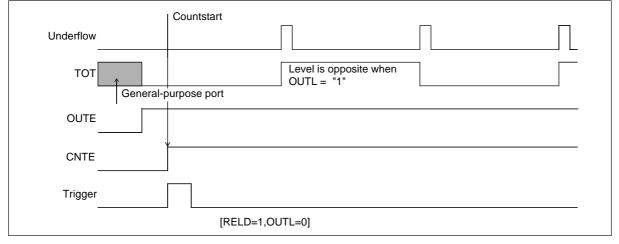

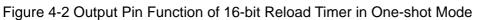

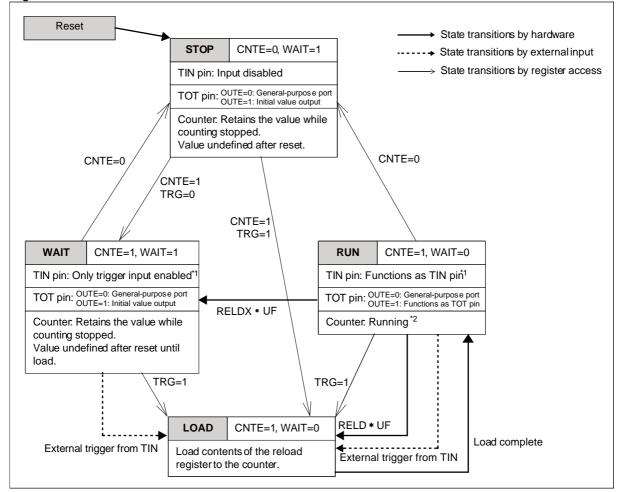

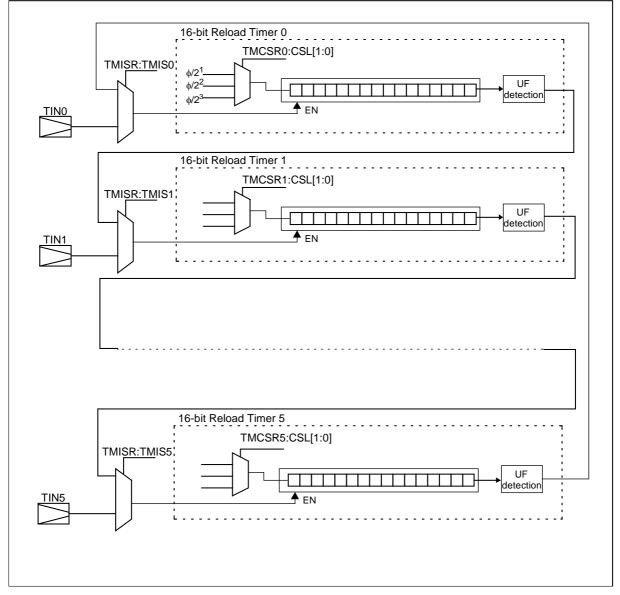

| CHAPTER 13: 16-BIT RELOAD TIMER (WITH EVENT COUNT FUNCTION)                              |     |

| 1. Overview                                                                              |     |

| 2. Internal Clock and External Event Counter Operations                                  | 290 |

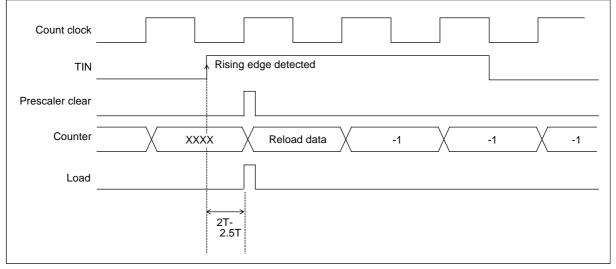

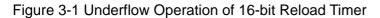

| 3. Underflow Operation                                                                   |     |

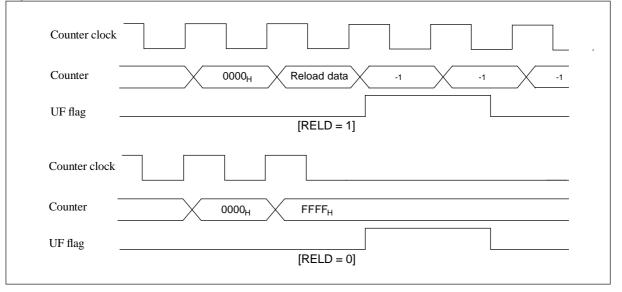

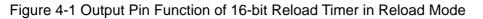

| 4. Output Pin Functions                                                                  |     |

| 5. Counter Operation State                                                               |     |

|                                                                                          |     |

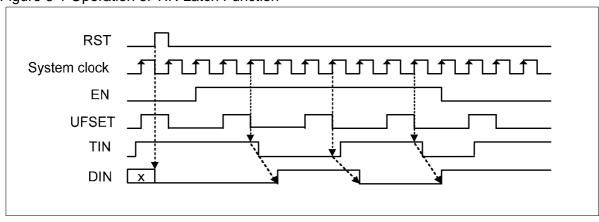

| 6. TIN Latch Function                                                                    |     |

| 7. 16-Bit Reload Timer (With Event Count Function)                                       |     |

| 7.1. Timer Control Status Register (TMCSRn)                                              | 297 |

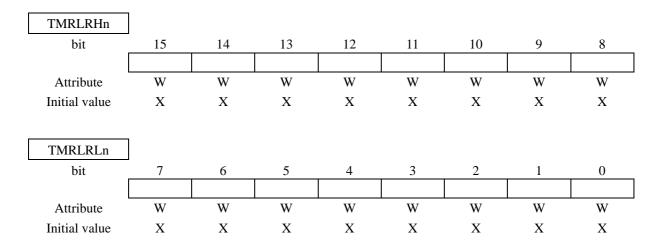

| 7.2. Register Layout of 16-bit Timer Register (TMRn)/<br>16-bit Reload Register (TMRLRn) | 300 |

| 8. Cascading                                                                             |     |

| 8.1. Reload Timer Input Select Register (TMISR)                                          |     |

|                                                                                          |     |

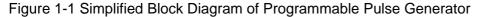

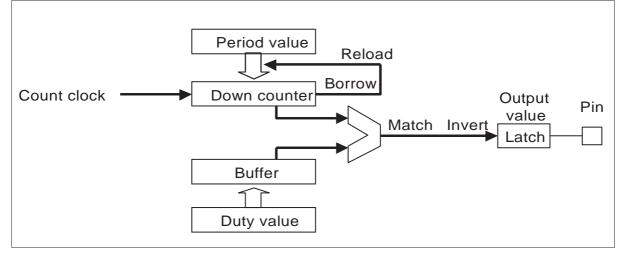

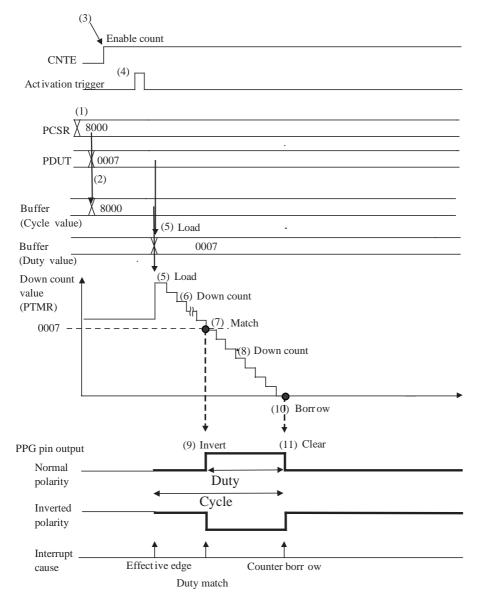

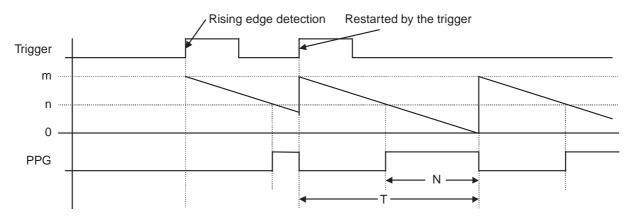

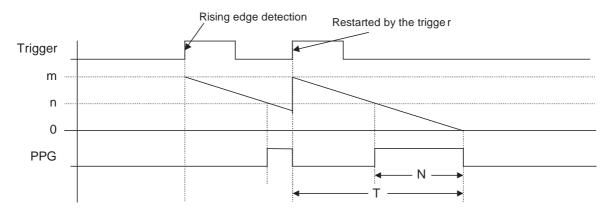

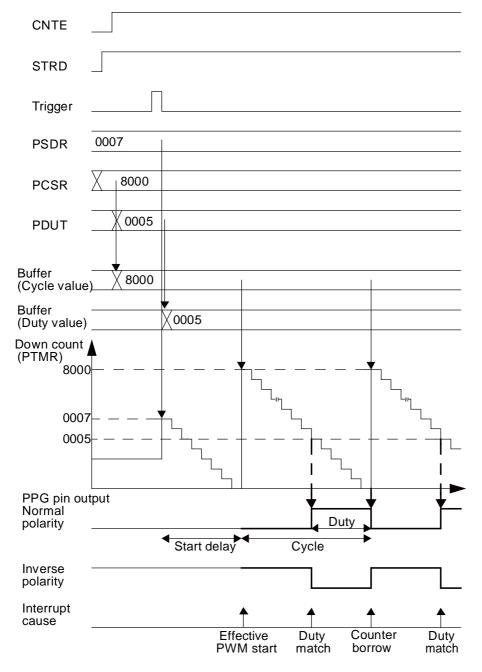

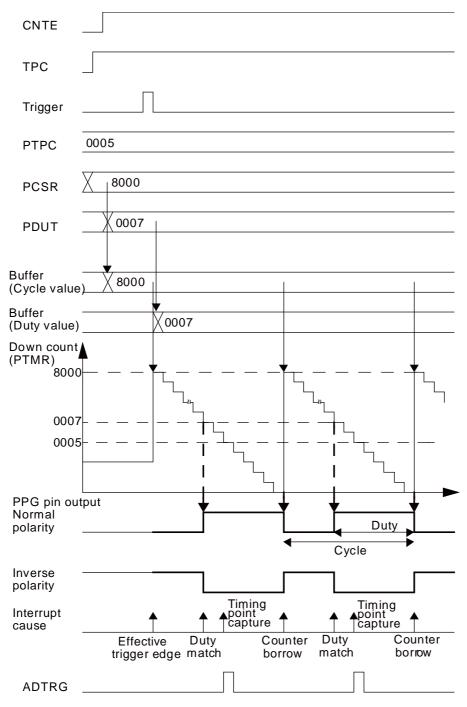

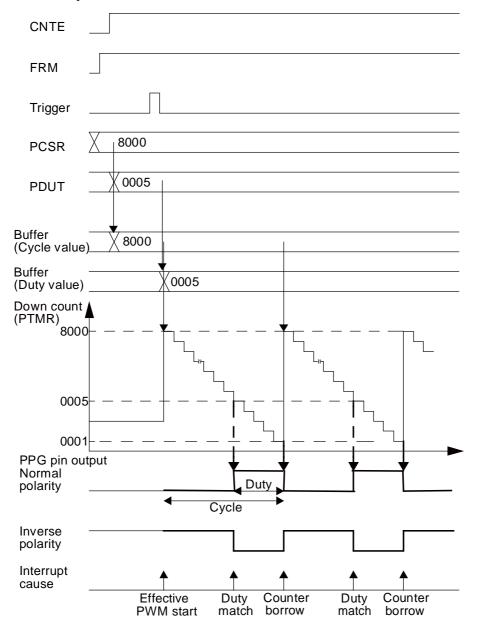

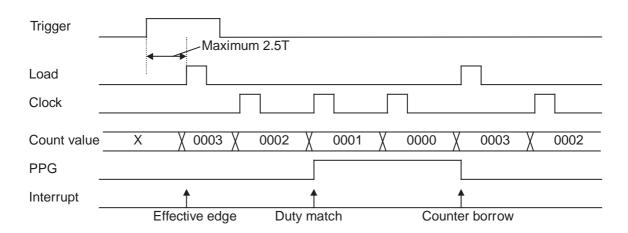

| CHAPTER 14: PROGRAMMABLE PULSE GENERATOR                                                 |     |

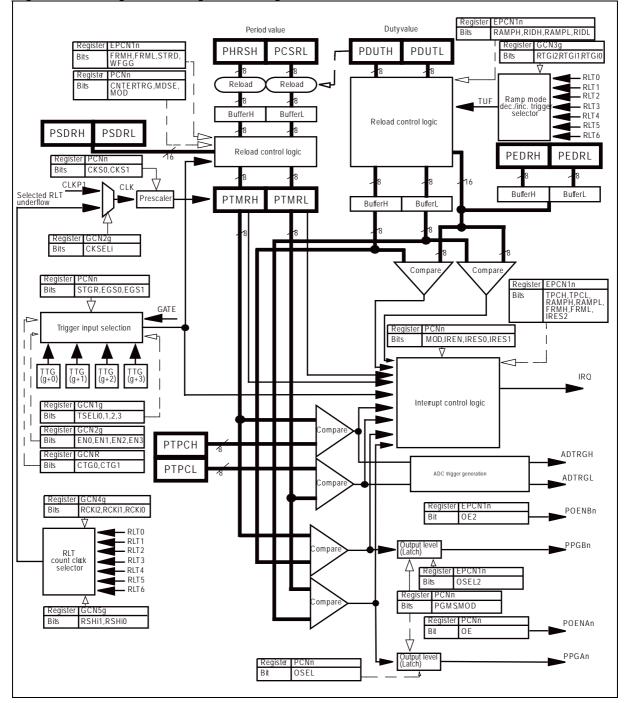

| 1. Overview                                                                              |     |

| 2. Operation                                                                             | 310 |

| 3. Registers                                                                             |     |

| 3.1. PPG Control Status Register (PCNn)                                                  |     |

| 3.2. Extended PPG Control Status Register 1 (EPCN1n)                                     |     |

| 3.3. Extended PPG Control Status Register 2 (EPCN2n)                                     |     |

| 3.4. General Control Register 1 (GCN1g)                                                  |     |

| 3.5. General Control Register 2 (GCN2g)                                                  |     |

| 3.6. General Control Register 3 (GCN3g)                                                  |     |

| 3.7. General Control Register 4 (GCN4g)                                                  |     |

| 3.8. General Control Register 5 (GCN5g)<br>3.9. PPG Cycle Setting Register (PCSRn)       |     |

| 3.10. PPG Duty Setting Register (PDUTn)                                                  |     |

| 3.11. PPG Timer Register (PTMRn)                                                         |     |

| 3.12. PPG Start Delay Register (PSDRn)                                                   |     |

| 3.13. PPG Timing Point Capture Register (PTPCn)                                          |     |

| 3.14. PPG End Duty Register (PEDRn)                                                      |     |

| 3.15. General Control Register (GCNR)                                                    |     |

| 4. Cautions                                                                              |     |

|                                                                                          |     |

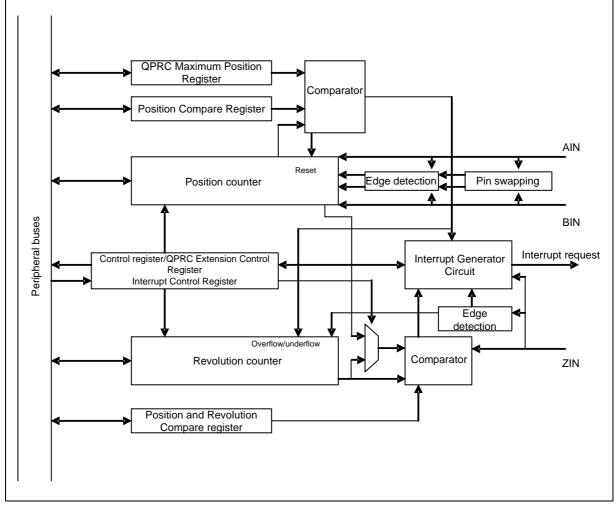

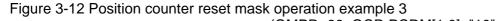

| CHAPTER 15: Quadrature Position/Revolution Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 343                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 344                                                                                                                                                           |

| 2. Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 345                                                                                                                                                           |

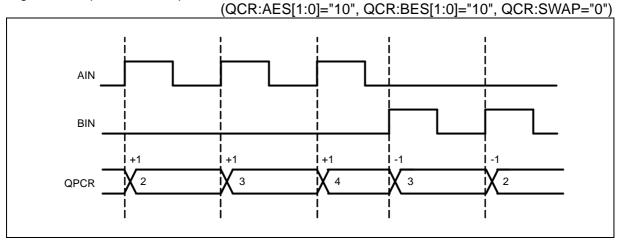

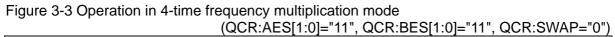

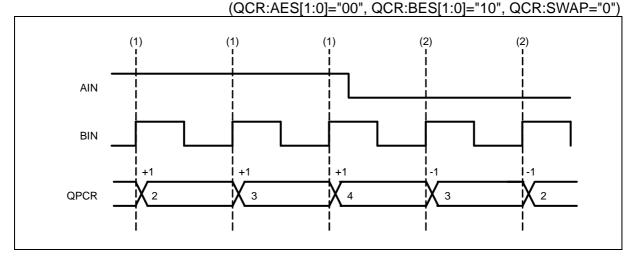

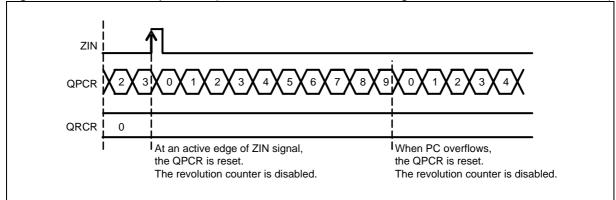

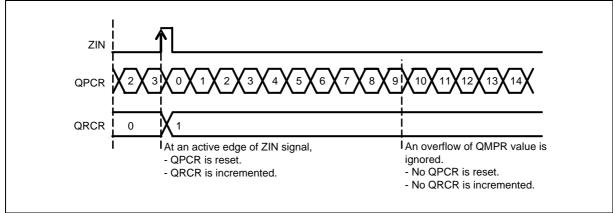

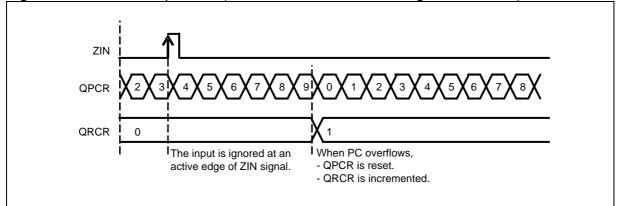

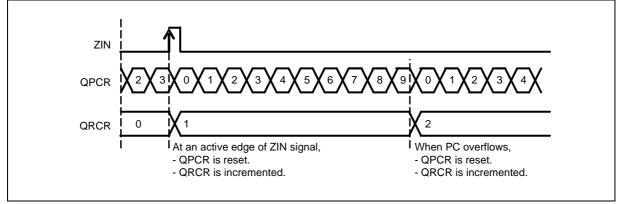

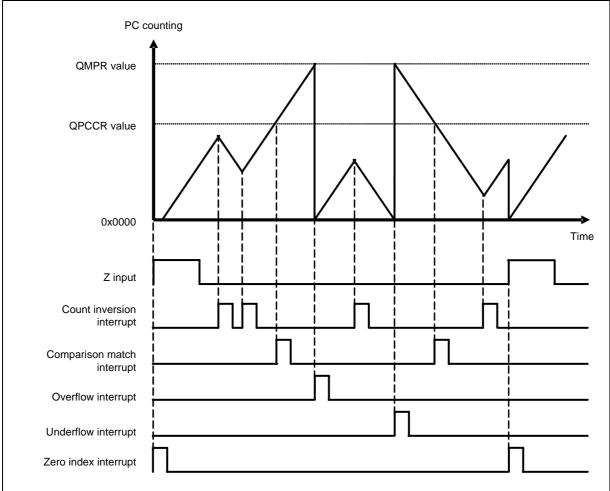

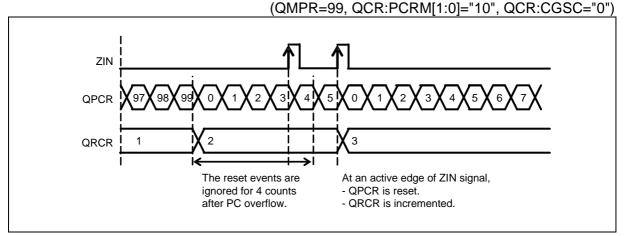

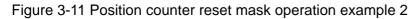

| 3. Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 346                                                                                                                                                           |

| 4. Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                               |

| 4.1. Quadrature Position/Revolution Counter Position Count Register (QPCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                               |

| 4.2. QPRC Revolution Count Register (QRCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                               |

| 4.3. QPRC Position Counter Compare Register (QPCCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 363                                                                                                                                                           |

| 4.4. QPRC Position and Revolution Counter Compare Register (QPRCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 364                                                                                                                                                           |

| 4.5. QPRC Control Register (QCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                               |