# **Advanced Products**

FUJITSU

B MBL8282 MBL8283 Bipolar Octal Latch November 1986 Edition 4.0

### Description

The MBL8282 and MBL8283 are 8-bit bipolar latches with 3state output buffers. They can be used to implement latches, buffers or multiplexers. The MBL8283 inverts the input data at its outputs while the MBL8282 does not. Thus, all of the principle peripherals and input/output functions of a microcomputer system can be implemented with these devices.

### **Features**

- Address Latch for MBL8086, MBL8088, MBL8089, MCS-80\*, MCS-85\*, MCS-48\* Families

- High Output Drive Capability for Driving System Data Bus

- Fully Parallel 8-Bit Data Register and Buffer

- Transparent during Active

- Strobe 3-State Outputs

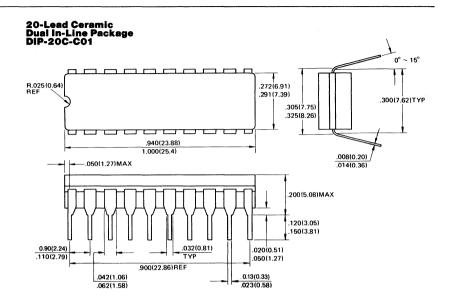

- 20-Pin DIP Package

- No Output Low Noise when Entering or Leaving High Impedance State

Portions reprinted by permission of Intel Corporation © Intel Corporation, 1983. Compilation and additional materials © 1985 by FUJITSU LIMITED, Tokyo, Japan.

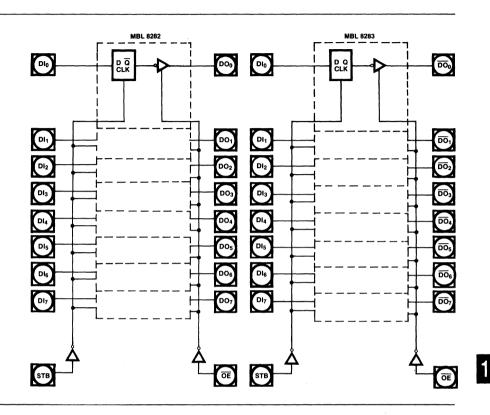

# Logic Diagrams

### **Pin Configurations**

| M                                               | ABL 8282 |                                                                                                                                                                                                  |                                        | MBL 828                                         | 3                                                                                                                                                                                                                                                                                                                         |

|-------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10 |          | 20 Vcc<br>19 DO <sub>0</sub><br>18 DO <sub>1</sub><br>17 DO <sub>2</sub><br>16 DO <sub>3</sub><br>15 DO <sub>4</sub><br>14 DO <sub>5</sub><br>13 DO <sub>6</sub><br>12 DO <sub>7</sub><br>11 STB | 50555555555555555555555555555555555555 | 1<br>2<br>3<br>4<br>5<br>5<br>7<br>8<br>9<br>10 | $\begin{array}{c c} 20 & \square & \underline{V_{CC}} \\ 19 & \underline{DO_0} \\ 18 & \underline{DO_1} \\ 17 & \square & \underline{DO_2} \\ 16 & \square & \underline{DO_3} \\ 15 & \square & \underline{DO_5} \\ 13 & \square & \underline{DO_6} \\ 12 & \square & \underline{DO_7} \\ 11 & \square & STB \end{array}$ |

FUJITSU

### **Functional Description**

The MBL8282 and MBL8283 are 8-bit latches with 3-state output buffers. Data having satisfied the setup time requirements is clocked into the data latches by strobing the STB line HIGH to LOW. Holding the STB line in its active HIGH state makes the latches appear transparent. Data is presented to the data output pins by activating the OE input line. When OE is inactive HIGH the output buffers are in their high impedance state. Enabling or disabling the output buffers will not cause negative-going transients to appear on the data output bus.

### **Pin Description**

| Pin                                                                                             | Description                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| STB                                                                                             | STROBE (Input). STB is an input control pulse used to strobe data at the data input pins $(A_0-A_7)$ into the data latches. This signal is active to HIGH to allow data in. The data is latched during the HIGH to LOW transition of STB.                                                                   |  |  |  |  |

| OE                                                                                              | OUTPUT ENABLE (Input) $\overline{OE}$ is an input control signal which<br>when active LOW enables the contents of the data latches to be<br>sent to the data output pins (B <sub>0</sub> -B <sub>7</sub> ). $\overline{OE}$ being inactive HIGH forces<br>the output buffers to their high impedance state. |  |  |  |  |

| DI <sub>0</sub> -DI <sub>7</sub>                                                                | DATA INPUT PINS (Input). Data present at these pins is clocked<br>into the data input latches when STB is strobed.                                                                                                                                                                                          |  |  |  |  |

| DO <sub>0</sub> -DO <sub>7</sub><br>(MBL 8282)<br>DO <sub>0</sub> -DO <sub>7</sub><br>(MBL8283) | DATA OUTPUT PINS (Output). When $\overline{OE}$ is low, the data in the data latches appears as inverted (MBL8283) or non-inverted (MBL8282) data on the data output pins.                                                                                                                                  |  |  |  |  |

### Absolute Maximum Ratings\*

| Parameter                            | Rating        | Unit<br>°C |  |

|--------------------------------------|---------------|------------|--|

| Temperature Under Bias               | 0° to 70°     |            |  |

| Storage Temperature                  | -65° to +150° | °C         |  |

| Supply Voltage                       | -0.5 to +7.0  | V          |  |

| All Input Voltages                   | -0.5 to +7.0  | V          |  |

| All Output Voltages (3-State Output) | +5.5          | V          |  |

| Power Dissipation                    | 1.0           | W          |  |

|                                      |               |            |  |

Note: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# D.C. Characteristics

$(V_{CC} = 5V \pm 10\%, T_A = 0^{\circ}C to 70^{\circ}C)$

| Symbol          | Parameter             | Min. | Max. | Units | Test Conditions                                                                      |

|-----------------|-----------------------|------|------|-------|--------------------------------------------------------------------------------------|

| Vc              | Input Clamp Voltage   |      | -1   | V     | I <sub>C</sub> = -5 mA                                                               |

| I <sub>CC</sub> | Power Supply Current  |      | 160  | mA    |                                                                                      |

| I <sub>F</sub>  | Forward Input Current |      | -0.2 | mA    | V <sub>F</sub> = 0.45V                                                               |

| I <sub>R</sub>  | Reverse Input Current |      | 50   | μA    | V <sub>R</sub> = 5.25V                                                               |

| VOL             | Output Low Voltage    |      | 0.45 | V     | I <sub>OL</sub> = 32 mA                                                              |

| V <sub>OH</sub> | Output High Voltage   | 2.4  |      | V     | I <sub>OH</sub> = -5 mA                                                              |

| IOFF            | Output Off Current    |      | ±50  | μA    | V <sub>OFF</sub> = 0.45V to 5.25V                                                    |

| V <sub>IL</sub> | Input Low Voltage     |      | 0.8  | V     | V <sub>CC</sub> = 5.0V See Note 1                                                    |

| VIH             | Input High Voltage    | 2.0  |      | V     | V <sub>CC</sub> = 5.0V See Note 1                                                    |

| C <sub>IN</sub> | Input Capacitance     |      | 12   | pF    | F = 1 MHz<br>V <sub>BIAS</sub> = 2.5V, V <sub>CC</sub> = 5V<br>T <sub>A</sub> = 25°C |

### Note:

1. Output Loading I<sub>OL</sub> = 32mA, I<sub>OH</sub> = -5mA, C<sub>L</sub> = 300pF.

### **A.C. Characteristics**

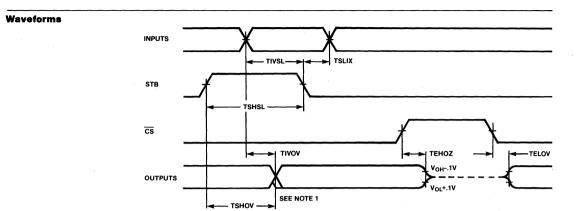

A.C. Characteristics  $(V_{CC} \in 50 \pm 10\%, T_A = 0^{\circ}C$ to 70°C, Loading: Outputs—  $I_{OL} = 32mA, I_{OH} = -5mA,$  $C_L = 300pF)$

| Symbol       | Parameter                                                                 | Min. | Max.     | Units    | Test Conditions                               |

|--------------|---------------------------------------------------------------------------|------|----------|----------|-----------------------------------------------|

| TIVOV        | Input to Output Delay<br>—Inverting (MBL8283)<br>—Non-Inverting (MBL8282) |      | 22<br>30 | ns<br>ns | <u>, , , , , , , , , , , , , , , , , , , </u> |

| TSHOV        | STB to Output Delay<br>—Inverting (MBL8283)<br>—Non-Inverting (MBL8282)   |      | 40<br>45 | ns<br>ns |                                               |

| TEHOZ        | Output Disable Time                                                       | 5    | 18       | ns       | (See Note 1)                                  |

| TELOV        | Output Enable Time                                                        | 10   | 30       | ns       | •                                             |

| TIVSL        | Input to STB Setup Time                                                   | 0    |          | ns       | -                                             |

| TSLIX        | Input to STB Hold Time                                                    | 25   |          | ns       |                                               |

| TSHSL        | STB High Time                                                             |      |          | ns       | •                                             |

| TILIH, TOLOH | Input, Output Rise Time                                                   |      | 20       | ns       | From 0.8V to 2.0V                             |

| TIHIL, TOHOL | Input, Output Fall Time                                                   |      | 12       | ns       | From 2.0V to 0.8V                             |

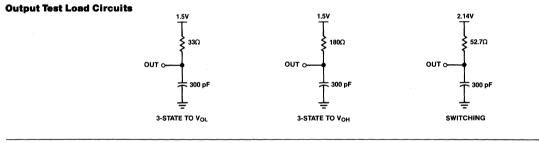

### Note:

1. See waveforms and test load circuit on following page.

### A.C. Testing Input/ Output Waveform

2.4 TEST POINTS 1.5 0.45 =

A.C. TESTING: INPUTS ARE DRIVEN AT 2.4V FOR A LOGIC "1" AND 0.4SV FOR A LOGIC "0." TIMING MEAS-UREMENTS ARE MADE AT 1.5V FOR BOTH A LOGIC "1" AND "0." INPUT RISE AND FALL TIMES ARE MEASURED FROM ).SV TO 2.0V AND ARE DRIVEN AT S  $\pm 2ns.$

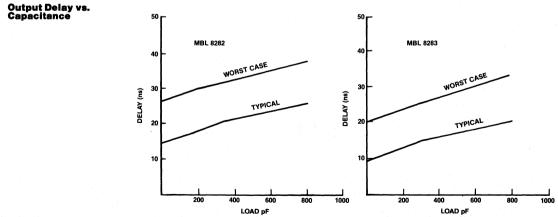

### MBL8282 MBL8283

### MBL8282 MBL8283

# Package Dimensions Dimensions in inches (millimeters)