## MC10H155

## **Advance Information**

#### CONTENT ADDRESSABLE MEMORY

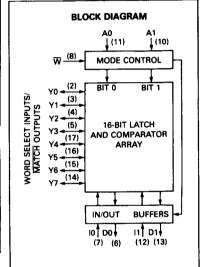

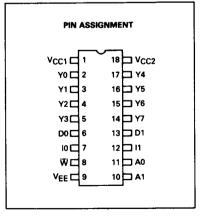

The MC10H155 is a 16-bit ECL Content Addressable Memory (CAM). The device is organized as an array of 8 words by 2 bits with each cell of the array containing an exclusive-OR comparator, a D-type latch as well as control logic. The modes of operation possible with the MC10H155 are reading, writing, associate, masked associate and the hybrid mode.

- Associate Time 7.0 ns Max

- Single Bit Masking

- Open Emitter Match Lines for Easy Bit Expansion

- Improved Noise Margin 150 mV (Over Operating Voltage and Temperature Range)

- Voltage Compensated

- MECL 10K-Compatible

#### **MAXIMUM RATINGS**

| Characteristic                                | Symbol           | Rating                         | Unit |

|-----------------------------------------------|------------------|--------------------------------|------|

| Power Supply (V <sub>CC</sub> = 0)            | VEE              | -8.0 to 0                      | Vdc  |

| Input Voltage (V <sub>CC</sub> = 0)           | VI               | 0 to VEE                       | Vdc  |

| Output Current — Continuous<br>— Surge        | out              | 50<br>100                      | mA   |

| Operating Temperature Range                   | TA               | 0 to +75                       | °C   |

| Storage Temperature Range — Plastic — Ceramic | T <sub>stg</sub> | - 55 to + 150<br>- 55 to + 165 | °C   |

## ELECTRICAL CHARACTERISTICS (VEE = -5.2 V ±5%) (See Note)

|                                                                       |        | 0      | C          | 25     | °C         | 7      | 5°                |      |

|-----------------------------------------------------------------------|--------|--------|------------|--------|------------|--------|-------------------|------|

| Characteristic                                                        | Symbol | Min    | Max        | Min    | Max        | Min    | Max               | Unit |

| Power Supply Current                                                  | ΙE     |        | 135        | _      | 125        | 1      | 135               | mA   |

| Input Current High<br>Pins 2,3,4,5,7,<br>12,14,15,16,17<br>Pins 10,11 | linH   | _      | 380<br>435 | _      | 240<br>270 |        | 240<br>270<br>250 | Αц   |

| Pin 8 Input Current Low                                               | inL    | 0.5    | 400        | 0.5    | 250        | 0.3    | 250               | μА   |

| High Output Voltage                                                   | VOH    | - 1.02 | - 0.84     | - 0.98 | - 0.81     | - 0.92 | - 0.735           | Vdc  |

| Low Output Voltage                                                    | VOL    | - 1.95 | 1.63       | - 1.95 | 1.63       | - 1.95 | - 1.60            | Vdc  |

| High Input Voltage                                                    | VIH    | 1.17   | - 0.84     | - 1.13 | - 0.81     | - 1.07 | -0.735            | Vdc  |

| Low Input Voltage                                                     | VIL    | - 1.95 | - 1.48     | - 1.95 | - 1.48     | - 1.95 | - 1.45            | Vdc  |

#### NOTE:

Each MECL 10KH series circuit has been designed to meet the dc specifications shown in the test table, after thermal equilibrium has been established. The circuit is in a test socket or mounted on a printed circuit board and transverse air flow greater than 500 lfpm is maintained. Outputs are terminated through a 50 ohm resistor to -2.0 volts.

This document contains information on a new product. Specifications and information herein is subject to change without notice.

#### AC PARAMETERS

| AC PARAMETERS                          |                      |                                              | 0°  |                   | 2!  | 5°                | 75          | ℃                 | _    |

|----------------------------------------|----------------------|----------------------------------------------|-----|-------------------|-----|-------------------|-------------|-------------------|------|

|                                        | Cherecteristic       |                                              | Min | Max               | Min | Max               | Min         | Max               | Unit |

| Associate Time                         |                      | (I to Y) TA1<br>(A to Y) TA2                 | =   | 6.0<br>6.0        | _   | 6.0<br>6.0        |             | 7.0<br>7.0        | ns   |

| Disable Time                           |                      | (A to Y) TD1<br>(A to D) TD2<br>(Y to D) TD3 |     | 6.0<br>4.0<br>7.5 | =   | 6.0<br>4.0<br>7.5 | _<br>_<br>_ | 7.0<br>5.0<br>8.0 | ns   |

| Setup Time                             |                      | (A to W) TS2<br>(Y to W) TS3<br>(I to W) TS4 | =   | 8.0<br>3.0<br>4.0 | =   | 8.0<br>3.0<br>4.0 | <u>-</u>    | 9.0<br>4.0<br>5.0 | ns   |

| Write Pulse Width<br>Write Access Time | TS4 ≥ TW<br>TS4 ≥ TW | TW<br>(W to D) TA3<br>(I to D) TA4           | =   | 8.0<br>8.0<br>6.0 | =   | 8.0<br>8.0<br>6.0 | <u> </u>    | 9.0<br>9.0<br>7.0 | ns   |

| Hold Time                              |                      | (W to A) TH1<br>(W to Y) TH2<br>(W to I) TH3 | =   | 1.0<br>3.0<br>3.0 | =   | 1.0<br>3.0<br>3.0 | =           | 1.5<br>4.0<br>4.0 | ns   |

| Read Access Time                       | TS4 ≥ TW<br>TS4 ≥ TW | (Y to D) TA5<br>(A to D) TA6                 | =   | 6.0<br>4.0        |     | 6.0<br>4.0        | =           | 6.0<br>5.0        | ns   |

| Cycle Time, CP Rate                    | e                    |                                              | 40  | <u> </u>          | 40  |                   | 35          | <u> </u>          | MH   |

## TOUTH TAREF

| TRUTH TABLE                          | AO | A1            | 10       | 11  | W | DO | D1 | Qn0   | Qn1   | Yn                   |

|--------------------------------------|----|---------------|----------|-----|---|----|----|-------|-------|----------------------|

| Mode                                 |    | <del></del> - | <u> </u> |     |   |    | •  | 0-0   | Qn1   | Qn0 + Qn1 + Qn1 + I1 |

| Associate <sup>1</sup>               | 1  | 1 _           | 1/0      | 1/0 | Х | 0  | 0_ | Qn0   | uni   |                      |

| Associate <sup>1,2</sup><br>(Masked) | 1  | 0             | 1/0      | X   | 1 | 0  | D1 | Qn0   | Qn1   | Qn0 ⊕ 10             |

| Associate <sup>1,2</sup><br>(Masked) | 0  | 1             | ×        | 1/0 | 1 | D0 | 0  | Qn0   | Qn1   | Qn1 ⊕ l1             |

| Read <sup>2,3</sup>                  | 0  | 0             | X        | x   | 1 | D0 | D1 | Qn0   | Qn1   | 0 (Selected Address) |

| Write <sup>3,4</sup>                 | 0  | 0             | 1/0      | 1/0 | 0 | 10 | 11 | 10    | 11    | 0 (Selected Address) |

| Hybrid <sup>5</sup>                  | 1  | 0             | 1/0      | 1/0 | 0 | 0  | 11 | Qn0   | I1•₹n | Qn0 ⊕ 10             |

| Hybrid <sup>5</sup>                  | 0  | 1             | 1/0      | 1/0 | 0 | 10 | 0  | I0•₹n | Qn1   | Qn1 ⊕ I1             |

X = Don't Care

Qn0 = Contents of Address n, Bit 0 (n = 0 to 7)

Qn1 = Contents of Address n, Bit 1

- 1. 1 (High) = Mismatch of Qn  $\oplus$ I, 0 (Low) = Match of Qn  $\oplus$ I 2. D0 = Q00  $\cdot$   $\overline{Y}$ 0 + Q10  $\cdot$   $\overline{Y}$ 1 +  $\cdot \cdot \cdot \cdot$  + Q70  $\cdot$   $\overline{Y}$ 7 D1 = Q01  $\cdot$   $\overline{Y}$ 0 + Q11  $\cdot$   $\overline{Y}$ 1 +  $\cdot \cdot \cdot \cdot$  + Q71  $\cdot$   $\overline{Y}$ 7

- 3. Under normal operation, only one Y address is selected for read or write.

- 4. The write is transparent.5. At all "matched" addresses there exists a simultaneous Associate and Write.

#### **DESCRIPTION OF MODES OF OPERATION**

The MC10H155 can be operated in any of the following modes: Read, Write, Associate, Masked Associate and Hybrid. Lines Y0-Y7 can be used as either inputs (a linear word select in the read/write mode) or as outputs (indicating match/mismatch in the associate mode).

#### **Associate**

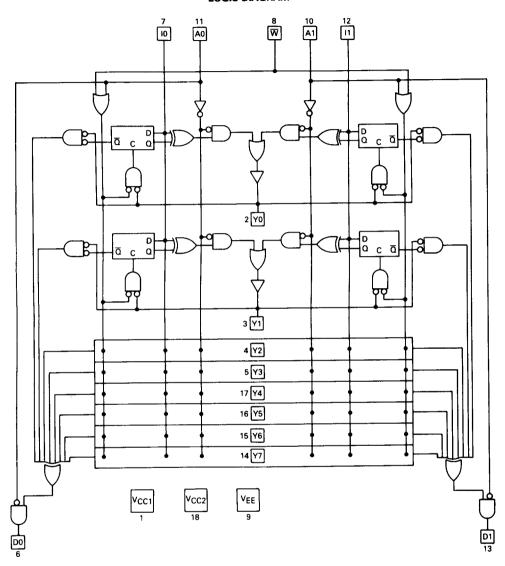

Data present on the IO and I1 inputs are compared with the latch outputs (Qn0, Qn1) of each cell. If the data input is at the same state as the latch output of a particular Y location, that Y-line goes low. Because these Y outputs are open emitters, expansion in multiples of 2 bits is obtained by tying additional MC10H155's to the Y-bus lines.

#### **Masked Associate**

This mode allows only the comparison of a single bit which is selected by bringing the corresponding A0- or A1-line high. The other bit is inhibited by holding the corresponding A0- or A1-line low.

#### Read

The particular cell output to be read is selected by bringing the associated Y-input low. Under normal op-

eration only one cell is selected to be read, all Y-inputs of deselected cells must be held high. The state of the selected cell appears on outputs D0 and D1. In the case where more than one cell is selected, the outputs of these cells are OR-ed together and appear on the D0-, D1-outputs.

#### Write

In this mode data present at the IO-, I1-inputs is transferred to the latch outputs. Since the DO-, D1-outputs are transparent, they follow the state of these IO-, I1-inputs. The particular cells to be written into are selected by taking their respective Y-inputs low. All deselected cells, Y-inputs must be held high.

#### Hvbrid

In this mode, only one of the I0- or I1-data inputs are associated with their respective latch outputs, Qn0 or Qn1. If a match exists, the corresponding Yn-line(s) will go low. As the Y-line goes low, this will address the other half of the memory for writing new data. Thus, when I0 matches Qn0, it is possible to write I1 in Qn1 or vice versa.

## LOGIC DIAGRAM

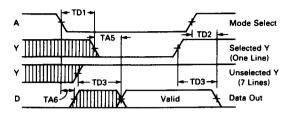

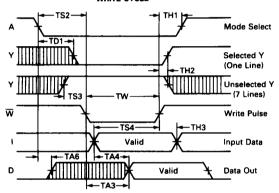

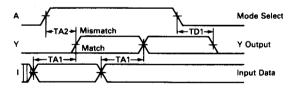

## **TIMING DIAGRAMS**

### READ CYCLE

### WRITE CYCLE

## ASSOCIATE CYCLE

T-90-20

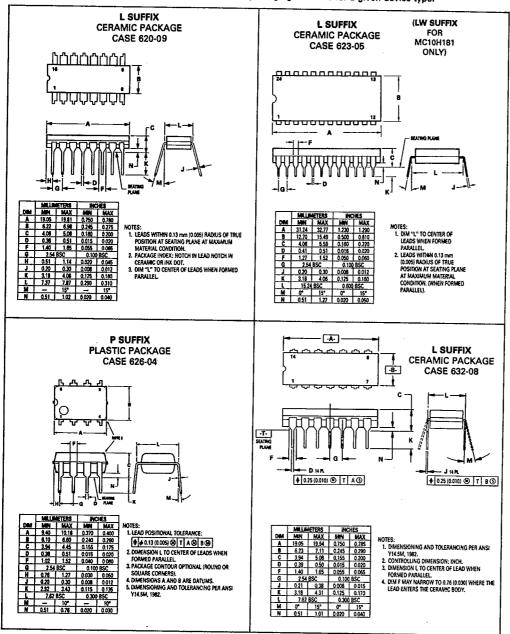

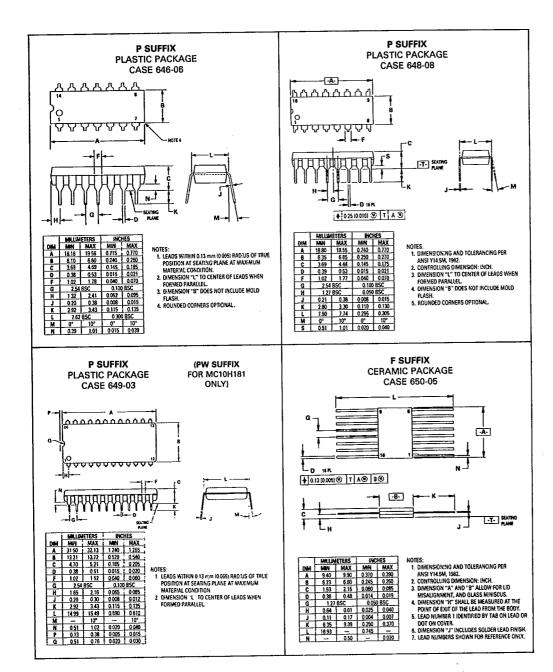

## **PACKAGE OUTLINE DIMENSIONS**

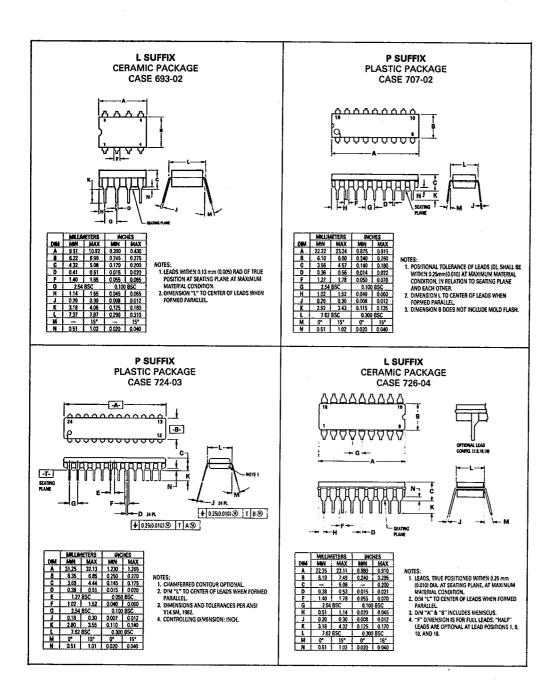

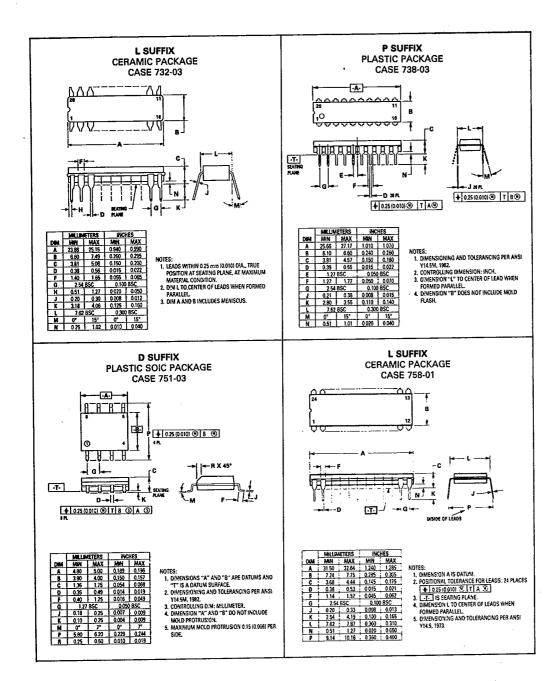

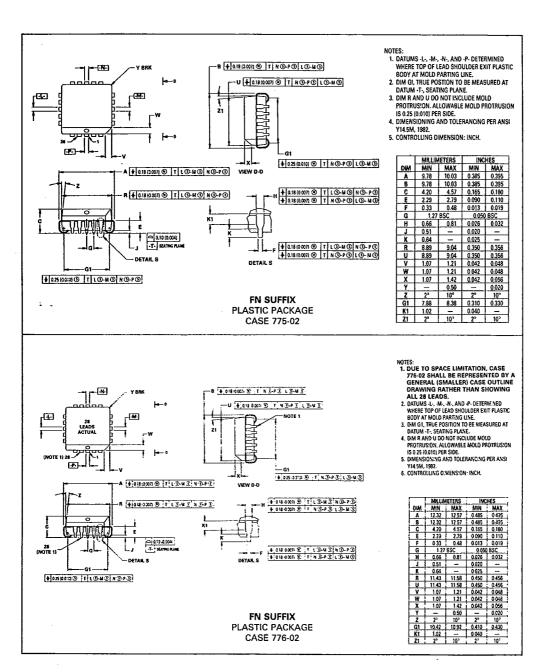

A letter suffix to the MECL logic function part number is used to specify the package style (see drawings below). See appropriate selector guide for specific packaging available for a given device type.

## **PACKAGE OUTLINE DIMENSIONS (continued)**

## **PACKAGE OUTLINE DIMENSIONS (continued)**

## **PACKAGE OUTLINE DIMENSIONS (continued)**

## **MECL Logic Surface Mount**

#### WHY SURFACE MOUNT?

Surface Mount Technology is now being utilized to offer answers to many problems that have been created in the use of insertion technology.

Limitations have been reached with insertion packages and PC board technology. Surface Mount Technology offers the opportunity to continue to advance the State-of-the-Art designs that cannot be accomplished with Insertion Technology.

Surface Mount Packages allow more optimum device performance with the smaller Surface Mount configuration. Internal lead lengths, parasitic capacitance and inductance that placed limitations on chip performance have been reduced.

The lower profile of Surface Mount Packages allows more boards to be utilized in a given amount of space. They are stacked closer together and utilize less total volume than insertion populated PC boards.

Printed circuit costs are lowered with the reduction of the number of board layers required. The elimination or reduction of the number of plated through holes in the board, contribute significantly to lower PC board prices.

Surface Mount assembly does not require the preparation of components that are common on insertion technology lines. Surface Mount components are sent directly to the assembly line, eliminating an intermediate step.

Automatic placement equipment is available that can place Surface Mount components at the rate of a few thousand per hour to hundreds of thousands of components per hour.

Surface Mount Technology is cost effective, allowing the manufacturer the opportunity to produce smaller units and offer increased functions with the same size product.

## MECL AVAILABILITY IN SURFACE MOUNT

Motorola is now offering MECL 10K and MECL 10KH in the PLCC (Plastic Leaded Chip Carrier) packages.

MECL in PLCC may be ordered in conventional plastic rails or on Tape and Reel. Refer to the Tape and Reel section for ordering details.

## TAPE AND REEL

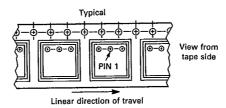

Motorola has now added the convenience of Tape and Reel packaging for our growing family of standard Integrated Circuit products. The packaging fully conforms to the latest EIA RS-481A specification. The antistatic embossed tape provides a secure cavity sealed with a peel-back cover tape.

## **GENERAL INFORMATION**

- Reel Size 13 inch (330 mm) Suffix: R2

- Tape Width 16 mmUnits/Reel 1000

## MECHANICAL POLARIZATION

### ORDERING INFORMATION

- Minimum Lot Size/Device Type = 3000 Pieces.

- No Partial Reel Counts Available.

- To order devices which are to be delivered in Tape and Reel, add the appropriate suffix to the device number being ordered.

#### **EXAMPLE:**

## ORDERING CODE

MC10100FN MC10100FNR2 MC10H100FN MC10H100FNR2 MC12015D MC12015DR2

## SHIPMENT METHOD

Magazines (Rails)

13 inch Tape and Reel

Magazines (Rails)

13 inch Tape and Reel

Magazines (Rails)

13 inch Tape and Reel

# DUAL-IN-LINE PACKAGE TO PLCC PIN CONVERSION DATA

The following tables give the equivalent I/O pinouts of Dual-In-Line (DIL) packages and Plastic Leaded Chip Carrier (PLCC) packages.

## Conversion Tables

| 16 PIN DIL<br>20 PIN PLCC | 1 | 2  | 3 | 4   | 5  | 6 | 7 | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 |    |    |    |    |    |    |    |    |

|---------------------------|---|----|---|-----|----|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 20 PIN PLCC               | 2 | 3  | 4 | 5   | 7  | 8 | 9 | 10 | 12 | 13 | 14 | 15 | 17 | 18 | 19 | 20 |    |    |    |    |    |    |    |    |

| 20 PIN DIL                | 1 | 2  | 3 | 4   | 5  | 6 | 7 | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 |    |    |    |    |

| 20 PIN DIL<br>20 PIN PLCC | 1 | 2  | 3 | 4   | 5  | 6 | 7 | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 |    |    |    |    |

| 24 PIN DII                | 1 | 12 | 3 | ا ا | ls | 6 | 7 | la | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 |

| 24 PIN DIL<br>28 PIN PLCC | 2 | 3  | 4 | 5   | 6  | 7 | 9 | 10 | 11 | 12 | 13 | 14 | 16 | 17 | 18 | 19 | 20 | 21 | 23 | 24 | 25 | 26 | 27 | 28 |