# MC33664

### Isolated network high-speed transceiver

Rev. 5.0 — 27 August 2024

Product data sheet

### 1 General description

The MC33664 is a SMARTMOS transceiver physical layer transformer driver designed to interface a microcontroller conveniently to a high speed isolated communication network. MCU serial peripheral interface (SPI) data bits are directly converted to pulse bit information and transferred to the bus network.

Slave response messages use the same structure to send pulse bit information to the MC33664, which is converted and sent back to the MCU as a SPI bit stream.

#### 2 Features and benefits

- · 2.0 Mbit/s isolated network communication rate

- · Dual SPI architecture for message confirmation

- · Robust conducted and radiated immunity with wake-up

- 3.3 V and 5.0 V compatible logic thresholds

- · Low sleep mode current with automatic bus wake-up

- · Ultra-low radiated emissions

### 3 Applications

- · Automotive communication network

- · Industrial communication network

- · Utility vehicle battery systems

- · Forklift/mining battery systems

- · Battery backup systems

# 4 Ordering information

Table 1. Ordering information

| Type number                  | Package |                                                                                           |                       |          |

|------------------------------|---------|-------------------------------------------------------------------------------------------|-----------------------|----------|

|                              | Name    | Description                                                                               | T <sub>amb</sub> [°C] | Version  |

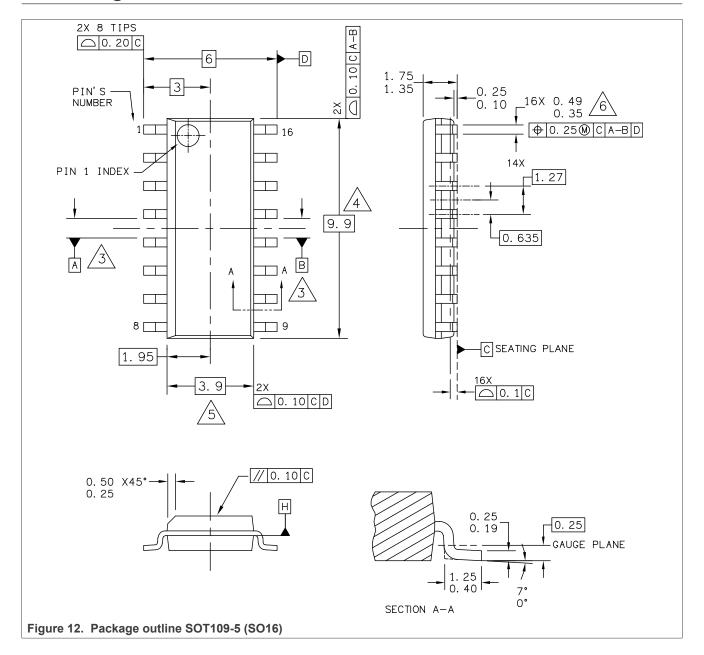

| MC33664ATL1EG <sup>[1]</sup> | SO16    | plastic small outline package; 16 leads; 1.27 mm<br>pitch; body 9.9 mm × 3.9 mm × 1.75 mm | -40 to +125           | SOT109-5 |

<sup>[1]</sup> To order parts in tape and reel, add R2 suffix to the part number.

Isolated network high-speed transceiver

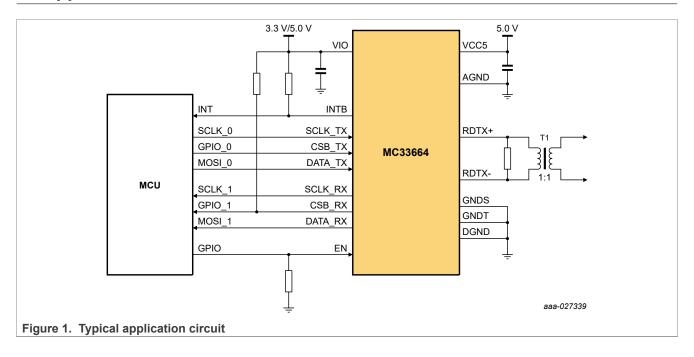

# 5 Application circuit

Isolated network high-speed transceiver

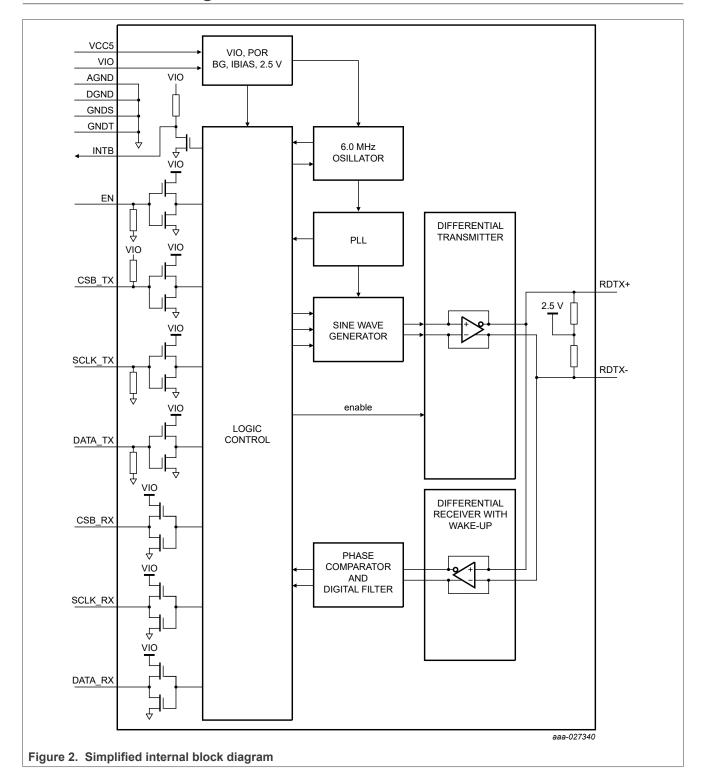

## 6 Internal block diagram

Isolated network high-speed transceiver

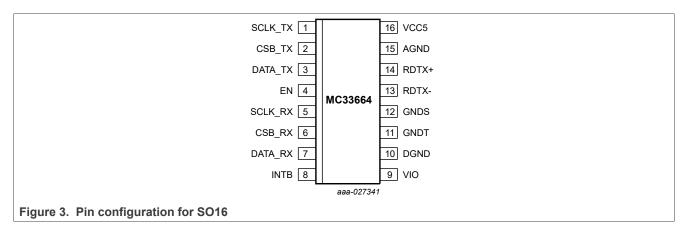

# 7 Pinning information

# 7.1 Pinning

### 7.2 Pin description

Table 2. Pin description

| Symbol  | Pin | Туре   | Description                                                                        |

|---------|-----|--------|------------------------------------------------------------------------------------|

| SCLK_TX | 1   | input  | SPI transmit clock from the microcontroller to the MC33664                         |

| CSB_TX  | 2   | input  | SPI transmit chip select from the microcontroller to the MC33664                   |

| DATA_TX | 3   | input  | SPI transmit data from the microcontroller to the MC33664                          |

| EN      | 4   | input  | enable control pin for the MCU to control the MC33664 to Sleep mode or Normal mode |

| SCLK_RX | 5   | output | message receive SPI clock output to the microcontroller                            |

| CSB_RX  | 6   | output | message receive SPI chip select output to the microcontroller                      |

| DATA_RX | 7   | output | message receive SPI data output to the microcontroller                             |

| INTB    | 8   | output | digital interrupt pin used to trigger MCU wake-ups                                 |

| VIO     | 9   | power  | digital 3.3 V/5.0 V power to the IC                                                |

| DGND    | 10  | ground | digital ground                                                                     |

| GNDT    | 11  | ground | terminate to ground                                                                |

| GNDS    | 12  | ground | substrate ground; terminate to ground                                              |

| RDTX-   | 13  | I/O    | transformer communication bi-directional bus                                       |

| RDTX+   | 14  | I/O    | transformer communication bi-directional bus                                       |

| AGND    | 15  | ground | analog ground                                                                      |

| VCC5    | 16  | input  | 5.0 V input supply                                                                 |

Isolated network high-speed transceiver

# 8 Ratings and operating requirements relationship

The operating voltage range pertains to the VCC5 and VIO pins referenced to the AGND and DGND pins.

Table 3. Ratings versus operating requirements

| Fatal range                                                 | Lower limited operating range                                                                                                                                        | Normal operating range                                                                          | Upper limited operating range                                                                                             | Fatal range                                                                  |

|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| V <sub>PWR</sub> < -0.3 V<br>Permanent failure<br>may occur | $4.5 \ V \le V_{CC5} \le 4.75 \ V$ no permanent failure, but IC functionality is not guaranteed $0 \ V \le V_{CC5} \le 4.5 \ V$ $0 \ V \le V_{IO} \le 3.1 \ V$ reset | 4.75 V ≤ V <sub>CC5</sub> ≤ 5.5 V<br>3.1 V ≤ V <sub>IO</sub> ≤ 5.5 V<br><b>100 % functional</b> | $5.5 \text{ V} \le \text{V}_{\text{CC5}} \le 7.0 \text{ V}$<br>$5.5 \text{ V} \le \text{V}_{\text{IO}} \le 7.0 \text{ V}$ | 7.0 V ≤ V <sub>CC5</sub> 7.0 V ≤ V <sub>IO</sub> permanent failure may occur |

|                                                             | handli                                                                                                                                                               | ng range; no permanen                                                                           | t failure                                                                                                                 |                                                                              |

## 9 Limiting values

#### Table 4. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

All voltages are respect to reference ground (AGND and DGND) unless otherwise noted. Exceeding these ratings may cause malfunction or permanent damage to the device.

| Symbol                                                            | Parameter                                       | Conditions                | Min                 | Max                   | Unit |

|-------------------------------------------------------------------|-------------------------------------------------|---------------------------|---------------------|-----------------------|------|

| V <sub>IO</sub>                                                   | supply input voltage                            |                           | -0.3                | +7.0                  | V    |

| V <sub>CC5</sub>                                                  | supply input voltage                            |                           | -0.3                | +7.0                  | V    |

| EN                                                                | digital enable pin for Sleep or<br>Normal mode  |                           | -0.3                | V <sub>IO</sub> + 0.3 | V    |

| RDTX+,<br>RDTX-                                                   | communication bus                               |                           | -10                 | +10                   | V    |

| INTB                                                              | interrupt pin                                   |                           | -0.3                | V <sub>IO</sub> + 0.3 | V    |

| SCLK_TX,<br>SCLK_RX,<br>CSB_TX,<br>CSB_RX,<br>DATA_TX,<br>DATA_RX | serial peripheral interface communication ports |                           | -0.3                | V <sub>IO</sub> + 0.3 | V    |

| V <sub>ESD</sub>                                                  | electrostatic discharge                         | human body model (HBM)    | ±2000               | -                     | V    |

|                                                                   | voltage                                         | charge device model (CDM) | ±500                | -                     | V    |

|                                                                   |                                                 | CDM corner pins           | ±750                | -                     | V    |

|                                                                   |                                                 | machine model (MM)        | ±200                | -                     | V    |

|                                                                   |                                                 | RDTX+, RDTX-; HBM         | <sup>1]</sup> ±4000 | -                     | V    |

|                                                                   |                                                 | RDTX+, RDTX-; MM          | ±200                | -                     | V    |

<sup>[1]</sup> Electrostatic discharge (ESD) testing is performed in accordance with the HBM ( $C_{ZAP}$  = 100 pF,  $R_{ZAP}$  = 1500  $\Omega$ ).

Isolated network high-speed transceiver

#### 10 Thermal characteristics

Table 5. Thermal characteristics

| Symbol                    | Parameter                                                 | Conditions            | Min | Max  | Unit |

|---------------------------|-----------------------------------------------------------|-----------------------|-----|------|------|

| T <sub>amb</sub>          | ambient temperature                                       |                       | -40 | +125 | °C   |

| Tj                        | junction temperature                                      | [1                    | -40 | +150 | °C   |

| T <sub>stg</sub>          | storage temperature                                       |                       | -55 | +150 | °C   |

| T <sub>reflow(peak)</sub> | peak reflow temperature                                   | [2] [3                | _   | 260  | °C   |

| R <sub>th(j-a)</sub>      | thermal resistance from junction to ambient               | single layer (1s)     | -   | 125  | °C/W |

| R <sub>th(j-pcb)</sub>    | thermal resistance from junction to printed-circuit board | multi layer (2s2p) [5 | -   | 62   | °C/W |

<sup>[1]</sup> Junction temperature is a function of on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

#### 11 Characteristics

#### Table 6. Characteristics

Characteristic noted under conditions  $4.75 \text{ V} \le V_{CC5} \le 5.5 \text{ V}$ ,  $3.1 \text{ V} \le V_{IO} \le 5.5 \text{ V}$ ,  $-40 \text{ °C} \le T_{amb} \le 125 \text{ °C}$ , unless otherwise noted. Typical values noted reflect the approximate parameter mean at  $V_{CC5} = 5.0 \text{ V}$ ,  $V_{IO} = 3.3 \text{ V}/5.0 \text{ V}$ ,  $T_{amb} = 25 \text{ °C}$  and device operating under nominal conditions unless otherwise noted.

| Symbol                    | Parameter                        | Conditions                                                | Min  | Тур | Max  | Unit     |

|---------------------------|----------------------------------|-----------------------------------------------------------|------|-----|------|----------|

| Power supply VC           | CC5                              |                                                           | -    | 1   |      |          |

| V <sub>CC5</sub>          | supply voltage                   | fully operational                                         | 4.75 | _   | 5.5  | V        |

|                           |                                  | limited operation                                         | 4.5  | _   | 4.75 | V        |

| I <sub>VCC5(NORMAL)</sub> | supply current                   | Normal mode; EN = 1;<br>continuous transmit;<br>50 Ω load | 15   | 40  | 70   | mA       |

|                           |                                  | Normal mode; EN = 1; continuous receive                   | 2.5  | 3.0 | 3.8  | mA       |

| IVCC5(SLEEP)              | supply current                   | Sleep mode; EN = 0;<br>INTB = 5.0 V                       | 10   | 30  | 50   | μΑ       |

| VCC5 <sub>UV</sub>        | VCC5 undervoltage POR threshold  |                                                           | 4.0  | _   | 4.5  | V        |

| VCC5 <sub>UV_FLT</sub>    | VCC5 undervoltage POR filter     |                                                           | 1.0  | 2.5 | 5.7  | μs       |

| VCC5 <sub>UVHYS</sub>     | VCC5 undervoltage POR hysteresis |                                                           | 50   | 100 | 175  | mV       |

| Power supply VI           | )                                |                                                           |      |     |      | <u> </u> |

| V <sub>IO</sub>           | supply voltage                   |                                                           | 3.1  | _   | 5.5  | V        |

| VIO <sub>UV</sub>         | VIO undervoltage POR threshold   |                                                           | 2.2  | _   | 3.1  | V        |

MC33664

All information provided in this document is subject to legal disclaimers.

© 2024 NXP B.V. All rights reserved.

<sup>[2]</sup> Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

<sup>[3]</sup> Package reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For peak package reflow temperature and moisture sensitivity levels (MSL), go to <a href="http://www.nxp.com">http://www.nxp.com</a>, search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts (i.e. MC33xxxD enter 33xxx)], and review parametric.

<sup>[4]</sup> Per SEMI G38-87 and JEDEC standard JESD51-2 with the single-layer board horizontal.

<sup>[5]</sup> Indicates the maximum thermal resistance between the die and the exposed pad surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1) with the cold plate temperature used for the case temperature.

Isolated network high-speed transceiver

Table 6. Characteristics...continued

Characteristic noted under conditions  $4.75 \text{ V} \le V_{CC5} \le 5.5 \text{ V}$ ,  $3.1 \text{ V} \le V_{IO} \le 5.5 \text{ V}$ ,  $-40 \text{ °C} \le T_{amb} \le 125 \text{ °C}$ , unless otherwise noted. Typical values noted reflect the approximate parameter mean at  $V_{CC5} = 5.0 \text{ V}$ ,  $V_{IO} = 3.3 \text{ V}/5.0 \text{ V}$ ,  $T_{amb} = 25 \text{ °C}$  and device operating under nominal conditions unless otherwise noted.

| Symbol                   | Parameter                                            | Conditions                                                  | Min | Тур | Max                   | Unit |

|--------------------------|------------------------------------------------------|-------------------------------------------------------------|-----|-----|-----------------------|------|

| VIO <sub>UV_FLT</sub>    | VIO undervoltage POR filter                          |                                                             | 1.0 | 2.5 | 5.7                   | μs   |

| VIO <sub>UVHYS</sub>     | VIO undervoltage POR hysteresis                      |                                                             | 50  | 100 | 150                   | mV   |

| I <sub>VIO(SLEEP)</sub>  | VIO sleep current                                    | EN = 0; INTB = 1                                            | 0.1 | _   | 4.5                   | μA   |

| I <sub>VIO(NORMAL)</sub> | VIO Normal mode current                              | EN = 1;<br>continuous communication;<br>SPI_1 open          | 0.1 | 1.0 | 2.0                   | mA   |

| Logic transmit EN,       | CSB_TX, SCLK_TX, DATA_TX                             |                                                             |     |     |                       |      |

| V <sub>IH</sub>          | HIGH-level input voltage                             |                                                             | 1.7 | _   | V <sub>IO</sub> + 0.3 | V    |

| V <sub>IL</sub>          | LOW-level input voltage                              |                                                             | _   | _   | 0.95                  | V    |

| V <sub>hys</sub>         | hysteresis voltage                                   |                                                             | 75  | 150 | 475                   | mV   |

| R <sub>pd</sub>          | pull-down resistance                                 | EN, SCLK_TX,<br>DATA_TX                                     | 50  | 100 | 200                   | kΩ   |

| R <sub>pu</sub>          | pull-up resistance                                   | CSB_TX                                                      | 50  | 100 | 200                   | kΩ   |

| t <sub>READY</sub>       | Sleep mode to Normal mode                            | EN LOW to HIGH<br>transition to device<br>ready to transmit | _   | _   | 100                   | μs   |

| tINTB_PULSE_DELAY        | EN LOW to HIGH transition to INTB verification pulse |                                                             | _   |     | 100                   | μs   |

| t <sub>INTB_PU</sub> LSE | INTB verification pulse duration                     |                                                             | _   | 100 | _                     | μs   |

| f <sub>SCLK_TX</sub>     | SPI_0 frequency                                      | SCLK_TX                                                     | 1.9 | 2.0 | 2.1                   | MHz  |

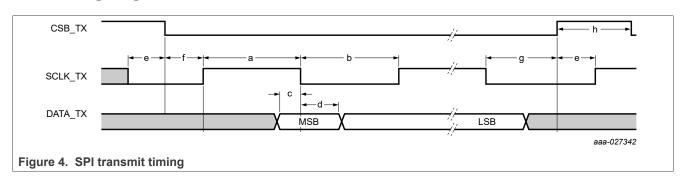

| а                        | SCLK_TX HIGH                                         | see Figure 4                                                | 240 | 250 | 260                   | ns   |

| b                        | SCLK_TX LOW                                          | see Figure 4                                                | 240 | 250 | 260                   | ns   |

| е                        | SCLK_TX to CSB_TX                                    | see Figure 4                                                |     | 250 | _                     | ns   |

| L                        | CSB_TX to start of message                           |                                                             | _   | _   | 1.1                   | μs   |

Isolated network high-speed transceiver

Table 6. Characteristics...continued

Characteristic noted under conditions  $4.75 \text{ V} \le V_{CC5} \le 5.5 \text{ V}$ ,  $3.1 \text{ V} \le V_{IO} \le 5.5 \text{ V}$ ,  $-40 \text{ °C} \le T_{amb} \le 125 \text{ °C}$ , unless otherwise noted. Typical values noted reflect the approximate parameter mean at  $V_{CC5} = 5.0 \text{ V}$ ,  $V_{IO} = 3.3 \text{ V}/5.0 \text{ V}$ ,  $T_{amb} = 25 \text{ °C}$  and device operating under nominal conditions unless otherwise noted.

| Symbol                | Parameter                                              | Conditions                                            | Min                   | Тур | Max | Unit |

|-----------------------|--------------------------------------------------------|-------------------------------------------------------|-----------------------|-----|-----|------|

| f                     | falling edge of CSB_TX to rising edge SCLK_TX          | see <u>Figure 4</u>                                   | 1.75                  | _   | _   | μs   |

|                       | CSB_TX SCLK_TX                                         |                                                       |                       |     |     |      |

| t <sub>RDTX_DLY</sub> | propagation delay SCLK_TX                              | [1]                                                   | _                     | 80  | 150 | ns   |

|                       | SCLK_TX RDTX+ RDTX-                                    |                                                       |                       |     |     |      |

| g                     | SCLK_TX LOW to CSB_TX<br>HIGH                          | see <u>Figure 4</u>                                   | 600                   | _   | _   | ns   |

| С                     | DATA_TX to SCLK_TX setup                               | see Figure 4                                          | 40                    | _   | _   | ns   |

| d                     | DATA_TX hold                                           | see Figure 4                                          | 40                    | _   | _   | ns   |

| tcsb_tx_high_eom      | propagation delay CSB_TX LOW to HIGH to end of message | [1]                                                   | _                     | _   | 150 | ns   |

| t <sub>1</sub>        | CSB_TX wake-up pulse                                   | CSB_TX LOW period                                     | 20                    | 21  | 24  | μs   |

| t <sub>2</sub>        | sequence timing  CSB_TX  T1                            | CSB_TX HIGH period                                    | 500                   | 600 | 700 | μs   |

| h                     | time between consecutive transmit messages             | see <u>Figure 4</u>                                   | 1.0                   | 3.0 | _   | μs   |

| Logic receive pins    | (CSB_RX, SCLK_RX, DATA_RX                              | ()                                                    | •                     |     | •   | •    |

| V <sub>OH</sub>       | HIGH-level output voltage                              | I <sub>OH</sub> = -2.0 mA;<br>V <sub>IO</sub> = 3.1 V | V <sub>IO</sub> - 0.4 | _   | _   | V    |

| V <sub>OL</sub>       | LOW-level output voltage                               | I <sub>OL</sub> = 2.0 mA;<br>V <sub>IO</sub> = 3.1 V  | _                     | _   | 0.4 | V    |

| f <sub>SPI</sub>      | SPI_1 frequency                                        | SCLK_RX                                               | 1.9                   | 2.0 | 2.1 | MHz  |

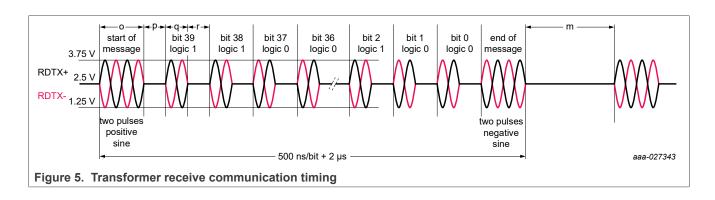

| q                     | pulse frequency                                        | see <u>Figure 5</u>                                   | 3.7                   | 4.0 | 4.3 | MHz  |

|                       | -                                                      |                                                       |                       |     |     |      |

MC33664

Isolated network high-speed transceiver

Table 6. Characteristics...continued

Characteristic noted under conditions  $4.75 \text{ V} \le V_{CC5} \le 5.5 \text{ V}$ ,  $3.1 \text{ V} \le V_{IO} \le 5.5 \text{ V}$ ,  $-40 \text{ °C} \le T_{amb} \le 125 \text{ °C}$ , unless otherwise noted. Typical values noted reflect the approximate parameter mean at  $V_{CC5} = 5.0 \text{ V}$ ,  $V_{IO} = 3.3 \text{ V}/5.0 \text{ V}$ ,  $T_{amb} = 25 \text{ °C}$  and device operating under nominal conditions unless otherwise noted.

| Symbol                     | Parameter                                                          | Conditions                               | Min   | Тур  | Max  | Unit |

|----------------------------|--------------------------------------------------------------------|------------------------------------------|-------|------|------|------|

| 0                          | start of message                                                   | see <u>Figure 5</u> [1]                  | 460   | 500  | 540  | ns   |

| а                          | SCLK_RX HIGH                                                       | [1]                                      | 230   | 250  | 270  | ns   |

| b                          | SCLK_RX LOW                                                        | [1]                                      | 210   | 250  | 290  | ns   |

| t <sub>SOM_CSB_RX</sub>    | start of message to CSB_RX  CSB_RX  RDTX+ RDTX-                    | [1]                                      | 140   | 160  | 350  | ns   |

| t <sub>EOM_CSB_RX</sub>    | end of message to CSB_RX  CSB_RX  RDTX+ RDTX-                      | [1]                                      | 40    | 60   | 160  | ns   |

| tpdb_sclk_data_rx          | pulse data bit to DATA_RX and SCLK_RX  DATA_RX SCLK_RX RDTX+ RDTX- | [1]                                      | 220   | 280  | 365  | ns   |

| r                          | start of message to MSB                                            | see Figure 5 [1]                         | _     | 250  | _    | ns   |

| p                          | (receive)                                                          | see Figure 5 [1]                         | _     | 600  | _    | ns   |

| m                          | time between consecutive messages received                         | see Figure 5                             | 1.0   | 3.0  | _    | μs   |

| Bus differential tran      | smitter/receiver                                                   | 1                                        | 1     | 1    |      | 1    |

| V <sub>RDTX(PK_DIFF)</sub> | RDTX± differential output voltage                                  | $R_L = 50 \Omega;$<br>$V_{CC5} = 4.75 V$ | 2.2   | 2.5  | 3.0  | V    |

| I <sub>RDTX</sub>          | RDTX± current limit                                                | sinking/sourcing to 2.5 V                | 65    | _    | 300  | mA   |

| V <sub>RDTX_IN(TH)</sub>   | RDTX± differential receiver                                        | rising edge                              | 0.68  | 0.74 | 0.80 | V    |

| _ 、 ,                      | threshold voltage                                                  | falling edge                             | 0.515 | 0.61 | 0.70 | V    |

| V <sub>RDTX_IN_HYST</sub>  | RDTX± differential receiver threshold voltage hysteresis           |                                          | 100   | 130  | 165  | mV   |

| V <sub>RDTX_BIAS</sub>     | transformer bias voltage                                           | transmitter in 3-state                   | 2.2   | 2.5  | 2.85 | V    |

|                            | I .                                                                | 1                                        | 1     |      | 1    | 1    |

MC33664

Isolated network high-speed transceiver

Table 6. Characteristics...continued

Characteristic noted under conditions  $4.75 \text{ V} \le V_{CC5} \le 5.5 \text{ V}$ ,  $3.1 \text{ V} \le V_{IO} \le 5.5 \text{ V}$ ,  $-40 \text{ °C} \le T_{amb} \le 125 \text{ °C}$ , unless otherwise noted. Typical values noted reflect the approximate parameter mean at  $V_{CC5} = 5.0 \text{ V}$ ,  $V_{IO} = 3.3 \text{ V}/5.0 \text{ V}$ ,  $T_{amb} = 25 \text{ °C}$  and device operating under nominal conditions unless otherwise noted.

| Symbol                     | Parameter                                                | Conditions   | Min | Тур | Max  | Unit |

|----------------------------|----------------------------------------------------------|--------------|-----|-----|------|------|

| f <sub>RDTX</sub>          | transmit/receive pulse frequency                         |              | 3.7 | 4.0 | 4.3  | MHz  |

| Wake-up receiver           |                                                          |              | ,   |     |      |      |

| V <sub>RDTXWU_TH</sub>     | RDTX± wake-up differential receiver threshold voltage    | rising edge  | 0.4 | 0.6 | 0.85 | V    |

|                            |                                                          | falling edge | 0.3 | 0.6 | 0.75 | V    |

| V <sub>RDTXWU_TH_HYS</sub> | RDTX± wake-up differential receiver threshold hysteresis |              | 50  | 100 | 150  | mV   |

| V <sub>RDTXWU_FLT</sub>    | RDTX± wake-up filter                                     |              | 20  | 50  | 80   | ns   |

<sup>[1]</sup> All bus network signals to SPI timing are referenced to 0.8 V differential threshold.

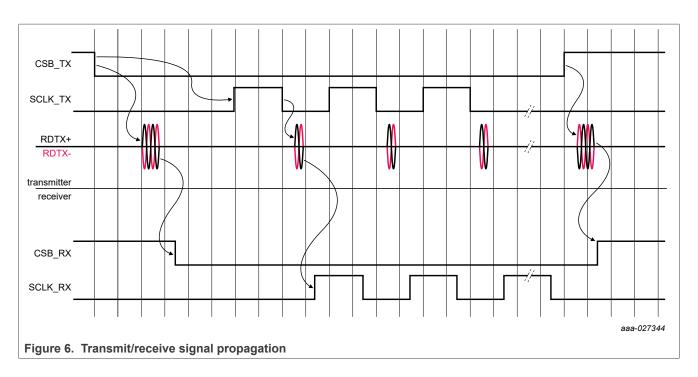

### 11.1 Timing diagrams

Isolated network high-speed transceiver

### 12 Functional description

#### 12.1 Introduction

The MC33664 provides the automotive industry a simple and convenient method for isolated high-speed differential communication. The device uses two MCU SPI ports for transmitting and receiving messages from the bus. The MC33664 is designed for half-duplex master-slave daisy chain architecture with a communication rate of up to 2.0 Mbit/s.

#### 12.2 Functional description

The MC33664 receives SPI transmit signals from the MCU and creates bit by bit pulse phase encoded differential signals which are transmitted to the bus through an isolation transformer. SPI data to transmit is determined on the falling edge of SCLK\_TX. Bus messages received by the MC33664 through the isolation transformer are converted bit by bit and transferred through the CSB\_RX, SCLK\_RX, and DATA\_RX to the MCU.

To start a message transmission, the MCU transitions CSB\_TX LOW. The falling edge of CSB\_TX is a start of message (SOM) indication to the MC33664 to initiate a message transmission. Via the falling edge of CSB\_TX, the MC33664 generates a positive phase encoded double pulse signal to the bus. With each SPI SCLK\_TX from the MCU, the MC33664 then generates a single differential positive or negative pulse, depending on the level of the DATA\_TX signal. On the rising edge of CSB\_TX, the MC33664 generates a negative phase encoded double pulse indicating an end of message (EOM) transmission.

Receiving messages from the bus begins with the SOM pulse. On reception of the SOM, the MC33664 transitions the CSB\_RX signal LOW. Each following single pulse generates a logic 1 or a logic 0 depending on the pulse phase. The bit information is clocked to the MCU through the SCLK\_RX and DATA\_RX pins. Receiving the EOM transmission ends the message and transitions the CSB\_RX signal HIGH.

Isolated network high-speed transceiver

### 12.3 Modes of operation

The MC33664 has the following modes of operation defined by the level of the VIO and EN pins:

Table 7. Modes of operation

| Mode        | EN pin | VIO pin |

|-------------|--------|---------|

| Normal mode | 1      | 1       |

| Sleep mode  | 0      | 1       |

| Reset       | X      | 0       |

In Normal mode, the MC33664 operates as a full transceiver. MCU messages transmitted on the SPI\_TX emerge on the SPI\_RX for the MCU to read. In Normal mode, the MCU has complete control of the bus through the transceiver. Before placing the transceiver into Sleep mode, it is recommended the MCU place the slave nodes in Sleep mode through communication.

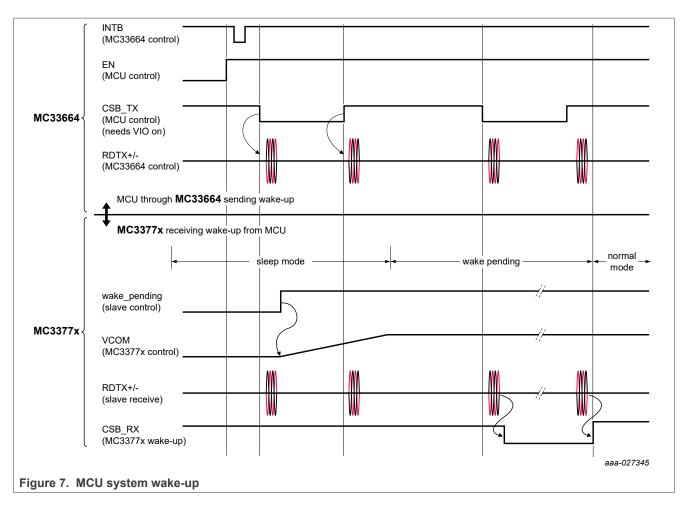

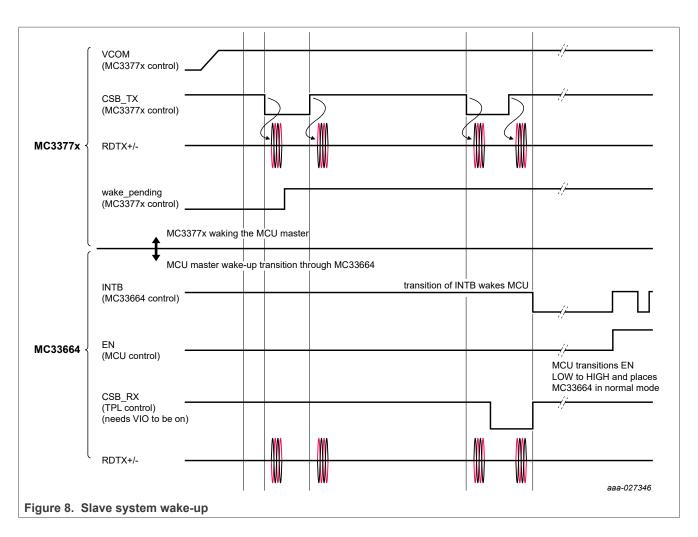

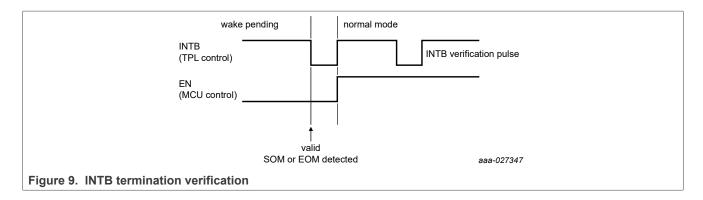

The MCU commands the MC33664 to Sleep mode by transitioning the EN pin to logic 0. In Sleep mode, the transceiver activates the INTB pin when a valid wake-up sequence is detected. The INTB pin remains LOW until the rising edge of the EN pin places the device in Normal mode. The MC33664 exits Sleep mode and enter Normal mode when the MCU enables the device through the EN pin.

**Note:** The MC33664 provides a verification pulse for termination verification of the INTB pin to the MCU on every rising edge of the EN pin.

#### 12.3.1 Unpowered mode

When VIO is below VIO<sub>UV</sub> or VCC5 is below VCC5<sub>UV</sub>, the device is in Reset mode. The RDTX± outputs are in high-impedance and the device is not able to transmit, receive, or report bus wake-up events.

#### 12.4 Wake-up pulse sequence

A wake-up pulse sequence can be generated by the master or any slave in the network system. The MCU commands a system wake-up by transitioning the EN pin from LOW to HIGH and generating two CSB\_TX transitions. No SCLK\_TX or DATA\_TX signals are necessary during the MCU controlled wake-up sequence. See timing parameters  $t_1$  and  $t_2$  in Table 6.

#### Isolated network high-speed transceiver

A wake-up pulse sequence can be generated by any slave node on the network by using the same wake-up pulse sequence. Figure 8 illustrates a wake-up generated by a slave device on the network.

Isolated network high-speed transceiver

## 13 Protection and diagnostics

The MC33664 physical layer is designed with a current limit protection feature to prevent failure of the output driver under shorted conditions. In the event the RDTX+ and RDTX- pins are shorted together, the current limit feature prevents failure of the drivers. The current limit feature also protects the output driver in the event the short occurs between the RDTX± outputs and ground. When the short conditions are removed, the device resumes normal operation.

All terminations between the MC33664 physical layer and the MCU can be confirmed. SPI transmit and receive messages are confirmed by performing a message transmit. The transmit message is received bit for bit with an additional phase delay. Performing this operation confirms the CSB\_TX, SCLK\_TX, DATA\_TX, and CSB\_RX, SCLK\_RX, DATA\_RX are terminated between the MCU and the MC33664. Additionally, the INTB and EN pin terminations are verified by transitioning the EN pin from LOW to HIGH. With each EN LOW to HIGH transition, a negative edge verification pulse is generated on the INTB pin. See t<sub>INTB\_PULSE\_DELAY</sub> and t<sub>INTB\_PULSE</sub> in Table 6 for timing parameters.

#### Isolated network high-speed transceiver

# 14 Application information

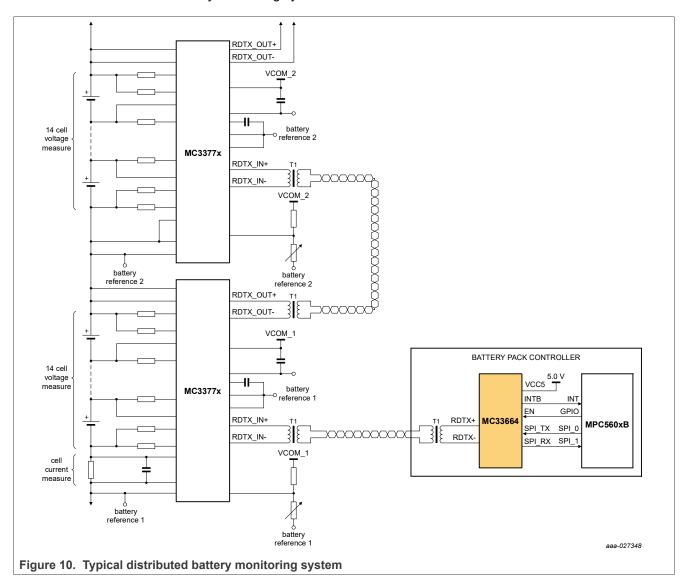

The MC33664 is designed primarily for automotive high-voltage electrical systems; however, the device can be used in any system requiring isolated communication. <u>Figure 10</u> illustrates a typical application diagram for an automotive electric vehicle battery monitoring system.

Isolated network high-speed transceiver

There are significant advantages to using transformers for isolation and communication. The most obvious benefit to the pulse transformers is the high degree of voltage isolation. Using pulse transformers allow the battery management system to achieve communication rates of 2.0 MHz with very low radiated emissions. Transformers by virtue of magnetic coupling, force the secondary signals to be true differential reducing radiated emissions and susceptibility. Recommended transformers are SUMIDA ESMIT-4180/C, PULSE HM2102NL, PULSE HM2103NL.

#### 14.1 Electromagnetic compatibility (EMC) considerations

The MC33664 is designed to minimize radiated emissions by using sine pulse wave transmission as an alternative to pulse square waves. Automotive radiated emission tests have been conducted and the data is available upon request.

The MC33664 is designed to communicate under automotive bulk current injection (BCI) and direct power injection (DPI) conditions with minimal external components.

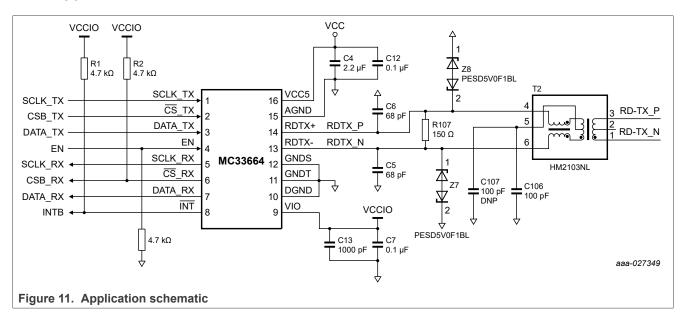

Minimal capacitance on a network system makes electrostatic discharge a constant concern for standard automotive physical layers. To protect the MC33664 from gun stress static discharge events, it is required to use a PESD5V0F1BL or equivalent ESD protection diode devices for protection on the primary side of the transformer.

### 14.2 PCB layout recommendations

Standard printed-circuit board (PCB) layout practices to be considered.

- SPI and digital interface traces routed over a continuous ground plane from the MC33664 to the MCU.

- Minimize the decoupling loop area for VCC5 to AGND, eliminating vias within the loop.

- Minimize the decoupling loop area for VIO to DGND, eliminating vias within the loop.

- Route RDTX+/RDTX- differentially from the MC33664 to the primary of the transformer over a continuous ground plane, eliminating all vias and stubs from the differential route.

- Locate the transformer as close as possible to the module connector.

- For maximum BCI performance, reduce the capacitance between the transformer and the PCB, by eliminating the ground plane under and around the transformer traces from the secondary to the connector and module connector itself. The ground must be removed from all PCB layers to be effective.

- Place the 150 Ω termination resistor close to the primary of the transformer without forming a stub.

- TVS devices should be placed close to the primary of the transformer. A minimum of two vias from the TVS

device to the ground plane minimizes the inductance for greater performance to ESD events.

#### Isolated network high-speed transceiver

### 14.3 Application schematic

Isolated network high-speed transceiver

# 15 Package outline

Isolated network high-speed transceiver

# 16 Revision history

Table 8. Revision history

| Revision      | Release date   | Modifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MC33664 v.5.0 | 27 August 2024 | changed security status to public                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.0           | 20170803       | <ul> <li>The format of this data sheet has been redesigned to comply with the new identity guidelines of NXP Semiconductors.</li> <li>Device number changed from 33664TL to MC33664</li> <li>Delete feature from list: Engineered for 5.0 meter, 15 node system</li> <li>Table 6: MCU spec text has been deleted</li> <li>Table 6: for symbol L, the reference to Figure 4 has been deleted</li> <li>Table 6: for symbol t<sub>1</sub>, the text 'MCU commanded bus wake-up' has been deleted</li> <li>Table 6: for symbol t<sub>2</sub>, the text 'Normal mode' has been deleted</li> <li>Table 6: for symbols a and b the reference to Figure 4 has been added</li> <li>Table 6: for symbols r, the text 'depends on communication frequency' has been deleted</li> <li>Table 6: for symbol p, minimum value has been changed from 600 ns to nothing, typical value has been changed from nothing to 600 ns</li> <li>Table 6: for symbols p and r, the text '250 ns blank time from SOM, 250 ns clock high, 100 ns for transmit logic to process falling of clock' has been deleted; reference to Figure 5 has been added</li> <li>Section 14.2: deleted list item 6 and changed the list to unnumbered</li> <li>Section 14.2: 300 Ω termination resistor replaced with 150 Ω termination resistor</li> <li>Added Section 14.3 "Application schematic"</li> </ul> |

| 3.0           | 12/2015        | Corrected typo for transmit/receive pulse frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|               | 11/2015        | Adjusted limits for I <sub>VCC5(NORMAL)</sub> , I <sub>VCC5(SLEEP)</sub> , VCC5 <sub>UVHYS</sub> , IIO <sub>SLEEP</sub> , CSB_TX to start of message, start of message to CSB_RX, end of message to CSB_RX, pulse data bit to DATA_RX and SCLK_RX, V <sub>RDTX_IN(TH)</sub> , V <sub>RDTX_IN_HYST</sub> , and V <sub>RDTX_BIAS</sub> Rewrote the steps in Section 14.2     Updated Freescale form and style                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2.0           | 4/2014         | Updated parameter table     Updated PCB layout recommendations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.0           | 2/2014         | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

Isolated network high-speed transceiver

## **Legal information**

#### Data sheet status

| Document status <sup>[1][2]</sup> | Product status <sup>[3]</sup> | Definition                                                                            |

|-----------------------------------|-------------------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet      | Development                   | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet    | Qualification                 | This document contains data from the preliminary specification.                       |

| Product [short] data sheet        | Production                    | This document contains the product specification.                                     |

- [1] Please consult the most recently issued document before initiating or completing a design.

- [2] The term 'short data sheet' is explained in section "Definitions".

- The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL <a href="https://www.nxp.com">https://www.nxp.com</a>.

#### **Definitions**

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

Product specification — The information and data provided in a Product data sheet shall define the specification of the product as agreed between NXP Semiconductors and its customer, unless NXP Semiconductors and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the NXP Semiconductors product is deemed to offer functions and qualities beyond those described in the Product data sheet.

#### **Disclaimers**

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at https://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**No offer to sell or license** — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

**Quick reference data** — The Quick reference data is an extract of the product data given in the Limiting values and Characteristics sections of this document, and as such is not complete, exhaustive or legally binding.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

MC33664

All information provided in this document is subject to legal disclaimers.

© 2024 NXP B.V. All rights reserved.

#### Isolated network high-speed transceiver

**HTML publications** — An HTML version, if available, of this document is provided as a courtesy. Definitive information is contained in the applicable document in PDF format. If there is a discrepancy between the HTML document and the PDF document, the PDF document has priority.

**Translations** — A non-English (translated) version of a document, including the legal information in that document, is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security — Customer understands that all NXP products may be subject to unidentified vulnerabilities or may support established security standards or specifications with known limitations. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP.

NXP has a Product Security Incident Response Team (PSIRT) (reachable at <a href="PSIRT@nxp.com">PSIRT@nxp.com</a>) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

Suitability for use in automotive applications (functional safety) -This NXP product has been qualified for use in automotive applications. It has been developed in accordance with ISO 26262, and has been ASIL classified accordingly. If this product is used by customer in the development of, or for incorporation into, products or services (a) used in safety critical applications or (b) in which failure could lead to death, personal injury, or severe physical or environmental damage (such products and services hereinafter referred to as "Critical Applications"), then customer makes the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, safety, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP. As such, customer assumes all risk related to use of any products in Critical Applications and NXP and its suppliers shall not be liable for any such use by customer. Accordingly, customer will indemnify and hold NXP harmless from any claims, liabilities, damages and associated costs and expenses (including attorneys' fees) that NXP may incur related to customer's incorporation of any product in a Critical Application.

Suitability for use in industrial applications (functional safety) — This NXP product has been qualified for use in industrial applications. It has been developed in accordance with IEC 61508, and has been SIL-classified accordingly. If this product is used by customer in the development of, or for incorporation into, products or services (a) used in safety critical applications or (b) in which failure could lead to death, personal injury, or severe physical or environmental damage (such products and services hereinafter referred to as "Critical Applications"), then customer makes the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, safety, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP. As such, customer assumes all risk related to use of any products in Critical Applications and NXP and its suppliers shall not be liable for any such use by customer. Accordingly, customer will indemnify and hold NXP harmless from any claims, liabilities, damages and associated costs and expenses (including attorneys' fees) that NXP may incur related to customer's incorporation of any product in a Critical Application.

$\ensuremath{\mathsf{NXP}}\xspace\,\ensuremath{\mathsf{B.V.}}\xspace - \ensuremath{\mathsf{NXP}}\xspace\,\ensuremath{\mathsf{B.V.}}\xspace$  is not an operating company and it does not distribute or sell products.

#### **Trademarks**

Notice: All referenced brands, product names, service names, and trademarks are the property of their respective owners.

NXP — wordmark and logo are trademarks of NXP B.V

### Isolated network high-speed transceiver

### **Tables**

| Tab. 1. | Ordering information1                       | Tab. 5.  | Thermal characteristics                | (  |

|---------|---------------------------------------------|----------|----------------------------------------|----|

| Tab. 2. | Pin description4                            | Tab. 6.  | Characteristics                        | 6  |

| Tab. 3. | Ratings versus operating requirements5      | Tab. 7.  | Modes of operation                     |    |

| Tab. 4. |                                             |          | Revision history                       |    |

| Figui   | es                                          |          |                                        |    |

| Fig. 1. | Typical application circuit2                | Fig. 8.  | Slave system wake-up                   | 14 |

| Fig. 2. | Simplified internal block diagram 3         | Fig. 9.  | INTB termination verification          | 15 |

| Fig. 3. | Pin configuration for SO164                 | Fig. 10. | Typical distributed battery monitoring |    |

| Fig. 4. | SPI transmit timing10                       | _        | system                                 | 15 |

| Fig. 5. | Transformer receive communication timing 10 | Fig. 11. | Application schematic                  | 17 |

| Fig. 6. | Transmit/receive signal propagation11       | Fig. 12. | Package outline SOT109-5 (SO16)        | 18 |

| Fig. 7. | MCU system wake-up 13                       | _        | . , ,                                  |    |

### Isolated network high-speed transceiver

### **Contents**

| 1      | General description                 | 1            |

|--------|-------------------------------------|--------------|

| 2      | Features and benefits               |              |

| 3      | Applications                        | 1            |

| 4      | Ordering information                | 1            |

| 5      | Application circuit                 | 2            |

| 6      | Internal block diagram              | 3            |

| 7      | Pinning information                 |              |

| 7.1    | Pinning                             |              |

| 7.2    | Pin description                     |              |

| 8      | Ratings and operating requirements  |              |

|        | relationship                        | 5            |

| 9      | Limiting values                     |              |

| 10     | Thermal characteristics             | <del>6</del> |

| 11     | Characteristics                     | 6            |

| 11.1   | Timing diagrams                     | 10           |

| 12     | Functional description              | 11           |

| 12.1   | Introduction                        | 11           |

| 12.2   | Functional description              |              |

| 12.3   | Modes of operation                  | 12           |

| 12.3.1 | Unpowered mode                      | 12           |

| 12.4   | Wake-up pulse sequence              | 12           |

| 13     | Protection and diagnostics          |              |

| 14     | Application information             | 15           |

| 14.1   | Electromagnetic compatibility (EMC) |              |

|        | considerations                      |              |

| 14.2   | PCB layout recommendations          |              |

| 14.3   | Application schematic               |              |

| 15     | Package outline                     |              |

| 16     | Revision history                    | 19           |

|        | Legal information                   | 20           |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.