## **8-BIT PARITY TREE**

## MC4308 MC4008

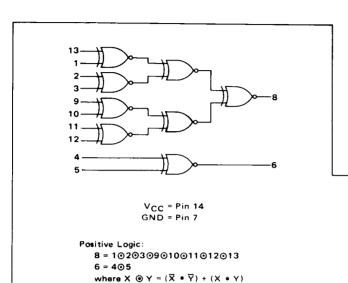

This device consists of seven Exclusive NOR gates connected to check even parity. The output will be in the logic "1" state as long as the "1" state is present on an even number of inputs. The additional Exclusive NOR gate can be used to connect two 8-bit parity trees to form a 16-bit parity tree, or it can be used to convert the parity tree to check odd parity by connecting one gate input to the output of the parity tree and grounding the other input. This conversion can also be accomplished by connecting a simple inverter to the output of the parity tree.

Input Loading Factor = 2

Output Loading Factor = 10

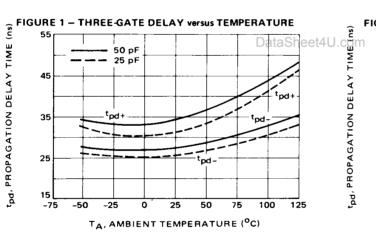

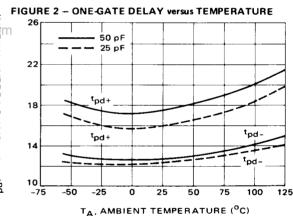

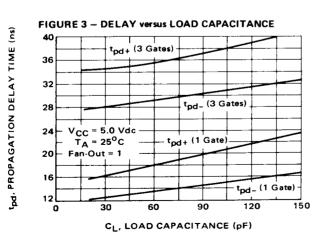

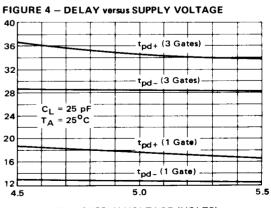

Total Power Dissipation = 150 mW typ/pkg Propagation Delay Time = 15-30 ns typ

## TYPICAL PROPAGATION DELAY TIMES

V<sub>CC</sub>, SUPPLY VOLTAGE (VOLTS)

104

tod, PROPAGATION DELAY TIME (ns)

www.DataSheet4U.com

DataSheet4U.com

t4U\_com